TM 7705 Service Manual

16 bit

模

数转换器 TM7705

一、特性描述

TM7705 是应用于低频测量的 2/3 通道的模拟前端。该器件可以接受直接来自传感器

的低电平的输入信号,然后产生串行的数字输出。利用Σ-Δ转换技术实现了 16 位无丢失代码

性能。选定的输入信号被送到一个基于模拟调制器的增益可编程专用前端。片内数字滤波器

处理调制器的输出信号。通过片内控制寄存器可调节滤波器的截止点和输出更新速率,从而

对数字滤波器的第一个陷波进行编程。

TM7705 只需 2.7~3.3V 或 4.75~5.25V 单电源。TM7705 是双通道全差分模拟输入,

带有一个差分基准输入。当电源电压为 5V、基准电压为 2.5V 时,该器件都可将输入信号

范围从 0~+20mV 到 0~+2.5V 的信号进行处理。还可处理±20mV~±2.5V 的双极性输入

信号,对于 TM7705 是以 AIN(-)输入端为参考点。当电源电压为 3V、基准电压为 1.225V

时,可处理 0~+10mV 到 0~+1.225V 的单极性输入信号,它的双极性输入信号范围是

±10mV 到±1.225V。因此,TM7705 可以实现 2/3 通道系统所有信号的调理和转换。

TM7705 是用于智能系统、微控制器系统和基于 DSP 系统的理想产品。其串行接口可

配置为三线接口。增益值、信号极性以及更新速率的选择可用串行输入口由软件来配置。该

器件还包括自校准和系统校准选项,以消除器件本身或系统的增益和偏移误差。

CMOS 结构确保器件具有极低功耗,掉电模式减少等待时的功耗至 20μW(典型值)。

TM7705 采用 16 脚塑料双列直插(DIP)、16 脚宽体(0.3 英寸)SOIC、16 脚 TSSOP、16

脚SOP和16脚SSOP封装。

二、功能特点

TM7705:2个全差分输入通道的ADC

16位无丢失代码

0.003%非线性

可编程增益前端

增益:1~128

三线串行接口

有对模拟输入缓冲的能力

2.7~3.3V或4.75~5.25V工作电压

3V电压时,最大功耗为1mW

等待电流的最大值为8μA

16脚DIP、SOIC(宽体) 、TSSOP、SOP和SSOP封装

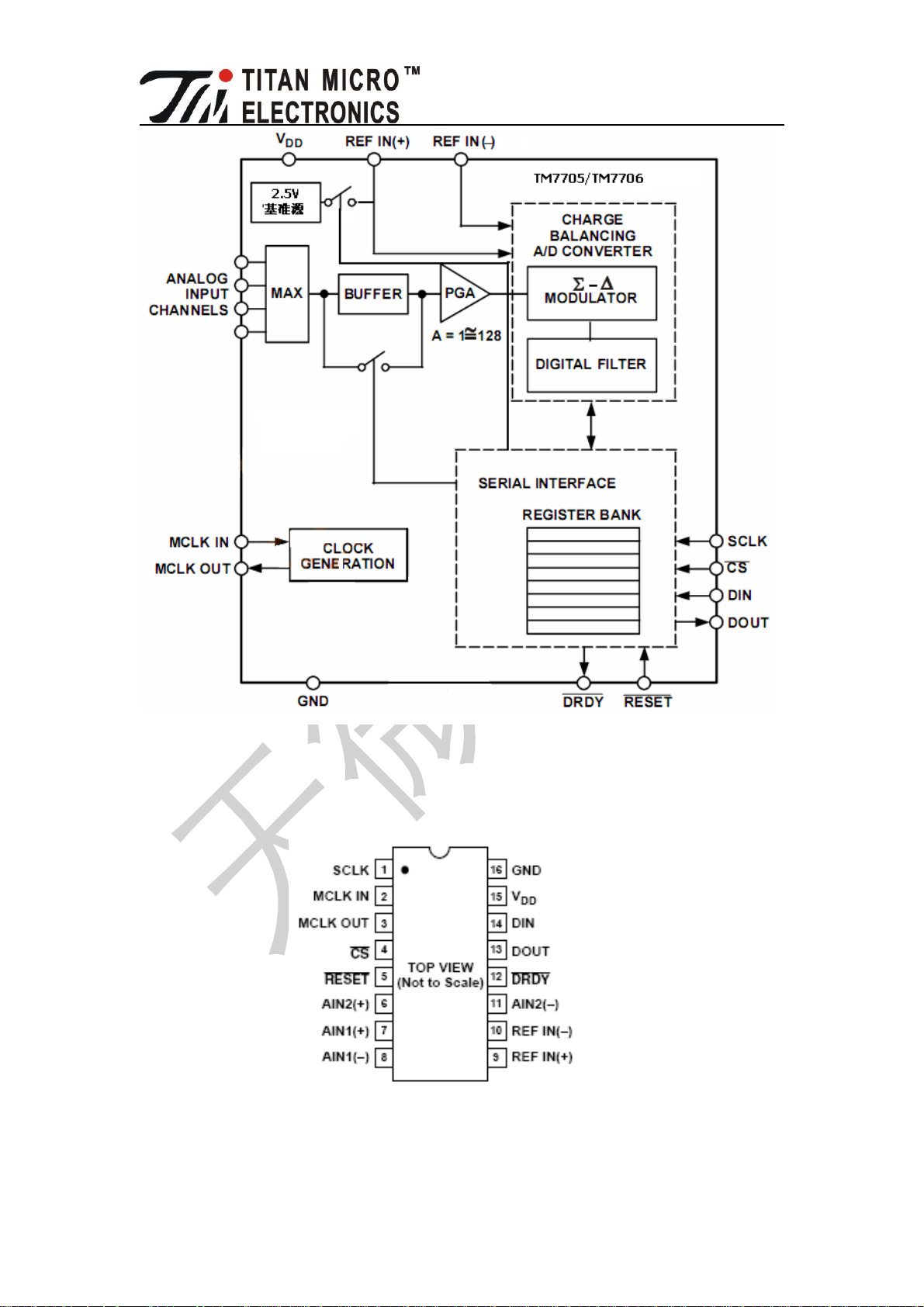

三、功能方框图

Titan Micro Electronics www.titanmec.com -

©

V1.2

1

-

16 bit

模

数转换器 TM7705

四、引脚排列与功能

TM7705 的引脚排列

TM7705

Titan Micro Electronics www.titanmec.com -

©

V1.2

2

-

16 bit

模

数转换器 TM7705

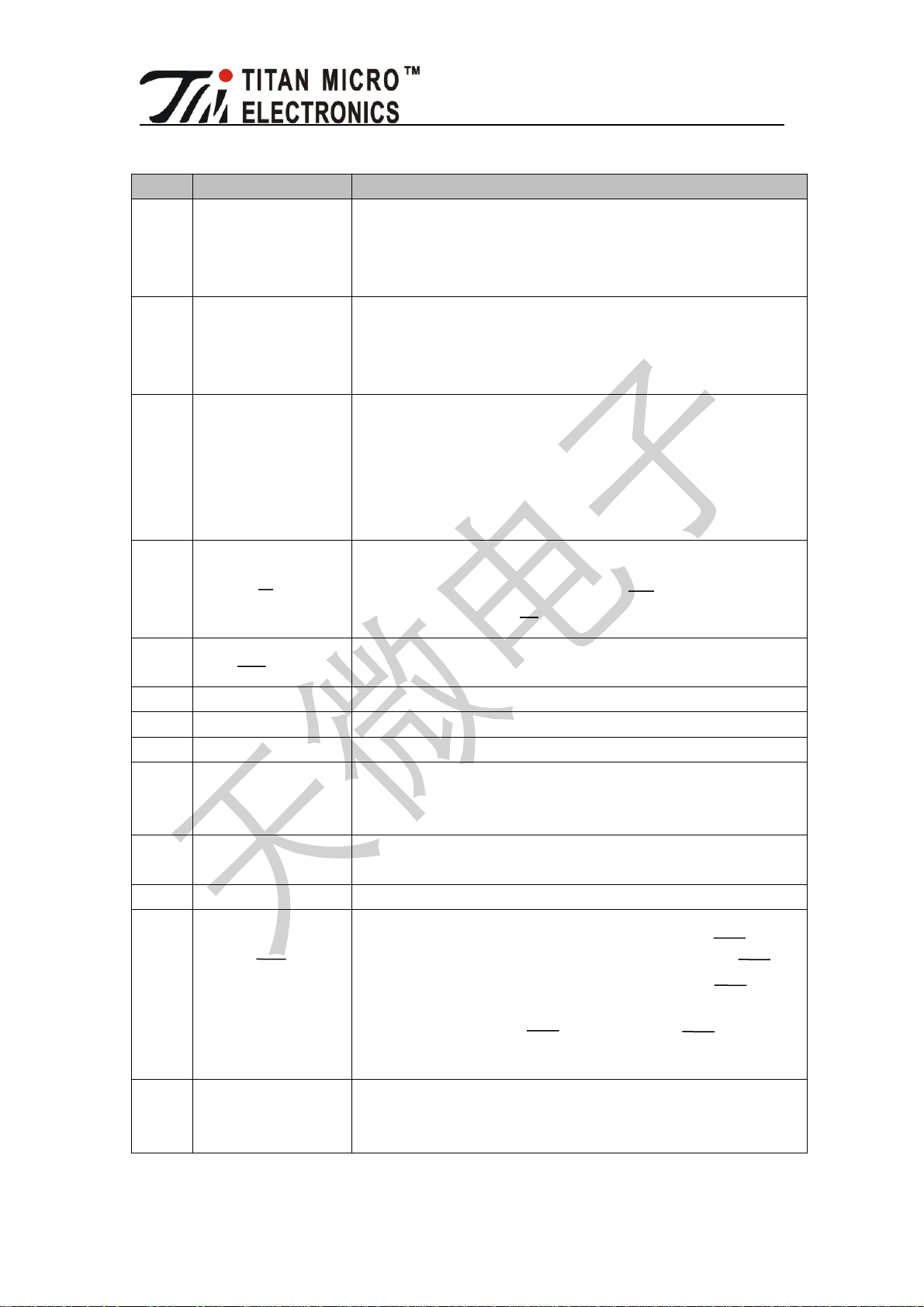

五、引脚功能

编号 名称 功能

串行时钟,施密特逻辑输入。将一个外部的串行时钟加于这一输入端口,

1SCLK

2MCLKIN

3MCLKOUT

4

5

6 AIN2(+)[AIN1] 对于 TM7705,差分模拟输入通道 2 的正输入端。

7 AIN1(+)[AIN2] 对于 TM7705,差分模拟输入通道 1 的正输入端。

8 AIN1(-)[COMMON] 对于 TM7705,差分模拟输入通道 1 的负输入端;

9 REF IN(+)

10 REF IN(-)

11 AIN2(-)[AIN3] 对于 TM7705,差分模拟输入通道 2 的负输入端。

12

13 DOUT

CS

RESET

DRDY

以访问 TM7705 的串行数据。该串行时钟可以是连续时钟以连续的脉冲

串传送所有数据 。反之 ,它也可以是非连续时钟 ,将信息以小批型数

据发送给 TM7705

为转换器提供主时钟信号。能以晶体/谐振器或外部时钟的形式提供。晶

体/谐振器可以接在 MCLK IN 和MCLK OUT 二引脚之间。此外,MCLK

IN 也可用 CMOS 兼容的时钟驱动,而 MCLK OUT 不连接。时钟频率的

范围为 500kHz~5MHz

当主时钟为晶体/谐振器时,晶体/谐振器被接在 MCLK IN 和 MCLK OUT

之间。如果在 MCLK IN 引脚处接上一个外部时钟,MCLK OUT 将提供

一个反相时钟信号。这个时钟可以用来为外部电路提供时钟源,且可以

驱动一个 CMOS 负载。如果用户不需要,MCLK OUT 可以通过时钟寄存

器中的 CLK DIS 位关掉。这样,器件不会在 MCLK OUT 脚上驱动电容负

载而消耗不必要的功率

片选,低电平有效的逻辑输入,选择 TM7705。将该引脚接为低电平,

TM7705 能以三线接口模式运行 (以 SCLK、DIN 和 DOUT 与器件接口)。

在串行总线上带有多个器件的系统中,可由 CS 对这些器件作出选择,

或在与 TM7705 通信时,CS 可用作帧同步信号

复位输入。低电平有效的输入,将器件的控制逻辑、接口逻辑、校准系

数、数字滤波器和模拟调制器复位至上电状态

基准输入端。TM7705 差分基准输入的正输入端。基准输入是差分的,并

规定 REF IN (+)必须大于 REF IN (-)。REF IN (+)可以取 VDD

和 GND 之间的任何值

基准输入端。TM7705 差分基准输入的负输入端。REF IN(- )可以取

VDD 和 GND 之间的任何值,且满足 REF IN(+ )大于 REF IN (- )

逻辑输出。这个输出端上的逻辑低电平表示可从 TM7705 的数据寄存器

获取新的输出字。完成对一个完全的输出字的读操作后,DRDY 引脚立

即回到高电平。如果在两次输出更新之间,不发生数据读出,DRDY 将

在下一次输出更新前 500 ×tCLKIN 时间返回高电平。当 DRDY 处于高

电平时,不能进行读操作,以免数据寄存器中的数据正在被更新时进行

读操作。当数据被更新后,DRDY 又将返回低电平。DRDY 也用来指示

何时 TM7705 已经完成片内的校准序列

串行数据输出端。从片内的输出移位寄存器读出的串行数据由此端输出。

根据通讯寄存器中的寄存器选择位,移位寄存器可

容纳来自通讯寄存器、时钟寄存器或数据寄存器的信息

Titan Micro Electronics www.titanmec.com -

©

V1.2

3

-

16 bit

模

串行数据输入端。向片内的输入移位寄存器写入的串行数据由此输入。

14 DIN

15 VDD 电源电压,+2.7V~+5.25V

16 GND 内部电路的地电位基准点

根据通讯寄存器中的寄存器选择位,输入移位寄存器中的数据被传送到

设置寄存器、时钟寄存器或通讯寄存器

数转换器 TM7705

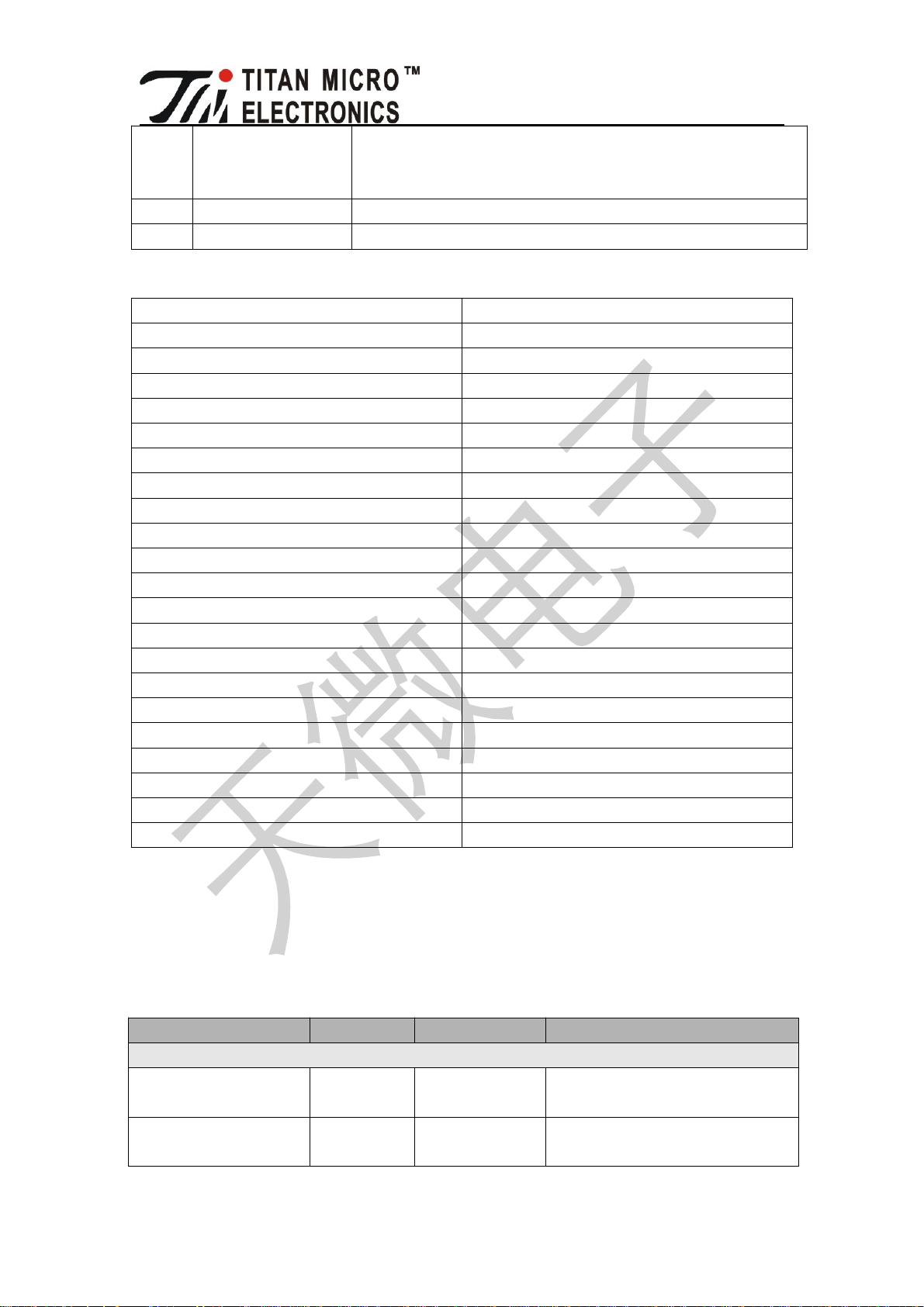

六、极限参数(TA = +25℃,除非另有说明)

VDD 对 GND -0.3V ~+7V

模拟输入电压对 GND -0.3V ~V

基准输入电压对 GND -0.3V ~V

数字输入电压对 GND -0.3V ~V

数字输出电压对 GND -0.3V ~V

工作温度范围 (商业级,B ) -40℃~+85℃

储存温度范围 -65℃~+150℃

结温 +150℃

功耗 (塑料 DIP 封装) 450mW

θJA 热阻 105℃/W

引脚温度 (焊接 ,10 秒) +260℃

功耗(塑料 SOIC 封装) 450mW

θJA 热阻 75℃/W

引脚温度 (焊接 )

汽相 (60 秒) +215℃

红外线 (15 秒) +220℃

功耗 (SSOP 封装) 450mW

θJA 热阻 139℃/W

引脚温度(焊接)

汽相(60 秒) +215℃

红外线(15 秒) +220℃

抗 ESD >4000V

注:强度超出所列的极限参数可能导致器件的永久性损坏。这些仅仅是极限参数,并不意味

着在极限条件下或在任何其它超出推荐工作条件所示参数的情况下器件能有效地工作。延长

在极限参数条件下的工作时间会影响器件的可靠性。

DD

DD

DD

DD

+0.3V

+0.3V

+0.3V

+0.3V

七、电特性

(VDD=+3V 或+5V,REF IN(+)=+1.225V;REF IN(-)=GND,MCLK IN =2.4576MHz,

T

A=TMIN~TMAX

Parameter B Version

STATIC PERFORMANCE

No Missing Codes 16 Bits min

Output Noise

Titan Micro Electronics www.titanmec.com -

©

,除非另有说明)

See Tables I

and III

1

Units Conditions/Comments

Guaranteed by Design. Filter

Notch < 60 Hz

Dependson Filter Cutoffs and

Selected Gain

V1.2

4

-

16 bit

模

数转换器 TM7705

Integral Nonlinearity

2

±0.003 %of FSR max

Unipolar Offset Error See Note3

Unipolar Offset Drift

4

0.5 μV/℃ typ

Bipolar Zero Error See Note 3

Bipolar Zero Drift

4

0.5 μV/℃ typ For Gains1,2and4

0.1 μV/℃ typ For Gains8,16,32,64and128

5

Positive Full-Scale Error

Full-Scale Drift

Gain Error

Gain Drift

4.6

7

4.8

Bipolar Negative Full

-Scale Error

2

Bipolar Negative Full

-Scale Drift

4

See Note3

0.5 μV/℃ typ

See Note3

0.5

ppm of FSR/ ℃

typ

±0.003 %of FSR/℃ typ Typically±0.001%

1μV/℃typForGainsof1to4

0.6 μV/℃ typ For Gains of 8 to 128

ANALOG INPUTS/REFERENCE INPUTS

Input Common-Mode Rejection(CMR)

VDD=5V

Gain=1 96 dB typ

Gain=2 105 dB typ

Gain=4 110 dB typ

Gain=8 128 130 dB typ

=3V

V

DD

Gain=1 105 dB typ

Gain=2 110 dB typ

Gain=4 120 dB typ

Gain=8 128 130 dB typ

Normal-Mode50Hz

Rejection

2

Normal-Mode60Hz

Rejection

2

Common-Mode 50Hz

Rejection

2

Common-Mode 60Hz

Rejection

2

Absolute/Common-Mo

de REF IN Voltage

2

Absolute/Common-Mo

de AIN Voltage

2。9

98 dB typ

98 dB typ

150 dB typ

150 dB typ

GND to V

DD

GND—30mV Vmin BUF Bit of Setup Register=0

2

Vmin to V mas

Filter Notch < 60 Hz. Typically

0.0003%

Specifications for AIN and REF

IN UnlessNoted

For Filter Notches of

25Hz,50Hz,±0.02×f

For Filter Notches of

20Hz,60Hz,±0.02×f

For Filter Notches of

25Hz,50Hz,±0.02×fNOTCH

For Filter Notches of

20Hz,60Hz,±0.02×fNOTCH

NOTCH

NOTCH

Titan Micro Electronics www.titanmec.com -

©

V1.2

5

-

16 bit

模

数转换器 TM7705

VDD+30mV Vmax

Absolute/Common-Mo

de AIN Voltage

2。9

GND+50mV Vmin BUF Bit of Setup Register=1

VDD—1.5V Vmax

2

AIN DC Input Current

AIN

SamplingCapacitance

AIN Differential Voltage

10

Range

1nAmax

10 pF max

2

0to+V

N

±V

/GAI

REP

11

/GAIN nom Bipolar Input Range(B/U Bit of

REP

nom

Unipolar Input Range(B/U Bit of

Setup Register=1)

Setup Register=0)

AIN Input Sampling

Rate,fs

GAIN×f

CLKIN

/

For Gains of 1 to 4

64

f

/8 For Gains of 8 to 128

CLKIN

Referencelnput Range

REFIN(+)—REFIN( - )Volt

age

REFIN(+)—REFIN( - )Volt

age

REF IN Input

SamplingRate, fs

1/1.75 Vmin/max

1/3.5 Vmin/max

f

/64

CLKIN

V

=2.7Vto3.3V.V

DD

Specifled Performance

V

=4.75Vto5.25V.V

DD

Specifled Performance

LOGIC INPUTS

Input Current

All Inputs Except MCLKIN±1 μA max Typically±20nA

=1.225±1% for

REF

=2.5±1% for

REF

MCLK ±10 μA max Typically±20μA

All Inputs Except SCLK

and MCLK IN

Input Low Voltage 0.8 Vmax VDD=5V

V

INL,

0.4 Vmax V

Input High Voltage 2.0 Vmin VDD=3V and 5V

V

INL,

SCLK Only(Schmitt

=3V

DD

=5V NOMINAL

V

DD

Triggered Input)

V

T+

_ 0.8/1.4 Vmin/V max

V

T

_ 0.4/0.8 Vmin/V max

V

T+—VT

1.4/3 Vmin/V max

SCLK Only(Schmitt

Triggered Input)

V

T+

_ 0.4/1.1 Vmin/Vmax

V

T

V

_ 0.375/0.8 Vmin/Vmax

T+VT

MCLK IN Only V

Titan Micro Electronics www.titanmec.com -

©

1/2.5 Vmin/Vmax

=5V NOMINAL

DD

V1.2

6

-

16 bit

模

V

Input Low Voltage 0.8 V max

INL,

V

Input High Voltage 3.5 V min

INL,

MCLK IN Only V

Input Low Voltage 0.4 V max

V

INL,

V

Input High Voltage 2.5 V min

INL,

数转换器 TM7705

=3V NOMINAL

DD

LOGIC OUTPUTS(Including MCLK OUT)

,Output Low Voltage 0.4 V max I

V

OL

=800μA Exceptfor MCLK OUT.

SINK

VDD=5V.

V

,Output Low Voltage 0.4 V max I

OL

=100μA Exceptfor MCLK OUT.

SINK

VDD=3V.

,Output High

V

OH

Voltage

,Output High

V

OH

Voltage

Floating StateLeakage

4VminI

VDD—0.6 V min I

=200μA Exceptfor MCLK

SOURCE

12

OUT.

VDD=5V.

=100μA Exceptfor MCLK

SOURCE

12

OUT.

VDD=3V.

±10 μA max

Current

Floating StateOutput

Capacitance

13

9pFtyp

Data Output Coding Binary Unipolar Mode

OffsetBinary Bipolar Mode

SYSTEM CALIBRATION

Positive Full—Scale

Calibration Limit

14

Negative Full—Scale

Calibration Limit

14

Offset Calibration Limit

Input Span

15

14

(1.05×V

GAIN

—(1.05×

V

REF

—(1.05×

V

REF

(0.8×

V

REF

(2.1×

V

REF

REF

) GAIN

) GAIN

)/GAIN

)/GAIN

)

V max GAIN Is the Selected PGA Gain(1

to 128)

V max GAIN Is the Selected PGA Gain(1

to 128)

V max GAIN Is the Selected PGA Gain(1

to 128)

V min GAIN Is the Selected PGA Gain(1

to 128)

V max GAIN Is the Selected PGA Gain(1

to 128)

POWER REQUIREMENTS

Voltage +2.7 to +3.3 Vmin to Vmax For Specified Performance

V

DD

12

12

Digital I/Ps=0V or V

External MCLK

DD.

IN and CLK DIS=1

Power Supply

Currents

16

0.32 mA max BUF Bit=O. f

128

0.6 mA max BUF Bit=1. f

=1MHz.Gains of 1 to

CLKIN

=1MHz.Gainsof1to

CLKIN

128

0.4 mA max BUF Bit=O.f

=2.4576MHz. Gains

CLKIN

of 1 to 4

Titan Micro Electronics www.titanmec.com -

©

V1.2

7

-

16 bit

模

数转换器 TM7705

0.6 mA max BUF Bit=O. f

=2.4576MHz.

CLKIN

Gains of 8 to 128

0.7 mA max BUF Bit=O. f

=2.4576MHz.

CLKIN

Gains of 1 to 4

1.1 mA max BUF Bit=1. f

=2.4576MHz.

CLKIN

Gains of 8 to 128

V

DD

Voltage

+4.75 to

+5.25

Vmin toVmax For Specified Performance

Digital I/Ps=0V or VDD.External

MCLK IN and CLK DIS=1.

0.45 mA max BUF Bit=0. f

=1MHz.Gainsof1to

CLKIN

128

Power Supply Currents

0.7 mA max BUF Bit=1. f

16

0.6 mA max BUF Bit=0. f

128

=1MHz.Gainsof1to

CLKIN

=2.4576MHz.

CLKIN

Gains of 1 to 4

0.85 mA max BUF Bit=0. f

=2.4576MHz.

CLKIN

Gains of 8 to 128

0.9 mA max BUF Bit=1. f

=2.4576MHz.

CLKIN

Gains of 1 to 4

1.3 mA max BUF Bit=1. f

=2.4576MHz.

CLKIN

Gains of 8 to 128

16 μA max External MCLK IN=0V or VDD.

V

Standby(Power-Down)

Current

17

Power Supply

Rejection

18

8 μA max External MCLK IN=0V or V

See Note 19 dB typ

=5V.SeeFigure9

DD

V

=3V

DD

DD

.

注释:

B 级温度范围为-40℃~+85℃。

这些数据是按最初设计的产品发布的。

一次校准实际上是一次转换,因此这些误差就是表 1 和表 3 所示转换噪声的阶数。这

适用于在期望的温度下校准后。

任何温度条件下的重新校准将会除去这些漂移误差。

正满标度误差包括零标度误差 (Zero-Scale Error )(单极性偏移误差或双极性零误

差),且既适用于单极性输入范围又适用于双极性输入范围。

满标度漂移包括零标度漂移 (单极性偏移漂移或双极性零漂移)且适用于单极性及

双极性输入范围。

增益误差不包括零标度误差,它被计算为满标度误差——对单极性范围为单极性偏移

误差,而对双极性范围为满标度误差——双极性零误差。

增益误差漂移不包括单极性偏移漂移和单极性零漂移。当只完成了零标度校准时,增

益误差实际上是器件的漂移量。

Titan Micro Electronics www.titanmec.com -

©

V1.2

8

-

16 bit

模

数转换器 TM7705

共模电压范围:模拟输入电压不超过 VDD+30mV,不低于 GND-30mV。电压低于

GND-200mV 时,器件功能有效,但在高温时漏电流将增加。

这里给出的 AIN(+)端的模拟输入电压范围,对 TM7705 来说,是指相对于 AIN(- )

端的电压;对 TM7706 而言是指 COMMON 输入端。输入模拟电压不应超过

VDD+30mV,不应低于 GND-30mV。GND-200mV 的输入电压也可采用,但高温时

漏电流将增加。

VREF=REF IN(+ )-REF IN(-)。

只有当加载一个 CMOS 负载时,这些逻辑输出电平才适用于 MCLK OUT。

+25℃时测试样品,以保证一致性。

校准后,如果模拟输入超过正满标度,转换器将输出全 1,如果模拟输入低于负满标度,

将输出全 0。

在模拟输入端所加校准电压的极限不应超过 VDD +30mV 或负于 GND-30mV。

当用晶体或陶瓷谐振器作为器件的时钟源时 (通过 MCLK 引脚 ),VDD 电流和功耗

随晶体和谐振器的类型而变化 (见“时钟和振荡器电路”部分)。

在等待模式下,外部的主时钟继续运行,5V 电压时等待电流增加到 150 μ A,3V 电

压时增加到 75 μ A。当用晶体或陶瓷谐振器作为器件的时钟源时,内部振荡器在等待

模式下继续运行,电源电流功耗随晶体和谐振器的类型而变化 (参看“等待模式”

一节)。

在直流状态测量,适用于选定的通频带。50Hz 时,PSRR 超过 120dB (滤波器陷波

为 25Hz 或 50Hz )。 60Hz 时,PSRR 超过 120dB (滤波器陷波为 20Hz 或 60Hz )。

PSRR 由增益和 VDD 决定,如下:

增益 1 2 4 8~128

VDD=3V 86 78 85 93

VDD=5V 90 78 84 91

八、定时参数

(VDD= +2.7V~+5.2V;GND=0V;f

=V

除非另有说明)

DD

Limit at

Parameter

T

MIN,TMAX

(B Version)

3,4

f

CLKIN

t

CLKIN LO

t

CLKIN HI

t

1

t

2

Read Operation

t

3

Titan Micro Electronics www.titanmec.com -

©

400 kHzmin

2.5 MHz max for Specified Performance

0.4×t

CLKIN

0.4×t

CLKIN

500×t

CLKIN

100 ns min RESETPulsewidth

0 ns min DRDY to CS Setup Time

=2.4567MHz;Input Logic 0=0 V,Logic 1

CLKIN

Units Conditions/Comments

Master Clock Frequency: Crystal

Oscillator or Externally Supplied

ns min

ns min Master Clock Input High Time.

ns mon DRDY High Time

V1.2

Master Clock Input Low Time. t

f

CLKIN

CLKIN

=1/

9

-

16 bit

模

数转换器 TM7705

t

4

120 ns min CS Falling Edge to SCLK Rising Edge

Setup Time

5

t

5

t

6

t

7

t

8

6

t

9

0 ns min SCLK Falling Edge to Data Valid Delay

80 ns max V

100 ns max V

=+5V

DD

=+3.0V

DD

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0nsmin

CS Rising Edge to SCLK Rising Edge

Hold Time

10 ns min Bus RelinguishTimeafter SCLK Rising

Edge

60 ns max VDD=+5V

100 ns max V

t

10

100 ns max SCLK Falling Edge to DRDY High

=+3.0V

DD

Write Operation

t

11

120 ns min CS Falling Edge to SCLK Rising Edge

Setup Time

t

12

30 ns min Data Valid to SCLK Rising Edge Setup

Time

t

13

20 ns min Data Valid to SCLK Rising Edge Hold

Time

t

14

t

15

t

16

100 ns min SCLK High Pulsewidth

100 ns min SCLK High Pulsewidth

0 ns min CS Rising Edge to SCLK Rising Edge

Hold Time

注释:

样品测试温度为+25℃以保证一致性。所有的输入信号满足:tr=tf=5ns(V

DD

的 10%~90% ),且从 1.6V 电平计时。

见图 16 和图 17。

f

占空比为 45%~55%。只要 TM7705 不在等待模式下,必须提供 f

CLKIN

。在这种情

CLKIN

况下 如果没有时钟,器件就会吸取较规定更大的电流并可能变成未校准的。

f

= 2.4567MHz 时进行生产测试,以保证器件工作于 400kHz。

CLKIN

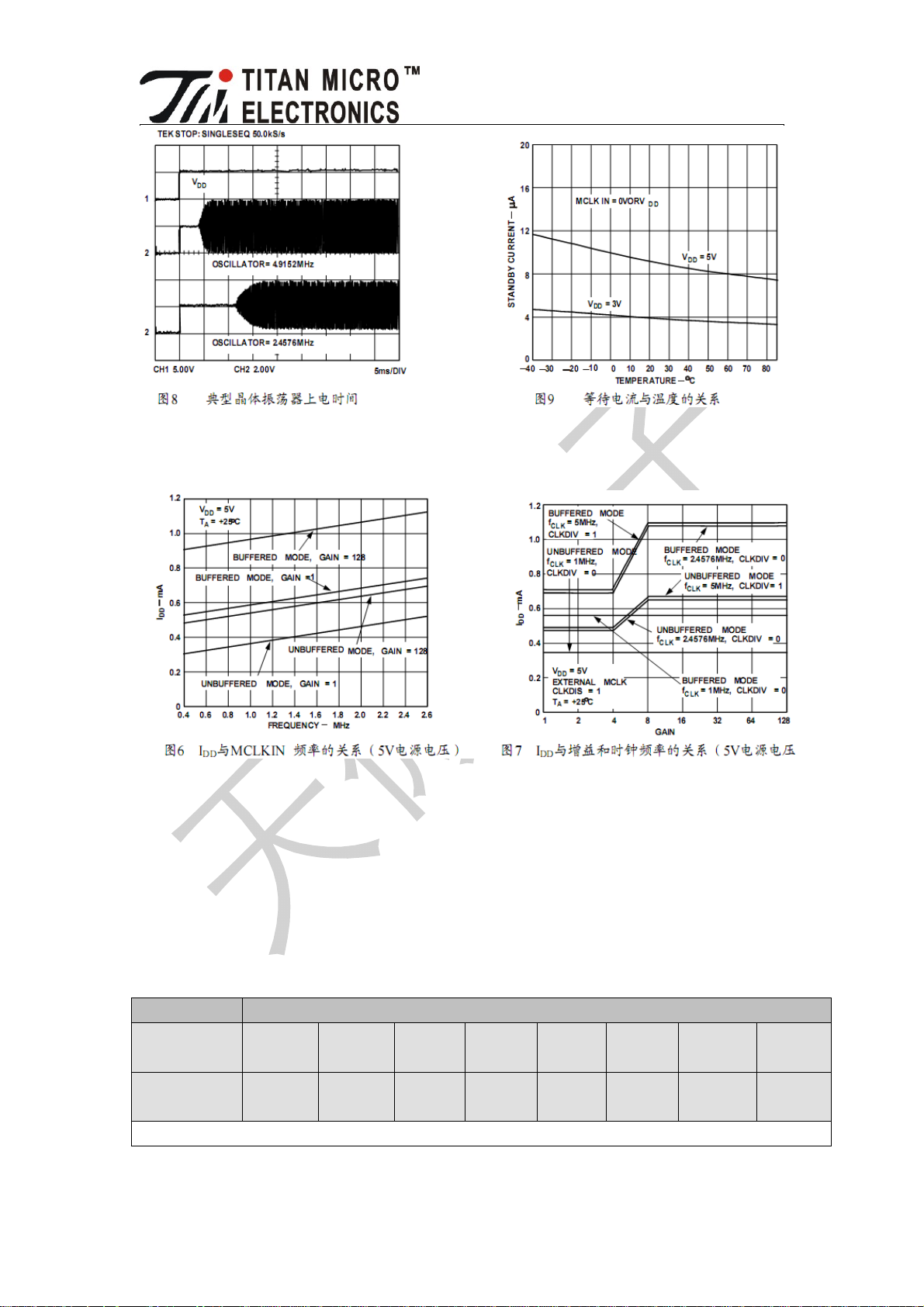

这些数字是在图 1 的负载电路下测定的。它们被定义为输出通过 V

OL

或V

OH

该数值是在数据输出为 0.5V 时测量的 (负载情况如图 1 所示)。然后被测的数值又推

演回来,以消除对 50pF 电容器充电或放电的影响。这就是说定时参数表中提到的所有

时间值都是真正的总线撤回时间(relinquish time ),而因此与外部的总线负载电容无

关。

输出更新后,DRDY 在第一次从器件读出后返回高电平。当 DRDY 为高电平时,如果

需要,同一数据可以再次读出。但是必须注意在下一次输出更新后,不会很快发生随后

的读出。

7

Titan Micro Electronics www.titanmec.com -

©

V1.2

10

-

模

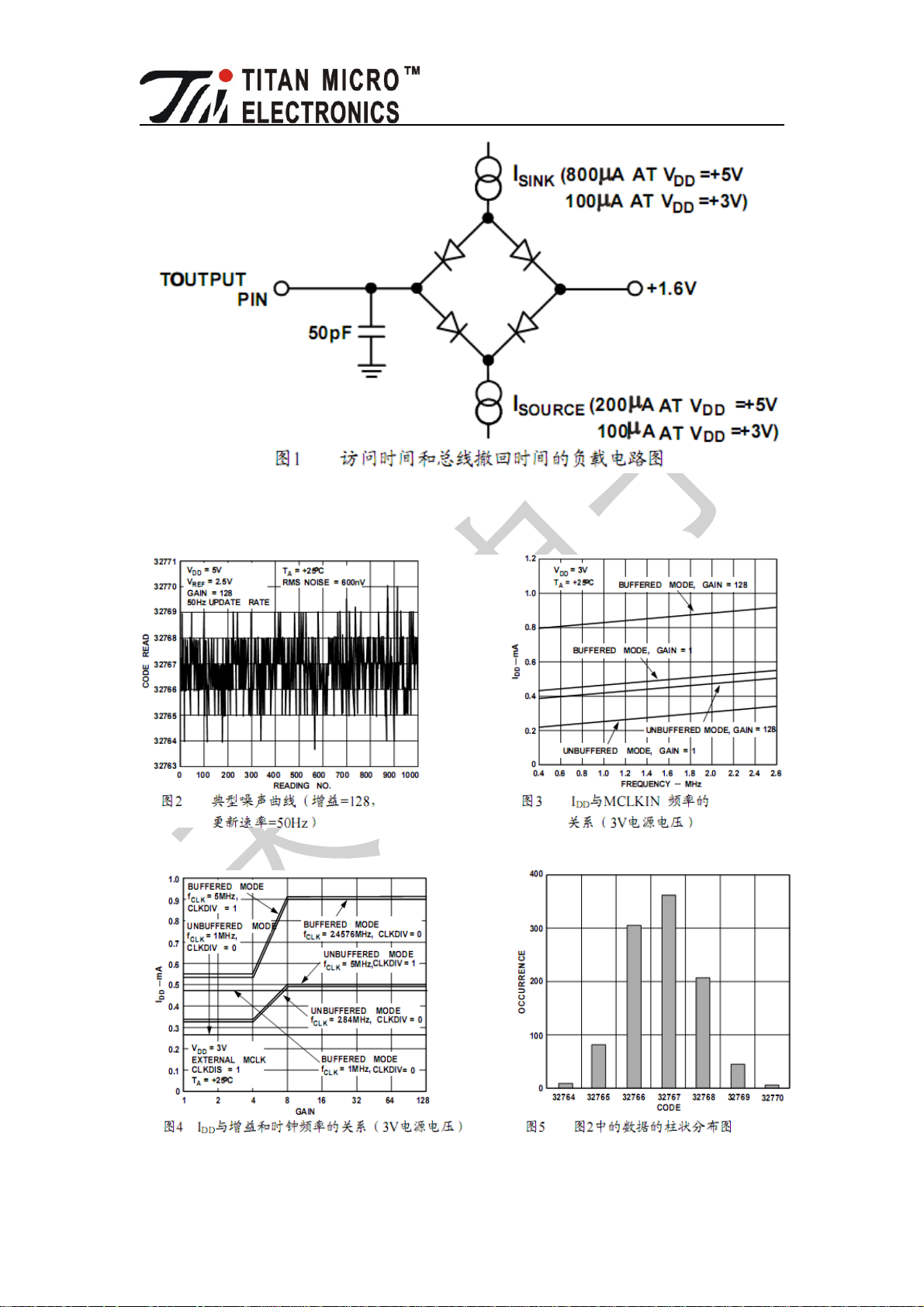

九、典型特性曲线

16 bit

数转换器 TM7705

Titan Micro Electronics www.titanmec.com -

©

V1.2

11

-

模

十、输出噪声

16 bit

数转换器 TM7705

表 1、3 显示了 TM7705 在可选陷波为器件的-3dB 频率时的输出噪声 (有效值 ),由

时钟寄存器的 FS0 和 FS1 选择。这些给出的数字是在双极性输入,V

= +2.5V,VDD=5V

REF

时的数值。这些数值是器件工作在缓冲模式或非缓冲模式,模拟输入电压为 0V 时产生的典

型值。表 2、4 显示了输出噪声峰-峰值。特别要注意的是这些数字所表示的分辨率将是没有

代码闪烁的。这些数值不是基于有效值 (RSM )而是基于峰-峰值计量的噪声。这些给出

的数值适用于缓冲模式和非缓冲模式下双极性输入范围 (V

=+1.225V )。 这些数值是

REF

典型值,并靠近最近的 LSB。要求时钟寄存器的 CLK DIV 位置为 0。

表 1 输出噪声(RMS )与增益和输出更新速率的关系(5V 电压 )

Filter First Typical Output RMS Noise in μ V

Notch and

O/P—3 dB

Data Rate

Frequency

MCLK IN=2.4576MHz

Titan Micro Electronics www.titanmec.com -

©

增益值 增益值 增益值 增益值 增益值 增益值 增益值 增益值

1 2 4 8 16 32 64 128

12

V1.2

-

16 bit

模

50Hz 13.1Hz 4.1 2.1 1.2 0.75 0.7 0.66 0.63 0.6

60Hz

15.72Hz

250Hz

65.5Hz

500Hz

131Hz

MCLK IN=1MHz

20Hz

5.24Hz

25Hz

6.55Hz

100Hz

26.2Hz

200Hz

52.4Hz

5.1 25 1.4 0.8 0.75 0.7 0.67 0.62

110 49 31 17 8 3.6 2.3 1.7

550 285 145 70 41 22 9.1 4.7

4.1 2.1 1.2 0.75 0.7 0.66 0.63 0.6

5.1 2.5 1.4 0.8 0.75 0.7 0.67 0.62

110 49 31 17 8 3.6 2.3 1.7

550 285 145 70 41 22 9.1 4.7

数转换器 TM7705

表 2 峰-峰值 (Peak - Peak )分辨率与增益和输出更新速率的关系 (5V 电压 )

Filter First Typical Peak-to-Peak Resolution Bits

Notch and

O/P—3 dB

Data Rate

Frequency

MCLK IN=2.4576MHz

50Hz 13.1Hz 16 16 16 16 16 16 15 14

60Hz

15.72Hz

250Hz

65.5Hz

500Hz

131Hz

MCLK IN=1MHz

20Hz

5.24Hz

25Hz

6.55Hz

100Hz

26.2Hz

200Hz

52.4Hz

增益值 增益值 增益值 增益值 增益值 增益值 增益值 增益值

1 2 4 8 16 32 64 128

16 16 16 16 15 14 14 13

13 13 13 13 13 13 12 12

10 10 10 10 10 10 10 10

16 16 16 16 16 16 15 14

16 16 16 16 15 14 14 13

13 13 13 13 13 13 12 12

10 10 10 10 10 10 10 10

Titan Micro Electronics www.titanmec.com -

©

V1.2

13

-

16 bit

模

数转换器 TM7705

表 3 输出噪声 (RMS )与增益和输出更新速率的关系 (3V 电压 )

Filter First Typical Output RMS Noise in μV

Notch and

O/P—3 dB

Data Rate

Frequency

MCLK IN=2.4576MHz

50Hz 13.1Hz 3.8 2.4 1.5 1.3 1.1 1.0 0.9 0.9

60Hz

15.72Hz

250Hz

65.5Hz

500Hz

131Hz

MCLK IN=1MHz

20Hz

5.24Hz

25Hz

6.55Hz

100Hz

26.2Hz

200Hz

52.4Hz

增益值 增益值 增益值 增益值 增益值 增益值 增益值 增益值

1 2 4 8 16 32 64 128

5.1 2.9 1.7 1.5 1.2 1.0 0.9 0.9

50 25 14 9.9 5.1 2.6 2.3 2.0

270 135 65 41 22 9.7 5.1 3.3

3.8 2.4 1.5 1.3 1.1 1.0 0.9 0.9

5.1 2.9 1.7 1.5 1.2 1.0 0.9 0.9

50 25 14 9.9 5.1 2.6 23 2.0

270 135 65 41 22 9.7 5.1 3.3

表 4 峰-峰值 (Peak - Peak )分辨率与增益和输出更新速率的关系 (3V 电压 )

Filter First Typical Peak-to-Peak Resolution Bits

Notch and

O/P—3 dB

Data Rate

Frequency

MCLK IN=2.4576MHz

50Hz 13.1Hz 16 16 15 15 14 13 13 12

60Hz

15.72Hz

250Hz

65.5Hz

500Hz

131Hz

MCLK IN=1MHz

20Hz

5.24Hz

25Hz

6.55Hz

增益值 增益值 增益值 增益值 增益值 增益值 增益值 增益值

1 2 4 8 16 32 64 128

16 16 15 14 14 13 13 12

13 13 13 13 12 12 11 11

10 10 10 10 10 10 10 10

16 16 15 15 14 13 13 12

16 16 15 14 14 13 13 12

Titan Micro Electronics www.titanmec.com -

©

V1.2

14

-

Loading...

Loading...