USPIIi-1v

Hardware Manual

Revision B4

Themis Computer—Rest of World

20 rue du Tour de l’Eau

38400 Saint Martin d’Hères, France

Phone +33 476 59 60 46

Fax +33 476 59 60 49

Themis Computer—Americas and Pacific Rim

3185 Laurelview Court

Fremont, CA 94538

Phone (510) 252-0870

Fax (510) 490-5529

World Wide Web http://www.themis.com

USPIIi-1v Hardware Manual

Version B4 — December 2001

Copyright © 2000 Themis Computer, Inc.

ALL RIGHTS RESERVED. No part of this publication may be reproduced in any form, by

photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without

the prior written permission of Themis Computer.

The information in this publication has been carefully checked and is believed to be accurate. However,

Themis Computer assumes no responsibility for inaccuracies. Themis Computer retains the right to

make changes to this publication at any time without prior notice. Themis Computer does not assume

any liability arising from the application or use of this publication or the product(s) described herein.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the United States Government

is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

TRADEMARKS

SOLARIS

™

is a registered trademark of Sun Microsystems

SPARC

™

is a registered trademark of SPARC International

All other trademarks used in this publication are the property of their respective owners.

USPIIi-1v Hardware Manual

December 2001

Part Number: 105614

Themis Customer Support

Telephone: +1 510-252-0870

Fax: +1 510-490-5529

E-mail: support@themis.com

Web Site: http://www.themis.com

Version Revision History

Version B4 December 2001

Replaced Universe II with Universe IIB throughout manual.

Corrected misspellings throughout manual.

Reenforced definition of backplane reset on pages 2-2 and B-2.

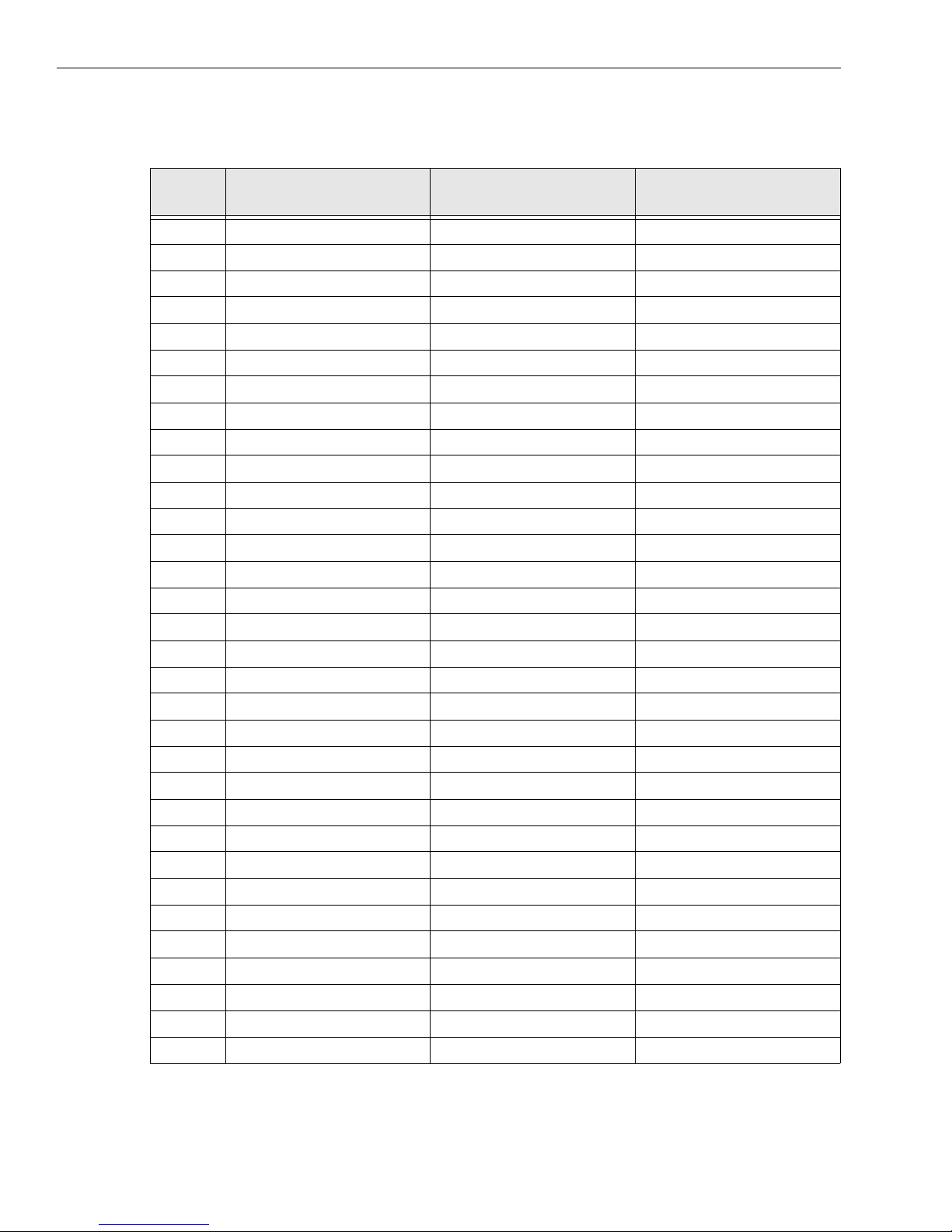

Defined non-standard signal for P2 pin B3 in Table A-2, page A-3.

Reversed Serial Port C and D callouts, pages C-3, C-4, and D-5.

Version B3 October 5, 2000

Corrected I/O Board Jumper Setting references on page B-5.

Version B2 July 20, 2000

Changed definition of OBP in System and User 1 flash.

Fixed minor inconsistencies in B.2.1 and 3.2.3.

Version B1 May 25, 2000

Reworked for 360/440 MHz CPU.

Fixed Jumper references.

Version B January 17, 2000

Version A1 September 29, 1998

Version A July 29, 1998

Initial Customer Release.

USPIIi-1v User’s Manual

Themis Computer

Themis Computer v

Table of Contents

1 Introduction ........................................................................................................... 1-1

1.1 How to Use This Manual ....................................................................................... 1-1

1.2 Intended Audience ................................................................................................. 1-1

1.3 Product Warranty and Registration........................................................................ 1-2

1.4 Unpacking.............................................................................................................. 1-2

1.5 How to Start Quickly ............................................................................................. 1-3

1.6 Chapter Overview .................................................................................................. 1-4

1.7 Related References ................................................................................................ 1-4

2 Installation ............................................................................................................. 2-1

2.1 Determine Board Type and Configuration ............................................................ 2-1

2.2 Configuration ......................................................................................................... 2-2

2.3 Backplane Jumper Settings.................................................................................... 2-2

2.4 Installing The USPIIi-1v Paddle Board ................................................................. 2-3

2.5 Attaching Cables to Peripheral Devices ................................................................ 2-4

2.5.1 Console Port (TTYA) ............................................................................ 2-4

2.5.2 Keyboard and Mouse ............................................................................. 2-5

2.5.3 Ethernet Network................................................................................... 2-5

2.5.4 SCSI A and B......................................................................................... 2-5

2.5.5 Creator Graphics Card ........................................................................... 2-6

2.6 Configuring The VME Interface............................................................................ 2-6

3 Specification.......................................................................................................... 3-1

3.1 Overview................................................................................................................ 3-1

3.1.1 Baseboard............................................................................................... 3-1

3.1.2 I/O Board and Creator Graphics ............................................................ 3-2

3.1.3 PMC Carrier Board................................................................................ 3-2

3.1.4 Paddle Board.......................................................................................... 3-2

3.1.5 Block Diagram....................................................................................... 3-3

3.2 System Specification.............................................................................................. 3-4

3.2.1 Processor & Memory Subsystems ......................................................... 3-4

USPIIi-1v Hardware Manual

vi

Themis Computer

3.2.2 I/O Subsystem........................................................................................ 3-5

3.2.3 Auxiliary Functions ............................................................................... 3-6

3.3 Environmental Specification.................................................................................. 3-7

3.4 Estimated Power Requirements ............................................................................. 3-8

4 Hardware Overview................................................................................................ 4-1

4.1 Major Components ................................................................................................ 4-1

4.1.1 SME UltraSPARC-IIi Processor and Cache.......................................... 4-1

4.1.2 E-Cache.................................................................................................. 4-1

4.1.3 SME Advanced PCI Bridge (APB) ....................................................... 4-2

4.1.4 SME Reset, Interrupt, and Clock (RIC)................................................. 4-2

4.1.5 Tundra Universe IIB .............................................................................. 4-2

4.1.6 SME PCI I/O Controller ........................................................................ 4-3

4.1.7 Symbios SCSI Controller....................................................................... 4-3

4.1.8 FPGA ..................................................................................................... 4-3

4.1.9 National Super I/O ................................................................................. 4-3

4.1.10 Seimens SAB 82532 .............................................................................. 4-3

4.1.11 FLASH.................................................................................................. 4-3

4.1.12 TOD and NVRAM................................................................................. 4-4

4.2 Memory Subsystem ............................................................................................... 4-4

4.3 PMC Carrier Subsystem ........................................................................................ 4-5

4.4 OpenBoot PROM................................................................................................... 4-5

5 Universe-IIB Description ....................................................................................... 5-1

5.1 Features.................................................................................................................. 5-1

5.2 USPIIi-1v and the Universe IIB PCI Interface ...................................................... 5-2

5.3 VMEbus Interface.................................................................................................. 5-2

5.3.1 VMEbus Configuration.......................................................................... 5-2

5.3.2 Universe IIB as the VMEbus Slave ....................................................... 5-2

5.3.3 Universe IIB as the VMEbus Master..................................................... 5-3

5.3.4 VMEbus First Slot Detector .................................................................. 5-4

5.3.4.1 Automatic Slot Identification............................................. 5-5

5.3.4.2 Registered Access at the power up .................................... 5-6

5.3.5 Universe IIB’s hardware Power -Up Options........................................ 5-6

5.4 Slave Image Programming..................................................................................... 5-7

5.4.1 VME Slave Images ................................................................................ 5-8

5.4.1.1 VMEbus Fields .................................................................. 5-8

5.4.1.2 PCI Bus Fields ................................................................... 5-8

5.4.1.3 Control Fields .................................................................... 5-9

5.4.2 PCI Bus Target Images .......................................................................... 5-9

5.4.2.1 PCI Bus Fields ................................................................... 5-10

5.4.2.2 VMEbus Fields .................................................................. 5-10

5.4.2.3 Control Fields .................................................................... 5-11

5.4.2.4 Special PCI Target Image .................................................. 5-11

Themis Computer vii

Table of Contents

5.5 Universe IIB’s Interrupt and Interrupt Handler ..................................................... 5-14

5.5.1 VME and PCI Interrupters:.................................................................... 5-14

5.5.2 VMEbus Interrupt Handling: ................................................................. 5-15

5.5.3 Universe IIB’s Mailbox Registers: ........................................................ 5-15

5.5.4 Universe IIB’s Semaphores ................................................................... 5-15

5.5.5 Programmable slave images on the VMEbus and PCI bus: .................. 5-15

5.5.6 DMA Controller..................................................................................... 5-16

6 FPGA, Watchdog, Voltage and Temperature Sensors ...................................... 6-1

6.1 FPGA ..................................................................................................................... 6-1

6.1.1 Introduction............................................................................................ 6-1

6.1.2 Boot Address Decoder ........................................................................... 6-1

6.1.3 3-Level Watchdog.................................................................................. 6-2

6.1.4 Power Management System................................................................... 6-3

6.2 Temperature Sensor ............................................................................................... 6-4

7 Resets .................................................................................................................... 7-1

7.1 Overview................................................................................................................ 7-1

7.2 UltraSPARC-IIi Reset Request Signals................................................................. 7-2

7.2.1 Power-On Reset (POR).......................................................................... 7-2

7.2.2 Externally Initiated Reset (XIR) ............................................................ 7-2

7.2.3 Watchdog Reset (WDR) ........................................................................ 7-2

7.2.4 Software Initiated Reset (SIR) ............................................................... 7-3

7.3 Reset Sources......................................................................................................... 7-3

7.3.1 Push Button Reset.................................................................................. 7-3

7.3.2 Power Management Resets.................................................................... 7-3

7.3.3 VMEbus Resets...................................................................................... 7-4

7.3.4 3-Level Watchdog Resets ...................................................................... 7-4

7.3.5 Software POR ........................................................................................ 7-4

7.3.6 Software XIR ......................................................................................... 7-4

7.4 UltraSPARC-IIi Reset Control Register ................................................................ 7-5

7.5 USPIIi-1v Reset Tree Diagram.............................................................................. 7-6

A Connector Pinouts, LEDs, Switches ................................................................... A-1

A.1 Introduction............................................................................................................ A-1

A.2 Baseboard Front Panel ........................................................................................... A-1

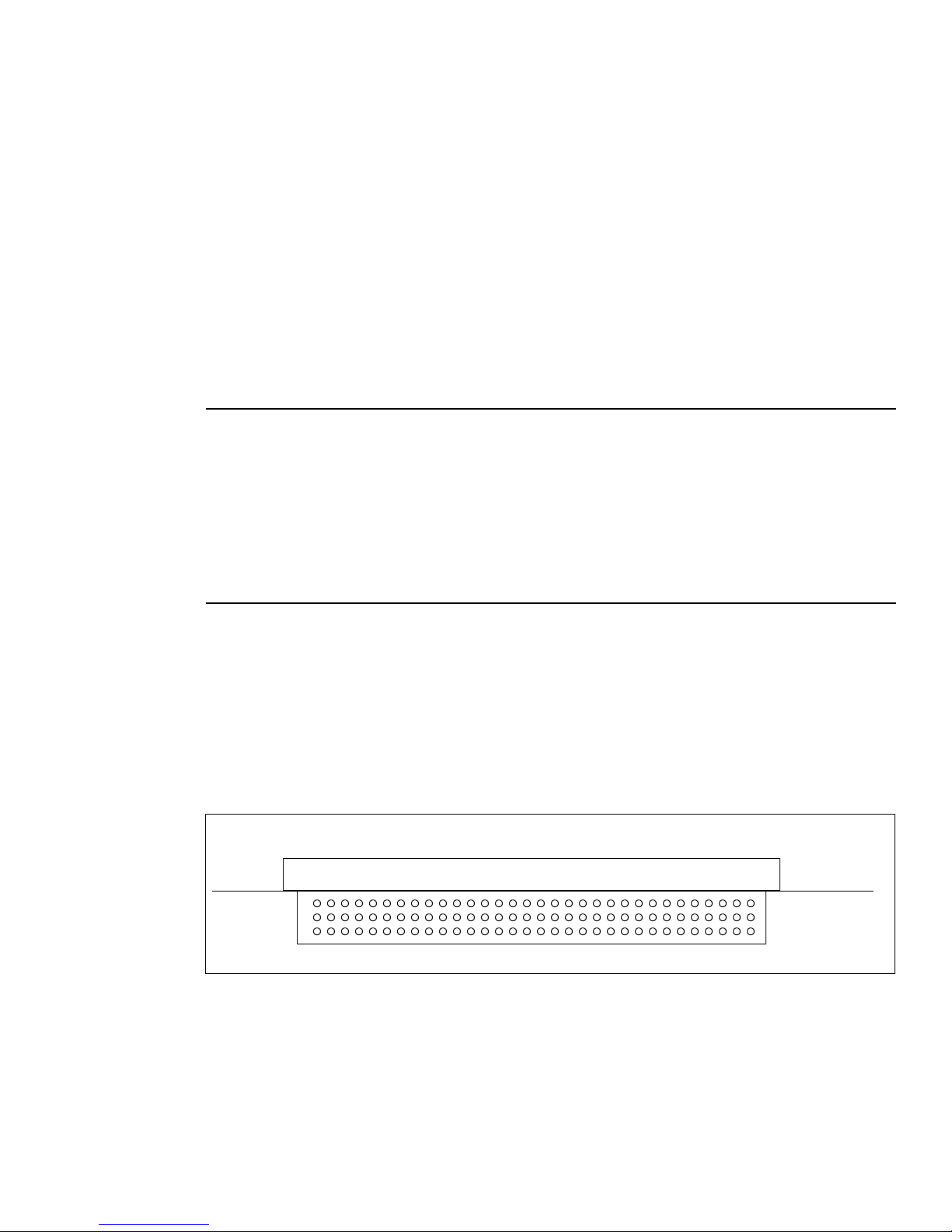

A.2.1 Baseboard VME P1 ............................................................................... A-1

A.2.2 Baseboard VME P2 ............................................................................... A-3

A.2.3 SCSI A and B......................................................................................... A-6

A.2.4 RJ45 Ethernet A Connector ................................................................... A-8

A.2.5 Keyboard/Mouse Connector and Serial Port A (PS/2 Mode only)........ A-9

A.2.6 PS/2 Keyboard/Mouse Split Cable ........................................................ A-10

A.2.7 Serial Port A (Console) Adapter Cable (PS/2 Mode only).................... A-11

A.2.8 Keyboard/Mouse Connector and Serial Port A (Sun Mode only) ......... A-12

A.2.9 LEDs ...................................................................................................... A-13

USPIIi-1v Hardware Manual

viii

Themis Computer

A.2.10 Push-Button RESET .............................................................................. A-13

A.3 I/O Board ............................................................................................................... A-14

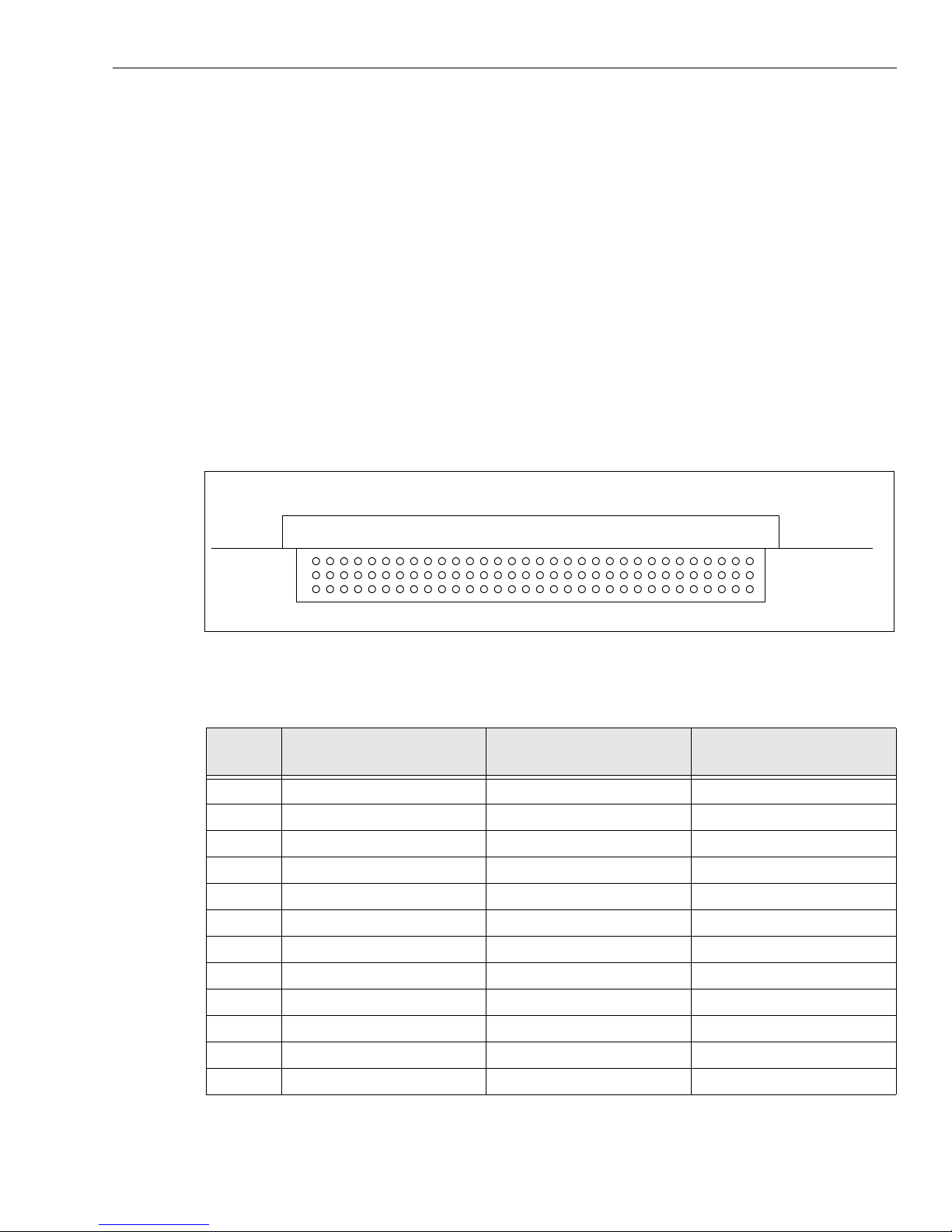

A.3.1 I/O Board VME P2 ................................................................................ A-14

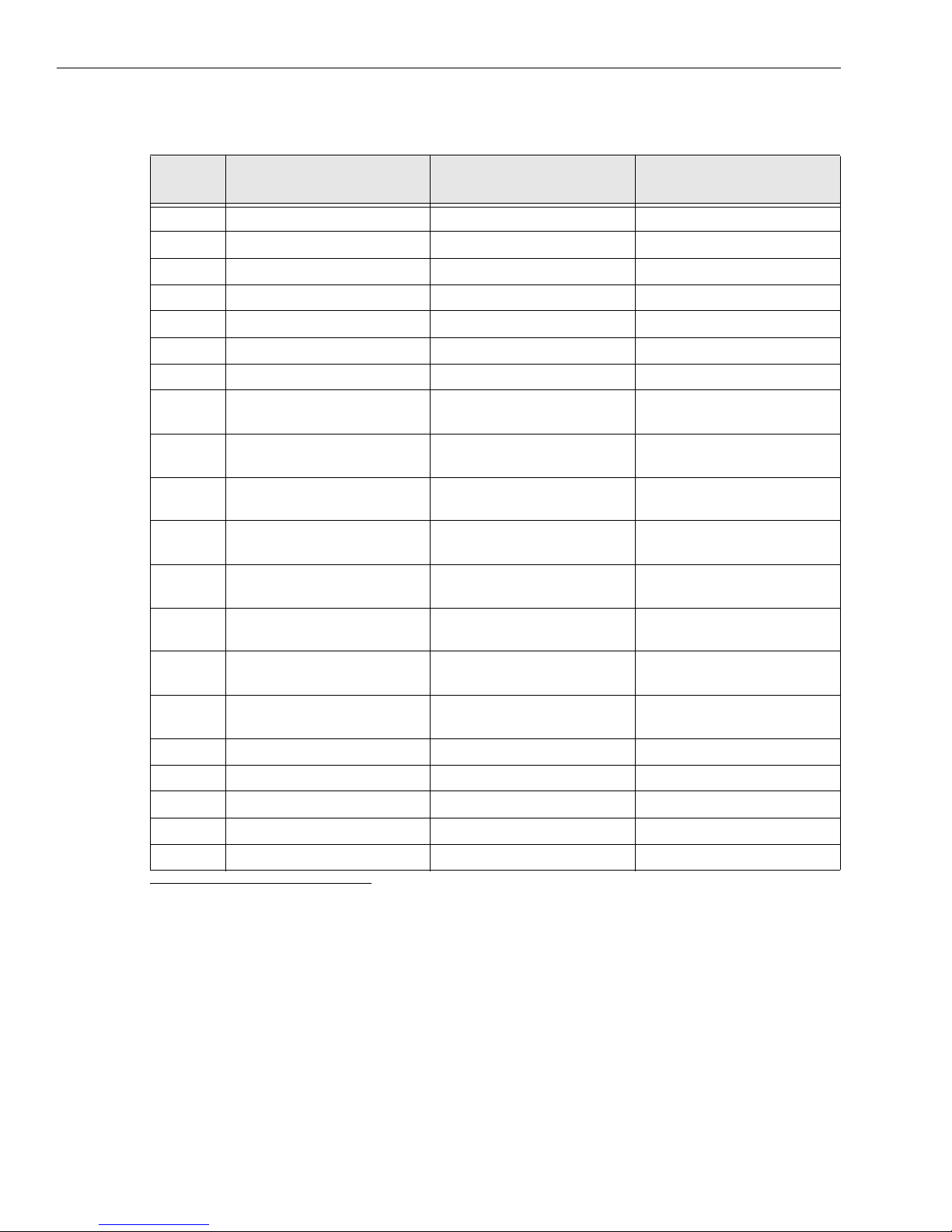

A.3.2 Serial Port C (TTYC or Console) and Serial Port D (TTYD or Aux Port) A16

A.3.3 Parallel Port............................................................................................ A-18

A.3.4 RJ45 Ethernet B Connector ................................................................... A-19

A.3.5 Audio ..................................................................................................... A-19

A.3.6 Creator Graphics Slot............................................................................. A-19

A.4 PMC Carrier Board................................................................................................ A-20

A.4.1 PMC Carrier Board P1 Connector ......................................................... A-20

A.4.2 PMC Carrier Board VME P2 Connector ............................................... A-22

A.4.3 PMC Carrier Slot User I/O .................................................................... A-24

A.4.3.1 PMC Carrier Slot #1: 64 Bit User I/O Configuration ........ A-24

A.4.3.2 PMC Carrier Slot #1: 32 Bit User I/O Configuration ........ A-26

A.4.3.3 PMC Carrier Slot #2: 32 Bit User I/O Configuration ........ A-27

A.5 Paddle Board.......................................................................................................... A-28

A.5.1 SCSI Connector ..................................................................................... A-28

A.5.2 MII Connector........................................................................................ A-30

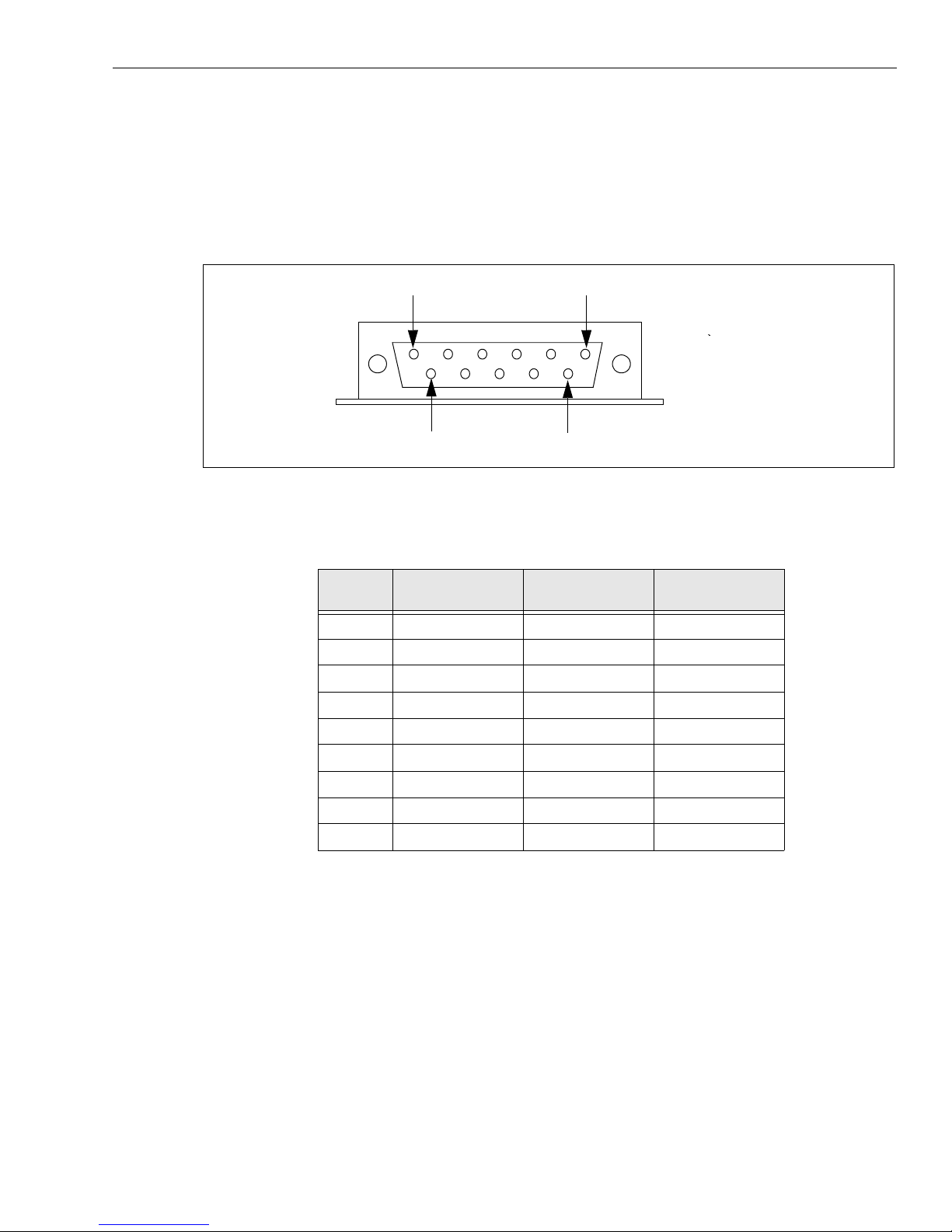

A.5.3 DB9 Connector ...................................................................................... A-31

B Jumper and Solder Bead Configurations ............................................................ B-1

B.1 Overview................................................................................................................ B-1

B.2 Field Configurables................................................................................................ B-1

B.2.1 Baseboard Jumpers ................................................................................................ B-1

B.2.2 I/O Board Jumpers ................................................................................................. B-4

B.2.3 PMC Carrier Board Jumpers.................................................................. B-6

B.3 Factory Configurables............................................................................................ B-6

B.3.1 Baseboard Solder Beads ........................................................................ B-6

B.3.2 I/O Board Solder Beads ......................................................................... B-10

B.3.3 PMC Carrier Board Solder Beads.......................................................... B-10

C Front Panel Diagrams............................................................................................ C-1

C.1 Introduction............................................................................................................ C-1

C.2 Baseboard Front Panel ........................................................................................... C-2

C.3 Baseboard, I/O Board, and Creator Graphics Front Panels ................................... C-3

C.4 Baseboard, I/O Board, and PMC Carrier Board Front Panel................................. C-4

D Board Diagrams ..................................................................................................... D-1

D.1 Baseboard Board Diagrams ................................................................................... D-1

D.2 I/O Board Diagrams............................................................................................... D-5

D.3 PMC Board ............................................................................................................ D-6

D.4 Paddle Board.......................................................................................................... D-8

E Glossary.................................................................................................................. F-1

E.1 Terminology........................................................................................................... F-1

Themis Computer ix

List of Tables

Table 2-1. Summary of different connectors configuration.................................................................... 2-4

Table 3-1. Processor Specifications........................................................................................................ 3-4

Table 3-2. Memory Specification ........................................................................................................... 3-4

Table 3-3. I/O Sub-system Specification................................................................................................ 3-5

Table 3-4. Auxiliary Functions Specifications ....................................................................................... 3-6

Table 3-5. USPIIi-1v Operating Environmental Specifications ............................................................. 3-7

Table 3-6. USPIIi-1v Non-operating Environmental Specifications...................................................... 3-7

Table 3-7. Estimated Power Requirements............................................................................................. 3-8

Table 4-1. Flash EPROM Jumpers ......................................................................................................... 4-4

Table 5-1. Universe IIB PCI Interface Pins............................................................................................ 5-2

Table 5-2. Universe IIB Miscellaneous Control Register (MISC_CTL)................................................ 5-4

Table 5-3. Universe IIB Power Up Options ........................................................................................... 5-6

Table 5-4. PCI Configuration Base Address 0 Register (PCI_BS0) ...................................................... 5-7

Table 5-5. PCI Configuration Base Address 1 Register (PCI_BS1) ...................................................... 5-7

Table 5-6. VMEbus Fields for VMEbus Slave Image............................................................................ 5-8

Table 5-7. PCI Bus Fields for VMEbus Slave Image............................................................................. 5-8

Table 5-8. Control Fields for VMEbus Slave Image .............................................................................. 5-9

Table 5-9. PCI Bus Fields for PCI Bus Target Image .......................................................................... 5-10

Table 5-10. PCI Bus Fields for PCI Bus Target Image ........................................................................ 5-11

Table 5-11. Control Fields for PCI Bus Target Image ......................................................................... 5-11

Table 5-12. PCI Bus Fields for Special PCI Bus Target Image ........................................................... 5-12

Table 5-13. PCI Bus Fields for Special PCI Bus Target Image ........................................................... 5-12

Table 5-14. Control Fields for Special PCI Bus Target Image............................................................. 5-12

Table 5-15. Special PCI Target Image Register (Offset 188)............................................................... 5-12

Table 6-1. Mapping of Flash Devices: J3304 on 2-3 or removed (Boot from System Flash)................ 6-1

Table 6-2. Mapping of Flash Devices: J3304 on 1-2 (Boot from User Flash) ....................................... 6-2

Table 6-3. Jumper J3303 setting ............................................................................................................. 6-2

USPIIi-1v Hardware Manual

x

Themis Computer

Table 6-4. Watchdog POR Enable/Disable ............................................................................................ 6-2

Table 6-5. Watchdog Enable/Disable ..................................................................................................... 6-3

Table 7-1. UltraSPARC-IIi Reset_Control Register............................................................................... 7-5

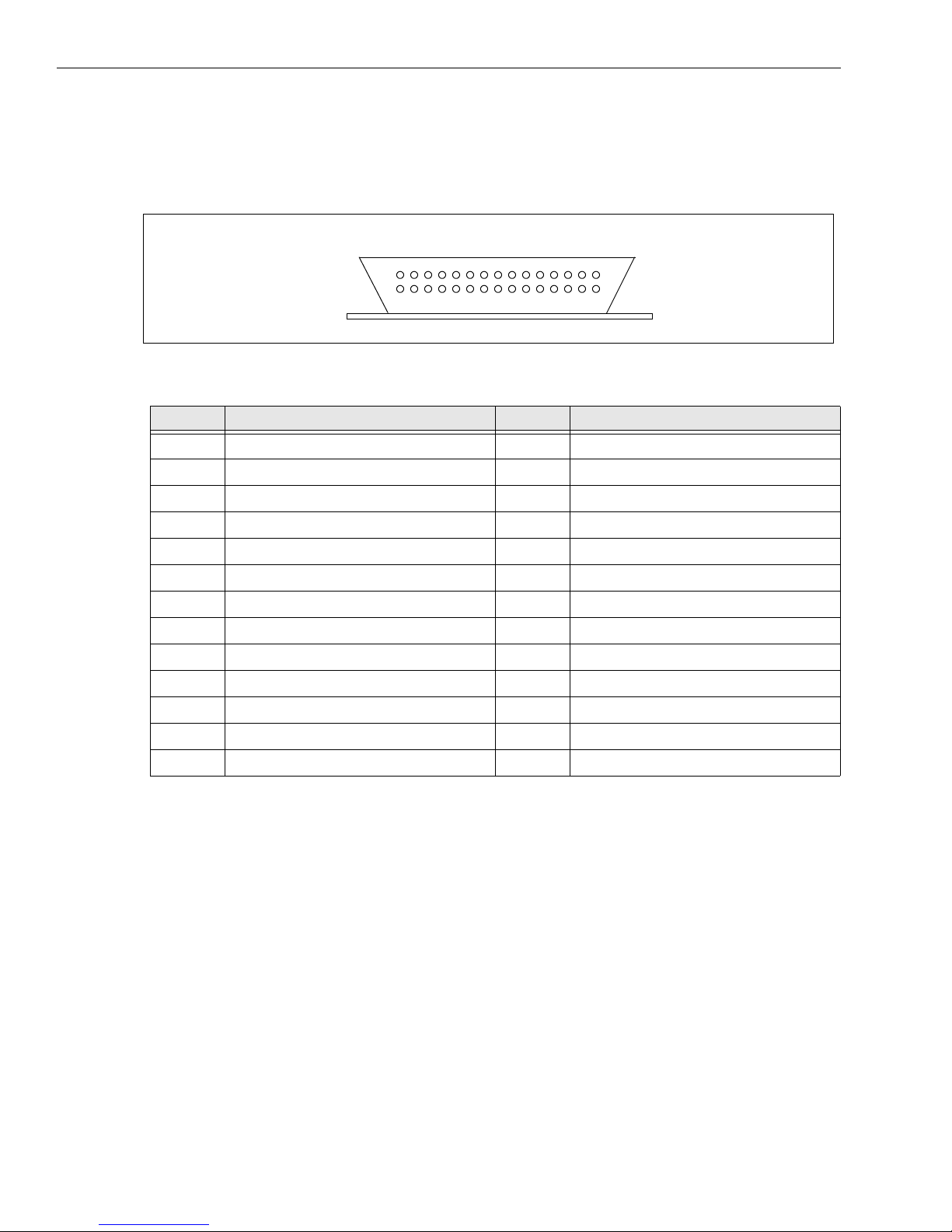

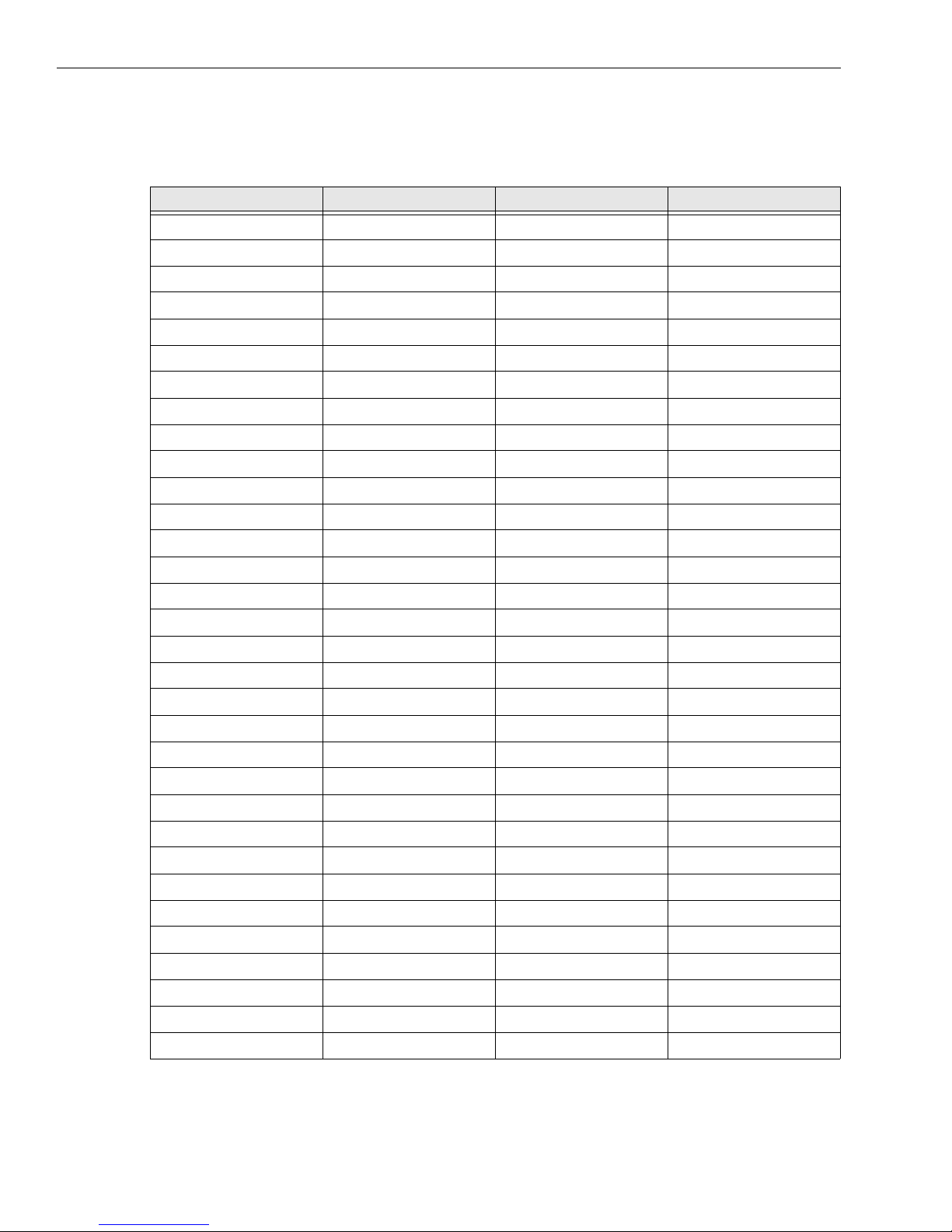

Table A-1. Baseboard VME P1 Pinout.................................................................................................. A-2

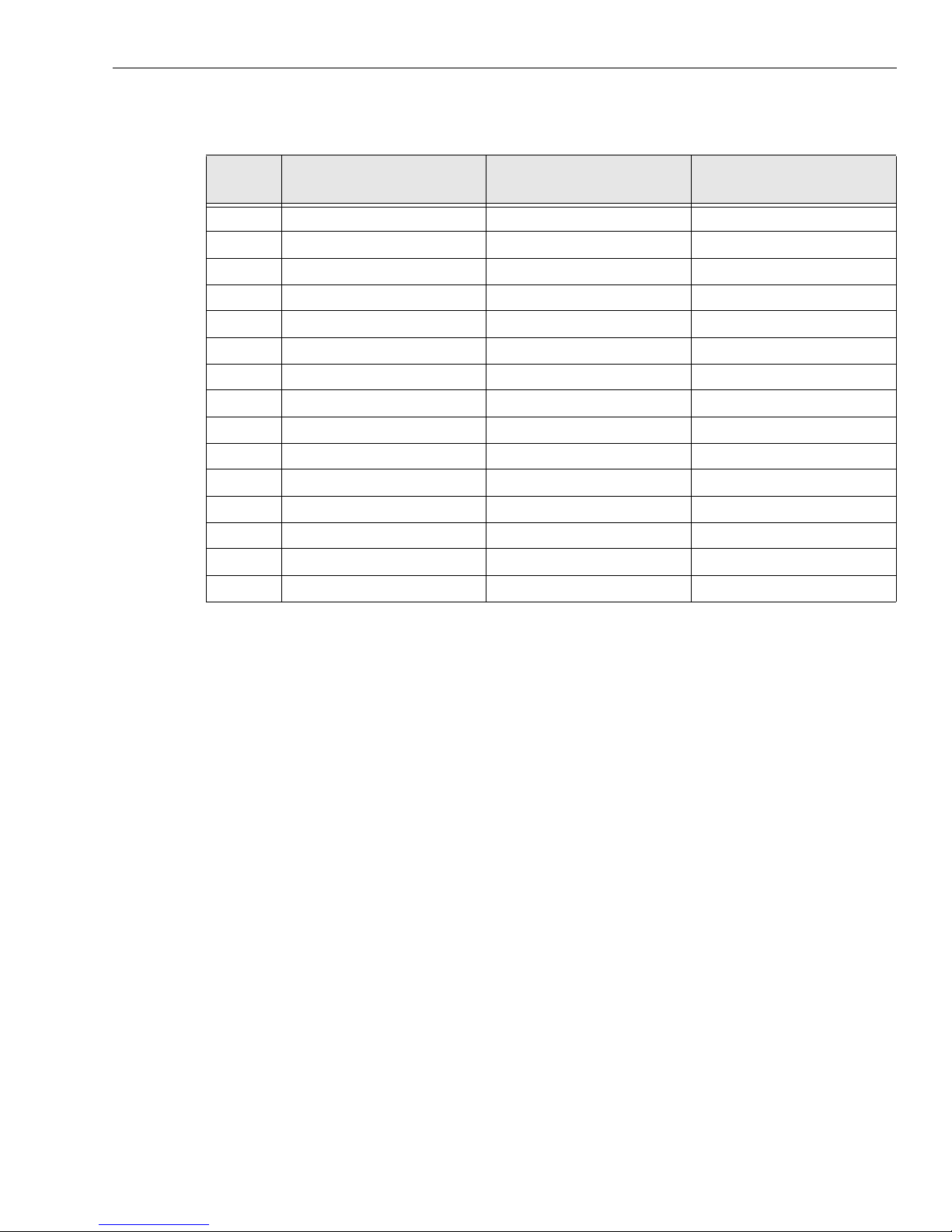

Table A-2. Baseboard VME P2 Connector in PS/2 Mode..................................................................... A-3

Table A-3. Baseboard VME P2 Connector in Sun Mode...................................................................... A-4

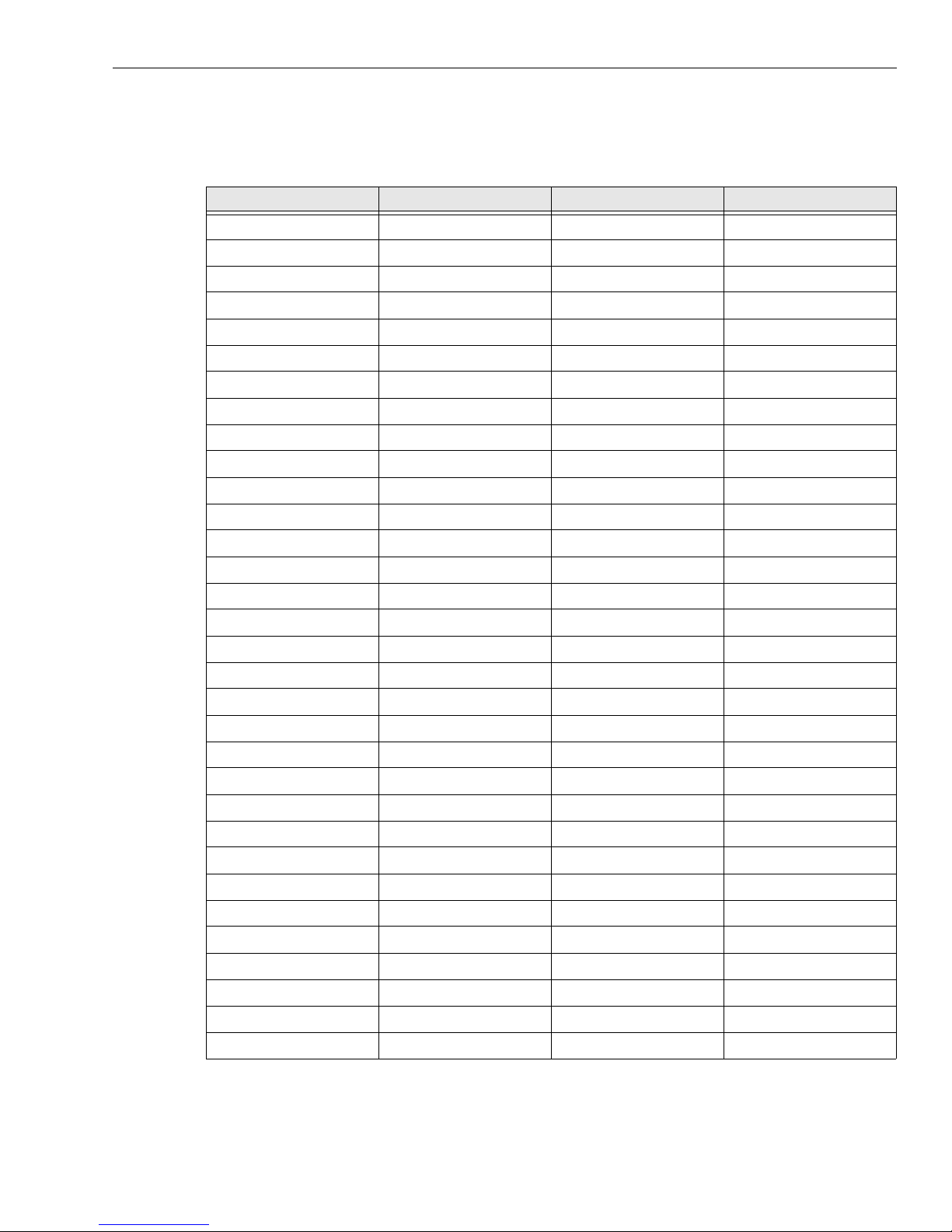

Table A-4. Baseboard SCSI A and B Pinout ......................................................................................... A-6

Table A-5. RJ45 Ethernet A Pinout ....................................................................................................... A-8

Table A-6. Baseboard Console and Keyboard/Mouse Pinout (PS/2 Mode).......................................... A-9

Table A-7. PS/2 Keyboard/Mouse Split Cable Pinout ........................................................................ A-10

Table A-8. Serial Port A (Console) Adapter Cable ............................................................................. A-11

Table A-9. Baseboard Console and Keyboard/Mouse Pinout (Sun Mode)......................................... A-12

Table A-10. Possible colors of the ALARM LED............................................................................... A-13

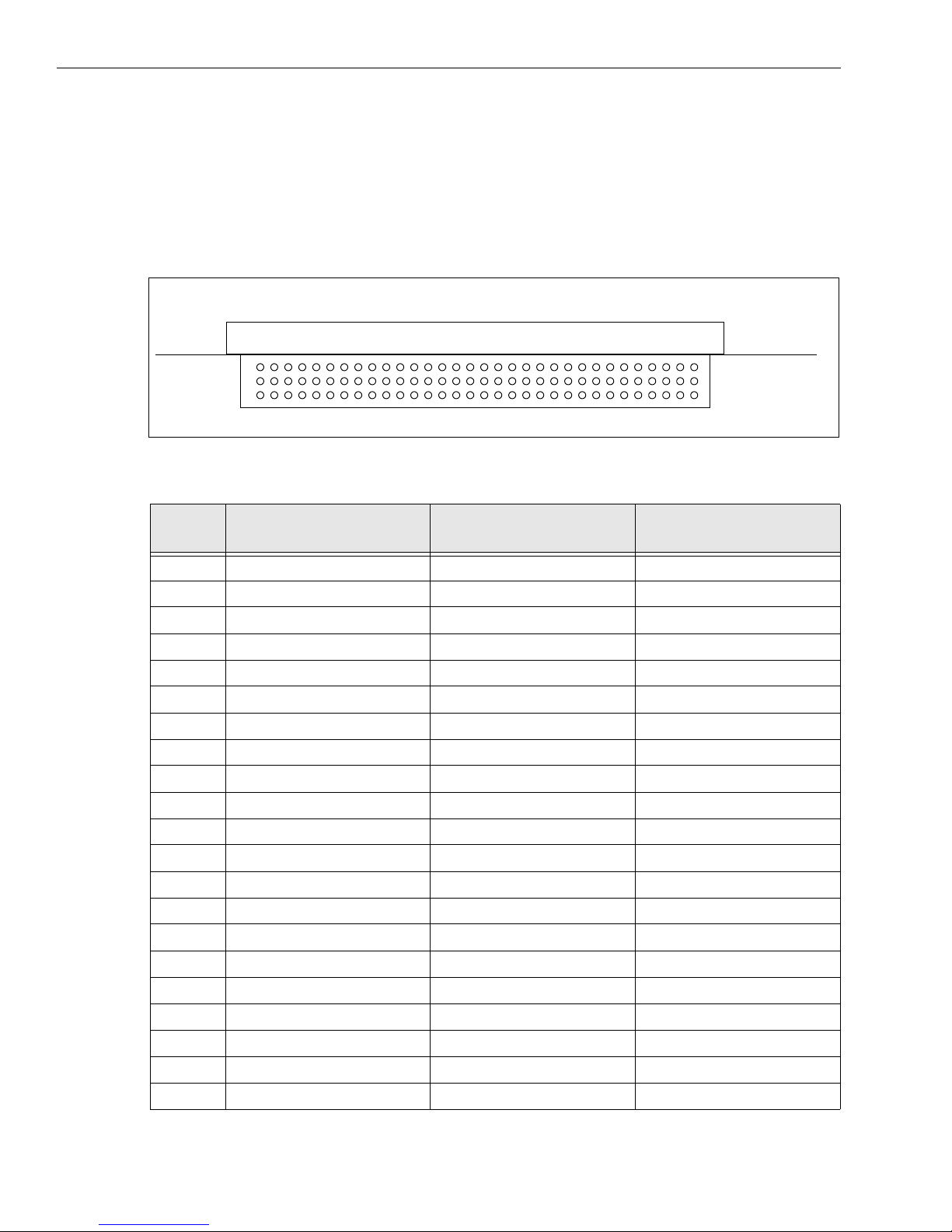

Table A-11. I/O Board VME P2 Connector ........................................................................................ A-14

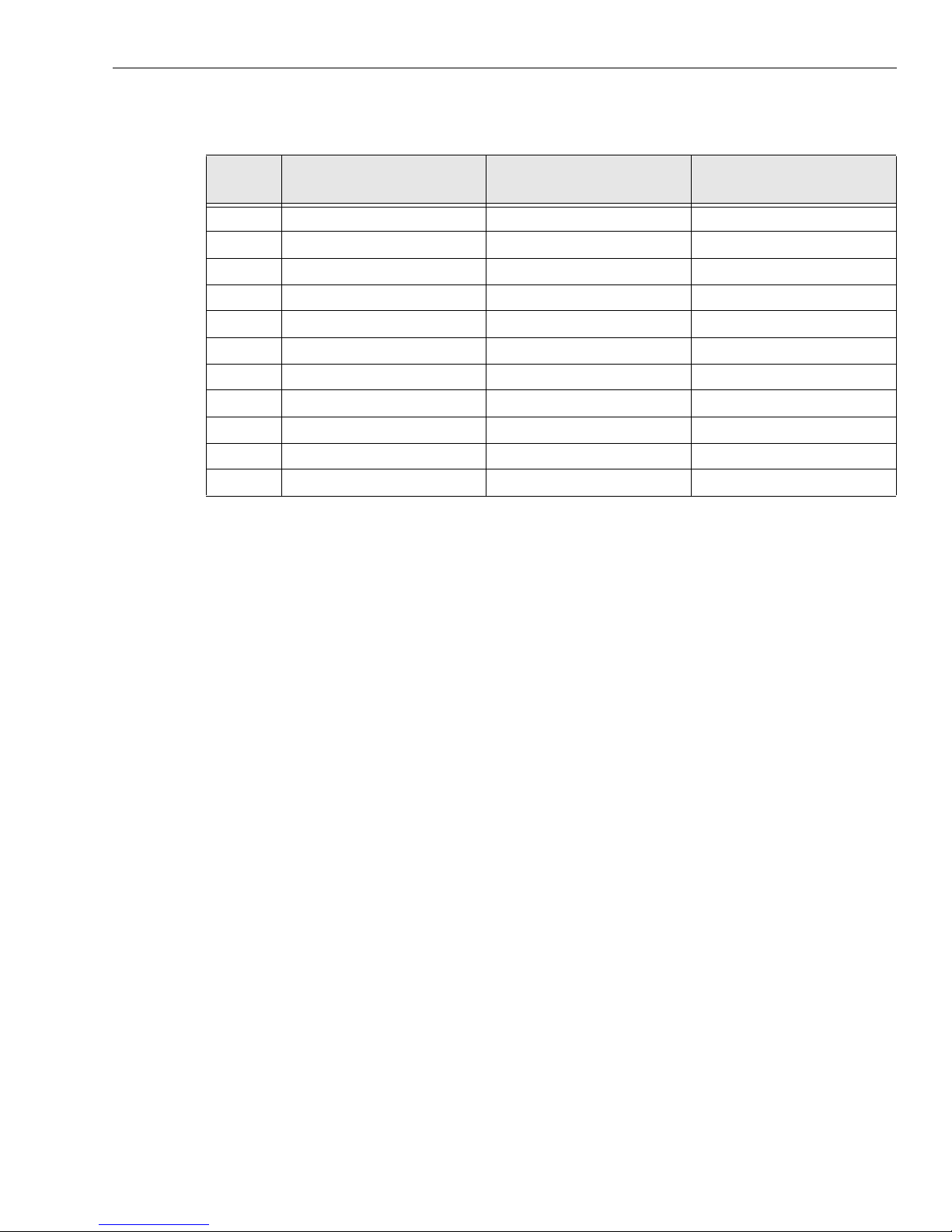

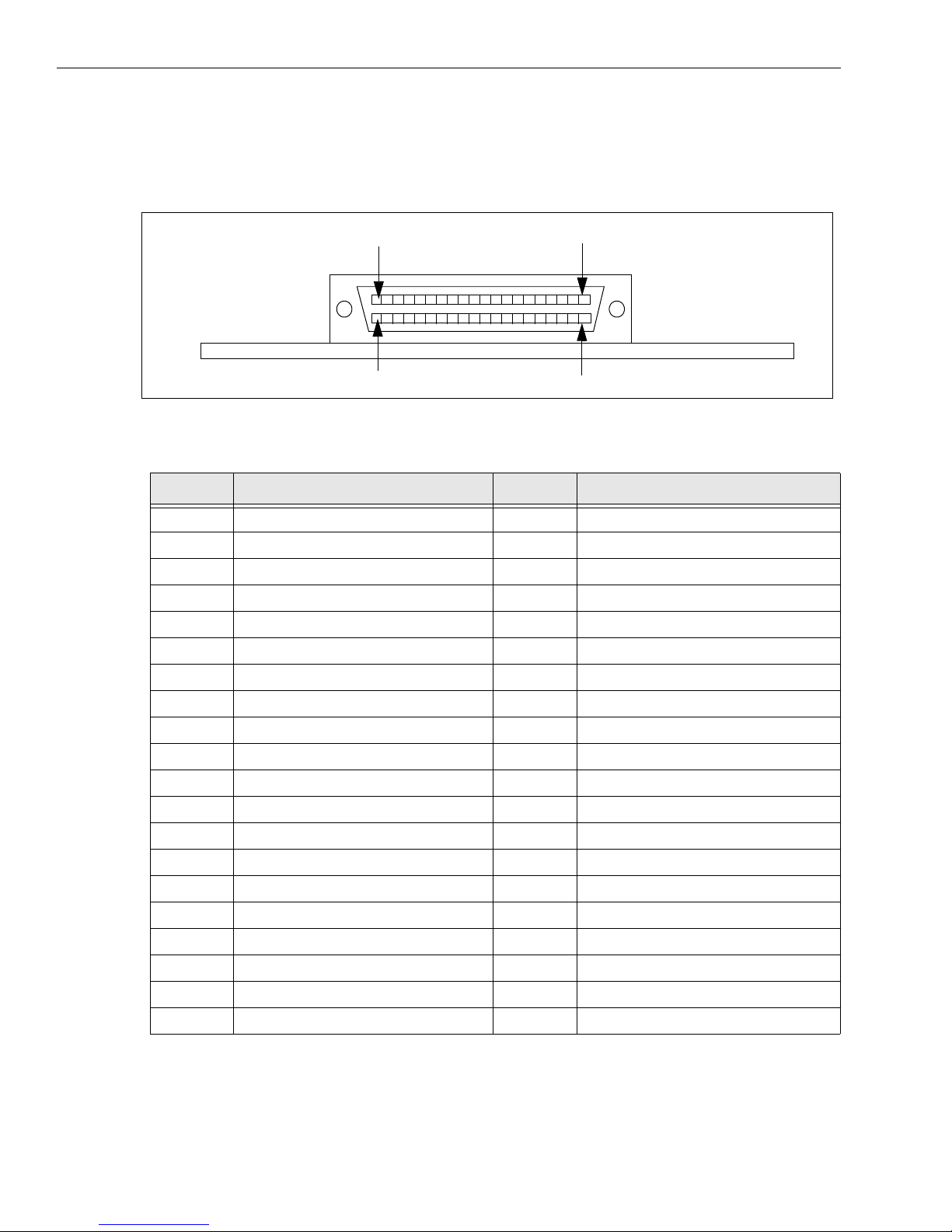

Table A-12. I/O Board TTY C AND TTY D Pinout........................................................................... A-16

Table A-13. I/O Board Parallel Port Pinout......................................................................................... A-18

Table A-14. RJ45 Ethernet B Pinout ................................................................................................... A-19

Table A-15. PMC Carrier Board VME P1 Pinout ............................................................................... A-20

Table A-16. PMC Carrier Board VME P2 Pinout ............................................................................... A-22

Table A-17. PMC Carrier Slot #1 with 64 Bits of User I/O ................................................................ A-24

Table A-18. PMC Carrier Slot #1 with 32 Bits of User I/O ................................................................ A-26

Table A-19. PMC Carrier Slot #2 with 32 Bits of User I/O ................................................................ A-27

Table A-20. Paddle Board SCSI Connector Pinout............................................................................. A-28

Table A-21. Paddle Board MII Connector Pinout ............................................................................... A-30

Table A-22. Paddle Board DB9 Connector Pinout.............................................................................. A-31

Table B-1. Baseboard Jumper Setting ....................................................................................................B-1

Table B-2. I/O Board Jumper Setting .....................................................................................................B-4

Table B-3. Baseboard Component Side Solder Beads............................................................................B-6

Table B-4. Baseboard Solder Side Solder Beads....................................................................................B-6

Table B-5. I/O Board Solder Side Solder Beads...................................................................................B-10

Themis Computer xi

List of Figures

Figure 3-1. USPIIi-1v Baseboard Block Diagram..................................................................................3-3

Figure 4-1. Memory Sub-System Topology ........................................................................................... 4-5

Figure 5-1. Universe IIB Architectural Diagram.................................................................................... 5-4

Figure 5-2. Address Translation for VMEbus to PCI Bus Transfers...................................................... 5-9

Figure 5-3. Address Translation for PCI Bus to VMEbus Transfers.................................................... 5-10

Figure 5-4. Memory Mapping in the Special PCI Target Image .......................................................... 5-14

Figure 7-1. USPIIi-1v Reset Diagram .................................................................................................... 7-6

Figure A-1. VME P1 Baseboard Connector Orientation....................................................................... A-1

Figure A-2. Baseboard VME P2 Connector Orientation....................................................................... A-3

Figure A-3. Baseboard SCSI A and B Connector Orientation .............................................................. A-6

Figure A-4. Ethernet A Connector Orientation ..................................................................................... A-8

Figure A-5. Baseboard Console and Keyboard/Mouse Connector Orientation (PS/2 Mode)............... A-9

Figure A-6. PS/2 Keyboard/Mouse Split Cable................................................................................... A-10

Figure A-7. Serial Port Adapter Cable................................................................................................. A-11

Figure A-8. Baseboard Console and Keyboard/Mouse Connector Orientation (Sun Mode) .............. A-12

Figure A-9. I/O Board VME P2 Connector Orientation...................................................................... A-14

Figure A-10. I/O Board TTYC and TTYD Connector Orientation..................................................... A-16

Figure A-11. I/O Board Parallel Port Connector Orientation.............................................................. A-18

Figure A-12. Ethernet B Connector Orientation..................................................................................A-19

Figure A-13. PMC Carrier Board VME P1 Connector Orientation .................................................... A-20

Figure A-14. PMC Board VME P2 Connector Orientation................................................................. A-22

Figure A-15. PMC Carrier Board User I/O Connector........................................................................ A-24

Figure A-16. Paddle Board SCSI Connector .......................................................................................A-28

Figure A-17. Paddle Board MII Connector ......................................................................................... A-30

Figure A-18. Paddle Board DB9 Connector........................................................................................A-31

Figure B-1. Baseboard Jumper Locations...............................................................................................B-3

USPIIi-1v Hardware Manual

xii

Themis Computer

Figure B-2. I/O Board Jumper Locations ...............................................................................................B-5

Figure B-3. Baseboard Component Side Solder Bead Locations...........................................................B-8

Figure B-4. Baseboard Solder Side Solder Bead Locations ...................................................................B-8

Figure B-5. I/O Board Solder Side Solder Beads .................................................................................B-10

Figure C-1. Single Slot Front Panel........................................................................................................C-2

Figure C-2. Double Slot Front Panels.....................................................................................................C-3

Figure C-3. Triple Slot Front Panel ........................................................................................................C-4

Figure D-1. Baseboard Front Panel Diagram ........................................................................................ D-2

Figure D-2. Baseboard Component Diagram ........................................................................................D-3

Figure D-3. Baseboard Connector Diagram .......................................................................................... D-4

Figure D-4. I/O Board Component Side................................................................................................ D-5

Figure D-5. PMC Carrier Board Component Side ................................................................................ D-6

Figure D-6. PMC Board Connector Diagram........................................................................................D-7

Figure D-7. Paddle Board Component Side .......................................................................................... D-8

Themis Computer 1-1

1

1Introduction

1.1 How to Use This Manual

Thank you for purchasing the Themis USPIIi-1v single board computer. This manual describes the USPIIi-1v,

a SPARC version 9.0 compliant computer with a VMEbus interface and an UltraSPARC-IIi processor.

We value our customer’s comments and concerns. Themis Computer is eager to know what is thought of our

products. A “Reader Comment Card” is located at the end of this manual for your use. Please take the time fill

it out and return it to Themis Computer.

Before you begin, carefully read each of the procedures in this manual and the associated CPU manual.

Improper handling of the equipment can cause serious damage to the equipment.

1.2 Intended Audience

This manual is written for system integrators and programmers. It contains all necessary information for

installation and configuration of the USPIIi-1v and assumes the Open Boot Program (OBP) code is installed

in the system flash. If you intend to operate the USPIIi-1v with an operating system other than Solaris, such

as VxWorks or other real-time kernel, please consult the appropriate documentation supplements

accompanying your OS or kernel software.

Although all specific hardware and software features are described in this manual, programmers wishing to

write code for the USPIIi-1v without the benefit of an operating system or real-time kernel will require

additional data sheets. Please refer to the Section 1.7, "Related References," on page 1-4 for information

concerning this documentation.

The reader should have a working knowledge of the VMEbus specifications, SPARC processor architecture,

Ethernet, and SCSI (ANSI X3.131-1986) specifications.

USPIIi-1v Hardware Manual

1-2

Themis Computer

1.3 Product Warranty and Registration

Please review the Themis Computer warranty and complete the product registration card delivered with your

USPIIi-1v board(s). Return of the registration card is not required to activate your product warranty but, by

registering your USPIIi-1v, Themis Computer will be better able to provide you with timely updated

information and product enhancement notifications.

Our Customer Support department is committed to providing the best product support in the industry.

Customer support is available 8am - 5pm (PST), Monday through Friday via telephone, fax, e-mail or our

World Wide Web site.

Themis Customer Support

Telephone: +1 510-252-0870

Fax: +1 510-490-5529

E-mail: support@themis.com

Web Site: http://www.themis.com

1.4 Unpacking

The following section describes the shipping contents of the USPIIi-1v.

Caution —

The USPIIi-1v contains statically sensitive components. Industry standard anti-static measures

must be observed when removing the USPIIi-1v from its shipping container and during any subsequent

handling. A wrist strap (or grounding strap) provides grounding for static electricity between your body and

the chassis of the system unit. Electric current and voltage do not pass through the wrist strap.

Remove the USPIIi-1v and accessories from the shipping container and check the contents against the

packing list. Be certain to observe industry standard ESD protection procedures when handling static sensitive

components. The package should include:

• USPIIi-1v board assembled in the configuration ordered

– Baseboard

– Memory Cards

– I/O Expansion Board

– Creator Graphics Card

– PMC Carrier Board with PMC User I/O Adapter Card

• USPIIi-1v Hardware and Software Manuals, if ordered.

• INT-KIT-USPIIi-1V/1-VME: USPIIi-1v/1 or 1v/2p integration kit, if ordered (Themis P/N 108890)

• INT-KIT-USPIIi-1V/2-VME: USPIIi-1v/2c or 1v/3 integration kit, if ordered (Themis P/N 108891)

The INT-KIT-USPIIi-1V/1-VME integration kit includes:

• A Micro DB9 connector to PS/2 Keyboard and Mouse split adapter cable for the baseboard PS/2

keyboard and mouse; Themis Part Number: 108114.

Themis Computer 1-3

1. Introduction

• A Micro DB9 connector to Male, DB25 Console adapter cable for the Baseboard Console (TTY A)

port; Themis Part Number 108113.

• A 68 pin, Sub-Miniature connector to 0.005”, male standard SCSI-3 connector adapter cable for the

Baseboard SCSI A; Themis Part Number 108712.

• A Paddle Board, Themis Part Number 105581. This paddle board must be connected behind the first

slot occupied by the USPIIi-1v board

• A 68 pin, SCSI-3 ribbon cable for the paddle board SCSI (SCSI A); Themis Part Number 108432.

The INT-KIT-USPIIi-1V/2-VME integration kit includes:

• The INT-KIT-USPIIi-1V/1-VME integration kit

• A second Paddle Board, Themis Part Number 105581. This paddle board must be connected behind the

second slot occupied by the USPIIi-1v board

• A second 68 pin, SCSI-3 ribbon cable for the second paddle board SCSI (SCSI B); Themis Part Number

108432.

• A Micro DB9 connector to Sun type 5 Keyboard and Mouse connector (Din-8) adapter cable; Themis

Part Number: 108783.

• A 26 pin, Male, Amplimite connector to a DB25 connector Adapter Cables for Serial Ports C or D;

Themis Part Number 108376.

• A 26 pin Male, Amplimite connector to DB25 printer cable for the Parallel Port; Themis Part Number

104077.

Please report any discrepancies to Themis Computer customer support immediately.

Remove the USPIIi-1v board from its antistatic wrapping and verify that it is in the ordered configuration. For

information on the available configurations and their appearances refer to Chapter 3, "Specification."

1.5 How to Start Quickly

To start quickly with the USPIIi-1v Themis Computer recommends that you read the following sections:

• Chapter 2, "Installation," This appendix contains vital information on configuring the USPIIi-1v and the

design and setup of VMEbus based systems.

• Consult Appendix B, "Jumper and Solder Bead Configurations." This appendix contains a complete

listing of all user configurable jumpers and the default settings. Verify that the jumpers on your board

are set to meet your application requirements.

In addition to the USPIIi-1v hardware manual, the USPIIi-1v software manual (Themis P/N 108966) contains

information on software registers, address maps, additional Openboot commands as well as a description of

the Themis Computer VME software package for Solaris.

USPIIi-1v Hardware Manual

1-4

Themis Computer

1.6 Chapter Overview

This document is organized in chapters and appendices of increasing information content and detail. A brief

outline of the contents of each chapter is provided:

• Chapter 1, "Introduction," contains a brief overview of this document, warranty information and related

references.

• Chapter 2, "Installation," provides instructions on the installation and configuration of the USPIIi-1v for

your particular environment and application. The information contained in this chapter is mandatory

for the correct operation of the USPIIi-1v. This chapter should be read in its entirety before use

of the board.

• Chapter 3, "Specification," provides a tabular description subsystems on the USPIIi-1v as well as the

System, Environmental, Electrical, and Performance specifications.

• Chapter 4, "Hardware Overview," provides a brief description of the major components on the USPIIi-

1v, the memory subsystem and the Open Boot Program code (OBP).

• Chapter 5, "Universe-II Description," provides detailed information concerning the VMEbus interface

for the USPIIi-1v, the Tundra Universe IIB. For a more detailed description of the Universe IIB, refer

the “Universe II User’s Manual”, available on the Tundra web-site at http://www.tundra.com.

• Chapter 6, "FPGA, Watchdog, Voltage and Temperature Sensors," provides a description of the FPGA

and EPLD on the USPIIi-1v. Included in this chapter are description of the temperature warning system,

boot address decoder, power management system, and the 3-level watchdog.

• Chapter 7, "Resets," describes the Reset Tree of the USPIIi-1v.

• Appendix A, "Connector Pinouts, LEDs, Switches," provides connector part numbers and pinouts for

the User I/O on the USPIIi-1v.

• Appendix B, "Jumper and Solder Bead Configurations," provides a detailed description of each of the

user configurable jumpers on the USPIIi-1v, as well as diagrams illustrating the location of all solder

beads and jumpers.

• Appendix C, "Front Panel Diagrams," illustrates front panels for single, double, and triple slot

configurations of the USPIIi-1v.

• Appendix D, "Board Diagrams," provides board diagrams of the USPIIi-1v.

• Appendix E, "Glossary," provides the general definition of terms and abbreviations used in this manual.

1.7 Related References

The following is a list of related references.

• USPIIi-1v Software Manual (P/N 108966)

• PCI Local Bus Specification, Revision 2.1, PCI Special Interest Group, Portland

• American National Standard for VME64, ANSI/VITA, 1994

• PCI System Architecture, by Shanley and Anderson, MindShare Press

• IEEE Standard 1275-1994, Standard For Boot (Initialization, Configuration) Firmware, Core Practices and

Requirements

•

IEEE Standard 1275.1-1994, Standard For Boot (Initialization, Configuration) Firmware, ISA Supplement for

IEEE P1754 (SPARC)

Themis Computer 1-5

1. Introduction

• IEEE Standard P1275.6/D4, Standard For Boot (Initialization, Configuration) Firmware, 64 Bit Extensions

•

OpenBoot 3.x Command Reference, Sun Microsystems (802-5837-10, Rev A)

• PCI Bus Binding to IEEE 1275-1994, Standard for Boot (Initialization, Configuration) Firmware, Revision 1.0,

14 April 1994, Prepared by the Open Firmware Task Force of the PCI Alliance

•

OpenBoot 3.x Command Supplement for PCI, Sun Microsystems (805-1627-10)

• The SPARC Architecture Manual, Version 9, David L. Weaver and Tom Germond, editors, PTR Prentice Hall

•

SunVTS™ 2.1 SunVTS User’s Guide Part No. 802-7299 August 1997, Rev. A

• SunVTS™ Quick Reference Card, Part No. 802-7301 August 1997, Rev. A

• SunVTS™ 2.1.3 Test Reference Manual Part No. 805-4163-10, May 1998, Rev. A

Integrated Circuit Specifications:

• UltraSPARC-IIi User’s Manual (SUN Part Number: 805-0087-01)

• SME1040 Highly Integrated 64-bit RISC Processor, PCI Interface Data Sheet

(SUN Part Number: 805-0086-02)

• STP2210QFP Reset/Interrupt/Clock Controller (RIC) User’s Manual

(SUN Part Number: 805-0167-01)

• SME2411BGA-66 Advanced PCI Bridge (APB) User’s Manual

(SUN Part Number: 805-1251-01)

• SME STP2003QFP: PCI Input to Output Controller User’s Manual

(SUN Part Number: 802-7837-01)

• Universe II User Manual, Tundra, Spring, 1998

• National Semiconductor DP83843 Phyter Data Sheet, Version E, August, 1997, National

Semiconductor Corporation,

• Symbios SYM53C876 SCSI I/O Processor Data Manual, Version 3.0, 1996

Sun documents are available for download on www.sun.com or docs.sun.com. Hardcopies can be ordered on the the

catalog section of the SunExpress™ Internet site at www.sun.com/sunexpress. Non-Sun documents are available from their

respective vendor’s Web site.

USPIIi-1v Hardware Manual

1-6

Themis Computer

Themis Computer 2-1

2

2Installation

2.1 Determine Board Type and Configuration

Check the white sticker located on your board’s P2 connector. It contains information on board type, serial

number and release number.

Example:

[ USPIIi-1v/1-2MB-512-440 A1] [S1300786]

– Board Type: USPIIi-1v/1

– Extended (second level, or “L2”) Cache Size: 2 MBytes

– DRAM: 512 MBytes

– CPU Frequency: 440 MHz

– Revision: A1

– Serial Number: S1300786

See Chapter 3.1, "Overview," for a specification of possible board types.

The USPIIi-1v can be provided in two factory configurations, referenced in this manual as “PS/2

configuration” and “Sun configuration”. PS/2 configuration means that the board was pre-configured to use

PS/2-type keyboard and mouse; Sun configuration means that Sun type 5 keyboard and mouse can be

installed. USPIIi-1v and -1v/2p boards are only available in PS/2 mode. To determine the mode configured on

USPIIi-1v/2c and -1v/3 boards, check the position of jumper JP3304 on the baseboard (the slot #1 board).

– JP3304 not installed or set to 2-3 (inner position): board runs in Sun configuration

– JP3304 set to 1-2 (outer position): board runs in PS/2 configuration

Similarly, solder beads SB1801 to 1811 define the configuration in place. Refer to Appendix § B Jumper and

Solder Bead Configurations for a complete listing of jumper definitions.

Warning —

!

You must determine your board type and configuration in order to attach it properly to

peripheral devices. To change to a keyboard/mouse configuration different than the one set on your board,

please contact technical support.

USPIIi-1v Hardware Manual

2-2

Themis Computer

2.2 Configuration

When you first receive the USPIIi-1v, confirm that the installation of jumpers is appropriate to your

application

. Refer to Appendix § B Jumper and Solder Bead Configurations for a complete listing of jumper

definitions. The default jumper configuration is as follows:

• Baseboard:

– JP1401 set to 1-2 to set the System FLASH to Read-Only

– JP1601 set to 2-3. This jumper setting should not be changed

– JP3801 set to 1-2 to enable assertion of VME SYSRESET (USPIIi-1v must be system controller)

– JP3901 set to 1-2 to enable reception of VME SYSRESET

– JP3304: factory set to mirror PS/2 or Sun configuration. See § 2.1 Determine Board Type and

Configuration

– All other baseboard jumpers are left uninstalled

• I/O Board:

– JP0705, JP0706 installed to configure Serial Port C and D as RS232.

– JP0801, JP0802, JP0803, JP0804, JP0805, JP0806, JP0808 set to 2-3 to configure Serial Port C

and D as RS232.

– All other I/O board jumpers are left uninstalled

• PMC Carrier Board:

– J11 and J12, the User I/O Adapter Card, is left uninstalled. This will route all 64 bits of User I/O

on the PMC Carrier board to PMC #1, as opposed to routing 32 bits of User I/O to PMC #1 and

32 bits of User I/O to PMC #2.

If the default jumper settings meet your requirements you are now ready to install the USPIIi-1v in a standard

VME chassis.

In addition to the USPIIi-1v a standard VME chassis with P1/P2 backplane is required. If the USPIIi-1v is to

be used in a workstation configuration instead of as an embedded controller, a hard disk and graphics frame

buffer or serial terminal will also be required.

2.3 Backplane Jumper Settings

In the case of the USPIIi-1v/2c and USPIIi-1v/3, certain signals require jumpers on the backplane of the VME

chassis. If the VME chassis does not have auto-jumpering capability, these jumpers need to be manually set.

The pins that require jumpers are located on the second slot occupied by the USPIIi-1v board:

• Pin A20 should be jumpered to pin A21 (IACK)

• Pin B4 should be jumpered to pin B5 (BG0)

Themis Computer 2-3

2. Installation

• Pin B6 should be jumpered to pin B7 (BG1)

• Pin B8 should be jumpered to pin B9 (BG2)

• Pin B10 should be jumpered to pin B11 (BG3)

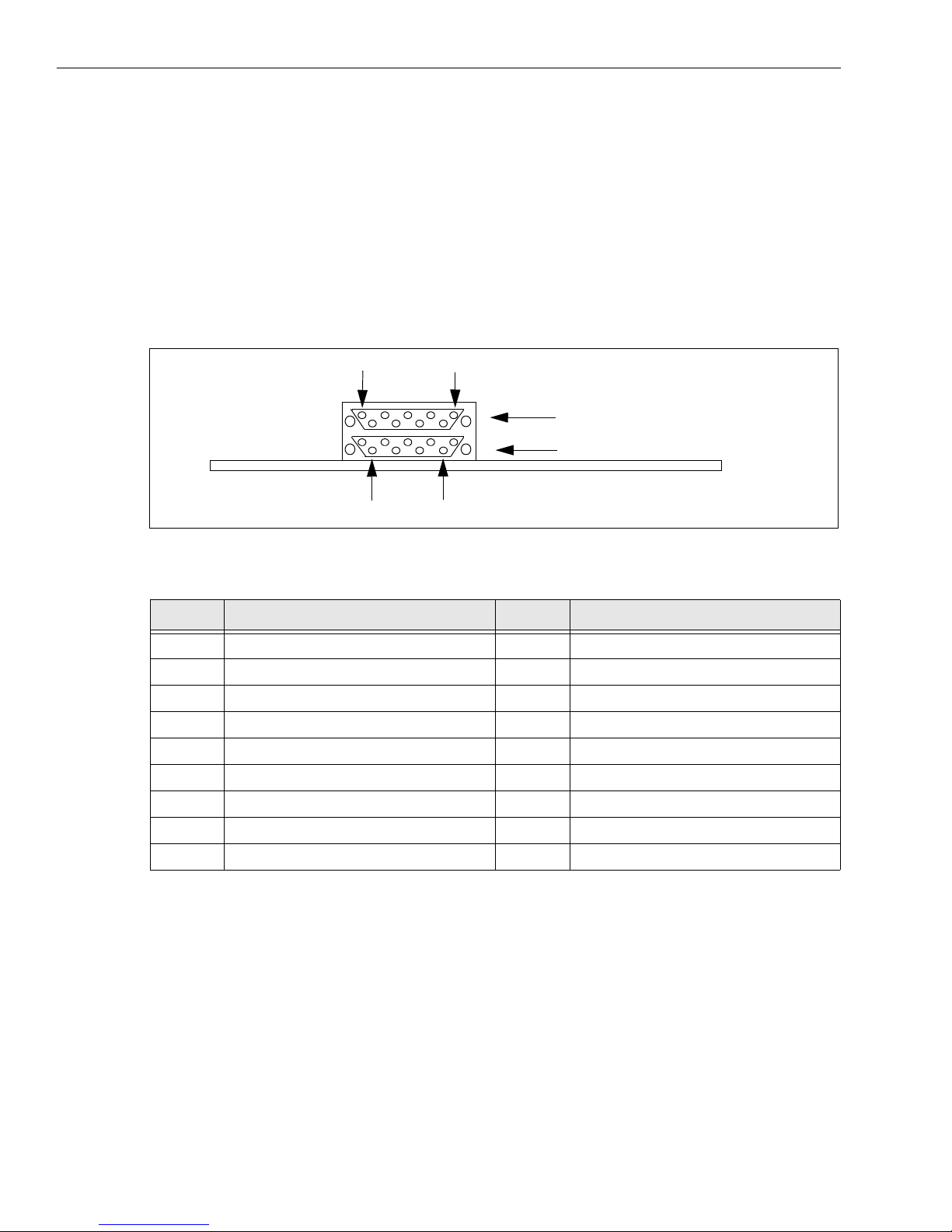

2.4 Installing The USPIIi-1v Paddle Board

The paddle board, also referred to as a “transition board”, attaches to the rear of the P2 backplane of the VME

chassis. It provides connectors for Serial Ports, Ethernet MII and SCSI.

• For the USPIIi-1v/1 and USPII-1v/2p, only one paddle board can be installed. It is part of the single slot

integration kit, INT-KIT-USPIIi-1v/1-VME. This paddle board must be installed at the rear of the P2

backplane, behind the position occupied by the baseboard (for the USPIIi-1v/2p, a second VME slot is

occupied by the PMC extension carrier). The paddle board provides connectors for:

– Serial Port B or keyboard/mouse (PS/2 or Sun)

– SCSI Port A

– Ethernet Port A MII

• For the USPIIi-1v/2c and USPIIi-1v/3, two paddle boards can be installed. They are part of the two- slot

integration kit, INT-KIT-USPIIi-1v/2-VME. The first paddleboard must be installed at the rear of the P2

backplane, behind the position occupied by the baseboard, as described above. The second paddle board

goes behind the position occupied by the second slot, also referred as the I/O board. It provides

connectors for:

– Serial Port C or D

– SCSI Port B

– Ethernet Port B MII

USPIIi-1v Hardware Manual

2-4

Themis Computer

2.5 Attaching Cables to Peripheral Devices

Attach adapter cables to the appropriate front panel and P2 paddle board connectors. The following sections

provide information on what adapter cables are required and how to attach them. Also refer to Appendices §

C Front Panel Diagrams and § D Board Diagrams.

The location of the console connector and of the keyboard and mouse connectors depends of the configuration

of the USPIIi-1v.

2.5.1 Console Port (TTYA)

In PS/2 mode: attach one end of cable 108113 to the front panel “Console” connector and the other end to a

ASCII serial terminal or emulator

In Sun mode: attach one end of cable 108376 to the front panel “TTYC” connector and the other end to a

ASCII serial terminal or emulator.

Note —

USPII-1v serial ports are wired in “DCE” mode. A null modem and a gender-changer may be

required for attachment to your serial terminal or emulator

Note —

If the USPIIi-1v is used with Creator Graphics, it is not mandatory to attach it to a serial terminal if

already connected to PS/2 or Sun keyboard/mouse. In this case, software will automatically use this keyboard

for input and the Graphics port for output.

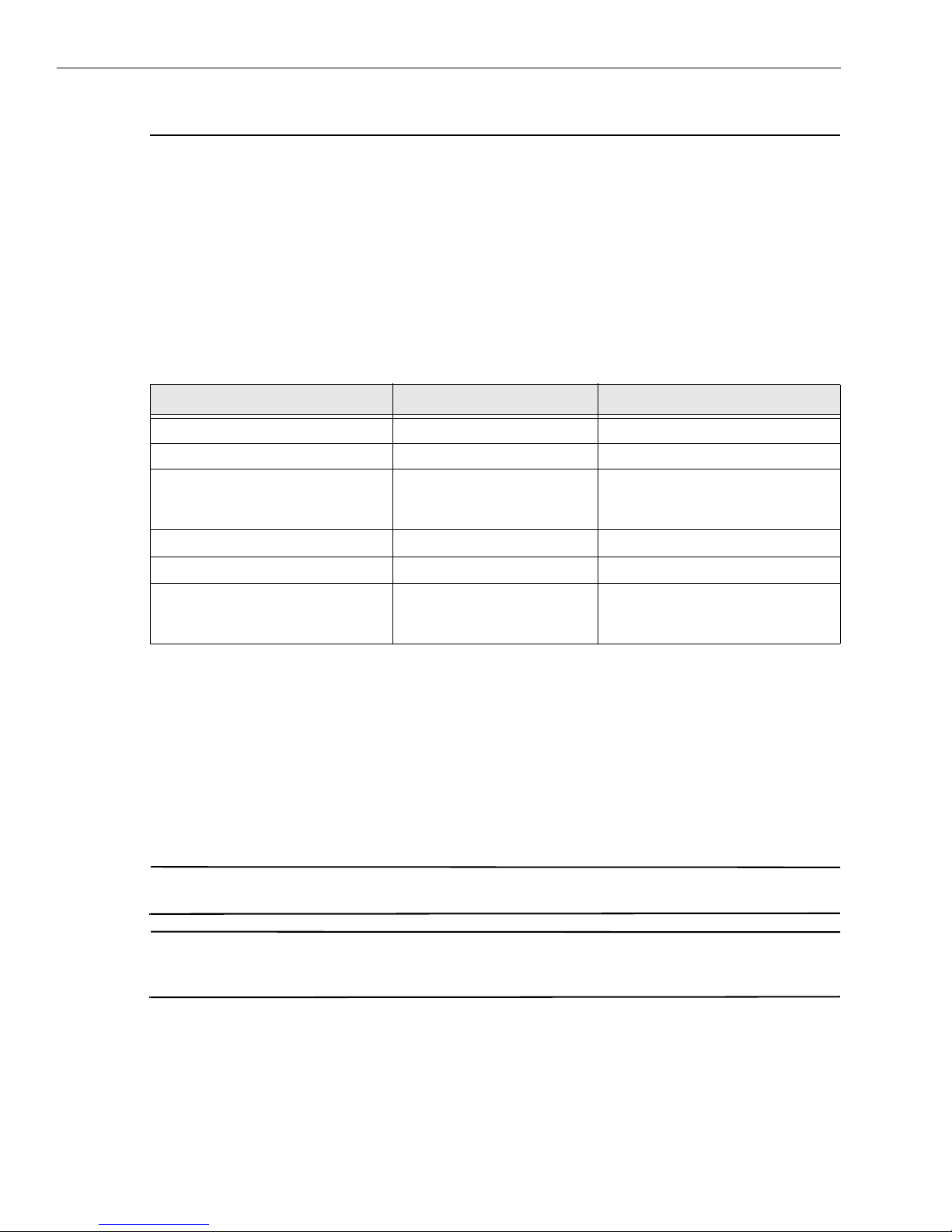

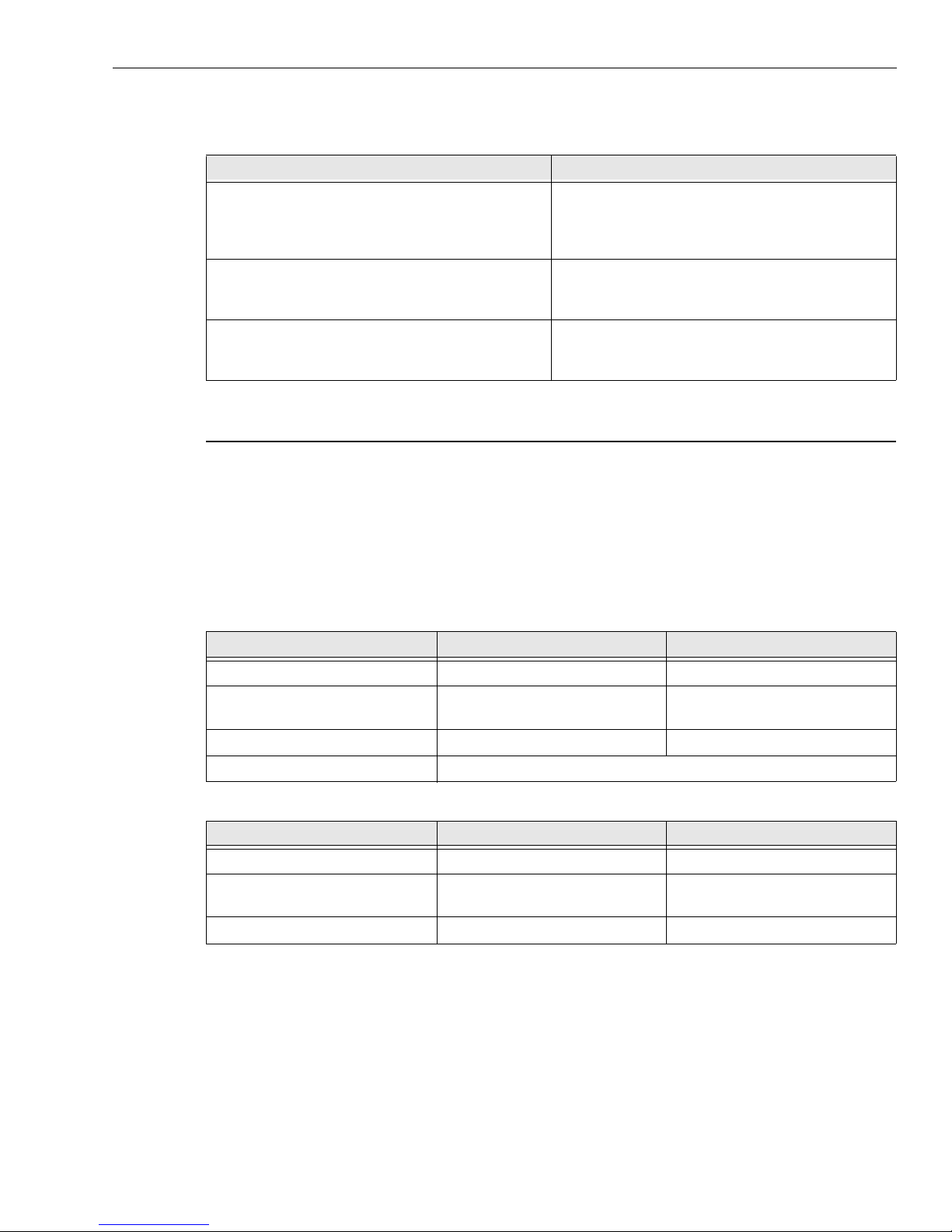

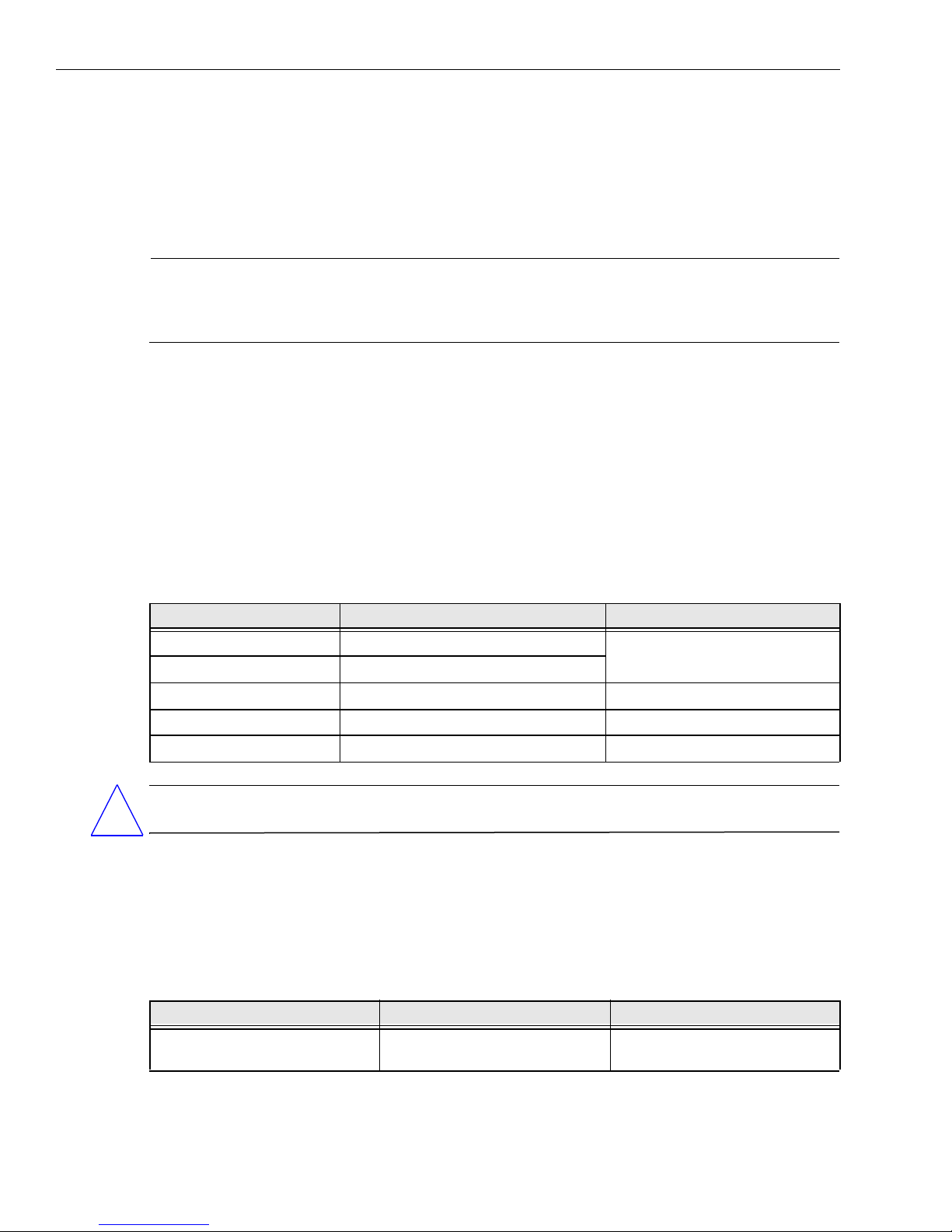

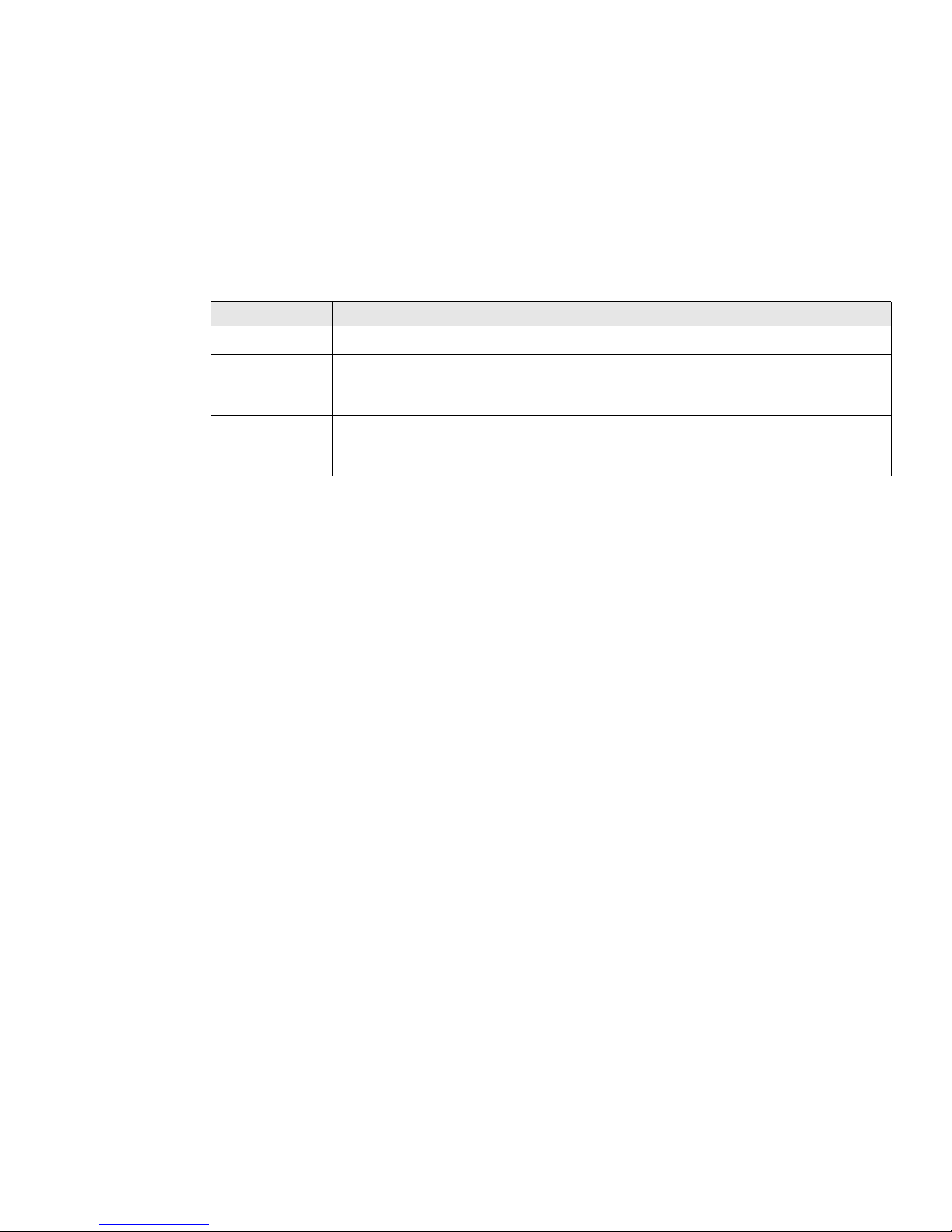

Table 2-1. Summary of different connectors configuration.

Connectors PS/2 Configuration Sun Configuration

Front panel “kybd/mouse” connector used as PS/2 keyboard NOT USED

Front panel “Console” connector used as Console port (TTYA) used as Sun keyboard/mouse port

Paddle board #1 DB9 used as PS/2 or Aux port

(TTYB), depending on solder

beads SB1807-1811

used as Sun keyboard/mouse port

Front panel “TTYC” used as serial port C (TTYC) used as Console Port (TTYA)

Front panel “TTYD” used as serial port C (TTYD) used as Aux port (TTYB)

Paddle board #2 DB9 used as serial port C or D,

depending on solder beads

SB301-306 (default: port C)

used as Console (TTYA) or Aux port

(TTYB) (default: Console)

Themis Computer 2-5

2. Installation

2.5.2 Keyboard and Mouse

In PS/2 mode: attach one end of cable 108114 to the front panel ““kybd/mouse” connector and the two other

ends to a PS/2 keyboard and a PS/2 mouse.

In Sun mode: attach one end of cable 108783 to the front panel “Console” connector and the other end to a

Sun type 5 keyboard/mouse set.

Note —

The POST (power on self test) displays the message “Warning: no keyboard detected” if no

keyboard is attached to the USPIIi-1v.

2.5.3 Ethernet Network

The USPIIi-1v features an RJ-45 for 10/100 BaseT Ethernet interface connections. An MII interface is

provided on the paddle board. The interface has auto-detection capabilities and no configuration is necessary.

If only the baseboard is present, a single network connection (Ethernet A) available, either through the RJ45

connector or MII. If the I/O Board is present a second ethernet (Ethernet B) is available. Both Ethernets A and

B may be active simultaneously.

After attaching the USPIIi-1v to a network, you can verify proper physical connection by executing the

Openboot network selftest (test net). This test will indicate external loopback failure on each of the network

interfaces when there is not a proper physical connection:

2.5.4 SCSI A and B

Themis Computer provides adapter cables for SCSI A or B with conversion to standard 68 pin, 0.050 inch,

male SCSI connectors. Attach cable 108712 to the desired SCSI connection (SCSI A or SCSI B) on the front

panel min-din 68 connector labelled either “SCSI A” or “SCSI B”. Additionally, you can attach cable 108432

to the SCSI connector of paddle board #1 (SCSI A) or #2 (SCSI B). It is possible to use both front and rear

connections simultaneously. The USPIIi-1v features an automatic SCSI termination system for each

individual SCSI port. When the board is located at one end of the SCSI chain (i.e. SCSI devices connected

ok test net

Using MII Ethernet Interface

Lance Register test -- succeeded

Internal loopback test -- succeeded

External loopback test -- Lost Carrier (transceiver cable problem?)

send failed

Using TP Ethernet Interface

Lance Register test -- succeeded

Internal loopback test -- succeeded

External loopback test -- succeeded

send ok

net selftest succeeded

ok

USPIIi-1v Hardware Manual

2-6

Themis Computer

either at the front OR at the back), onboard SCSI terminators will be activated to terminate that end of the

SCSI bus. When the board is sitting in the middle of the SCSI chain (i.e. devices connected both at the front

and at the back), onboard terminators will be automatically removed.

You can verify proper physical connection by executing the Openboot command probe-scsi. This command

transmits an inquiry command to SCSI devices connected to the system unit onboard SCSI interface. If the

SCSI device is connected and active, the target address, unit number, device type, and manufacturer name is

displayed. The example below identifies the probe-scsi output me

ssage:

2.5.5 Creator Graphics Card

A Creator Graphics Card can be installed by Themis Computer on the USPIIi-1v/2c and USPIIi-1v/3. A

DB13W3 video output connector is available at the front, together with a Din-8 synchronization port for

stereo displays.

Note —

Creator Graphics must be used in conjunction with a PS/2 or Sun keyboard and mouse. If the latter

are not attached to the USPIIi-1v board prior to power on, OpenBoot will redirect its text output to the

serial console and not to Creator Graphics

2.6 Configuring The VME Interface

Themis has implemented a variable and flexible VMEbus interface using both onboard jumpers, OpenBoot

PROM (OBP) commands, and OBP environment variables specific to the USPIIi-1v board.

The USPIIi-1v is typically re-configured when VMEbus boards are added, removed, or changed in the

chassis. Board configuration normally involves allocation of VMEbus master access address, interrupts, and

slave base address of the USP-2.

Only the VME SYSRESET function is configured by hardware jumpers. Consult Appendix B.2.1, "Baseboard

Jumpers," for details. All other VMEbus interface related options are configured using extensions to the Sun

OpenBoot PROM monitor program and are described in the “USPIIi-1v Software Manual”, Themis P/N

108966.

ok probe-scsi

Primary UltraSCSI bus:

Target 0

Unit 0 Disk SEAGATE ST32272W 0876

Target 6

Unit 0 Removable Read Only device TOSHIBA CD-ROM XM-6201TA1037

Secondary UltraSCSI bus:

ok

Themis Computer 3-1

3

3Specification

3.1 Overview

The USPIIi-1v is available under four product configurations:

• USPIIi-1v/1, “USPIIi-1v Baseboard” is the single slot baseboard.

• USPIIi-1v/2c, “USPIIi-1v with Graphics and Expanded I/O” provides the USPIIi-1v baseboard and, in

the second slot, an I/O Expansion board and an optional Creator Graphics card.

• USPIIi-1v/2p, “USPIIi-1v with a PMC Carrier Board” provides the USPIIi-1v baseboard and, in the

second slot, a triple PMC Carrier board.

• USPIIi-1v/3, “USPIIi-1v with Graphics, Expanded I/O, and PMC Carrier Board” provides the all the

features in the “USPIIi-1v with Graphics and Expanded I/O” and the “USPIIi-1v with a PMC Carrier

Board”. The optional Creator Graphics card and Expanded I/O are located in the second slot. The PMC

Carrier board is located in the third slot.

The Creator Graphics card is physically separate from the I/O board and is completely optional. It is also

possible to have the Baseboard with Creator Graphics without the I/O board or the Baseboard with the I/O

Board but without Creator Graphics card. These options are also possible with the triple slot version of the

USPIIi-1v.

A single slot, P2 paddle board is also available for the Baseboard and the I/O Board. The paddle board

provides I/O connections for the MII, SCSI, and Serial signals.

3.1.1 Baseboard

The USPIIi-1v Baseboard is intended to provide an UltraSPARC-IIi platform in an industry standard single

slot, 6U, VME form factor. It has been optimized for service in the telecommunications and embedded

systems industries. The baseboard is implemented as a single slot VMEbus board with an on board

UltraSPARC-IIi processor/cache complex and proprietary coplanar memory boards. The UltraSPARC-IIi is

available in 360 MHz or 440 MHz with 2 MB external cache.

The memory subsystem utilizes a family of proprietary, coplanar, stackable DRAM memory modules of

either 64 MB, 128MB, 256 MB or 512 MB per module. Memory configurations of 64 MB, 128 MB, 256 MB,

512 MB, and 1GB are supported.

USPIIi-1v Hardware Manual

3-2

Themis Computer

The local I/O subsystem is PCI based, with separate PCI channels provided for I/O functions and external

VMEbus backplane access. SCSI ports A and B, Ethernet A, Console Port and PS/2 Keyboard/Mouse

connections are provided on the front panel of the baseboard.

The back panel VMEbus interface provides signals for UltraWide SCSI A, Ethernet A MII, and Serial Port B.

Additional signals are provided for System, Alarm, Warning, and RESET.

3.1.2 I/O Board and Creator Graphics

The USPIIi-1v I/O Board occupies the second slot and provides front panel access to RS-232/422 Serial Ports

C and D, Sun Keyboard/mouse, Bidirectional IEEE1284 Parallel Port, RJ-45 10/100-BaseT Ethernet B, and

Audio Line-In and Line-out. Also, rear access is provided on the P2 connector for Ethernet B MII, SCSI B

and Serial ports C or D.

3.1.3 PMC Carrier Board

A PMC Carrier Board is available for vendor specific, 32-bit, 33 MHz, PMC expansion boards. Up to three

(3) PMC expansion cards are supported.

The User I/O on the PMC Carrier Board may be configured. Either 64 bits of User I/O may be made available

on PMC #1, while the User I/O on PMC #2 is not used. Or, 32 bits of User I/O may be made available on

both PMC #1 and PMC #2.

3.1.4 Paddle Board

A single slot, P2 paddle board is available for the USPIIi-1v baseboard and for the USPIIi-1v I/O board. The

same paddle board design used for the baseboard is used for the I/O board.

When used in conjunction with the baseboard, the paddle board provides the user with connections for MII A,

Serial B, and SCSI A. When used in conjunction with the I/O Board, the paddle board provides connections

for Serial port C or D, MII B and SCSI B.

Themis Computer 3-3

3. Specification

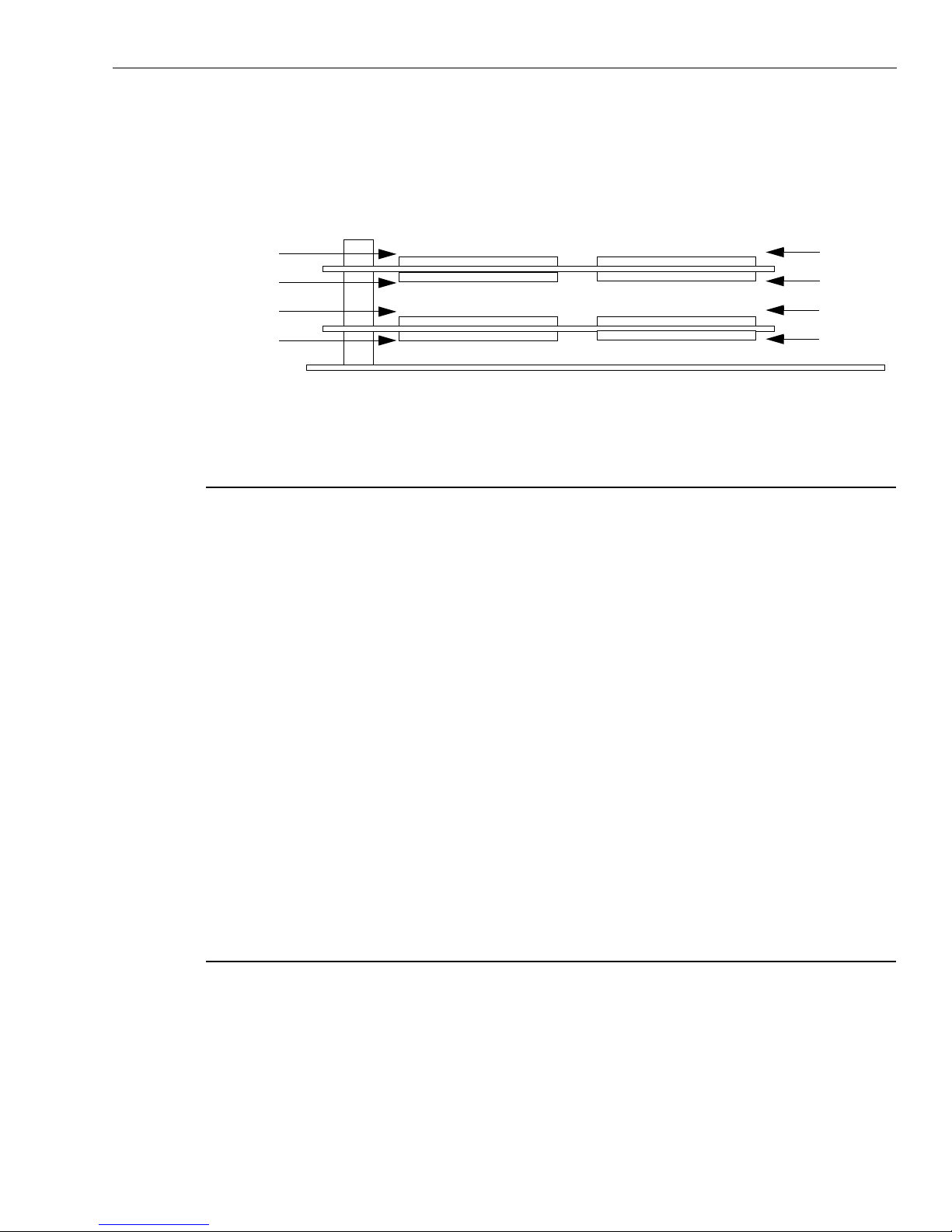

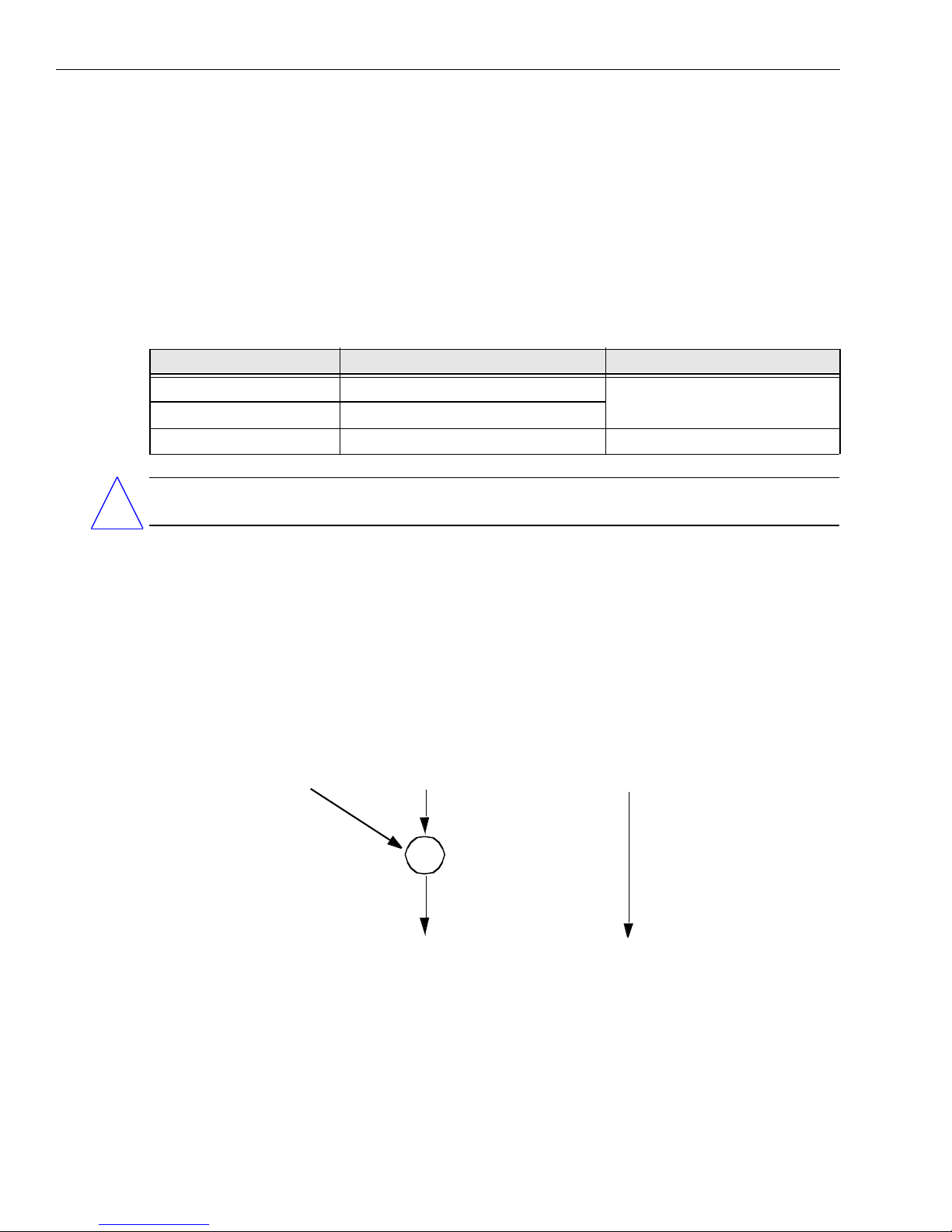

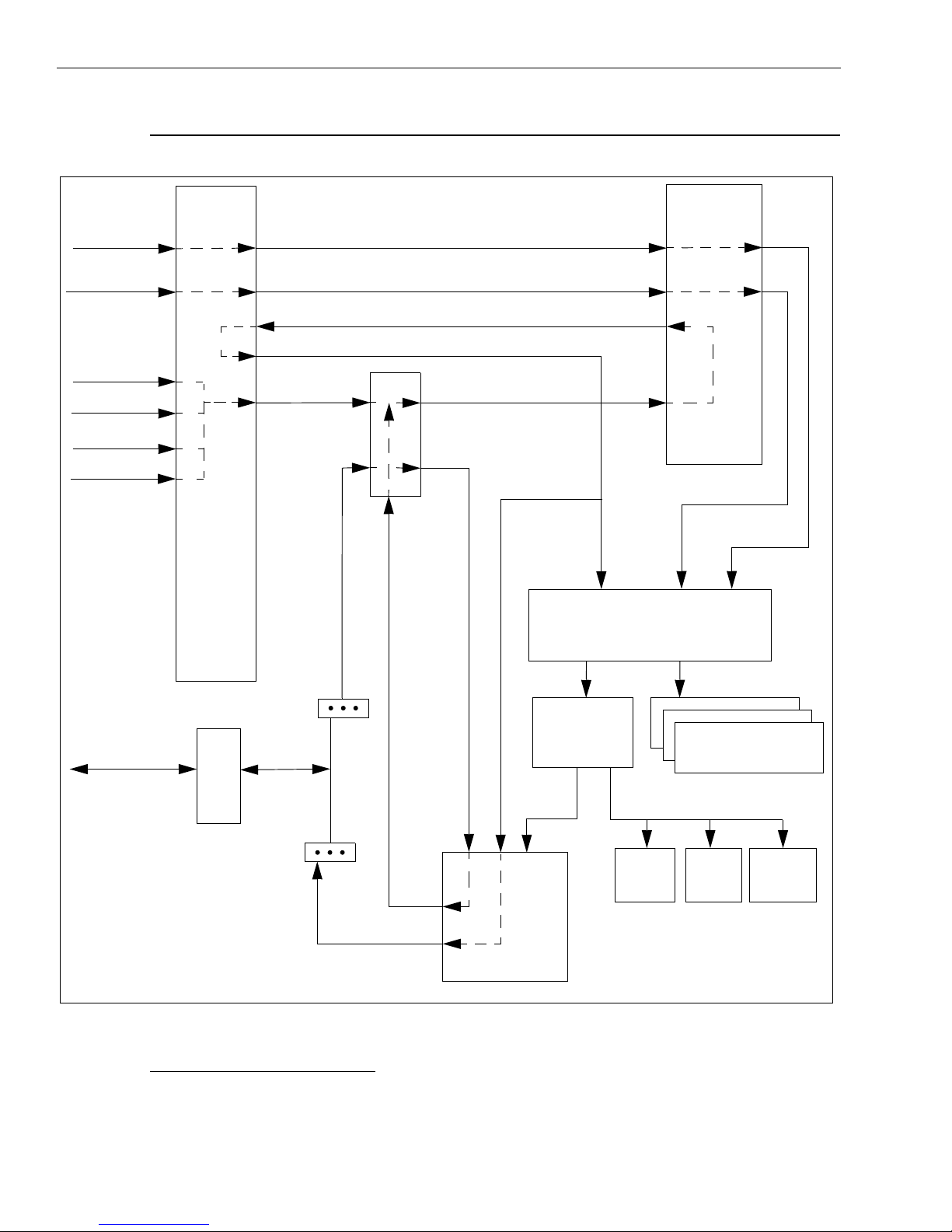

3.1.5 Block Diagram

Figure 3-1. USPIIi-1v Baseboard Block Diagram

UltraSPARC-IIi

E-Cache

DRAM interface

PCI interface

Memory Mezzanine

72

Xcvers

buffers

EDO DRAM chips

EDO DRAM chips

Addr/

144

PCI-VME

66MHz

32-bit PCI

SCSI

Ethernet A

Super I/O

TOD

Flash

E-Bus

Serial

Keyboard

Parallel

RIC

PCIOs

f

f

f *

f

b

b

f

33MHz

APB

Cards

Cache Interface

f

BA

A

b

Bridge

PMC

Expansion

PMC

Slot

#1

PMC

Slot

#2

ff

CNTLs

32-bit PCI

PMC

Slot

#3

f

I/O

Exp.

b*

Exp. Conn

Ethernet B

33MHz

AB

Other

I/O

32-bit PCI

2nd & 3rd Slot Exp.

b *

* via I/O Board

b

f

Creator Graphics

UPA64

DATA

MII

PHY

MII

USPIIi-1v Hardware Manual

3-4

Themis Computer

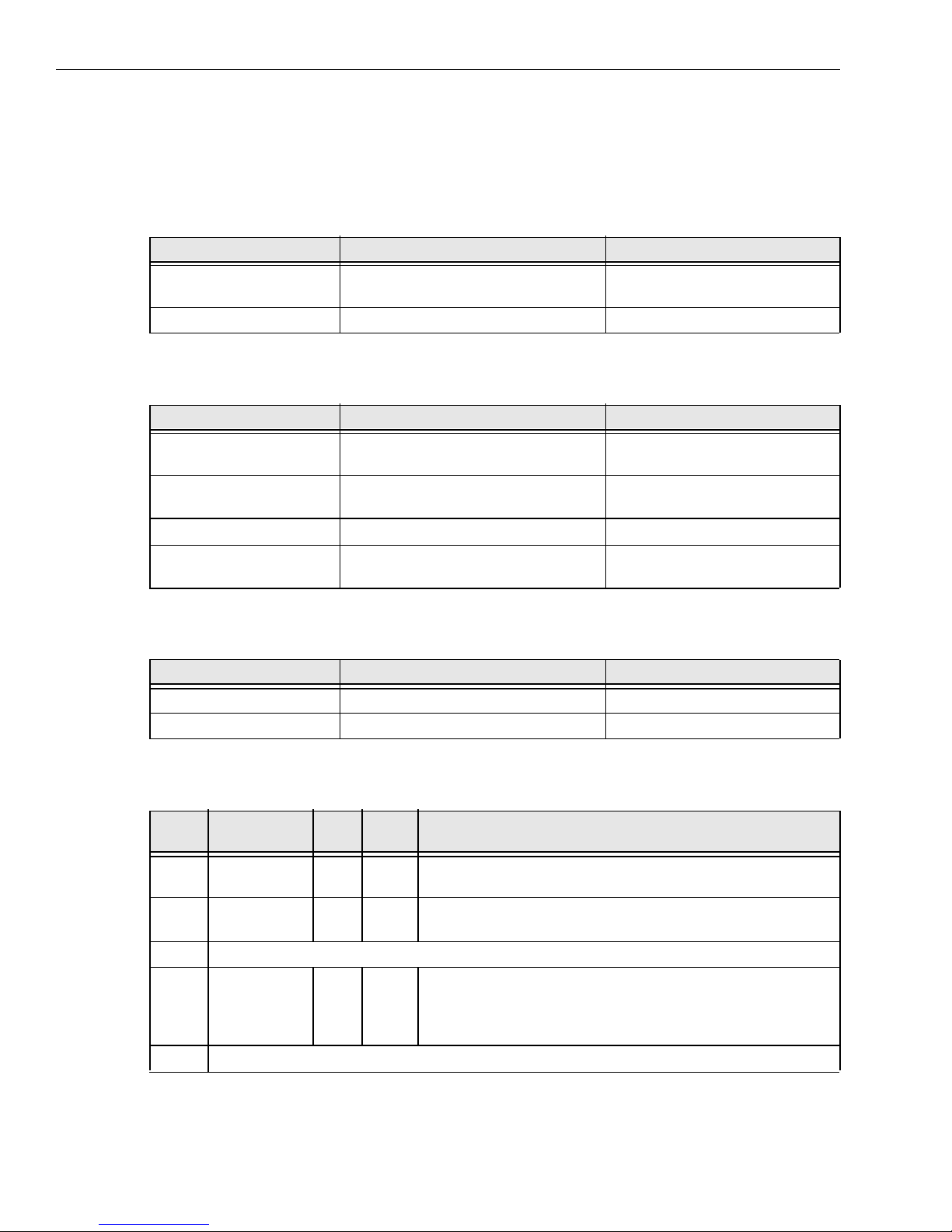

3.2 System Specification

3.2.1 Processor & Memory Subsystems

Below are the processor and memory subsection specifications.

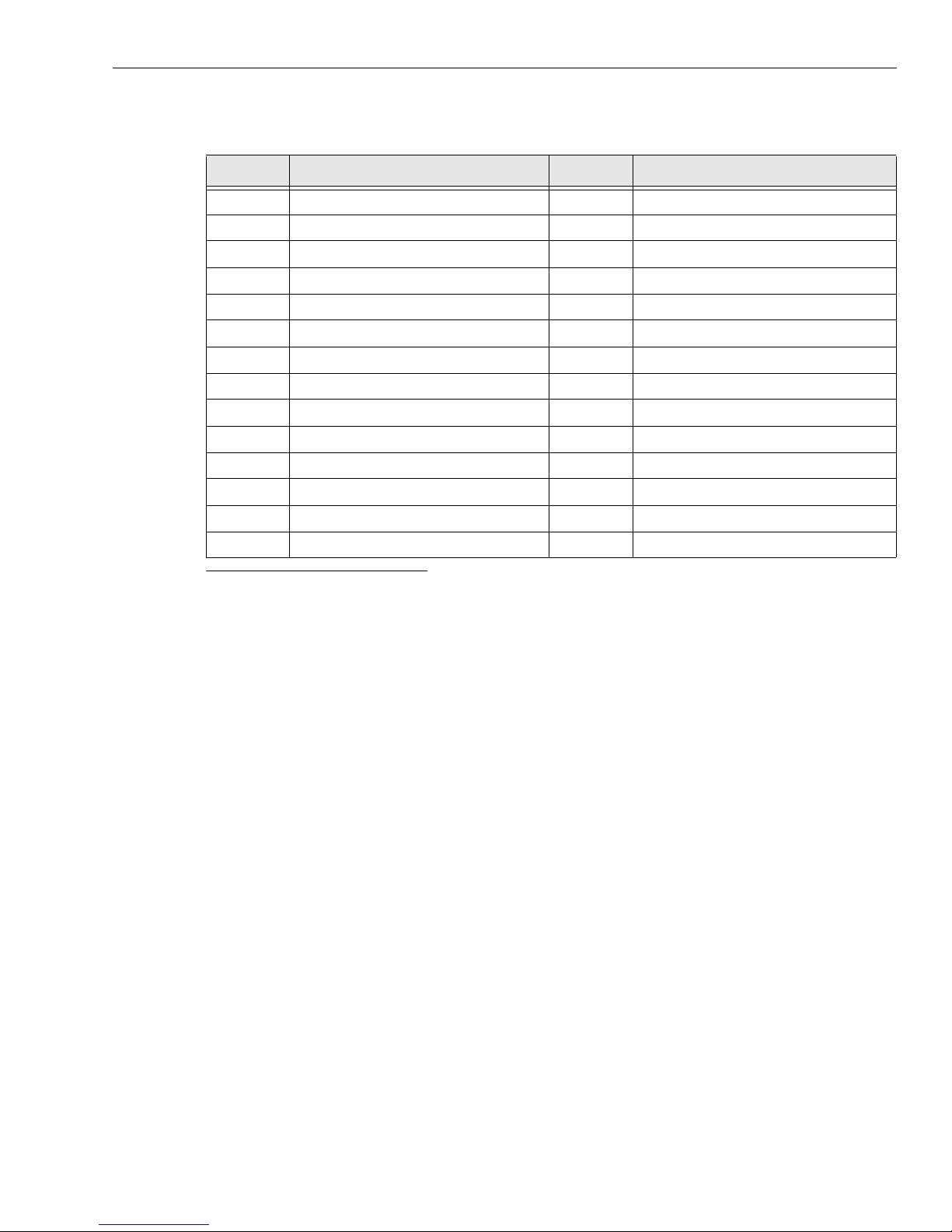

Table 3-1. Processor Specifications

Feature/Function Specifications

Processor UltraSPARC-IIi

Processor Speed Grade 1 - 360 MHz

Grade 2 - 440 MHz

Performance 18.3 SPECint95 @ 440 MHz w/ 2 MB cache (estimate)

20.4 SPECfp95 @ 440 MHz w/ 2 MB cache (estimate)

External Cache 2 MB SRAM, fast Register-Latch access mode

I/O Bus Interface 32 bit/66MHz PCI data path from CPU

Table 3-2. Memory Specification

Feature/Function Specifications

Main Memory Proprietary Coplanar Modules

One or Two Modules

a

a. Under certain conditions, it is actually possible to stack four memory modules for a total of 1 GBytes. Consult the factory.

Memory Bus Interface 72 bit Data Path from CPU, including 8 bit ECC

2 to 1 Interleave to DRAM

13 bit Address Bus

3.3V Level Interface

Memory Modules Four Module Types

64 MB, using 36 - 4Mx4 EDO DRAMs

128 MB, using 18 - 4Mx16 EDO DRAMs

256 MB, using 36 - 4Mx16 EDO DRAMs

512 MB, using 36 - 4Mx64 EDO DRAMs

Memory Configurations 64 MB - One 64 MB Module

128 MB - One 128 MB Module

256 MB - One 256 MB Module

512 MB - Two 256 MB Modules

512 MB - One 512 MB Module

1 GByte - Two 512 MB Modules

Themis Computer 3-5

3. Specification

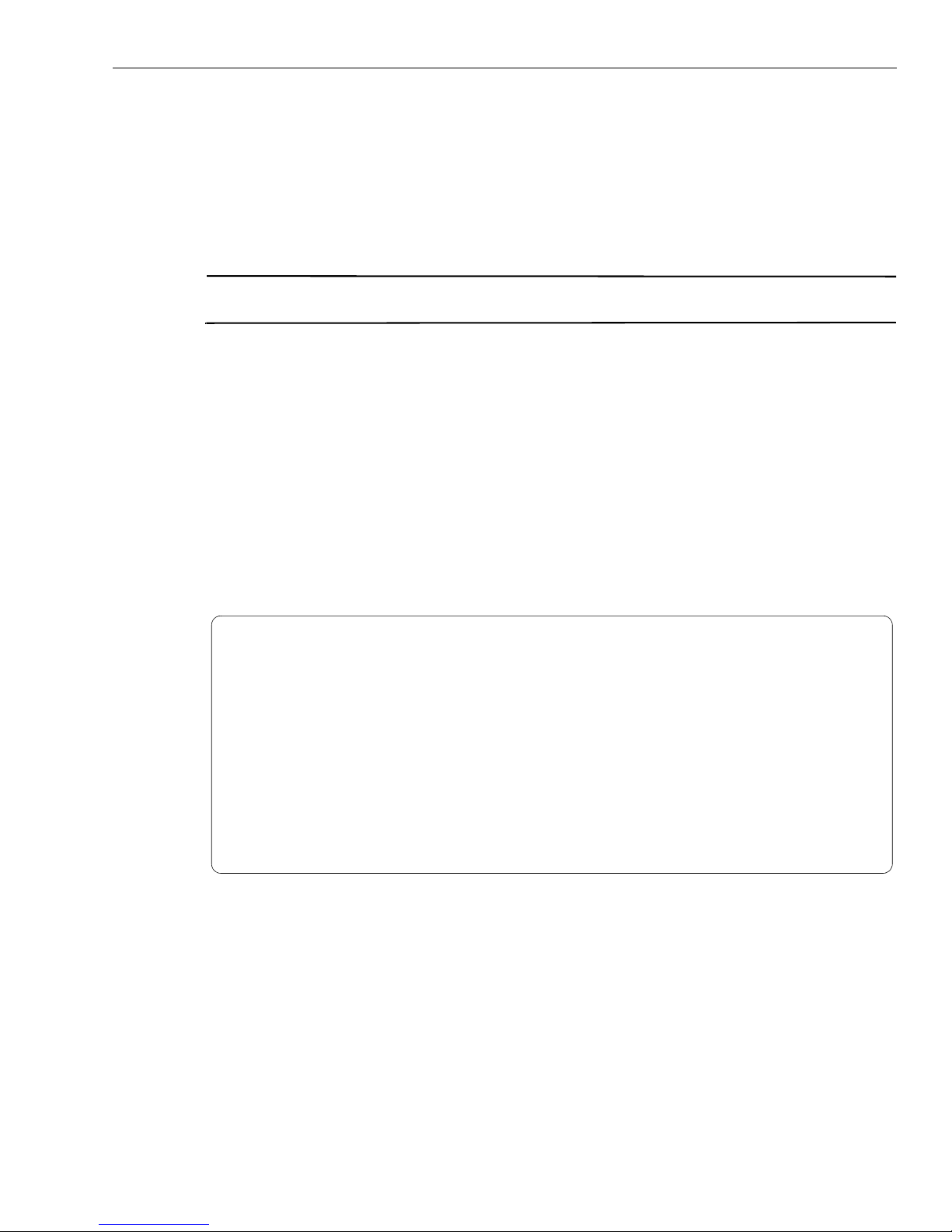

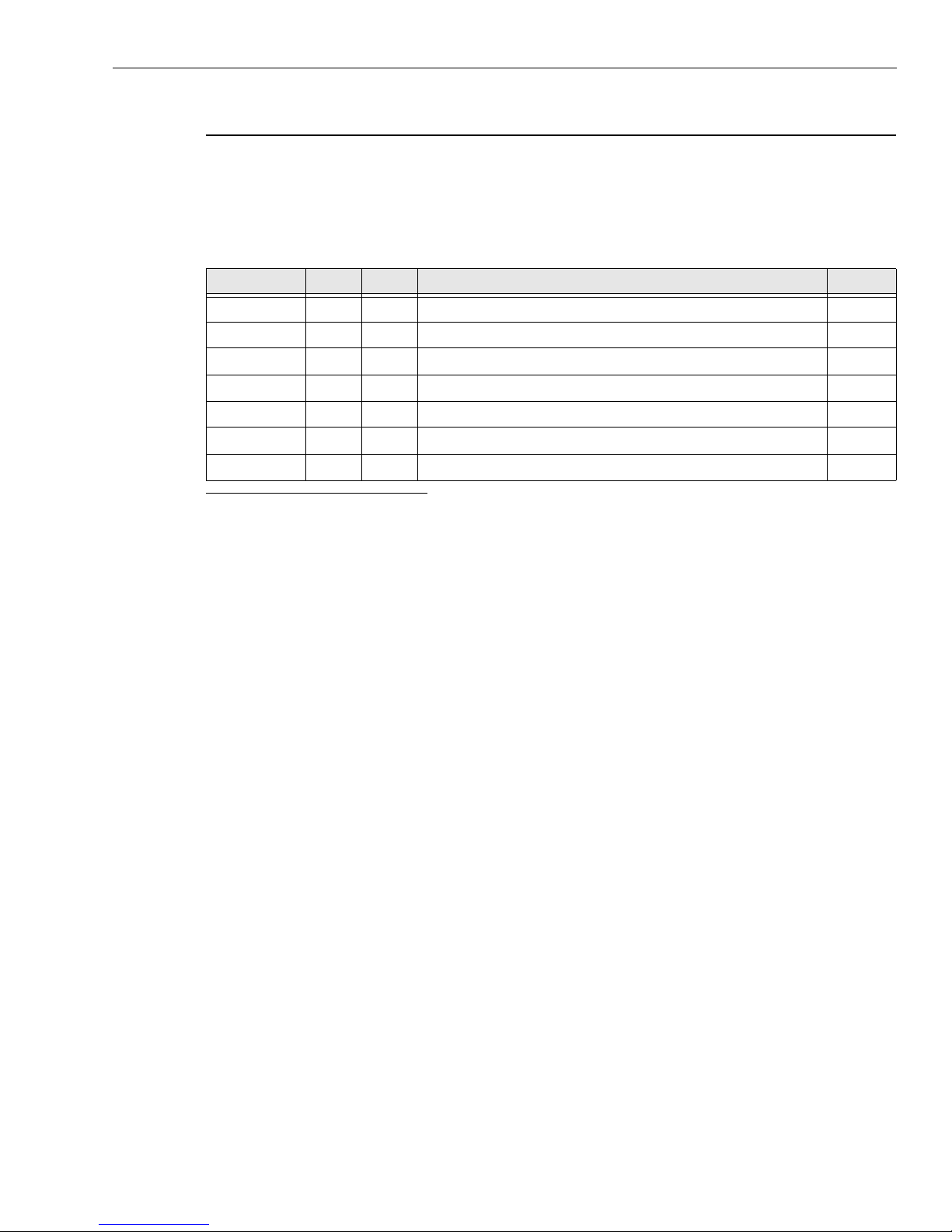

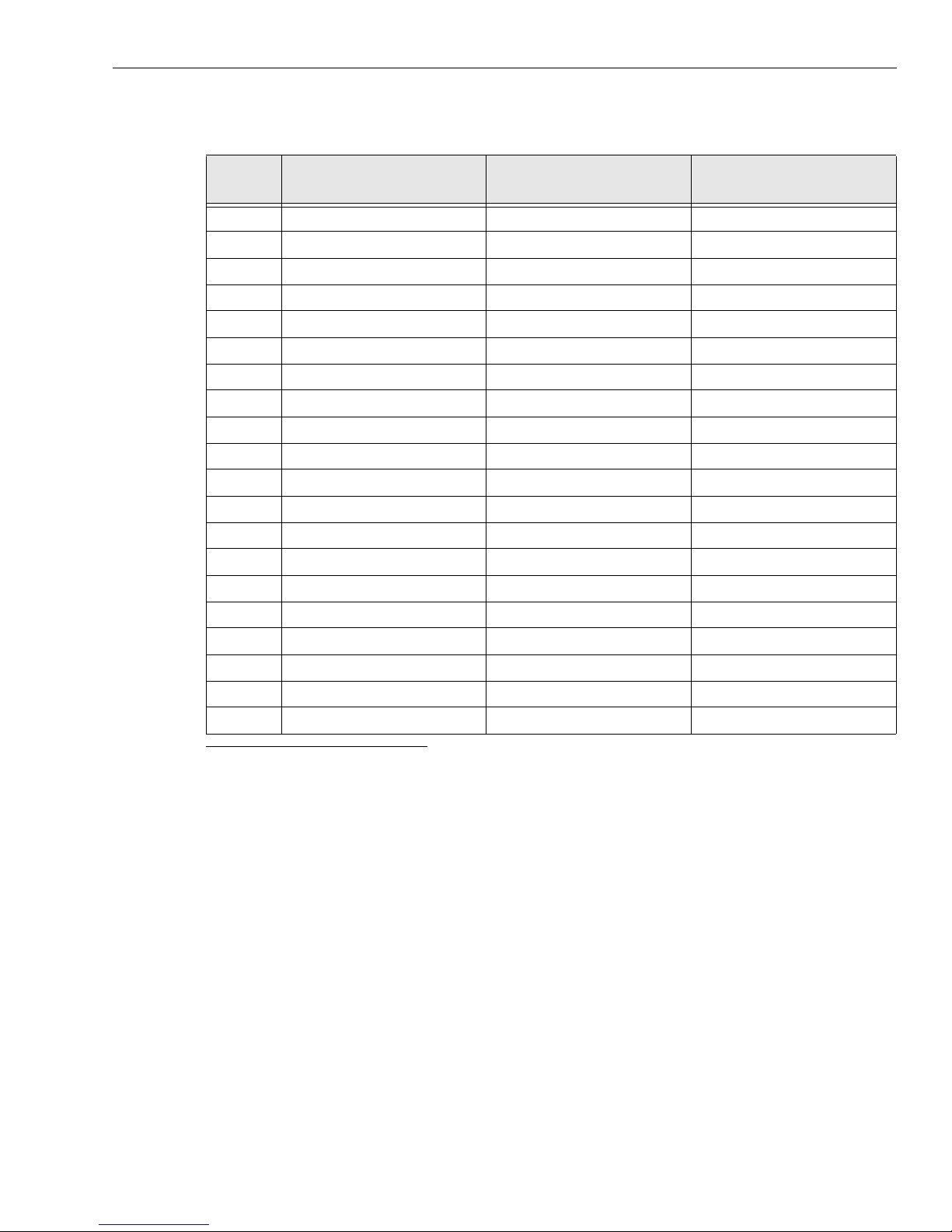

3.2.2 I/O Subsystem

Table 3-3, "I/O Sub-system Specification," on page 3-5, summarizes the I/O subsystem functionality of the

various product configurations.

Table 3-3. I/O Sub-system Specification

Function

Single Slot

(Baseboard)

Dual Slot

(Baseboard,

Creator

Graphics and

I/O Board)

Dual Slot

(Baseboard and

PMC Carrier

Board)

Triple Slot

(Baseboard,

Creator

Graphics, I/O

Board, and PMC

Carrier Board)

KB/Mouse Port

PS/2 Compatible

Slot 1 FP/P2

b

Slot 1 FP/P2

b

Slot 1 FP/P2

b

Slot 1 FP/P2

b

KB/Mouse Port

Sun compatible (requires I/O

board)

a

Slot 1 FP/P2 Slot 1 FP/P2 Slot 1 FP/P2 Slot 1 FP/P2

Serial Port A (async RS-232)

- not available in Sun mode-

Slot 1 FP Slot 1 FP Slot 1 FP Slot 1 FP

Serial Port B (async RS-232)

- not available in Sun mode-

Slot 1 P2

b

Slot 1 P2

b

Slot 1 P2

b

Slot 1 P2

b

Serial Port C

Asynchronous/Synchronous

RS-232/422

na Slot 2 FP/P2

c

na Slot 2 FP/P2

c

Serial Port D

Asynchronous/Synchronous

RS232/422

na Slot 2 FP/P2

c

na Slot 2 FP/P2

c

Parallel Port

Bi-Directional IEEE1284

na Slot 2 FP na Slot 2 FP

Ethernet Port A

Auto-negotiating

10/100BaseT on FP

MII Interface on P2

Slot 1 FP RJ45 Slot 1 FP RJ45,

P2 MII

Slot 1 FP RJ45,

P2 MII

Slot 1 FP RJ45,

P2 MII

Ethernet Port B

Auto-negotiating

10/100BaseT on FP

MII Interface on P2

na Slot 2 FP RJ45,

P2 MII

na Slot 1 FP RJ45,

P2 MII

SCSI Port A

Single Ended Ultra/Wide SCSI

40 MB/s

Slot 1 FP/P2 Slot 1 FP/P2 Slot 1 FP/P2 Slot 1 FP P2

SCSI Port B

Single Ended Ultra/Wide SCSI

40 MB/s

Slot 1 FP Slot 1 FP &

Slot 2 P2

Slot 1 FP Slot 1 FP &

Slot 2 P2

PMC Expansion, 32-bit/33MHz

Three PMC Slots in a single

VME slot

d

na na Slot 2:

PMC1:FP/P2

PMC2: FP/P2

PMC3: FP

Slot 3:

PMC1: FP/P2

PMC2: FP/P2

PMC3: FP

Creator Graphics na Slot 2

(Optional)

na Slot 2 (Optional)

USPIIi-1v Hardware Manual

3-6

Themis Computer

* Key:

FP - Interface via front panel connector

P2 - Interface via P2 connector

Slot 1, 2, and 3 refer to the position of the VME slots. Baseboard is always on slot 1.

3.2.3 Auxiliary Functions

Table 3-4, "Auxiliary Functions Specifications," on page 3-6 summarizes the functional specifications of the

auxiliary functions. These specifications apply to all four product configurations.

Audio Line In

Impedance = 10Kohm

Vrms(max) = 2 V

na Slot 2 na Slot 2

Audio Line Out

Impedance = 200 ohm

Vrms(max) = 2 V

na Slot 2 na Slot 2

a. Sun keyboard/mouse utilizes the two baseboard serial ports (serial A and B). Therefore, the console port becomes the next one available,

serial port C on the I/O board.

b. Selection is exclusive: Only one between port B and PS/2 keyboard/mouse is available on P2

c. Selection is exclusive: Only one between ports C and D is available on P2

d. The User I/O on the PMC Carrier Board may be configured. Either 64 bits of User I/O may be made available on PMC #1, while the User I/O

on PMC #2 is not used. Or, 32 bits of User I/O may be made available on both PMC #1 and PMC #2.

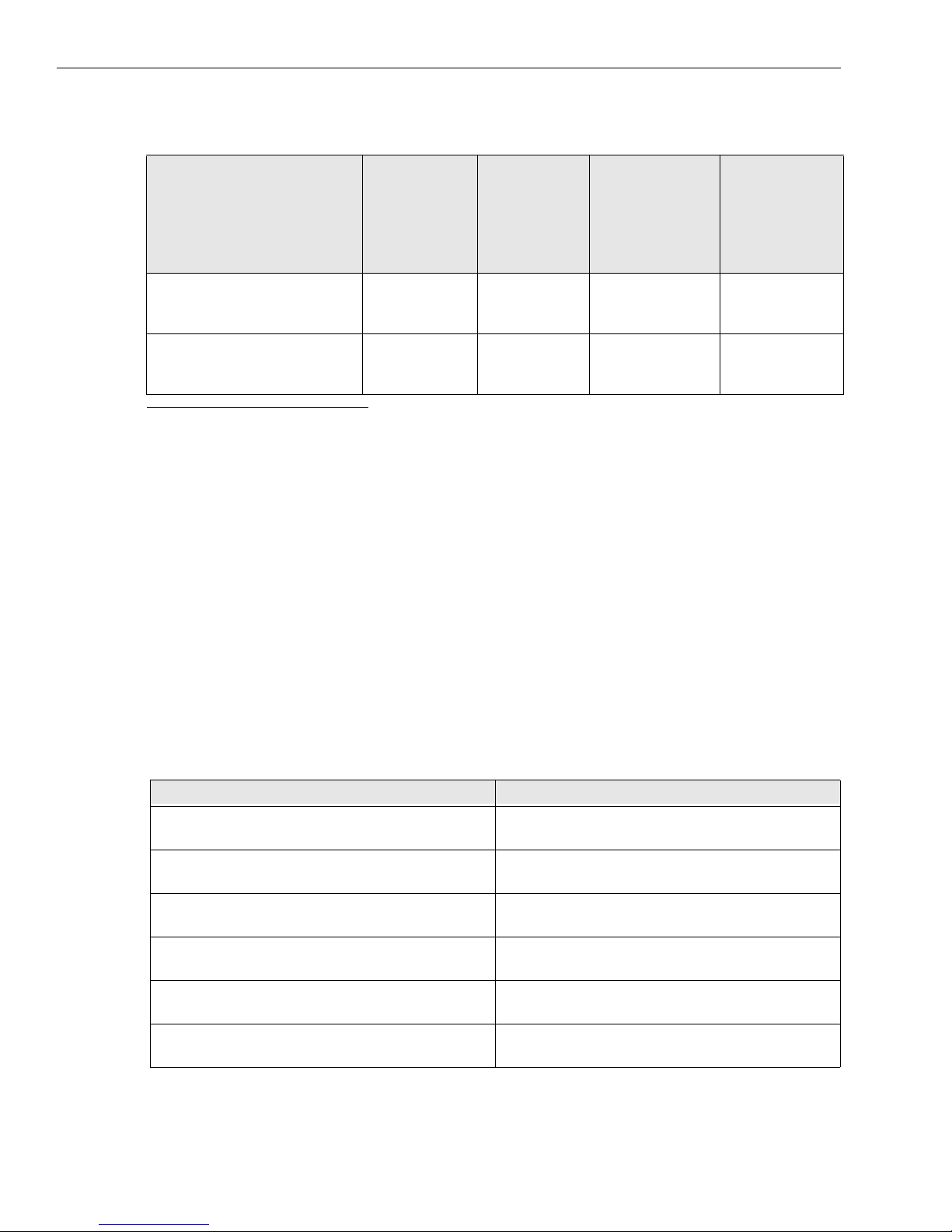

Table 3-4. Auxiliary Functions Specifications

Feature/Function Specifications

Boot Flash 2 MB or 4 MB

One 28F016 or 28F032 Device

User Flash 8 MB

Two 28F032 Devices

NVRAM/TOD 8 KB (8Kx8), Battery Backed

M48T59

Power OK LED One Bi-color Green/Amber/Red LED

Located on Front Panel of the Baseboard

System Status LED One Green LED

Located on Front Panel of the Baseboard

Reset Switch Momentary Push-button - Generates POR

Located on Front Panel

Table 3-3. I/O Sub-system Specification

Function

Single Slot

(Baseboard)

Dual Slot

(Baseboard,

Creator

Graphics and

I/O Board)

Dual Slot

(Baseboard and

PMC Carrier

Board)

Triple Slot

(Baseboard,

Creator

Graphics, I/O

Board, and PMC

Carrier Board)

Themis Computer 3-7

3. Specification

3.3 Environmental Specification

When measuring the operating environment air temperature for the USPIIi-1v, measure the air temperature as

close to the air intake port on the enclosure as possible.

Although the thermal characteristics of the USPIIi-1v are quite good, the maximum air flow should be across

the USPIIi-1v board processor section.

Watchdog Timers Three Level Watchdog

Level One: Interrupt

Level Two: XIR

Level Three: POR Reset

Voltage Sensors Monitors +5V Supply

XIR when outside of 4.75-5.25 V

POR when outside of 4.5V-5.5 V

Temperature Sensors Two Level

Level One: XIR

Level Two: Shutdown

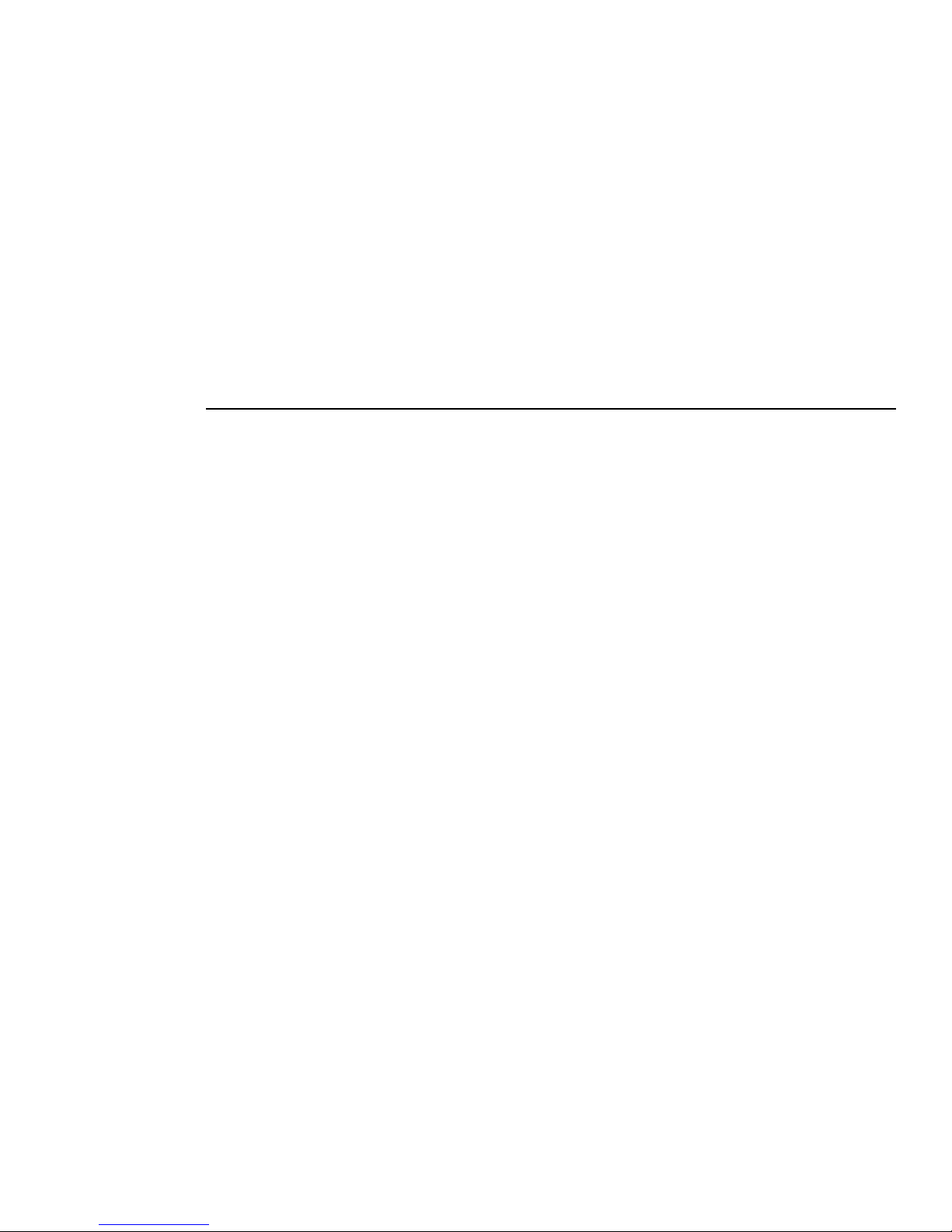

Table 3-5. USPIIi-1v Operating Environmental Specifications

Description Minimum Value Maximum Value

Temperature Range 0 C 55 C

Humidity Range (relative

non-condensing at 104 F (40 C)

5% 95%

Altitude Range -500 meters 9,843 feet (3,000meters)

Air Flow 300 lfm airflow at 50 C

Table 3-6. USPIIi-1v Non-operating Environmental Specifications

Description Minimum Value Maximum Value

Temperature Range -40 C 85 C

Humidity Range (relative non-con-

densing at 104 F (40 C)

5% 95%

Altitude Range 0 feet (0 meters) 38,370 feet (12000 meters)

Table 3-4. Auxiliary Functions Specifications

Feature/Function Specifications

USPIIi-1v Hardware Manual

3-8

Themis Computer

3.4 Estimated Power Requirements

Table 3-7. Estimated Power Requirements

Configuration

(USPIIi-1v/1 with

360/440 MHz processor)

Watts Dissipation

(typical)

128 MBytes memory 32/34 Watts

256 MBytes memory 34/36 Watts

1024 MBytes memory 35/37 Watts

Themis Computer 4-1

4

4Hardware Overview

4.1 Major Components

The following sections provide a description of the major of the USPIIi-1v. More detailed explanations of

certain subsystems is provided in later sections and chapters.

4.1.1 SME UltraSPARC-IIi Processor and Cache

The Central Processor for the USPIIi-1v is the UltraSPARC-IIi (SME: SME1430). There are two versions of

CPU available, the UltraSPARC IIi-360 and the UltraSPARC IIi-440. The architecture complies with SPARC

V9 instruction set, which enables the system to use a wide range of peripherals and the high performance

Solaris 2.6 operating system. For further details on the UltraSPARC-IIi CPU refer to the “USPIIi-1v Software

Manual”, or the SME1430 Highly Integrated 64-bit RISC Processor, PCI Interface Data Sheet, SUN

document number 805-0086-02, and the UltraSPARC-IIi User’s Manual, SUN part number 805-0087-01.

4.1.2 E-Cache

The E-Cache (also referred to as “Level 2 Cache”) is a unified, write-back, allocating-on-misses, direct

mapped cache. The E-Cache is physically indexed and physically tagged (PIPT) and has no virtual or context

information. Except for stable storage and error management, the operating system requires no knowledge of

the E-Cache after initialization. The E-Cache includes the content of the Instruction Cache (I-Cache) and the

Data Cache (D-Cache). For more information on the I-Cache and D-Cache, Section 5.2.6, "Instruction and

Data Cache (I- and D- Cache)," on page 5-3.

The USPIIi-1v E-Cache uses a fast Register-Latch access mode. In the Register-Latched mode (also referred

to as “2-2”) the E-Cache Static RAMs have a cycle time equal to twice the processor cycle time. Depending

on the grade of UltraSPARC-IIi processor ordered, the SRAM access time will either be 4.5 nanoseconds, for

the 440 MHz processor, or 5.5 nanoseconds for the 360 MHz processor. In the Register-Latched mode, two

processor clocks are consumed to send the address and two processor clocks are consumed to return the ECache data giving a 4-cycle pin-to-pin latency. As a result of the tight control over the SRAM turn on and

turn off times, no dead cycles are necessary when alternating between reads and writes.

Memory accesses to the E-Cache must be cacheable. Consequently, no E-Cache enable bit is present in the

LSU_Control_Register (Refer to Table 5-4, "LSU_Control_Register," on page 5-12). Instruction fetches are

directed to non-cacheable PCI or UPA64S space when any of the following conditions are true:

USPIIi-1v Hardware Manual

4-2

Themis Computer

• The I-MMU is disabled

• The UltraSPARC-IIi is in RED_state

• The access is mapped by the I-MMU as physically non-cacheable

Data accesses to non-cacheable PCI or UPA64S space occur when either:

• The D-MMU enable bit (DM) in the LSU_Control_Register is clear, or

• The access is mapped by the D-MMU as non-physical cacheable (unless ASI_PHYS_USE-EC is used).

Note —

When non-cacheable accesses are used, the associated addresses must be legal according to the

UltraSPARC-IIi physical address map (refer to the “USPIIi-1v Software Manual).

4.1.3 SME Advanced PCI Bridge (APB)

The SME Advanced PCI Bridge (SME: SME2411) interfaces directly with the UltraSPARC-IIi

microprocessor and concentrates two (2), +5V, 32-bit, 33MHz PCI buses into one +3.3V, 32-bit, 66 MHz PCI

bus that interface directly with the UltraSPARC-IIi. The 66 MHz PCI-to-CPU can achieve a peak bandwidth

of 2 GBits/sec. Within the USPIIi-1v, the two (2), 33 MHz PCI busses are referred to as PCIA and PCIB.

4.1.4 SME Reset, Interrupt, and Clock (RIC)

The SME Reset, Interrupt and Clock (SME: STP2210QFP) ASIC provides a variety of functions on the

USPIIi-1v. The RIC manages system resets, system interrupts, system scans, and system clock control

functions. These functions are divided into independent functional blocks on the RIC.

The interrupt controller on the RIC accepts all interrupts from the USPIIi-1v subsystems (up to 41 interrupts)

and delivers encoded interrupts on the six (6) interrupt lines routed to the UltraSPARC-IIi microprocessor.

Interrupts are accepted by the RIC in a round-robin priority scheme. The interrupts received by the RIC are

not passed to the UltraSPARC-IIi in the order they are received. Instead, a priority level is assigned. Eight (8)

interrupt levels are implemented in hardware. For more information concerning the SME RIC ASIC, refer to

Chapter 7, "Resets."

4.1.5 Tundra Universe IIB

The Tundra Universe IIB (Tundra: CA91C142) ASIC interfaces the local 32-bit PCI bus to the VMEbus. The

Universe IIB includes a 33 MHz, 32-bit PCI bus interface, a fully compliant, high performance, 64-bit

VMEbus interface as well as a broad range of VMEbus address and data transfer modes of:

• A32/A24/A16 master and slave transfer, except for A64 and A40

• D64/D32/D16/D08 master and slave transfer, except for MD32

• MBLT, BLT, ADOH, RMW, LOCK, and location monitors

The Universe IIB also includes support for full VMEbus System Controller, nine user programmable slave

images, and seven interrupt lines. For more information on the Universe IIB, refer to Chapter 5, "UniverseIIB Description." and the Tundra Universe II User Manual, published by Tundra (Tundra Document Number

8091142.MD300.01).

Themis Computer 4-3

4. Hardware Overview

4.1.6 SME PCI I/O Controller

The SME PCI I/O Controller (SME: STP2003QFP) is a +5 Volt ASIC that provides a Master / Slave interface

bus compliant with PCI Local Bus Specification, Revision 2.1. The PCI I/O is connected to the SME APB via

the local PCI bus. MII support for 10Base-T (802.3) and 100Base-T (802.30) Ethernet is provided by PCI I/O

as well as an IEEE 1149.1 JTAG compliant architecture, a 40 MHz SCSI clock oscillator, a 10MHz real-time

clock, and an expansion bus interface (EBus2).

Support for CS4231 Audio CODEC, the National PC87303 Super I/O, the Siemens SAB82532 Dual 16C550

Synchronous/Asynchronous Serial Port controllers, the NVRAM, Time-of-Day, Voltage Sensors, and a boot

PROM control port is provided via the EBus2. The boot PROM control port interface directly to the EPROM.

4.1.7 Symbios SCSI Controller

The Symbios SCSI Controller (SYM53C876) provides two (2) UltraWide SCSI interfaces (40 MB/sec). In

order to maximize speed, it is attached directly to the SME APB through local 33 MHz PCI Bus A. A

maximum burst rate of up to 132 MB/sec is supported.

4.1.8 FPGA

The FPGA device on the USPIIi-1v is the Altera EPF8820. It resides on the EBus2 of the baseboard PCI I/O

ASICs. Physically, the FPGA is located on the baseboard. The FPGA implements a voltage monitor, boot

address decoder, a three-level watchdog timer, and the SYSTEM_OK_LED register. At boot-up the FPGA

self loads from a serial EPROM (Altera EPC1213PC8) to program itself for these features. For more

information on the FPGA, refer to Chapter 6, "FPGA, Watchdog, Voltage and Temperature Sensors."

4.1.9 National Super I/O

The National Super I/O (PC87307-ICE) is an industry standard, single-chip solution that provides support for

a Floppy Disk Controller, PS/2 Keyboard and Mouse, real-time clock, two (2) fast full function synchronous/

asynchronous serial ports (Serial Ports C and D), and an IEEE 1284 bi-directional parallel port. Each

component is individually configured to maximize the performance of the USPIIi-1v.

4.1.10 Seimens SAB 82532