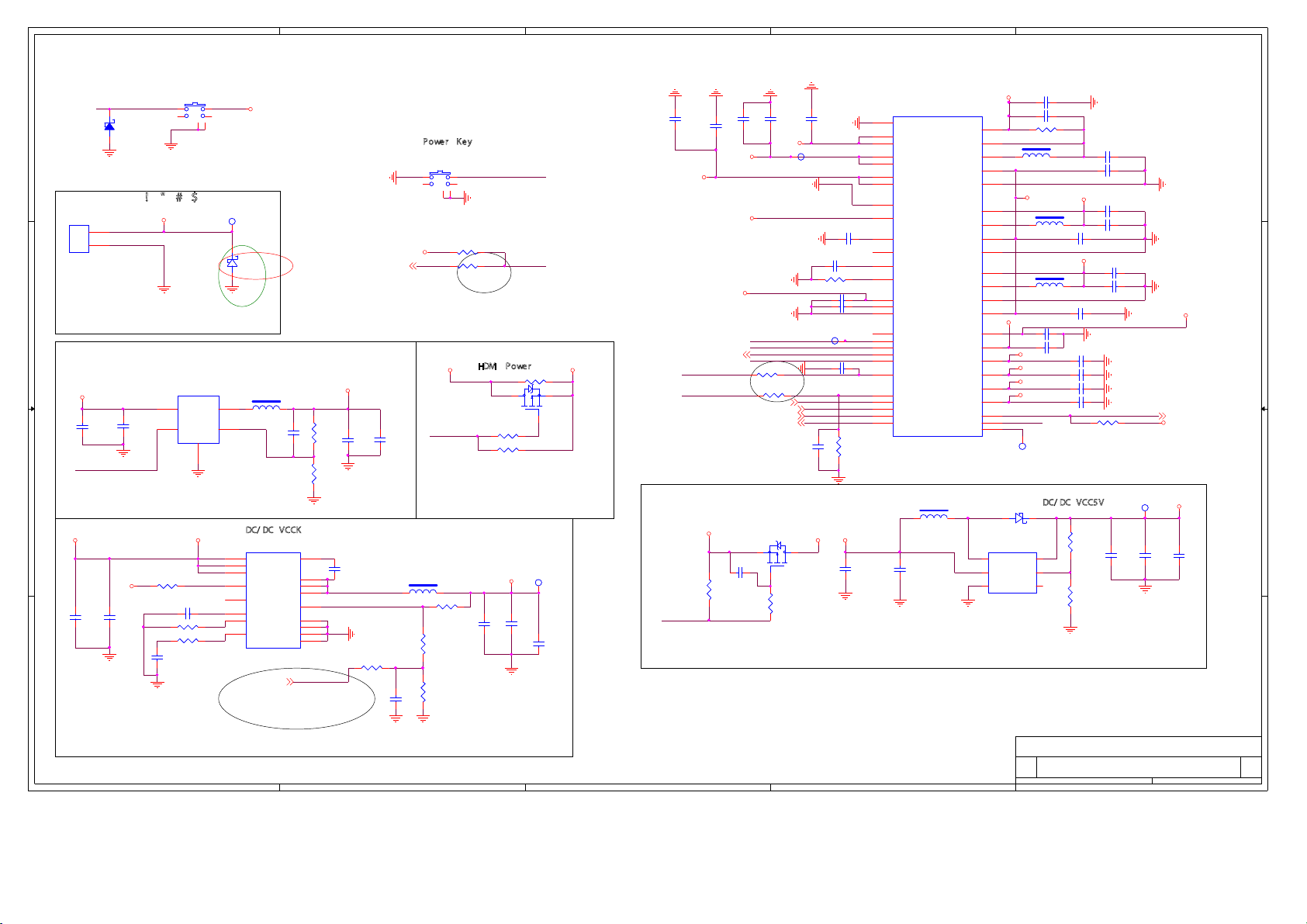

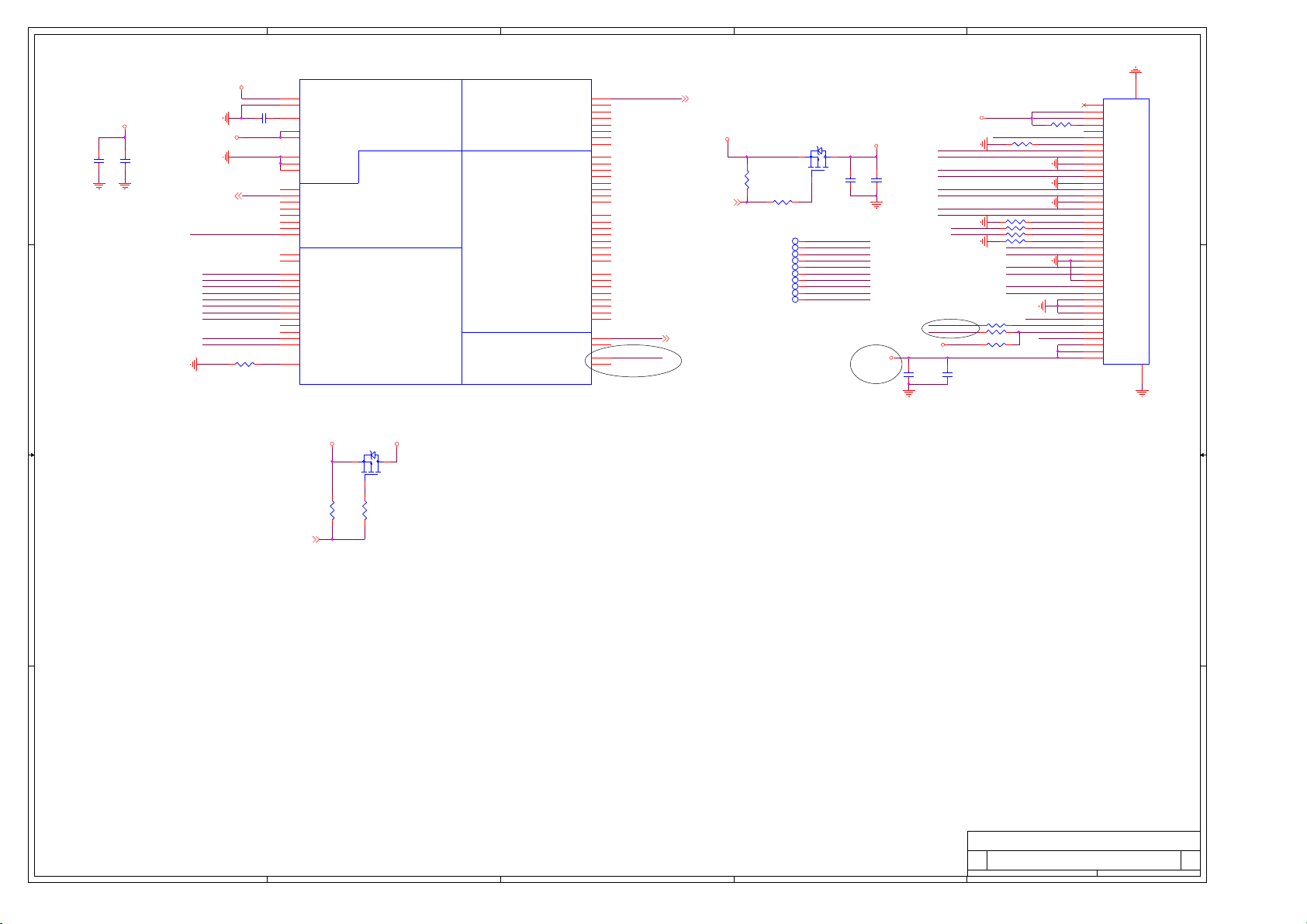

Page 1

5

1 cel l l i t hi um bat t er y

<MOS> <Boost>

VCCx2

Keep power on in off state

keep power on in sleep# state

Only power on in Active state

D D

For option

VCCx

<MOS> <Boost>

VCCx3

4

Power T r ee

<Boost>

VCC5V

VCC_AMP

LCD_AVDD

LED backlight

<MOS>

<MOS>

HDMI_PW

USB_OTG_PWR

3

2

1

<DC/DC3>

DC_IN

USB PWR

VBAT

C C

PMU

PWM

Charger

<DC/DC2>

<BUCK>

<BUCK>

<LDO1>

<LDO2>

<LDO2>

<LDO4>

VDD_AO

DDR3_1.5V

RTC_VDD

VDDIO_AO

AVDD2.5V

AVDD3.3/3.0V

VCCK(1.2V)

VDDIO

3.15V

(PLL/VDAC/USB/ ADC/AudioCodac)

HDMI_3.3V

Core Voltage

<LDO>

VCC1.8V(Camera)

VDDIO_CPU

VDDIO_CM

G/C/M Sensor

HDMI_PLL_AVDD

<MOS>

<MOS>

CARD_VCC

LCD_3.0V

(Control the card power in romboot)

Touch (From VDDIO or AVDD3.3)

B B

A A

T itle

T itle

T itle

A ML 8726 -MX_R E F -A

A ML 8726 -MX_R E F -A

TM-7043

5

4

3

2

A ML 8726 -MX_R E F -A

S ize Doc umen t Nu mber R ev

S ize Doc umen t Nu mber R ev

S ize Doc umen t Nu mber R ev

A3

A3

A3

Da te: S hee t

Da te: S hee t

Da te: S hee t

B lock

B lock

B lock

of

of

of

1 13T hurs da y, J ul y 12 , 2012

1 13T hurs da y, J ul y 12 , 2012

1 13T hurs da y, J ul y 12 , 2012

1

V 1.0

V 1.0

V 1.0

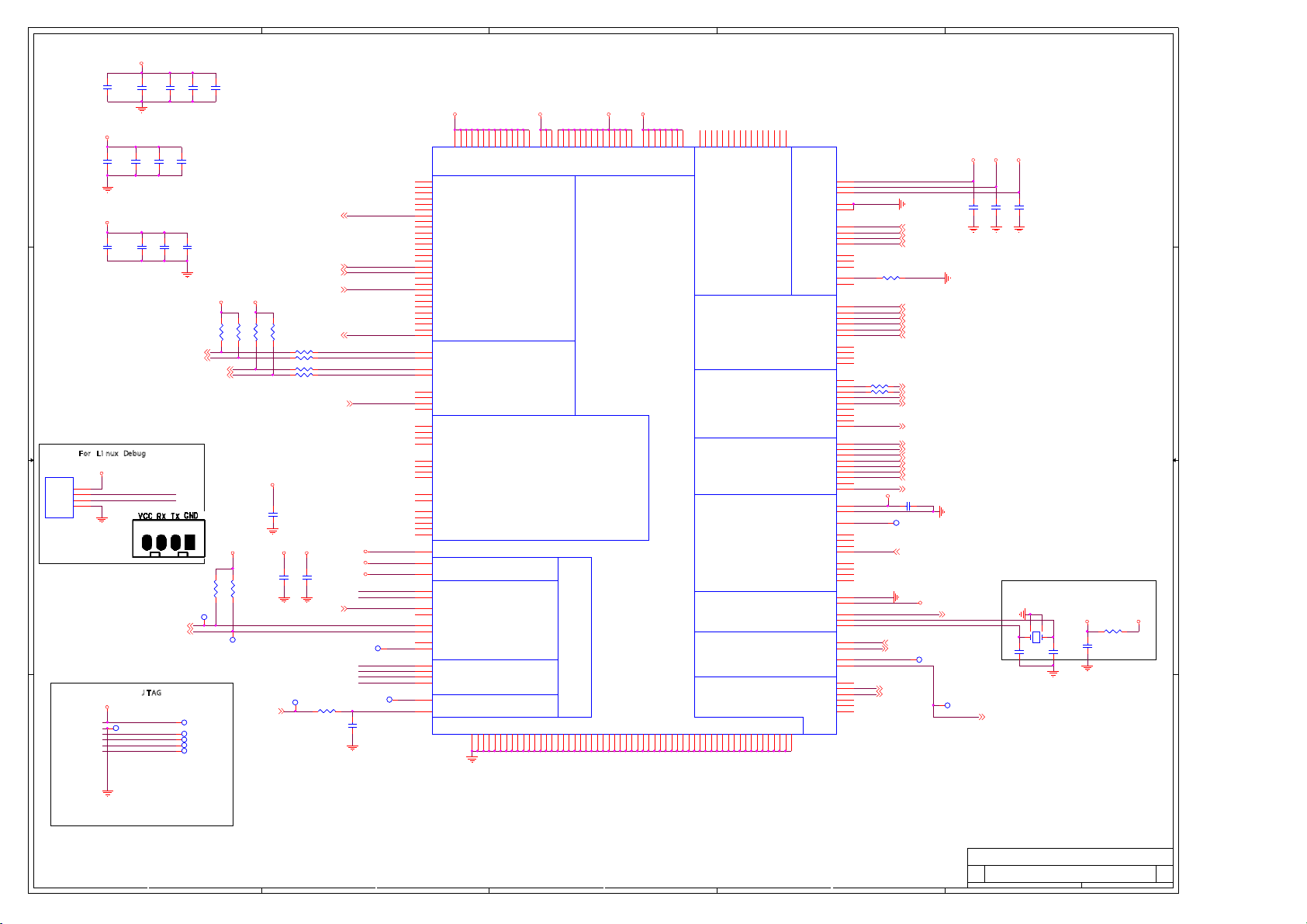

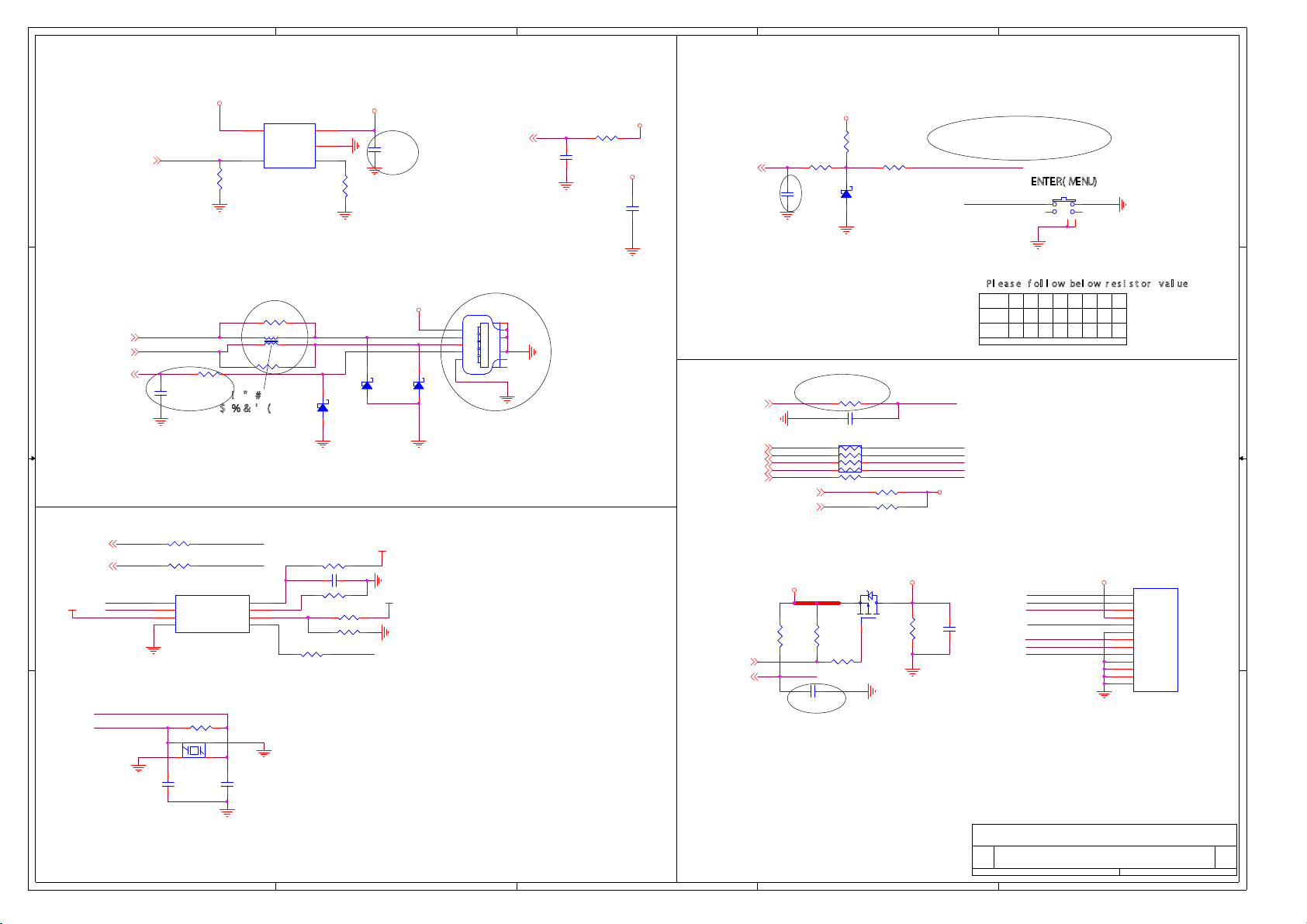

Page 2

5

4

3

2

1

GND

PMU _IRQ

G

G

1

C6

C6

10uF _6.3V

10uF _6.3V

C0 805

C0 805

VBAT

GND

GND

GND

Q1

Q1

DS

DS

S OT-23

S OT-23

S i2305

S i2305

R23

R23

470K

470K

R0402

R0402

GND

C8

C8

10uF _6.3V

10uF _6.3V

C0 805

C0 805

TP1

TP1

TEST

TEST

GND

GND

C7 1uF

C7 1uF

C0 402

C0 402

R16 200 K_1%

R16 200 K_1%

R0402

R0402

C1 2 0.1 uF

C1 2 0.1 uF

C1 3 1uF

C1 3 1uF

TP3

TP3

TES T3

TES T3

C1 6 1nF

C1 6 1nF

C9

C9

1nF

1nF

C0 402

C0 402

VCC X2

3

GND

C5 0.1uF

C5 0.1uF

C0 402

C0 402

C0 402

C0 402

C0 402

C0 402

N_OEPMU _R ST N_OE

GND

VCC X2

GND

C0 402

C0 402

VINT

6,7

R194

R194

10K

10K

R0402

R0402

C5 5

C5 5

22uF _6.3V

22uF _6.3V

C0 805

C0 805

3

3

10uF _10V

10uF _10V

USB _ P WR

VCC X 2_EN

GNDGND

C2 6

C2 6

C1 9

C1 9

0.1uF

0.1uF

C0 402

C0 402

C0 805

C0 805

VCC X

USB _ P WR

VCC X

VCC X 3_E N# 6

PW R _KEY

R195 1KR0402R 195 1KR0402

3

VCC X

C5 7

C5 7

10nF

10nF

R21

R21

C0 402

C0 402

47K

47K

R0402

R0402

C1 28

C1 28

1uF

1uF

C0 402

C0 402

VCC X 2_EN

HDMI3V _EN

VCC X 3_E N#

VDD IO_E N

R10 4.7KR 0402R 10 4.7KR0 402

!"#

USB _ P WR _C TL

I2C_ S CK _P MU

I2C_ S DA_ PMU

2

RESET

!

S T1112A

S T1112A

DC/DC VDDIO

U2

U2

S Y8008B

S Y8008B

4

VIN

1

EN

2

GND

VCC X

VCC K _EN

C4 9 10nF

C4 9 10nF

C0 402

C0 402

R49 182K

R49 182K

R0402

R0402

R50 20K

R50 20K

R0402

R0402

C5 1

C5 1

470pF

470pF

C0 402

C0 402

12

34

56

TES T2

TES T2

LX

EB

GND

S OT23_5 H14A

S OT23_5 H14A

S W2

S W2

Button_PKEY

Button_PKEY

TP 61

TP 61

GND

3

5

VCC X

D3

D3

1N5819

1N5819

S OD123 H14A

S OD123 H14A

L20 4 .7uH_1. 5A

L20 4 .7uH_1. 5A

L4D 18H2A

L4D 18H2A

C3 8

C3 8

R234

0.6V

47pF

47pF

C0 402

C0 402

GND

R234

200K _1%

200K _1%

R0402

R0402

R236

R236

47K _1%

47K _1%

R0402

R0402

DC/ DC V CCK

U4

U4

1

VINA

2

VIN

16

VIN

15

EN

14

PG

9

SS

8

RT

7

CO MP

G5193 R 41

G5193 R 41

TQF N3X 3_16

TQF N3X 3_16

VG HL_ CS 1

max 150uA, 15 step x 10uA

1.0-1.3V

package to GND

AG ND

13

BS

12

LX

11

LX

10

LX

6

FB

FB = 0.8 27V

17

EP

5

4

GND

3

GND

3

VDD IO

GND

C4 7

C4 7

0.1uF

0.1uF

C0 402

C0 402

VCC K _SW

VCC KF

R97 1K

R97 1K

6

GND

PW R _KE Y _DET

3.15V

C2 4

C2 4

10uF _6.3V

10uF _6.3V

C0 805

C0 805

0.6V

GND

R0402

R0402

Po wer K ey

S W1

S W1

Button_PKEY

Button_PKEY

R22 4.7K

VDD _R TC

C2 5

C2 5

0.1uF

0.1uF

C0 402

C0 402

GND

R22 4.7K

R45 100K

R45 100K

HDMI3V _EN

For HDMI Certica tion, we lding Q6/ R9/R20, N C

R11;

Without HDMI Cert ication , welding R11 only .

L5

L5

2.2uH_2A

2.2uH_2A

L6X6

L6X6

R46 60.4 K_1%

R46 60.4 K_1%

R0402

R0402

R47

R47

100K _1%

100K _1%

R0402

R0402

R52

R52

3.16 K_1%

3.16 K_1%

C5 0

C5 0

R0402

R0402

1nF

1nF

C0 402

C0 402

GND

4

12

34

S T1112A

S T1112A

GND

56

R0402

R0402

R0402

R0402

!"#

HDMI Power

R9

R20

1.3V

C4 5

C4 5

0.1uF

0.1uF

C0 402

C0 402

Close to DC- DC

S OT-23

S OT-23

S i2305

S i2305

R0402R9

R0402

R0402R20

R0402

3

VCC K

GND

PW R _KEY

PW R _KEY

R11

Q6

Q6

470K

470K

47K

47K

TES T2

TES T2

C4 6

C4 6

22uF _6.3V

22uF _6.3V

C0 805

C0 805

R0402R11

R0402

DS

DS

TP 53

TP 53

G

G

1

NC /0R

NC /0R

2

C5 2

C5 2

22uF _6.3V

22uF _6.3V

C0 805

C0 805

Applicat ion of VC CX3_EN#:

Add a 0R resistor to VCCX 3_EN# and connect to

pin3 of Q22; R1 73/C154/ R174/Q22 change to NC.

HDMI_3 .3VAV DD3 .3V

3

PMU _R ST

D21

D21

NC /ES D9 B5V

D D

NC /ES D9 B5V

D0603

D0603

! " # $

VDD IO

VBAT0

GND

C4 4

C4 4

0.1uF

0.1uF

C0 402

C0 402

C2 3

C2 3

0.1uF

0.1uF

C0 402

C0 402

R53 10K

R53 10K

VBAT

GND

R0402

R0402

GND

5

NC

1

+

2

-

CN 20NCCN 20

VBAT0-

C C

VCC X

C4 2

C4 2

10uF _6.3V

10uF _6.3V

C0 805

C0 805

VDD IO_E N

B B

VCC X

C4 3

C4 3

10uF _6.3V

10uF _6.3V

C0 805

C0 805

GND

A A

PMU

U1

U1

AXP 202 -02

AXP 202 -02

37

TS

38

BAT

39

BAT

34

IPS OUT

35

IPS OUT

32

AC IN

33

AC IN

49

EP

31

VB US

30

BA C KUP

36

CH GL ED

26

VINT

23

BIAS

21

APS

24

VR EF

22

AG ND

19

GP IO0/LD Oio0

18

GP IO1

5

GP IO2(O D)

3

GP IO3(O D)

20

EX TE N

47

PW R ON

4

N_OE

6

N_VB U SEN

48

IRQ

2

S CK

1

S DA

QF N-48P

QF N-48P

L6 4.7uH_1 .5A

L6 4.7uH_1 .5A

L4D 18H2A

L4D 18H2A

C5 6

C5 6

0.1uF

0.1uF

C0 402

C0 402

GND GND

2

BA TSE NSE

CH SE N SE

PG ND1

DCDC2

PG ND2

DCDC3

PG ND3

LD O3IN

LD O24IN

LD O1

LD O2

LD O3

LD O4

PW R OK

PW R EN

DC 3SET

LX1

VIN1

LX2

VIN2

LX3

VIN3

4

3

VBAT

C2 8 4.7 uF_6 .3V

C2 8 4.7 uF_6 .3V

C0 805

C0 805

C3 3 1uF _6.3V

C3 3 1uF _6.3V

C0 402

42

43

45

44

46

10

8

7

9

17

15

16

14

VCC X

40

13

28

12

41

11

25

27

29

D2 1N5819

D2 1N5819

U5

U5

LX

EN1FB

GND

RT 9266

RT 9266

S OT23 -6

S OT23 -6

C0 402

R19 0.03R _1%

R19 0.03R _1%

R1206

R1206

L18 4.7uH_1 .5A

L18 4.7uH_1 .5A

L4D 18H2A

L4D 18H2A

VCC X

VCC X

4.7uH_1 .5A

4.7uH_1 .5A

L17

L17

L4D 18H2A

L4D 18H2A

4.7uH_1 .5A

4.7uH_1 .5A

L19

L19

L4D 18H2A

L4D 18H2A

C3 6 4.7 uF_6 .3V

C3 6 4.7 uF_6 .3V

C0 805

C0 805

C3 7 4.7 uF_6 .3V

C3 7 4.7 uF_6 .3V

C0 805

C0 805

VDD _R TC

VDD IO_A O

AV DD2 .5V

AV DD3 .3V

VINT

TP4

TP4

TES T3

TES T3

DC/ DC V CC5V

S OD123 H14A

S OD123 H14A

5

VDD

6

2

EXT

FB = 1.2 5V

Title

Title

Title

AML 8726 -MX_R E F-A

AML 8726 -MX_R E F-A

AML 8726 -MX_R E F-A

S ize Document Number Rev

S ize Document Number Rev

S ize Document Number Rev

Cus tom

Cus tom

Cus tom

Date: S heet

Date: S heet

Date: S heet

GND

C2 9 4.7uF _6. 3V

C2 9 4.7uF _6. 3V

C3 0 10uF _6.3V

C3 0 10uF _6.3V

DDR 3_1 .5V

C1 5 22uF _6.3V

C1 5 22uF _6.3V

C1 7 0.1uF

C1 7 0.1uF

C1 8 10uF _6. 3V

C1 8 10uF _6. 3V

C0 805

C0 805

VDD _AO

C2 0 22uF _6. 3V

C2 0 22uF _6. 3V

C2 2 0.1 uF

C2 2 0.1 uF

C2 7 10uF _6. 3V

C2 7 10uF _6. 3V

C0 805

C0 805

GND

C4 8 1uF _6.3V

C4 8 1uF _6.3V

C0 402

C0 402

C3 13 4.7uF_6 .3V

C3 13 4.7uF_6 .3V

C0 805

C0 805

C7 5 4.7 uF_6 .3V

C7 5 4.7 uF_6 .3V

C0 805

C0 805

C3 5 4.7 uF_6 .3V

C3 5 4.7 uF_6 .3V

C0 805

C0 805

R25 4.7KR 0402R25 4.7KR 0402

R55

R55

82.5 K_1%

82.5 K_1%

R0402

R0402

R58

R58

27K _1%

27K _1%

R0402

R0402

GND

P o wer

P o wer

P o wer

C0 805

C0 805

C0 805

C0 805

C0 805

C0 805

C0 402

C0 402

C0 805

C0 805

C0 402

C0 402

GND

GND

GND

GND

C3 2

C3 2

22uF _6.3V

22uF _6.3V

C0 805

C0 805

TES T2

TES T2

GND

GND

1.1V

GND

VDD IO

GND

CP U_ RS T

VDD IO_A O

VCC 5V

TP 54

TP 54

C3 4

C3 4

22uF _6.3V

22uF _6.3V

C0 805

C0 805

GND

1

C5 4

C5 4

0.1uF

0.1uF

C0 402

C0 402

2 13Thursday, July 12, 2012

2 13Thursday, July 12, 2012

2 13Thursday, July 12, 2012

3

V1 .0

V1 .0

V1 .0

of

of

of

Page 3

5

VCCK

C60

11,13

11,13

C67

C67

0.1uF

0.1uF

C0402

C0402

C70

C70

0.1uF

0.1uF

C0402

C0402

I2C_S DA _A

I2C_S C K_A

C59

C59

0.1uF

0.1uF

C0402

C0402

9,12

9,12

GND

C246

C246

0.1uF

0.1uF

C0402

C0402

C71

C71

0.1uF

0.1uF

C0402

C0402

I2C_S DA _B

I2C_S C K_B

C60

0.1uF

0.1uF

C0402

C0402

VDDIO

C61

C61

0.1uF

0.1uF

C0402

C0402

R64

R64

2.2K

2.2K

R0402

R0402

R65

R65

2.2K

2.2K

R0402

R0402

VDDIO

R110

R110

2.2K

2.2K

R0402

R0402

TP_ S HUTDN#13

GSE N_INT

TOUCH _INT

HP_ DET

R111

R111

2.2K

2.2K

6

LCD_ PW R _E N#

R0402

R0402

R0402

R0402

R67 22R

R67 22R

R0402

R0402

R68 22R

R68 22R

R112

R0402R112

R0402

22R

22R

R124

R0402R124

R0402

22R

22R

UAR T_A _CTS _N 8

C58

C58

C31

C31

1uF_6. 3V

1uF_6. 3V

10uF_6 .3V

10uF_6 .3V

C0402

C0402

C0805

C0805

GND

D D

C C

VDD_ AO

VDDIO

GND

C65

C65

10uF_6 .3V

10uF_6 .3V

C0805

C0805

C68

C68

4.7uF _6. 3V

4.7uF _6. 3V

C0805

C0805

C66

C66

0.1uF

0.1uF

C0402

C0402

C69

C69

0.1uF

0.1uF

C0402

C0402

For L i nux Debug

VDDIO _AO

J3

J3

VCC

GND

4x2mm

NC/C ON4P

NC/C ON4P

SM TXH-V-4

SM TXH-V-4

mark signal name on PCB

B B

A A

PCB# $%& '(

4

3

RX

2

TX

1

GND

VDDIO _AO

JTAG a nd con sol pl ace to the

easy w elding place where can b e

weld w hen op en the shell .

J T AG

TP51 TES T2TP51 TES T2

mark signal name on PCB

GND

Linux_RX

Linux_TX

I2C_S C K_ PMU2

I2C_S DA _P MU2

PCB

5

#$% &'(

TMS

TCK

TDO

TDI

TP7

TP7

TP50 TES T2TP50 TES T2

TP46 TES T2TP46 TES T2

TP47 TES T2TP47 TES T2

TP48 TES T2TP48 TES T2

TP49 TES T2TP49 TES T2

TES T3

TES T3

VDDIO _AO

R70

R70

4.7K

4.7K

R0402

R0402

TP8

TP8

TES T3

TES T3

R71

R71

4.7K

4.7K

R0402

R0402

AV DD2.5V

C186

C186

0.1uF

0.1uF

C0402

C0402

GND

VDD_ AO

VDDIO _AO

C80

C80

C79

C79

1uF

1uF

C0402

C0402

1uF

1uF

C0402

C0402

GND

GND

PMU _IRQ

TP58

TP58

TES T3

TES T3

R77 1K

CP U_R ST 2

R77 1K

R0402

R0402

AV DD2.5V

VDD_ AO

VDDIO _AO

4

FOR TS_A INPUT

3G_WAK EIN

3G_EN

FOR TS_A INPUT

FOR TS_A INPUT

FOR TS_A INPUT

FOR TS_A INPUT

Reserved for FE C_EN

Reserved for FE C_RST

Reserved for EX TIO_INT

For AV_DET too

SPI IO

Reserved for SA TA_RST

Reserved for SA TA_EN

SPI IO

SPI IO

SPI IO

TP13 TES T3TP 13 TES T3

TP62TES T2T P62TES T2

RESE T_CP U

C179

C179

1nF

1nF

C0402

C0402

GND

4

3

VDD_ AO VDDIOVCCK

U37A

U37A

AML8726 -MX

JOG_UP

JOG_DOWN

JOG_L

JOG_R

DC_DET

CHG_STAT

BAT_SEL

UIM_DET

Light_INT

VCCX2_EN#

ISO7816

Linux_TX

Linux_RX

AML8726 -MX

AML8726 -MX

AML8726 -MX

9

13

12

2

TCK

TMS

TDI

TDO

G7

U22

H22

VDD_ EE

C24

GP IOA_0 ( LCDi n_R 0 // F E C _D0_ A)

B24

GP IOA_1 ( LCDi n_R 1 // F E C _D1_ A)

C23

GP IOA_2 ( LCDi n_R 2 // F E C _D2_ A)

B23

GP IOA_3 ( LCDi n_R 3 // F E C _D3_ A // F EC _D 0_C)

C22

GP IOA_4 ( LCDi n_R 4 // F E C _D4_ A // F EC _C L K_C)

B22

GP IOA_5 ( LCDi n_R 5 // F E C _D5_ A // F EC _S O P_C)

A22

GP IOA_6 ( LCDi n_R 6 // F E C _D6_ A // F EC _D _VA LID_C)

C21

GP IOA_7 ( LCDi n_R 7 // F E C _D7_ A // F EC _F AIL_ C)

D23

GP IOA_8 ( LCDi n_G 0 // F E C_ CL K_ A)

D22

GP IOA_9 ( LCDi n_G 1 // F E C_ SO P_ A)

E21

GP IOA_10 ( LCDi n_G 2 // FE C _D_ VAL ID_A)

G21

GP IOA_11 ( LCDi n_G 3 // FE C _F AIL_ A)

E20

GP IOA_12 ( LCDi n_G 4 // ENC _0)

F21

GP IOA_13 ( LCDi n_G 5 // ENC _1)

D20

GP IOA_14 ( LCDi n_G 6 // ENC _2)

E19

GP IOA_15 ( LCDi n_G 7 // ENC _3)

A21

GP IOA_16 ( LCDi n_B 0 // E NC _4)

B21

GP IOA_17 ( LCDi n_B 1 // E NC _5)

C19

GP IOA_18 ( LCDi n_B 2 // E NC _6)

B20

GP IOA_19 ( LCDi n_B 3 // E NC _7)

C20

GP IOA_20 ( LCDi n_B 4 // E NC _8)

B19

GP IOA_21 ( LCDi n_B 5 // E NC _9)

C18

GP IOA_22 ( LCDi n_B 6 // E NC _10)

B18

GP IOA_23 ( LCDi n_B 7 // E NC _11)

A18

GP IOA_24 ( LCDi n_C L K // E NC_ 12)

C17

GP IOA_25 ( LCDi n_HS // E NC _13)

A17

GP IOA_26 ( LCDi n_VS // ENC _14)

B17

GP IOA_27 ( LCDi n_D E // ENC _15)

J4

GP IOX_25 ( I2C_ S DA_A)

J3

GP IOX_26 ( I2C_ S CK _A)

J2

GP IOX_27 ( I2C_ S DA_B)

K5

GP IOX_28 ( I2C_ S CK _B)

G6

GP IOX_13 ( UAR T_ TX_ A)

F3

GP IOX_14 ( UAR T_ RX_ A)

F2

GP IOX_15 ( UAR T_ CT S _A)

F1

GP IOX_16 ( UAR T_ RT S _A)

G3

GP IOX_17 ( UAR T_ TX_ B // IS O781 6_ DE T // PC M_C LK // I2S _AM_C LK)

G1

GP IOX_18 ( UAR T_ RX_ B // IS O7 816_ R ESE T // PC M_F S // I2S _AO_ CL K)

G2

GP IOX_19 ( UAR T_ CT S _B // ISO 7816_ C LK // PC M_O UT // I2S_L R _C LK)

H5

GP IOX_20 ( UAR T_ RT S _B // ISO 7816_ D ATA // PC M_IN // I2S _IN_C H01 // I2S _OUT _C H01)

H4

GP IOX_21 ( UAR T_ TX_ C // IS O 7816_ DE T)

H3

GP IOX_22 ( UAR T_ RX_ C / / ISO 7816_ R ESE T)

H2

GP IOX_23 ( UAR T_ CT S _C // UAR T_ TX_ B // IS O7 816_ C LK)

J5

GP IOX_24 ( UAR T_ RT S _C // UAR T _R X_B // ISO 7816_ DA TA)

K3

GP IOX_29 ( I2C_ S CK _C // SP I_SS 2)

K2

GP IOX_30 ( I2C_ S DA_C // SP I_RD Yn)

K1

GP IOX_31 ( SP I_SS 0)

L5

GP IOX_32 ( SP I_SS 1)

L4

GP IOX_33 ( SP I_S CL K)

M4

GP IOX_34 ( SP I_MOS I)

M5

GP IOX_35 ( SP I_MIS O)

N22

EF USE _ VDD 25

AC25

VDD_ AO

AE27

VDD_ IO_AO

AF2 5

GP IOAO _0 (UAR T _T X_AO)

AF2 7

GP IOAO _1 (UAR T _R X_AO)

AD24

GP IOAO _2 (UAR T _C TS _AO )

AE26

GP IOAO _3 (UAR T _R TS _ AO)

AD25

GP IOAO _4 (I2C _S CK _AO)

AD26

GP IOAO _5 (I2C _S DA_ AO)

AC26

GP IOAO _6 (WD _G PIO // CL K_ OUT 2)

AB25

GP IOAO _7 (R E MOT E_ INPUT)

AB26

GP IOAO _8 (JT AG _T CK)

AB27

GP IOAO _9 (JT AG _T MS)

AA25

GP IOAO _10 (J TAG _T DI)

AA26

GP IOAO _11 (J TAG _T DO // C LK_ OUT 2)

Y22

TES T_ N (G PO)

AA27

RESE T _N

BGA SMT&Soldering NOTE

1)Scattered chips or vacuum-broken packed chips need

to bake more than 12 hours at 100 degrees,before on-SMT line

And must completed soldering within 48 hours if open vacuum-packed or nish baking

Otherwise, burst vapor will damage the chip during the welding process

2)Require both sides of heating equipment, in order to avoid PCB damage or PCB distortion

3) Should have skilled operators for manual soldering

It is recommended to welding in professional BGA soldering factory.

If cpu had bad welding or welding damage, It will be very dicult to debug PCBA

AB18

AA22

F11

D19

F20

T22

AA14

AB10

D11

VDD_ EE

VDD_ EE

VDD_ EE

VDD_ EE

VSSF6VSS

VSS

U17

GND

L6

F13

L15

F7

VDD_ EE

VDD_ EE

VDD_ EE

VDD_ EE

VDD_ EE

VDD_ EE

VDD_ EEU6VDD_ EE

VDD_ EE

VSS

VSS

VSS

P17

N17

U11

R17

M17

VDD_ CPUF9VDD_ CPU

VDD_ CPU

VDD_ CPU

TS IN

TS IN

GPIO

GPIO

I2C

I2C

UART

UART

AO GPIOJTAG

AO GPIOJTAG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T16

L16

T15

P16

U16

R16

N16

U15

M16

"

G14

L11

F17

F18

VDD_ CPU

VDD_ CPU

VDD_ CPU

VDD_ CPU

Always on

Always on

VSS

VSS

VSS

VSS

VSS

P15

R15

N15

M15

L17

U14

VCCK

T6

P21

P22

L13

M6

VDD_ CPU

VDD_ CPU

VDD_ CPUR6VDD_ CPU

VDD_ CPU

VDD_ CPUJ6VDD_ CPU

VDD_ CPUN6VDD_ CPU

(L ib V er sion: 1227 )

(L ib V er sion: 1227 )

ISO7816

ISO7816

UART

UART

SPI I/O

SPI I/O

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T14

T13

L14

P14

R14

N14

U13

R13

M14

3

F8

F12

K22

V22

AA7

P7

F16

VDD_ IO4H6VDD_ IO3

VDD_ IO8

VDD_ IO7

VDD_ IO6

VDD_ IO5

VDD_ IO2

VDD_ IO1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T12

T17

P13

P12

U12

N13

R12

N12

M13

M12

For RM/RGMII

P6

P5

L3

L1

GP IOY _14 (E T H_MDC)

GP IOY _13 (E T H_MDIO)

GP IOY _1 (E TH _TX _C LK)

GP IOY _0 (E TH _PH Y_ RE F_ CL K)

RM/RGMII

RM/RGMII

SDIO

SDIO

PCM

PCM

D AUDIO

D AUDIO

GP IOE _3 (I2S _O UT_ AO_ CL K // A UDIN_AO _C LK)

GP IOE _1 (I2S _O UT_ LR _C L K // AUDIN_L R _C LK)

GP IOE _5 (I2S _O UT_ CH23 // I2S _O UT_L R _C LK)

GP IOE _6 (I2S _O UT_ CH45 // I2S _O UT_ AM_C LK)

GP IOE _7 (I2S _O UT_ CH67 // I2S _O UT_ AO_ CL K)

CARD

CARD

ADC

ADC

RTC

RTC

Always on

Always on

OSC

OSC

GPIO

GPIO

VSS

VSS

VSS

VSS

VSS

T11

L12

P11

R11

M2

L2

M3

N2

N3

P2

P1

N5

P3

GP IOY _4 (E TH _TX D2)

GP IOY _6 (E TH _TX D0)

GP IOY _5 (E TH _TX D1)

GP IOY _3 (E TH _TX D3)

GP IOY _9 (E TH _R XD3)

GP IOY _12 (E T H_R XD 0)R1GP IOY _11 (E T H_R XD 1)R3GP IOY _10 (E T H_R XD 2)

GP IOY _8 (E TH _R X_D V)

GP IOY _7 (E TH _R X_C L K)

GP IOX_9 (S DXC _C MD_A)

GP IOX_8 (S DXC _C LK _A)

GP IOX_0 (S DXC _D 0_A)

GP IOX_1 (S DXC _D 1_A)

GP IOX_2 (S DXC _D 2_A)

GP IOX_3 (S DXC _D 3_A)

GP IOX_4 (S DXC _D 4_A // P C M_OUT)

GP IOX_5 (S DXC _D 5_A // P C M_IN)

GP IOX_6 (S DXC _D 6_A // P C M_F S)

GP IOX_7 (S DXC _D 7_A // P C M_CL K)

GP IOE _8 (SP D IF_ OUT)

GP IOE _2 (I2S _O UT_ AM_C LK)

GP IOE _4 (I2S _O UT_ CH01 )

GP IOE _0 (I2S _AUD IN_CH01 )

CARD _5 ( SD XC_ CMD_ B // S D_ CMD_ B)

CARD _4 ( SD XC_ CL K_ B // S D_C L K_B)

CARD _0 ( SD XC_ D0_B // S D_D 0_B)

CARD _1 ( SD XC_ D1_B // S D_D 1_B)

CARD _2 ( SD XC_ D2_B // S D_D 2_B)

CARD _3 ( SD XC_ D3_B // S D_D 3_B)

GP IOC _15 (C LK _O UT1)

GP IOX_12 ( CL K_ OUT 3)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSE5VSSP4VSS

F19

AF8

N11

AB7

M11

AB20

AD17

AD12

AG22

Reserved for RM II_RST

R5

USB

USB

GP IOY _15

USB _VDD 33

USB _VDD 25

USB _DV DD

USBA _VSSA

GP IOY _2 (E TH _TX _E N)

USBB _ VSSA

USBA _VB US

USBB _ VBUS

USBA _T XR TUNE

USBB _ TXR T UNE

AVDD 25_A DC

AVSS 25_ADC

ANALOG _ OUT

SAR ADC _ CH7 (iA)

SAR ADC _ CH6

SAR ADC _ CH5

SAR ADC _ CH4

SAR ADC _ CH3 (Y -)

SAR ADC _ CH2 (X-)

SAR ADC _ CH1 (Y +)

SAR ADC _ CH0 (X+)

RT C _AVSS

RT C _VBAT

RT C _G PO

RT C _XO UT

sys _osc out

GP IOE _11

GP IOX_10

GP IOX_11

GP IOC _14

VSS

VSS

P27

Y23

USBA _DP

USBA _DM

USBA _ID

USBB _ DP

USBB _ DM

CARD _6

CARD _7

CARD _8

RT C _XIN

sys _osc in

GP IOE _9

GP IOE _10

2

2

L24

M23

K24

L22

J22

L23

J27

J26

K23

H25

H26

G25

J25

G26

E4

E2

B2

B1

D4

C1

C2

D3

D2

E3

D7

B9

C9

A9

B8

C8

B7

C7

A10

U5

T2

R2

R4

T5

T3

U4

U3

U2

E23

F22

E22

B25

A25

C26

B26

A26

C27

B27

A27

AF2 6

AE25

AG25

AG26

AG27

AG3

AF3

AG6

G5

E7

E6

D5

F4

F5

AD5

R0402

R0402

R62 200R_1%

R62 200R_1%

R0402

R0402

R371 22R

R371 22R

R0402

R0402

R78 22R

R78 22R

Reserved for CA RD WP

AV DD2.5V

VBAT_C UR

VBAT_D ET

ADC_YADC_XADC_Y+

ADC_X+

CM_P W DN2 11

CM_P W DN1 11

GND

VB US1

DP1

DM1

ID1

WIF I_S D_C MD 8

WIF I_S D_C LK 8

WIF I_S D_D0 8

WIF I_S D_D1 8

WIF I_S D_D2 8

WIF I_S D_D3 8

I2S _MCLK 12

I2S _S CLK 12

I2S _LRC LK 12

I2S _DOUT 12

I2S _DIN 12

SD _CMD _B

SD _CL K_B

SD _D0_B

SD _D1_B

SD _D2_B

SD _D3_B

CARD _D ET 7

CARD _E N

C78 0.1uF

C78 0.1uF

C0402

C0402

TP14

TP14

TES T3

TES T3

ADC _KEY

GND

VCC _R TC

RTC _XIN

RTC _XOUT

OS CIN

OS CO UT 7

TP15

TP15

TES T3

TES T3

1

AV DD2.5V

7

7

7

7

GND

7

7

7

7

7

7

7

GND

7

PW R _KEY _DET 2

7

TP12

TP12

TES T3

TES T3

AV DD3.3V

VDD_ AO

C74

C74

C64

C64

C178

C178

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

C0402

C0402

GNDGND

GND

RTC layout notes:

close to CPU, keep XIN/XOUT short,

Do not break GND path

32.768 KHz _12. 5pF_10pp m_20K OHM

32.768 KHz _12. 5pF_10pp m_20K OHM

C81

C81

2

18pF_5% _NP O

18pF_5% _NP O

C0402

C0402

keep the line o f crystal short,

do not break GN D path

WIF I_32K

Title

Title

Title

AML 8726 -MX_R E F -A

AML 8726 -MX_R E F -A

AML 8726 -MX_R E F -A

Siz e Document Number Rev

Siz e Document Number Rev

Siz e Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

VCC _R TC

Y1

Y1

14

3

MC_146

MC_146

C82

C82

18pF_5% _NP O

18pF_5% _NP O

C0402

C0402

8

C PU

C PU

C PU

1

R33 100R

R33 100R

R0402

R0402

C83

C83

1uF_6. 3V

1uF_6. 3V

C0402

C0402

3 13Thursday , July 12, 2012

3 13Thursday , July 12, 2012

3 13Thursday , July 12, 2012

VDD_ RTC

of

of

of

V1.0

V1.0

V1.0

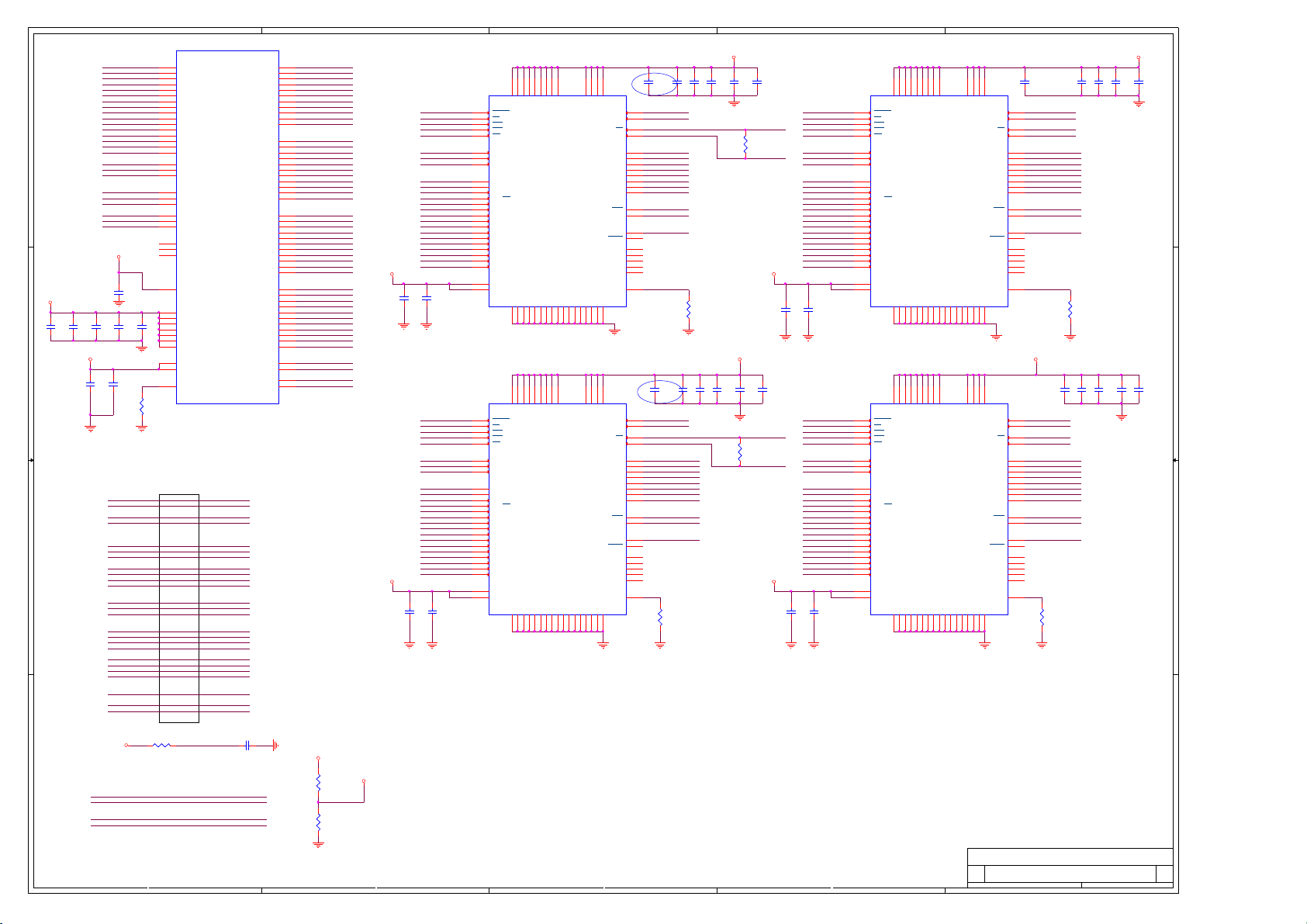

Page 4

5

U37B

U37B

AML8726 -MX

AML8726 -MX

(L ib V er sion: 1227 )

DDR3_ A0

DDR3_ A1

DDR3_ A2

DDR3_ A3

DDR3_ A4

DDR3_ A5

DDR3_ A6

DDR3_ A7

DDR3_ A8

DDR3_ A9

DDR3_ A10

DDR3_ A11

DDR3_ A12

D D

DDR3_1 .5V

C100

C100

10uF_6 .3V

10uF_6 .3V

C0805

C0805

C C

B B

A A

DDR3_ A13

DDR3_ A14

DDR3_ A15

DDR3_ BA0

DDR3_ BA1

DDR3_ BA2

DDR3_n RA S

DDR3_n CAS

DDR3_n WE

DDR3_n CS

DDR3_ CKE 0

DDR3_ ODT0

DDR3_1 .5V

C97

C97

0.1uF

0.1uF

C0402

C0402

GND

C104

C104

C101

C101

C122

C122

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

C0402

C0402

MDDR 3_V RE F0

C120

C120

C110

C110

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

GND

DDR3_n CS MDDR 3_nCS 0

DDR3_n RA S MDDR 3_nR AS

DDR3_ ODT0 MDDR 3_ ODT0

DDR3_n WE MDDR 3_nWE

DDR3_ BA2 MDDR 3_BA2

DDR3_ A7 MDDR 3_A7

DDR3_ A13 MDDR 3_A13

DDR3_ A0 MDDR 3_A0

DDR3_ BA0 MDDR 3_BA0

DDR3_ A14 MDDR 3_A14

DDR3_ A6 MDDR 3_A6

DDR3_ A1 MDDR 3_A1

DDR3_ CKE 0 MDDR 3_ CKE0

DDR3_1 .5V GND

C102

C102

0.1uF

0.1uF

C0402

C0402

GND

R94

R94

240R _1%

240R _1%

R0402

R0402

GND

R86 10K

R86 10K

5

R0402

R0402

AE17

AF1 3

AE13

AF1 7

AE14

AG18

AG14

AE19

AF1 4

AG15

AE18

AE16

AE15

AF1 8

AF1 5

AC17

AF1 6

AC16

AC13

AC14

AD15

AC15

AD18

AD14

AB15

AB13

AB14

AB16

AB17

AC18

AC19

AB12

AB11

AA13

AB19

AB21

AA21

AA9

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

RAS _N

CAS _N

WE _n

CS 0_N

CKE0

ODT0

CS 1_N

CKE1

ODT1

VDDQ _AO

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VR E F0

VR E F1

PZQ

AML8726 -MX

AML8726 -MX

MDDR 3_R ST

MDDR 3_nCA SDDR3_n CAS

MDDR 3_A2DDR3_ A2

MDDR 3_A9DDR3_ A9

MDDR 3_A5DDR3_ A5

MDDR 3_A3DDR3_ A3

MDDR 3_A8DDR3_ A8

MDDR 3_A11DDR3_ A11

MDDR 3_A4DDR3_ A4

MDDR 3_A12DDR3_ A12

MDDR 3_BA1DDR3_ BA1

MDDR 3_A15DDR3_ A15

MDDR 3_A10DDR3_ A10

C103 1uF _6.3V

C103 1uF _6.3V

MDDR 3_CL K p0DDR3_ CL Kp0

MDDR 3_CL K n0DDR 3_CL Kn0

MDDR 3_CL KP1DDR3_ CL Kp1

MDDR 3_CL K N1DDR3_C LK n1

(L ib V er sion: 1227 )

AF1 2

C0402

C0402

DQS0

DQS 0_n

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS1

DQS 1_n

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS2

DQS 2_N

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS3

DQS 3_N

CK _N

CK 1_N

AC8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DM0

DQ8

DQ9

DM1

DM2

DM3

CK1

DDR3_ D0

AC12

DDR3_ D1

AC7

DDR3_ D2

AC11

DDR3_ D3

AC6

DDR3_ D4

AD11

DDR3_ D5

AD6

DDR3_ D6

AC10

DDR3_ D7

AC9

DDR3_ DQM0

AD8

DDR3_ DQS p0

AD9

DDR3_ DQS n0

AG11

DDR3_ D8

AE7

DDR3_ D9

AG10

DDR3_ D10

AF7

DDR3_ D11

AE11

DDR3_ D12

AG7

DDR3_ D13

AE10

DDR3_ D14

AE8

DDR3_ D15

AF1 0

DDR3_ DQM1

AE9

DDR3_ DQS p1

AF9

DDR3_ DQS n1

AC21

DDR3_ D16

AA23

DDR3_ D17

AD21

DDR3_ D18

AB23

DDR3_ D19

AC20

DDR3_ D20

AB24

DDR3_ D21

AD20

DDR3_ D22

AC24

DDR3_ D23

AC23

DDR3_ DQM2

AC22

DDR3_ DQS p2

AD23

DDR3_ DQS n2

AE23

DDR3_ D24

AF2 0

DDR3_ D25

AF2 3

DDR3_ D26

AF1 9

DDR3_ D27

AF2 2

DDR3_ D28

AE20

DDR3_ D29

AG23

DDR3_ D30

AG19

DDR3_ D31

AE22

DDR3_ DQM3

AE21

DDR3_ DQS p3

AF2 1

DDR3_ DQS n3

AF1 1

DDR3_ CL Kp0

CK

AE12

DDR3_ CL Kn0

AE24

DDR3_ CL Kp1

AF2 4

DDR3_ CL Kn1

DDR3_1 .5V

R81

R81

1K_1%

1K_1%

R0402

R0402

R84

R84

1K_1%

1K_1%

R0402

R0402

GND

MDDR 3_V RE F0

4

MDDR 3_V RE F0

GND

MDDR 3_V RE F0

4

3

DDR3_1 .5V

C94

C94

C95

C95

C96

0.1uF

0.1uF

C0402

C0402

C107

C107

0.1uF

0.1uF

C0402

C0402

0.1uF

0.1uF

C0402

C0402

150R _1%

150R _1%

150R _1%

150R _1%

GND

MDDR 3_CL K n0

R80

R80

R0402

R0402

DDR3_1 .5V

C108

C108

0.1uF

0.1uF

C0402

C0402

R93

R93

R0402

R0402

GND

C96

C189

C189

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

MDDR 3_CL K p0 MDDR 3_BA1

MDDR 3_V RE F0

C109

C109

C201

C201

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

MDDR 3_CL K N1

MDDR 3_CL KP1

MDDR 3_V RE F0

GND GNDGNDGNDGND

C93

C93

C92

C92

0.1uF

0.1uF

10uF_6 .3V

10uF_6 .3V

C0402

C0402

C0805

E2

B9

G8

K9

A2

D7

K1

M1

G2

U41

U41

N2

MDDR 3_R ST

MDDR 3_nCS 0

MDDR 3_nR AS

MDDR 3_nCA S

MDDR 3_nWE

MDDR 3_BA2

MDDR 3_BA1

MDDR 3_BA0

MDDR 3_A15

MDDR 3_A14

MDDR 3_A13

MDDR 3_A12

MDDR 3_A11

MDDR 3_A10

MDDR 3_A9

MDDR 3_A8

MDDR 3_A7

MDDR 3_A6

MDDR 3_A5

MDDR 3_A4

MDDR 3_A3

MDDR 3_A2

MDDR 3_A1

MDDR 3_A0

C99

C99

C98

C98

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

GND

MDDR 3_R ST

MDDR 3_nCS 0

MDDR 3_nR AS

MDDR 3_nCA S

MDDR 3_nWE

MDDR 3_BA2

MDDR 3_BA1

MDDR 3_BA0

MDDR 3_A15

MDDR 3_A14

MDDR 3_A13

MDDR 3_A12

MDDR 3_A11

MDDR 3_A10

MDDR 3_A9

MDDR 3_A8

MDDR 3_A7

MDDR 3_A6

MDDR 3_A5

MDDR 3_A4

MDDR 3_A3

MDDR 3_A2

MDDR 3_A1

MDDR 3_A0

C112

C112

C111

C111

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

GND

GND

DDR3_78 P _8b

DDR 3_78P _8b

BG A78-DDR3

BG A78-DDR3

DDR3_78 P _8b

DDR 3_78P _8b

BG A78-DDR3

BG A78-DDR3

RESET

H2

CS

F3

RAS

G3

CAS

H3

WE

J3

BA2

K8

BA1

J2

BA0

J7

A15

N7

A14

N3

A13

K7

A12/BC

M7

A11

H7

A10/AP

M3

A9

N8

A8

M2

A7

M8

A6

L2

A5

L8

A4

K2

A3

L3

A2

L7

A1

K3

A0

J8

VR E FCA

E1

VR E FDQ

U43

U43

N2

RESET

H2

CS

F3

RAS

G3

CAS

H3

WE

J3

BA2

K8

BA1

J2

BA0

J7

A15

N7

A14

N3

A13

K7

A12/BC

M7

A11

H7

A10/AP

M3

A9

N8

A8

M2

A7

M8

A6

L2

A5

L8

A4

K2

A3

L3

A2

L7

A1

K3

A0

J8

VR E FCA

E1

VR E FDQ

M9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSSA1VSS

VSS

VSS

VSS

VSS

VSS

VSS

J1

L1

F2

A8

B1

D8

N1

K1

M1

G2

D7

M9

K9

G8

A2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSSA1VSS

VSS

VSS

VSS

VSS

VSS

J1

F2

L1

B1

A8

N1

D8

E9

C1

A9

VDD

VDDQ

VDDQ

VDDQ

VDDQ

DM/TDQS

NU/TDQS

VSSQ

VSS

VSSQC9VSSQ

VSS

VSS

VSSQ

VSSQ

VSS

J9

F8

L9

B8

B2

D9

N9

D1

GND

E2

B9

E9

A9

C1

VDD

VDDQ

VDDQ

VDDQ

VDDQ

DM/TDQS

NU/TDQS

VSSQ

VSSQ

VSSQ

VSS

VSSQC9VSSQ

VSS

VSS

VSS

J9

F8

L9

B2

B8

D1

D9

N9

C0805

G9

MDDR 3_CK E0

CKE

G1

MDDR 3_ODT0

ODT

G7

CK

F7

CK

B3

DDR3_ D0

DQ0

C7

DDR3_ D3

DQ1

C2

DDR3_ D4

DQ2

C8

DDR3_ D1

DQ3

E3

DDR3_ D6

DQ4

E8

DDR3_ D5

DQ5

D2

DDR3_ D2

DQ6

E7

DDR3_ D7

DQ7

D3

DDR3_ DQS n0

DQS

C3

DDR3_ DQS p0

DQS

B7

DDR3_ DQM0

A7

F1

NC

H1

NC

H9

NC

F9

NC

A3

NC

H8

ZQ

CKE

ODT

CK

CK

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

DQS

NC

NC

NC

NC

NC

ZQ

R83

R83

240R _1%

240R _1%

R0402

R0402

GND

C105

C105

C106

C106

10uF_6 .3V

10uF_6 .3V

0.1uF

0.1uF

C0805

C0805

C0402

C0402

G9

MDDR 3_CK E0

G1

MDDR 3_ODT0

G7

F7

B3

DDR3_ D16

C7

DDR3_ D21

C2

DDR3_ D22

C8

DDR3_ D19

E3

DDR3_ D20

E8

DDR3_ D17

D2

DDR3_ D18

E7

DDR3_ D23

D3

DDR3_ DQS n2

C3

DDR3_ DQS p2

B7

DDR3_ DQM2

A7

F1

H1

H9

F9

A3

H8

R99

R99

240R _1%

240R _1%

R0402

R0402

C121

C121

0.1uF

0.1uF

C0402

C0402

C173

C173

0.1uF

0.1uF

C0402

C0402

GND

MDDR 3_R ST

MDDR 3_nCS 0

MDDR 3_nR AS

MDDR 3_nCA S

MDDR 3_nWE

MDDR 3_BA2

MDDR 3_BA0

MDDR 3_A15

MDDR 3_A14

MDDR 3_A13

MDDR 3_A12

MDDR 3_A11

MDDR 3_A10

MDDR 3_A9

MDDR 3_A8

MDDR 3_A7

MDDR 3_A6

MDDR 3_A5

MDDR 3_A4

MDDR 3_A3

MDDR 3_A2

MDDR 3_A1

MDDR 3_A0

C126

C126

0.1uF

0.1uF

C0402

C0402

MDDR 3_R ST

MDDR 3_nCS 0

MDDR 3_nR AS

MDDR 3_nCA S

MDDR 3_nWE

MDDR 3_BA2

MDDR 3_BA1

MDDR 3_BA0

MDDR 3_A15

MDDR 3_A14

MDDR 3_A13

MDDR 3_A12

MDDR 3_A11

MDDR 3_A10

MDDR 3_A9

MDDR 3_A8

MDDR 3_A7

MDDR 3_A6

MDDR 3_A5

MDDR 3_A4

MDDR 3_A3

MDDR 3_A2

MDDR 3_A1

MDDR 3_A0

GND

C171

C171

0.1uF

0.1uF

C0402

C0402

2

DDR3_78 P _8b

DDR 3_78P _8b

BG A78-DDR3

BG A78-DDR3

DDR3_78 P _8b

DDR 3_78P _8b

BG A78-DDR3

BG A78-DDR3

1

DDR3_1 .5V

C129

C129

C130

C130

C127

DDR3_ D11

DDR3_ D10

DDR3_ D13

DDR3_ D12

DDR3_ D15

DDR3_ D8

DDR3_ D9

DDR3_ D14

240R _1%

240R _1%

R0402

R0402

R101

R101

240R _1%

240R _1%

R0402

R0402

C127

0.1uF

0.1uF

C0402

C0402

R95

R95

GND

C134

C134

C133

C133

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

0.1uF

0.1uF

C0402

C0402

C138

C138

0.1uF

0.1uF

C0402

C0402

C123

C123

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

GND

C174

C174

C203

C203

0.1uF

0.1uF

0.1uF

0.1uF

C0402

C0402

C0402

C0402

GND

C200

C200

0.1uF

0.1uF

C0402

E2

B9

K1

A2

G2

D7

M1

K9

M9

G8

U42

U42

VDD

VDD

VDD

VDD

VDD

VDD

VDD

RESET

CS

RAS

CAS

WE

BA2

BA1

BA0

A15

A14

A13

A12/BC

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VR E FCA

VR E FDQ

U44

U44

RESET

CS

RAS

CAS

WE

BA2

BA1

BA0

A15

A14

A13

A12/BC

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VR E FCA

VR E FDQ

VDD

VSSA1VSS

VSS

VSS

VSS

VSS

VSS

VSS

J1

L1

F2

A8

B1

D8

N1

K1

M1

A2

K9

M9

G8

G2

D7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSSA1VSS

VSS

VSS

VSS

VSS

VSS

VSS

J1

L1

F2

B1

A8

N1

D8

N2

H2

F3

G3

H3

J3

K8

J2

J7

N7

N3

K7

M7

H7

M3

N8

M2

M8

L2

L8

K2

L3

L7

K3

J8

E1

N2

H2

F3

G3

H3

J3

K8

J2

J7

N7

N3

K7

M7

H7

M3

N8

M2

M8

L2

L8

K2

L3

L7

K3

J8

E1

E9

C1

A9

VDD

VDDQ

VDDQ

VDDQ

DM/TDQS

NU/TDQS

VSSQ

VSSQ

VSS

VSSQC9VSSQ

VSSQ

VSS

VSS

VSS

J9

F8

L9

B8

B2

D9

D1

N9

E2

B9

A9

C1

E9

VDD

VDDQ

VDDQ

VDDQ

DM/TDQS

NU/TDQS

VSSQ

VSSQ

VSSQ

VSS

VSSQC9VSSQ

VSS

VSS

VSS

J9

F8

L9

B8

B2

D1

D9

N9

C0402

G9

VDDQ

GNDGND

VDDQ

MDDR 3_CK E0

CKE

G1

MDDR 3_ODT0

ODT

G7

MDDR 3_CL K n0

CK

F7

MDDR 3_CL K p0

CK

B3

DQ0

C7

DQ1

C2

DQ2

C8

DQ3

E3

DQ4

E8

DQ5

D2

DQ6

E7

DQ7

D3

DDR3_ DQS n1

DQS

C3

DDR3_ DQS p1

DQS

B7

DDR3_ DQM1

A7

F1

NC

H1

NC

H9

NC

F9

NC

A3

NC

H8

ZQ

DDR3_1 .5V

G9

MDDR 3_CK E0

CKE

G1

MDDR 3_ODT0

ODT

G7

MDDR 3_CL K N1

CK

F7

MDDR 3_CL KP1

CK

B3

DDR3_ D29

DQ0

C7

DDR3_ D28

DQ1

C2

DDR3_ D27

DQ2

C8

DDR3_ D24

DQ3

E3

DDR3_ D31

DQ4

E8

DDR3_ D26

DQ5

D2

DDR3_ D25

DQ6

E7

DDR3_ D30

DQ7

D3

DDR3_ DQS n3

DQS

C3

DDR3_ DQS p3

DQS

B7

DDR3_ DQM3

A7

F1

NC

H1

NC

H9

NC

F9

NC

A3

NC

H8

ZQ

4 pcs DDR3 are placed on same layer

To place DDR3 on 2 side,

please refer to another schematic

Title

Title

Title

AML 8726 -MX_R E F -A

AML 8726 -MX_R E F -A

AML 8726 -MX_R E F -A

Siz e Document Number Rev

Siz e Document Number Rev

Siz e Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

2

Date: Sheet

DDR

DDR

DDR

4 13Thursday , July 12, 2012

4 13Thursday , July 12, 2012

1

4 13Thursday , July 12, 2012

V1.0

V1.0

V1.0

of

of

of

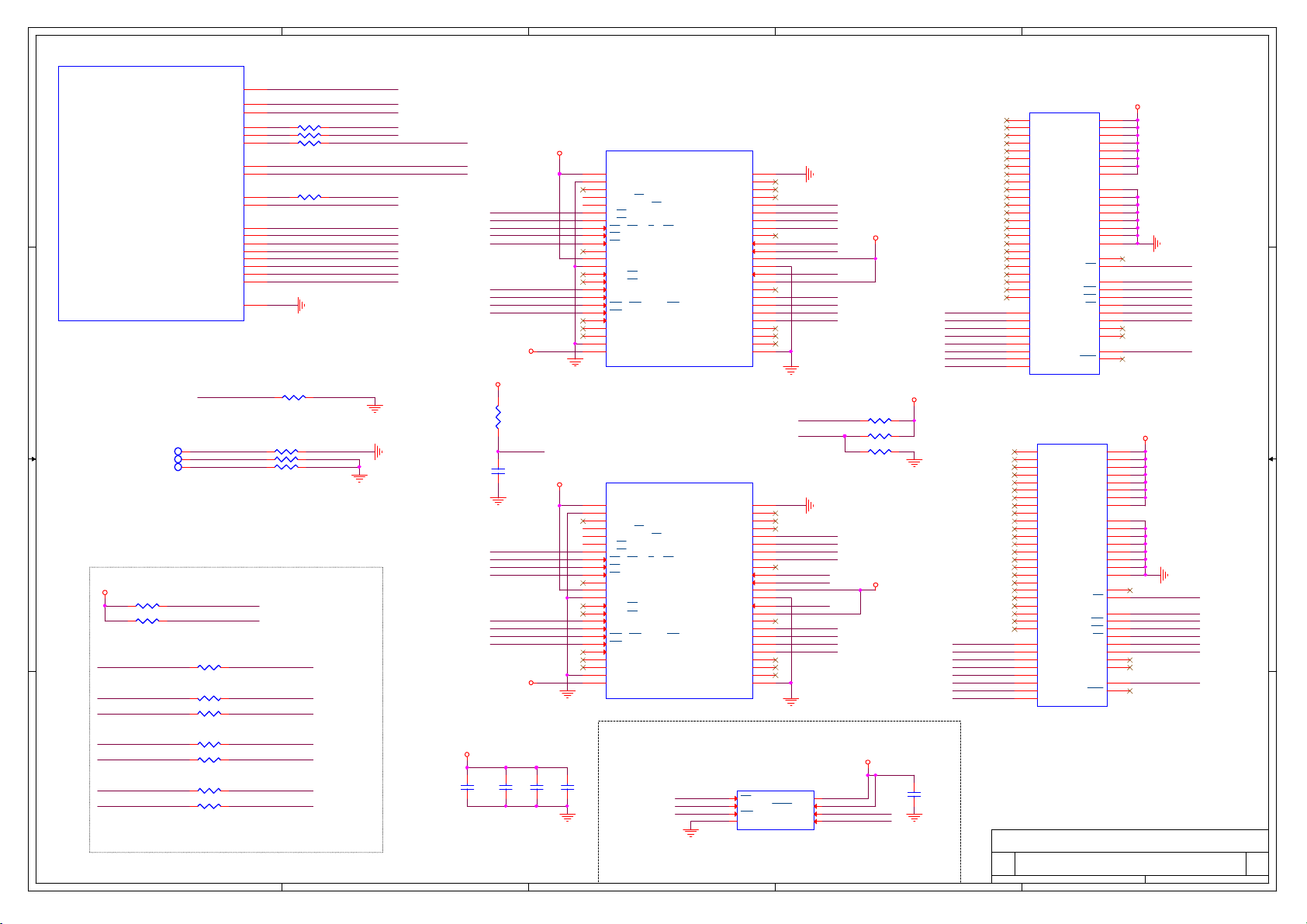

Page 5

5

U37C

U37C

AML8726-MX

AML8726-MX

(L ib V ers ion:1227 )

(L ib V ers ion:1227 )

BO OT _17 (S P I_ NOR _ CS _ n_A)

BO OT _8 (NA ND_CE 0)

BO OT _9 (NA ND_CE 1)

BO OT _16 (N AND_ DQS)

D D

C C

BO OT _14 (N AND_ WE n_ CL K // SP I _NOR _C _ A)

BO OT _11 (N AND_ CE 3 // NAND_ RB 1 // SDXC _ CL K _C)

BO OT _10 (N AND_ CE 2 // NAND_ RB 0 // SDXC _ CMD _C)

BO OT _0 (NA ND_I O_0 // SDXC _D 0_C // BSD _T DO)

BO OT _1 (NA ND_I O_1 // SDXC _D 1_C // BSD _T DI )

BO OT _2 (NA ND_I O_2 // SDXC _D 2_C // BSD _T MS)

BO OT _3 (NA ND_I O_3 // SDXC _D 3_C // BSD _T CK)

BO OT _4 (NA ND_I O_4 // SDXC _D 4_C // BSD _T RS T)

AML8726-MX

AML8726-MX

BO OT _15 (N AND_ RE n_W R)

BO OT _13 (N AND_ CL E // SP I _NOR _ Q_ A)

BO OT _12 (N AND_ AL E // SP I _NOR _D _A)

BO OT _5 (NA ND_I O_5 // SDXC _D 5_C)

BO OT _6 (NA ND_I O_6 // SDXC _D 6_C)

BO OT _7 (NA ND_I O_7 // SDXC _D 7_C)

place to easy welding place where can be

weld when open the shell.

Po wer ON Cong

NAND_CLE

1 NAND Async mode

0 NAND Toggle mode

R126 22R

R126 22R

R140 22R

R140 22R

R154 22R

R154 22R

R150 NC/22R

R150 NC/22R

R142 NC/22R

R142 NC/22R

R163 NC/22R

R163 NC/22R

R156 NC/22R

R156 NC/22R

5

NAND_D4

NAND_D3

NAND_D2

NAND_CS3

NAND_CS4

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

R0402

T P16T ES T 3T P16T ES T3

T P11T ES T 3T P11T ES T3

T P10T ES T 3T P10T ES T3

NAND_D4 NAND_D3 NAND_D2

1 1 1 Boot from nand without RB

1 1 0 Nand with RB

1 0 X SPI nor ash romboot

0 1 1 Boot from iNAND uses SDIOC

0 1 0 Boot from iNAND uses SDIOB

0 0 1 Boot from iNAND uses SDIOA

B B

VDD IO

R127 10K

R127 10K

R0402

R0402

R128 10K

R128 10K

R0402

R0402

NAND_CS3

NAND_CS2 NAND_CS_B1

NAND_CS4

A A

NAND_CS3 NAND_CS_B1

Nand config, default 1CE only

When using 2x2CE, R/B# pins are not used,

need to change Power on config

BSD _ EN

NAND_CLE

T2 5

Y24

W 24

T26

U26

U27

U24

U23

V23

W 23

Y25

Y26

W 25

W 26

V25

V26

V27

U25

W 22

R113 NCR0402R113 NCR0402

NC R0402

NC R0402

NC/4.7K R0402

NC/4.7K R0402

4.7K R0402

4.7K R0402

NAND_R/B#_ A1

NAND_R/B#_B1

NAND_CS_ A2NAND_CS2

NAND_R/B#_ A2NAND_CS4

NAND_CS_B2NAND_CS4

R115 22R

R115 22R

R0402

R0402

R116 22R

R116 22R

R0402

R0402

R117 22R

R117 22R

R0402

R0402

R114 22R

R114 22R

R0402

R0402

GND

R121

R121

R122

R122

R123

R123

NAND_CS3&NAND_CS4

also for NAND_R/B#

NC when 2 pcs 2CE

welding when 2 pcs 1CE

welding when 1 pcs 2CE

welding when 2 pcs 2CE

SP I_CS

NAND_CS1

NAND_CS2

NAND_nDQS

NAND_nRE

NAND_nWENAND_nWE SP I_C

NAND_CLENAND_CLE SP I_Q

NAND_ ALENAND_ ALE SP I_D

NAND_CS4

NAND_CS3

NAND_D0

NAND_D1

NAND_D2

NAND_D3

NAND_D4

NAND_D5

NAND_D6

NAND_D7

GND

GND

GND

4

3

2

1

TSOP_NAND

Layout

)&"

U10*U19+Lay

U9

*

NAND1

VDD IO

NAND_R/B#_ A2

NAND_R/B#_ A1

NAND_nRE

NAND_CS1

NAND_CS_ A2

NAND_CLE

NAND_ ALE

NAND_nWE

WP#

VDD IO

VDD IO

R106

R106

47K

47K

R0402

R0402

WP#

C117

C117

0.1uF

0.1uF

VDD IO

C0402

C0402

GND

NAND_R/B#_B1

NAND_nRE

NAND_CS_B1

NAND_CS_B2

NAND_CLE

NAND_ ALE

NAND_nWE

WP#

VDD IO

GND

VDD IO

CLOSE TO NAND

C114

C114

C115

0.1uF

0.1uF

C0402

C0402

C115

0.1uF

0.1uF

C0402

C0402

GND

C113

C113

4.7uF_6.3V

4.7uF_6.3V

C0805

C0805

4

U10

U10

Normal // M icron,ONFI // Toshiba

Normal // Micro n,ONFI // Toshiba

1

NC // NC // VCC

2

NC // NC // VSS

3

NC

4

NC // R/B Y4 // NC

5

NC // NC // R /BY 3 // NC

6

R /BY2

7

R /BY1

8

RE // RE (W /R ) // RE

9

CE1

10

CE2

11

NC

12

VCC

13

VSS

14

NC // CE 3 // NC

15

NC // CE 4 // NC

16

C LE

17

ALE

18

W E // W E (C LK ) // WE

19

WP

20

NC // VSP 3 // NC

21

NC

22

NC

23

NC // NC // VSS2

NC // NC // VCC224NC // VSS Q // VSS3

GND

29F32G08CB ACA

29F32G08CB ACA

NC // VSS Q // VSS4

(I/O1 5)

(I/O1 4)

(I/O1 3)

(I/O1 2)

NC // VCC Q // PSL

NC // VSP 1 // VCCQ

NC // VSP 2( DQS ) // NC

NC // VCC Q // VCCQ

(I/O1 1)

(I/O1 0)

T SOP-48H1_2A

T SOP-48H1_2A

welding this NAND when using one TSOP NAND

NAND2

U9

U9

Normal // Micro n,ONFI // Toshiba

Normal // Micro n,ONFI // Toshiba

1

NC // NC // VCC

2

NC // NC // VSS

3

NC

4

NC // R/B Y4 // NC

5

NC // NC // R /BY 3 // NC

6

R /BY2

7

R /BY1

8

RE // RE (W /R ) // RE

9

CE1

10

CE2

11

NC

12

VCC

13

VSS

14

NC // CE 3 // NC

15

NC // CE 4 // NC

16

C LE

17

ALE

18

W E // W E (C LK ) // WE

19

WP

20

NC // VSP 3 // NC

21

NC

22

NC

23

NC // NC // VSS2

NC // NC // VCC224NC // VSS Q // VSS3

NC/29F32G08CB ACA

NC/29F32G08CB ACA

NC // VSS Q // VSS4

(I/O1 5)

(I/O1 4)

(I/O1 3)

(I/O1 2)

NC // VCC Q // PSL

NC // VSP 1 // VCCQ

NC // VSP 2( DQS ) // NC

NC // VCC Q // VCCQ

(I/O1 1)

(I/O1 0)

T SOP-48H1_2A

T SOP-48H1_2A

SPI NOR

C116

C116

0.1uF

0.1uF

C0402

C0402

3

Reserved for Debug

SP I_CS

SP I_Q

WP#

GND

SPI nor flash places to the easy welding

place where can be weld when open the shell.

48

47

46

45

44

I/O7

43

I/O6

42

I/O5

41

I/O4

40

39

38

37

VCC

36

VSS

35

34

33

32

I/O3

31

I/O2

30

I/O1

29

I/O0

28

27

(I/O9 )

26

(I/O8 )

25

48

47

46

45

44

I/O7

43

I/O6

42

I/O5

41

I/O4

40

39

38

37

VCC

36

VSS

35

34

33

32

I/O3

31

I/O2

30

I/O1

29

I/O0

28

27

(I/O9 )

26

(I/O8 )

25

U13

SO IC-8-208M ILU13

SO IC-8-208M IL

1

CS

2

SO /S IO1

3

W P/S IO2

GND4S I/S IO0

NC/2MByte_SP I_Nor

NC/2MByte_SP I_Nor

MBM29LV160TE

NAND_D7

NAND_D6

NAND_D5

NAND_D4

NAND_PSL

NAND_ VSP

NAND_D3

NAND_D2

NAND_D1

NAND_D0

GND

NAND_D7

NAND_D6

NAND_D5

NAND_D4

NAND_PSL

NAND_ VSP

NAND_D3

NAND_D2

NAND_D1

NAND_D0

GND

VCC

HOL D/S IO3

SC L K

GND

NAND_nDQS

NAND_PSL

NAND_ VSP

GND

NAND_nDQS

8

7

6

5

SP I_C

SP I_D

U20+Lay

VDD IO

R100 NC/0R

R100 NC/0R

R0402

R0402

R102 NC/0R

R102 NC/0R

R0402

R0402

R104 NC/0R

R104 NC/0R

R0402

R0402

VDD IO

VDD IO

2

VDD IO

GND

GND

C177

C177

NC/0.1uF

NC/0.1uF

C0402

C0402

NAND_D0

NAND_D1

NAND_D2

NAND_D3

NAND_D4

NAND_D5

NAND_D6

NAND_D7

NAND_D0

NAND_D1

NAND_D2

NAND_D3

NAND_D4

NAND_D5

NAND_D6

NAND_D7

NAND1'

U19

U19

OA1

N/U1

N/U2

N/U3

N/U4

N/U5

N/U6

N/U7

N/U8

N/U9

N/U10

N/U11

N/U12

N/U13

N/U14

N/U15

N/U16

N/U17

N/U18

N/U19

N/U20

N/U21

N/U22

N/U23

N/U24

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

NC/T OGGLE N AND

NC/T OGGLE N AND

LG A-60

LG A-60

NAND2'

U20

U20

N/U1

N/U2

N/U3

N/U4

N/U5

N/U6

N/U7

N/U8

N/U9

N/U10

N/U11

J2

N/U12

L2

N/U13

N/U14

N/U15

L8

N/U16

J8

N/U17

N/U18

N/U19

N/U20

N/U21

N/U22

N/U23

N/U24

DQ0

DQ1

J4

DQ2

DQ3

L6

DQ4

DQ5

J6

DQ6

DQ7

NC/T OGGLE N AND

NC/T OGGLE N AND

LG A-60

LG A-60

VCC Q1

VCC Q2

VCC Q3

VCCQ4

VCCQ5

VCC Q6

VCC1

VCC2

VSS Q1

VSS Q2

VSS Q3

VSS Q4

VSS Q5

VSS Q6

VSS1

VSS2

C LE

WP

WE

ALE

R /B

VREF

VPP

DQS

DQS

VCC Q1

VCC Q2

VCC Q3

VCCQ4

VCCQ5

VCC Q6

VCC1

VCC2

VSS Q1

VSS Q2

VSS Q3

VSS Q4

VSS Q5

VSS Q6

VSS1

VSS2

VREF

FL ASH

FL ASH

FL ASH

OE1

OA9

A2

E8

A8

C6

C4

M5

K5

G2

J2

L2

N4

N6

L8

J8

G8

OC1

E2

G6

D3

D5

D7

G4

H3

J4

K3

L6

K7

J6

H7

OA1

OE1

OA9

A2

E8

A8

C6

C4

M5

K5

G2

N4

N6

G8

OC1

E2

G6

D3

D5

D7

G4

H3

K3

K7

H7

T itle

T itle

T itle

A ML 8726 -MX _R E F -A

A ML 8726 -MX _R E F -A

A ML 8726 -MX _R E F -A

Si ze Docu ment Number Rev

Si ze Docu ment Number Rev

Si ze Docu ment Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

VDD IO

OD1

OF1

OB9

OG9

N8

N2

B7

M7

OB1

OG1

OD9

OF9

F7

L4

B3

M3

B5

RE

C8

RE

A4

F3

E4

A6

CE

C2

E6

OC9

OE9

H5

F5

OD1

OF1

OB9

OG9

N8

N2

B7

M7

OB1

OG1

OD9

OF9

F7

L4

B3

M3

B5

RE

C8

RE

A4

C LE

F3

WP

E4

WE

A6

CE

C2

ALE

E6

R /B

OC9

OE9

VPP

H5

DQS

F5

DQS

GND

NAND_nRE

NAND_CLE

WP#

NAND_nWE

NAND_CS1

NAND_ ALE

NAND_R/B#_ A1

NAND_nDQS

VDD IO

GND

NAND_nRE

NAND_CLE

WP#

NAND_nWE

NAND_CS_B1

NAND_ ALE

NAND_R/B#_B1

NAND_nDQS

1

of

of

of

5 13T hursday, July 12, 2012

5 13T hursday, July 12, 2012

5 13T hursday, July 12, 2012

V1.0

V1.0

V1.0

Page 6

5

U3 7D

U3 7D

AML 872 6 -M X

AV DD 2. 5V

C 154 1uF

AV DD 2. 5V

Reserved for AMP_MUTE

BL _ EN

LV D S _0P

LV D S _0N

LV D S _1P

LV D S _1N

LV D S _2P

LV D S _2N

LV D S _3P

LV D S _3N

LV D S _C KP

LV D S _C KN

R 281

C 154 1uF

C 0402

C 0402

VCCx3_EN

R 040 2R 281

R 040 2

AV DD 2. 5V

D D

C C

C 183

C 183

0. 1uF

0. 1uF

C 0402

C 0402

C 141

C 141

1uF

1uF

C 0402

C 0402

8

WI FI _P W R EN

AML 872 6 -M X

(Lib Ver s ion:1227)

(Lib Ver s ion:1227)

V6

AV DD25 _D PLL

V4

AVSS 25_D P LL

V5

DP LL_L D O_EX TC AP

W6

AV DD25_ L VDS

W5

AV DD25_ L VDS

AC3

VSS

Y4

AVSS 25_L VD S

Y5

AVSS 25_L VD S

AD4

GP IOC _9 ( TC ON_7_ A // SP D IF_o ut // E NC _17 // PW M_C)

AF4

GP IOC _8 ( TC ON_6_ A // TC ON_ VC OM // SP D IF_ in)

AE4

GP IOC _7 ( TC ON_5_ A // TC ON_ CP H_ A)

N25

GP IOC _6 ( TC ON_4_ A // TC ON_ OEV 1)

R26

GP IOC _5 ( TC ON_3_ A // TC ON_ CP V 1)

R25

GP IOC _4 ( TC ON_2_ A // TC ON_ OE H)

R23

GP IOC _3 ( TC ON_1_ A // TC ON_ S TV1)

R22

GP IOC _2 (mL V DS TC ON _0_A // TCO N_S TH1)

AA3

MINILVD S _C KP

Y2

MINILVD S _C KN

AC2

LV DS _0P

AC1

LV DS _0N

AB1

LV DS _1P

AB2

LV DS _1N

AB3

LV DS _2P

AA2

LV DS _2N

Y3

LV DS _3P

W2

LV DS _3N

W1

LV DS _4P

V1

LV DS _4N

V2

LV DS _5P

V3

LV DS _5N

1. 5K

1. 5K

W3

LV DS _R EX T_600

AML 872 6 -M X

AML 872 6 -M X

4

TCON FOR

TCON FOR

MiniLVDS

MiniLVDS

TTL TCON

TTL TCON

GP IOD_9 (TC O N_7_ B // PW M_A // ENC _16)

GP IOD_8 (T CO N_6_ B // TC ON_ VC OM_ B)

GP IOD_7 (TC O N_5_ B // // TCON _C PH _B)

GP IOD_6 (T CO N_4_ B // TC ON_ OEV 1_ B)

GP IOD_5 (T CO N_3_ B // TC ON_ CPV 1_B )

GP IOD_4 (TC O N_2_ B // TC ON_ OE H_B)

GP IOD_3 (T CO N_1_ B // TC ON_ ST V1_ B)

GP IOD_2 (L CD TC ON _0_B // TC ON_S T H1_B)

GP IOB _7 (L CD _R 7 // FE C _D 7_B )

GP IOB _6 (L CD _R 6 // FE C _D 6_B )

GP IOB _5 (L CD _R 5 // FE C _D 5_B )

GP IOB _4 (L CD _R 4 // FE C _D 4_B )

GP IOB _3 (L CD _R 3 // FE C _D 3_B )

GP IOB _2 (L CD _R 2 // FE C _D 2_B )

GP IOB _1 (L CD _R 1 // FE C _D 1_B )

GP IOB _0 (L CD _R 0 // FE C _D 0_B )

GP IOB _15 (LCD _ G7 // FE C _ CL K_ OUT)

GP IOB _14 (LCD _ G6 // FE C _ SO P_ OUT)

GP IOB _13 (LCD _ G5 // F EC _ D_VA L ID_OU T)

GP IOB _12 (LCD _ G4 // F EC _ FA IL_OUT)

GP IOB _11 (LCD _ G3 // FE C _ FA IL_B)

GP IOB _10 (LCD _ G2 // FE C _ D_VA L ID_B)

GP IOB _9 (L CD _G 1 // FE C _S OP _ B)

GP IOB _8 (L CD _G 0 // FE C _C L K_B )

GP IOB _23 (LCD _ B7 // FE C_ D7_ OUT)

GP IOB _22 (LCD _ B6 // FE C_ D6_ OUT)

GP IOB _21 (LCD _ B5 // FE C_ D5_ OUT)

GP IOB _20 (LCD _ B4 // FE C_ D4_ OUT)

GP IOB _19 (LCD _ B3 // FE C_ D3_ OUT)

GP IOB _18 (LCD _ B2 // FE C_ D2_ OUT)

GP IOB _17 (LCD _ B1 // FE C_ D1_ OUT)

GP IOB _16 (LCD _ B0 // FE C_ D0_ OUT)

VG HL_ CS 1

GP IOD_1 (L E D_B L_ PW M // PWM _D)

GP IOD_0 (L CD _V GHL_ P WM // P WM_C)

LE D_ C S0

3

D8

E8

E9

E 10

D10

E 11

E 12

E 13

E 14

F15

E 15

E 16

D16

D17

E 17

E 18

C1 3

A14

B14

C1 4

B15

C1 5

B16

C1 6

B10

C1 0

B11

C1 1

B12

C1 2

B13

A13

C2 5

D24

D13

BL _ PW M

D14

LC D _P W R _ E N#

VG H L_ C S1

7"

BL_EN

:

BL_EN;PWM

USB _ PW R _ C TL 2,7

VD DI O

2

896

GPIOC_2

<

R 151

R 151

100 K

100 K

R 040 2

R 040 2

R 155

R 040 2R 15 5

R 040 2

LOW:POWER ON;

HIGHT:POWER DOWN

TP6TES T2 TP6TES T2

TP9TES T2 TP9TES T2

TP 23TES T2 TP 23TE S T2

TP 24TES T2 TP 24TE S T2

TP 26TES T2 TP 26TE S T2

TP 27TES T2 TP 27TE S T2

TP 29TES T2 TP 29TE S T2

TP 30TES T2 TP 30TE S T2

TP 34TES T2 TP 34TE S T2

TP 37TES T2 TP 37TE S T2

2

470 K

470 K

3

1

G

G

S i230 5

S i230 5

Q1 8

Q1 8

DS

DS

3

S OT -2 3

S OT -2 3

C LKE D ID

DA TAE DID

,-. /01 234

56

VBAT?

2

TES T 23

TES T 24

TES T 26

TES T 27

TES T 29

TES T 30

TES T 34

C AB C _EN

C 139

C 139

0. 1uF

0. 1uF

C 0402

C 0402

LC D _3 .0 V

VC C x3

7' LCD

C 140

C 140

10u F _6 .3 V

10u F _6 .3 V

C 0805

C 0805

LC D _3 .0 V

C 142

C 142

10u F _6 .3 V

10u F _6 .3 V

C 0805

C 0805

BL _ PW M

BL _ EN

LC D _3 .0 V

LV D S _0N

LV D S _0P

LV D S _1N

LV D S _1P

LV D S _2N

LV D S _2P

LV D S _C KN

LV D S _C KP

LV D S _3N

LV D S _3P

C 155

C 155

0. 1uF

0. 1uF

C 0402

C 0402

R 1330RR 040 2R 1330RR 040 2

R 1340RR 040 2R 1340RR 040 2

R 135

R 040 2R 135

R 040 2

C LKE D ID

R 166 NC /0 RR 0 402R 166 NC /0 RR 0 402

R 167 NC /0 RR 040 2R 16 7 NC /0RR 040 2

R 131NCR 040 2R 131NCR 040 2

R 132NCR 040 2R 132NCR 040 2

R 164 NC /0 RR 040 2R 16 4 NC /0RR 040 2

TES T 23

TES T 24

TES T 26

TES T 27

TES T 29

TES T 30

4. 7K/ NC

4. 7K/ NC

TES T 34

R 165 NC /0 RR 040 2R 16 5 NC /0RR 040 2

DA TAE DID

C AB C _EN

1

N0 70 IC G -L E D4

N0 70 IC G -L E D4

FP C 40 _ PT 05 _ H2B

FP C 40 _ PT 05 _ H2B

1024x600 7'

IPS: RD070HD28

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

1

2

3

4

5

6

7

8

9

J1 9

J1 9

NC

VDD

VDD

V_ EE D ID

NC

CL KE DID

DAT AE DID

RX IN0RX IN0+

GND

RX IN1RX IN1+

GND

RX IN2RX IN2+

GND

RX C LK INRX C LK IN+

NC

NC

NC

GND

NC

NC

GND

NC

NC

GND

NC

NC

LE DLE DLE DNC

LE D_ PWM

LE D_ EN

CA B C_ EN

LE D_ VCC

LE D_ VCC

LE D_ VCC

S H1

GND

GND

S H2

VC C x3VC Cx

Q2 1

Q2 1

DS

DS

3

2

S OT -2 3

S OT -2 3

G

G

S i230 5

S i230 5

1

R 169

R 169

R 171

R 171

47K

47K

470 K

470 K

R 040 2

R 040 2

R 040 2

R 040 2

VC C x 3_ E N#

B B

A A

5

2

4

3

2

Check PCB package pin1 carefully

Title

Title

Title

AM L8726 -MX _R E F -A

AM L8726 -MX _R E F -A

AM L8726 -MX _R E F -A

S ize Do cu men t Nu mbe r Re v

S ize Do cu men t Nu mbe r Re v

S ize Do cu men t Nu mbe r Re v

C us tom

C us tom

C us tom

Da te: S hee t

Da te: S hee t

Da te: S hee t

P ane l& T OU CH

P ane l& T OU CH

P ane l& T OU CH

1

6 13Th urs da y, J uly 12 , 20 12

6 13Th urs da y, J uly 12 , 20 12

6 13Th urs da y, J uly 12 , 20 12

of

of

of

V 1.0

V 1.0

V 1.0

Page 7

5

4

3

2

1

USB OTG

limite output current

V CC 5V

D D

US B _ P W R_ C TL

DM1 D1 -

DM1

DP1

C C

DP1

ID1

C3 05

C3 05

1nF

1nF

C0 402

C0 402

R 1841KR 0402R18 41KR 0402

ABC D

5

4

2,6

R 186

R 186

100K

100K

R 0402

R 0402

R 3020RR 0402R30 20RR 0402

NC /0R x2

NC /0R x2

2

1

L9

R 3030RR 0402R30 30RR 0402

! " #

$ % & ' (

U16

U16

LP 5 206X

LP 5 206X

S OT 23 _5 H1 4A

S OT 23 _5 H1 4A

IN

EN

+

Lay

L080 5 x2L9

L080 5 x2

OUT

GND

SET

4

3

US B _ ID1ID1

1

2

3

D1+

D25

D25

NC /ES D9 B 5V

NC /ES D9 B 5V

D06 03

D06 03

R 193

R 193

6.8 K

6.8 K

R 0402

R 0402

US B _ P WR

C1 65

C1 65

0.1 uF

0.1 uF

C0 402

C0 402

D23

D23

NC /ES D9 B 5V

NC /ES D9 B 5V

D06 03

D06 03

ABC DEF

US B _ P WR

D24

D24

NC /ES D9 B 5V

NC /ES D9 B 5V

D06 03

D06 03

VB US 13

CO N2

CO N2

US B _ MICR O B _5S

US B _ MICR O B _5S

1

VBUS

VBUS

2

D-

D-

3

D+

D+

4

ID

ID

5

GND

GND

MICR O US B _ 5pin_ S M D

MICR O US B _ 5pin_ S M D

R 1831KR 0402R18 31KR 0402

C1 67

C1 67

1nF

1nF

C0 402

C0 402

6

7

10

11

8

9

US B _ P WR

US B _ P WR

C3

C3

1nF _2 5V

1nF _2 5V

C0 402

C0 402

R 188

R 0402R18 8

C1 68

C1 68

1nF

1nF

C0 402

C0 402

close to CPU

R 0402

3

ADC _ KE Y

when using less keys,

delete right side buttons.

Only the left key works when

pressing multiple keys imultaneously

key like "OK", and other

special keys should be placed to the right side

Close to CPU

S D_ CL K _B 3

S D_ D0_ B

S D_ D1_ B

S D_ D2_ B

S D_ D3_ B

S D_ CM D_B 3 ,7

S D_ D0_ B 3,7

S D_ CM D_B 3,7

ADC KEY

AV DD 2. 5V

0%

R 187

R 187

4.7 K _1%

4.7 K _1%

R 0402

R 0402

47K

47K

R 189 4. 7K _1 %

R 189 4. 7K _1 %

R 0402

R 0402

+

=>? @"

D15

D15

NC /ES D9 B 5V

NC /ES D9 B 5V

R 0603

R 0603

22R

22R

R 198

R 0402R1 98

R 0402

C1 69 NC /10pF

C1 69 NC /10pF

C0 402

C0 402

RN 04 02

RN 04 02

1

8

3,7

R P5

R P5

2

7

3

3

6

3

4x 22R

4x 22R

45

3

22R

22R

R3

R 0402R3

R 0402

R 191 NC /10K

R 191 NC /10K

R 192 NC /10K

R 192 NC /10K

R 0402

R 0402

R 0402

R 0402

S D_ CL K

S D_ D0

S D_ D1

S D_ D2

S D_ D3

S D_ CM D

ESC

HOMEVOL+MENU VOL-

14% 26% 38% 50%

VOL-/+

G

KEY _ HO ME

ENTER( ME NU)

S T 1112 A

S T 1112 A

56

12

34

K2

K2

B utton_P KEY

B utton_P KEY

1%

KEY _ HO ME

Button labeled corresponding function

Pl e as e f ol l o w be l ow r e s i s t or va l ue

KEY 1

2 3 4 5 6 7 8

Value

0% 14 % 26% 38% 50 % 62% 75% 87 %

Resist er 750R1%910R1%1.2K1%1.8K1%3K1%6.2K1%18K

pull-u p: 4.7 K_1%$ MA X 8 AD C KEYs

V DDIO

M_ CL K _IN

M_ CL K _O UT

GN D

R 125 0R R 0402R 125 0R R 0402

R 0402

R 0402

R 75 100R

R 75 100R

1

XIN/CLK IN

2

XOUT

3

SSON/OFF

GND4ModOut

U11

U11

NC /SS DC P 11 08 AF

NC /SS DC P 11 08 AF

DF N8 -P T 05 -H0_ 8A

DF N8 -P T 05 -H0_ 8A

GN D

R 85 1M

R 85 1M

2

24 MHz _20 pF

24 MHz _20 pF

S MD 4P 322 5

S MD 4P 322 5

C8 8

C8 8

27p F _N PO

27p F _N PO

C0 402

C0 402

5

3

OS C IN

3

OS C O UT

B B

V DDIO

A A

M_ CL K _IN

M_ CL K _O UT

334

Y2

Y2

R 0402

R 0402

M_ CL K _IN

R 212 NC /51R

M_ CL K _O UT

8

VDD

7

SSE XTR

6

CP

5

24MHz_20pF

4

112

GN D

C8 9

C8 9

27p F _N PO

27p F _N PO

C0 402

C0 402

GN D

R 212 NC /51R

C2 14 NC /1uF

C2 14 NC /1uF

R 217 NC /200K

R 217 NC /200K

R 218 NC /100R

R 218 NC /100R

R 0402

R 0402

V DDIO

R 0402

R 0402

C0 402

C0 402

R 0402

R 0402

R 216 NC /4. 7K

R 216 NC /4. 7K

R 0402

R 0402

R 215 NC

R 215 NC

R 0402

R 0402

OS C IN

V DDIO

GN D

GN D

CA RD _ V CC

1

2

3

4

5

6

7

8

9

10

11

12

13

TF _ S D_ S O CK ET

TF _ S D_ S O CK ET

TF _ C ARDH 1 _7A

TF _ C ARDH 1 _7A

1

U17

U17

DAT A2

CD/D ATA3

CMD

VDD

CLK

VSS

DAT A0

DAT A1

CD

G1

G2

G3

G4

7 13T hurs da y, J ul y 12 , 2012

7 13T hurs da y, J ul y 12 , 2012

7 13T hurs da y, J ul y 12 , 2012

V 1 .0

V 1 .0

V 1 .0

of

of

of

CA RD _ EN 3

3

CA RD _ DE T

V DDIO

R 207

R 207

NC /10K

NC /10K

R 0402

R 0402

CA RD _ DE T

C1 76 1nF

C1 76 1nF

C0 402

C0 402

R 203

R 203

NC /10K

NC /10K

R 0402

R 0402

R 202

R 202

2

47K

47K

R 0402

R 0402

CA RD _ V CC

Q2 3

Q2 3

DS

DS

3

S OT -2 3

S OT -2 3

G

G

S i23 05

S i23 05

1

R 301

R 301

10K

10K

R 0402

R 0402

C3 01

C3 01

1uF _ 6. 3V

1uF _ 6. 3V

C0 402

C0 402

S D_ D2

S D_ D3

S D_ CM D

S D_ CL K

S D_ D0

S D_ D1

CA RD _ DE T

ABCD

T itle

T itle

T itle

A M L8726 - MX _R E F -A

A M L8726 - MX _R E F -A

A M L8726 - MX _R E F -A

S ize Doc umen t Nu mber R ev

S ize Doc umen t Nu mber R ev

S ize Doc umen t Nu mber R ev

A3

A3

A3

K e y & I R & U S B & C a rd

K e y & I R & U S B & C a rd

K e y & I R & U S B & C a rd

Da te: S hee t

Da te: S hee t

4

3

2

Da te: S hee t

Page 8

5

4

3

2

1

VDD IO

1

W IF I_SD _D2 3

W IF I_SD _D0 3

D D

C C

B B

W IF I_SD _D1 3

W IF I_SD _D3 3

W IF I_SD _C MD 3

W IF I_SD _C LK 3

8

7

6

R 283

Close to CPU

C 263 NC/22pF

C 263 NC/22pF

4x22R

4x22R

R N0402

R N0402

R 0402R 283

R 0402

R 280

W IF I_D2

2

W IF I_D0

RP6

RP6

3

W IF I_D1

45

W IF I_D3

22R

22R

R 0402R 280

R 0402

C 0402

C 0402

R8NC /10K R8NC /10K

R7NC /10K R7NC /10K

R12NC /10K R 12NC /10K

R18NC/10K R 18NC/10K

22R

22R

UART _ A_C TS_N3

UART_A_CTS_N is used as WIFI_WAKE

in WL-211 (to cpu)

W IF I_P W REN

R28NC /10K R 28NC /10K

W IF I_C MD

W IF I_C LK

W IF I_D0

W IF I_D1

W IF I_D2

W IF I_D3

W IF I_C LK

W IF I_C MD

R 307 4.7KR 0402R 307 4.7KR04 02

6

U45

U45

W L-211

W L-211

21

S DIO _DAT A_0