Page 1

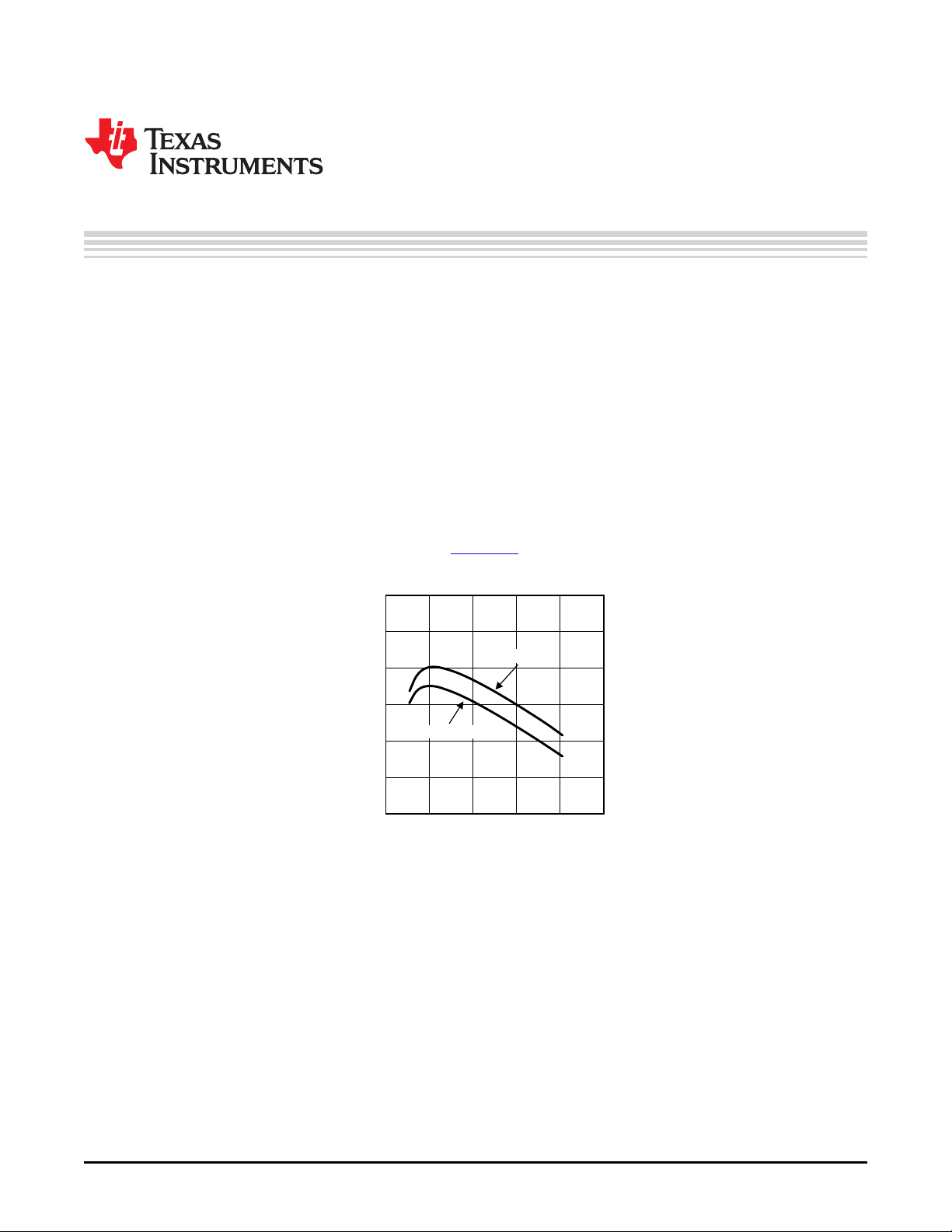

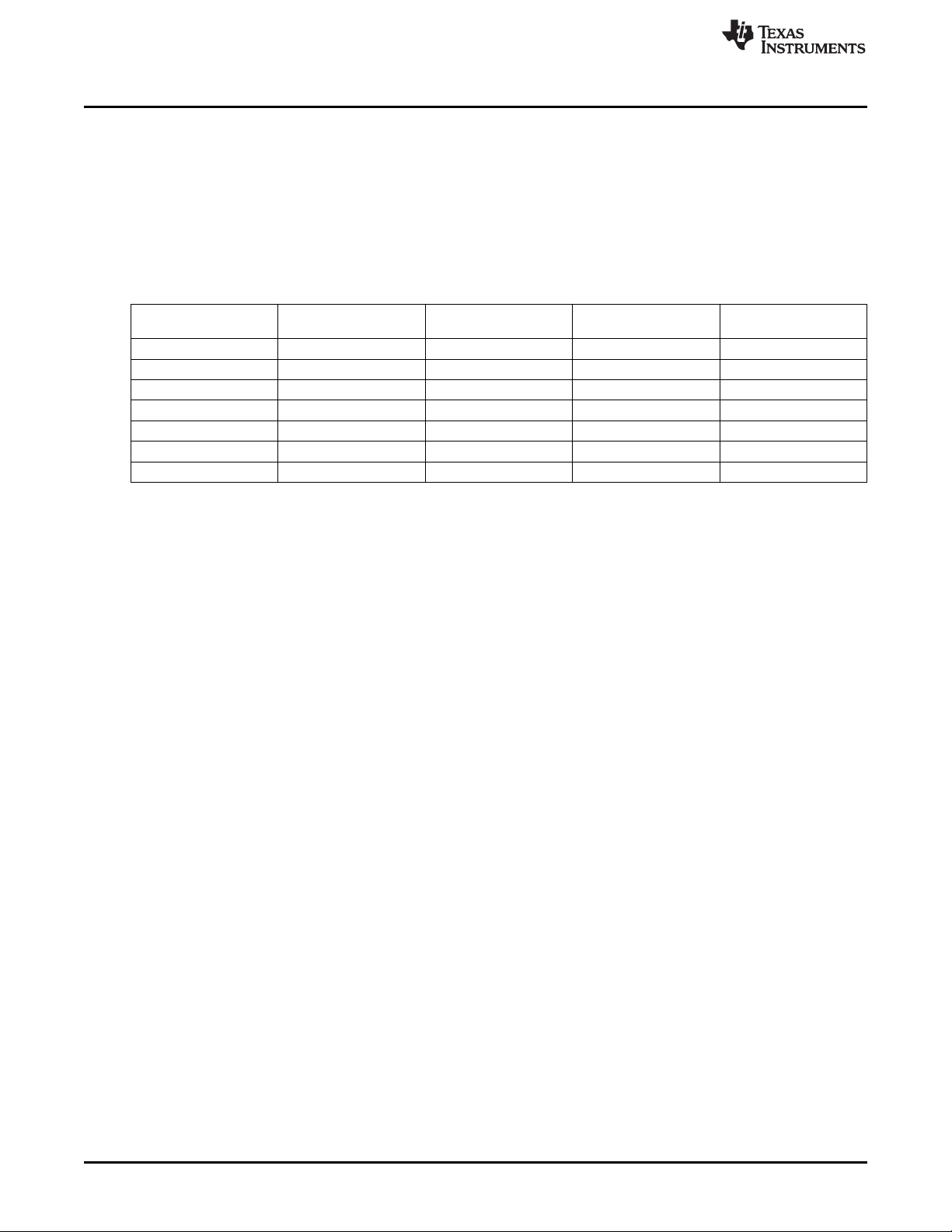

VIN (V)

EFFICIENCY (%)

100

95

90

85

80

75

70

0 16 32 48 64 80

Q1 is IPD200N15N3

Q1 is FDD3682

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

1 Introduction

This wide range evaluation board showcases the LM3423 NFET controller used with a buck-boost current

regulator. It is designed to drive 4 to 8 LEDs at a maximum average LED current of 700mA from a DC

input voltage of 10 to 70V.

The evaluation board showcases most features of the LM3423 including PWM dimming, fault and LED

status flags, output overvoltage protection and input under-voltage lockout. Note that there are two

revisions of this PCB. The documentation for the latest revision (551600305-002 RevA) is shown first. The

schematic, layout and bill of materials for the first revision (551600305-001 Rev1) can be found at the end

of this document.

The buck-boost circuit can be easily redesigned for different specifications by changing only a few

components (see the Alternate Designs section found at the end of this application note). Note that design

modifications can change the system efficiency. See the LM3421/21Q1/21Q0 LM3423/23Q1/23Q0 N-Ch

Controllers for Constant Current LED Drivers (SNVS574) data sheet for a comprehensive explanation of

the device and application information.

User's Guide

SNVA415C–June 2010–Revised May 2013

All trademarks are the property of their respective owners.

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Figure 1. Efficiency with 6 Series LEDS at 700mA

1

Copyright © 2010–2013, Texas Instruments Incorporated

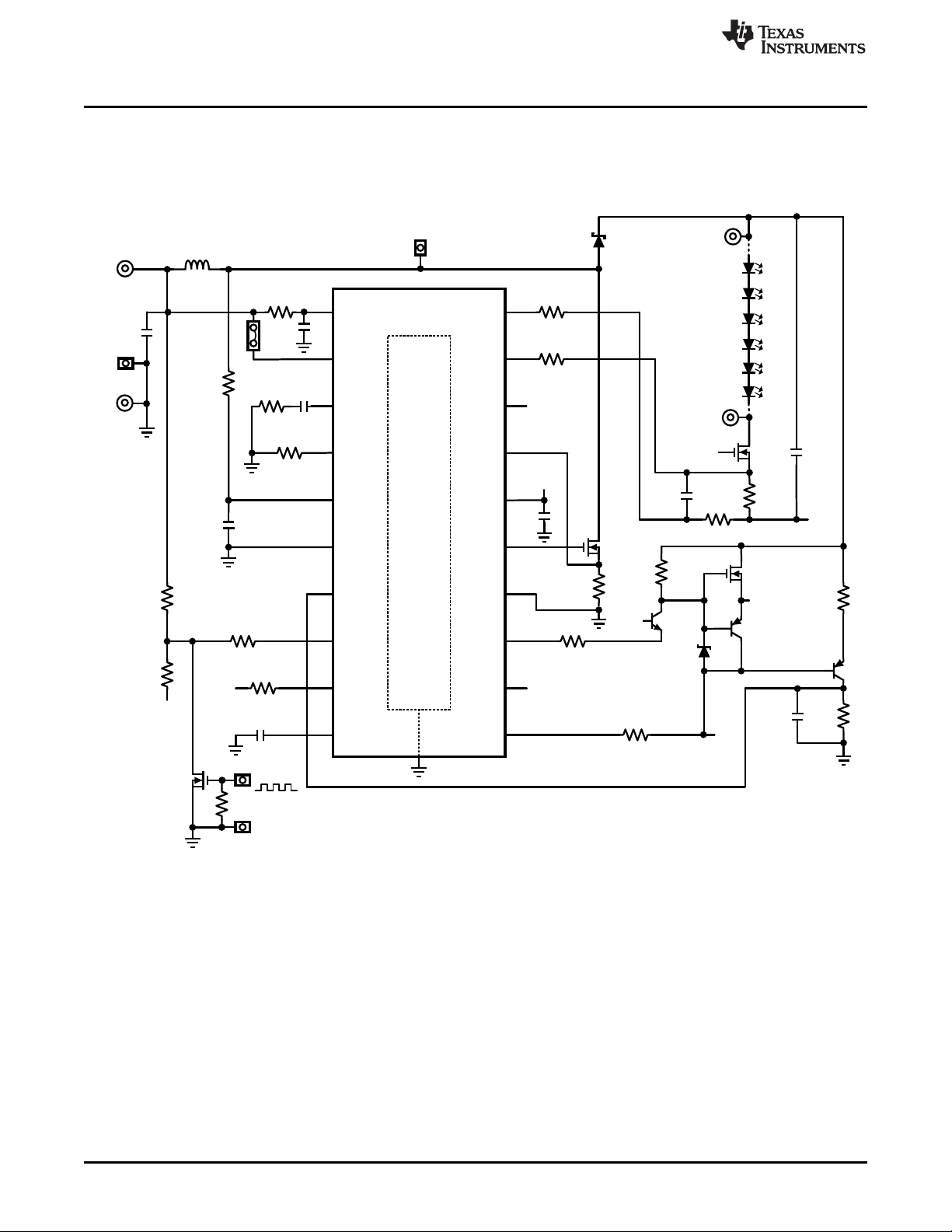

Page 2

C4,

C6

(a-d)

Q1

R18

R11

R9

R20

C12

C11

Q5

V

IN

Q7

Q6

Q4

D2

DIM

R17

R19

DIM

Q2

V

IN

L1

C9

R6

C8

R1

R10

R13

R5

R8

R7

R4

C7

C2, C3

OVP

nDIM

LM3423

AGND

PGND

DDRV

DAP

GATE

EN

COMP

VIN

CSH

RCT

IS

HSP

RPD

VCC

HSN

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

FLT DPOL

9 12

TIMR LRDY

10 11

R2

C10

R14

V

IN

R15

V

IN

V

CC

V

CC

LED-

D1

TP1

Q3

PWM

R12

TP5

RPD

RPD

TP10

GND

J3

C1

R3

J1

J2

J5

LED+

J4

TP6

GND

Schematic for 551600305-002 REVA

2 Schematic for 551600305-002 REVA

www.ti.com

Figure 2. Board Schematic

2

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Page 3

www.ti.com

3 Pin Descriptions

LM3423 LM3421 Name Description Function

1 1 V

2 2 EN Enable

3 3 COMP Compensation

4 4 CSH Current Sense High

5 5 RCT Resistor Capacitor Timing

6 6 AGND Analog Ground provide ground return for CSH, COMP, RCT, and

7 7 OVP Over-Voltage Protection

8 8 nDIM from VINto program input under-voltage lockout

9 - FLT Fault Flag MosFET open drain output is high when a fault

10 - TIMR Fault Timer

11 - LRDY LED Ready Flag MosFET open drain output pulls down when the

12 - DPOL Dim Polarity channel MosFET or leave open when dimming with

13 9 DDRV Dim Gate Drive Output Connect to the gate of the dimming MosFET.

14 10 PGND Power Ground

15 11 GATE Main Gate Drive Output Connect to the gate of the main switching MosFET.

16 12 V

17 13 IS Main Switch Current Sense switch for R

18 14 RPD Resistor Pull Down (VINUVLO, OVP) to implement “zero-current”

19 15 HSP LED Current Sense Positive

20 16 HSN LED Current Sense Negative

DAP (21) DAP (17) DAP Thermal PAD on bottom of IC Star ground, connecting AGND and PGND.

Pin Descriptions

IN

Input Voltage

Dimming Input /

Under-Voltage Protection

CC

Internal Regulator Output

Bypass with 100 nF capacitor to AGND as close to

the device as possible in the circuit board layout.

Connect to AGND for zero current shutdown or

apply > 2.4V to enable device.

Connect a capacitor to AGND to set the

compensation.

Connect a resistor to AGND to set the signal current.

For analog dimming, connect a controlled current

source or a potentiometer to AGND as detailed in

the Analog Dimming section.

External RC network sets the predictive “off-time”

and thus the switching frequency.

Connect to PGND through the DAP copper pad to

TIMR.

Connect to a resistor divider from VOto program

output over-voltage lockout (OVLO). Turn-off

threshold is 1.24V and hysteresis for turn-on is

provided by 23 µA current source.

Connect a PWM signal for dimming as detailed in

the PWM Dimming section and/or a resistor divider

(UVLO). Turn-on threshold is 1.24V and hysteresis

for turn-off is provided by 23 µA current source.

Connect to pull-up resistor from VIN and N-channel

condition is latched by the timer.

Connect a capacitor to AGND to set the time delay

before a sensed fault condition is latched.

Connect to pull-up resistor from VIN and N-channel

LED current is not in regulation.

Connect to AGND if dimming with a series Pseries N-channel MosFET.

Connect to AGND through the DAP copper pad to

provide ground return for GATE and DDRV.

Bypass with 2.2 µF–3.3 µF ceramic capacitor to

PGND.

Connect to the drain of the main N-channel MosFET

sensing or to a sense resistor

installed in the source of the same device.

DS-ON

Connect the low side of all external resistor dividers

shutdown.

Connect through a series resistor to the positive side

of the LED current sense resistor.

Connect through a series resistor to the negative

side of the LED current sense resistor.

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

3

Page 4

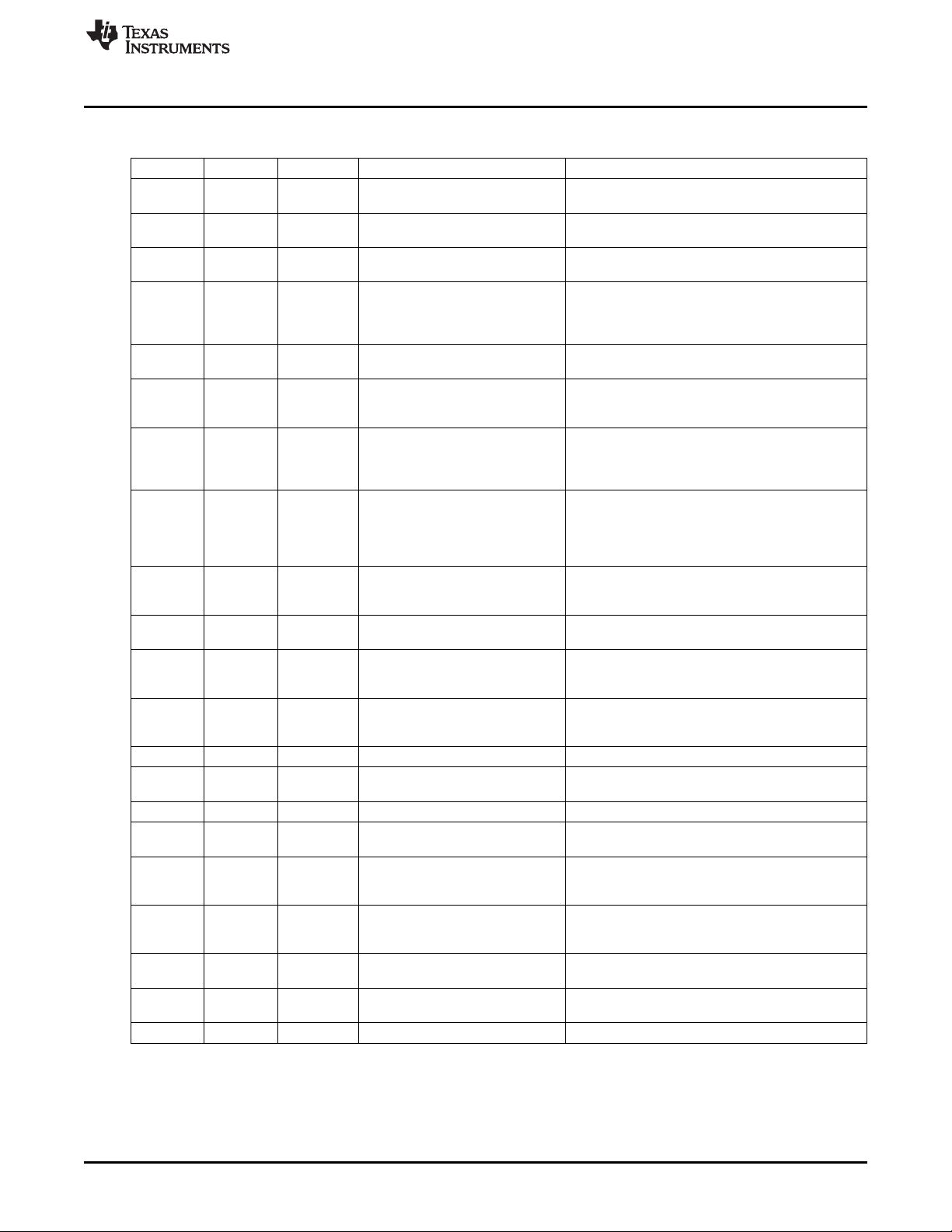

Bill of Materials for 551600305-002 REVA

4 Bill of Materials for 551600305-002 REVA

Qty Part ID Part Value Manufacturer Part Number

2 C1, C12 0.1 µF X7R 10% 50V TDK C1608X5R1H104K

2 C2, C8 1.0 µF X7R 10% 50V MURATA GRM21BR71H105KA12L KA01L

1 C3 68 µF 20% 100V UCC EMVY101ARA680MKE

1 C4 0.1 µF X7R 10% 100V TDK C2012X7R2A104M

4 C6(a-d) 10 µF X7R 10% 50V (4 TDK C5750X7R1H106

installed for a total of 40 µF)

1 C7 1000 pF X5R 5% 100V MURATA C2012X5R2E102K

1 C9 2.2 µF X7R 10% 16V MURATA GRM21BR71C225KA01L

1 C10 10 nF X7R 10% 50V PANASONIC ECJ2VB1H103 KA12L

1 C11 47 pF COG/NPO 5% 50V PANASONIC ECJ2VG1H470 KA01L

1 D1 Schottky 100V 12A (or 6A) VISHAY 12CWQ10FNPBF (or 6CWQ10FNPBF)

1 D2 Zener 10V ON-SEMI BZX84C10-V

4 J1, J2, J4, J5 banana jack KEYSTONE 575-8

1 J3 1x2 male header (with shunt SAMTEC TSW-102-07-T-S

tab)

1 L1 47 µH 20% 6.3A COILCRAFT MSS1260-473MLB

2 Q1, Q2 NMOS 150V 50A (or 100V INFINEON (or IPD200N15N3 (or FDD3682)

32A) FAIRCHILD)

2 Q3, Q7 NMOS 60V 260 mA ON-SEMI 2N7002ET1G

1 Q4 PNP 40V 200 mA FAIRCHILD MMBT3906

1 Q5 PNP 150V 600 mA FAIRCHILD MMBT5401

1 Q6 NPN 300V 500 mA FAIRCHILD MMBTA42

2 R1, R11 12.4 kΩ 1% VISHAY CRCW080512k4FKEA

1 R2 0Ω 1% VISHAY CRCW08050000Z0EA

2 R3, R20 10Ω 1% VISHAY CRCW080510R0FKEA

1 R4 16.9 kΩ 1% VISHAY CRCW080516k9FKEA

3 R5, R7, R8 1.40 kΩ 1% VISHAY CRCW08051k40FKEA

1 R6 0.06Ω 1% 1W VISHAY WSL2512R0600FEA

1 R9 0.2Ω 1% 1W PANASONIC ERJ12RSFR20U

1 R10 35.7 kΩ 1% VISHAY CRCW080535k7FKEA

3 R12, R13, R19 10.0 kΩ 1% VISHAY CRCW080510k0FKEA

3 R14, R15, R17 100 kΩ 1% VISHAY CRCW0805100kFKEA

1 R18 432 kΩ 1% VISHAY CRCW0805432kFKEA

5 TP1, TP5, TP6, turret KEYSTONE 1502-2

TP10

1 U1 Buck-boost controller TI LM3423

www.ti.com

4

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Page 5

www.ti.com

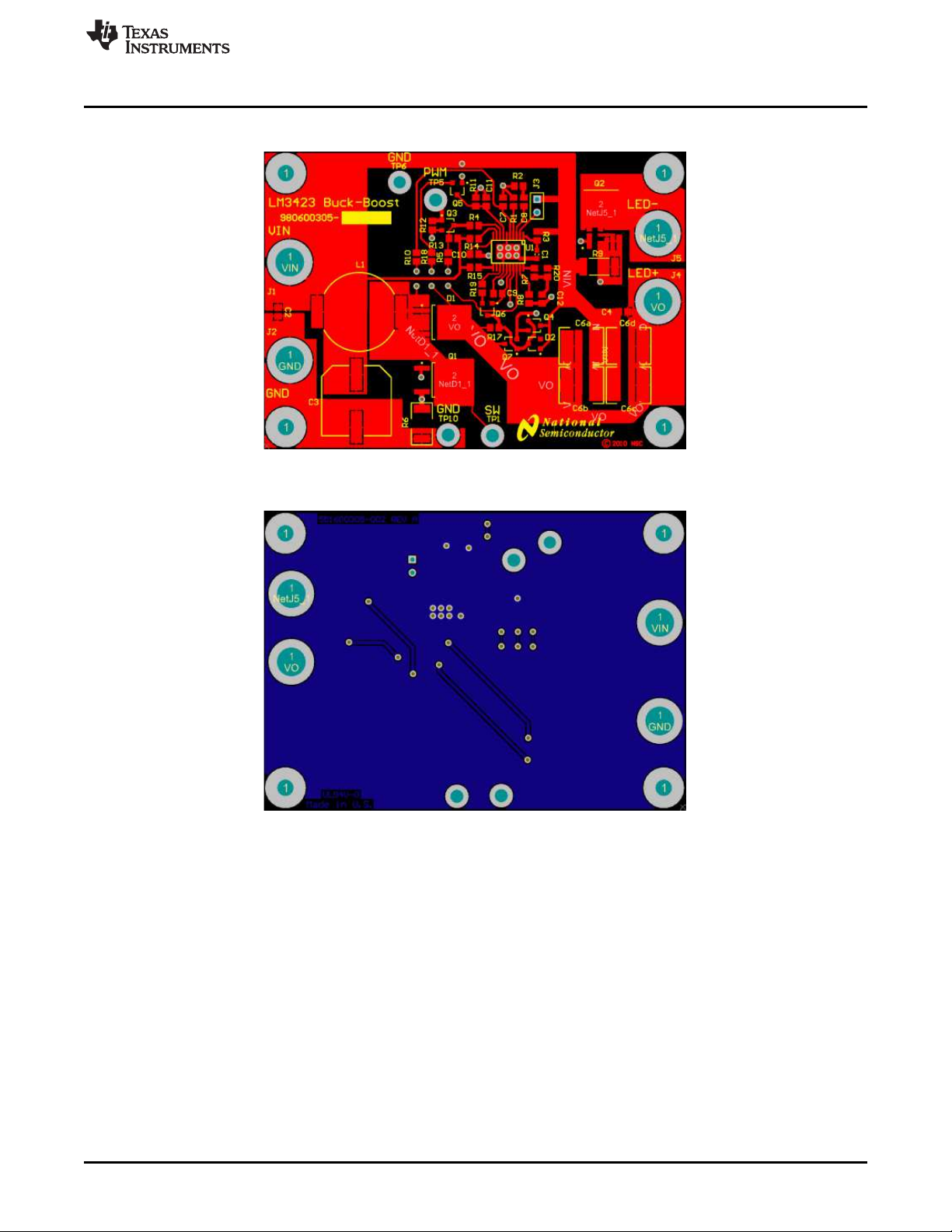

5 PCB Layout for 551600305-002 REVA

Figure 3. Top Layer

PCB Layout for 551600305-002 REVA

Figure 4. Bottom Layer

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

5

Page 6

2525

=

35.7 k: x 1 nF

fSW =

R10 x C7

= 700 kHz

2525

=

700 kHz x 1 nF

= 35.7 k:

R10 =

fSW x C7

21V

=

21V + 10V

= 0.677

D

MAX

=

VO + V

IN-MIN

V

O

21V

=

21V + 70V

= 0.231

D

MIN

=

VO + V

IN-MAX

V

O

D' = 1 - D = 1 - 0.467 = 0.533

D =

=

21V

VO + V

IN

21V + 24V

= 0.467

V

O

rD = N x r

LED

= 6 x 325 m: = 1.95:

VO = N x V

LED

= 6 x 3.5V = 21V

Design Procedure

6 Design Procedure

Refer to the LM3421/21Q1/21Q0 LM3423/23Q1/23Q0 N-Ch Controllers for Constant Current LED Drivers

(SNVS574 data sheet for design considerations.

6.1 Specifications

N = 6

V

= 3.5V

LED

r

= 325 mΩ

LED

VIN= 24V

V

= 10V; V

IN-MIN

fSW= 700 kHz

V

= 150 mV

SNS

I

= 700 mA

LED

Δi

= 350 mA

L-PP

Δi

Δv

I

LIM

V

V

LED-PP

IN-PP

= 4A

TURN-ON

TURN-OFF

= 50 mA

= 100 mV

IN-MAX

= 10V; V

=44V; V

HYS

HYSO

www.ti.com

= 70V

= 3.4V

= 10V

6.2 Operating Point

Solve for VOand rD:

Solve for D, D', D

MAX

, and D

6.3 Switching Frequency

Assume C7 = 1 nF and solve for R10:

The closest standard resistor is actually 35.7 kΩ therefore the fSWis:

MIN

(1)

(2)

:

(3)

(4)

(5)

(6)

(7)

6

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

(8)

Submit Documentation Feedback

Page 7

700 mA x 0.467

1.95: x 50 mA x 700 kHz

= 4.79 PF

CO =

CO =

rD x 'i

LED-PP

x f

SW

I

LED

x D

L1 = 47 PH

340 mA x 0.533

700 mA

I

L-RMS

=

I

LED

D'

I

L-RMS

=

700 mA

0.533

I

L-RMS

= 1.32A

I

LED

'I

L-PP

x D'

2

¸

¸

¹

·

¨

¨

©

§

¸

¸

¹

·

¨

¨

©

§

1 +

12

1

x

1 +

12

1

x

2

x

x

24V x 0.467

=

47 PH x 700 kHz

= 340 mA

'i

L-PP

=

L1 x f

SW

VIN x D

24V x 0.467

=

350 mA x 700 kHz

= 46 PH

L1 =

'i

L-PP

x f

SW

VIN x D

R8 = R7 = 1.4 k:

R1 = 12.4 k:

R9 = 0.2:

1.24V x 1.4 k:

=

= 700 mA

I

LED

=

1.24V x R8

R9 x R1

0.2: x 12.4 k:

30107716

700 mA x 12.4 k: x 0.2:

=

1.24V

= 1.4 k:

R8 =

I

LED

x R1 x R9

1.24V

30107715

150 mV

=

700 mA

= 0.214:

V

SNS

I

LED

C7 = 1 nF

R10 = 35.7 k:

www.ti.com

The chosen components from Section 6.3 are:

6.4 Average LED Current

Solve for R9:

Assume R1 = 12.4 kΩ and solve for R8:

The closest standard resistor for R9 is 0.2Ω and the closest for R8 (and R7) is actually 1.4 kΩ therefore

I

is:

LED

The chosen components from Section 6.4 are:

Design Procedure

(9)

(10)

(11)

(12)

(13)

6.5 Inductor Ripple Current

Solve for L1:

The closest standard inductor is 47 µH therefore the actual Δi

Determine minimum allowable RMS current rating:

The chosen component from Section 6.5 is:

6.6 Output Capacitance

L-PP

(14)

is:

(15)

(16)

(17)

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Solve for CO:

(18)

7

Copyright © 2010–2013, Texas Instruments Incorporated

Page 8

rad

sec

Z

P3

= 25k x 10 = 250k

Z

P3

= max (ZP1, ZZ1) x 10 = ZZ1 x 10

rad

sec

=

= 0.28 PF

C8 =

1

rad

sec

Z

P2

x 5e

6

:

1

0.709 x 5e

6

:

Z

P1

=

5 x 5360

= 0.709

Z

P2

=

5 x T

U0

min(ZP1, ZZ1)

rad

sec

=

5 x 5360

19k

rad

sec

0.533 x 620V

=

1.467 x 700 mA x 0.06:

= 5360

TU0 =

(1 + D) x I

LED

x R6

D' x 620V

1.95: x 0.533

2

=

0.467 x 47 PH

= 25k

Z

Z1

=

D x L1

rD x D'

2

rad

sec

1.467

=

1.95: x 40 PF

= 19k

Z

P1

=

rD x C

O

1 + D

rad

sec

R6 = 0.06:

=

0.06:

= 4.1A

I

LIM

=

R6

245 mV 245 mV

=

4A

= 0.061:

R6 =

I

LIM

245 mV 245 mV

C6 = 4 x 10 PF

1- 0.677

= 1.01A

1 - D

MAX

D

MAX

I

CO-RMS

= I

LED

x

= 700 mA x

0.677

700 mA x 0.467

1.95: x 40 PF x 700 kHz

= 6 mA

'i

LED-PP

=

rD x CO x f

SW

I

LED

x D

'i

LED-PP

=

Design Procedure

www.ti.com

A total value of 40 µF (using 4 10 µF X7R ceramic capacitors) is chosen therefore the actual Δi

Determine minimum allowable RMS current rating:

The chosen components from Section 6.6 are:

6.7 Peak Current lmit

Solve for R6:

The closest standard resistor is 0.06 Ω therefore I

The chosen component from Section 6.7 is:

LIM

is:

LED-PP

is:

(19)

(20)

(21)

(22)

(23)

6.8 Loop Compensation

ω

is approximated:

P1

ω

is approximated:

Z1

TU0is approximated:

To ensure stability, calculate ωP2:

Solve for C8:

To attenuate switching noise, calculate ωP3:

(24)

(25)

(26)

(27)

(28)

(29)

8

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

(30)

Submit Documentation Feedback

Page 9

PD = ID x VFD = 700 mA x 600 mV = 420 mW

I

D-MAX

= I

LED

= 700 mA

V

RD-MAX

= V

IN-MAX

+ VO = 70V + 21V = 91V

Q1 o 40A, 100V, DPAK

PT = I

T-RMS

2

x R

DSON

= 897 mA2 x 50 m: = 40 mW

x

x

700 mA

D =

0.533

I

T-RMS

=

I

LED

D'

0.467 = 897 mA

0.677

1 - 0.677

x 700 mA = 1.46A

I

T-MAX

=

V

T-MAX

= V

IN-MAX

+ VO = 70V + 21V = 91V

C3 = 68 PF

1- 0.677

= 1.01A

1 - D

MAX

D

MAX

I

CO-RMS

= I

LED

x

= 700 mA x

0.677

700 mA x 0.467

=

100 mV x 700 kHz

= 4.67 PF

CIN =

'V

IN-PP

x f

SW

I

LED

x D

C8 = 1.0 PF

R20 = 10:

C12 = 0.1 PF

=

= 0.4 PF

C12 =

1

rad

sec

1

10: x 250k

10: x Z

P3

www.ti.com

Assume R20 = 10Ω and solve for C12:

Since PWM dimming can be evaluated with this board, a much larger compensation capacitor C8 = 1.0 µF

is chosen and a smaller high frequency capacitor C12 = 0.1 µF is chosen.

The chosen components from Section 6.8 are:

6.9 Input Capacitance

Solve for the minimum CIN:

To minimize power supply interaction a much larger capacitance of 68 µF is used, therefore the actual

Δv

Determine minimum allowable RMS current rating:

is much lower.

IN-PP

Design Procedure

(31)

(32)

(33)

The chosen components from Section 6.9 are:

6.10 NFET

Determine minimum Q1 voltage rating and current rating:

A 100V NFET is chosen with a current rating of 40A due to the low R

PT:

The chosen component from Section 6.10 is:

6.11 DIODE

Determine minimum D1 voltage rating and current rating:

= 50 mΩ. Determine I

DS-ON

T-RMS

(34)

(35)

(36)

(37)

and

(38)

(39)

(40)

A 100V diode is chosen with a current rating of 12A and VD= 600 mV. Determine PD:

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

(41)

(42)

(43)

9

Copyright © 2010–2013, Texas Instruments Incorporated

Page 10

V

TURN-OFF

=

R11

1.24V x (0.5 x 12.4 k: + 432 k:)

12.4 k:

1.24V x (R11 + R18)

= 44V

V

TURN-OFF

=

1.24V x R18

V

TURN-OFF

± 620 mV

= 12.3 k:

R11 = =

1.24V x 432 k:

44V ± 620 mV

V

HYSO

= R18 x 23 PA = 432 k: x 23 PA = 9.9V

V

HYSO

23 PA

= 435 k:

R18 =

10V

=

23 PA

R4 = 16.9 k:

R13 = 10 k:

R5 = 1.4 k:

HYS

=

R5

23 PA x 16.9 k: x (1.4 k: + 10 k:)

1.4 k:

HYS

=

+ 23 PA x R13

23 PA x R4 x (R5 + R13)

+ 23 PA x 10 k: = 3.4V

R4 =

R5 x (V

HYS

- 23 PA x R13)

23 PA x (R5 + R13)

= 16.9 k:

R4 =

1.4 k: x (3.4V - 23 PA x 10 k:)

23 PA x (1.4 k: + 10 k:)

V

TURN-ON

=

R5

1.24V x (1.4 k: + 10 k:)

1.4 k:

1.24V x (R5 + R13)

= 10.1V

V

TURN-ON

=

1.24V x R13

V

TURN-ON

- 1.24V

= 1.42 k:

R5 = =

1.24V x 10 k:

10V - 1.24V

D1 o 12A, 100V, DPAK

Design Procedure

The chosen component from Section 6.11 is:

6.12 Input UVLO

Since PWM dimming will be evaluated, a three resistor network will be used. Assume R13 = 10 kΩ and

solve for R5:

The closest standard resistor is 1.4 kΩ therefore V

Solve for R4:

The closest standard resistor is 16.9 kΩ making V

TURN-ON

:

HYS

www.ti.com

(44)

(45)

is:

(46)

(47)

The chosen components from Section 6.12 are:

6.13 Output OVLO

Solve for R18:

The closest standard resistor is 432 kΩ therefore V

Solve for R11:

The closest standard resistor is 12.4 kΩ making V

HYSO

TURN-OFF

(48)

(49)

(50)

is:

(51)

(52)

:

10

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

(53)

Submit Documentation Feedback

Page 11

R11 = 12.4 k:

R18 = 432 k:

www.ti.com

The chosen components from Section 6.13 are:

6.14 PWM Dimming

The LM3423 Buck-boost Evaluation board is configured to demonstrate PWM dimming of the LEDs. For

best operation, use a PWM signal that has greater than 3V amplitude at a frequency between 120Hz and

5kHz. Apply the PWM signal to the BNC connector (J6) and the inverted signal (seen by the nDIM pin)

can be monitored at TP5.

The output PWM drive signal (DDRV) is level shifted to the floating LED stack using several components

(R19, R17, Q4, Q6, Q7, and D2) and ultimately controls the series dimming FET (Q2). This level shift

adds a several microsecond delay from input to output as seen in the Typical Waveforms section. This

delay, along with the time it takes to slew the LED current from zero to its nominal value, limits the

contrast ratio for a given dimming frequency.

Using the evaluation board (24V input, 21V output), at 5kHz dimming frequency the best case contrast

ratio is approximately 40:1, but at 200Hz the same system is more like 1000:1 ratio. In general, contrast

ratios much above 2000:1 are not possible for any operating point using the LM3423 buck-boost

evaluation board.

6.15 Fault and LED Current Monitoring

The LM3423 has a fault detection flag in the form of an open-drain NFET at the FLT pin. Using the

external pull-up resistor (R14) to VIN, the fault status can be monitored at the FLT pin (high = fault). The

fault timer interval is set with the capacitor (C10) from TIMR to GND (10nF yields roughly 1ms). If a fault is

detected that exceeds the programmed timer interval, such as an output over-voltage condition, the FLT

pin transitions from high to low and internally GATE and DDRV are latched off. To reset the device once

the fault is removed, either the input power must be cycled or the EN pin must be toggled.

This can be tested directly with the evaluation board by opening the LED load. An OVP fault will occur

which disables GATE and DDRV. Then if the LEDs are reconnected, the EN pin jumper (J3) can be

removed and reinserted to restart normal operation of the LM3423.

The LED status flag (LRDY) can be seen by monitoring TP4. LRDY is also an open-drain NFET

connection which has an external pull-up resistor (R15) to VIN. If the LED current is in regulation the

voltage at TP4 will be high, but when it falls out of regulation the NFET turns on and pulls TP4 low. The

LM3423 datasheet lists all of the conditions that affect LRDY, FLT, and TIMR.

Design Procedure

(54)

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

11

Page 12

I

LED

(A)

V

DIM

(V)

400 és/DIV

V

DIM

4

2

0

0.0

0.5

1.0

I

LED

I

LED

(A)

V

DIM

(V)

2 és/DIV

V

DIM

4

2

0

0.0

0.5

1.0

I

LED

Typical Waveforms

7 Typical Waveforms

TA= +25°C, VIN= 24V and VO= 21V.

Figure 5. 1kHz 50% PWM DIMMING Figure 6. 1kHz 50% PWM DIMMING (Rising Edge)

TP5 dim voltage (V

LED current (I

) TP5 dim voltage (V

DIM

) LED current (I

LED

LED

)

DIM

www.ti.com

)

12

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Page 13

C4, C6

Q1

R18

R11

R9

R20

C12

C11

Q5

V

IN

Q7

Q6

Q4

D2

DIM

R17

R19

DIM

Q2

V

IN

L1

C9

R6

C8

R1

R10

R13

R5

R8

R7

R4

C7

C2, C3

OVP

nDIM

LM3423

AGND

PGND

DDRV

DAP

GATE

EN

COMP

VIN

CSH

RCT

IS

HSP

RPD

VCC

HSN

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

FLT DPOL

9 12

TIMR LRDY

10 11

R2

C10

R14

V

IN

R15

V

IN

V

CC

V

CC

LED-

8

9

10

12

13

14

7

6

5

3

2

1

J7

11 4

D1

LED+

TP1

Q3

PWM

R12

BNC

TP5

TP7

RPD

RPD

TP4

TP10

J3

R16

C5

C1

R3

J1

J2

J4

J5

J6

www.ti.com

8 Schematic for 551600305-001 REV1

Schematic for 551600305-001 REV1

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

13

Page 14

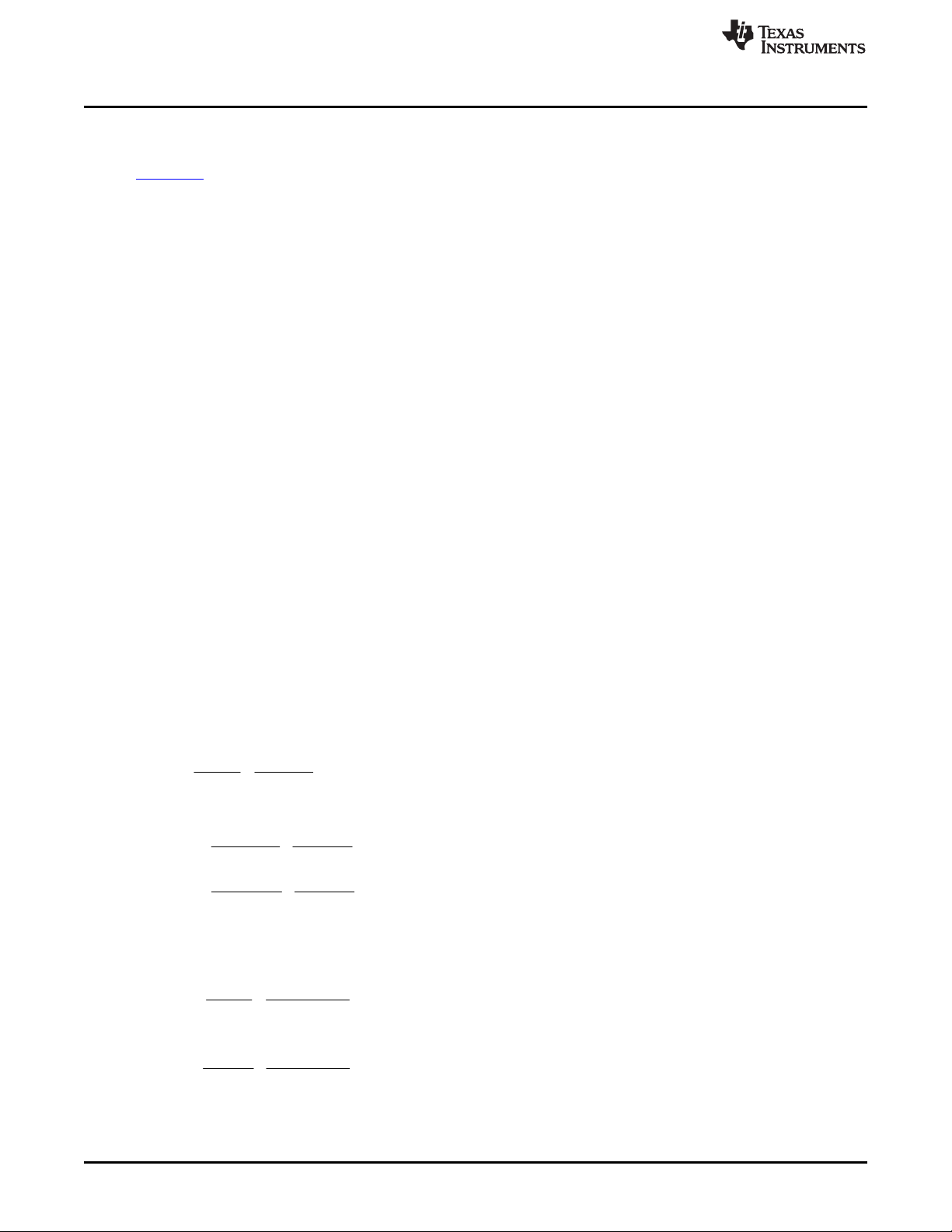

PCB Layout for 551600305-001 REV1

9 PCB Layout for 551600305-001 REV1

Figure 7. Top Layer

www.ti.com

14

Figure 8. Bottom Layer

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Page 15

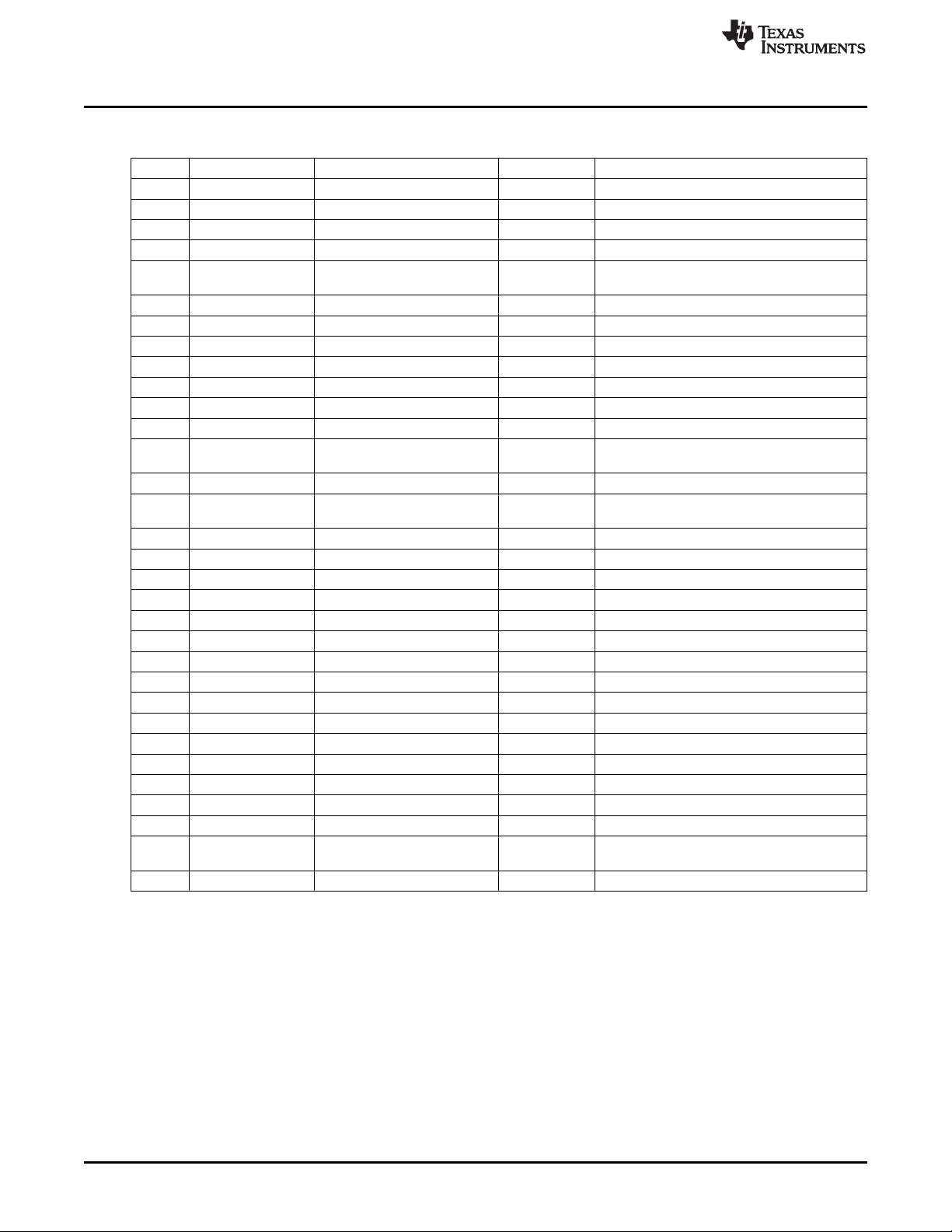

www.ti.com

10 Bill of Materials for 551600305-001 REV1

Qty Part ID Part Value Manufacturer Part Number

2 C1, C12 0.1 µF X7R 10% 50V TDK C1608X5R1H104K

2 C2, C8 1.0 µF X7R 10% 50V MURATA GRM21BR71H105KA12L KA01L

1 C3 68 µF 20% 100V UCC EMVY101ARA680MKE

1 C4 0.1 µF X7R 10% 100V TDK C2012X7R2A104M

1 C5 DNP

4 C6 10 µF X7R 10% 50V (4 installed TDK C5750X7R1H106

for a total of 40 µF)

1 C7 1000 pF X5R 5% 100V MURATA C2012X5R2E102K

1 C9 2.2 µF X7R 10% 16V MURATA GRM21BR71C225KA01L

1 C10 10 nF X7R 10% 50V PANASONIC ECJ2VB1H103 KA12L

1 C11 47 pF COG/NPO 5% 50V PANASONIC ECJ2VG1H470 KA01L

1 D1 Schottky 100V 7A VISHAY 6CWQ10FNPBF

1 D2 Zener 10V ON-SEMI BZX84C10-V

4 J1, J2, J4, J5 banana jack KEYSTONE 575-8

1 J3 1x2 male header (with shunt tab) SAMTEC TSW-102-07-T-S

1 J6 BNC connector AMPHENOL 112536

1 J7 DNP

1 L1 47 µH 20% 6.3A COILCRAFT MSS1260-473MLB

2 Q1, Q2 NMOS 100V 40A VISHAY SUD40N10-25

2 Q3, Q7 NMOS 60V 260 mA ON-SEMI 2N7002ET1G

1 Q4 PNP 40V 200 mA FAIRCHILD MMBT3906

1 Q5 PNP 150V 600 mA FAIRCHILD MMBT5401

1 Q6 NPN 300V 500 mA FAIRCHILD MMBTA42

2 R1, R11 12.4 kΩ 1% VISHAY CRCW080512k4FKEA

1 R2 0Ω 1% VISHAY CRCW08050000Z0EA

2 R3, R20 10Ω 1% VISHAY CRCW080510R0FKEA

1 R4 16.9 kΩ 1% VISHAY CRCW080516k9FKEA

3 R5, R7, R8 1.40 kΩ 1% VISHAY CRCW08051k40FKEA

1 R6 0.06Ω 1% 1W VISHAY WSL2512R0600FEA

1 R9 0.2Ω 1% 1W PANASONIC ERJ12RSFR20U

1 R10 35.7 kΩ 1% VISHAY CRCW080535k7FKEA

3 R12, R13, R19 10.0 kΩ 1% VISHAY CRCW080510k0FKEA

3 R14, R15, R17 100 kΩ 1% VISHAY CRCW0805100kFKEA

1 R16 DNP

1 R18 432 kΩ 1% VISHAY CRCW0805432kFKEA

5 TP1, TP4, TP5, turret KEYSTONE 1502-2

TP7, TP10

1 U1 Buck-boost controller TI LM3423

Bill of Materials for 551600305-001 REV1

SNVA415C–June 2010–Revised May 2013 AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

15

Page 16

Alternate Designs

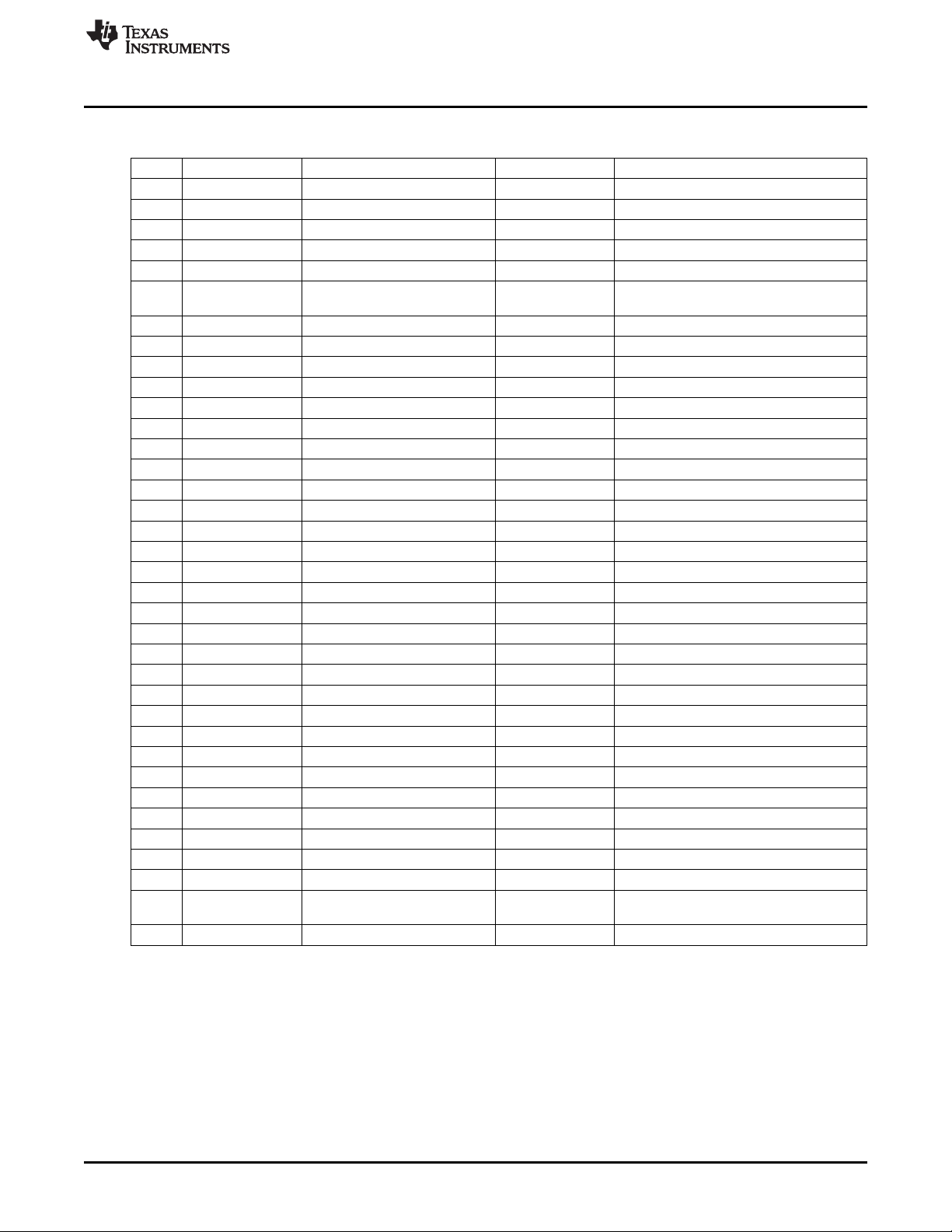

11 Alternate Designs

Alternate designs with the LM3423 evaluation board are possible with very few changes to the existing

hardware. The evaluation board FETs and diodes are already rated higher than necessary for design

flexibility. The input UVLO, output OVP, input and output capacitance can remain the same for the designs

shown below. These alternate designs can be evaluated by changing only R9, R10, and L1.

Table 1 gives the main specifications for four different designs and the corresponding values for R9, R10,

and L1. PWM dimming can be evaluated with any of these designs.

Specification / Design 1 Design 2 Design 3 Design 4

Component

V

IN

V

O

f

SW

I

LED

R9 0.05Ω 0.2Ω 0.04Ω 0.08Ω

R10 41.2 kΩ 35.7 kΩ 49.9 kΩ 35.7 kΩ

L1 22µH 68µH 15µH 33µH

www.ti.com

Table 1. Alternate Designs Specifications

10V - 45V 15V - 50V 20V - 55V 25V - 60V

14V 21V 28V 35V

600kHz 700kHz 500kHz 700kHz

2A 500mA 2.5A 1.25A

16

AN-2010 LM3423 Buck-Boost 2 Layer Evaluation Board SNVA415C–June 2010–Revised May 2013

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Page 17

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other

changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest

issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All semiconductor products (also referred to herein as “components”) are sold subject to TI’s terms and conditions of sale

supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms

and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary

to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily

performed.

TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information

published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration

and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered

documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service

voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice.

TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which

anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause

harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use

of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components

which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and

regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive

Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications

Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers

DLP® Products www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP dsp.ti.com Energy and Lighting www.ti.com/energy

Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2013, Texas Instruments Incorporated

Loading...

Loading...