10/96

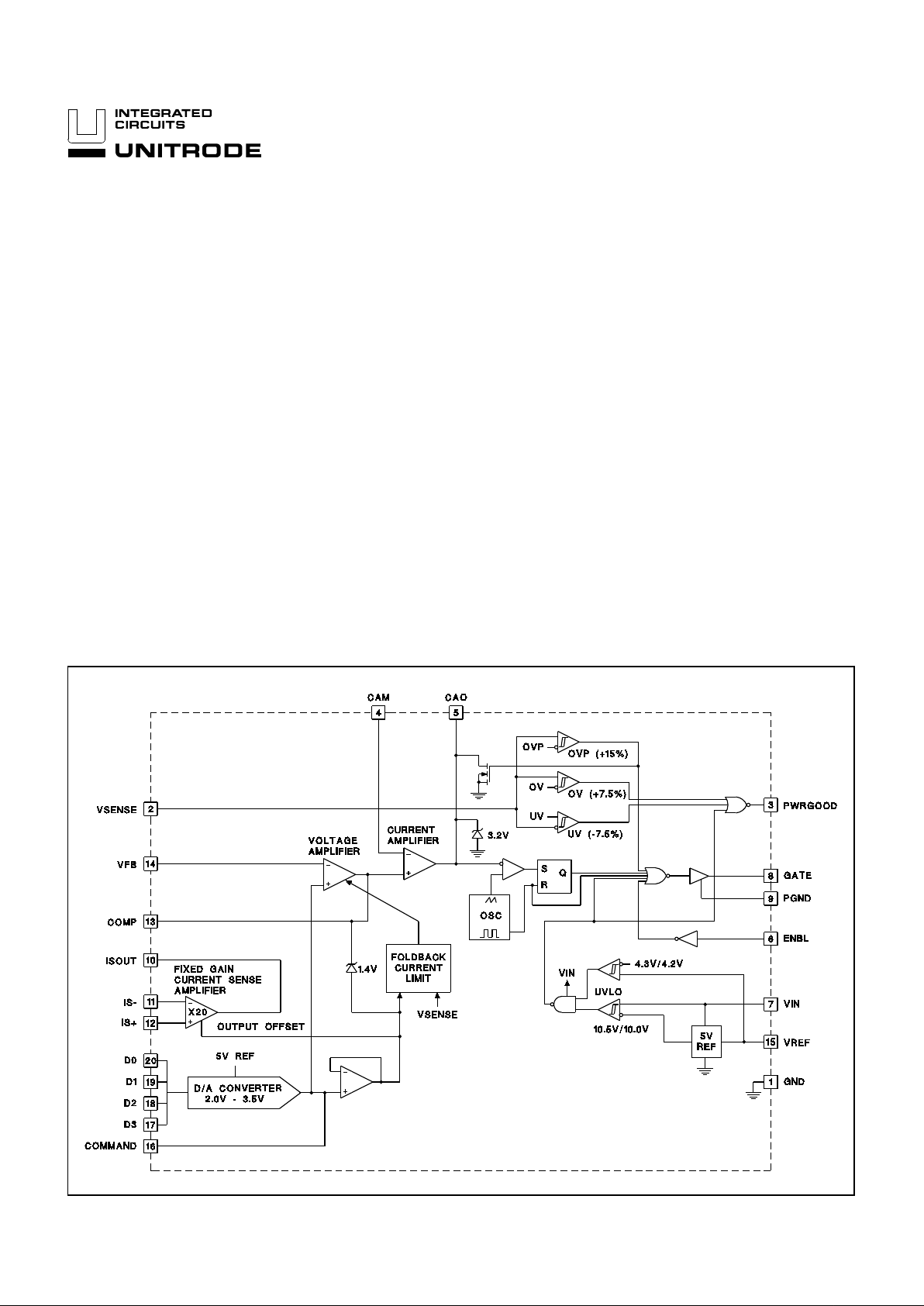

BLOCK DIAGRAM

• Combined DAC/Voltage

Monitor and PWM Functions

• 4-Bit Digital-to-Analog

Converter (DAC)

• 1.0% DAC/Reference

• Low Offset X20 Current Sense

Amplifier

• 100kHz, 200kHz, 400kHz

Oscillator Frequency Options

• Foldback Current Limiting

• Overvoltage and Undervoltage

Fault Windows

• Undervoltage Lockout

• 2Ω Totem Pole Output

• Chip Disable Function

Pentium® Pro Controller

FEATURES DESCRIPTI ON

UDG-96106-1

UCC2880-4/-5/-6

UCC3880-4/-5/-6

PRELIMINARY

The UCC3880-4/-5/-6 combines high precision reference and voltage monitoring circuitry with average current mode PWM controller circuitry to power Intel

Pentium Pro and other high-end microprocessors with a minimum of external

components. The UCC3880-x converts 5VDC to an adjustable output, ranging

from 2.0VDC to 3.5VDC in 100mV steps with 1% DC system accuracy.

The chip incl udes a precision 5V reference which is capable of sourcing current to an external load. The output voltage of the DAC is derived from this

reference, and is programmed directly by Intel’ s VID pins (Table 1).

The accuracy of the DAC/reference combination is 1.0%. The overvoltage and

undervoltage comparators monitor the system output voltage and indicate

when it rises above or falls below its programmed value by more than 7.5%. A

second overvoltage protection comparator pulls the current amplifier output

voltage low to force zero duty cycle w hen the system output voltage exceeds

its designed value by more than 15%. This comparator also terminates the cycle. Undervoltage lockout circuitry assures the correct logic states at the outputs during powerup and powe rdown . Grounding the ENABLE pin forces the

GATE output low.

(continued)

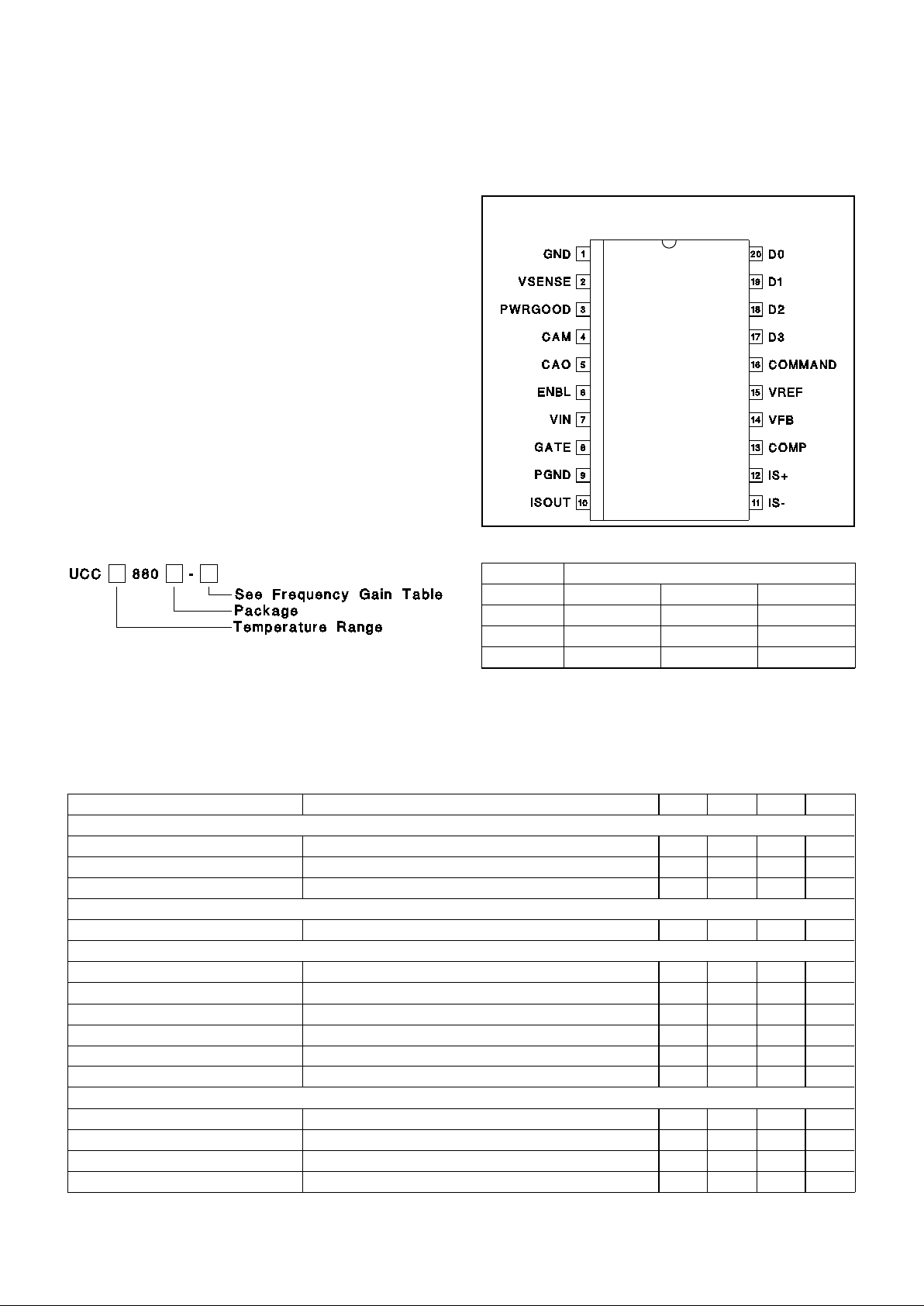

UCC2880-4/-5/-6

UCC3880-4/-5/-6

CONNECTION DIAG RAM

SOIC-20 (Top View)

DW Package

ELECTRICAL CHARACTE RIST I CS:

Unless otherwise specified, VIN = 12V, VSENSE = 3.5V, VENBL = 5V, VD0 = VD1 = VD2

= VD3 = 0V, 0°C < T

A < 70°C, TA = TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Undervol ta ge Lockout

VIN UVLO Turn-on Thr esh old 10.5 10. 8 V

VIN UVLO Turn-off Threshold 9.5 10 V

UVLO Threshold Hysteresis 500 mV

Supply Cur ren t

l

IN 3.5 mA

DAC/Reference

COMMAND Voltage Accu rac y 10.8V < VIN < 13.2V, I

VREF = 0mA –1 1 %

D0-D3 Voltage High DX Pin Floating 5 V

D0-D3 Input Bias Curre nt DX Pin Tied to GND –70 –20 µA

VREF Output Voltage 4.975 5 5.025 V

VREF Load Regulat io n I

VREF = 0mA to 5mA –10 0 mV

VREF Sourcing Current VREF = 0V 10 mA

OVP Comparator

Trip Point % Over COMMAND Volt age 10 15 20 %

Hystere s is 20 30 mV

VSENSE Input Bias Current OV, OVP, UV Combined –0.1 µA

Propagation Delay 1 µs

The voltage and current amplifiers have a 4MHz gain

bandwidth p roduct to satisfy high performance system requirements. The internal current sense amplifier permits

the use of a low val ue current sense resistor, minimizing

power loss. The oscillator frequency is fixed internally at

100kHz, 200kHz, or 400kHz, depending upon the option

selected. The foldback circuit reduces the converter short

circuit current limit to 50% of its nominal value when the

converter is short circuited. The gate driver is a 2Ω totem

pole output stage capable of driving an external MOSFET.

This device is available in 20-pin dual i n-line and surface

mount packa ges. The UCC2880-x is specifie d for operation from –25°C to 85°C, and the UCC3880-x is specified

for operation from 0°C to 70°C.

Pentium® Pro is a registered trademark of Intel Corporation.

DESCRIPTION (cont. )

Frequency

100kHz 200kHz 400kHz

UCC3880-4 X

UCC3880-5 X

UCC3880-6 X

Frequency Gain Table

ORDERING INFORMATION

Consult factory f or temper at ure ran ge or package opt ions

not shown.

2

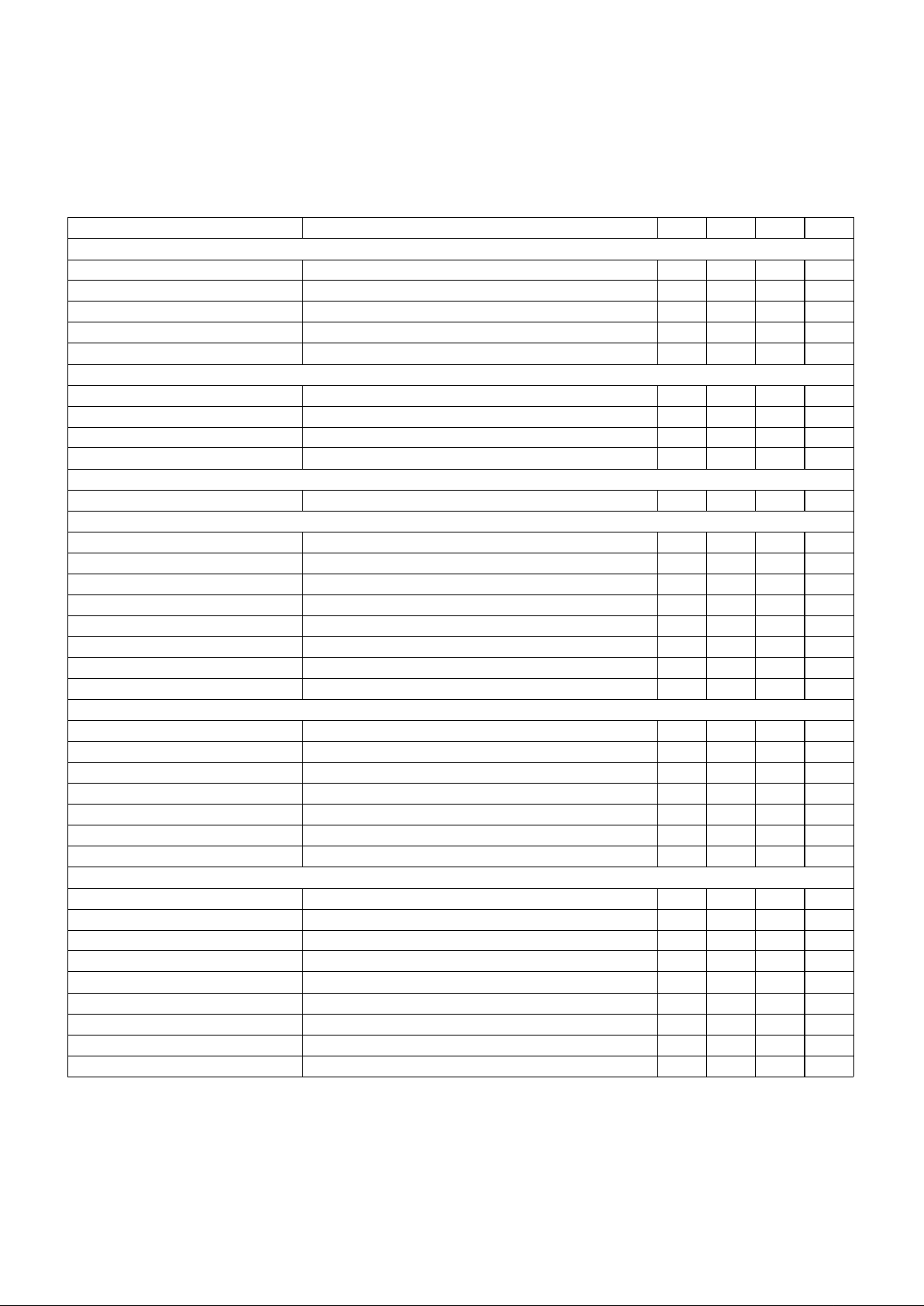

ELECTRICAL CHARACTE RISTICS (cont.): Unless otherw ise specified, VIN = 12V, VSENSE = 3.5V, VENBL = 5V, VD0 =

VD1 = VD2 = VD3 = 0V, 0°C < T

A < 70°C, TA = TJ.

PARAMETER TEST CONDIT IONS MI N TYP MAX UNIT S

OV Comparator

Trip Point % Over COMMAND Voltage ( Not e 1) 7.6 10 %

Return Point % Over COMMAND Voltage ( Not e 1) 5 7.4 %

Hystere sis 20 30 mV

PWRGOOD Equiva lent Resist ance VSENSE = 2.0V 470 Ω

Propagation Delay 1 µs

UV Comparator

Trip Point % Over COMMAND Voltage ( Not e 1) –10 –7.6 %

Return Point % Over COMMAND Voltage ( Not e 1) –7.4 – 5 %

Hystere sis 20 30 mV

Propagation Delay 1 µs

Enable Pi n

Pull-up Cur ren t V

ENBL = 2.5V –50 –20 µA

Voltage Error Amplifier

Input Offset Voltage V

COMP = 3.5V 0.0 mV

Input Bias Current V

CM = 3.0V –0.0 2 0 µA

Open Loo p Ga in 1V < V

COMP < 4V 90 dB

Common Mode Rejection Rat i o 2V < V

COMP < 3.5V 90 dB

Power Supply Reject ion Rat i o 10.8V < VIN < 15 V 85 dB

Output Sourcing Current V

VFB = 2V, VCOMMAND = VCOMP = 2.5V –0.5 mA

Output Sinking Current V

VFB = 3V, VCOMMAND = VCOMP = 2.5V 2.0 mA

Gain Bandwidth Product F = 100kHz 3 MHz

Current Sense Amplifier

Gain 20 V/V

Input Resistance 5kΩ

Common Mode Rejection Rat i o 0V < V

CM < 4.5V 60 dB

Power Supply Reject ion Rat i o 10.8V < VIN < 15 V 80 dB

Output Sourcing Current V

IS– = 2V, VISOUT = VIS+ = 2.5V –0.5 mA

Output Sinking Current V

IS– = 3V, VISOUT = VIS+ = 2.5V 6.0 mA

–3dB Freque ncy At GAIN = 20 1.75 MHz

Current Amplifier

Input Offset Voltage V

CM = 3.0V 10 mV

Input Bias Current V

CM = 3.0V 0.15 µA

Open Loo p Ga in 1V < V

CAO < 3V 90 dB

Output Voltage High VCOMP = 3V, VCAM = 2.5V 3.2 V

Common Mode Rejection Rat i o 1.5V < V

CM < 4.9V 80 dB

Power Supply Reject ion Rat i o 10.8V < VIN < 15 V 80 dB

Output Sourcing Current V

CAM = 2V, VCAO = VCOMP = 2.5V –0.5 mA

Output Sinking Current V

CAM = 3V, VCAO = VCOMP = 2.5V 2.0 mA

Gain Bandwidth Product F = 100kHz 3.5 MHz

UCC2880-4/-5/-6

UCC3880-4/-5/-6

3

UCC2880-4/-5/-6

UCC3880-4/-5/-6

PIN DESCRIPTIONS (cont.)

CAM (Current Amplifier Inverting Input): The average

load current feedback from ISOUT is applied through a

resistor to thi s pin. The current loop compensation network is also connected to this pin (see CAO below).

CAO (Current Amplifier Outp u t): The current loop compensation network is connected between this pin and

CAM. The voltage on this pin is the input to the PWM

comparator and regulates the o utput voltage o f the system. The GATE output is disabl ed (held low) unless the

voltage on this pin exceeds 1V, allowing the PWM to

force zero duty cycle when necessary. The PWM forces

maximum duty cycle when the voltage on CAO exceeds

the oscillator peak voltage (3V). A 3.2V clamp circuit prevents the CAO voltage from rising excessively past the

oscillator peak voltage for excellent transient response.

COMMAND (Digital-to-Analog Converter Output Voltage): This pin is the output of the 4-bit digital-to-analog

converter (DAC) and the noninverting input of the voltage

amplifier. The voltage on this pin sets the switching regulator output voltage. Setting all input control codes low

produces 3.5V at COMMAND; setting all codes high produces 2.0V at COMMAND. The DAC LSB step size (i.e.

resolution) is 100mV (See Table 1). The COMMAND

source impedance is typicall y 1.2kΩ and must therefore

drive only high impedance inputs if accuracy is to be

maintained. Bypass COMMAND with a 0.01µF, low ESR,

low ESL capacitor for best circuit noise immunity.

COMP (Voltage Amplifier Output): The system voltage

compensation network is applied between COMP and

VFB.

D0 - D3 (DAC Digital Input Control Codes): These are

the DAC digital input control codes, with D0 representing

the least significant bit (LSB) and D3, the most significant

bit (MSB). A bit is set low by being connected to GND. A

ELECTRICAL CHARACTE RISTICS (cont.):

Unless otherwise specified, VIN = 12V, VSENSE = 3.5V, V ENBL = 5V, VD0 =

VD1 = VD2 = VD3 = 0V, 0°C < T

A < 70°C, TA = TJ.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Oscillator

Frequenc y (-4) 85 100 115 kHz

Frequenc y (-5) 200 kHz

Frequenc y (-6) 400 kHz

Frequenc y Change Wit h Voltage 10. 8V < VIN < 15V 1 %

Output Secti on

Maximum Duty Cycle 90 95 99 %

Output Low Voltage I

GATE = –100mA 0.20 V

Output High Voltage IGATE = 100mA 11.8 V

Rise Time C

GATE = 3.3nF 20 80 ns

Fall Time C

GATE = 3.3nF 15 80 ns

Output Impedance I

GATE = 100mA 2 Ω

I

GATE = –100mA 2 Ω

Foldback Curr ent Li mit

Clamp Level Measured at Voltage EA Output;

V

SENSE = VCOMMAND = 3V

4.4 V

V

COMMAND = 3V, VSENSE = 0 3.7 V

Note 1: This percenta ge is me asur ed wit h respect to the ideal CO MM AND volt age program med by the D0 - D3 pins.

Decimal

Code

D3 D2 D1 D0 COMMAND

Voltage

151111 2.0

141110 2.1

131101 2.2

121100 2.3

111011 2.4

101010 2.5

91001 2.6

81000 2.7

70111 2.8

60110 2.9

50101 3.0

40100 3.1

30011 3.2

20010 3.3

10001 3.4

00000 3.5

Table 1. Programming the COMMAND Voltage

4

UCC2880-4/-5/-6

UCC3880-4/-5/-6

PIN DESCRIPTIONS (cont.)

bit is set high by floating it, or connecting it to a 5V

source. Each control pin is pulled up to approximately 5V

by an internal 70µA current source.

ENBL (Chip Enable Pin): This input is used to disable

the GATE and PWRGOOD outputs. Grounding this pin

causes the GATE output to be held low; floating the pin or

pulling it up to 5V ensures normal operation. ENBL is

pulled up to 5V internally.

GATE (PWM Output, MOSFET Driver): This output provides a 2Ω totem pole driver. Use a series resistor of at

least 5Ω between this pin and the gate of the external

MOSFET to prevent excessive overshoot.

GND (Signal Ground): All voltages are mea sured with

respect to GND. Bypass capacitors on the VCC and

VREF pins should be connected directly to the ground

plane near the GND pin.

IS– (Current Sense Amplifier Inverting Input): This pin

is the inverting input to the current sense amplifier and is

connected to the low side of the average current sense

resistor.

IS+ (Current Sense Amplifier Noninverting Input):

This pin is the noninverting input to the current sense amplifier and is con nected to the high side of the average

current sense resistor.

ISOUT (Current Sense Amplifier Output): This pin is

the output of the current sense amplifier. The voltage on

this pin is (COMMAND + G

CSA • I • RSENSE), where

COMMAND is the voltage on the COMMAND pin, G

CSA

is the fixed gain of the current sense amplifier, equal to

20, I

is the current through the sense resistor, and

R

SENSE is the value of the average current sensing resis-

tor.

PGND (Power Ground): This pin provides a dedicated

ground for the o utput gate driver. The GND and PGND

pins should be connected externally using a short printed

circuit board trace close to the IC. Decouple VIN to

PGND with a low ESR capacitor ≥ 0.10µF.

PWRGOOD (Undervoltage/Lower Overvoltage Output): This pin is an open drain output which is driven low

to reset the microprocessor when VSENSE rises above

or falls below its nominal value by 7.5%. The on resistance of the open drain switch will be no higher than

470Ω. The OV and UV comparators’ hysteresis is fixed at

20mV independent of the COMMAND voltage.

VIN (Positive Supply Voltage): This p in supplies power

to the chip. Connect VIN to a stable voltage source of at

least 10.8V. The GATE and P WRGOOD outputs will be

held low until VCC exceeds the upper undervoltage lockout threshold. This pin should be bypassed directly to the

GND pin.

VFB (Voltage Amplifier Inverting Input): This input is

connected to COMP through a feedback network and to

the power supply output through a resistor or a divider

network.

VREF (Voltage Reference Output): This pin provides an

accurate 5V reference and is internally short circuit current limited. VREF powers the D/A converter and also

provides a threshold voltage for the UVLO comparator.

For best reference stability , bypass VREF directly to GND

with a low ESR, low ESL capacit or of at least 0.01µF.

VSENSE (Output Voltage Sensing Input): This pin is

connected to the system output voltage through a low

pass filter. When the voltage on VSENSE rises above or

falls below the COMMAND voltage by 7.5%, the

PWRGOOD output is driven low to reset the microprocessor. When the voltage on VSENSE rises above the

COMMAND voltage by 15 %, the OVP comparator pulls

the current amplifier output voltage below the oscillator

valley voltage to force zero duty cycle at the GATE output. This pin is also used by the foldback current limiting

circuitry.

Current Limit

The short circuit current limit, I

SC, is set according to:

I

SC =

1.4V

R

SENSE • GCSA

where RSENSE is the average current sense resistor and

G

CSA is the current sense amplifier gain, where GCSA

equals 20. Example: Choose RSENSE to set the short circuit current limit at 16A using the UCC3880-5

R

SENSE =

1.4V

16A • 20

= 4.4mΩ

A lower resistance value may be needed if the AC ripple

current in the inductor is more than 20% of the full load

current.

Related Publication s

U-156 and U-157 are Unitrode Application Notes describing the operation of the UC3886 and the UC3886/

UC3910 together in a Pentium® Pro application.

APPLICATION INFORMATION

5

UCC3880 Configured for Powering the Pentium® Pro

TYPICAL APPLICATION

The UCC3 880-x is ideal for converting the 5.0V system bus i nto the required Pentium® Pro bus voltage.

UDG-96224

UCC2880-4/-5/-6

UCC3880-4/-5/-6

6

UNITRODE INTEGRA TED CIRCUITS

7 CONTINENTA L BLVD. • MERRIMACK, NH 03054

TEL. (603) 424-2410 • FAX (603) 424-3460

Pentium® Pro is a register ed tra dem ark of Intel Corpor at ion.

UCC2880-4/-5/-6

UCC3880-4/-5/-6

REF. DESCRIPTION PACKAGE

U1 Unitrode UCC3830DWP-5 DAC/PWM SOIC-20 Wide

C1 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C2 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C3 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C4 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C5 Sprague/Vishay 595D475X0016A2B, 4.7µF 16V Tantalum SPRAGUE Size A

C6 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C7 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C8 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C9 Sanyo 6MV1500GX, 1500 µF, 6. 3V, Aluminum Electrolyt ic 10x20mm Radial C an

C10 Sanyo 6MV1500G X, 1500µF, 6. 3V, Aluminum Electrolytic 10x20mm Radial Ca n

C11 Sprague 593D107X9010D2, 100µF, 6.3V Tantalum EIA Size D SMD

C12 0.10µF Ceramic 1206 SMD

C13 0.01µF Ceramic 0603 SMD

C14 0.01µF Ceramic 0603 SMD

C15 0.01µF Ceramic 0603 SMD

C16 1000pF Ceramic 0603 SMD

C17 0.10µF Ceramic 1206 SMD

C18 33pF NPO Ceramic 0603 SMD

C19 1500pF Ceramic 0603 SMD

C20 82pF NPO Ceramic 0603 SMD

C21 0.10µF Ceramic 1206 SMD

C22 0.10µF Ceramic 1206 SMD

CR1 Internationa l Rectifier 32CTQ 030 30V, 30A Schot tky Diode TO-220AB

L1 Micrometals T50- 52B, 10 Tu rns #16AW G, 4.5µH Toroid

Q1 International Rectifier I RL3103, 30V, 56A TO-220AB

R1 Dale/Vishay WSR-2 0.005Ω 1% SMD Power Packa ge

R2 10Ω, 5%, 1/16 Watt 0603 SMD

R3 8.2kΩ, 5%, 1/16 Watt 0603 SMD

R4 6.81kΩ, 1%, 1/16 Watt 0603 SMD

R5 3.92kΩ, 1%, 1/16 Watt 0603 SMD

R6 261kΩ, 1%, 1/16 Watt 0603 SMD

R7 100kΩ, 1%, 1/16 Watt 0603 SMD

R8 3.92kΩ, 1%, 1/16 Watt 0603 SMD

R9 10.5kΩ, 1%, 1/16 Watt 0603 SMD

Q1-HS AAVID 576802 TO-220 Heat Sink TO-220AB

CR1-HS AAVI D 577 002 TO-220 Heat Sink TO-220AB

PARTS LIST

7

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...