Page 1

DESCRIPTION

The UC1852 provides a low-cost so lution to active power-f actor corr ection (PF C)

for systems that would otherwise draw high peak current pulses from AC power

lines. This circuit implements zero-current switched boost conversion, producing

sinusoidal input currents with a minimum of external components, while keeping

peak current substantially below that of fully-discontinuous convert ers.

The UC1852 provides controlled switch on-time to regulate the output bulk DC

voltage, an off-time defined by the boost inductor, and a zero-current sensing

circuit to reactivate the switch cycle. Even though switching frequency var ies with

both load and instantaneous line voltage, it can be maintained within a reasonable

range to minimize noise generation.

While allowing higher peak switch currents than continuous PFCs such as the

UC1854, this device offers less extern al circuitry and smaller inductors, yet better

performance and easier line-noise filtering than discontinuous current PFCs with

no sacrifice in complexity or c ost. The ability to obtain a power fact or in excess of

0.99 makes the UC1852 an optimum choice for low-cost applications in the 50 to

500 watt power range. Protect ion features of these devices include under-v oltage

lockout, output clamping, peak-current limiting, and maximum-frequency

clamping.

The UC1852 family is available in 8-pin plastic and ceramic dual in-line packages,

and in the 8-pin small outline IC package (SOIC). The UC1852 is specified for

operation from -55°C to +125°C, the UC2852 is specified for operation from -40°C

to +85°C, and the UC3852 is specified for operation from 0°C to +70° C.

UC1852

UC2852

UC3852

High Power-Factor Preregulato r

This Material Copyrighted By Its Respective Manufacturer

FEATURES

Low-Cost Power Factor

•

Correction

• Power Factor Greater Than 0.99

• Few External Parts Required

• Controlled On-Time Boost PWM

• Zero-Current Switching

• Limited Peak Current

• Min and Max Frequency Limits

• Starting Current Less Than 1mA

• High-Current FET Drive Output

• Under-Voltage Lockout

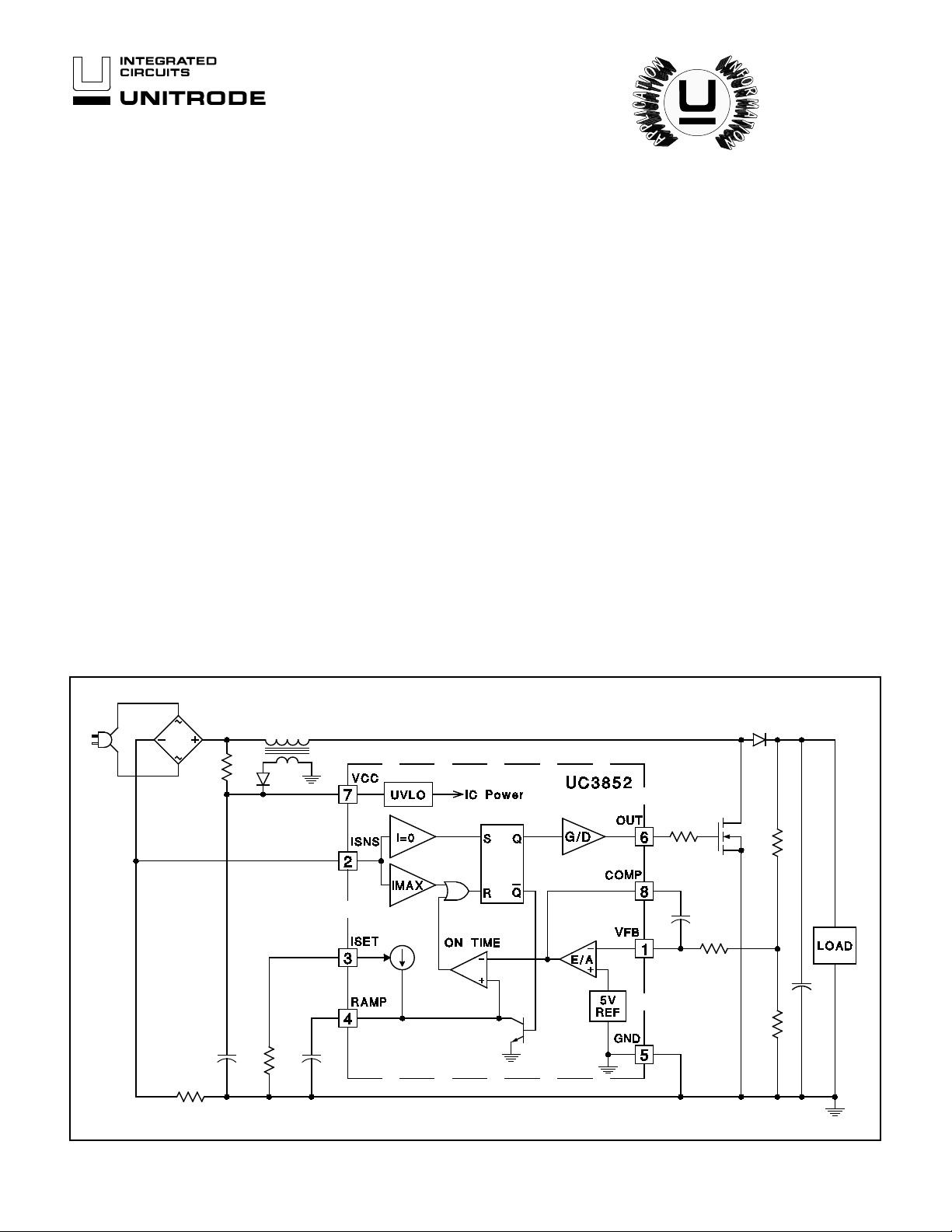

TYPICAL APPLICATION

10/94

UDG-92001

Page 2

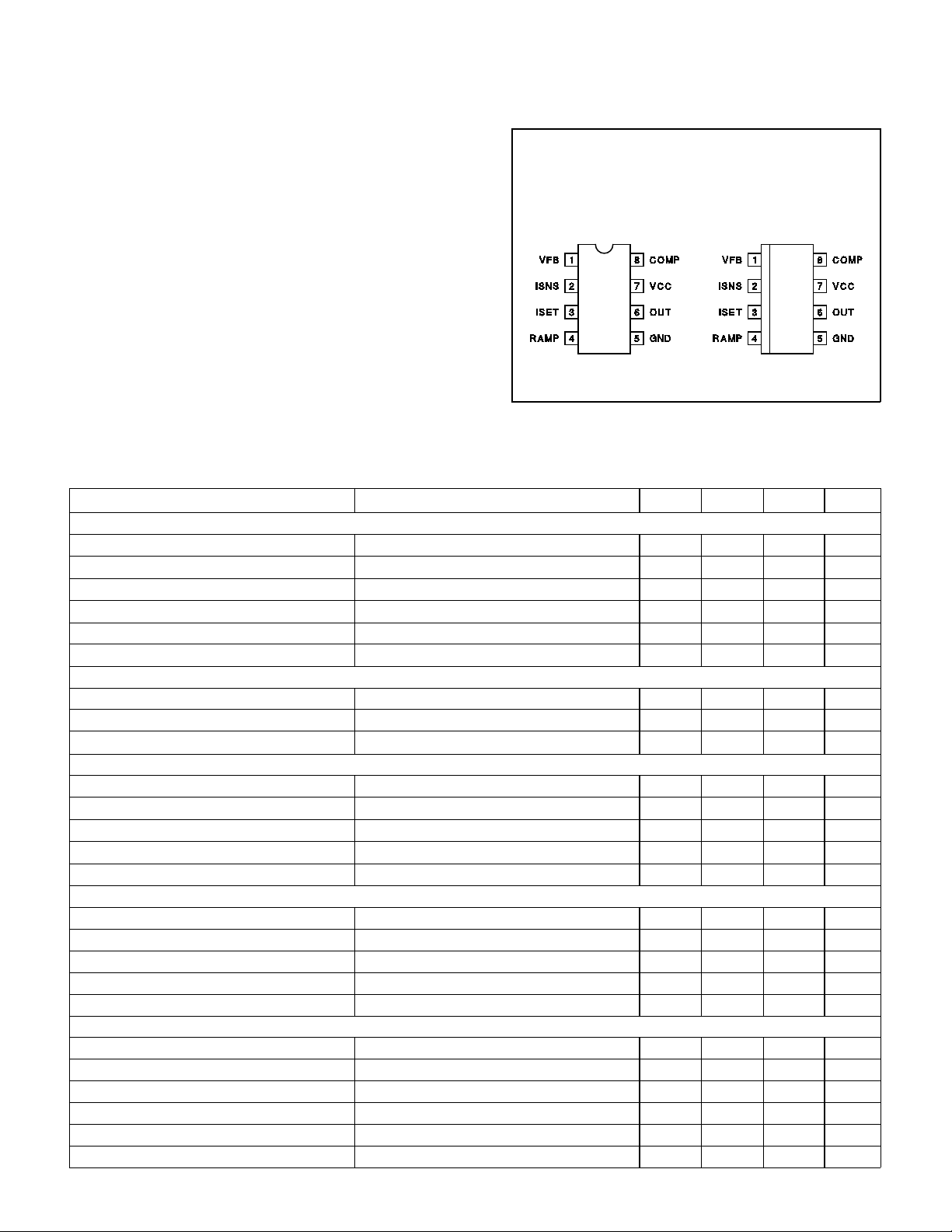

SOIC–8 (TOP VIEW)

D Package

Unless otherwise stated, VCC=2 4V, ISET=50k Ω to GND, RAMP=1nF to GND, ISNS=

–0.1V, VFB conne cted to COM P, no load on OU T, –5 5 °C<Ta<+125°C for the UC1852,

–40°C<Ta<+85°C f or the UC2852, and 0 °C<Ta<+70°C for the UC3852, and Ta=Tj.

ABSOLUTE MAXIMUM RATINGS

This Material Copyrighted By Its Respective Manufacturer

Supply Voltage (Lo w-im peda nce Sou rce )..........................30.0V

Supply Current (High-impedance Source)......................30.0mA

OUT Current, Peak.................. .... .... .... .... .... ... .... .... .... .... ....±1.0A

OUT Energy, Capacitive Load................ .... .... .... .... ..... .... ...5.0 µJ

Input Voltage, ISNS............................................................±5.0V

Input Voltage, VFB.............................................–0.3V to +10.0V

COMP Current...............................................................±10.0mA

ISET Current............ .... ... .... .... . .... ... .... .... . .... ... .... .... . .... ..–10.0mA

Power Dissipation at T a≤25°C (Note 3) ..............................1.0W

Storage Temperature .......................................–65°C to +150°C

Lead Temperat ur e (Soldering, 10 Sec onds )...................+300°C

Note 1: All voltages with respe ct to GND (Pin 1).

Note 2: All current s are posit iv e into the specif ied term inal.

Note 3: Refers to DIL-8 Packa ge. Consu lt Packaging Sec tion of

Unitrode Inte gra ted C ircuit s datab ook f or thermal lim ita tion s and

consideratio ns of package.

ELECTRICAL CHARACTERIST ICS

PARAMETER TEST CONDITIONS MIN. TYP. MAX. UNITS

Timer Sectio n

ISET Voltage 4.5 5.0 5.5 V

RAMP Charge Current RAMP=2.5V 88 98 108

RAMP Discharge Current ISNS= –1.0V, RAMP= 1 .0V 12 28 50 mA

RAMP Saturation Volt age

RAMP Threshold - Maximum Fre quen cy VFB=10V, COMP open 0.92 1.02 1.12 V

RAMP Threshold - PWM Comp ara tor 3.9 4.3 4.8 V

Current Sense Co mparator

ISNS Restart Threshold –18 –10 –4 mV

ISNS Fault Thres hold –550 –45 0 –350 mV

ISNS Input Current –100 –30 100

Error Amplifier Se cti o n

VFB Input Voltage 4.6 5.0 5.3 V

VFB Input Bias Current –5.00 –0.03 5.00

COMP Sink Current COMP=7.5V 10 mA

COMP Source Current COMP=2.5V –300 –175 –100

COMP Clamp Voltage VFB=0.0V, COMP open 9.2 10.0 10.6 V

OUT Output

OUT Saturation Voltag e High VCC=13V, I

OUT Saturation Voltag e Lo w I

OUT Saturation Voltag e Low @ 10m A I

OUT Clamp Voltage I

OUT Voltage during UVLO I

Overall Secti on

Inactive Supply Current VCC=10V 0.2 0.4 1.0 mA

Active Supply Current 3.0 6.0 10.0 mA

VCC Clamp Voltage ICC=25mA 30 33 36 V

VCC Turn-On Threshold 14.5 16.3 17.5 V

VCC Turn-Off Threshold 10.5 11.5 13.0 V

VCC Threshold Hysteresis 3 5 7 V

ISNS= –1.0V, I

OUT=200mA, ISNS= –1.0V 0.5 1.6 2.2 V

OUT=10mA, ISNS= –1.0V 0.05 0.40 V

OUT= –200mA, RAMP=2V 10.0 12.0 14.5 V

OUT=100mA, VCC=0V 0.5 1.0 2.2 V

RAMP=100µA

OUT= –200mA, RAMP=2V 0.5 1.7 2.5 V

2

CONNECTION DIAG RAM

DIL–8 (TOP VIEW)

J or N Package

UC1852

UC2852

UC3852

UDG-92002

µA

0.006 0.200 V

µA

µA

µA

Page 3

DETAILED BLOCK DIAGRAM

This Material Copyrighted By Its Respective Manufacturer

UC1852

UC2852

UC3852

UDG-92003

PIN DESCRIPTIONS

COMP: COMP is the output of the error amplifier and the

input of the PWM comparator. To limit PWM on-time, this

pin is clamped to approximately 10V. To implement soft

start, the COM P pin can be pulled low and ramped up with

a PNP transistor, a capacitor, and a resistor.

GND: Ground for all functions is through this pin.

ISET: The dominant function is of this pin is to program

RAMP charging current. RAMP charging current is

approximately 5V divided by the external resistor placed

from ISET to ground. Resistors in the range of 10kΩ to

50kΩ are recommended, producing currents in the range

of 100µA to 50 0 µA.

A second function of ISET is as reference output. T he ISET

pin is normally regulated to 5V ±10%. It is critical that this

pin only see the loading of the RA MP programming res istor,

but a high input-impedanc e comparator or amplifier may be

connected to this p in or to a tap on t he RAMP programming

resistor if required.

The third function of the ISET pin is as a FAULT output . In

the event of an over-current fault, the ISET pin is forced to

approximately 9V by the f ault comparator. This can be used

to trip an external protection circuit which can disable the

load or start a fault restart cycle.

ISNS: This input to the zero and over curr ent com parator s

is specially built to allow operation over a ±5V dynamic

range. In noisy systems or systems with very high Q

inductors, it is desirable to filter the s ignal entering the ISNS

input to prevent premature restart or fault cycles. For best

accuracy, ISNS should be connected to a current sense

resistor through no more than 200 ohms.

OUT: The output of a high-current power driver capable of

driving the gate of a power MOSFET with peak currents

exceeding ±500mA. To prevent damage to the power

MOSFET, the OUT pin is internally driven by a 12V supply.

However, lead inductance between the OUT pin and the

load can cause overshoot and ringing. External current

boost transistors will increase this ov ershoot and ringing. If

there is any significant distance between the IC and the

MOSFET, external clamp diodes and/or series damping

resistors may be required. OUT is actively held low when

the VCC is below the UVLO threshold.

RAMP: A controlled on-time PWM requires a timer whose

time can be modulated by an external voltage. The timer

current is programmed by a resistor from ISET to GND. A

capacitor from RAMP to GND sets the on time in

conjunction with the voltage on COMP. Recommended

values for the timer capacitors are between 100pF and 1nF.

VCC: VCC is the logic and contr ol power connection for this

device. VCC current is the sum of active device supply

current and the average OUT current. Knowing the

maximum operating frequency and the MOSFET gate

charge (Qg), average OUT current can be estimated by:

I

OUT

= Q

× F

g

To prevent noise problems, bypass VCC to GND with both

a ceramic and an electrolytic capacitor.

VFB: VFB is the error amplifier inverting input. This input

serves as both the voltage sense input to the error amplifier

3

Page 4

UDG-92006

UDG-92008

TYPICAL CHARACTERISTI CS

This Material Copyrighted By Its Respective Manufacturer

UC1852

UC2852

UC3852

Gain

(dB)

Phase

(deg)

Error Amplifier Gain and Phase

100

80

Phase

60

40

Gain

20

0

-20

10 100 1000 10000

Frequency, kHz

UDG-92005

Maximum

Frequency,

kHz

Max Frequency vs. Rset and Ct

1000

100pF

500pF

1nF

3nF

100

10

1 10 100

Rset, k

Ω

Maximum

On-Time

µ

s

Max On-Time vs. Rset and Ct

1000

100

10nF

3nF

10

1nF

300pF

100pF

1

1 10 100

Rset, k

Ω

UDG-92007

ns

OUT Rise and Fall Time

200

Fall Time

150

100

Rise Time

50

0

0510

Load Capacitance, nF

4

Page 5

APPLICATIO N INFO RMATIO N: A 100 Watt Power Factor Preregulator

This Material Copyrighted By Its Respective Manufacturer

UC1852

UC2852

UC3852

UDG-92004

This circuit demonstrates a complete power factor preregulator based on the UC3852. This preregulator will supply

up to 100 watts at 400VDC and exhibit power factor greater than 0.995 with less than 10% total harmonic distortion.

Operating input range is 90V to 160V RMS at 50Hz to 60Hz.

This design is intentionally simple, yet fully funct ional. The UC3852 can also be used in designs featuring soft start,

over-voltage protection, wide power-line voltage operation, and fault latching. For more information on applying

the UC3852, refer to Unitrode Application Note U–132.

PARTS LIST

C1 0.47µF/250VAC X2 Class Polyester

C2 1nF/ 16V Cer amic

C3 68µF/35V Aluminum Electrolytic

C4 180pF/16V Ceramic

C5 0.1µF/16V Polyester or Ceramic

C6 82µF/450V Aluminu m Electrolyt ic

D1 2A/500V Bridge Rect ifier (Collmer

KBPC106 or Powertex MB11A02V60)

D2 100mA/5 0V Sw itchin g Diode (1N4148 )

D3 2A/50 0V 250n s Recovery -Tim e Rect if ie r

(Motorola MR856 )

IC1 UC3852N Power Factor Controller IC

Q1 IRF830 4.5A/500V 1. 5 Ω Power FET

L1 680µH (Renco RL3792 with

10 Turn 24 AWG Secondary)

R1 150kΩ,

R2 0.2Ω,

R3 10Ω,

R4 13.3kΩ,

R5 1MΩ,

R6 20kΩ,

R7 200kΩ,

R8 200kΩ,

1

⁄4W

1

⁄2W Carbon Composition

1

⁄4W

1

⁄4W

1

⁄4W

1

⁄4W

1

⁄2W

1

⁄2W

UNITRODE INTEGRATED CIRCUITS

7 CONTINENTAL BLVD. • MERRIMACK, NH 03054

TEL. (603) 424-2410 • FAX (603) 424-3460

5

Page 6

IMPORTANT NOTICE

This Material Copyrighted By Its Respective Manufacturer

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICA TIONS USING SEMICONDUCT OR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...