TVP5160

NTSC/PAL/SECAM/Component 2x10-Bit Digital Video

Decoder

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SLES135C

February 2005–Revised May 2010

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

www.ti.com

Contents

1 Introduction ........................................................................................................................ 9

1.1 Features ...................................................................................................................... 9

1.2 Applications .................................................................................................................. 9

1.3 Description ................................................................................................................... 9

1.4 Related Products .......................................................................................................... 12

1.5 Trademarks ................................................................................................................. 12

1.6 Document Conventions ................................................................................................... 12

1.7 Ordering Information ...................................................................................................... 12

1.8 Functional Block Diagram ................................................................................................ 13

1.9 Terminal Assignments .................................................................................................... 14

2 Functional Description ....................................................................................................... 17

2.1 Analog Processing and A/D Converters ................................................................................ 17

2.1.1 Video Input Switch Control .................................................................................... 18

2.1.2 480p and 576p Component YPbPr ........................................................................... 18

2.1.3 Analog Input Clamping ......................................................................................... 18

2.1.4 Automatic Gain Control ........................................................................................ 18

2.1.5 Analog Video Output ........................................................................................... 18

2.1.6 A/D Converters .................................................................................................. 19

2.2 Digital Video Processing .................................................................................................. 19

2.2.1 2x Decimation Filter ............................................................................................ 19

2.2.2 Composite Processor .......................................................................................... 19

2.2.3 Color Low-Pass Filter .......................................................................................... 19

2.2.4 Y/C Separation .................................................................................................. 20

2.2.5 3D Frame Recursive Noise Reduction ....................................................................... 20

2.2.6 Time Base Corrector ........................................................................................... 20

2.2.7 IF Compensation ............................................................................................... 20

2.2.8 Luminance Processing ......................................................................................... 21

2.2.9 Color Transient Improvement ................................................................................. 21

2.3 Clock Circuits .............................................................................................................. 22

2.4 Real-Time Control (RTC) ................................................................................................. 22

2.5 Output Formatter .......................................................................................................... 23

2.6 Fast Switches for SCART and Digital Overlay ........................................................................ 24

2.7 Discrete Syncs ............................................................................................................. 26

2.8 Embedded Syncs .......................................................................................................... 31

2.9 I

2.10 VBI Data Processor ....................................................................................................... 34

2.11 Powerup, Reset, and Initialization ....................................................................................... 36

2.12 Adjusting External Syncs ................................................................................................. 37

2

C Host Interface .......................................................................................................... 32

2.9.1 Reset and I

2.9.2 I

2

C Operation .................................................................................................... 33

2

C Bus Address Selection ....................................................................... 32

2.9.3 VBUS Access ................................................................................................... 33

2.9.3.1 VBUS Write ......................................................................................... 34

2.9.3.2 VBUS Read ......................................................................................... 34

2.10.1 VBI FIFO and Ancillary Data in Video Stream .............................................................. 35

2.10.2 VBI Raw Data Out .............................................................................................. 36

2 Contents Copyright © 2005–2010, Texas Instruments Incorporated

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

3 Internal Control Registers ................................................................................................... 38

3.1 Register Definitions ........................................................................................................ 43

3.2 VBUS Register Definitions ............................................................................................... 87

4 Typical Application Circuit .................................................................................................. 95

4.1 Typical Application Circuit ................................................................................................ 95

5 Typical Register Programming Sequence ............................................................................. 96

6 Electrical Specifications ..................................................................................................... 97

6.1 Absolute Maximum Ratings .............................................................................................. 97

6.2 Recommended Operating Conditions .................................................................................. 97

6.3 Crystal Specifications ..................................................................................................... 98

6.4 DC Electrical Characteristics ............................................................................................. 98

6.5 Analog Processing and A/D Converters ................................................................................ 99

6.6 Data Clock, Video Data, Sync Timing .................................................................................. 99

6.7 I

6.8 SDRAM Timing ........................................................................................................... 101

6.9 Example SDRAM Timing Alignment ................................................................................... 102

6.10 Memories Tested ......................................................................................................... 103

6.11 Thermal Specification – WIP ........................................................................................... 103

2

C Host Port Timing ..................................................................................................... 100

7 Designing with PowerPAD™ ............................................................................................. 104

8 Revision History .............................................................................................................. 106

Copyright © 2005–2010, Texas Instruments Incorporated Contents 3

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

www.ti.com

List of Figures

1-1 TVP5160 PNP-Package Terminal Diagram .................................................................................. 15

2-1 Analog Processors and A/D Converters ...................................................................................... 18

2-2 Luminance Edge-Enhancer Peaking Block ................................................................................... 21

2-3 Peaking Filter Frequency Response NTSC/PAL ITU_R BT.601 Sampling............................................... 21

2-4 Reference Clock Configuration................................................................................................. 22

2-5 RTC Timing ....................................................................................................................... 23

2-6 Fast-Switches for SCART and Digital Overlay ............................................................................... 25

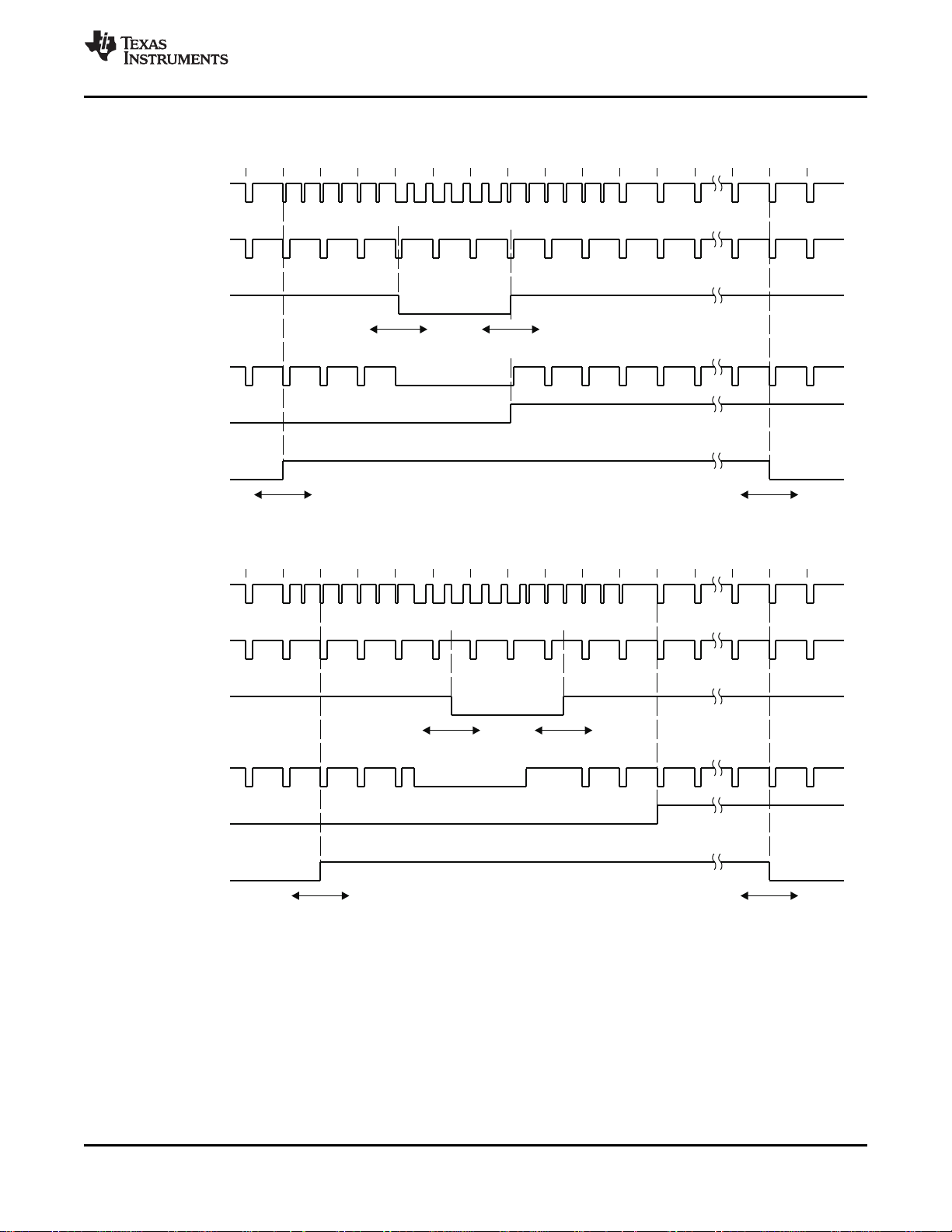

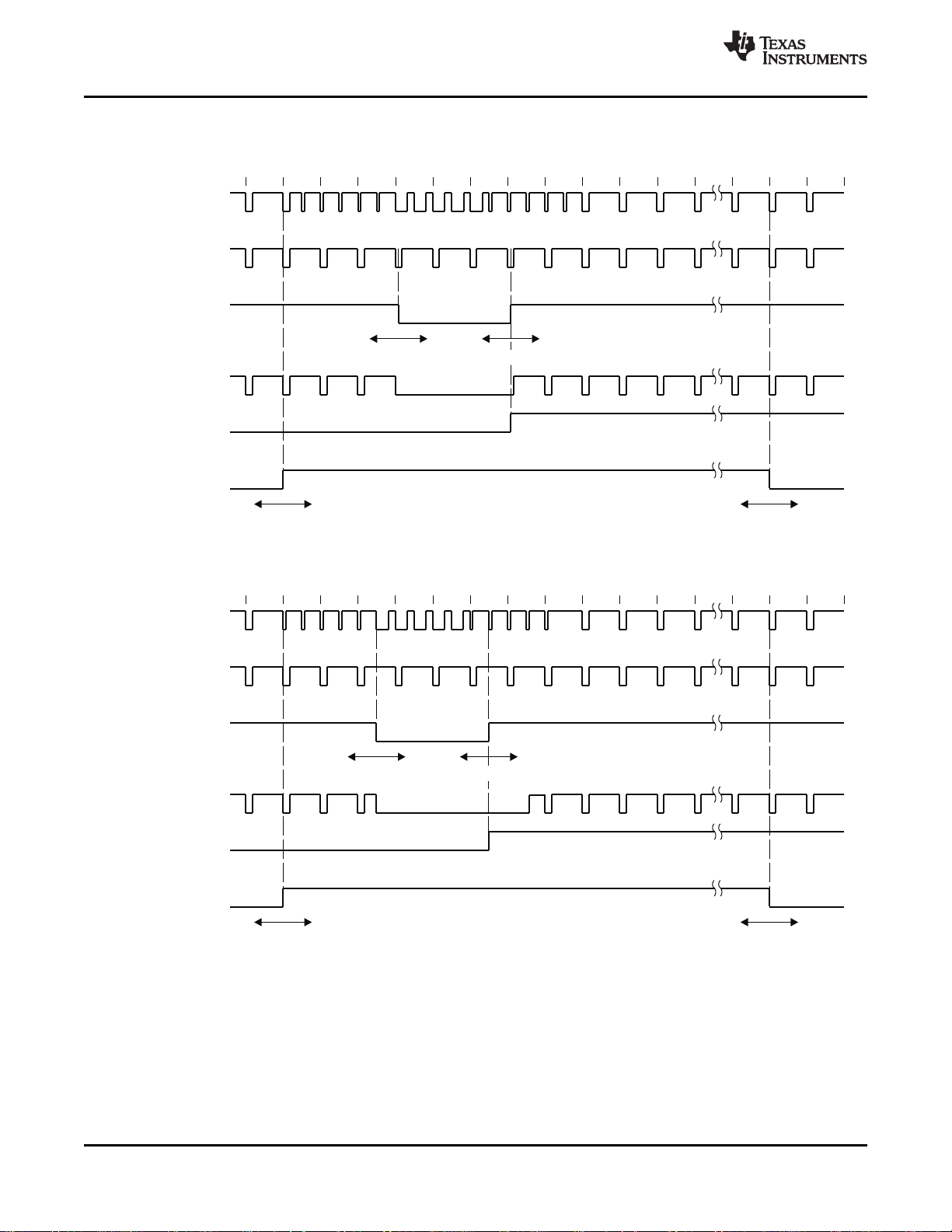

2-7 Vertical Synchronization Signals for 525-Line System...................................................................... 28

2-8 Vertical Synchronization Signals for 625-Line System...................................................................... 28

2-9 Horizontal Synchronization Signals for 10-Bit 4:2:2 Mode.................................................................. 29

2-10 Horizontal Synchronization Signals for 20-Bit 4:2:2 Mode.................................................................. 30

2-11 VS Position with Respect to HS for Interlaced Signals...................................................................... 31

2-12 VS Position with Respect to HS for Progressive Signals ................................................................... 31

2-13 VBUS Access..................................................................................................................... 33

2-14 Reset Timing...................................................................................................................... 37

3-1 Teletext Filter Function .......................................................................................................... 80

4-1 Application Example ............................................................................................................. 95

6-1 Clocks, Video Data, and Sync Timing ....................................................................................... 100

6-2 I

6-3 SDRAM Interface Timing ...................................................................................................... 101

6-4 TVP5160 Timing Relationship with K4S161622E-80 SDRAM............................................................ 102

7-1 128-Pin PowerPAD Package.................................................................................................. 105

2

C Host Port Timing............................................................................................................ 100

4 List of Figures Copyright © 2005–2010, Texas Instruments Incorporated

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

List of Tables

1-1 Terminal Functions .............................................................................................................. 15

2-1 Y/C Separation Support by Video Standard.................................................................................. 20

2-2 Output Format .................................................................................................................... 23

2-3 Summary of Line Frequency, Data Rate, and Pixel/Line Counts .......................................................... 24

2-4 Fast-Switch Modes............................................................................................................... 25

2-5 Look-Up Table for Converting from Digital RGB to 10-Bit YCbCr Data................................................... 26

2-6 EAV and SAV Sequence........................................................................................................ 32

2-7 I2C Host Interface Terminal Description ...................................................................................... 32

2-8 I

2-9 Supported VBI System .......................................................................................................... 34

2-10 Ancillary Data Format and Sequence ......................................................................................... 35

2-11 Reset Sequence.................................................................................................................. 36

3-1 I

3-2 VBUS Registers Summary...................................................................................................... 42

3-3 Input/Output Select .............................................................................................................. 43

3-4 Analog Channel and Video Mode Selection.................................................................................. 43

3-5 AFE Gain Control ................................................................................................................ 44

3-6 Video Standard Select .......................................................................................................... 44

3-7 Operation Mode .................................................................................................................. 44

3-8 Autoswitch Mask ................................................................................................................. 45

3-9 Color Killer ........................................................................................................................ 45

3-10 Luminance Processing Control 1 .............................................................................................. 46

3-11 Luminance Processing Control 2 .............................................................................................. 46

3-12 Luminance Processing Control 3 .............................................................................................. 47

3-13 Luminance Brightness .......................................................................................................... 47

3-14 Luminance Contrast ............................................................................................................. 47

3-15 Chrominance Saturation ........................................................................................................ 48

3-16 Chroma Hue ...................................................................................................................... 48

3-17 Chrominance Processing Control 1 ........................................................................................... 49

3-18 Chrominance Processing Control 2 ........................................................................................... 50

3-19 R/Pr Saturation .................................................................................................................. 50

3-20 G/Y Saturation ................................................................................................................... 50

3-21 B/Pb Saturation .................................................................................................................. 51

3-22 G/Y Brightness ................................................................................................................... 51

3-23 AVID Start Pixel .................................................................................................................. 51

3-24 AVID Stop Pixel .................................................................................................................. 52

3-25 HS Start Pixel .................................................................................................................... 52

3-26 HS Stop Pixel .................................................................................................................... 52

3-27 VS Start Line ..................................................................................................................... 52

3-28 VS Stop Line ..................................................................................................................... 53

3-29 VBLK Start Line .................................................................................................................. 53

3-30 VBLK Stop Line .................................................................................................................. 53

3-31 Embedded Sync Offset Control 1 ............................................................................................. 53

3-32 Embedded Sync Offset Control 2 ............................................................................................. 54

3-33 Fast-Switch Control ............................................................................................................. 54

3-34 Fast-Switch Overlay Delay ..................................................................................................... 55

2

C Host Interface Device Addresses.......................................................................................... 32

2

C Registers Summary.......................................................................................................... 38

Copyright © 2005–2010, Texas Instruments Incorporated List of Tables 5

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

3-35 Fast-Switch SCART Delay ..................................................................................................... 55

3-36 Overlay Delay .................................................................................................................... 55

3-37 SCART Delay .................................................................................................................... 56

3-38 CTI Control ....................................................................................................................... 56

3-39 Brightness and Contrast Range Extender .................................................................................... 56

3-40 Component Autoswitch Mask .................................................................................................. 57

3-41 Sync Control ..................................................................................................................... 57

3-42 Output Formatter Control 1 ..................................................................................................... 58

3-43 Output Formatter Control 2 ..................................................................................................... 58

3-44 Output Formatter Control 3 ..................................................................................................... 59

3-45 Output Formatter Control 4 ..................................................................................................... 59

3-46 Output Formatter Control 5 ..................................................................................................... 60

3-47 Output Formatter Control 6 ..................................................................................................... 61

3-48 Clear Lost Lock Detect .......................................................................................................... 61

3-49 Status 1 ........................................................................................................................... 62

3-50 Status 2 ........................................................................................................................... 63

3-51 AGC Gain Status ................................................................................................................ 63

3-52 Video Standard Status .......................................................................................................... 64

3-53 GPIO Input 1 ..................................................................................................................... 64

3-54 GPIO Input 2 ..................................................................................................................... 65

3-55 Back End AGC Status 1 ........................................................................................................ 65

3-56 AFE Coarse Gain for CH 1 ..................................................................................................... 65

3-57 AFE Coarse Gain for CH 2 ..................................................................................................... 66

3-58 AFE Coarse Gain for CH 3 ..................................................................................................... 66

3-59 AFE Coarse Gain for CH 4 ..................................................................................................... 66

3-60 AFE Fine Gain for B/Pb ......................................................................................................... 67

3-61 AFE Fine Gain for G/Y/Chroma ............................................................................................... 67

3-62 AFE Fine Gain for R/Pr ......................................................................................................... 67

3-63 AFE Fine Gain for CVBS/Luma ................................................................................................ 68

3-64 656 Version ....................................................................................................................... 68

3-65 SDRAM Control .................................................................................................................. 68

3-66 3DNR Y Noise Sensitivity ...................................................................................................... 69

3-67 3DNR UV Noise Sensitivity .................................................................................................... 69

3-68 3DNR Y Coring Threshold Limit ............................................................................................... 69

3-69 3DNR UV Coring Threshold Limit ............................................................................................. 69

3-70 3DNR Low Noise Limit .......................................................................................................... 69

3-71 "Blue" Screen Y Control ........................................................................................................ 69

3-72 "Blue" Screen Cb Control ....................................................................................................... 69

3-73 "Blue" Screen Cr Control ....................................................................................................... 70

3-74 "Blue" Screen LSB Control ..................................................................................................... 70

3-75 Noise Measurement ............................................................................................................. 70

3-76 3DNR Y Core0 ................................................................................................................... 70

3-77 3DNR UV Core0 ................................................................................................................. 70

3-78 F- and V-Bit Decode Control ................................................................................................... 71

3-79 Back-End AGC Control ......................................................................................................... 72

3-80 AGC Decrement Speed ......................................................................................................... 72

3-81 ROM Version ..................................................................................................................... 72

3-82 AGC White Peak Processing .................................................................................................. 73

www.ti.com

6 List of Tables Copyright © 2005–2010, Texas Instruments Incorporated

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

3-83 F-Bit and V-Bit Control .......................................................................................................... 73

3-84 AGC Increment Speed .......................................................................................................... 74

3-85 AGC Increment Delay ........................................................................................................... 74

3-86 Analog Output Control 1 ........................................................................................................ 74

3-87 Chip ID MSB ..................................................................................................................... 74

3-88 Chip ID LSB ...................................................................................................................... 74

3-89 Color PLL Speed Control ....................................................................................................... 75

3-90 3DYC Luma Coring LSB ........................................................................................................ 75

3-91 3DYC Chroma Coring LSB ..................................................................................................... 75

3-92 3DYC Luma/Chroma Coring MSB ............................................................................................ 75

3-93 3DYC Luma Gain ................................................................................................................ 75

3-94 3DYC Chroma Gain ............................................................................................................. 76

3-95 3DYC Signal Quality Gain ...................................................................................................... 76

3-96 3DYC Signal Quality Coring .................................................................................................... 76

3-97 IF Compensation Control ....................................................................................................... 76

3-98 IF Differential Gain Control ..................................................................................................... 77

3-99 IF Low Frequency Gain Control ............................................................................................... 77

3-100 IF High Frequency Gain Control ............................................................................................... 77

3-101 Weak Signal High Threshold ................................................................................................... 77

3-102 Weak Signal High Threshold ................................................................................................... 77

3-103 Status Request .................................................................................................................. 77

3-104 3DYC NTSC VCR Threshold .................................................................................................. 78

3-105 3DYC PAL VCR Threshold ..................................................................................................... 78

3-106 Vertical Line Count .............................................................................................................. 78

3-107 AGC Decrement Delay ......................................................................................................... 78

3-108 VDP TTX Filter and Mask ...................................................................................................... 79

3-109 VDP TTX Filter Control ......................................................................................................... 79

3-110 VDP FIFO Word Count ......................................................................................................... 80

3-111 VDP FIFO Interrupt Threshold ................................................................................................. 81

3-112 VDP FIFO Reset ................................................................................................................. 81

3-113 VDP FIFO Output Control ...................................................................................................... 81

3-114 VDP Line Number Interrupt .................................................................................................... 81

3-115 VDP Pixel Alignment ............................................................................................................ 82

3-116 VDP Line Start ................................................................................................................... 82

3-117 VDP Line Stop ................................................................................................................... 82

3-118 VDP Global Line Mode ......................................................................................................... 82

3-119 VDP Full Field Enable .......................................................................................................... 83

3-120 VDP Full Field Mode ............................................................................................................ 83

3-121 Interlaced/Progressive Status .................................................................................................. 83

3-122 VBUS Data Access with No VBUS Address Increment .................................................................... 83

3-123 VBUS Data Access with VBUS Address Increment ........................................................................ 83

3-124 VDP FIFO Read Data ........................................................................................................... 84

3-125 VBUS Address ................................................................................................................... 84

3-126 Interrupt Raw Status 0 .......................................................................................................... 84

3-127 Interrupt Raw Status 1 .......................................................................................................... 85

3-128 Interrupt Status 0 ................................................................................................................ 85

3-129 Interrupt Status 1 ................................................................................................................ 86

3-130 Interrupt Mask 0 ................................................................................................................. 86

Copyright © 2005–2010, Texas Instruments Incorporated List of Tables 7

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

3-131 Interrupt Mask 1 ................................................................................................................. 86

3-132 Interrupt Clear 0 ................................................................................................................. 87

3-133 Interrupt Clear 1 ................................................................................................................. 87

3-134 VDP Closed Caption Data ...................................................................................................... 88

3-135 VDP WSS/CGMS Data ......................................................................................................... 88

3-136 VDP VITC Data .................................................................................................................. 89

3-137 VDP V-Chip TV Rating Block 1 ................................................................................................ 89

3-138 VDP V-Chip TV Rating Block 2 ................................................................................................ 89

3-139 VDP V-Chip TV Rating Block 3 ................................................................................................ 90

3-140 VDP V-Chip MPAA Rating Data ............................................................................................... 90

3-141 VDP General Line Mode and Line Address .................................................................................. 91

3-142 VDP VPS, Gemstar EPG Data ................................................................................................ 92

3-143 Analog Output Control 2 ........................................................................................................ 93

3-144 Interrupt Configuration .......................................................................................................... 93

3-145 Interrupt Raw Status 1 .......................................................................................................... 93

3-146 Interrupt Status 1 ................................................................................................................ 94

3-147 Interrupt Mask 1 ................................................................................................................. 94

3-148 Interrupt Clear 1 ................................................................................................................. 94

6-1 Memories Tested ............................................................................................................... 103

8-1 Revision History................................................................................................................. 106

www.ti.com

8 List of Tables Copyright © 2005–2010, Texas Instruments Incorporated

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

NTSC/PAL/SECAM/Component 2x10-Bit Digital Video Decoder

Check for Samples: TVP5160

1 Introduction

1.1 Features

1

• Two 11-Bit 60-MSPS Analog-to-Digital (A/D) • Fast Switch 4x Oversampled Input for Digital

Converters With Analog Preprocessors RGB Overlay Switching Between Any CVBS,

(Clamp/AGC) S-Video, or Component Video Input

• Fixed RGB-to-YUV Color Space Conversion • SCART 4x Oversampled Fast Switching

• Robust Sync Detection for Weak and Noisy

Signals as well as VCR

• Supports NTSC (J, M, 4.43), PAL (B, D, G, H, I,

M, N, Nc, 60) and SECAM (B, D, G, K, K1, L) • Chrominance Processor

CVBS, S-Video

• Supports Component Standards 480i, 576i,

480p, and 576p

• Supports ITU-R BT.601 Pixel Sampling

Frequencies

• Supports 3D Y/C Separation, or 2D 5-Line (5H) With Discrete Syncs)

Adaptive Comb and Chroma Trap Filter for

both PAL and NTSC Signals

• Concurrent Temporal, Frame Recursive, Noise

Reduction (3DNR)

• IF Compensation

• Line-Based Time Base Correction (TBC)

Between Component RGB Input and CBVS

Input

• Analog Video Output

• Luminance Processor

• Clock/Timing Processor and Power-Down

Control

• Output Formatter Supports Both ITU-R BT.656

(Embedded Syncs) and ITU-R BT.601 (4:2:2

• I2C Host Port Interface

• VBI Data Processor

• "Blue" Screen (Programmable Color) Output

• Macrovision™ Copy Protection Detection

Circuit (Types 1, 2, and 3) on Both Interlaced

and Progressive Signals

1.2 Applications

• Digital TV

• LCD TV/monitors

• DVD-R

• PVR

• PC video cards

• Video capture/video editing

• Video conferencing

1.3 Description

The TVP5160 device is a high quality, digital video decoder that digitizes and decodes all popular

baseband analog video formats into digital component video. The TVP5160 decoder supports the A/D

conversion of component YPbPr and RGB (SCART) signals, as well as the A/D conversion and decoding

of NTSC, PAL, and SECAM composite and S-Video into component YCbCr. Additionally, component

progressive signals can be digitized. The chip includes two 11-bit, 60-MSPS, A/D converters (ADCs). Prior

to each ADC, each analog channel contains an analog circuit, which clamps the input to a reference

voltage and applies a programmable gain and offset. A total of 12 video input terminals can be configured

to a combination of YPbPr, RGB, CVBS, and S-Video video inputs.

Progressive component signals are sampled at 2× clock frequency (54 MHz) and are then decimated to

the 1× rate. In SCART mode the component inputs and the CVBS inputs are sampled at 54 MHz

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2005–2010, Texas Instruments Incorporated

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

alternately, then decimated to the 1× rate. Composite or S-Video signals are sampled at 4× the ITU-R

BT.601 clock frequency (54 MHz), line-locked for correct pixel alignment, and are then decimated to the

1× rate. CVBS decoding utilizes advanced 3D Y/C filtering and 2-dimensional complementary 5-line

adaptive comb filtering for both the luma and chroma data paths to reduce both cross-luma and

cross-chroma artifacts. 3D Y/C color separation may be used on both PAL and NTSC video signals. A

chroma trap filter is also available. On CVBS and Y/C inputs, the user can control video characteristics

such as hue, contrast, brightness, and saturation via an I2C host port interface. Furthermore, luma peaking

with programmable gain is included, as well as a patented color transient improvement (CTI) circuit.

Attenuation at higher frequencies or asymmetrical color subcarrier sidebands are compensated using the

IF compensation block. Frame adaptive noise reduction may be applied to reduce temporal noise on

CVBS, S-Video, or component inputs.

3D noise reduction and 3D Y/C separation may be used at the same time or independently.

The TVP5160 decoder uses Texas Instruments' patented technology for locking to weak, noisy, or

unstable signals and can auto-detect between broadcast quality and VCR-style (nonstandard) video

sources.

The TVP5160 decoder generates synchronization, blanking, field, active video window, horizontal and

vertical syncs, clock, genlock (for downstream video encoder synchronization), host CPU interrupt and

programmable logic I/O signals, in addition to digital video outputs.

The TVP5160 decoder includes methods for advanced vertical blanking interval (VBI) data retrieval. The

VBI data processor (VDP) slices and performs error checking on teletext, closed caption, and other VBI

data. A built-in FIFO stores up to 11 lines of teletext data, and, with proper host port synchronization,

full-screen teletext retrieval is possible. The TVP5160 decoder can pass through the output formatter 2×

sampled raw Luma data for host-based VBI processing.

www.ti.com

Digital RGB overlay can be synchronously switched with any video input, with all signals being

oversampled at 4× the pixel rate.

The TVP5160 detailed functionality includes:

• Two high-speed, 60-MSPS, 11-bit, A/D channels with programmable clamp and gain control

The two ADCs can sample CVBS or S-Video at 54 MHz. YPbPr/RGB is multiplexed between the two

ADCs which sample at 54 MHz giving a channel sampling frequency of 27 MHz.

• Supports ITU-R BT.601 pixel sampling frequencies.

Supports ITU-R BT.601 sampling for both interlaced and progressive signals.

• RGB-to-YUV color space conversion for SCART signals

• 3D Y/C separation or 2D 5-line (5H) adaptive comb and chroma trap filter

3-frame NTSC and PAL color separation

• Temporal frame recursive noise reduction (3DNR)

Frame recursive noise reduction can be applied to interlaced CVBS, S-Video, or component inputs for

interlaced signals. Noise reduction can be used at the same time as 3D Y/C separation. Noise

reduction cannot be applied to progressive video signals.

• Line-based time base correction (TBC)

Line based time correction corrects for horizontal phase errors encountered during video decoding up

to ±80 pixels of error. This improves the output video quality from jittery sources such as VCRs. It also

reduces line tearing during video trick modes such as fast forward and rewind.

• IF compensation

Attenuation at higher frequencies or asymmetrical color subcarrier sidebands are compensated using

the IF compensation block

• Fast switch 4× oversampling for digital RGB overlay signals for switching between any CVBS, S-Video,

or component video inputs

The fast switch overlay signals (FSO, DR, DG, DB) are oversampled at 4× the pixel clock frequency.

10 Introduction Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

www.ti.com

• SCART 4x oversampled fast switching between component RGB input and CBVS input

• Analog video output

• Supports NTSC (J, M, 4.43), PAL (B, D, G, H, I, M, N, Nc, 60), SECAM (B, D, G, K, K1, L), CVBS, and

• Twelve analog video input terminals for multi-source connection

• User-programmable video output formats

• HS/VS outputs with programmable position, polarity, and width and FID (Field ID) output

• Composite and S-Video processing

• Vertical blank interval data processor

• I2C host port interface

• "Blue" screen output

• Macrovision copy protection detection circuit (types 1, 2, and 3) on both interlaced and progressive

SLES135C–FEBRUARY 2005–REVISED MAY 2010

The phase of these signals is used to mix the selected video input format and a digital RGB input to

generate an output video stream. This improves the overlay picture quality when the external FSO and

digital RGB signals are generated by an asynchronous source.

The SCART overlay control signal (FSS) is oversampled at 4x the pixel clock frequency. The phase of

this signal is used to mix between the CVBS input and the analog RGB inputs. This improves the

analog overlay picture quality when the external FSS and analog video signals are generated by an

asynchronous source.

Buffered analog output with automatic PGA

S-Video

– 10-bit ITU-R BT.656 4:2:2 YCbCr with embedded syncs

– 20-bit 4:2:2 YCbCr with discrete syncs

– 10-bit 4:2:2 YCbCr with discrete syncs

– 2× sampled raw VBI data in active video during a vertical blanking period

– Sliced VBI data during a horizontal blanking period

– Adaptive 3D/2D Y/C separation using 5-line adaptive comb filter for composite video inputs;

chroma-trap available

– Automatic video standard detection and switching (NTSC/PAL/SECAM/progressive)

– Luma-peaking with programmable gain

– Output data rates either 1× or 2× pixel rate

– Patented architecture for locking to weak, noisy, or unstable signals

– Single 14.31818-MHz reference crystal for all standards (ITU-R.BT601 sampling, interlaced or

progressive)

– Line-locked internal pixel sampling clock generation with horizontal and vertical lock signal outputs

– Certified Macrovision copy protection detection on composite and S-Video inputs (NTSC, PAL)

– Genlock output (RTC) for downstream video encoder synchronization

– Teletext (NABTS, WST)

– Closed caption (CC) and extended data service (XDS)

– Wide screen signaling (WSS)

– Copy generation management system (CGMS)

– Video program system (VPS/PDC)

– Vertical interval time code (VITC)

– EPG video guide 1×/2× (Gemstar)

– V-Chip decoding

– Custom mode

– Register readback of CC, CGMS, WSS, VPS, VITC, V-Chip, EPG 1× and 2× sliced data, CGMS-A

and RC for progressive signals.

signals

Copyright © 2005–2010, Texas Instruments Incorporated Introduction 11

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Macrovision detection on standard definition signals of types 1, 2, and 3, and to Revision 1.2 for

progressive signals

• Reduced power consumption: 1.8-V digital core, 3.3-V and 1.8-V analog core with power-save and

power-down modes

• 128-TQFP PowerPAD™ package

1.4 Related Products

• TVP5146M2

• TVP5147M1

• TVP5150AM1

• TVP5151

• TVP5154A

• TVP5158

1.5 Trademarks

• TI and PowerPAD are trademarks of Texas Instruments.

• Macrovision is a trademark of Macrovision Corporation.

• Gemstar is a trademark of Gemstar-TV Guide International.

• Other trademarks are the property of their respective owners

www.ti.com

1.6 Document Conventions

Throughout this data manual, several conventions are used to convey information. These conventions are

listed below:

1. To identify a binary number or field, a lower case b follows the numbers. For example: 000b is a 3-bit

binary field.

2. To identify a hexadecimal number or field, a lower case h follows the numbers. For example: 8AFh is a

12-bit hexadecimal field.

3. All other numbers that appear in this document that do not have either a b or h following the number

are assumed to be decimal format.

4. If the signal or terminal name has a bar above the name (for example, RESETB), then this indicates

the logical NOT function. When asserted, this signal is a logic low, 0, or 0b.

5. RSVD indicates that the referenced item is reserved.

1.7 Ordering Information

T

A

0°C to 70°C TVP5160PNP Tray

PACKAGED DEVICES

128-Pin TQFP-PowerPAD

PACKAGE OPTION

12 Introduction Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

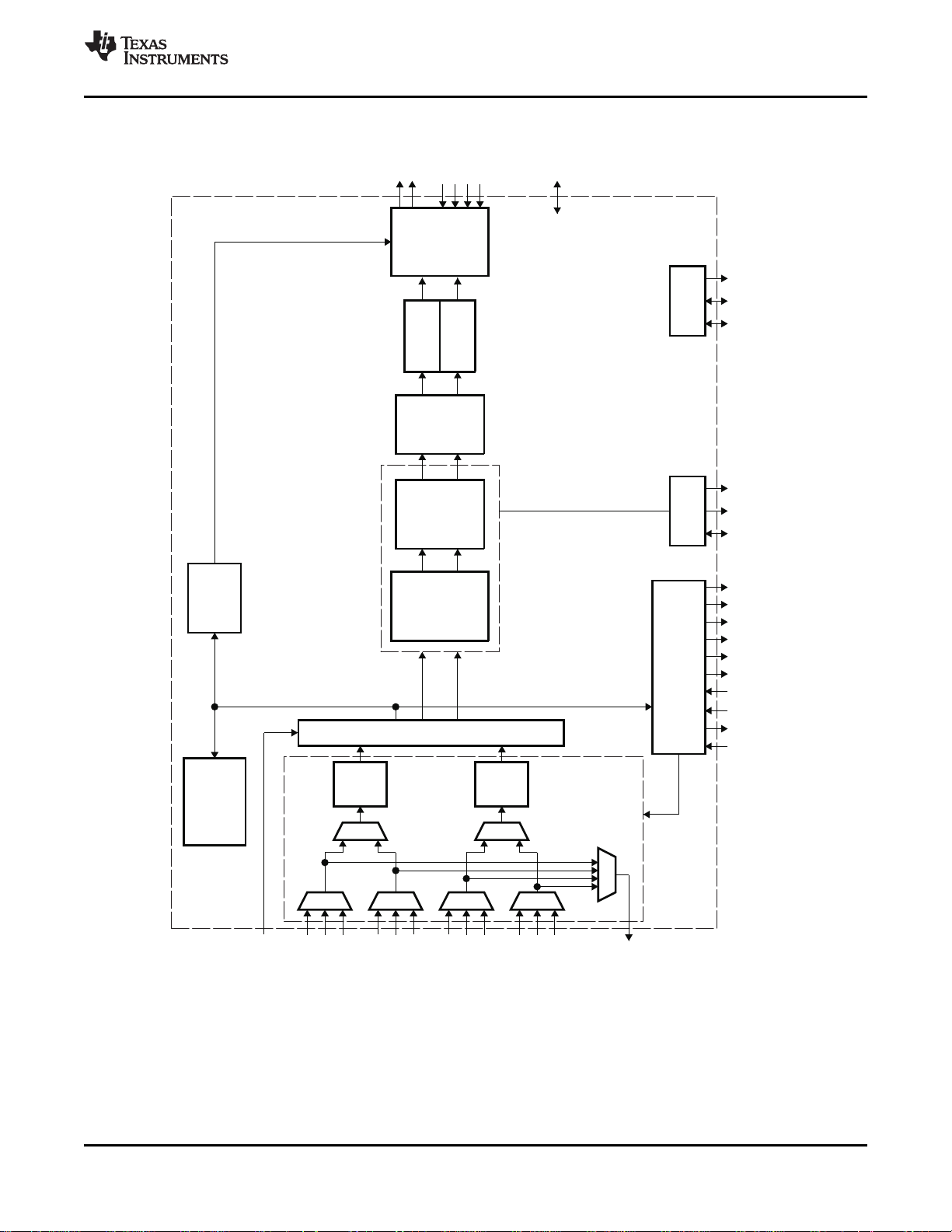

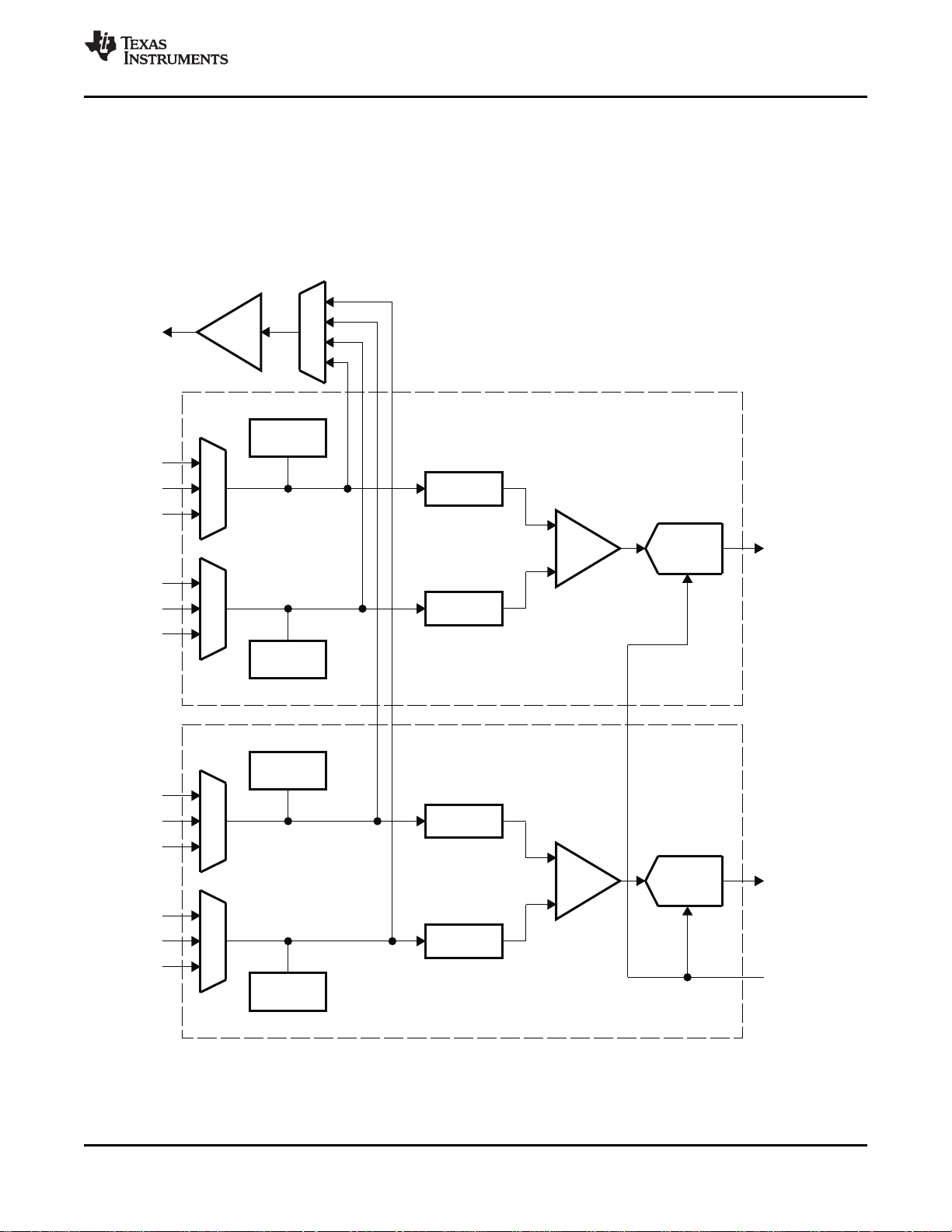

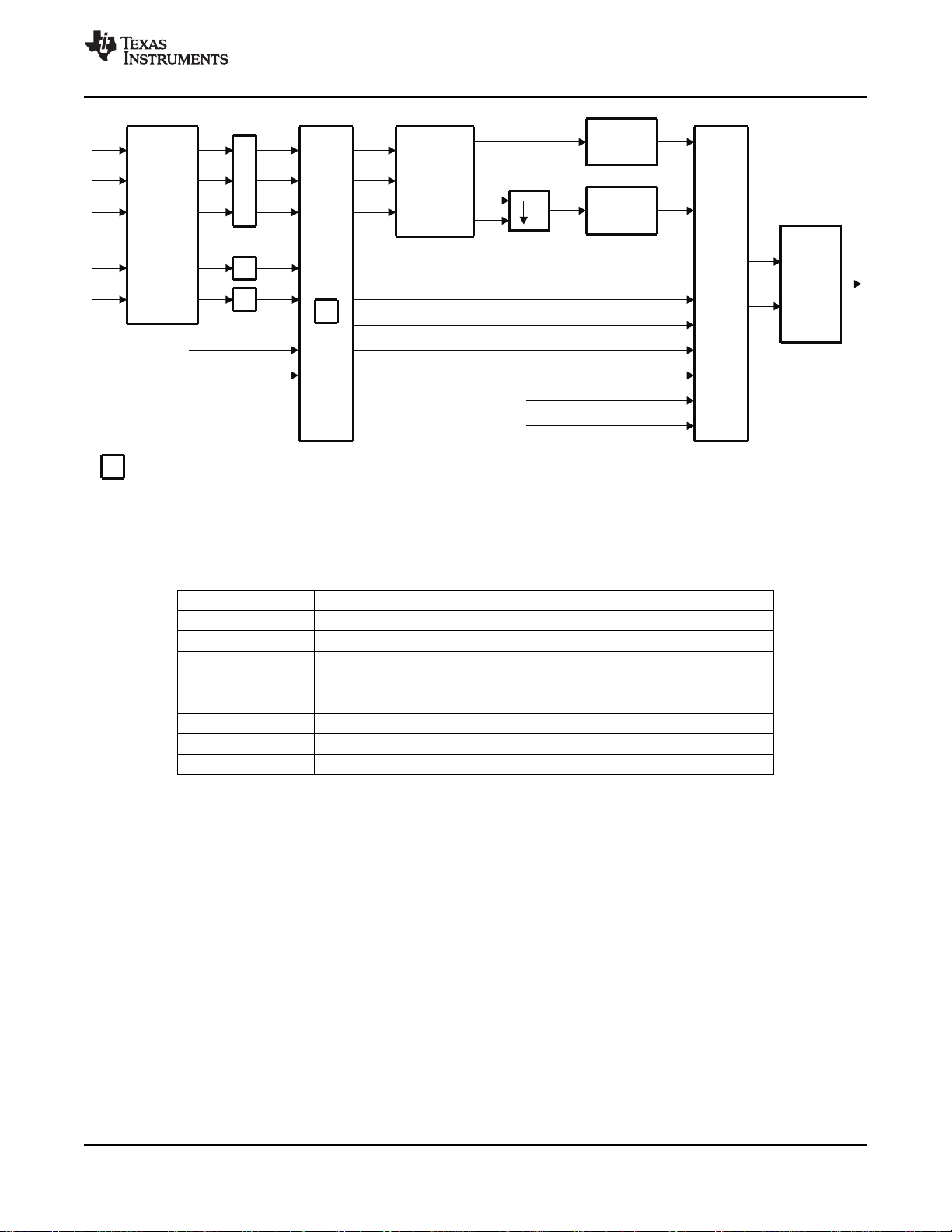

Y/C

Separation

3D/5-line

Adaptive

Comb

Filter

ADC1

MUX

CVBS/Y

C/CbCr

C

Y

Output

Formatter

Y[9:0]

VBI

Data

Slicer

MacroVision

Copy

Protection

Detection

C[9:0]

Host

Interface

Timing Processor

With Sync Detector

Analog Out

CVBS/

Pr/C/R

CVBS/

Y/G

CVBS/

Pb/C/B

CVBS/Y

Analog Front End

Sampling

Clock

GPIO

HS/CS

VS/VBLK

FID

AVID

XIN

XOUT

SCLK

RESETB

GLCO

PWDN

SCL

INTREQ

VI_1

CVBS/

Y/G

VI_2

VI_3

VI_4

VI_5

VI_6

VI_7

VI_8

VI_9

VI_10

VI_11

VI_12

Luma

Processing

3D Noise

Reduction

ADC2

Chroma

Processing

TBC/

IF Comp

DB

DG

DR

FSO

SDA

SDRAM

Interface

Data

Control

Address

C

Y

C

Y

C

Y

FSS

TVP5160

www.ti.com

1.8 Functional Block Diagram

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Copyright © 2005–2010, Texas Instruments Incorporated Introduction 13

Submit Documentation Feedback

Product Folder Link(s): TVP5160

A33 G ND

Ana log _ o ut

A33 G ND

A33 V D D

PLL 1 8 G N D

PLL 1 8 V D D

XO U T

XIN

D G N D

FSS

VS/V B LK/G P IO

H S/C S /G PIO

FID /G PIO

AV ID /GP IO

C _0 /GP IO

C _1 /GP IO

D G N D

DV D D

C _2 /GP IO

C _3 /GP IO

C _4 /GP IO

C _5 /GP IO

IO G N D

IOVDD

C _6 /GP IO/D R

C _7 /GP IO/D G

C _8 /GP IO/D B

C _9 /GP IO/F S O

D G N D

DV D D

Y_0

Y_1

12 8

12 7

12 6

12 5

12 4

12 3

12 2

12 1

12 0

11 9

11 8

11 7

11 6

11 5

11 4

11 3

11 2

11 1

11 0

10 9

10 8

10 7

10 6

10 5

10 4

10 3

10 2

10 1

10 0

999897

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

PNP PACKAGE

(TOP VIEW)

Y_2

Y_3

Y_4

IOGND

IOVDD

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

SCLK

GLCO/GPIO/I2CA0

GPIO/I2CA1

A3

A2

A1

A0

A10

BA1

IOGND

IOVDD

BA0

RAS

CAS

WE

A4

A5

A6

DGND

DVDD

A33GND

A33VDD

VI_1

VI_2

VI_3

NC

VI_4

VI_5

VI_6

NC

A18VDD

A18GND

A18VDD

A18GND

A18GND

A18VDD

VI_7

VI_8

VI_9

NC

VI_10

VI_11

VI_12

NC

A33VDD

A33GND

A33GND

A33GND

DGND

SCL

SDA

INTREQ

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

DV D D

D G N D

PW D N

R ESETB

IOVDD

IO G N D

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

DV D D

D G N D

D 15

D 14

D 13

D 12

D 11

D 10

D 9

D 8

IOVDD

IO G N D

D Q M

SDR A M _C LK

A11

A9A8A7

33343536373839404142434445464748495051525354555657585960616263

64

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

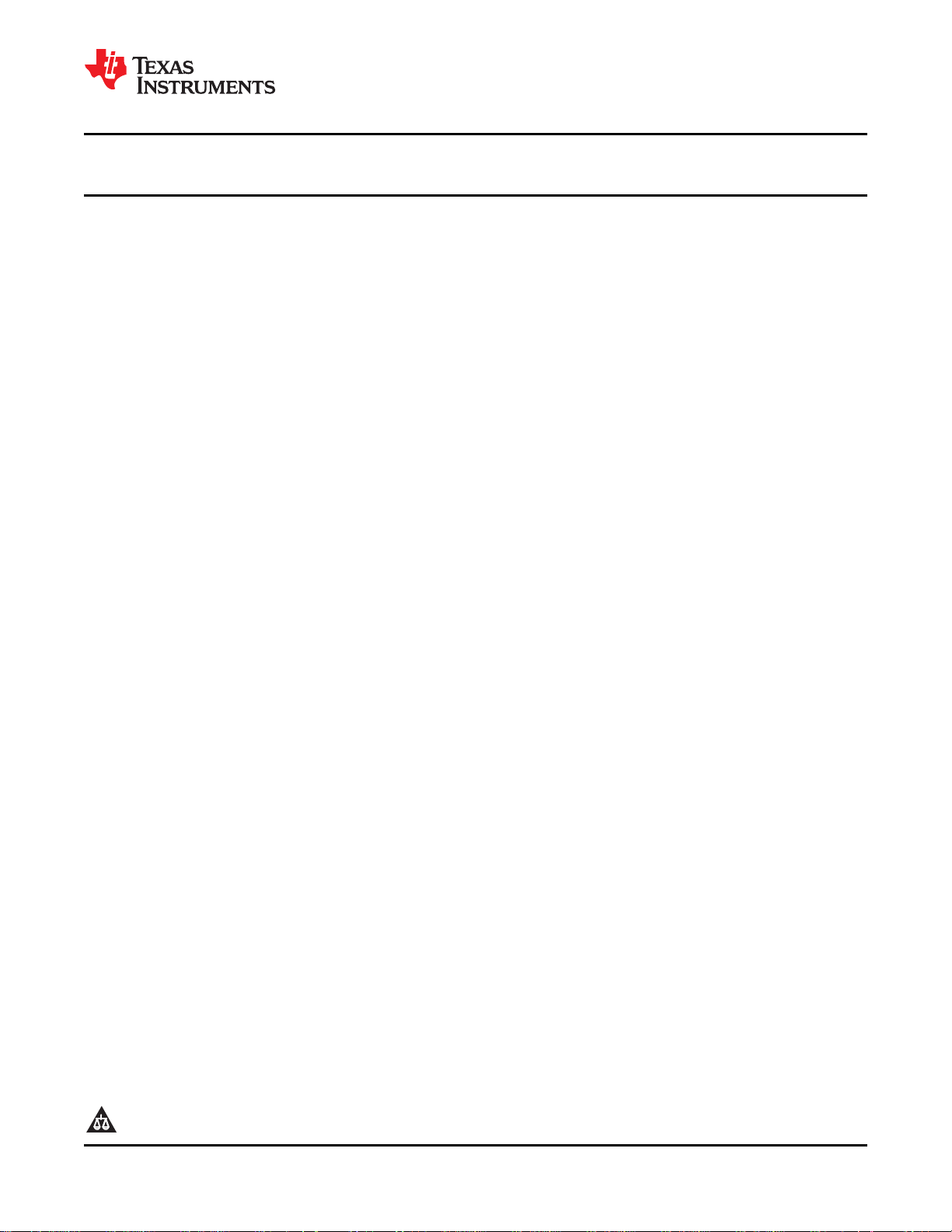

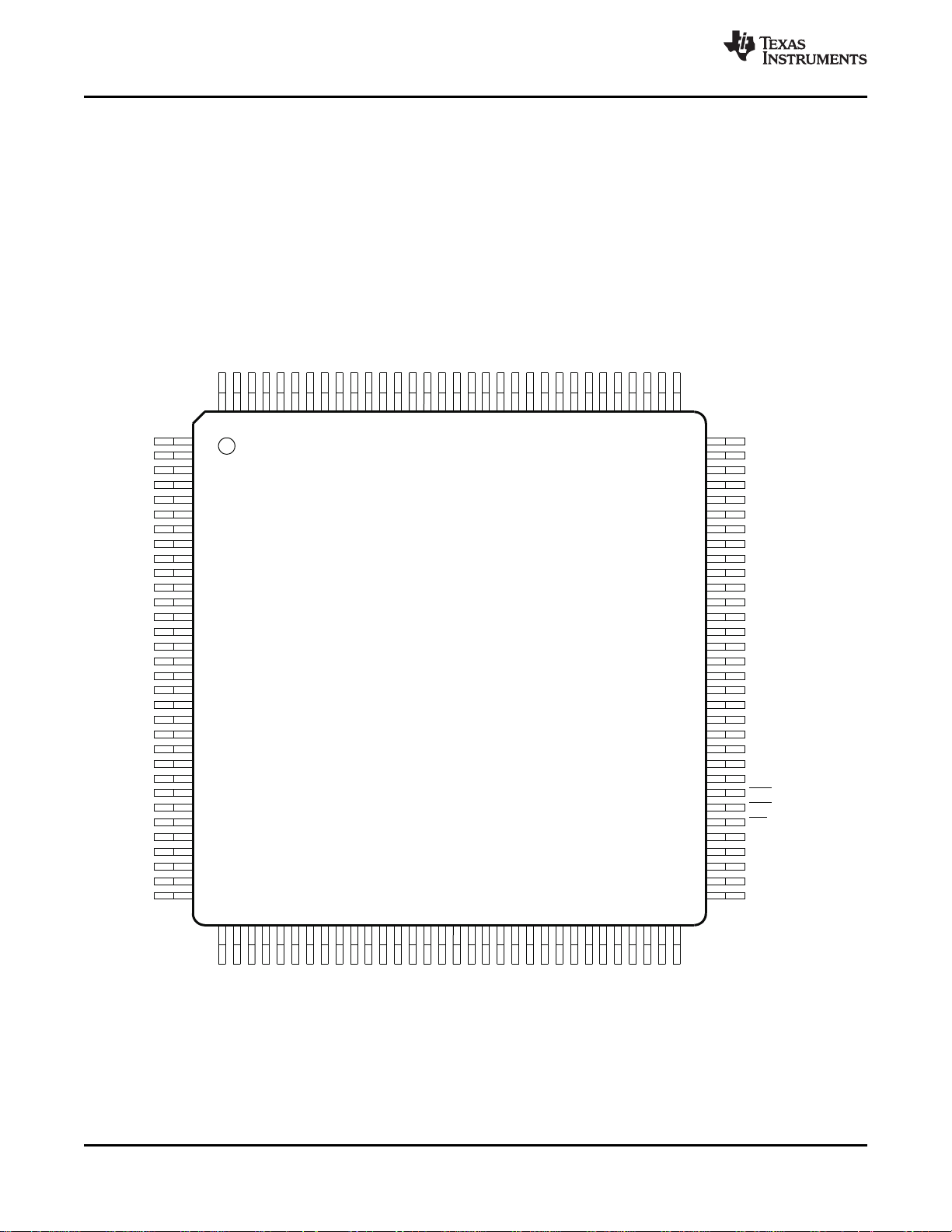

1.9 Terminal Assignments

The TVP5160 video decoder is packaged in a 128-terminal PNP PowerPAD package. Figure 1-1 is the

PNP-package terminal diagram. Table 1-1 gives a description of the terminals.

www.ti.com

PNP PACKAGE

(TOP VIEW)

Figure 1-1. TVP5160 PNP-Package Terminal Diagram

14 Introduction Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

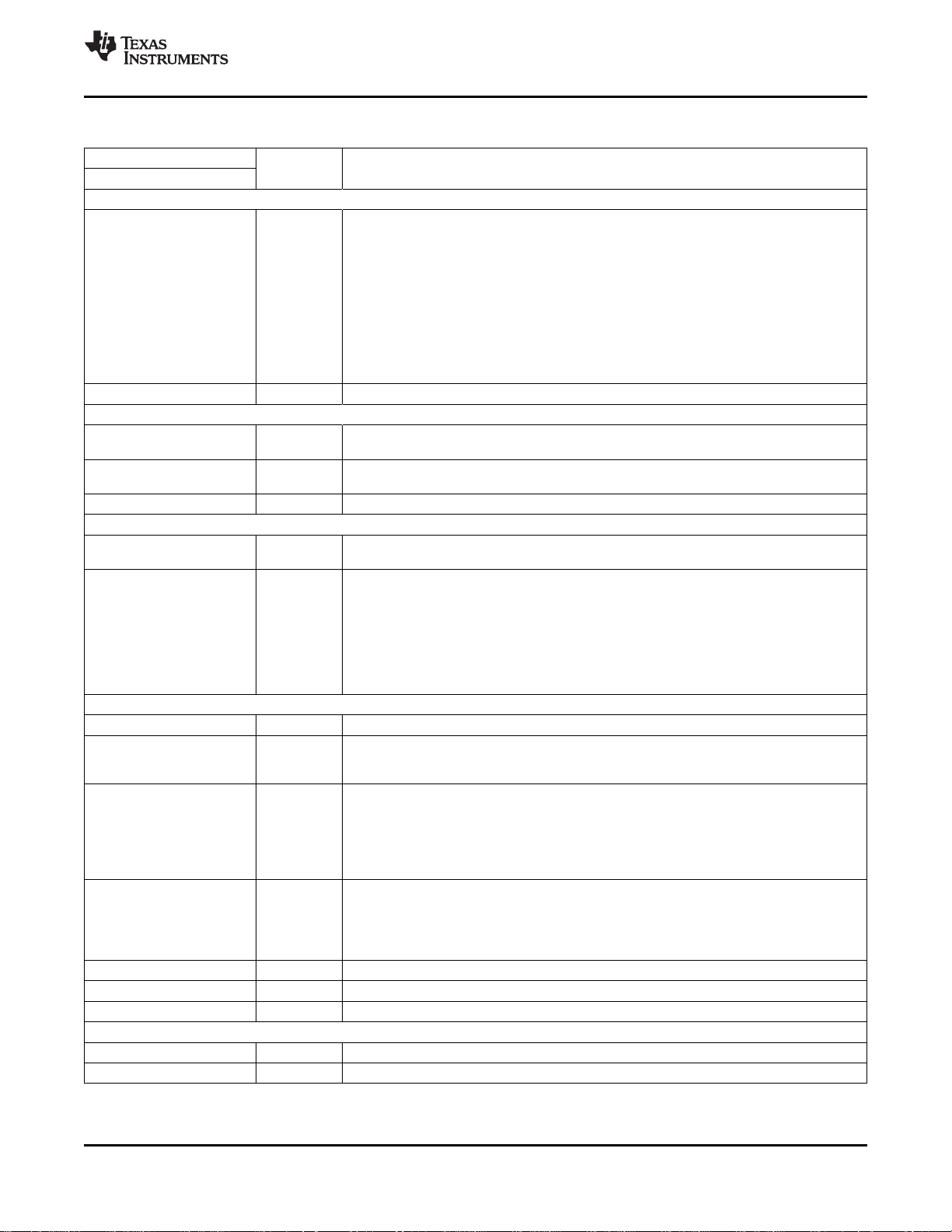

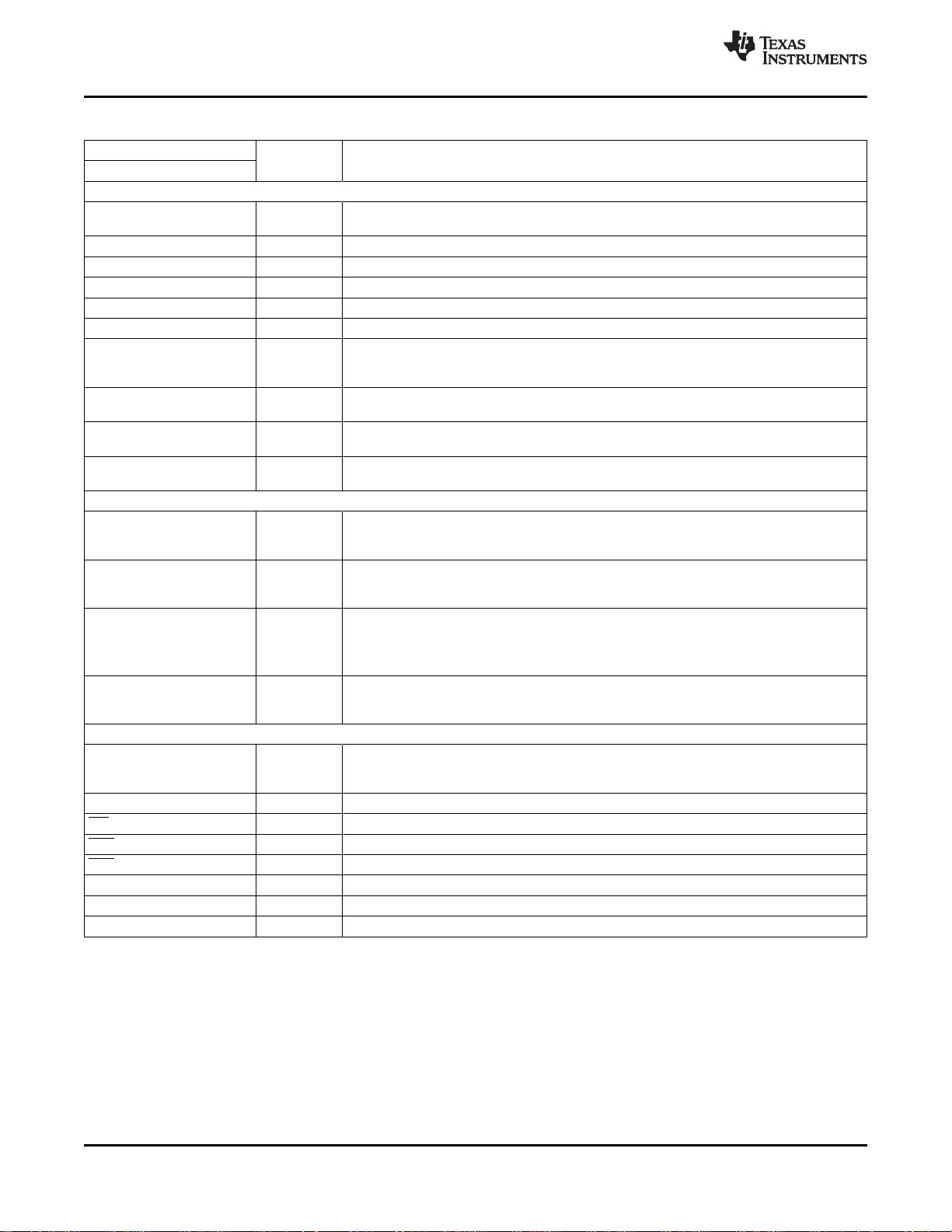

Table 1-1. Terminal Functions

PIN

NAME NO.

Analog Video

VI_1 3 I VI_x: analog video inputs

VI_2 4 Up to 12 composite, 6 S-Video, or 3 component video inputs (or combinations thereof) can

VI_3 5 be

VI_4 7 supported. Also, 4-channel SCART is supported.

VI_5 8 The inputs must be ac-coupled. The recommended coupling capacitor is 0.1 µF.

VI_6 9 The possible input configurations are listed in the input select register 00h.

VI_7 17 Unused inputs must be connected to ground through 0.1-µF capacitors.

VI_8 18

VI_9 19

VI_10 21

VI_11 22

VI_12 23

Analog_out 127 O Unbuffered analog video output

Clock Signals

XIN 121 I External clock reference input. It may connected to external oscillator with 1.8-V compatible

XOUT 122 O External clock reference output. Not connected if XTAL1 is driven by an external

SCLK 84 O Line-locked data output clock

Digital Video

Y[9:0] 87–91, O Digital video output of Y/YCbCr, Y_9 is MSB and Y_0 is LSB. For 8-bit operation, the upper

94–98 8 bits must be connected.

C[9:0] / GPIO 101–104, I/O Digital video output of CbCr, C_9 is MSB and C_0 is LSB. These terminals can be

107–110, programmable general purpose I/O, or as digital overlay controls. For 8-bit operation, the

113, 114 upper 8 bits must be connected.

FSO 101 I Fast-switch overlay between digital RGB and any video input

DB 102 I Digital BLUE input from overlay device

DG 103 I Digital GREEN input from overlay device

DR 104 I Digital RED input from overlay device

Miscellaneous Signals

RESETB 36 I Reset input, active low

PWDN 35 I Power down input

GLCO / 83 I/O

GPIO / I2CA0

GPIO / I2CA1 82 I/O

INTREQ 32 O Interrupt request output (open drain when programmed to be active low)

FSS 119 I SCART fast switch input

NC 6, 10, 20, 24 N/A No internal connection. Connect to AGND through 0.1-µF capacitors for future compatibility.

Host Interface

SDA 31 I/O I2C data bus

SCL 30 I/O I2C clock input

I/O DESCRIPTION

clock signal or 14.31818-MHz crystal oscillator.

single-ended oscillator.

Unused GPIO pins must be either configured as outputs, or tied to either IOVDD or DGND

1 = Power down

0 = Normal mode

Genlock control output (GLCO). Supports the real-time control (RTC) format. This pin can

also be configured as a general-purpose I/O (GPIO).

During power on reset this pin is sampled along with pin 82 (I2CA1) as an input to determine

the I2C address the device will be configured to. A 10-kΩ resistor pulls this either high (to

IOVDD) or low to select between addresses.

Programmable general purpose I/O

During power on reset this pin is sampled along with pin 83 (I2CA0) as an input to determine

the I2C address the device will be configured to. A 10-kΩ resistor pulls this either high (to

IOVDD) or low to select between addresses.

Copyright © 2005–2010, Texas Instruments Incorporated Introduction 15

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Table 1-1. Terminal Functions (continued)

PIN

NAME NO.

Power Supplies

A33GND 1, 26, 27, P Analog 3.3-V return. Connect to analog ground.

28, 126, 128

A33VDD 2, 25, 125 P Analog power. Connect to analog 3.3-V supply.

A18GND 12, 14, 15 P Analog 1.8-V return. Connect to analog ground.

A18VDD 11, 13, 16 P Analog power. Connect to analog 1.8-V supply.

PLL18GND 124 P Analog power return. Connect to analog ground.

PLL18VDD 123 P Analog power. Connect to analog 1.8-V supply.

DGND 29, 34, 48,66, P Digital return. Connect to digital ground.

86, 100,112,

120

DVDD 33, 47, 65,85, P Digital core power. Connect to 1.8-V supply.

99, 111

IOGND 38, 58, 75,93, P Digital power return. Connect to digital ground.

106

IOVDD 37, 57, 74,92, P Digital I/O power. Connect to digital 3.3-V supply.

105

Sync Signals

HS / CS / 117 I/O Horizontal sync output or digital composite sync output

GPIO Programmable general purpose I/O

VS / VBLK / 118 I/O Vertical sync output. (for modes with dedicated VS) or vertical blanking output

GPIO Programmable general purpose I/O

FID / GPIO 116 I/O

AVID / GPIO 115 I/O Active video indicator

SDRAM Interface

Address[11:0] 61, 77, O SDRAM address bus

62–64,

67–69, 81–78

D[15:0] 49–56, 46–39 I/O SDRAM data bus

WE 70 O SDRAM write enable

CAS 71 O SDRAM CAS enable

RAS 72 O SDRAM RAS enable

DQM 59 O SDRAM input/output mask for data

BA[1:0] 76, 73 O SDRAM bank address

SDRAM_CLK 60 O SDRAM 108-MHz clock

I/O DESCRIPTION

Unused GPIO pins must be either configured as outputs, or tied to either IOVDD or DGND

Unused GPIO pins must be either configured as outputs, or tied to either IOVDD or DGND

Odd/even field indicator

Programmable general purpose I/O This pin must be pulled low through a 10-kΩ resistor for

correct device operation.

Programmable general purpose I/O

Unused GPIO pins must be either configured as outputs, or tied to either IOVDD or DGND

www.ti.com

16 Introduction Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

Clamp

PGA

ADC

ADC1 Out

Line-Locked

Sampling Clock

M

U

X

VI_1

VI_2

VI_3

PGA

Analog_out

M

U

X

Buffer

M

U

X

VI_4

VI_5

VI_6

Clamp

Buffer

PGA

ADC

ADC2 Out

M

U

X

VI_7

VI_8

VI_9

Buffer

M

U

X

VI_10

VI_11

VI_12

Buffer

Clamp

Clamp

TVP5160

www.ti.com

2 Functional Description

2.1 Analog Processing and A/D Converters

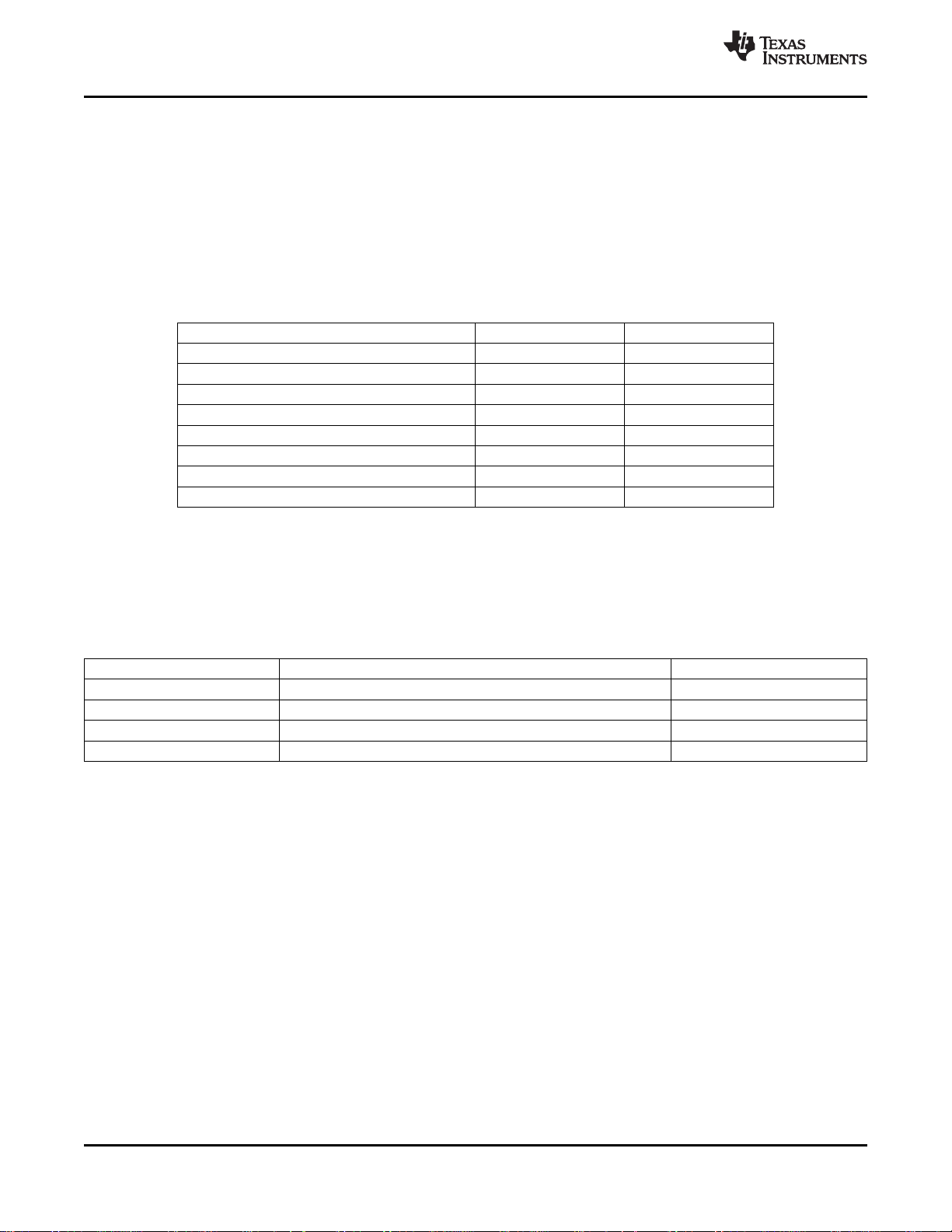

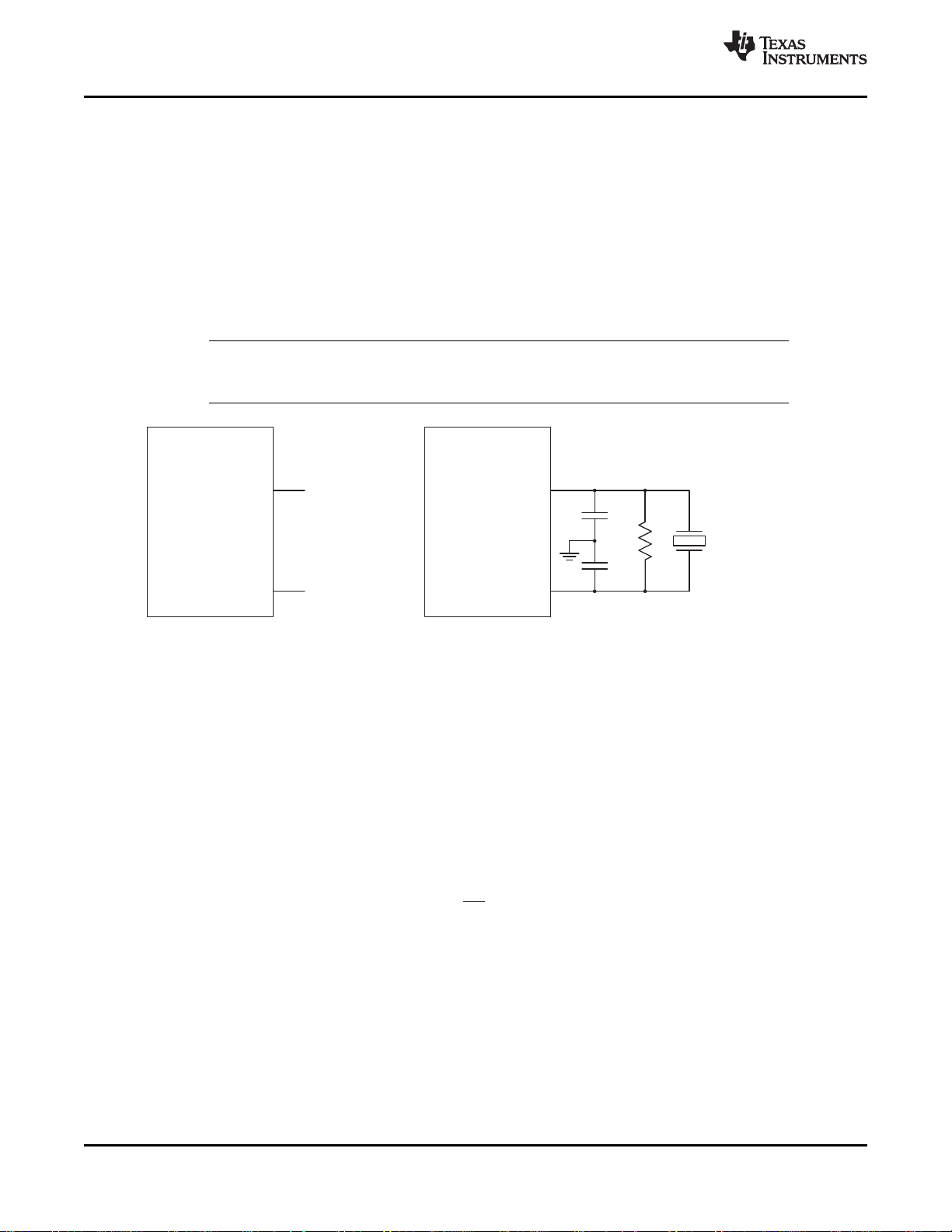

Figure 2-1 shows a functional diagram of the analog processors and A/D converters (ADCs). This block

provides the analog interface to all video inputs. It accepts up to 12 inputs and performs source selection,

video clamping, video amplification, A/D conversion, and gain and offset adjustments to center the

digitized video signal. The TVP5160 decoder supports one analog video output.

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Figure 2-1. Analog Processors and A/D Converters

Copyright © 2005–2010, Texas Instruments Incorporated Functional Description 17

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

2.1.1 Video Input Switch Control

The TVP5160 decoder has two analog channels that accept up to 12 video inputs. The user can configure

the internal analog video switches via I2C. The 12 analog video inputs can be used for different input

configurations, some of which are:

• 12 CVBS video inputs

• 4 S-Video inputs and 2 CVBS inputs

• 3 YPbPr video inputs and 3 CVBS input

• 2 YPbPr video inputs, 2 S-Video inputs, and 2 CVBS inputs

The input selection is performed by the input select register at I2C subaddress 00h.

2.1.2 480p and 576p Component YPbPr

The TVP5160 decoder supports progressive component video inputs. The YPbPr inputs of the TVP5160

decoder may accept 480p or 576p progressive inputs. The Y channel is fed into one ADC while PbPr are

sampled alternatively by the other ADC.

2.1.3 Analog Input Clamping

An internal clamping circuit restores the ac-coupled video signal to a fixed dc level. The clamping circuit

provides line-by-line restoration of the video sync level to a fixed dc reference voltage. The selection

between bottom and mid clamp is performed automatically by the TVP5160 decoder.

www.ti.com

2.1.4 Automatic Gain Control

The TVP5160 decoder utilizes two programmable gain amplifiers (PGAs); one per channel. The PGA can

scale a signal with a voltage input compliance of 0.5 VPPto 2.0 VPPto a full-scale, 11-bit, A/D output code

range. A 4-bit code sets the coarse gain with individual adjustment per channel. Minimum gain

corresponds to a code 0x0 (2.0-VPPfull-scale input, –6 dB gain) while maximum gain corresponds to code

0xF (0.5-VPPfull scale, +6 dB gain). The TVP5160 decoder also has 12-bit fine gain controls for each

channel and applies independently to coarse gain controls. For composite video, the input video signal

amplitude may vary significantly from the nominal level of 1 VPP. The TVP5160 decoder can adjust its

PGA setting automatically: an automatic gain control (AGC) can be enabled and can adjust the signal

amplitude such that the maximum input range of the ADC is reached without clipping. Some nonstandard

video signals contain peak white levels that saturate the ADC. In these cases, the AGC automatically cuts

back gain to avoid clipping. If the AGC is on, then the TVP5160 decoder can read the gain currently being

used.

The TVP5160 AGC comprises the front-end AGC before Y/C separation and the back-end AGC after Y/C

separation. The back-end AGC restores the optimum system gain whenever an amplitude reference, such

as the composite peak (which is only relevant before Y/C separation), forces the front-end AGC to set the

gain too low. The front-end and back-end AGC algorithms can utilize up to four amplitude references: sync

height, color burst amplitude, composite peak, and luma peak.

The specific amplitude references being used by the front-end and back-end AGC algorithms can be

independently controlled using the AGC white peak processing register located at subaddress 74h. The

TVP5160 gain increment speed and gain increment delay can be controlled using the AGC increment

speed register located at subaddress 78h and the AGC increment delay register located at subaddress

79h, respectively.

2.1.5 Analog Video Output

Any one of the analog input signals is available at the analog video output pin. The signal at this pin must

be buffered by a source follower if it drives a 75-Ω resister. The nominal output voltage is 2 VPP, and the

signal can drive a 75-Ω line when buffered. The magnitude is maintained with a PGA in 16 steps

controlled by the TVP5160 decoder.

18 Functional Description Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

www.ti.com

2.1.6 A/D Converters

All ADCs have a resolution of 11 bits and can operate up to 60 MSPS. All A/D channels receive an

identical clock from the on-chip, phase-locked loop (PLL) at a frequency between 24 MHz and 60 MHz. All

ADC reference voltages are generated internally.

2.2 Digital Video Processing

This block receives digitized video signals from the ADCs and performs composite processing for CVBS

and S-Video inputs, YCbCr signal enhancements for CVBS and S-Video inputs. It also generates

horizontal and vertical syncs, and other output control signals such as RTC for CVBS and S-Video inputs.

Additionally, it can provide field identification, horizontal and vertical lock, vertical blanking, and active

video window indication signals. The digital data output can be programmed to two formats: 20-bit 4:2:2

with external syncs or 10-bit 4:2:2 with embedded/discrete syncs. The circuit detects pseudo sync pulses,

AGC pulses and color striping in Macrovision-encoded copy protected material. Information present in the

VBI interval can be retrieved and either inserted in the ITU-R.BT656 output as ancillary data or stored in

an internal FIFO for retrieval via the I2C interface.

2.2.1 2x Decimation Filter

All input signals are typically oversampled by a factor of 4 (54 MHz). The A/D outputs first pass through

decimation filters that reduce the data rate to 1× pixel rate. The decimation filter is a half-band filter.

Oversampling and decimation filtering can effectively increase the overall signal-to-noise ratio by 3 dB.

SLES135C–FEBRUARY 2005–REVISED MAY 2010

2.2.2 Composite Processor

The TVP5160 digital composite video processing circuit receives a digitized composite or S-Video signal

from the ADCs and performs 2D or 3D Y/C separation (bypassed for S-Video input), chroma demodulation

for PAL/NTSC and SECAM, and YUV signal enhancements.

2.2.3 Color Low-Pass Filter

High filter bandwidth preserves sharp color transitions and produces crisp color boundaries. However, for

nonstandard video sources that have asymmetrical U and V side bands, it is desirable to limit the filter

bandwidth to avoid UV crosstalk. The color low-pass filter bandwidth is programmable to enable one of the

three notch filters.

Copyright © 2005–2010, Texas Instruments Incorporated Functional Description 19

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

2.2.4 Y/C Separation

Y/C separation may be done using 3D or 2D adaptive 5-line (5-H delay) comb filters or chroma trap filter

for both NTSC and PAL video standards as shown in Table 2-1. The comb filter can be selectively

bypassed in the luma or chroma path. If the comb filter is bypassed in the luma path, then chroma notch

filters are used. TI's patented adaptive comb filter algorithm reduces artifacts such as hanging dots at

color boundaries. It detects and properly handles false colors in high frequency luminance images such as

a multiburst pattern or circle pattern.

Table 2-1. Y/C Separation Support by Video Standard

Video Standard 2D Y/C 3D Y/C

NTSC-M Yes Yes

NTSC-J Yes Yes

PAL-B, D, G, H, I Yes Yes

PAL-N Yes Yes

PAL-M Yes No

PAL-Nc Yes No

NTSC-4.43, PAL-60 Yes No

SECAM No No

2.2.5 3D Frame Recursive Noise Reduction

www.ti.com

The TI proprietary frame recursive noise reduction or 3DNR reduces the level of noise in CVBS, S-Video,

or component inputs by comparing multiple frames of data and canceling out the resulting noise. The

3DNR utilizes the same frame buffer memory used by the 3DYC. The 3DNR may function concurrently

with 3DYC.

There are various modes of operation for the 3DNR and 3DYC:

MODES OPERATION MEMORY REQUIRED

Mode 0 3DYC + 3DNR 4 MBytes

Mode 1 3DYC only 2 MBytes

Mode 2 2D 5-line CF + 3DNR 2 MBytes

Mode 3 2D only (default None

2.2.6 Time Base Corrector

The time base corrector monitors and corrects for horizontal PLL phase offsets up to ±80 pixels. This

improves video decoder output quality by removing artifacts due to jittery horizontal syncs from broadcast

stations. It also reduces line tearing during VCR trick modes such as fast forward and rewind. 3DYC,

frame recursive noise reduction (3DNR), and time base correction (TBC) can be used simultaneously or

independently. Since TBC does not require any external memory, it can be used in all configurations.

2.2.7 IF Compensation

Attenuation of higher frequencies from the tuners input characteristics or due to channels that are not

correctly tuned can be corrected in the IF compensation block. This block can correct for uneven

sidebands resulting in incorrect and uneven UV demodulation.

20 Functional Description Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

Bandpass

Filter

x

Gain

Peaking

Filter

IN

+

OUT

Delay

Peak

Detector

TVP5160

www.ti.com

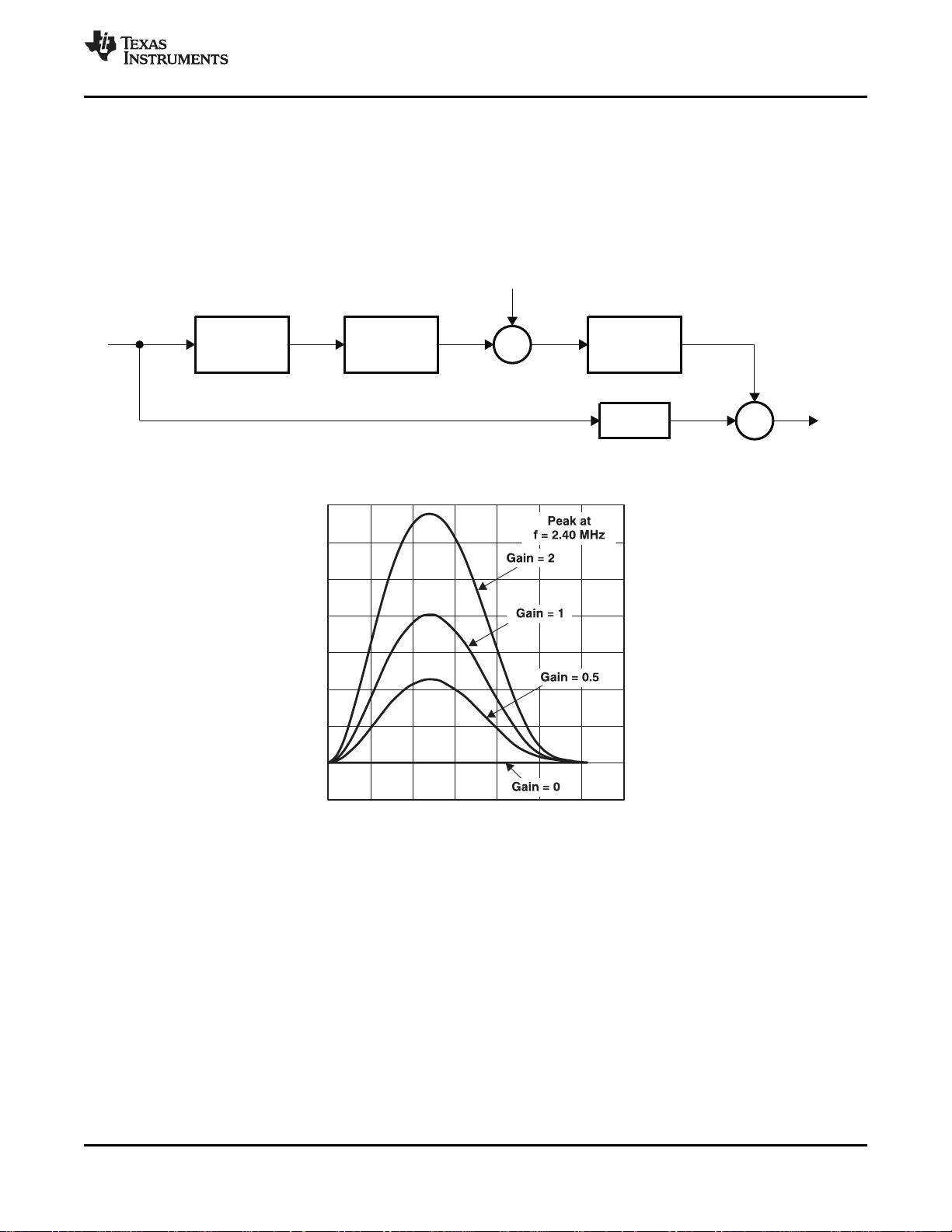

2.2.8 Luminance Processing

The luma component is derived from the composite signal by subtracting the remodulated chroma

information. The luminance signal is then fed to the input of a peaking circuit. Figure 2-2 illustrates the

basic functions of the luminance data path. In the case of S-Video, the luminance signal bypasses the

comb filter or chroma trap filter and is fed to the circuit directly. A peaking filter (edge-enhancer) amplifies

high frequency components of the luminance signal. Figure 2-3 shows the characteristics of the peaking

filter at four different gain settings that are user-programmable by the I2C.

Figure 2-2. Luminance Edge-Enhancer Peaking Block

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Figure 2-3. Peaking Filter Frequency Response NTSC/PAL ITU_R BT.601 Sampling

2.2.9 Color Transient Improvement

Color transient improvement (CTI) enhances horizontal color transients. The color difference signal

transition points are maintained, but the edges are enhanced for signals which have bandwidth limited

color components.

Copyright © 2005–2010, Texas Instruments Incorporated Functional Description 21

Submit Documentation Feedback

Product Folder Link(s): TVP5160

121

XIN

C

L1

C

L2

XOUT

122

R

TVP5160

121

XIN

XOUT

122

TVP5160

14.31818-MHz

1.8-V Clock

NC

14.31818-MHz

Crystal

33

2

= ×

CTRL

PLL SCLK

F

F F

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

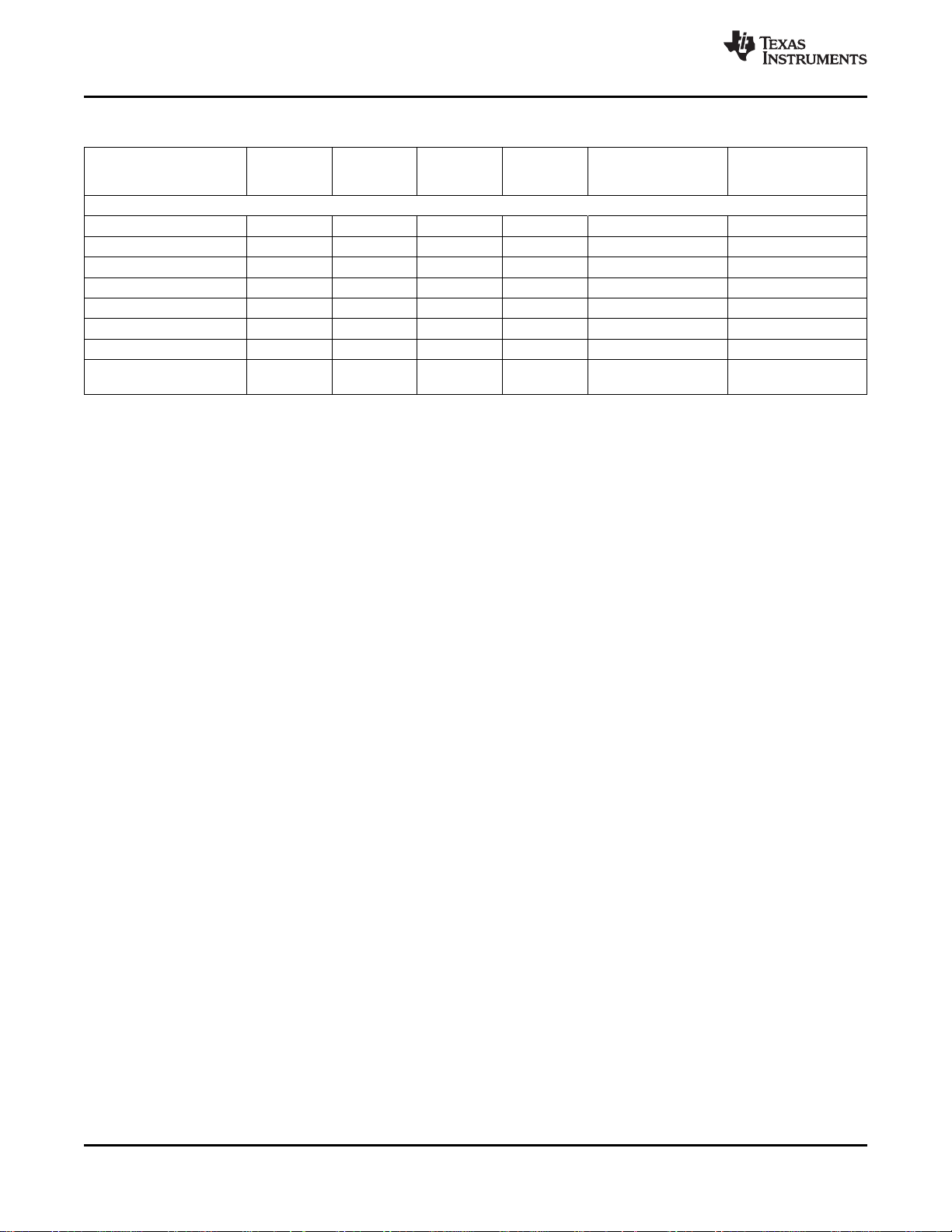

2.3 Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. A 14.31818-MHz clock is required to

drive the PLL. This may be input to the TVP5160 decoder at 1.8-V level on terminal 121 (XIN), or a crystal

of 14.31818-MHz fundamental resonant frequency may be connected across terminals 121 (XIN) and 122

(XOUT). If a parallel resonant circuit is used as shown in Figure 2-4, then the external capacitors must

have following relationship:

CL1= CL2= 2CL– C

where C

STRAY

specified by the crystal manufacturer. Figure 2-4 shows the reference clock configurations. The TVP5160

decoder generates the SCLK signal used for clocking data.

See crystal datasheet for correct loading specifications.

STRAY

is the pin capacitance with respect to ground, and CL is the crystal load capacitance

www.ti.com

NOTE

2.4 Real-Time Control (RTC)

Note: The resistor (R) in parallel with the crystal is recommended to support a wide range of crystal types. A 100-kΩ resistor

may be used for most crystal types.

Figure 2-4. Reference Clock Configuration

Although the TVP5160 decoder is a line-locked system, the color burst information is used to accurately

determine the color subcarrier frequency and phase. This ensures proper operation with nonstandard

video signals that do not follow exactly the required frequency multiple between color subcarrier frequency

and video line frequency. The frequency control word of the internal color subcarrier PLL and the

subcarrier reset bit are transmitted via the terminal 83 (GLCO) for optional use in an end system (for

example, by a video encoder). The frequency control word is a 23-bit binary number. The instantaneous

frequency of the color subcarrier can be calculated from the following equation:

where F

F

SCLK

is the frequency of the subcarrier PLL, F

PLL

is the 2× pixel frequency.

is the 23-bit PLL frequency control word and

CTRL

22 Functional Description Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

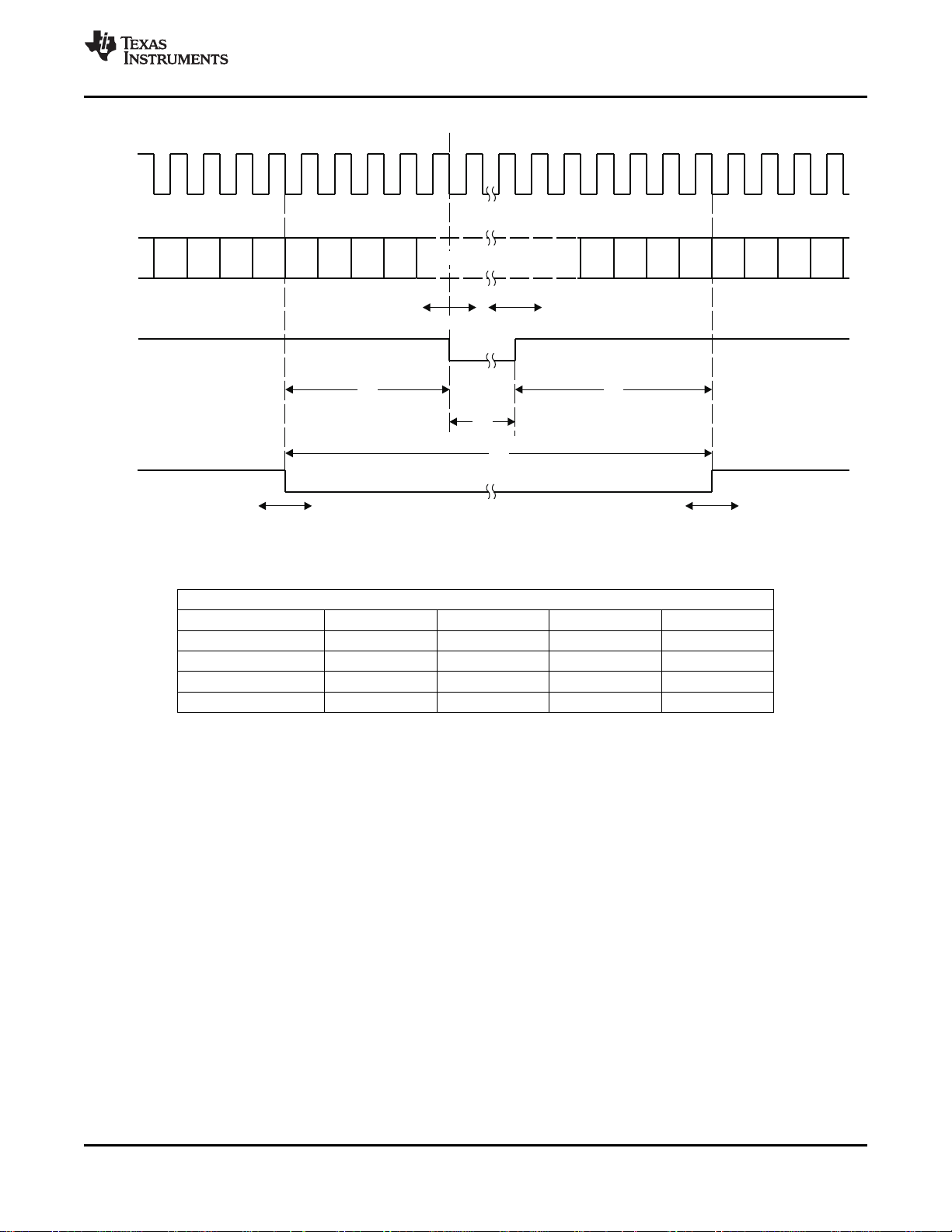

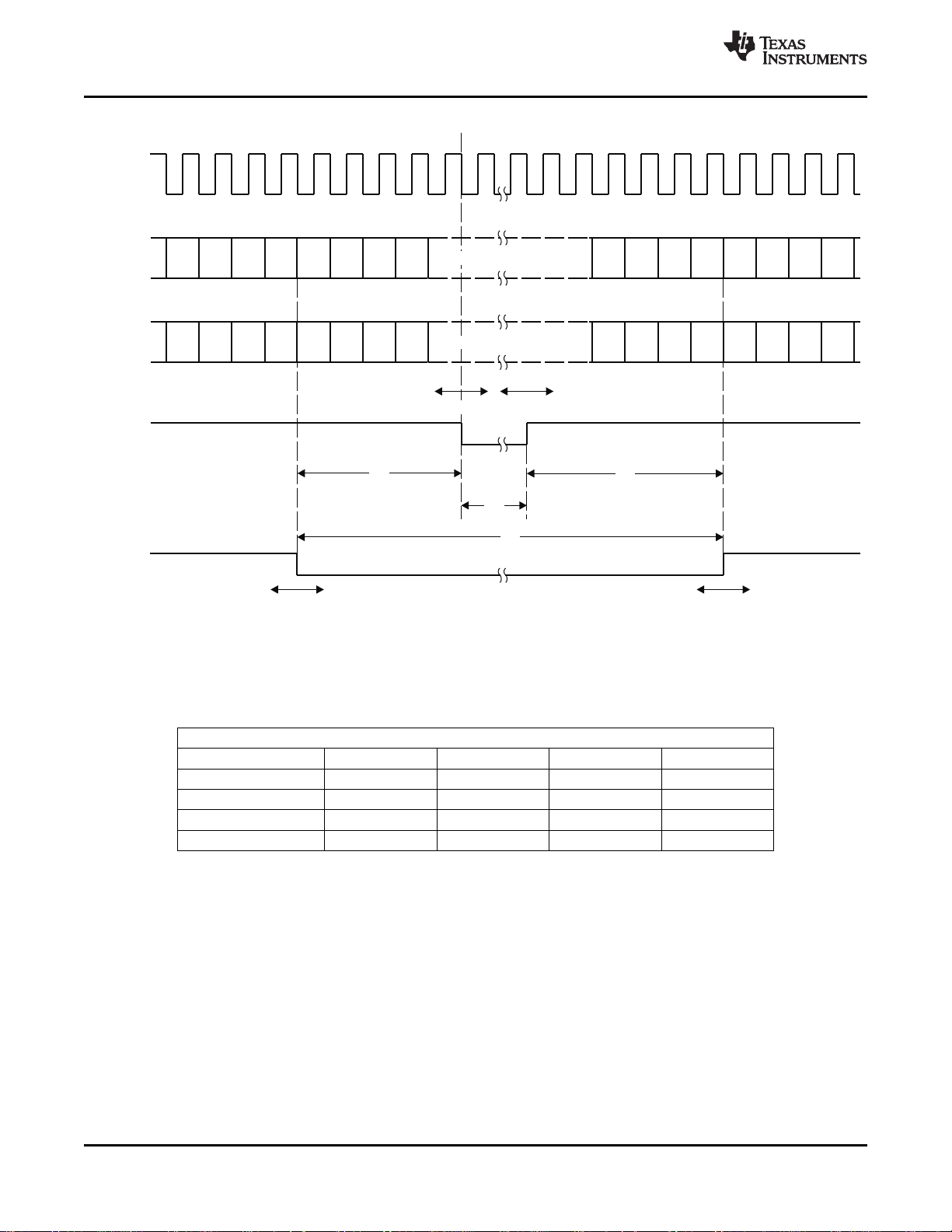

RTC

Mode

45 CLK18 CLK

L

S

B

0

3 CLK

23-Bit Fsc PLL Increment

Start

Bit

1 CLK

RS

M

S

B

22

Reserved

Valid

Sample

Valid

Sample

Valid

Sample

Valid

Sample

128 CLK

128 CLK128 CLK

TVP5160

www.ti.com

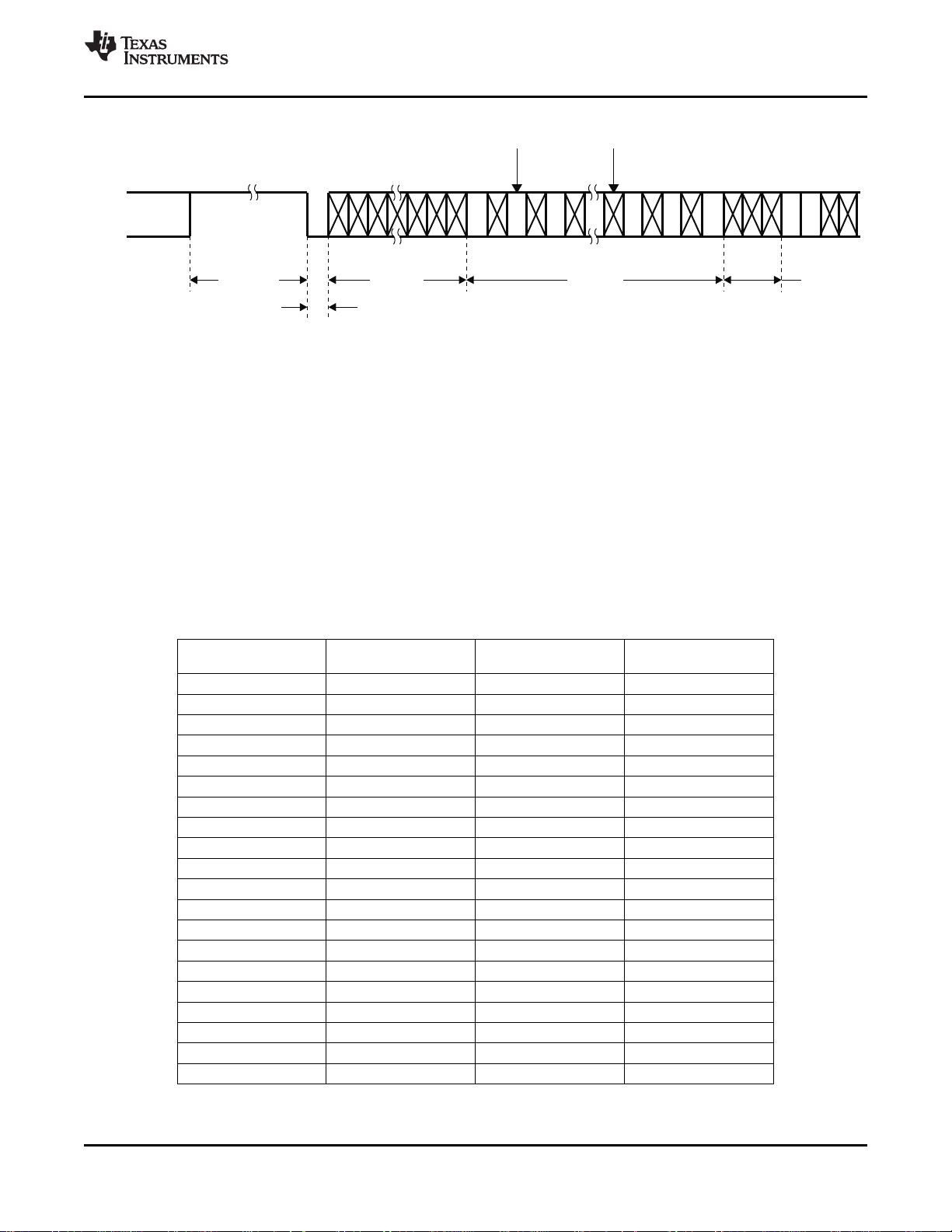

RTC: Reset bit (R) is active low 1 = (R-Y) line normal

2.5 Output Formatter

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Figure 2-5. RTC Timing

Sequence bit (S) PAL:

0 = (R-Y) line inverted

NTSC: 1 = no change

The output formatter sets how the data is formatted for output on the TVP5160 output buses. Table 2-2

shows the available output modes.

Table 2-2. Output Format

TERMINAL TERMINAL ITU-R BT.656 20-BIT 4:2:2

NAME NUMBER 10-Bit 4:2:2 YCbCr YCbCr

Y_9 87 Cb9, Y9, Cr9 Y9

Y_8 88 Cb8, Y8, Cr8 Y8

Y_7 89 Cb7, Y7, Cr7 Y7

Y_6 90 Cb6, Y6, Cr6 Y6

Y_5 91 Cb5, Y5, Cr5 Y5

Y_4 94 Cb4, Y4, Cr4 Y4

Y_3 95 Cb3, Y3, Cr3 Y3

Y_2 96 Cb2, Y2, Cr2 Y2

Y_1 97 Cb1, Y1, Cr1 Y1

Y_0 98 Cb0, Y0,Cr0 Y0

C_9 101 Cb9, Cr9

C_8 102 Cb8, Cr8

C_7 103 Cb7, Cr7

C_6 104 Cb6, Cr6

C_5 107 Cb5, Cr5

C_4 108 Cb4, Cr4

C_3 109 Cb3, Cr3

C_2 110 Cb2, Cr2

C_1 113 Cb1, Cr1

C_0 114 Cb0, Cr0

Copyright © 2005–2010, Texas Instruments Incorporated Functional Description 23

Submit Documentation Feedback

Product Folder Link(s): TVP5160

TVP5160

SLES135C–FEBRUARY 2005–REVISED MAY 2010

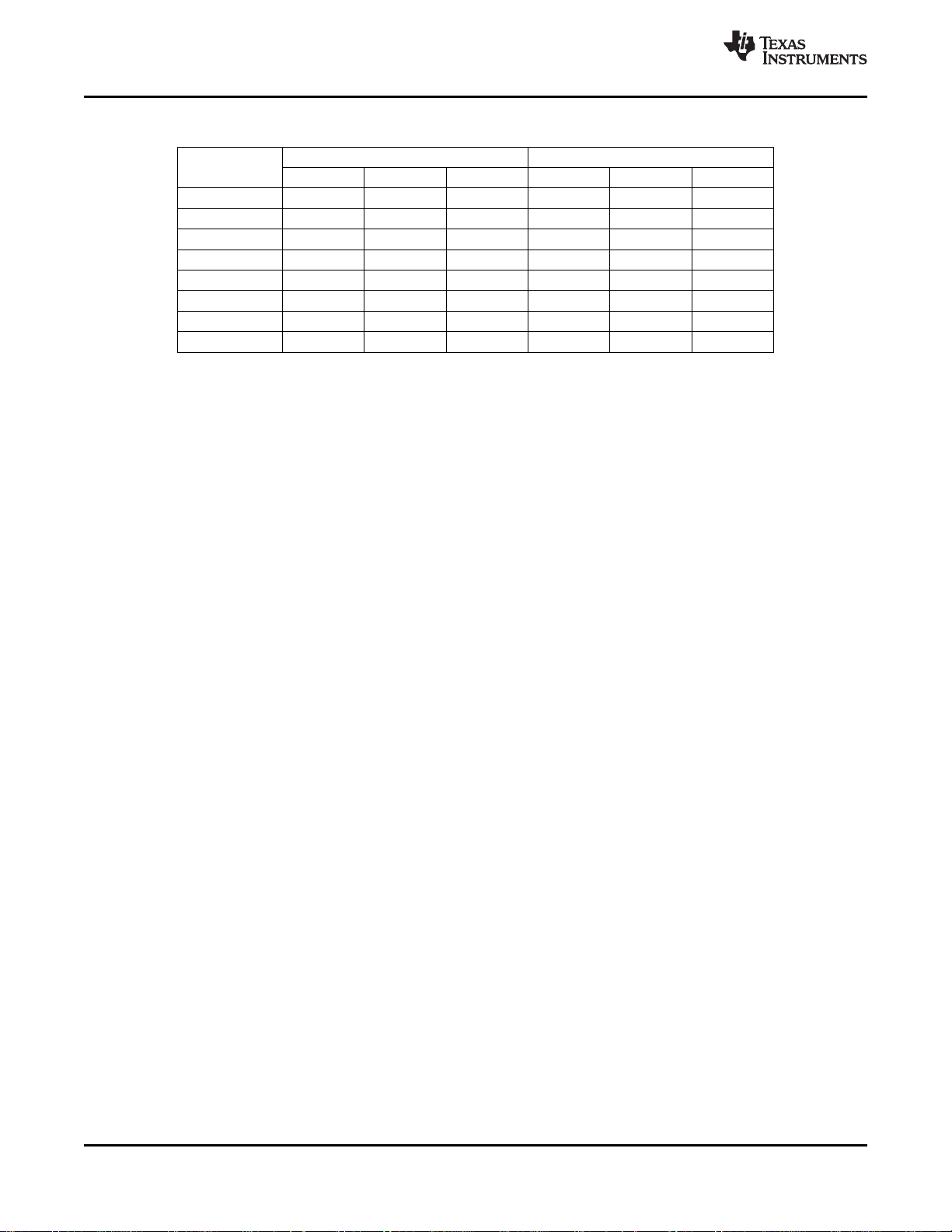

Table 2-3. Summary of Line Frequency, Data Rate, and Pixel/Line Counts

STANDARDS PIXELS SUBCARRIER

ITU-R BT.601 sampling

NTSC-J, M 858 720 525 13.5 3.579545 15.73426

NTSC-4.43 858 720 525 13.5 4.43361875 15.73426

PAL-M 858 720 525 13.5 3.57561149 15.73426

PAL-60 858 720 525 13.5 4.43361875 15.73426

PAL-B, D, G, H, I 864 720 625 13.5 4.43361875 15.625

PAL-N 864 720 625 13.5 4.43361875 15.625

PAL-Nc 864 720 625 13.5 3.58205625 15.625

SECAM 864 720 625 13.5 15.625

PIXELS LINES PER PIXEL FREQ HORIZONTAL

PER LINE FRAME (MHz) LINE RATE (kHz)

ACTIVE COLOR

PER LINE FREQUENCY (MHz)

Dr = 4.406250

Db = 4.250000

The TVP5160 input-to-output processing delay depends on the operating mode and the video standard.

When 3DYC is enabled, the processing delay is approximately 1 frame and 2-1/3 lines. When 3DYC is

disabled, the processing delay is approximately 2-1/3 lines.

www.ti.com

2.6 Fast Switches for SCART and Digital Overlay

The TVP5160 decoder supports the SCART interface used mainly in European audio/video end

equipment to carry mono/stereo audio, composite video, S-Video, and RGB video on the same cable. In

the event that composite video and RGB video are present simultaneously on the video pins assigned to a

SCART interface, the TVP5160 decoder assumes they are pixel synchronous to each other. The timing for

both composite video and RGB video is obtained from the composite source and its derived clock is used

to sample RGB video as well. The fast-switch input pin allows switching between these two input video

sources on a pixel-by-pixel basis. This feature can be used to, for example, overlay RGB graphics for

on-screen display onto decoded CVBS video. The SCART overlay control signals (FSS) are oversampled

at 4× the pixel clock frequency. The phase of this signal is used to mix between the CVBS input and the

analog RGB inputs. This improves the analog overlay picture quality when the external FSS and analog

video signals are generated by an asynchronous source. The TVP5160 decoder has two programmable

delays for component video in order to compensate for composite comb filter delays and two

programmable delays for digital RGB to compensate AFE and decimation filter delays.

If the overlay output is digital supporting 8 colors of data, the TVP5160 decoder can take digital overlay

inputs using terminals C6, C7, and C8. For this mode, output must be the 10-bit ITU-R BT.656 mode.

Figure 2-6 shows the block diagram of two fast-switches.Table 2-4 shows the fast-switch 1 and 2 controls.

24 Functional Description Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5160

B”

Prog

Delay

Color Space

Conversion

2

Gain

Output

Formatter

U

V

UV

Y

FSS’’’

FSO’’’

SCART/COMP_UV’

SCART/COMP_Y

SCART/COMP_UV

CVBS_SEP_Y

CVBS_SEP_UV

Y’’

UV’’

D

D

= User Prgrammable Delay

4

Oversample

×

R

G

B

FSS

FSO

R’

G’

B’

R”

G”

D

FSS’

FSO’

D

FSS”

FSO”

B’’’

R’’’

G’’’

SCART/COMP_Y’

Gain/Offset

Soft Mix

UV’

Y’

D

TVP5160

www.ti.com

SLES135C–FEBRUARY 2005–REVISED MAY 2010

Figure 2-6. Fast-Switches for SCART and Digital Overlay

Table 2-4. Fast-Switch Modes

MODES DESCRIPTION

000 CVBS ↔ SCART

001 CVBS, S_VIDEO ↔ Digital overlay

010 Component ↔ Digital overlay

011 (CVBS ↔ SCART) ↔ Digital overlay

100 (CVBS ↔ Digital overlay) ↔ SCART

101 CVBS ↔ (SCART ↔ Digital overlay

110 Composite