Page 1

TVP5154EVM

User's Guide

Literature Number: SLEU069A

February 2006 – Revised July 2006

Page 2

2 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 3

Contents

1 Functional Description ................................................................................................. 6

1.1 Description Overview ............................................................................................ 6

2 Board Level Description .............................................................................................. 7

2.1 Test Points and Jumpers ........................................................................................ 7

2.2 Common Board Interface ....................................................................................... 8

2.3 Video Input Description .......................................................................................... 8

2.4 Video Output Description ....................................................................................... 8

3 System-Level Description ............................................................................................ 9

4 Required Hardware and Equipment ............................................................................... 9

5 Hardware Setup .......................................................................................................... 9

6 Software Installation .................................................................................................. 10

7 WinVCC Quick Start ................................................................................................... 10

8 WinVCC in Depth ....................................................................................................... 13

8.1 Starting WinVCC ................................................................................................ 13

8.2 WinVCC Configuration Dialog Box ........................................................................... 14

8.3 I

8.4 Real-Time Polling ............................................................................................... 15

8.5 Main Menu ....................................................................................................... 16

8.6 TVP5154 Property Sheets ..................................................................................... 23

9 Programming the TMS320DM642 ................................................................................. 25

9.1 Development and Purpose of DM642 Code ................................................................ 25

9.2 Details of the DM642 Code and Control Registers ........................................................ 26

10 Troubleshooting ........................................................................................................ 33

10.1 Troubleshooting Guide ......................................................................................... 33

10.2 Corrective Action Dialogs ...................................................................................... 35

11 TVP5154EVM Schematics ........................................................................................... 37

2

C System Test................................................................................................. 14

SLEU069A – February 2006 – Revised July 2006 Table of Contents 3

Submit Documentation Feedback

Page 4

List of Figures

1 TVP5154EVM Block Diagram .............................................................................................. 7

2 Anti-Aliasing Filter Selection ................................................................................................ 8

3 TVP5154EVM System-Level Block Diagram ............................................................................. 9

4 WinVCC – I

5 Real-Time Polling Dialog .................................................................................................. 12

6 Decoder I

7 WinVCC – Main Screen ................................................................................................... 12

8 WinVCC – System Initialization .......................................................................................... 13

9 WinVCC Multiple Occurrences Error Message ......................................................................... 13

10 WinVCC I

11 I

2

C System Failure ......................................................................................................... 15

12 Real-Time Polling Dialog .................................................................................................. 16

13 WinVCC – Main Screen ................................................................................................... 16

14 Decoder I

15 System Initialization ........................................................................................................ 18

16 TVP5154 Register Map Editor ............................................................................................ 20

17 7311 Encoder Module Register Map Editor ............................................................................ 21

18 Generic I

19 Memory Map Editor ........................................................................................................ 22

20 TVP5154 Property Sheets ................................................................................................ 24

21 DM642 Control Window ................................................................................................... 26

22 I

2

C System Failure Dialog Box ........................................................................................... 35

23 Corrective Action Dialog Box ............................................................................................. 35

24 Corrective Action Required ............................................................................................... 36

25 Corrective Action Required ............................................................................................... 36

26 I

2

C Error ..................................................................................................................... 37

2

C Configuration Screen .................................................................................... 11

2

C Write and Read Enable .................................................................................... 12

2

C Address Configuration ..................................................................................... 14

2

C Write and Read Enable .................................................................................... 17

2

C Register Map Editor ......................................................................................... 22

4 List of Figures SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 5

List of Tables

1 I

2 Power-Down-Mode Selection Jumper (PDN, JP11) .................................................................... 7

3 Main Menu Summary ...................................................................................................... 16

4 TVP5154 Register Map Editor Controls ................................................................................. 21

5 Memory Map Editor Controls ............................................................................................. 23

6 Use of Property Sheet Controls .......................................................................................... 25

7 Property Sheet Button Controls .......................................................................................... 25

8 DM642 Control Window Controls ........................................................................................ 27

9 DM642 Virtual I

10 Decoder 1 Register ........................................................................................................ 28

11 Decoder 2 Register ........................................................................................................ 29

12 Decoder 3 Register ........................................................................................................ 30

13 Decoder 4 Register ........................................................................................................ 30

14 Decoder 1 Input Format Register ........................................................................................ 31

15 Decoder 2 Input Format Register ........................................................................................ 31

16 Decoder 3 Input Format Register ........................................................................................ 32

17 Decoder 4 Input Format Register ........................................................................................ 32

18 LED Control Register ...................................................................................................... 32

19 Flash Major Version Register ............................................................................................. 32

20 Flash Minor Version Register ............................................................................................. 32

21 TVP5154EVM Troubleshooting........................................................................................... 33

2

C Address Selection Jumpers (I2CSEL1, JP9 and I2CSEL2, JP10) ................................................ 7

2

C Register Map ......................................................................................... 27

SLEU069A – February 2006 – Revised July 2006 List of Tables 5

Submit Documentation Feedback

Page 6

1 Functional Description

The TVP5154EVM evaluation module is a printed circuit board designed for evaluation of the TVP5154

quad video decoder. The board includes the TMS320DM642 digital signal processor (DSP) and is

designed with a 120-pin connector, which allows a connection to multiple backends; the evaluation module

(EVM) is shipped with a professional encoder module. The board is designed to provide ease of use, while

allowing full evaluation of the video decoder.

1.1 Description Overview

The TVP5154EVM uses the PC parallel port to emulate the I2C bus, which provides communication with

the TVP5154 video decoder, DM642, and the video encoder. The Windows™ Video Control Center

(WinVCC) application software that communicates with the devices via the I2C is provided on the EVM

CD-ROM.

The analog video inputs supported by the TVP5154EVM include composite video and S-video. More detail

about the video inputs is discussed in section 2.3 Video Input Description. In general, the video decoder

converts the analog video input signal into digital component data. This data and the associated clocks

from the video decoder are sent to the DM642, which provides various image capture and display modes.

The DM642 is setup in I2C slave mode and is controlled through virtual I2C registers. The video encoder

then converts the digital data from the DM642 back into analog video. The analog video outputs supported

by the EVM include composite video, S-video, and component video. These are all output simultaneously.

To experiment with the programmable features of the TVP5154 video decoder and the video encoder, the

parallel port of the TVP5154 is connected to the parallel port of a PC. WinVCC, a Windows-compatible

application provides the user interface for performing register-level and high-level control of the TVP5154

video decoder and the video encoder.

User's Guide

SLEU069A – February 2006 – Revised July 2006

TVP5154EVM User's Guide

Code Composer Studio is a trademark of Texas Intruments.

All other trademarks are the property of their respective owners.

TVP5154EVM User's Guide6 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 7

www.ti.com

2 Board Level Description

Board Level Description

The TVP5154EVM consists of the TVP5154EVM module and the encoder EVM module. A 4-row 120-pin

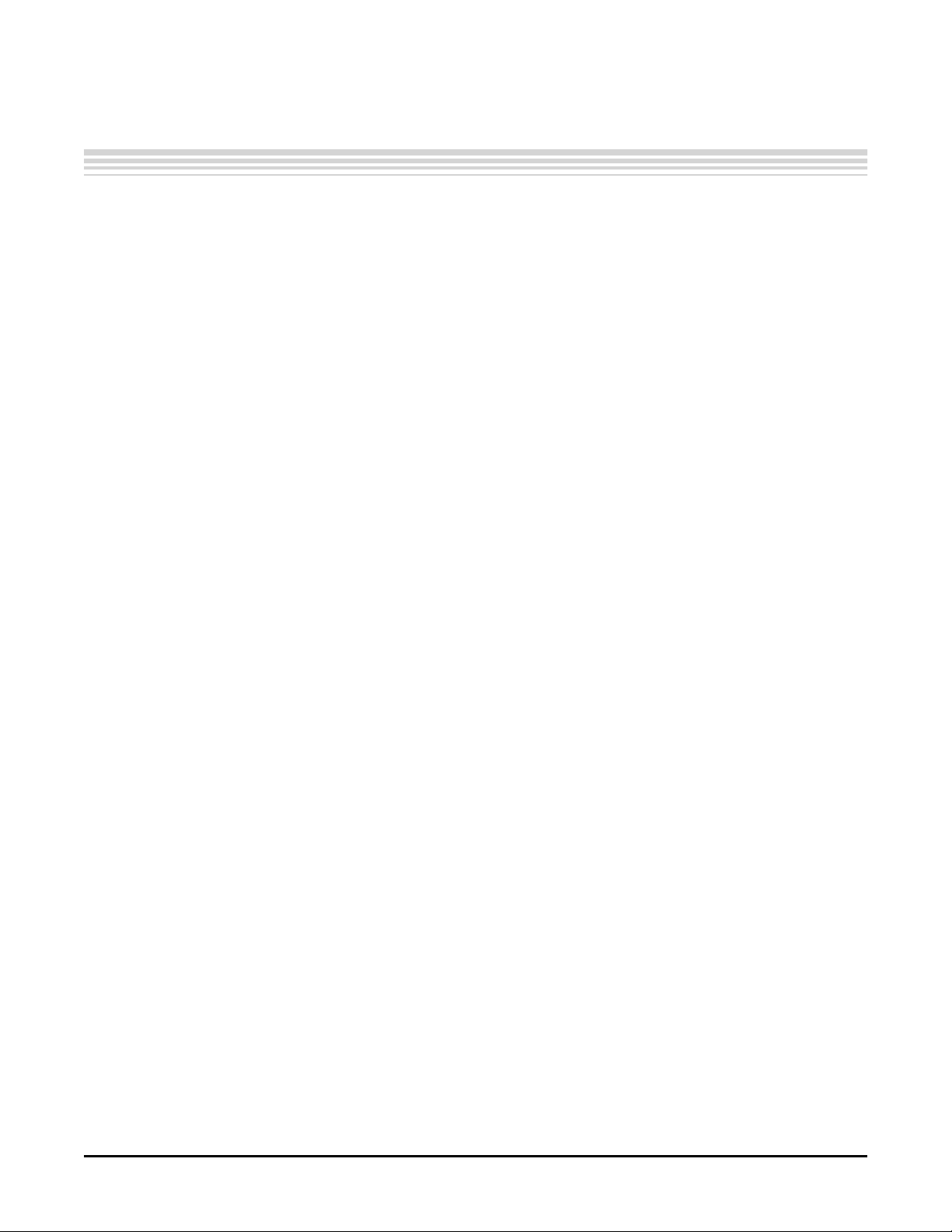

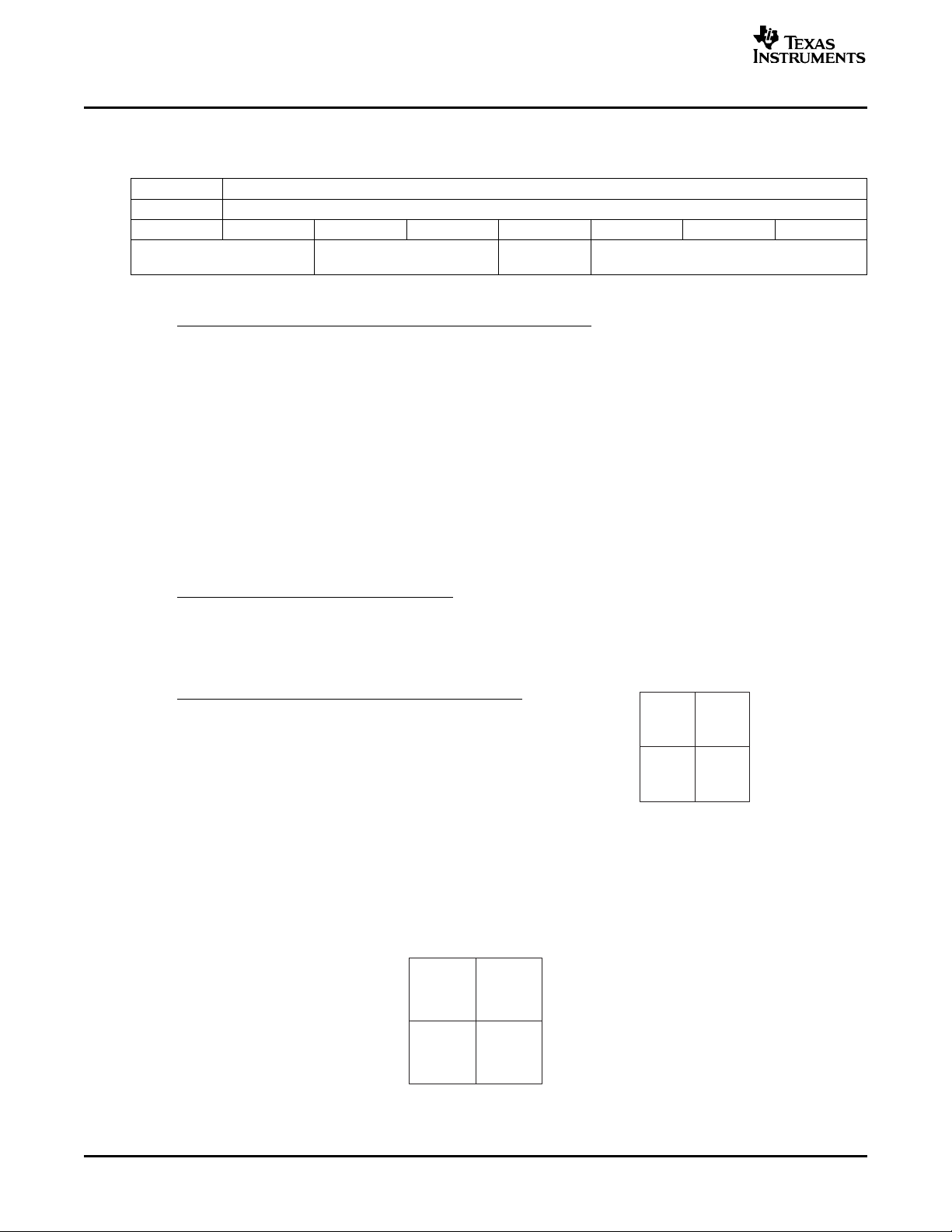

connector connects the boards. The block diagram of the EVM set is shown in Figure 1 .

2.1 Test Points and Jumpers

The TVP5154EVM was designed with test points and jumpers to help in evaluation and troubleshooting.

Each jumper is set by default in its preferred state for the TVP5154EVM. There are test points for SCL,

SDA, 3.3 V, and 1.8 V. All digital video data for each decoder core are brought out to a dual-row header,

which allows easy hookup to test equipment. The I2C address selection is made with two shunt jumpers,

which are only read after a reset or at power up. The default address is 0xB8. If the address needs to be

changed, the TVP5154 must receive a reset.

Figure 1. TVP5154EVM Block Diagram

Table 1. I2C Address Selection Jumpers

(I2CSEL1, JP9 and I2CSEL2, JP10)

JP9 JP10 I2C ADDRESS

2-3 2-3 0xB8

1-2 2-3 0xBA

2-3 1-2 0xBC

1-0 1-2 0xBE

Table 2. Power-Down-Mode Selection Jumper

(PDN, JP11)

PWDN

1-2 Normal operation

2-3 Power down

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 7

Submit Documentation Feedback

Page 8

www.ti.com

Board Level Description

Note: If the I2C address is changed on either the TVP5154 board or the encoder board while the

2.2 Common Board Interface

The TVP5154EVM uses a 4-row 120-pin connector to share common signals and the 5-V power supply

between the boards. This connection allows multiple backends to be connected to the TVP5154EVM. The

EVM package is shipped with an encoder module. This connector shares all digital video bits (Y[7:0]), all

video clocks (VS, HS, GLCO/FID, and DATACLK), 5 V, ground, I2C bus (SCL and SDA), and reset.

2.3 Video Input Description

The TVP5154EVM decoder has an analog input channel that accepts two video inputs for each decoder

core. The decoder supports a maximum input voltage range of 0.75 V, therefore, an attenuation of

one-half is needed for most input signals with a peak-to-peak variation of 1.5 V. The parallel termination

before the input to the device is 75 Ω . The two analog inputs can be connected as either two selectable

composite video inputs, or one S-video input.

The TVP5154EVM allows the user to have up to two composite inputs or one S-video input for each of the

four-channels. The EVM software sets up and controls this input selection. The S-video input uses two

connectors, one for the luma channel and one for the chroma channel.

The EVM has a resistor network on each of the inputs. These networks attenuate the signal and allow a

75- Ω resistor to ground to be placed after the anti-alias filter for termination.

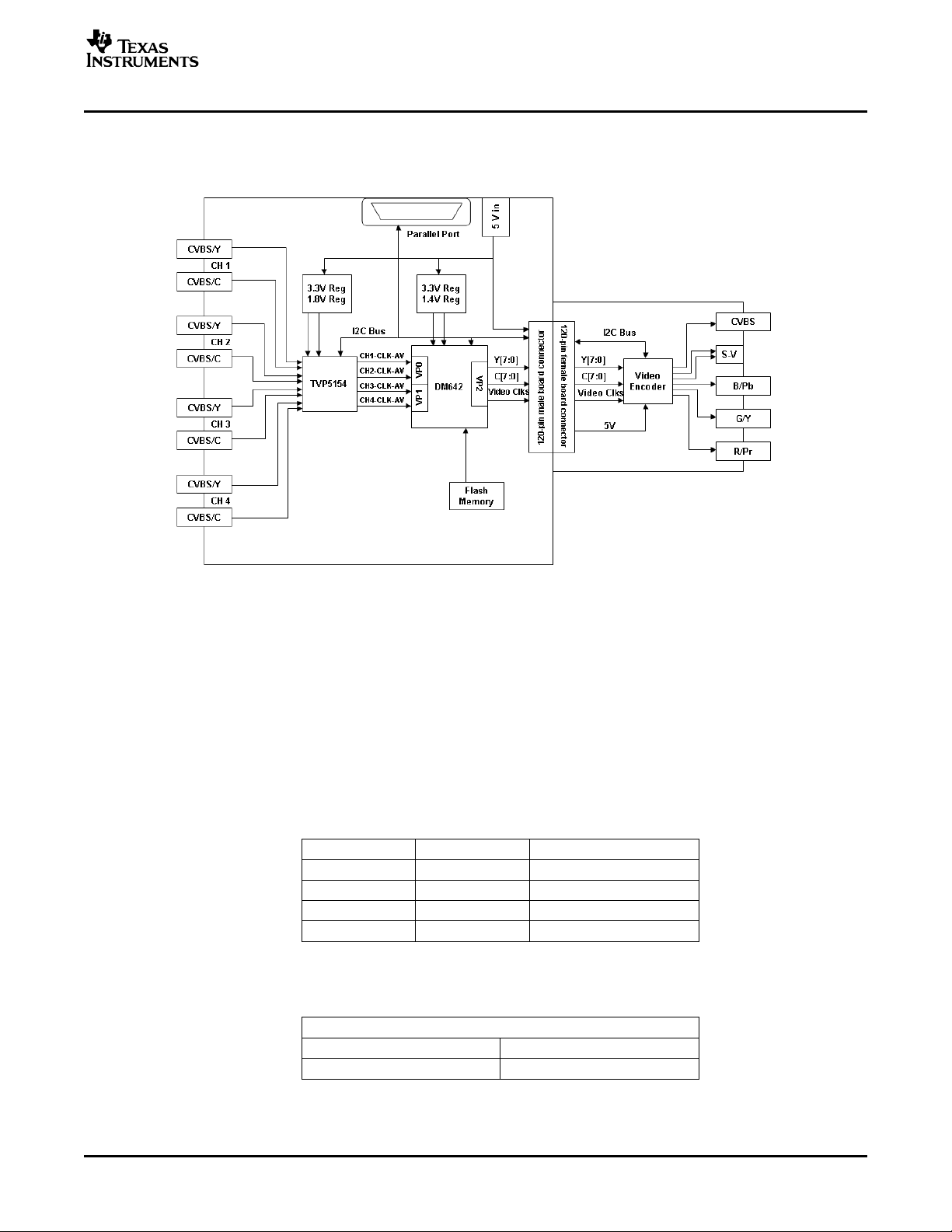

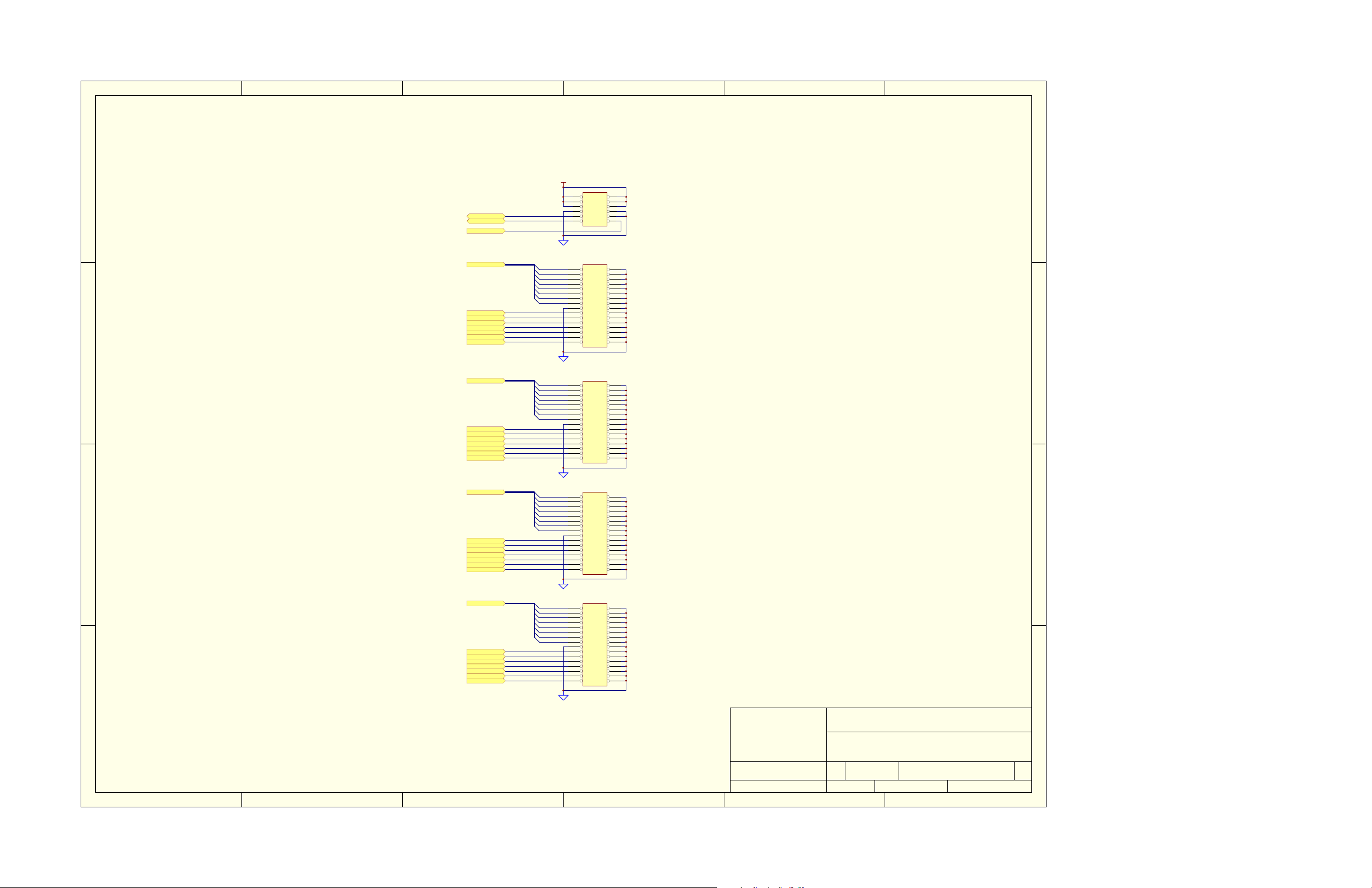

Each input has an anti-alias filter that can be in-circuit or bypassed by jumpers (JP1–JP8). To select the

filter, the shunts need to be positioned to short positions 1-3 and 2-4. To bypass the filter, the shunts need

to be moved to short positions 1-2 and 3-4 as shown in Figure 2 . The boards are shipped with the filter

bypassed.

TVP5154EVM is powered up, that device will not recognize the new I2C address. The reset

button on the TVP5154EVM must be pressed and WinVCC must be reconfigured for the new

I2C address.

Figure 2. Anti-Aliasing Filter Selection

2.4 Video Output Description

The 8-bit digital video outputs of the TVP5154 are routed to the four 32-pin headers (H2–H5), the DM642,

and finally to the 120-pin edge connector along with all video clocks on the TVP5154 module. The

encoder module connects to the 120-pin connector, and is capable of receiving digital video with or

without embedded syncs. The analog outputs of the encoder module are composite, S-video, and

component. For the user’s convenience, all of these outputs come out of the encoder module

simultaneously.

TVP5154EVM User's Guide8 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 9

www.ti.com

3 System-Level Description

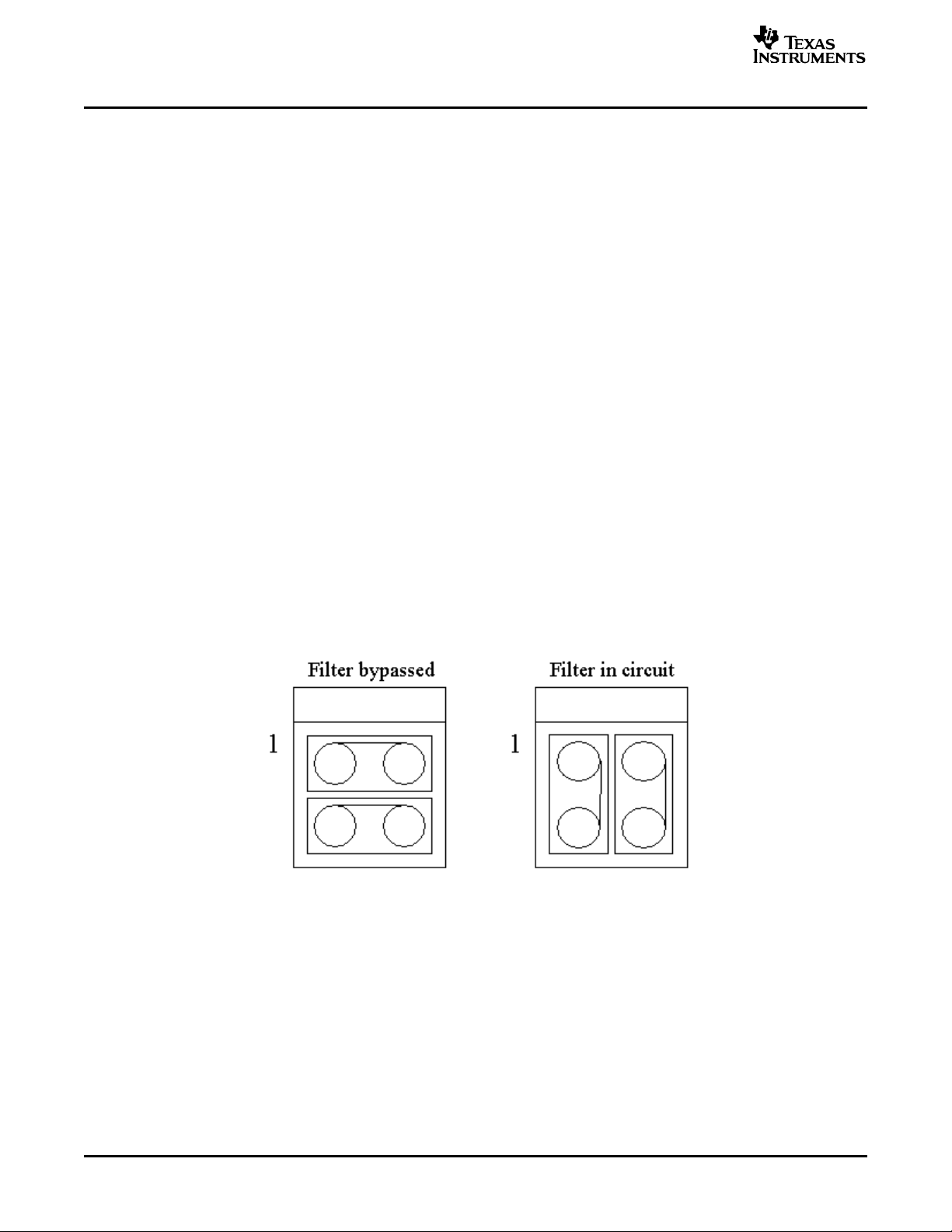

A system-level block diagram incorporating the TVP5154 is shown in Figure 3 . Typical

commercially-available test equipment is also shown. The primary features of this configuration are:

• Power is provided by a single 5-V power supply provided with the EVM and is shared between both

• Supported analog inputs include composite video and S-video.

• Re-encoded composite video and S-video are output via the encoder module.

• Component (YPbPr) video is output via the encoder module.

• I2C bus initializes the video devices via a PC parallel port.

• The TVP5154 video decoder performance parameters may be measured with a video analyzer.

System-Level Description

modules via the 120-pin connector.

4 Required Hardware and Equipment

The required hardware and equipment necessary to use the TVP5154EVM are:

• TVP5154EVM (provided)

• Universal 5-V power supply (provided)

• Parallel cable (provided)

• Windows-based PC with CD-ROM drive and Win95™ or later

• Composite or S-video cables for inputs

• Composite, S-video, or component cable for output

• Video sources (security camera, pattern generator, Quantum generator, DVD player, etc.)

• Display monitor that supports composite, S-video, or component video input

5 Hardware Setup

Figure 1 shows the TVP5154EVM layout and indicates the location of the power supply and the

appropriate connectors. All connectors are labeled according to their function. To prepare the EVM for

evaluation, connect the following:

1. TVP5154 module to encoder module

2. Parallel port cable from TVP5154EVM to the PC

3. Analog video sources to TVP5154EVM inputs

4. Analog video out from TVP5154EVM to monitor

5. 5-V power supply to the dc jack on the TVP5154 board. A green LED on each board should now be lit.

Figure 3. TVP5154EVM System-Level Block Diagram

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 9

Submit Documentation Feedback

Page 10

www.ti.com

Software Installation

6 Software Installation

The system comes with the anti-alias filters bypassed. To connect the filters, you must rotate the

appropriate jumpers (JP1–JP8) as described in section 2.3.

The I2C slave address can be selected with jumpers JP9 and JP10. There are four possible addresses:

B8, BA, BC, and BE. The default setting for these jumpers is for the shunt to short pins 2-3, which selects

0xB8. These are connected to pins 117 and 118, which are read at power up. If you move both the

jumpers to positions 1-2 and reset the board, the video decoder now responds to I2C slave address 0xBE.

If you choose to change the address, you must exit, restart WinVCC, and configure the software to use

the new I2C slave address.

WinVCC is a Windows application that uses the PC parallel port to emulate I2C, providing access to each

device on the I2C bus. WinVCC makes use of CMD files, a text editable file that allows preset video

setups to be programmed easily.

This feature allows the user to easily set multiple I2C registers with the press of a button. WinVCC also

has property sheets for the TVP5154, which allows the user to control the I2C registers with a GUI.

All necessary software for the TVP5154EVM is provided on the enclosed CD. Perform the following steps

to install WinVCC:

1. Explore the provided TVP5154EVM Software CD.

2. Install Port95NT.exe. This is the parallel port driver used by WinVCC. This driver must be installed and

the PC must be rebooted before WinVCC operates correctly. This does not affect normal parallel port

operation.

3. Install Setup.exe. Click Next at all prompts and click Finish to complete the installation process. This

installs WinVCC onto the PC. No reboot is required.

4. Run WinVCC.exe.

Note: A shortcut to WinVCC should now be available on the desktop. WinVCC and additional

7 WinVCC Quick Start

Perform the following steps in order to see a video output from the TVP5154EVM.

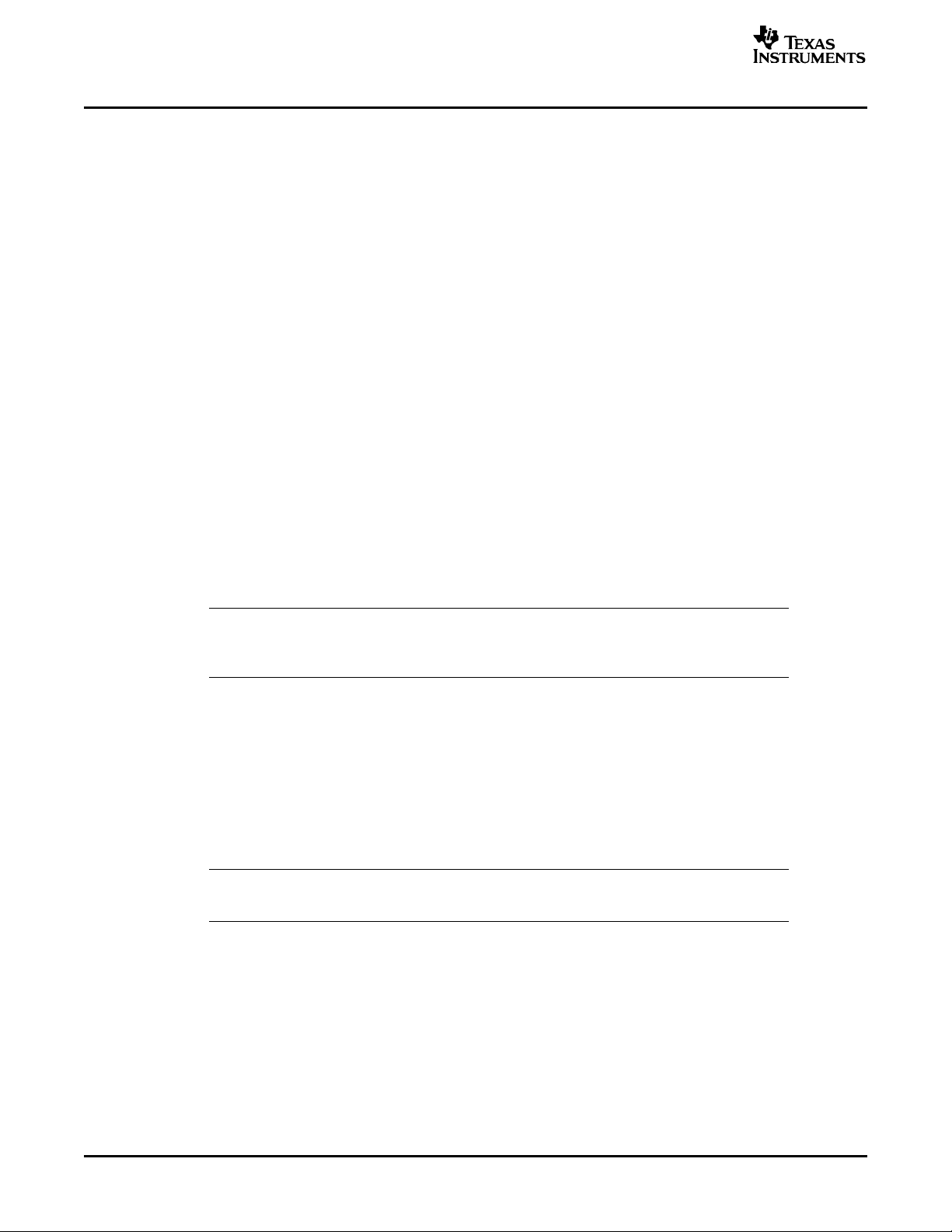

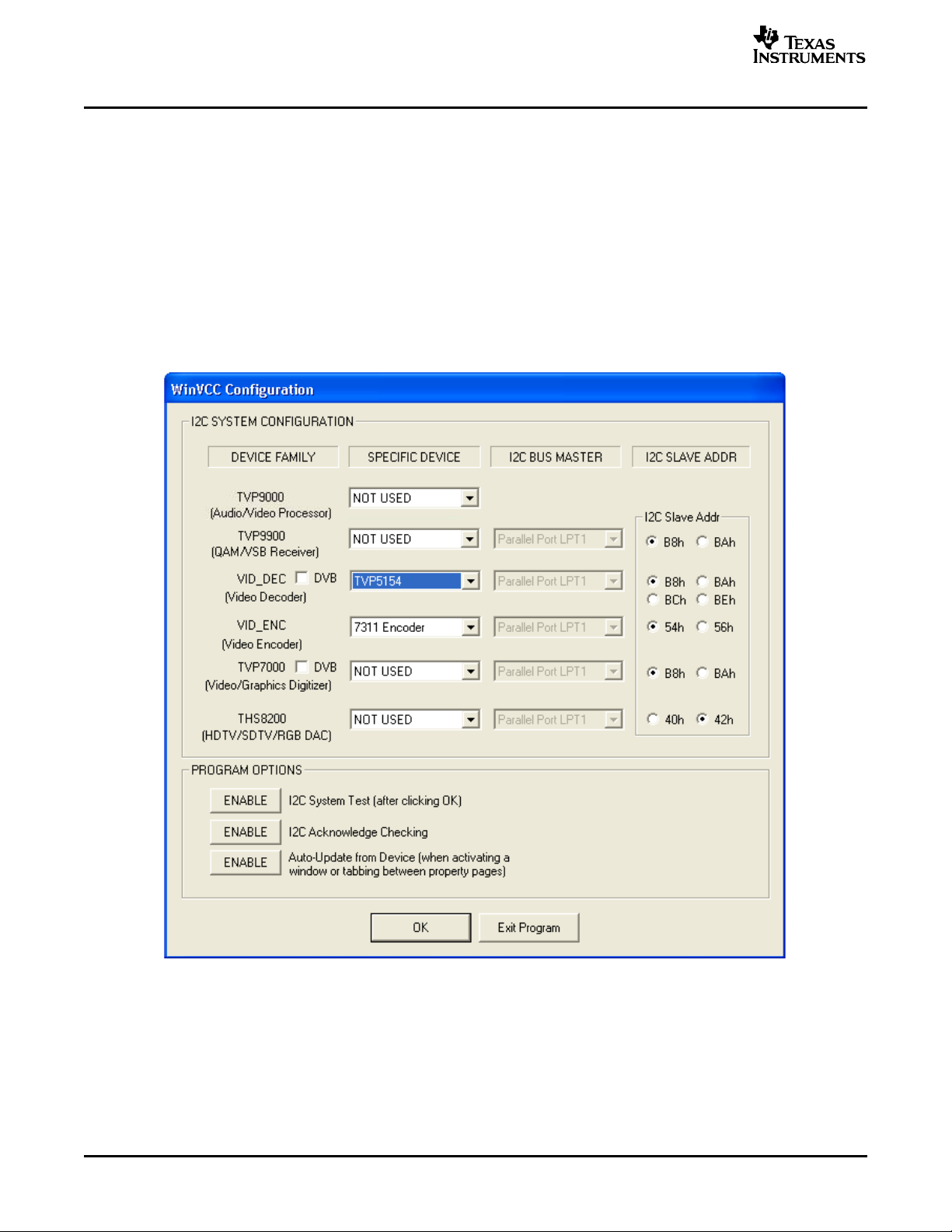

1. Once WinVCC is executed, the WinVCC Configuration screen appears, as shown in Figure 4 . This

dialog box configures the I2C bus. Next to VID_DEC, select the TVP5154 and ensure the I2C address

is set to 0xB8 (default setting on EVM.) This must match the I2C ADDR jumper on the TVP5154 board.

2. Next to VID_ENC, select the 7311 Encoder and ensure the I2C address is set to 0x54 (default setting

on EVM.) This must match the I2C ADDR jumper on the encoder board.

Note: If WinVCC is running and the TVP5154 or encoder board I2C address is changed, power

TVP5154-related documentation can also be found at Start → Programs → TVP5154EVM

Software.

must be cycled on the EVM.

10 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 11

www.ti.com

WinVCC Quick Start

Figure 4. WinVCC – I2C Configuration Screen

3. Ensure that all other boxes are selected as “Not Used” and that all program options buttons are set to

ENABLE. Click OK.

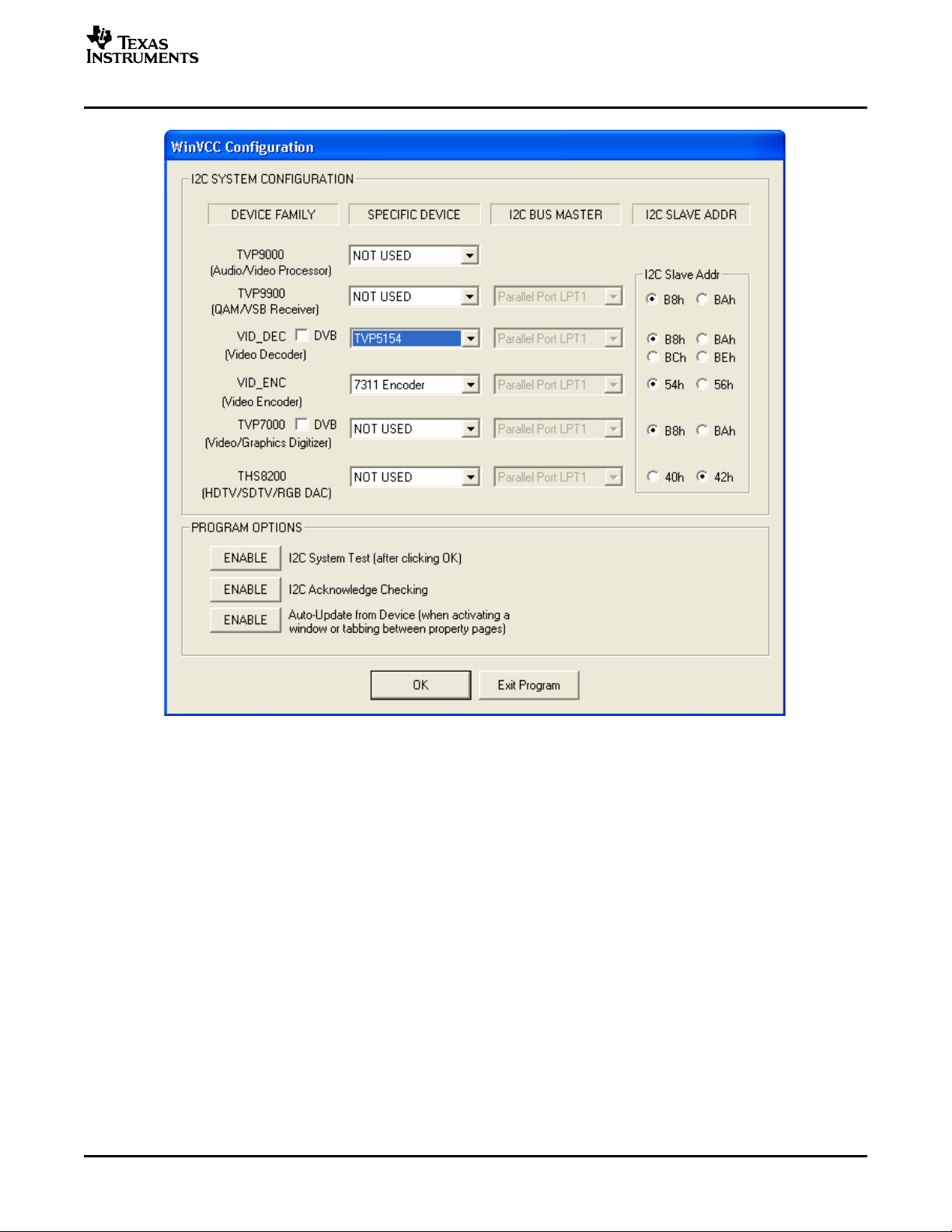

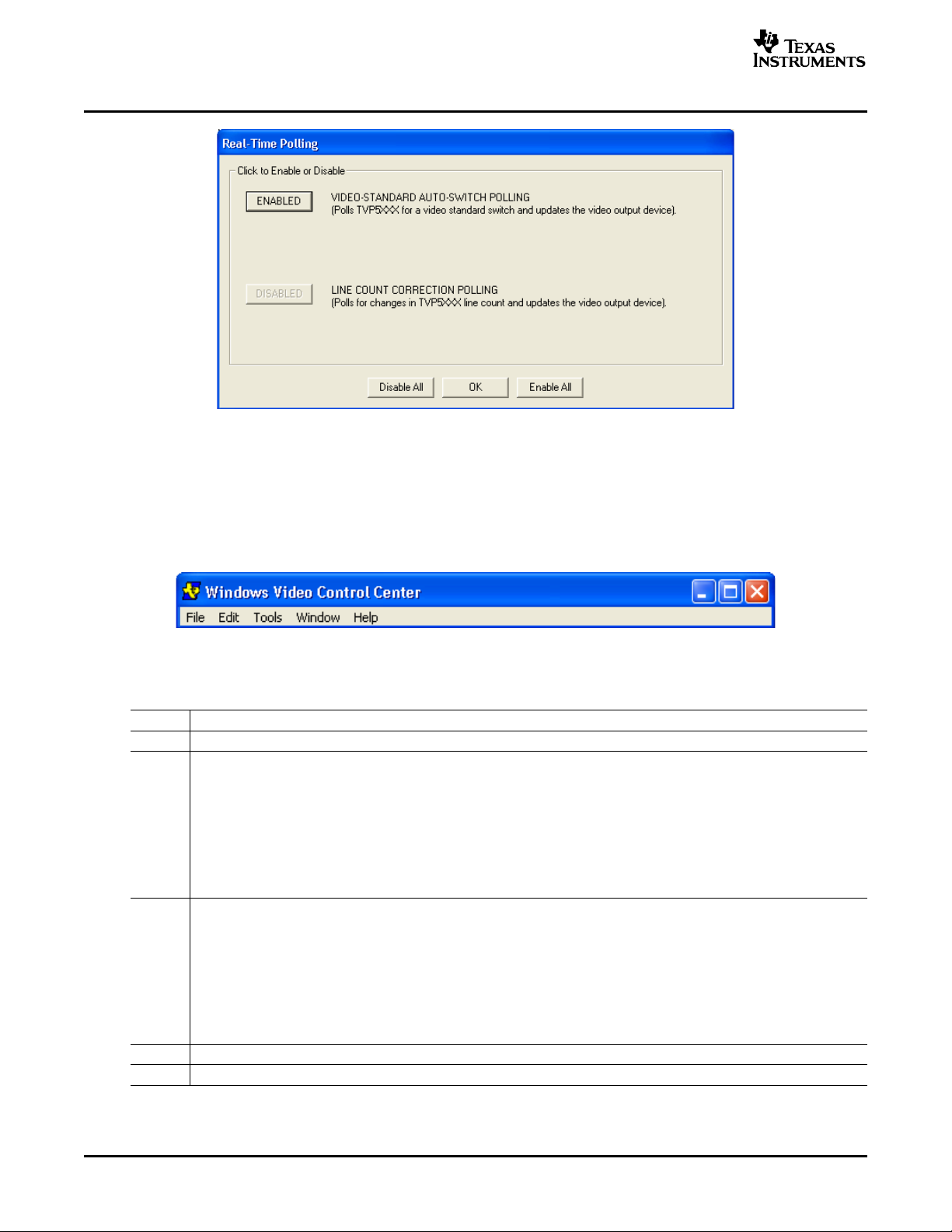

4. If there are no I2C communication issues, the Real-Time Polling dialog window displays next as shown

in Figure 5 . If there are I2C issues, an I2C Test Report box displays. Completely exit out of WinVCC,

double-check the parallel port cable connections, I2C address settings, cycle power on the

TVP5154EVM, and re-run WinVCC.

5. When using the TVP5154 EVM with a composite output from the 7311 encoder, it is required to disable

auto-switch polling in the Real-Time Polling dialog box by clicking on the ENABLED button. Click OK

and then the Main Control Window is seen, as shown in Figure 7 .

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 11

Submit Documentation Feedback

Page 12

www.ti.com

WinVCC Quick Start

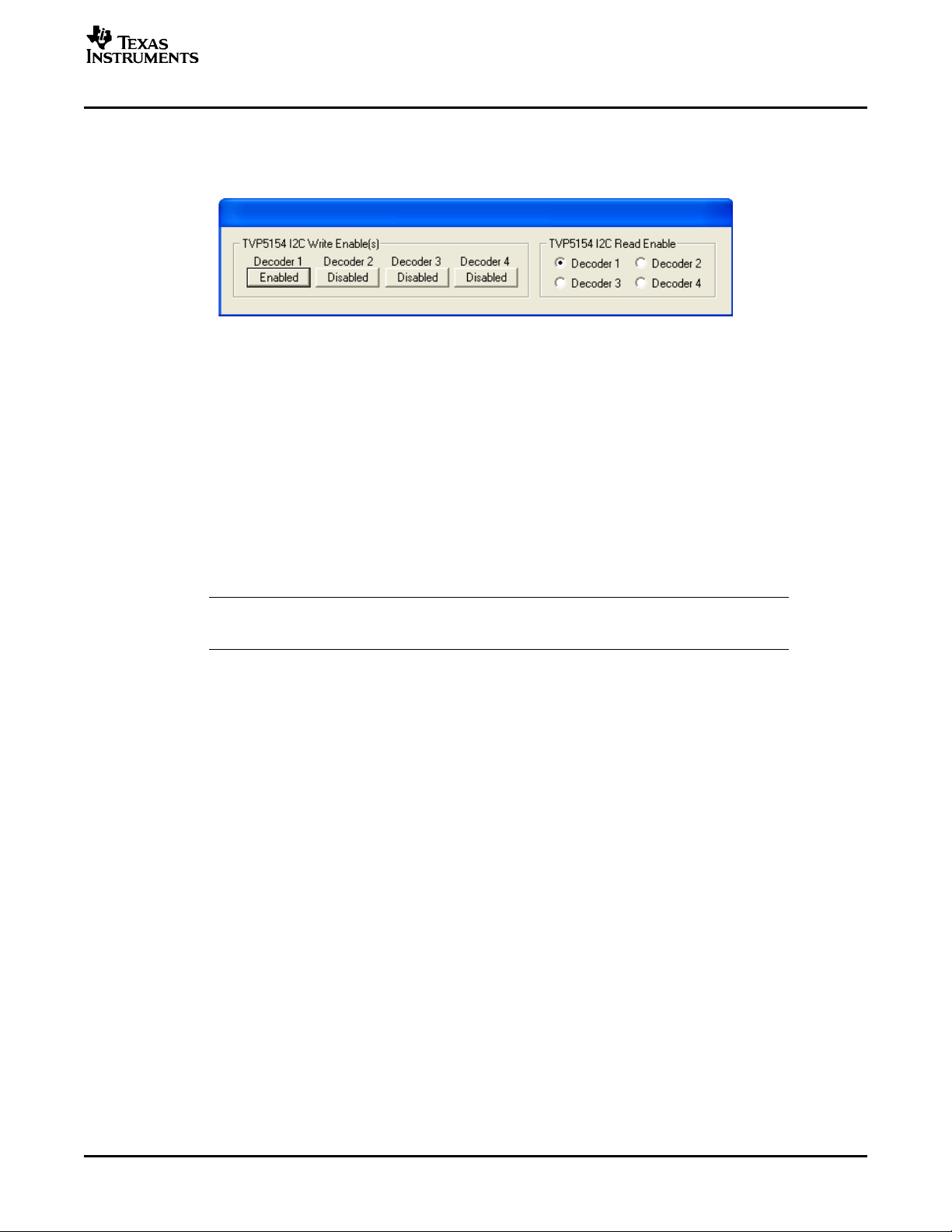

6. The TVP5154 I2C Write Enable(s) and Read Enable pop-up window is displayed as shown in Figure 6 .

Figure 5. Real-Time Polling Dialog

This is used to select which decoder or decoders (any combination of all four) will receive I2C Write

commands, and which decoder (only one) will receive I2C Read commands. Decoder 1 is Enabled by

default; enable the other three decoders by clicking on each decoder’s enable button.

Figure 6. Decoder I2C Write and Read Enable

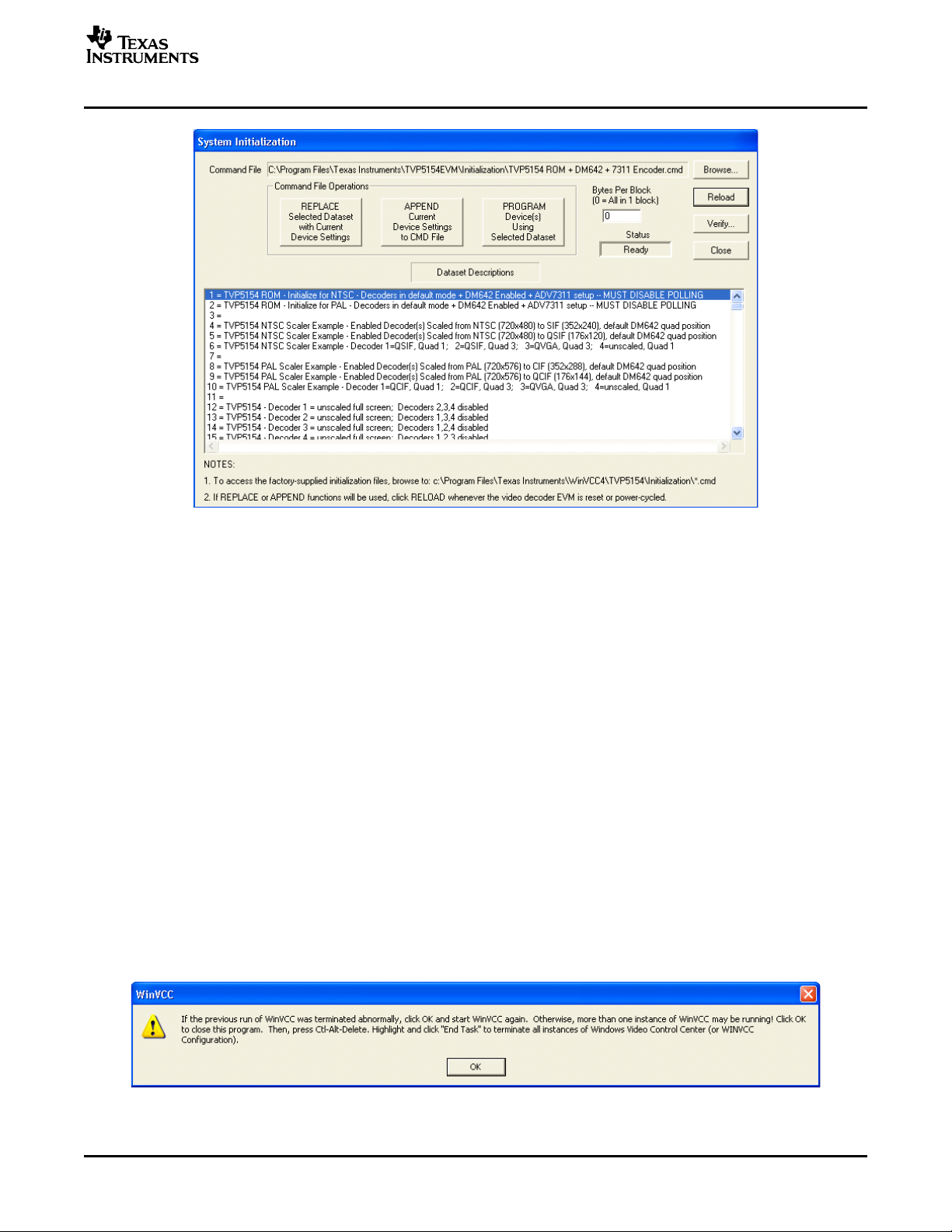

7. Load the provided Initialization command (CMD) file into WinVCC by clicking on Tools → System

Initialization → Browse. The default directory is C:\Program Files\Texas

Instruments\TVP5154EVM\Initialization.

Figure 7. WinVCC – Main Screen

8. In the System Initialization Window (see Figure 8 ), click the “TVP5154 ROM – Initialize for NTSC...” or

“TVP5154 ROM – Initialize for PAL...” dataset in the window and then click the PROGRAM Device(s)

Using Selected Dataset button to initialize the TVP5154EVM.

12 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 13

www.ti.com

Figure 8. WinVCC – System Initialization

WinVCC in Depth

9. With video sources provided at the BNC connectors and the EVM output connected to a monitor, video

from the source connected to CH1 should be viewable on the display monitor.

10. The other datasets in the command file are provided to demonstrate examples of 5154 scaling

performance. Refer to the TVP5154 data sheet (SLES163) or Scaler application report for more details

on programming the TVP5154 scaler. The DM642 settings can be controlled by using the DM642

Control Window, which is found by clicking on Tools → DM642 Control. Refer to Chapter 9 for details on

programming the DM642 through this window or through the Generic I2C registers.

8 WinVCC in Depth

The following sections describe how to use Windows™ Video Control Center (WinVCC) in depth. It

discusses various features and screens that the user may encounter while evaluating the TVP5154EVM.

8.1 Starting WinVCC

The Port95NT parallel port driver must be installed before using WinVCC. WinVCC may be started by

clicking on Start → All Programs → TVP5154EVM Software → WinVCC.

If the dialog box shown in Figure 9 is displayed, it means one of two things:

• WinVCC did not run to completion the last time it ran. In this case, click OK to exit the program and

restart WinVCC.

• There is more than one instance of WinVCC running at the same time. In this case, click OK to exit the

program. Then, press CTRL-ALT-DELETE to bring up the Task Manager. Select and click End Task

on all occurrences of WinVCC or WinVCC CONFIGURATION. Then restart WinVCC.

Figure 9. WinVCC Multiple Occurrences Error Message

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 13

Submit Documentation Feedback

Page 14

www.ti.com

WinVCC in Depth

8.2 WinVCC Configuration Dialog Box

The WinVCC Configuration dialog box (see Figure 10 ) should now be visible. This dialog box configures

the I2C bus on the TVP5154EVM. All settings from this dialog box are stored in the Windows registry and

are restored the next time the program is started. After initial installation, VID_DEC is set to TVP5154 and

VID_ENC is set to 7311 Encoder.

The I2C slave address for each device must match the I2C slave address selected by jumpers on the

TVP5154EVM. These jumpers are set by the factory to use 0xB8 for the TVP5154 and 0x54 for the

Encoder. It is also important to select the correct Specific Device type for the video decoder. TVP5154 and

7311 Encoder must be selected for this EVM.

All Program Options must be enabled. Disabling these options is only required if debugging a problem

with the I2C bus.

Clicking OK begins I2C communication with the selected devices.

Figure 10. WinVCC I2C Address Configuration

8.3 I2C System Test

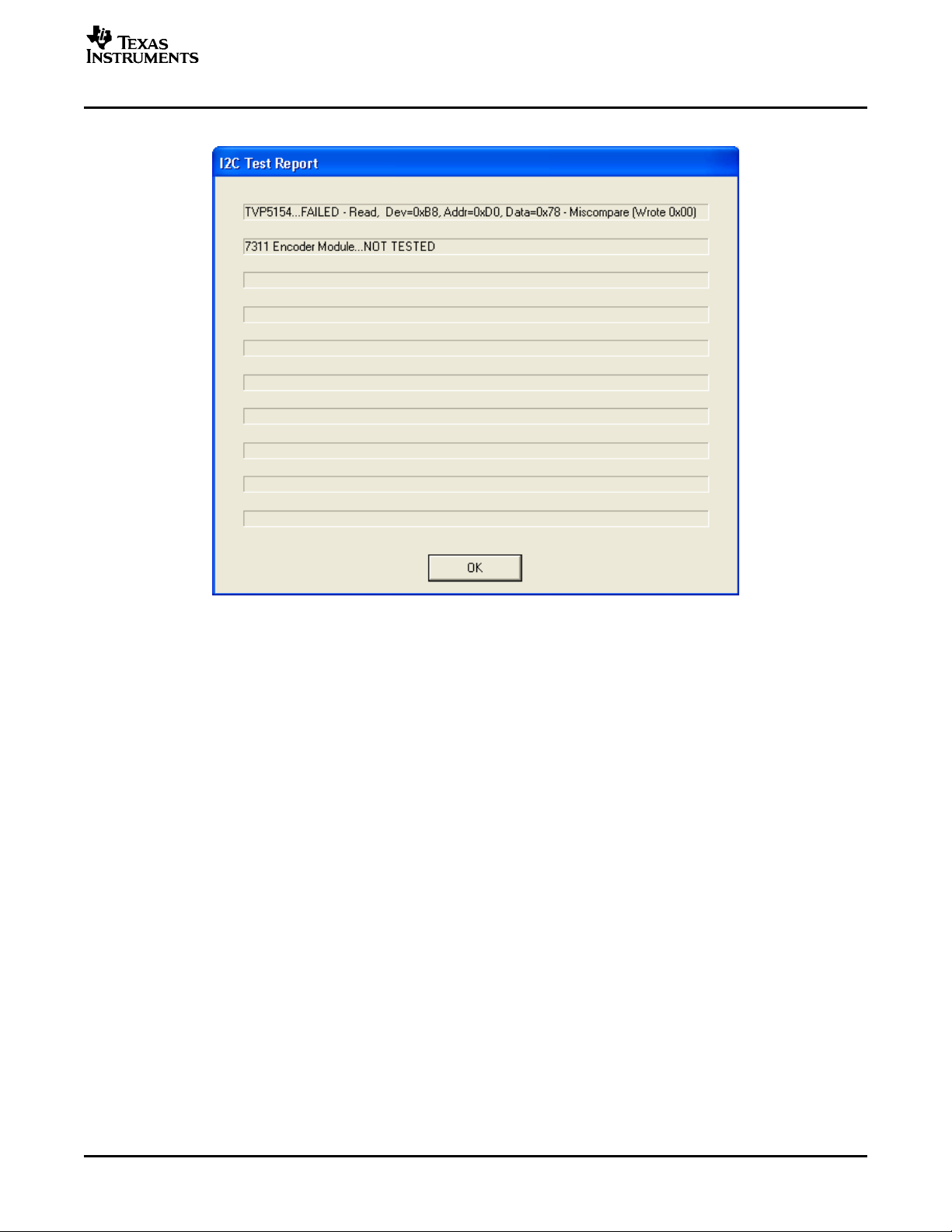

The I2C system test of selected registers runs immediately after closing the WinVCC Configuration dialog

box with OK (unless the I2C system test program options button was disabled).

If the I2C system test passes, only a PASS message appears. If the test failed, a dialog box like the one

shown in Figure 11 appears. See Section 10, Troubleshooting, for details on how to resolve this issue.

14 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 15

www.ti.com

The I2C system test can be run at anytime by clicking Run System I2C Test in the Tools menu.

WinVCC in Depth

8.4 Real-Time Polling

Real-time polling provides polling functions that execute continuously in the background, when enabled via

the Real-Time Polling dialog. There are two polling functions. The function that applies to the TVP5154 is

VIDEO-STANDARD AUTO-SWITCH POLLING.

When the TVP5154 detects a change in the input video standard, it automatically switches to operation in

the detected standard (which includes all necessary I2C register initialization) for proper decoding of the

input video. To enable auto-switch on the TVP5154, the Set Video Standard register must be set to

auto-switch mode (Reg 0x28 = 0x00).

If the WinVCC auto-switch polling function is enabled, the detected video standard status from the

TVP5154 is polled until a change in the input video standard (or in the TVP5154 sampling mode) is

detected. When a change is detected, the video encoder is reprogrammed as needed for the detected

standard. Using this feature, the video source can change its video standard and the system displays

using the new standard, without user intervention.

When using the TVP5154 EVM with the DM642 and a composite output from the 7311 encoder, it is

required to disable auto-switch polling by clicking on the ENABLED button in the Real-Time Polling dialog

box as shown in Figure 12 .

The real-time polling dialog can also be accessed once WinVCC is up and running by clicking Real-Time

Polling in the Tools menu.

Figure 11. I2C System Failure

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 15

Submit Documentation Feedback

Page 16

www.ti.com

WinVCC in Depth

8.5 Main Menu

Figure 12. Real-Time Polling Dialog

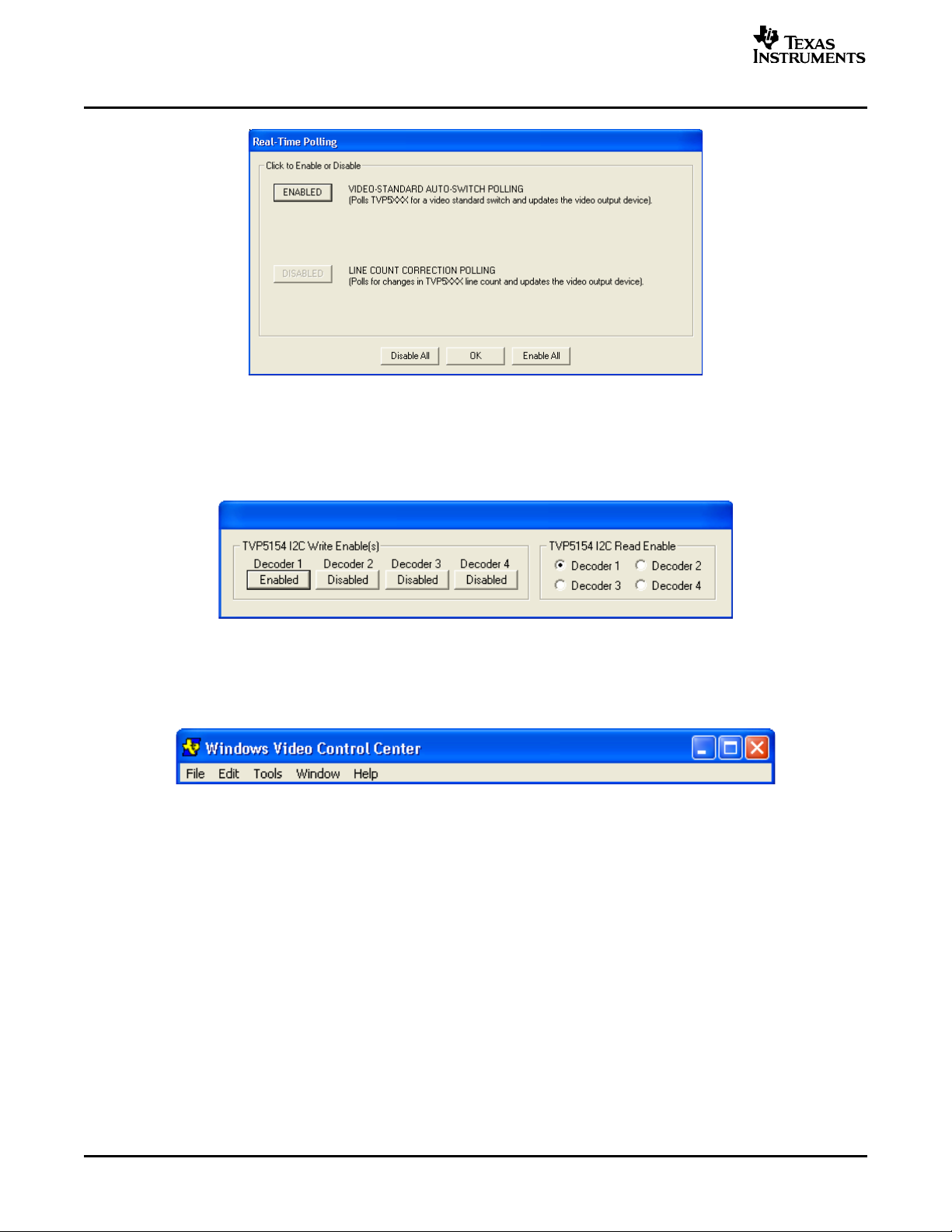

After closing the real-time polling dialog, the main menu is displayed as shown in Figure 13 . The menus,

which are used to operate WinVCC, are File, Edit, Tools, Window, and Help. The File menu’s only function

is Exit, which terminates the program. Table 3 summarizes the main menu contents.

Figure 13. WinVCC – Main Screen

Table 3. Main Menu Summary

MENU CONTENTS

File Exit

Edit Register Map

Tools System Initialization

Window Allows selection of the active window. Multiple windows can be open at the same time.

Help Displays program version

TVP5154

7311 Encoder Module

Generic I2C

Memory Map

TVP5154

7311 Encoder Module

Property Sheets

TVP5154

7311 Encoder Module

Real-time Polling

TV Tuner Control (FQ12xx series only)

Multiple-Byte I2C Transfers

Set I2C Bit Rate

Run System I2C Test

Run Continuous I2C Test

Read VBI FIFO

Capture Live VBI Data

DM642 Control

TVP5154EVM User's Guide16 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 17

www.ti.com

8.5.1 System Initialization

WinVCC in Depth

The TVP5154 I2C Write Enable(s) and Read Enable pop-up window is displayed as shown in Figure 14 .

This is used to select which decoder or decoders (any combination of all four) will receive I2C Write

commands, and which decoder (only one) will receive I2C Read commands. Decoder 1 is Enabled by

default; enable the other three decoders by clicking on each decoder’s enable button.

Figure 14. Decoder I2C Write and Read Enable

Clicking System Initialization in the Tools menu displays the dialog box shown in Figure 15 . This dialog

box provides the means for initializing the TVP5154 decoder(s) and/or video encoder for a particular video

mode, as well as programming settings for the DM642 through the Generic I2C registers. The details of

the initialization are contained in the command file (with a CMD file extension).

The command file is loaded using the Browse … button. Once the command file is opened, a text list

displays descriptions of the individual datasets contained within the command file.

Click once on the desired dataset description to select it. Click the Program Device(s) Using Selected

Dataset button to run the selected dataset, which loads the devices via the I2C bus. When the device

initialization has completed, the status indicator reads Ready.

Note: If Ready does not display, the devices are not initialized and the I2C bus is not

communicating. See Chapter 10, Troubleshooting, for possible solutions.

Click the OK button to close the dialog box. Each time the System Initialization dialog box is closed, the

initialization file pathname and the dataset selection number are saved in the Windows registry to allow

these settings to be retained for the next time WinVCC runs.

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 17

Submit Documentation Feedback

Page 18

www.ti.com

WinVCC in Depth

8.5.1.1 Adding a Custom Dataset

After programming the EVM via the System Initialization tool using the factory-supplied command file, you

can customize the device register settings to fit your needs. Perform the following steps to save your

custom settings:

1. Reopen the System Initialization dialog box via the Tools menu.

2. Click the Append Current Device Settings to Command File button. A dialog box requesting a

description of the new dataset appears.

3. Optionally, click the drop-down box and select one of the existing descriptions.

4. Modify the description text or type your own description.

5. Click OK. All nondefault register values from the TVP5154, DM642, and encoder are appended to the

current command file as an additional dataset.

Now, you can select your custom dataset and send it with a press of the Program … button.

By using the same procedure above with the Replace Selected Dataset with Current Device Settings

button you can overwrite an existing dataset with the current settings.

Note: If editing the command file (.CMD) using a standard editor, the file must be saved as plain

text.

Figure 15. System Initialization

TVP5154EVM User's Guide18 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 19

www.ti.com

8.5.1.2 Command Files

The command file is a text file that can be generated using any common editor; however, it must be saved

as plain text. Command files are especially useful for quickly switching between the various system

configurations. These .CMD files are unrelated to the typical Windows .CMD files.

A default command file is provided on the CD. This command file contains many examples of the desired

setups. This command file is located at:

c:\Program Files\Texas Instruments\TVP5154EVM\Initialization\

A command file can contain up to 250 datasets. A dataset is a set of register settings to initialize the

TVP5154 decoder, 7311 encoder, and/or DM642 for a particular video mode. Each dataset includes a

description that is displayed in one row of the dataset descriptions list. The register settings may be

located in the command file itself and/or may be stored in separate include file(s) (with an .INC file

extension) and be included into the command file using the INCLUDE statement.

8.5.1.3 Example Command File

An example of one dataset within a command file is shown below.

BEGIN_DATASET

DATASET_NAME,”TVP5154, Auto–switch, Stable Sync, Fast-lock, 656 Out”

// Initialize video encoder using an include file

INCLUDE, EncoderNTSC656_RTC.INC

// Program TVP5154 registers

WR_REG,VID_DEC,1,0x7F,0x00 // Reset 5154 microprocessor

WR_REG,VID_DEC,1,0x03,0x0D // Enable YCbCr outputs and syncs

WR_REG,VID_DEC,1,0x15,0x81 // Enable Stable Sync mode

WR_REG,VID_DEC,1,0x02,0x80 // Enable Fast-lock mode

WinVCC in Depth

END_DATASET

Each command file may contain individual write-to-register (WR_REG) commands.

• The comment indicator is the double-slash //.

• The command file is not case sensitive and ignores all white-space characters.

• All numbers can be entered as hexadecimal (beginning with 0x) or as decimal.

• Every dataset in a command file begins with BEGIN_DATASET and ends with END_DATASET. The

maximum number of datasets is 250.

• The dataset text description is entered between double quotes using the DATASET_NAME command.

The enclosed text can be up to 128 characters in length. This text appears in the System Initialization

dialog box when the command file is opened.

• The INCLUDE command inserts the contents of an include file (with an .INC file extension) in-line in

place of the INCLUDE command. Therefore, the include file must not contain the BEGIN_DATASET,

END_DATASET, and DATASET_NAME commands.

Note: All included files must be located in the same directory as the command (CMD) file.

• The write-to-register command is written as:

WR_REG, <DeviceFamily>, <Number of data bytes (N)>, <subaddress>, <Data1>, … , <DataN>

or

WR_REG, <Literal slave address>, <Number of data bytes (N)>, <subaddress>, <Data1>, … , <DataN>

The valid device family mnemonics are:

VID_DEC for the video decoders

VID_ENC for the video encoders

THS8200 for the THS8200 device

WinVCC translates the device family mnemonic to the slave address that was selected in the WinVCC

Configuration dialog box upon program startup. This eliminates having to edit command files if the

alternate slave address must be used.

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 19

Submit Documentation Feedback

Page 20

www.ti.com

WinVCC in Depth

If the literal slave address method is used, the slave address entered is used directly. This method is

normally used for programming the video encoder.

The slave address 0x40h is used to access the DM642.

• A delay may be inserted between commands using the WAIT command, which is written as:

WAIT,<# milliseconds>

8.5.2 Register Editing

The next section describes the five available modes of register editing: TVP5154 Register Map editor,

7311 Encoder Module Register Map editor, Generic I2C Register Map editor, TVP5154 memory map

editor, and TVP5154 Property Sheets. Each of these functions can be selected from the Edit menu.

8.5.2.1 Register Map Editor

The TVP5154 Register Map editor (see Figure 16 ) allows the display and editing of the entire used

register space of the device within a simple scrolling text box. To open this, click on Edit Register Map in

the Edit menu and click on the device type to edit. Table 4 describes how to use each of the controls in

the TVP5154 Register Map editor.

Figure 16. TVP5154 Register Map Editor

20 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 21

www.ti.com

Table 4. TVP5154 Register Map Editor Controls

CONTROL DEFINITION

Register Window Scrolling text box that displays the address and data for the I2C registers that are defined for the device

Address Edit Box

Data Edit Box Contains the data which will be written to, or was read from, the I2C subaddress.

Write Button Writes the byte in the Data Edit box to the address in the Address Edit box.

Read Button Reads the data from the address in the Address Edit box into the Data Edit box and the register window.

Read All Button Reads all defined readable registers from the device and updates the register window.

Hex Button Converts all values in the register window and address and data edit boxes to hexadecimal.

Dec Button Converts all values in the register window and address and data edit boxes to decimal.

Close Button Closes the dialog.

Loop Count

Contains the I2C subaddress that will be accessed using the Write and Read buttons. Clicking on a row selects

an address, which then appears in the address edit box.

NOTE: After clicking on a row, the Data Edit box contains the data that was in the register window. The device

has not yet been read.

The address up/down arrows are used to jump to the next/previous subaddress that is defined for the device. If

an address is not defined for the device, it can still be accessed by typing the subaddress in the Address Edit

box.

The data up/down arrows increment/decrement the data value by 1.

The I2C register is written to whether or not the data is different from the last time the register was read.

NOTE: Multiple edit register map windows can be open at the same time (one for each device). Use the

Window menu to navigate.

Causes subsequent write, read, or read all operations to be performed N times. N is entered as a decimal

number from 1 to 999.

WinVCC in Depth

8.5.2.2 Encoder Module Register Map Editor

The Encoder Module Register Map editor (see Figure 17 ) allows the display and editing of the video

encoder registers. This editor works like the TVP5154 Register Map editor.

To open this, click on Register Map in the Edit menu and click on 7311 Encoder Module.

Figure 17. 7311 Encoder Module Register Map Editor

8.5.2.3 Generic I2C Register Editor

The Generic I2C Register editor (see Figure 18 ) allows the display and editing of any device on the I2C

bus. This editor works like the TVP5154 Register Map editor, except that the I2C slave address must be

entered and the Read All button is disabled.

To open this, click on Register Map in the Edit menu and then click on Generic I2C.

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 21

Submit Documentation Feedback

Page 22

www.ti.com

WinVCC in Depth

The DM642 I2C registers can be edited using I2C sub-address 0x40. See Section 9 for details about the

DM642 registers.

The video encoder module registers can be edited using I2C sub-address 0x54 (default) or 0x56 if the

alternate slave address is being used.

8.5.2.4 Memory Map Editor

The memory map editor (see Figure 19 ) allows the display and editing of the data memory and hardware

registers of the device, such as the scaler setting registers.

To open this, click on Memory Map in the Edit menu and click on the device type to edit. The operation of

the memory map editor controls are explained in Table 5 .

Figure 18. Generic I2C Register Map Editor

Figure 19. Memory Map Editor

22 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 23

www.ti.com

WinVCC in Depth

Table 5. Memory Map Editor Controls

CONTROL DEFINITION

Base Address Selector The hardware registers use a 10-bit address internally. The base address selector allows quick entry

Address Offset Edit Box Contains the lowest byte of the 10-bit internal address. The full 10-bit address is formed by adding

Data Edit Boxes Contains the 16-bit data word that is written to or read from the register address. The LSB data is at

Write Button Writes the (2) bytes in the data edit boxes starting at the 10-bit register address BASE+OFFSET.

Read Button Reads (2) consecutive data bytes starting at the 10-bit register address BASE+OFFSET to the data

Loop Count Edit Box Causes subsequent write or read operations to be performed N times. N is entered as a decimal

Histogram on Creates a histogram of the results from the Loop Count Reads.

Loop Count Reads

Close Button Closes the dialog.

of the base address. The list contains base addresses for the major functional blocks of the

TVP5154.

the base address to the address offset. The address up/down arrows increment/decrement the

address offset by 1.

the lowest address. The data is written/read LSB first. The data up/down arrows

increment/decrement the data value by 1.

edit boxes.

number from 1 to 999.

Note: The memory map editor can remain open with other

windows. Use the Window menu to navigate.

8.6 TVP5154 Property Sheets

The property sheets represent the register data in a user-friendly format. The data is organized by

function, with each function having its own page and being selectable via tabs at the top (see Figure 20 ).

To open this, click on Edit Property Sheets in the Edit menu and select the device type to edit.

When the property sheet function is started or whenever the user tabs to a different page, all readable

registers in the device are read from hardware to initialize the dialog pages. Values on the page are

changed by manipulating the various dialog controls as described in Table 6 .

OK, Cancel, and Apply buttons are at the bottom of each property page. These are described in Table 7 .

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 23

Submit Documentation Feedback

Page 24

www.ti.com

WinVCC in Depth

8.6.1 Property Sheet Refresh

The property sheets are designed so that the data displayed is always current. Certain actions cause the

entire register map to be read from the device and to update the property sheets. This happens when:

• Property sheets are initially opened.

• When tabbing from one page to another.

• When Read All is clicked.

• When making the TVP5154 Property Sheets window the active window (by clicking on it).

• When making a TVP5154 Register Map editor window the active window (by clicking on it).

8.6.1.1 Auto-Update From Device

The last two items in the Property Sheet Refresh list (see section 8.6.1) are referred to as the

Auto-Update feature. Auto-Update can be disabled by setting its program option button to DISABLED.

This button is located on the initial dialog box (WinVCC Configuration).

With Auto-Update enabled (default), the user can open both the TVP5154 Property Sheets and the

TVP5154 Register Map editor at the same time. Changes made to the property sheets (and applied) are

updated in the register map window as soon as the Register Map window is clicked on. Additionally,

changes made in the TVP5154 Register Map editor are updated in the TVP5154 Property Sheets as soon

as the property sheets window is clicked on.

Figure 20. TVP5154 Property Sheets

TVP5154EVM User's Guide24 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 25

www.ti.com

Programming the TMS320DM642

Table 6. Use of Property Sheet Controls

PROPERTY SHEETS DIALOG CONTROL WHAT DO I DO WITH IT?

When is Hardware Updated?

Read-Only Edit Box Read status information N/A

Check Box Toggle a single bit After Apply

Drop-Down List Select from a text list After Apply

Edit Box Type a number After Apply

Edit Box with Up/Down arrows Use up/down arrows or type a number

Slider Slide a lever Immediately

Pushbutton Initiate an action Immediately

Up/Down arrows: Immediately

Type a number: After Apply

Table 7. Property Sheet Button Controls

BUTTON

CONTROL

OK Writes to all writeable registers whose data has changed. A register is flagged as changed if the value to be

written is different from the value last read from that address.

Closes the dialog.

Cancel Causes all changes made to the property page since the last Apply to be discarded. Changes made to dialog

controls with ‘immediate hardware update’ are not discarded, since they have already been changed in

hardware.

Does not write to hardware.

Closes the dialog.

Apply Writes to all writeable registers whose data has changed. A register is flagged as changed if the value to be

written is different from the value last read from that address.

DEFINITION

9 Programming the TMS320DM642

This chapter discusses how to change settings for the TMS320DM642 on this EVM. The DM642 settings

can be controlled by using the DM642 Control Window, which is found by clicking on Tools → DM642

Control, or through the Generic I2C registers.

9.1 Development and Purpose of DM642 Code

The TVP5154EVM was developed by the TI Digital Video Department, which is responsible for the

TVP5146 and TVP5150AM1 video decoders currently used on the DM642EVM released by Spectrum

Digital. The TVP5154EVM hardware and software are both based on this DM642EVM.

The TVP5154EVM was designed specifically for security customers interested in a quad video decoder.

The TVP5154EVM showcases the TVP5154 with various scaled/unscaled display modes, while making

the DM642 transparent to the customer during evaluation. This is made possible by placing the DM642

into an I2C slave mode and controlling the capture/display modes using virtual I2C registers. The entire

TVP5154EVM is controlled by a PC emulating I2C via the parallel port. By downloading the DM642 code

from flash at power up, it is not required to use Code Composer Studio™ software to program the DM642;

all relevant DM642 control registers can be accessed and controlled through a generic I2C address.

In addition to the command file provided with this EVM, additional command files to be used with TI’s EVM

control software (WinVCC) can be provided from TI to support easy programming of the TVP5154 and

DM642 registers to show the most common scaling configurations for both NTSC and PAL formats. When

using these command files or when setting the register values through a standard I2C bus interface, it is

important to enable and program the 5154 outputs before configuring the DM642 registers. The DM642

portion of the TVP5154EVM consists only of the DM642, SDRAM, and flash memory.

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 25

Submit Documentation Feedback

Page 26

www.ti.com

Programming the TMS320DM642

9.2 Details of the DM642 Code and Control Registers

Details of the DM642 code and control registers are:

• The DM642 device address is 0x40h by default. The DM642 is setup as an I2C slave.

• The DM642 executes code on power up from the flash using the PCI GPIO to control the address

MSB.

• Virtual I2C registers are created within the DM642 in order to control the capture and display of the

scaled/unscaled data from the TVP5154 video decoder. These registers are described in Table 9 .

• The virtual I2C registers support scaled and unscaled video outputs independently for each of the four

video decoders, with the option to overlay scaled video onto unscaled video, and to define the

quadrant location of each scaled channel.

• The virtual I2C registers provide easy control/access to the GPIOs currently tied to LEDs. Please refer

to the TVP5154EVM schematics for options to associate an LED on/off with a register setting.

• The DM642 is not responsible for any scaling. All video scaling is performed by the TVP5154. The

DM642 is only responsible for image capture and display.

• The DM642 virtual registers can be controlled by using the DM642 Control Window or through the

Generic I2C registers.

9.2.1 DM642 Control Window

The DM642 settings can be easily controlled by using the DM642 Control window. This window represents

the DM642 register data in a user-friendly format. The data is organized for each of the four decoders (see

Figure 21 ).

To open this, click on DM642 Control in the Tools menu.

Figure 21. DM642 Control Window

26 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 27

www.ti.com

Programming the TMS320DM642

When the DM642 Control window is opened, all readable registers for the device are read from software

to initialize the dialog page. Register details are given in Table 8 . Values on the page are changed by

manipulating the various dialog controls as described in Table 8 . The data is organized for each of the

four decoders, allowing independent control of each decoder.

Table 8. DM642 Control Window Controls

CONTROL DEFINITION

Read All Reads all defined readable registers from the device and updates the register window.

Causes all changes made to the page since the last Apply to be discarded. Changes made to dialog controls

Close registers.

Image Capture Enables image capture in the DM642 for that given decoder (1–4). Immediate register update.

Video Standard Apply is clicked.

Image Size is clicked.

Image Position Defines the quadrant location for the input of that given decoder (1–4). Immediate register update.

Apply

Flash

Major/Minor

LED Control Changes LED (1–7) status. Checked: LED is ON. Unchecked: LED is OFF. Immediate register update.

with ‘immediate register update’ are not discarded, since they have already been changed in the DM642

Does not write to registers.

Closes the dialog.

Used to inform the DM642 of the input color standard for that given decoder (1–4). No change in register until

Does not change the video standard setting for the TVP5154.

Used to inform the DM642 of the input image size for that given decoder (1–4). No change in register until Apply

Actual scaling is done in the TVP5154.

Immediately changes DM642 registers for input image size and input color standard for that given decoder

(1–4).

Enables TVP5154 scaler and programs correct scaling register settings into TVP5154 based on selected input

standard and image size for that given decoder (1–4).

Reads the data from the Flash Version registers and writes it into the register window.

9.2.2 DM642 Virtual I2C Register Map

REGISTER DESCRIPTION ADDRESS DATA (DEFAULT)

Decoder 1 Register 00h 02h

Decoder 2 Register 01h 12h

Decoder 3 Register 02h 22h

Decoder 4 Register 03h 32h

Decoder 1 Input Format Register 04h 01h

Decoder 2 Input Format Register 05h 01h

Decoder 3 Input Format Register 06h 01h

Decoder 4 Input Format Register 07h 01h

LED Control 08h 00h

Flash Version: Major 09h 01h

Flash Version: Minor 0Ah 00h

Table 9. DM642 Virtual I2C Register Map

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 27

Submit Documentation Feedback

Page 28

www.ti.com

Quad 1 Quad 2

Quad 3 Quad 4

Decoder1

Scaled

Decoder2

Unscaled

Decoder2

Unscaled

Decoder4

Scaled

Programming the TMS320DM642

9.2.3 DM642 Virtual I2C Register Details

Address 00h

Default 02h

7 6 5 4 3 2 1 0

Reserved Position Capture Size

Capture Size Bit 2 Bit 1 Bit 0

Unscaled 0 0 0

QSIF – 176 × 120 0 0 1

SIF – 352 × 240 (1/4 NTSC)

(default)

QCIF – 176 × 144 0 1 1

CIF – 352 × 288 (1/4 PAL) 1 0 0

QVGA – 320 × 240 1 0 1

VGA – 640 × 480 1 1 0

Reserved 1 1 1

Table 10. Decoder 1 Register

Capture

Enable

0 1 0

Capture Enable Bit 3

Disable (default) 0

Enable 1

Position Bit 5 Bit 4

Quadrant 1 (default) 0 0

Quadrant 2 0 1

Quadrant 3 1 0

Quadrant 4 1 1

Scaled capture sizes always take priority over unscaled capture sizes.

Decoder priorities are always such that Decoder 1 is the highest priority, Decoder 2 is the second highest,

etc.

For example, if Decoders 1 and 4 are scaled to 1/4 size and Decoders 2 and 3 are unscaled, this display

results:

28 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 29

www.ti.com

Quad 1 Quad 2

Quad 3 Quad 4

Programming the TMS320DM642

Note: The unscaled Decoder 2 displays in both Quadrant 2 and 3 since Decoder 2 takes priority

over Decoder 3 when both are unscaled.

Table 11. Decoder 2 Register

Address 01h

Default 12h

7 6 5 4 3 2 1 0

Reserved Position Capture Size

Capture

Enable

Capture Size Bit 2 Bit 1 Bit 0

Unscaled 0 0 0

QSIF – 176 × 120 0 0 1

SIF – 352 × 240 (1/4 NTSC)

(default)

0 1 0

QCIF – 176 × 144 0 1 1

CIF – 352 × 288 (1/4 PAL) 1 0 0

QVGA – 320 × 240 1 0 1

VGA – 640 × 480 1 1 0

Reserved 1 1 1

Capture Enable Bit 3

Disable (default) 0

Enable 1

Position Bit 5 Bit 4

Quadrant 1 0 0

Quadrant 2 (default) 0 1

Quadrant 3 1 0

Quadrant 4 1 1

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 29

Submit Documentation Feedback

Page 30

www.ti.com

Quad 1 Quad 2

Quad 3 Quad 4

Programming the TMS320DM642

Table 12. Decoder 3 Register

Address 01h

Default 22h

7 6 5 4 3 2 1 0

Reserved Position Capture Size

Capture

Enable

Capture Size Bit 2 Bit 1 Bit 0

Unscaled 0 0 0

QSIF – 176 × 120 0 0 1

SIF – 352 × 240 (1/4 NTSC)

(default)

0 1 0

QCIF – 176 × 144 0 1 1

CIF – 352 × 288 (1/4 PAL) 1 0 0

QVGA – 320 × 240 1 0 1

VGA – 640 × 480 1 1 0

Reserved 1 1 1

Capture Enable Bit 3

Disable (default) 0

Enable 1

Position Bit 5 Bit 4

Quadrant 1 0 0

Quadrant 2 0 1

Quadrant 3 (default) 1 0

Quadrant 4 1 1

Table 13. Decoder 4 Register

Address 01h

Default 32h

7 6 5 4 3 2 1 0

Reserved Position Capture Size

Capture

Enable

Capture Size Bit 2 Bit 1 Bit 0

Unscaled 0 0 0

QSIF – 176 × 120 0 0 1

SIF – 352 × 240 (1/4 NTSC)

(default)

0 1 0

QCIF – 176 × 144 0 1 1

CIF – 352 × 288 (1/4 PAL) 1 0 0

QVGA – 320 × 240 1 0 1

VGA – 640 × 480 1 1 0

Reserved 1 1 1

30 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 31

www.ti.com

Quad 1 Quad 2

Quad 3 Quad 4

Programming the TMS320DM642

Capture Enable Bit 3

Disable (default) 0

Enable 1

Position Bit 5 Bit 4

Quadrant 1 0 0

Quadrant 2 0 1

Quadrant 3 1 0

Quadrant 4 (default) 1 1

Table 14. Decoder 1 Input Format Register

Address 04h

Default 01h

7 6 5 4 3 2 1 0

Reserved Input Color Standard

Input Color Standard Bit 2 Bit 1 Bit 0

NTSC 0 0 0

(B, D, G, H, I, N) PAL

(default)

0 0 1

Reserved . . .

The Input Color Standard register is used to inform the DM642 of the input color standard for that given

decoder (1–4). The output format of the DM642 is set to the standard with the largest majority based on

Registers 04h–07h. If the number of input color standards is equal, the DM642 automatically default to

PAL output.

Table 15. Decoder 2 Input Format Register

Address 05h

Default 01h

7 6 5 4 3 2 1 0

Reserved Input Color Standard

Input Color Standard Bit 2 Bit 1 Bit 0

NTSC 0 0 0

(B, D, G, H, I, N) PAL

(default)

0 0 1

Reserved . . .

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 31

Submit Documentation Feedback

Page 32

www.ti.com

Programming the TMS320DM642

Table 16. Decoder 3 Input Format Register

Address 06h

Default 01h

7 6 5 4 3 2 1 0

Reserved Input Color Standard

Input Color Standard Bit 2 Bit 1 Bit 0

NTSC 0 0 0

(B, D, G, H, I, N) PAL

(default)

0 0 1

Reserved . . .

Table 17. Decoder 4 Input Format Register

Address 07h

Default 01h

7 6 5 4 3 2 1 0

Reserved Input Color Standard

Input Color Standard Bit 2 Bit 1 Bit 0

NTSC 0 0 0

(B, D, G, H, I, N) PAL

(default)

0 0 1

Reserved . . .

Table 18. LED Control Register

Address 08h

Default 00h

7 6 5 4 3 2 1 0

Reserved LED 7 Status LED 6 Status LED 5 Status LED 4 Status LED 3 Status LED 2 Status LED 1 Status

LED (1–7) Status

= 0 (LED off)

= 1 (LED on)

Table 19. Flash Major Version Register

Address 09h

Default 01h

7 6 5 4 3 2 1 0

Flash Major Version

Table 20. Flash Minor Version Register

Address 0Ah

Default 00h

7 6 5 4 3 2 1 0

Flash Minor Version

TVP5154EVM User's Guide32 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 33

www.ti.com

10 Troubleshooting

This chapter discusses ways to troubleshoot the TVP5154EVM.

10.1 Troubleshooting Guide

If you are experiencing problems with the TVP5154EVM hardware or the WinVCC software, see Table 21

for available solutions.

At startup, the error message Cannot find The parallel port driver supplied with the Run Port95NT.EXE on the CD to install

DLL file DLPORTIO.DLL appears. EVM has not been installed. the driver.

Blank screen Source is connected to the wrong input Connect source to the correct input

No color

Screen colors are only magenta and

green.

Video standard auto-switch does not work

on the video decoder side.

Video standard auto-switch does not work

on the video encoder side.

Table 21. TVP5154EVM Troubleshooting

SYMPTOM CAUSE SOLUTION

Go to Edit → Property Sheets → TVP5154,

Wrong video input is selected. video input(s) and click Apply.

connector. connector.

YCbCr outputs or clock output is disabled.

Wrong mode is selected for color

subcarrier genlock output.

GLCO pin is not set to output the GLCO Output Control page, set the drop down

signal. box labeled FID/GLCO (pin 23) to genlock

Wrong YCbCr output format output format to 8-bit 4:2:2 YCbCr

Auto-switch masks are not set correctly.

Video decoder is not in auto-switch mode. Mode Selection page, set the drop-down

Auto-switch polling is not enabled. Click Enable All and OK. This should be

Analog Video page, select the correct

(The composite video input 1 is selected

by default.)

Go to Edit → Property Sheets → TVP5154,

Output Control page, check the enable

YCbCr outputs and enable clock outputs

check boxes and click Apply.

Go to Edit → Property Sheets → TVP5154,

Synchronization page, set the Fsc control

format to RTC and click Apply.

Go to Edit → Property Sheets → TVP5154,

output (GLCO) and click Apply.

Go to Edit → Property Sheets → TVP5154,

Output Control page, set the YCbCr

w/ITU-R BT.656 embedded sync mode

and click Apply.

Go to Edit → Property Sheets → TVP5154,

Mode Selection page, uncheck all

standards to be included in auto-switch

processing and click Apply.

Go to Edit → Property Sheets → TVP5154,

box to multistandard and click Apply.

Click real-time polling in the Tools menu.

disabled if using a composite output.

Troubleshooting

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 33

Submit Documentation Feedback

Page 34

www.ti.com

Troubleshooting

Table 21. TVP5154EVM Troubleshooting (continued)

SYMPTOM CAUSE SOLUTION

Decoder I2C slave address is wrong. the TVP5154 decoder module are across

Encoder I2C slave address is wrong.

Parallel cable is not connected from PC

parallel port to the TVP5154 decoder Connect cable

module DB25 connector.

EVM is not powered on.

Wrong type of parallel cable. straight through pin for pin. Use the cable

No I2C communication supplied with the EVM.

Device was placed in power-down mode.

EVM was configured for an external I2C Reinstall 0- Ω resistors R5 and R6. Control

master. EVM using the PC parallel port.

PC parallel port mode is not set correctly.

Still no I2C communication

Make sure I2C slave address jumpers on

pins 2 and 3.

Slave address is hard coded to be 0x54 in

the command file. Make sure the I2C slave

address jumper on encoder module is

across pins 2 and 3.

Power supply must be plugged into a

100-V to 240-V/47-Hz to 63-Hz power

source, and the cord must be plugged into

the power connector on the EVM.

Some parallel cables are not wired

Press the Reset button on the TVP5154

Decoder Module.

DO THIS AS A LAST RESORT. Reboot

PC, enter BIOS setup program, and set

parallel port LPT1 mode (Addr 378h) to

ECP mode or bidirectional mode

(sometimes called PS/2 mode or byte

mode). If already set to one of these two

modes, switch to the other setting (see

Section 10.2 ).

PC may not be capable of operating in the

required parallel port mode. This is true of

some laptop computers. Use a different

computer, preferably a desktop PC.

When WinVCC is started and the WinVCC Configuration dialog box is closed with OK, the I2C system test

is performed (unless the I2C System Test program options button was disabled).

If the I2C system test fails, a dialog box (see Figure 22 ) appears. This example reports that a read from

TVP5154 failed, using slave address 0xB8, sub-address 0xD0. The data read was 0x78. The expected

data was 0x00.

After noting which device had a problem, click OK to continue. Next, the Corrective Action Dialog box

appears to fix the problem.

34 TVP5154EVM User's Guide SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 35

www.ti.com

Troubleshooting

10.2 Corrective Action Dialogs

After closing the I2C system test report dialog box, a dialog box (see Figure 23 ) appears.

1. If the parallel port cable is NOT connected between to PC and the TVP5154EVM, or if the EVM power

is not on:

Figure 22. I2C System Failure Dialog Box

Figure 23. Corrective Action Dialog Box

a. Click NO.

b. The dialog box shown in Figure 23 appears instructing you to correct the problem.

c. Correct the problem.

d. Click OK to continue. The Real-Time Polling dialog appears.

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 35

Submit Documentation Feedback

Page 36

www.ti.com

Troubleshooting

Figure 24. Corrective Action Required

2. If the cable is connected from the PC parallel port to the TVP5154EVM and the EVM power is on:

a. Click Yes.

b. The dialog box shown in Figure 24 appears. This dialog box appears if the PC parallel

port mode setting may need to be changed.

Note: Only run the PC BIOS setup program if the I2C communication problem cannot be

resolved in another way (correct slave address settings, reset or power cycle the

EVM, and/or check that the device type selected was TVP5154).

c. Click OK to continue.

d. The real-time polling dialog appears. Click OK to close it and get to the main menu.

e. Click Exit in the File menu to exit the program.

f. See the troubleshooting guide in Table 21 .

Figure 25. Corrective Action Required

10.2.1 Setting the PC Parallel Port Mode

Note: Only run the PC BIOS setup program if the I2C communication problem cannot be

resolved in another way (correct slave address settings, reset or power cycle the EVM,

and/or check that the device type selected was TVP5154).

1. Restart the PC.

2. During the boot process, enter the BIOS setup program by pressing the required key (usually the initial

text screen indicates which key to press).

3. Find the place where the parallel port settings are made.

4. Set the parallel port LPT1 at address 378h to ECP mode or bidirectional mode (sometimes called PS/2

mode or byte mode). If one of these two modes is already selected, change to the opposite mode.

5. Exit and save changes.

TVP5154EVM User's Guide36 SLEU069A – February 2006 – Revised July 2006

Submit Documentation Feedback

Page 37

www.ti.com

10.2.2 General I2C Error Report

The I2C Error Report shown in Figure 26 appears when an I2C error occurs at any time other than after

the I2C system test. In this example, there is acknowledge error at slave address 0x54 (the video encoder

module). The error occurred on Read Cycle Phase 1 on the device (slave) address byte.

11 TVP5154EVM Schematics

TVP5154EVM Schematics

Figure 26. I2C Error

SLEU069A – February 2006 – Revised July 2006 TVP5154EVM User's Guide 37

Submit Documentation Feedback

Page 38

54321

6

D

D

TVP5154EVMDVB R EV 1.2

I2C

page 17 - I2C

SDA

SCL

Anti-Aliasing Filters

C

B

page 11 - Anti-Aliasing Filters

1A_IN

1B_IN

2A_IN

2B_IN

3A_IN

3B_IN

4A_IN

4B_IN

1A_OUT

1B_OUT

2A_OUT

2B_OUT

3A_OUT

3B_OUT

4A_OUT

4B_OUT

TVP5154

page 2 - TVP5154

1A_IN

1B_IN

2A_IN

2B_IN

3A_IN

3B_IN

4A_IN

4B_IN

1A_OUT

1B_OUT

2A_OUT

2B_OUT

3A_OUT

3B_OUT

4A_OUT

4B_OUT

/RESET

CH1_OUT[7..0]

SCKS1

SCK1

FID1

CH2_OUT[7..0]

SCKS2

SCK2

FID2

CH3_OUT[7..0]

SCKS3

SCK3

FID3

CH4_OUT[7..0]

SCKS4

SCK4

FID4

SCL

SDA

HS1

VS1

AV1

VB1

HS2

VS2

AV2

VB2

HS3

VS3

AV3

VB3

HS4

VS4

AV4

VB4

DM642

page 4 - DM642

/RESET

SCL

SDA

CH1_OUT[7..0]

SCKS1

AV1

CH2_OUT[7..0]

SCKS2

AV2

CH3_OUT[7..0]

SCKS3

AV3

CH4_OUT[7..0]

SCKS4

AV4

GP13_A19

GP15_A21

GP14_A20

TCE1#

Power

page 7 - Power

/RESET

TED[63..0]

TSDRAS#

TEA[22..3]

TECLKOUT1

TSDWE#

TSDCAS#

TSDCKE

ENC_Y[7..0]

ENC_C[7..0]

DSP_TRST#

DSP_EMU[11..0]

TCE0#

TBE5#

TBE6#

TBE7#

ENC_SCLK

ENC_HS

ENC_VS

ENC_FID

DSP_TDO

DSP_TDI

DSP_TMS

DSP_TCLK

TBE3#

TBE4#

Connector

page 16 - Connector

SDA

SCL

/RESET

ENC_Y[7..0]

ENC_C[7..0]

ENC_SCLK

ENC_HS

ENC_VS

ENC_FID

JTAG

page 15 - JTAG

DSP_TDO

DSP_TDI

DSP_TMS

DSP_TCLK

DSP_TRST#

DSP_EMU[11..0]

TBE0#

TBE2#

TBE1#

C

B

SCL

SDA

/RESET

F&V Bit Breakout

page 12 - F&V Bit Breakout

Daughtercard Interface

page 3 - Daughtercard Interface

HS1

VS1

SCK1

SCKS1

CH1_OUT[7..0]

A

1 2 3 4 5 6

HS2

AV1

FID1

AV2

SCK2

SCKS2

CH2_OUT[7..0]

VS2

VB1

HS3

VS3

VB2

FID2

CH3_OUT[7..0]

SCKS3

SCK3

AV3

HS4

VS4

VB3

FID3

VB4

AV4

FID4

SCK4

SCKS4

CH4_OUT[7..0]

SCK4

CH4_OUT[7..0]

Flash Memory

page 14 - Flash Memory

/RESET

SDRAM

page 13 - SDRAM

TCE1#

TSDWE#

TSDCAS#

GP13_A19

GP15_A21

GP14_A20

TED[31..0]

TEA[22..3]

TED[63..0]

TEA[22..3]

TSDRAS#

TECLKOUT1

TCE0#

TBE7#

TSDCKE

TSDWE#

TSDCAS#

TBE0#

TBE2#

TBE1#

TBE3#

TBE4#

TBE5#

TBE6#

TEXAS INSTRUMENTS, INC.

12500 TI BLVD

DALLAS, TEXAS 75243

TVP5154EVM BLOCK DIAGRAM

Size FCSM No. DWG No. Rev

C 1

Scale Sheet

1 of 17

A

Page 39

54321

6

D

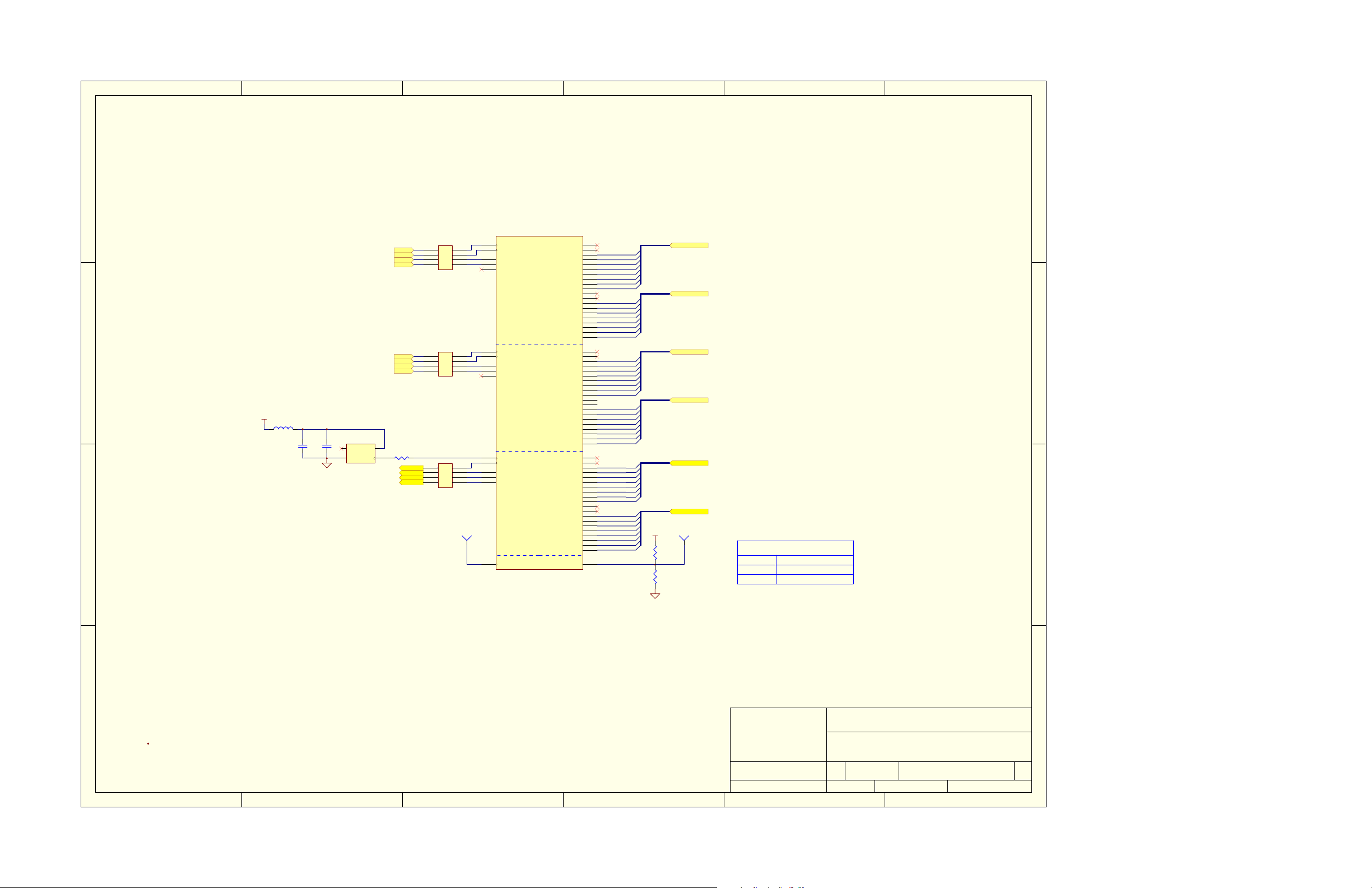

DM642 Clocks and Reset

page 6 - DM642 Clocks and R eset

/RESET

SCL

SDA

C

B

CH1_OUT[7..0]

SCKS1

AV1

CH2_OUT[7..0]

SCKS2

AV2

CH3_OUT[7..0]

SCKS3

AV3

CH4_OUT[7..0]

SCKS4

AV4

TED[63..0]

TEA[22..3]

TECLKOUT1

TSDCKE

TSDRAS#

TSDCAS#

TSDWE#

TCE0#

TCE1#

TBE7#

TBE6#

TBE5#

TBE4#

TBE3#

TBE2#

TBE1#

TBE0#

DSP_EMU[11..0]

DSP_TDI

DSP_TDO

DSP_TMS

DSP_TCLK

DSP_TRST#

GP13_A19

GP14_A20

GP15_A21

/RESET

SCL

SDA

DM642 Video Ports

page 5 - DM642 Video Ports

CH1_OUT[7..0]

SCKS1

AV1

CH2_OUT[7..0]

SCKS2

AV2

CH3_OUT[7..0]

SCKS3

AV3

CH4_OUT[7..0]

SCKS4

AV4

DM642 EMIF and JTAG

page 10 - DM642 EMIF and JTAG

TED[63..0]

TEA[22..3]

TECLKOUT1

TSDCKE

TSDRAS#

TSDCAS#

TSDWE#

TCE0#

TCE1#

TBE7#

TBE6#

TBE5#

TBE4#

TBE3#

TBE2#

TBE1#

TBE0#

DSP_EMU[11..0]

DSP_TDI

DSP_TDO

DSP_TMS

DSP_TCLK

DSP_TRST#

DM642 PCI_HPI_EM AC

page 8 - DM642 PCI_HPI_EMAC

GP13_A19

GP15_A21

GP14_A20

ENC_Y[7..0]

ENC_C[7..0]

ENC_SCLK

ENC_HS

ENC_VS

ENC_FID

DM642 Power Pins

page 9 - DM642 Power Pins

ENC_Y[7..0]

ENC_C[7..0]

ENC_SCLK

ENC_HS

ENC_VS

ENC_FID

D

C

B

TEXAS INSTRUMENTS, INC.

A

12500 TI BLVD

DALLAS, TEXAS 75243

A

DM642 BLOCK DIAGRAM

Size FCSM No. DWG No. Rev

C 1

Scale Sheet

4 of 17

1 2 3 4 5 6

Page 40

54321

6

D

D

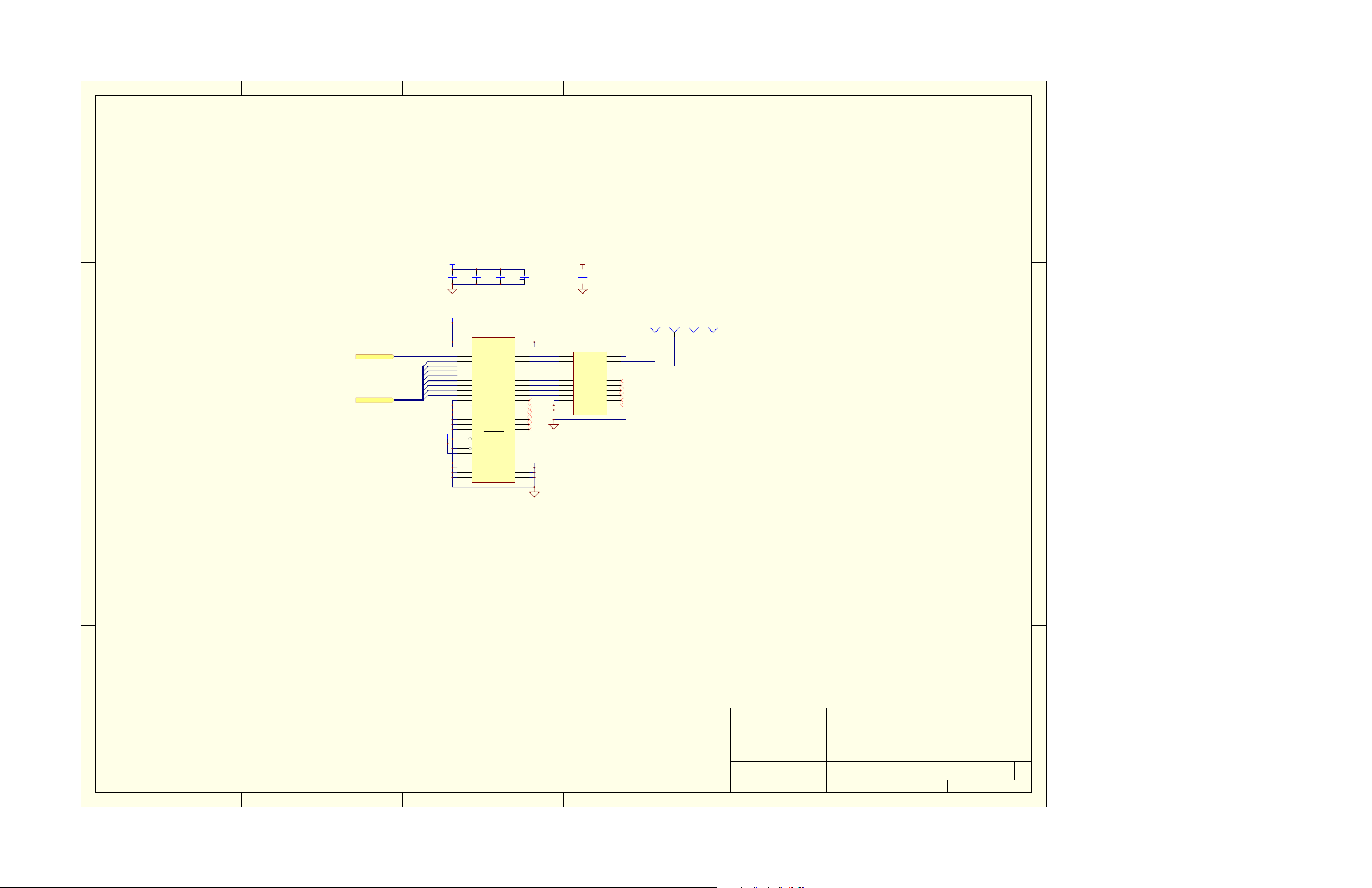

U25B

RPACK4-33

1

SCKS1

2

SCKS2

3

AV1

4 5

AV2

C

D3.3V

L1

SCKS3

SCKS4

AV3

AV4

RN25

RPACK4-33

1

2

3

4 5

RN26

BLM21P221SN

C1

0.1uF

1000pF

Y1

C2

1

2

27MHz_MIH_MMD

EN

GND

4

VCC

OUT

R1 33

3

ENC_SCLK

ENC_HS

ENC_VS

ENC_FID

RPACK4-33

1

2

3

4 5

RN27

B

AF14

8

7

6

8

7

6

8

7

6

VP0_CLK0

AF12

VP0_CLK1

AE17

VP0_CTL0

AC17

VP0_CTL1

AD17

VP0_CTL2

Video Port 0 / McBSP0 / McASP Control

AF8

VP1_CLK0

AF10

VP1_CLK1

AF4

VP1_CTL0

AE5

VP1_CTL1

AD5

VP1_CTL2

Video Port 1 / McBSP1 / McASP Data

A7

VP2_CLK0

A13

VP2_CLK1

B8

VP2_CTL0

D7

VP2_CTL1

C7

VP2_CTL2

CLKX0/VP0_D02

FSX0/VP0_D03

DX0/VP0_D04

CLKS0/VP0_D05

DR0/VP0_D06

FSR0/VP0_D07

CLKR0/VP0_D08

ACLKR0/VP0_D12

AFSR0/VP0_D13

AHCLKR0/VP0_D 14

AMUTEIN/VP0_D15

AMUTE/VP0_D16

ACLKX0/VP0_D17

AFSX0/VP0_D18

AHCLKX0/VP0_D19

CLKX1/VP1_D02

FSX1/VP1_D03

DX1/VP1_D04

CLKS1/VP1_D05

DR1/VP1_D06

FSR1/VP1_D07

CLKR1/VP1_D08

AXR0/VP1_D12

AXR1/VP1_D13

AXR2/VP1_D14

AXR3/VP1_D15

AXR4/VP1_D16

AXR5/VP1_D17

AXR6/VP1_D18

AXR7/VP1_D19

Video Port 2

TP1

TP

TP

1

AC1

TMX320DM642CGDK

STCLK

VIC

VDAC / GP08

VP0_D00

VP0_D01

VP0_D09

VP0_D10

VP0_D11

VP1_D00

VP1_D01

VP1_D09

VP1_D10

VP1_D11

VP2_D00

VP2_D01

VP2_D02

VP2_D03

VP2_D04

VP2_D05

VP2_D06

VP2_D07

VP2_D08

VP2_D09

VP2_D10

VP2_D11

VP2_D12

VP2_D13

VP2_D14

VP2_D15

VP2_D16

VP2_D17

VP2_D18

VP2_D19

AF18

AE18

AF17

AF16

AE16

AD16

AC16

AB16

AE15

AD15

AC15

AB15

AD14

AC14

AB14

AD13

AC13

AB13

AD12

AC12

AF5

AF6

AE6

AD6

AC6

AE7

AD7

AC7

AD8

AC8

AE9

AD9

AC9

AD10

AC10

AE11

AD11

AC11

AB11

AB12

C8

D8

A9

B9

C9

D9

A10

B10

C10

D10

A11

B11

C11

D11

E11

B12

C12

D12

E12

E13

AD1

CH1_OUT0

CH1_OUT1

CH1_OUT2

CH1_OUT3

CH1_OUT4

CH1_OUT5

CH1_OUT6

CH1_OUT7

CH2_OUT0

CH2_OUT1

CH2_OUT2

CH2_OUT3

CH2_OUT4

CH2_OUT5

CH2_OUT6

CH2_OUT7

CH3_OUT0

CH3_OUT1

CH3_OUT2

CH3_OUT3

CH3_OUT4

CH3_OUT5

CH3_OUT6

CH3_OUT7

CH4_OUT0

CH4_OUT1

CH4_OUT2

CH4_OUT3

CH4_OUT4

CH4_OUT5

CH4_OUT6

CH4_OUT7

ENC_Y0

ENC_Y1

ENC_Y2

ENC_Y3

ENC_Y4

ENC_Y5

ENC_Y6

ENC_Y7

ENC_C0

ENC_C1

ENC_C2

ENC_C3

ENC_C4

ENC_C5

ENC_C6

ENC_C7

CH1_OUT[7..0]

CH2_OUT[7..0]

CH3_OUT[7..0]

CH4_OUT[7..0]

ENC_Y[7..0]

ENC_C[7..0]

D3.3V

R6

NO POP

R29

1k

CH1_OUT[7..0]

CH2_OUT[7..0]

CH3_OUT[7..0]

CH4_OUT[7..0]

ENC_Y[7..0]

ENC_C[7..0]

TP2

TP

TP

1

PCI FREQ CONFIGURATION

R6/R27

0

1

MODE SELECTED

66MHz (DEFAULT)

33MHz

C

B

TEXAS INSTRUMENTS, INC.

A

12500 TI BLVD

DALLAS, TEXAS 75243

A

DM642 VIDEO PORT

Size FCSM No. DWG No. Rev

C 1

1 2 3 4 5 6

Scale Sheet

5 of 17

Page 41