SYS_IN

L1

SM1

PGND1

PGND2

SM2

L2

AGND0

SM3

FB3

L3

SM3SW

OUT

SIM

OUT

GPIO1

USB

GPIO2

LDO_PM

PWM

AC

RED

BAT

GREEN

BAT

BLUE

TMR

SCLK

ISET1

SDAT

DPPM

INT

TS

RESPWRON

RTC_OUT

TRSTPWON

HOT_RST

LDO1

LDO0

LDO3

LDO35_REF

VIN_LDO35

LDO4

ADC_REF

AGND2

ANLG1

ANLG2

LDO5

GPIO3

GROUNDPAD

AGND1

VIN_LDO02

PGND3

VIN_SM2

VIN_SM1

2

11

8

13

10

12

9

6

7

5

3

4

14

38

41

36

39

37

40

42

34

35

33

32

31

30

27

29

25 282624232219 21201817

LED_PWM

LDO2

48 47 434446 4549505154 5256 5355

1

1615

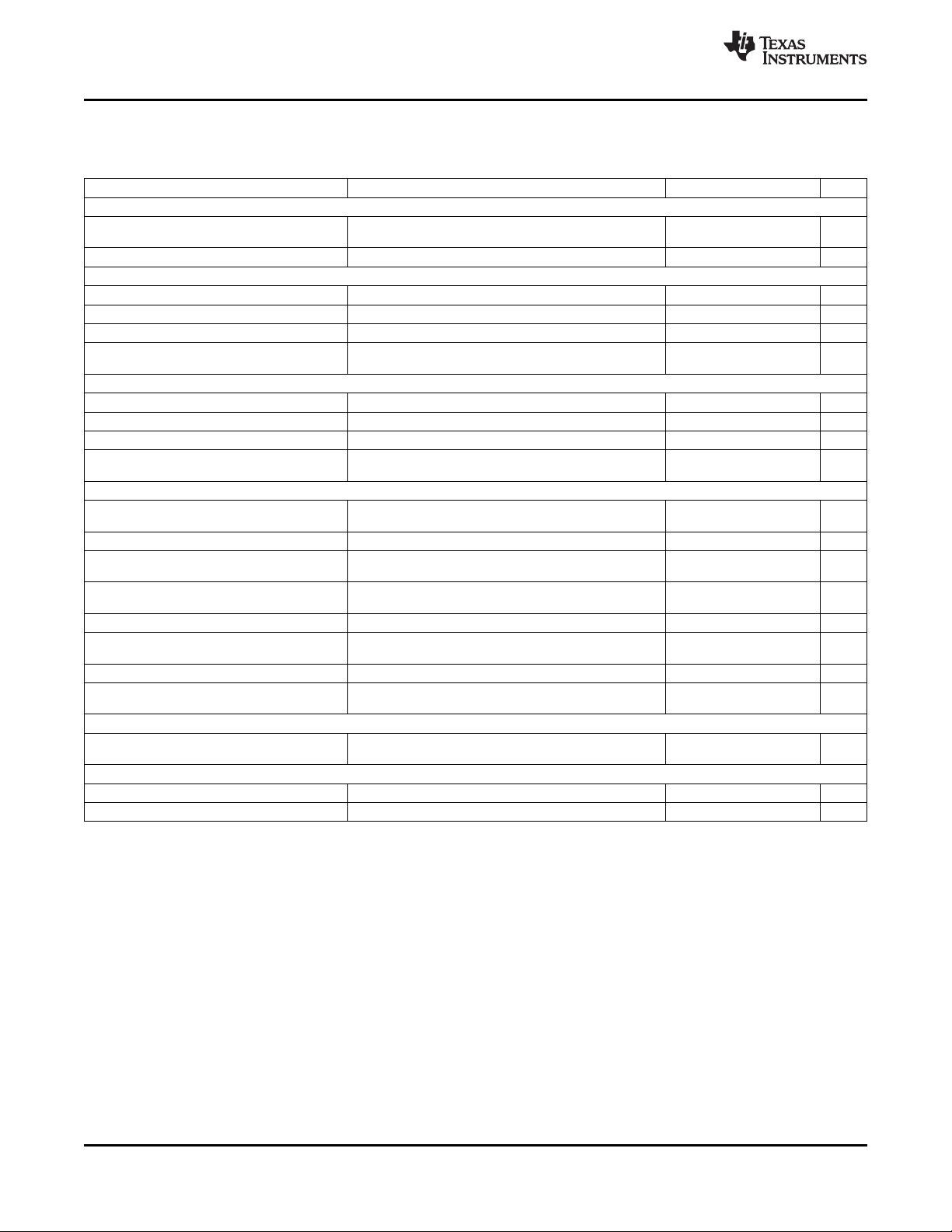

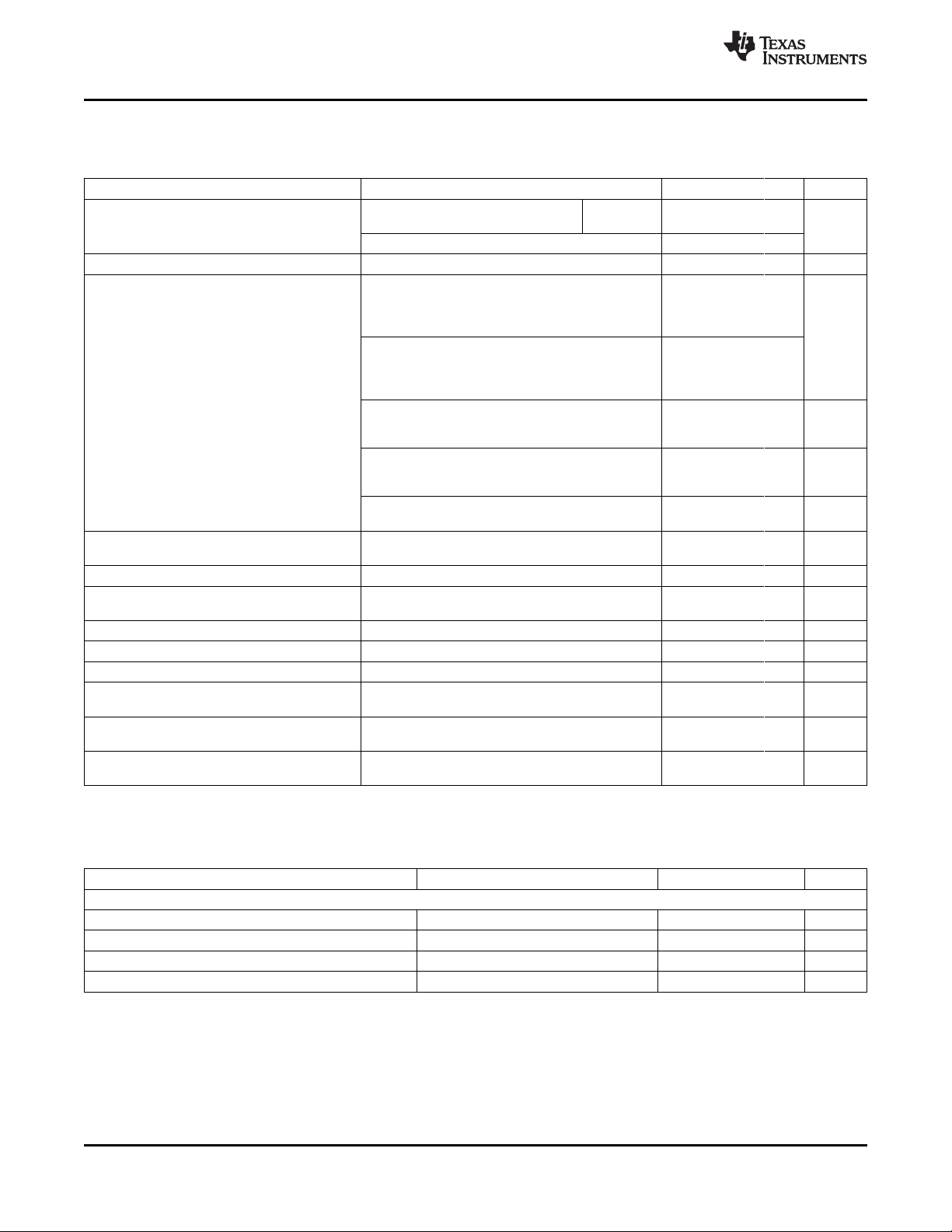

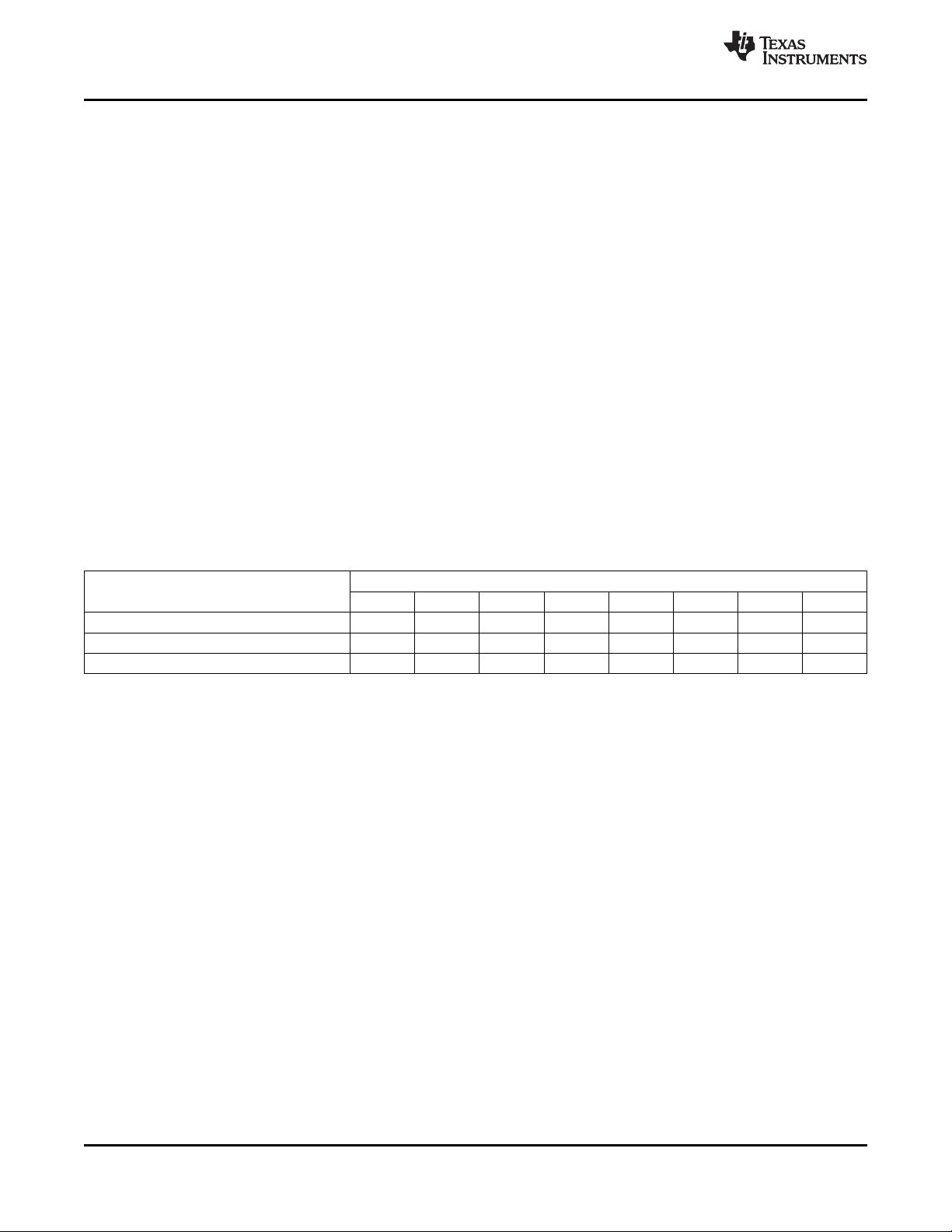

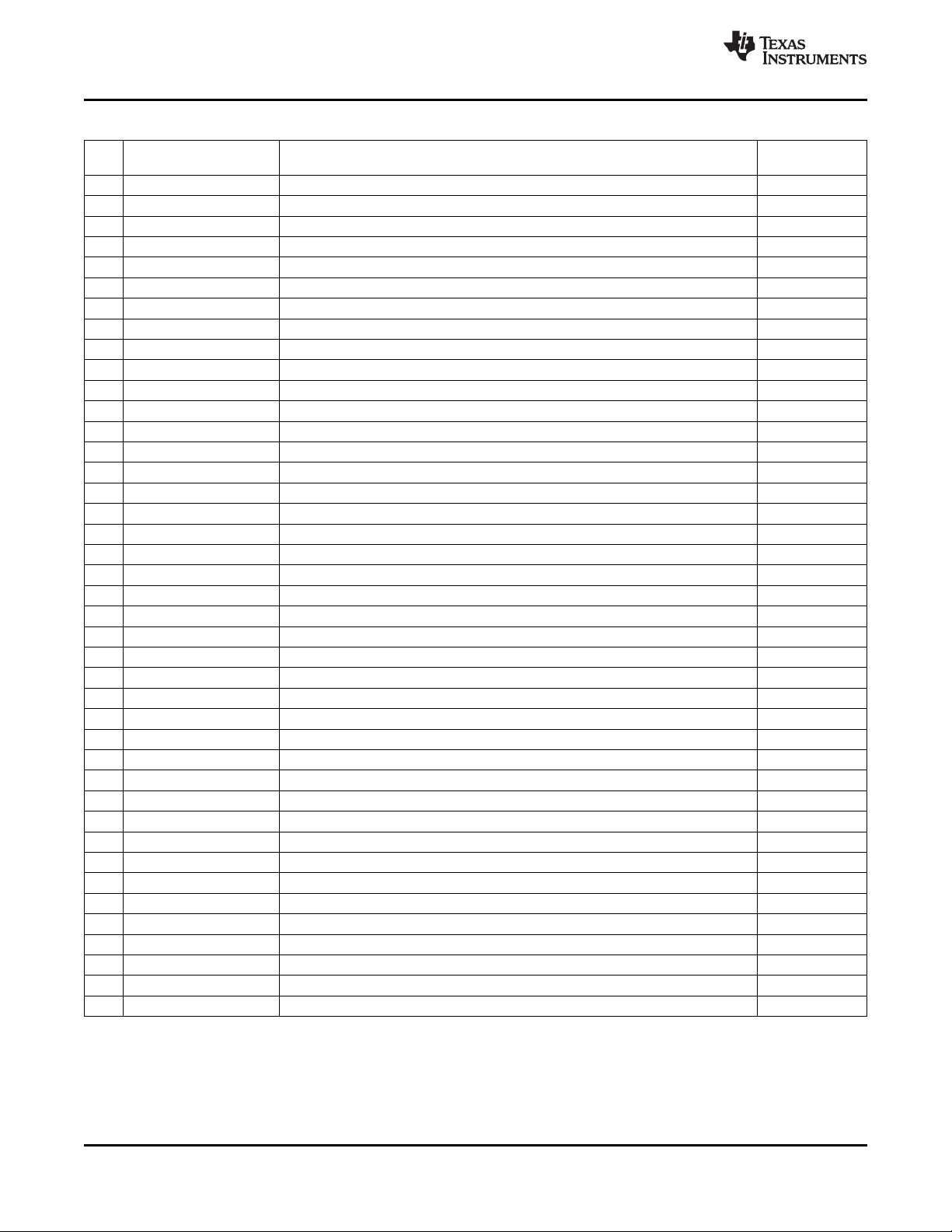

QFN56-Pin,7x7mmPackage

(TopView-NotToScale)

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

SINGLE-CELL Li-ION BATTERY- AND POWER-MANAGEMENT IC

1

FEATURES

• BATTERY CHARGER – Host can set system parameters and

– Complete charge management solution for

single Li-Ion/Li-Pol cell with thermal – Interrupt function with programmable

foldback, dynamic power management and masking signals system status modifiction

pack temperature sensing, supporting up to host

to 1.5-A max charge current

– Programmable charge parameters for AC integrated A/D trigger or buck converters

adapter and USB port operation standby mode control

• INTEGRATED POWER SUPPLIES

– A total of 9 LDOs are integrated:

– Six adjustable output LDOs (1.25-V to

3.3-V)

– Two fixed-voltage LDOs (3.3-V)

– One fixed-voltage, always-on LDO

(3.3-V)

– One RTC backup supply with low

leakage (3.1-V)

– Two 600-mA output current, 0.6-V to 3.4-V

programmable dc/dc buck converters with

enable, standby mode operation, and

automatic low-power mode setting

• DISPLAY FUNCTIONS

– Two open-drain PWM outputs with

programmable frequency and duty cycle.

Can be used to control keyboard backlight,

vibrator, or other external peripheral

functions

– RGB LED driver with programmable

flashing period and individual R/G/B

brightness control

– Constant-current white LED driver, with

programmable current level, brightness

control, and overvoltage protection can

• SYSTEM MANAGEMENT

1

drive up to 6 LEDs in series configuration

– Dual input power path function with input

current limiting and OVP protection

– POR function with programmable masking

monitors all integrated supplies outputs

– Software and hardware reset functions

– 8-channel integrated A/D samples system

parameters with single conversion, peak

detection, or averaging operating modes

spacer

spacer

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

• HOST INTERFACE

access system status using I2C interface

– 3 GPIO ports, programmable as drivers,

APPLICATIONS

• PDAs

• Smart Phones

• MP3s

• Internet Appliances

• Handheld Devices

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2006 – 2008, Texas Instruments Incorporated

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

www.ti.com

DESCRIPTION

The TPS65820 provides an easy to use, fully integrated solution for handheld devices, integrating charge

management, multiple regulated power supplies, system management and display functions, in a small

thermally-enhanced 7-mm × 7-mm package. The high level of integration enables typical board area space

savings of 70% when compared to equivalent discrete solutions, while implementing a high-performance and

flexible solution, portable across multiple platforms. If required, an external host may control the TPS65820 via

I2C interface, with access to all integrated systems. The I2C enables setting output voltages, current thresholds,

and operation modes. Internal registers have a complete set of status information, enabling easy diagnostics,

and host-controlled handling of fault conditions. The TPS65820 can operate in stand-alone mode, with no

external host control, if the internal power-up defaults are compatible with the system requirements

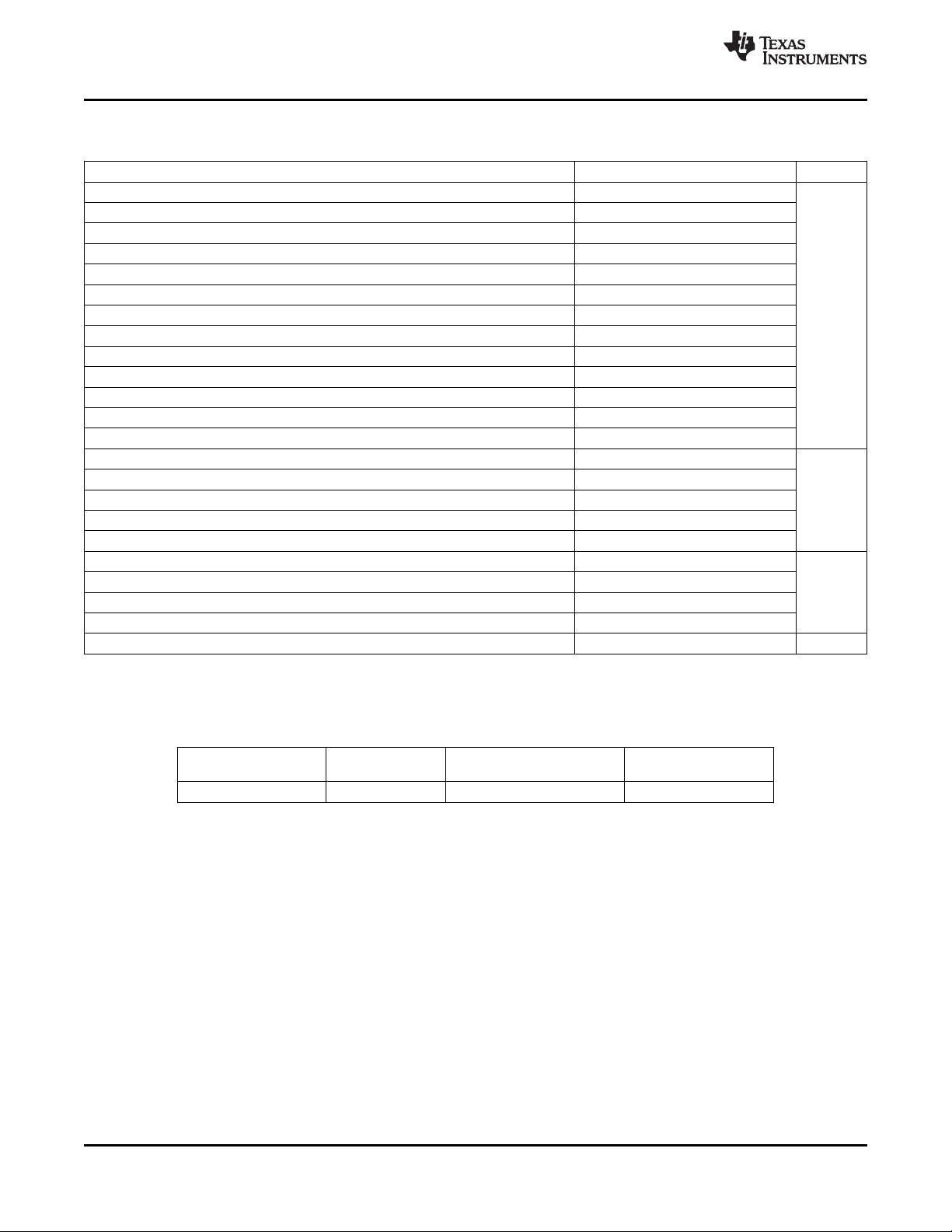

AVAILABLE OPTIONS

T

J

– 40 ° C to 125 ° C TPS65820RSH TPS65820

(1) For the most current package and ordering information, see the Package Option Addendum at the end

of this document, or see the TI Web site at www.ti.com .

(2) The RSH package is available in tape and reel. Add suffix R (TPS65820RSHR) to order quantities of

2000 parts per reel. Add suffix T (TPS65820RSHT) to order quantities of 250 parts per reel.

(3) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total

product weight, and is suitable for use in specified lead-free soldering processes. In addition, this

product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb)

above 0.1% of total product weight.

(4) Other power-up sequences and default power-up states for the supplies can be implemented upon

request. Consult factory for available options

DEVICES

(2) (3) (4)

(1)

MARKING

2 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

RTC_OUT

AC

BAT

OUT

USB

TMR

ISET1

TS

I2CINTERFACE

ANDINTERRUPT

CONTROLLER

INT

SDAT

SCLK

RESET

CONTROLLER

HOT_RST

RESPWRON

TRSTPWON

L1

PGND1

SM2

L2

L3

SM3

SIM

RED

BLUE

GREEN

SYS_IN

1.25V-3.3V

150 mA

LDO1

1.25V-3.3V

150 mA

LDO2

LDO3

1.224V-4.4V

100 mA

VIN_LDO35

1.224V-4.4V

100 mA

LDO4

LDO35_REF

ANLG1

ANLG2

GPIO1

GPIO2

3.3V

10 mA

LDO_PM

FB3

BAT

OUT

ADC_REF

GPIO3

AGND2

PGND3

VIN_SM1

VIN_SM2

PGND2

VIN_LDO12

DPPM

PWM

1.224V-4.4V

100 mA

LDO5

AGND1

LED_PWM

3.3V

150 mA

LDO0

AGND0

LDO3,4,5

LDO0,1,2

CONTROL

LOGIC

PWM

DRIVER

RGB

DRIVER

WHITELED

DRIVER

DISPLAY ANDI /O

GPIO’S

OUT

SM1

8 CHANNEL

MUX

A/D

CONVERTER

6 INTERNAL

CHANNELS

SM3_SW

2.6V/3.1V

8 mA

POWERPATH

CONTROL

LINEAR

CHARGER

0.6-1.8V

600 mA

1.0V-3.4V

600 mA

LDO_PM

CHARGE

MANAGEMENT

DC/DC

HOSTINTERFACE AND

SEQUENCING

ADC

AGND2

REFERENCE

SYSTEM

INTERNAL BIAS

OUT

OUT

OUT

TPS65820

SIM,RTCLDOS

SYSTEM

POWER

ON/OFF

OUT

AGND1AGND1

AGND1

OUT

AGND1

AGND1

AGND1

OUT

AGND1

BAT

AGND1

AGND 0,AGND 1 AND AGND 2PINSSHORTEDTOEACHOTHERINSIDETPS 65800. ALL AGNDPINS AREINTERNALLY CONNECTEDTO

THETPS 65800 THERMAL PAD ANDSUBSTRATE .

PGND1 ,PGND 3 ANDPGND 3PINS ARENOTCONNECTEDTOEACHOTHERORTOTHETPS

65800 SUBSTRATE / POWERPAD

DISPLAY ANDI/O

OUT

1.8V/3V

8mA

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

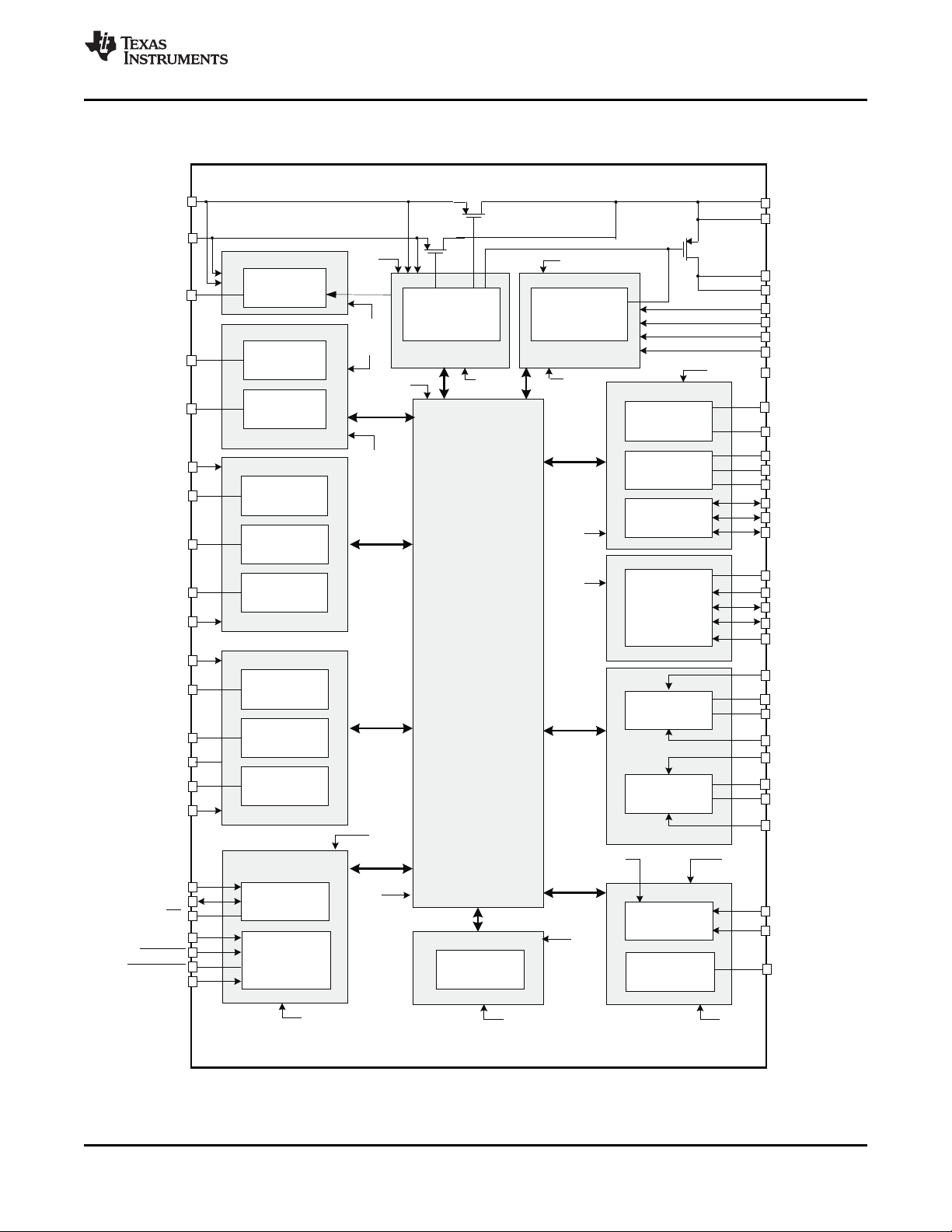

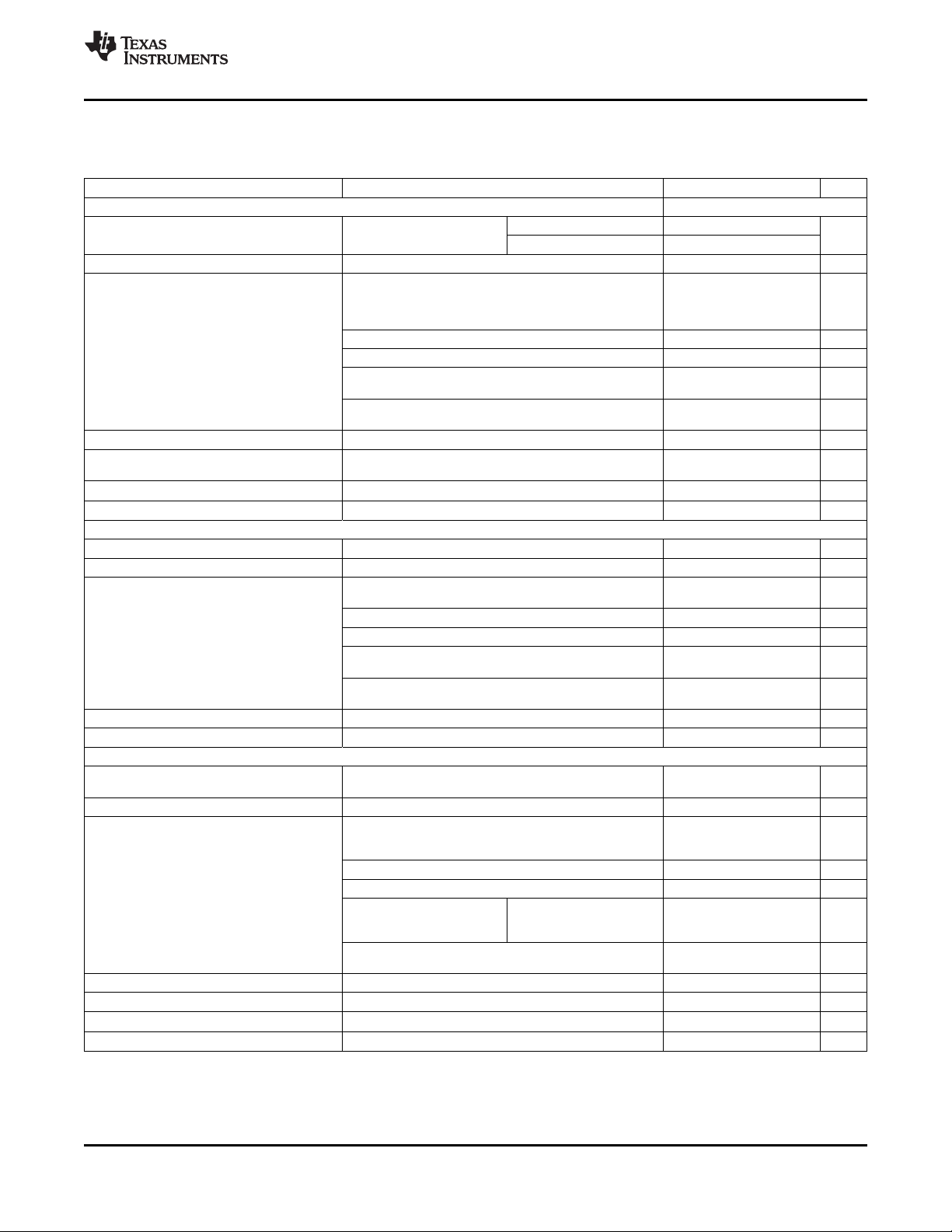

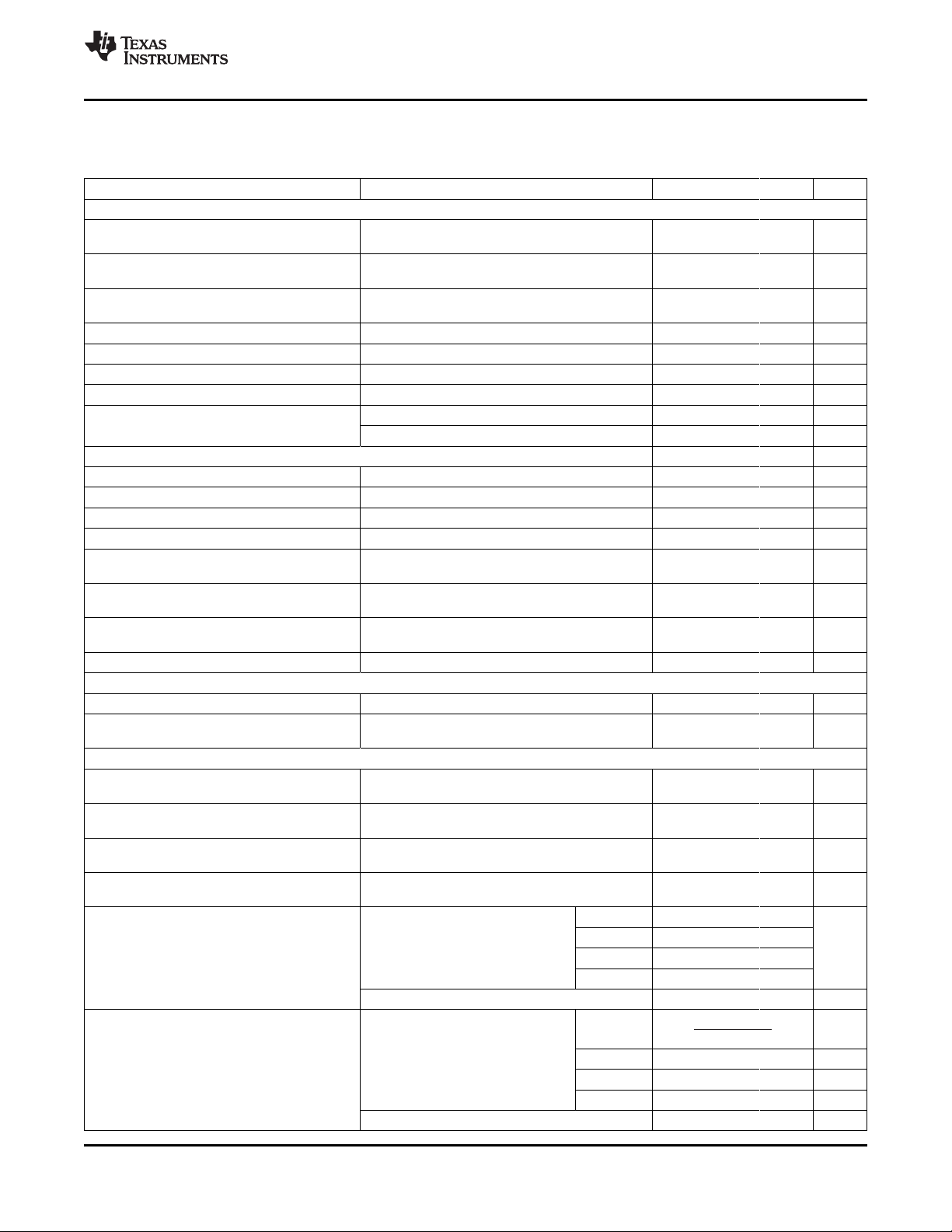

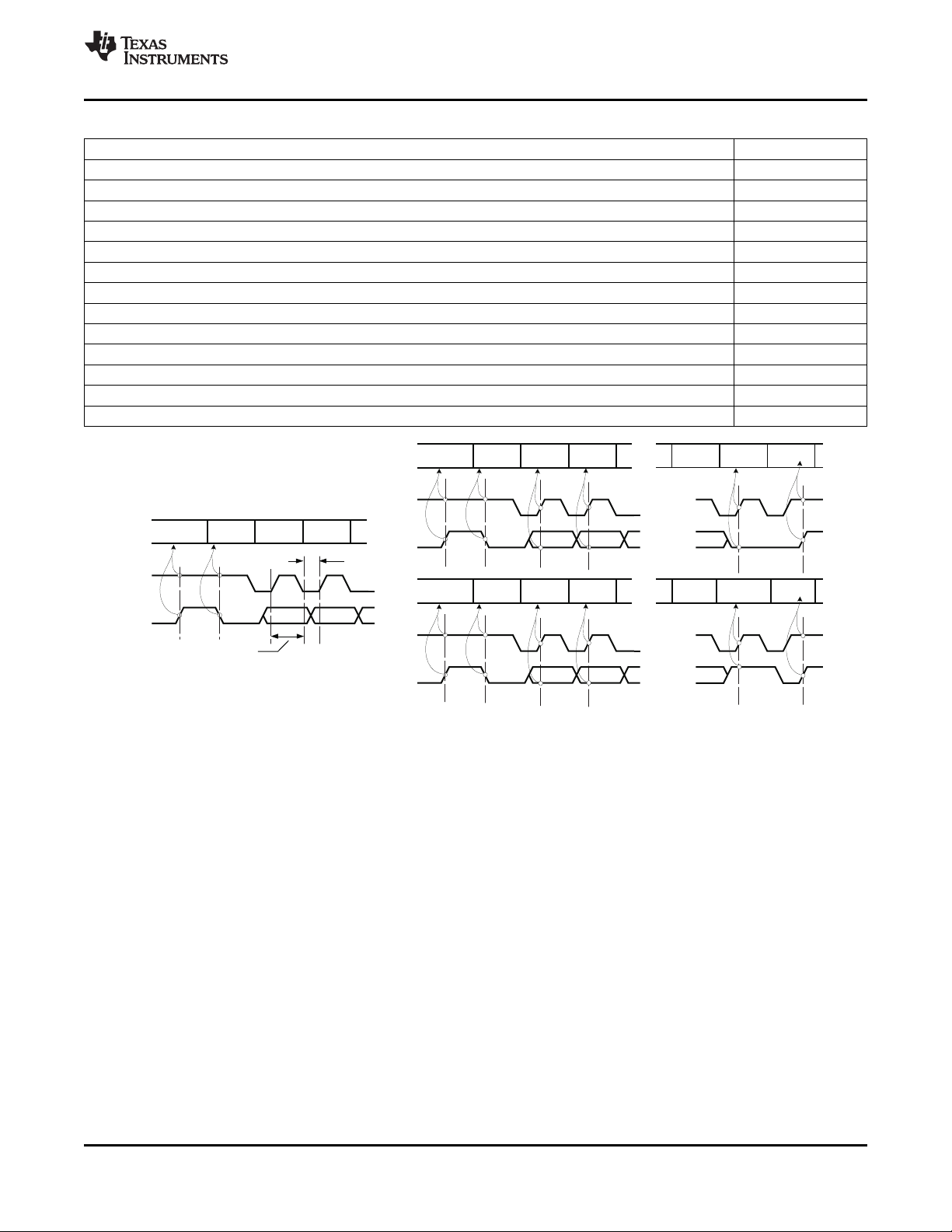

FUNCTIONAL BLOCK DIAGRAM

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 3

Figure 1. TPS65820 Simplified Block Diagram

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

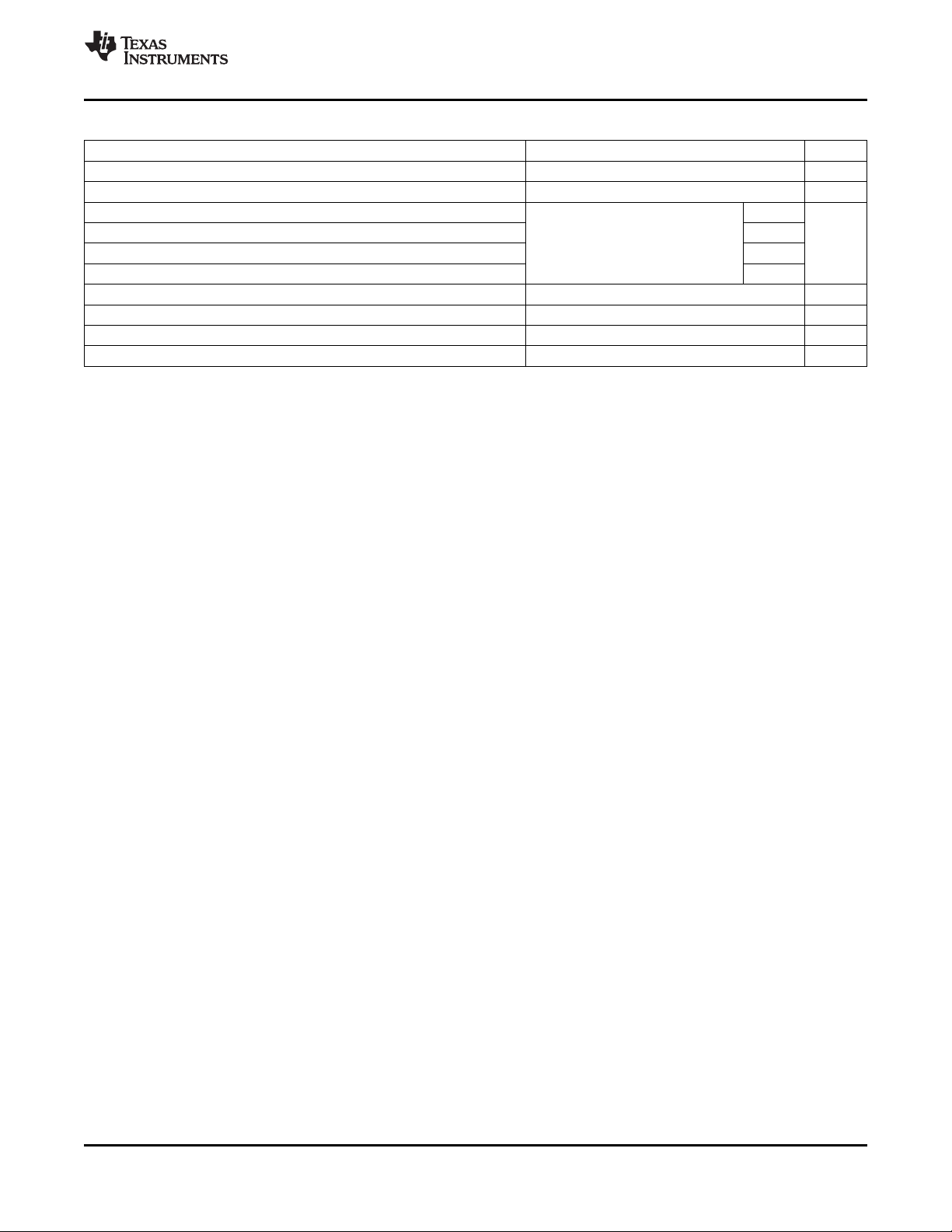

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)

AC and USB with respect to AGND1 – 0.3 to 18

ANLG1, ANLG2 with respect to AGND2 – 0.3 to V(OUT)

V(OUT) with respect to AGND1 5

VIN_LDO12, VIN_LDO35, LDO3, LDO4, LDO5 with respect to AGND2 – 0.3 to V(OUT)

LDO35_REF, ADC_REF with respect to AGND2 – 0.3 to smaller of: 3.6 or V(OUT)

SIM, RTC_OUT with respect to AGND1 – 0.3 to smaller of: 3.6 or V(OUT)

SM1, L1, VIN_SM1 with respect to PGND1 – 0.3 to V(OUT) V

SM2, L2, VIN_SM2 with respect to PGND2 – 0.3 to V(OUT)

SM3, L3 with respect to PGND3 – 0.3 to 29

SM3SW with respect to PGND3 – 0.3 to V(OUT)

FB3 with respect to PGND3 – 0.3 to 0.5

All other pins (except AGND and PGND), with respect to AGND1 – 0.3 to V(OUT)

AGND2, AGND0, PGND1, PGND2, PGND3 with respect to AGND1 – 0.3 to +0.3

Input Current, AC pin 2750

Input Current, USB pin 600

Output continuous current, OUT pin 3000 mA

Output conitnuous current, BAT pin – 3000

Continuous current at L1, PGND1, L2, PGND2 1800

T

T

T

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

Operating free-air temperature – 40 to 85

A

Maximum junction temperature 125

J

Storage temperature – 65 to 150

STG

Lead temperature 1,6 mm (1/16-inch) from case for 10 seconds 260

ESD rating, all pins 1.5 kV

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(1)

VALUE UNIT

www.ti.com

° C

DISSIPATION RATINGS

PACKAGE θ

(1) (2)

RSH

JA

21.7 ° C/W 3.22 W 0.046 W/ ° C

(1) This data is based on using the JEDEC High-K board and the exposed die pad is connected to a Cu

pad on the board. This is connected to the ground plane by a via matrix.

(2) The RSH package MSL Level : HIR3 at 260 ° C

4 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

TA≤ 55 ° C DERATING FACTOR

POWER RATING ABOVE TA= 55 ° C

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

RECOMMENDED OPERATING CONDITIONS

AC and USB with respect to AGND1 4.35 16.5

ANLG1,ANLG2 with respect to AGND2 0 2.6 V

VIN_LDO35 with respect to AGND2 Greater of : 3.6 V OR minimum input 4.7

VIN_LDO12 with respect to AGND1 4.7

VIN_SM1 with respect to PGND1 4.7

VIN_SM2 with respect to PGND2 4.7

SM3 with respect to PGND3 28 V

T

A

T

J(op)

T

J

Operating free-air temperature – 40 85 ° C

Junction temperature, functional operation assured – 40 125 ° C

Junction temperature, electrical characteristics assured 0 125 ° C

(1) Thermal operating restrictions are reduced or avoided if input voltage does not exceed 5 V.

voltage required for LDO/converter

operation outside dropout region

MIN MAX UNIT

(1)

V

V

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Link(s): TPS65820

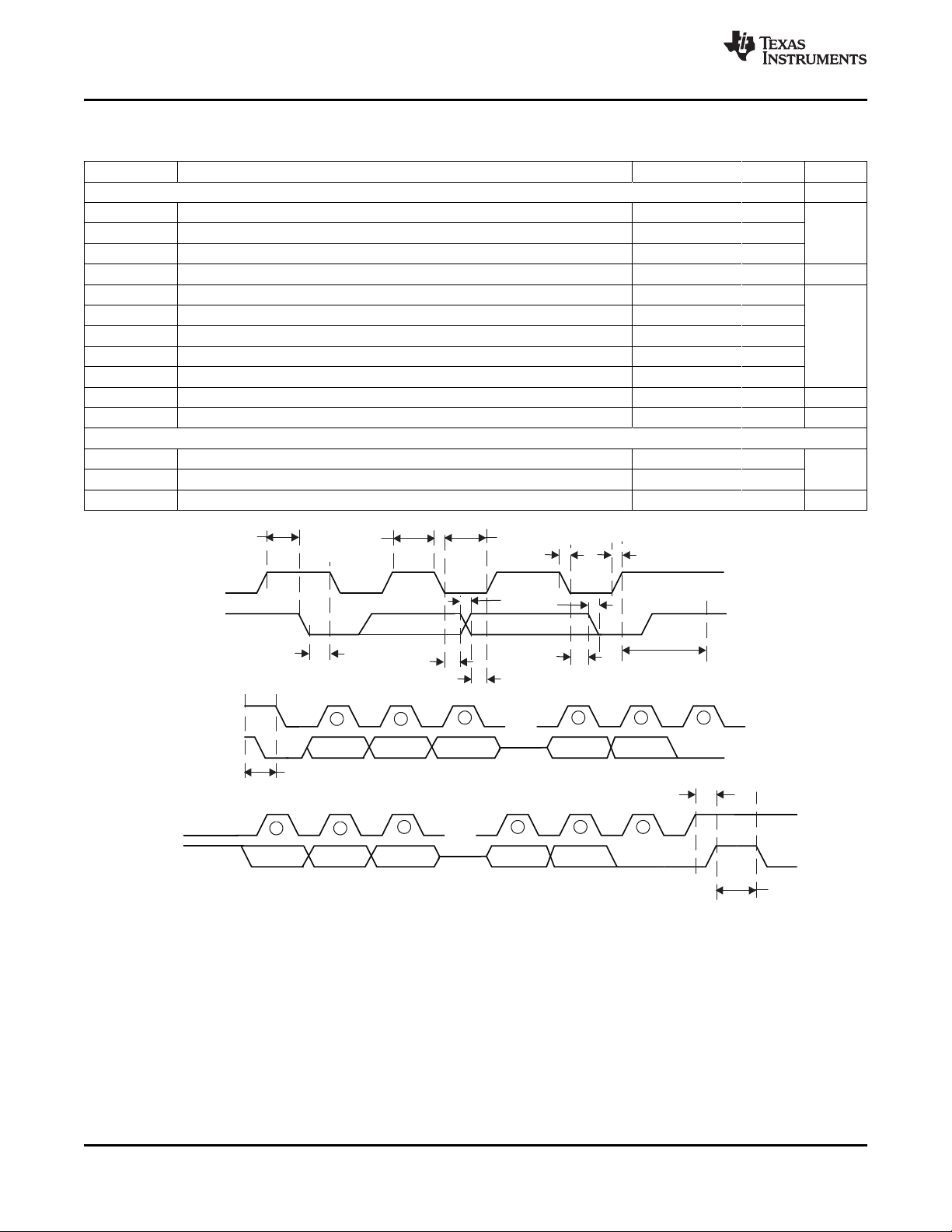

t

su(STOP)

t

(BUF)

STOP

START

1

9873

2

1

9873

2

ACK

ACK

SCL

SCL

SDA

SDA

t

su(STA)

START

t

r

STOP

t

h(STA)

t

h(DAT)

t

su(DAT)

SCL

SDA

t

w(H)

t

w(L)

t

f

t

r

t

f

t

h(DAT)

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

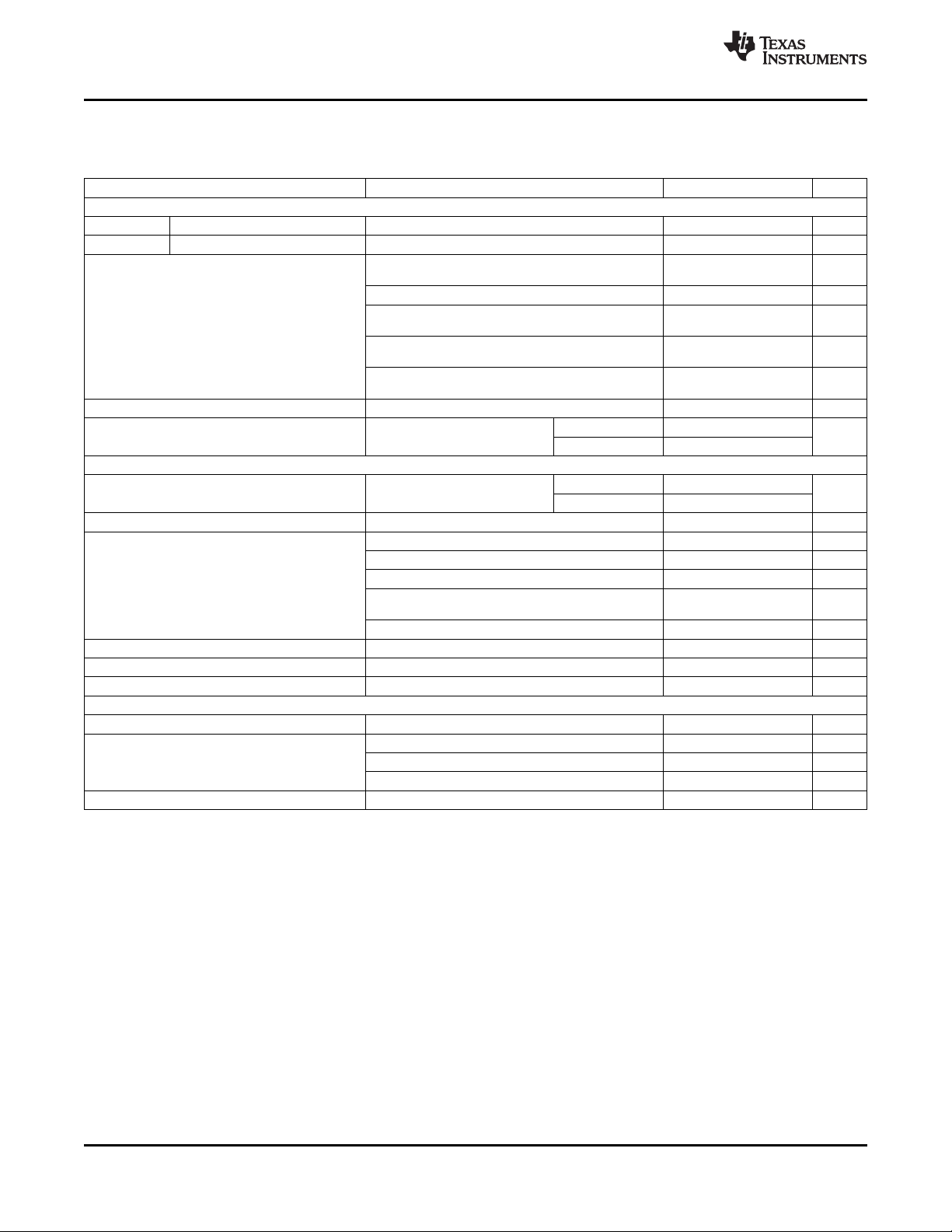

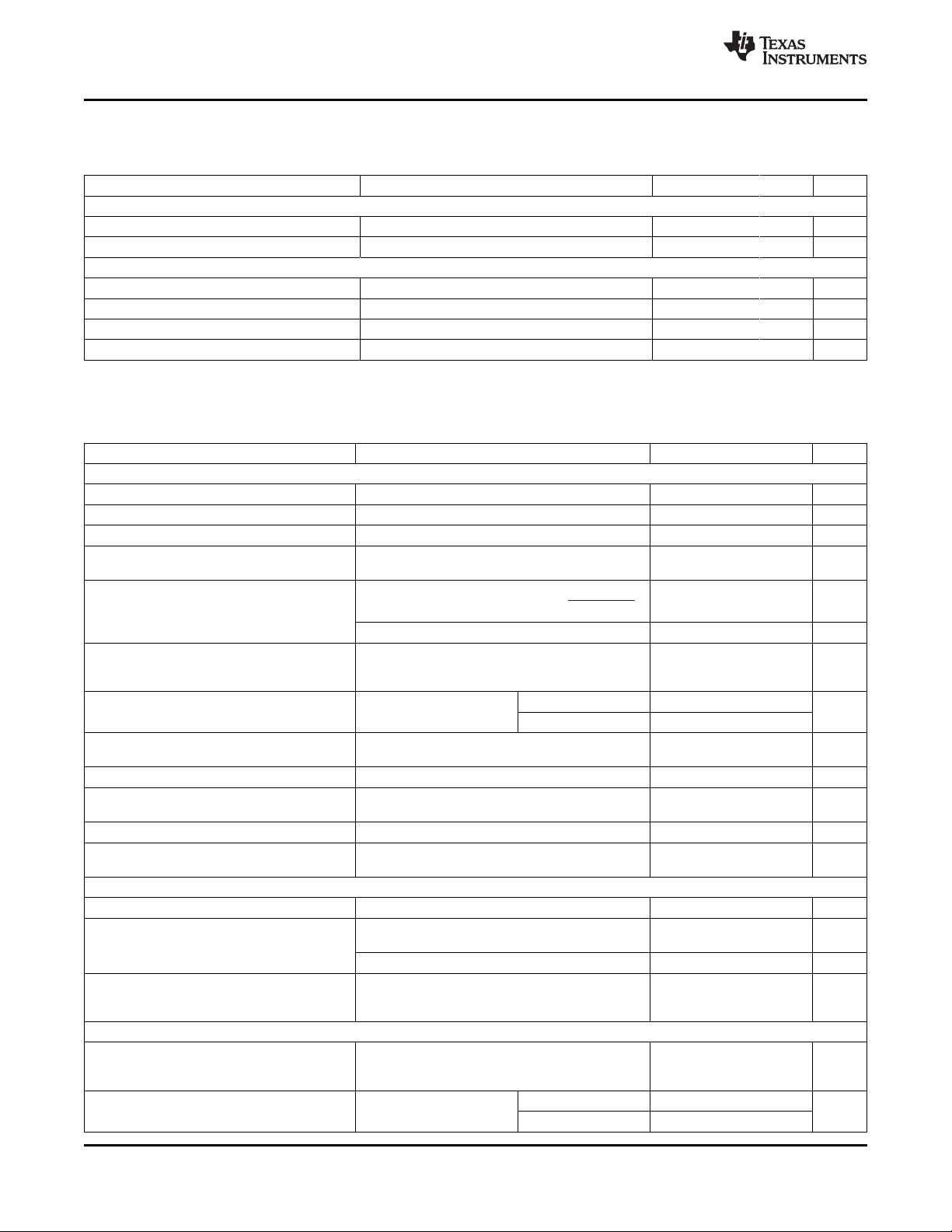

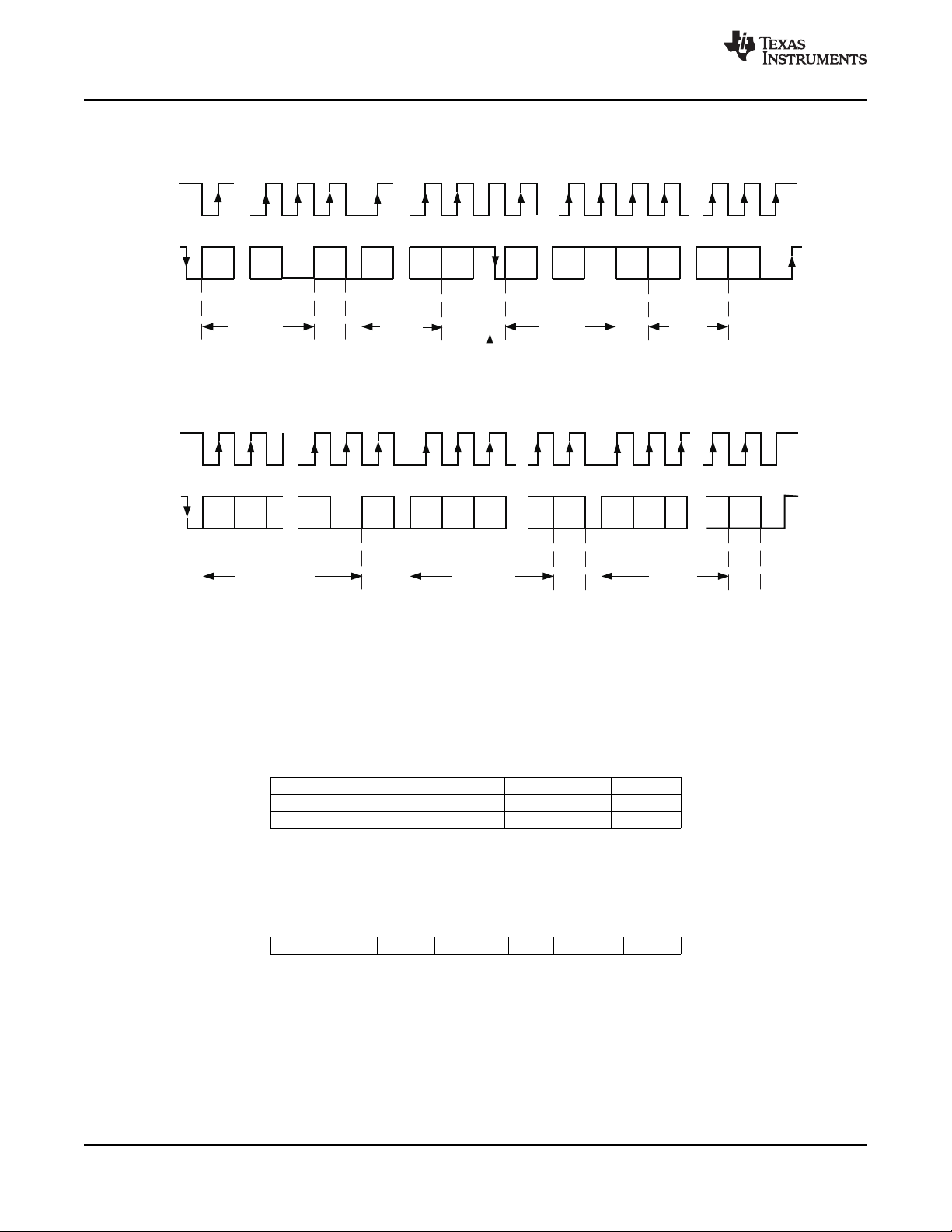

ELECTRICAL CHARACTERISTICS – I2C INTERFACE

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in figure (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I2C TIMING CHARACTERISTICS

t

R

t

F

t

W(H)

t

W(L)

t

SU(STA)

t

H(STA)

t

SU(DAT)

t

H(DAT)

t

SU(STOP)

t

(BUF)

FSCL Clock Frequency 400 kHz

I2C INTERFACE LOGIC LEVELS

V

IH

V

IL

I

H

SCLK/SDATA rise time 300

SCLK/SDATA fall time 300 ns

SCLK pulse width high 600

SCLK Pulse Width Low 1.3 µ s

Setup time for START condition 600

START condition hold time after which first clock pulse is generated 600

Data setup time 100 ns

Data hold time 0

Setup time for STOP condition 600

Bus free time between START and STOP condition 1.3 µ s

High level input voltage 1.3 6

Low level input voltage 0 0.6

Input bias current 0.01 µ A

www.ti.com

V

6 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Figure 2. I2C Timing

Product Folder Link(s): TPS65820

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

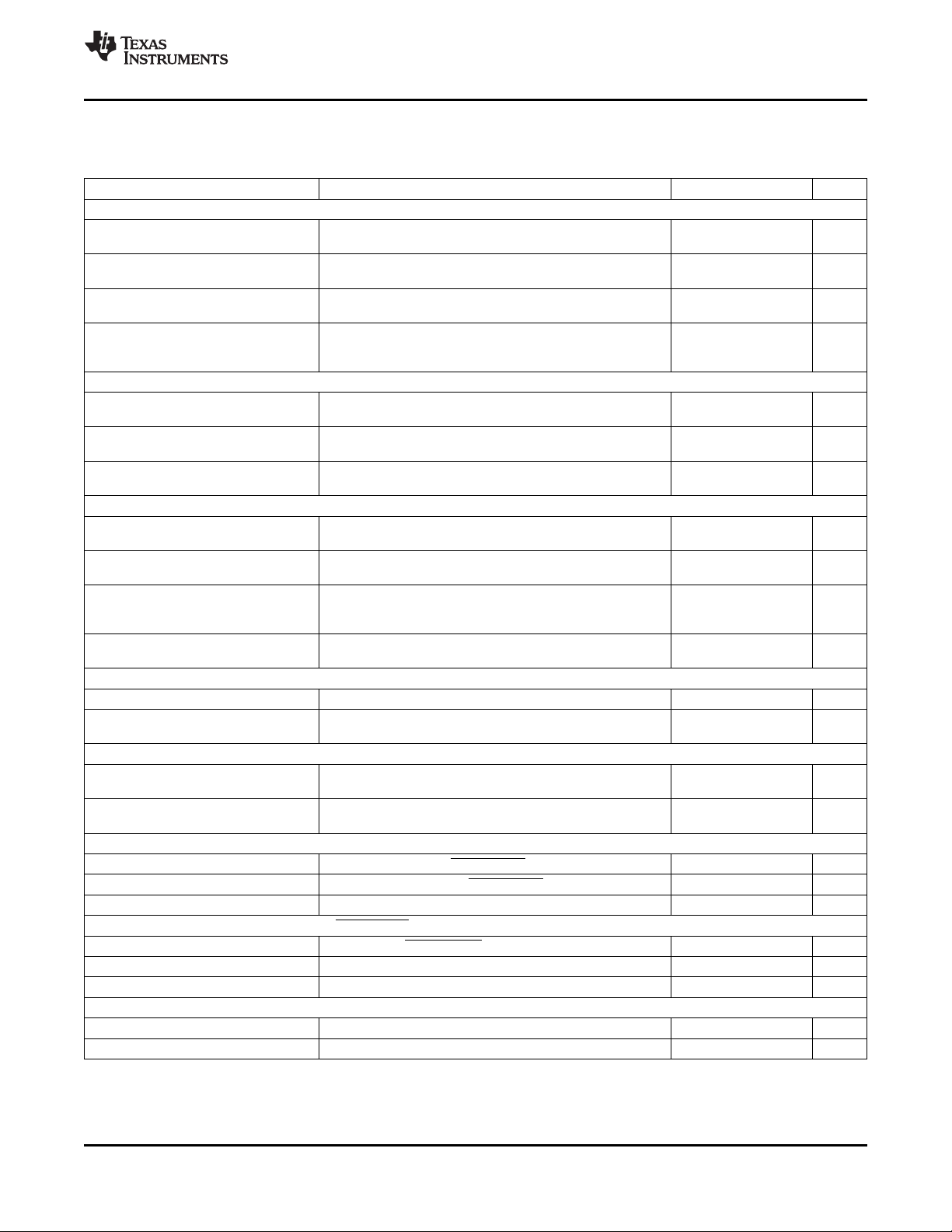

ELECTRICAL CHARACTERISTICS – SYSTEM SEQUENCING AND OPERATING MODES

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

QUIESCENT CURRENT

I

BAT(SLEEP)

I

BAT(DONE)

I

BAT(CHGOFF)

I

INP(CHGOFF)

UNDER-VOLTAGE LOCKOUT

V

UVLO

V

UVLO_HYS

t

DGL(UVLO)

SYSTEM LOW VOLTAGE THRESHOLD

V

LOW_SYS

V

HYS(LOWSYS)

t

DGL(HOTPLUG)

t

DGL(LOWSYS)

THERMAL FAULT

T

SHUT

T

HYS(SHUT)

INTEGRATED SUPPLY POWER FAULT DETECTION

V

PGOOD

V

HYS(PGOOD)

HOT RESET FUNCTION

V

HRSTON

V

HRSTOFF

t

DGL(HOTRST)

SYSTEM RESET – OPEN DRAIN OUTPUT RESPWRON

V

RSTLO

I

TRSTPWON

K

RESET

SEQUENCING DELAYS

t

DLY(D1)

t

DLY(D1)

BAT pin current, sleep

mode set

Input power not detected, V(BAT) = 4.2 V, Sleep mode set 370 µ A

BAT pin current, charge Charger function enabled by I2C, termination detected, input

terminated power detected and selected

BAT pin current, charge Charger function disabled by I2C, termination not detected,

function OFF input power detected and selected

AC or USB pin current,

charge function OFF

Internal UVLO detection NO POWER mode set at V(OUT) < V

threshold V(OUT) decreasing

UVLO detection

hysteresis

UVLO detection deglitch

time

Minimum system voltage System voltage V(SYS_IN) decreasing, SLEEP mode set if

detection threshold V(SYS_IN) < V

Minimum system voltage

detection hysteresis

Minimum system voltage

detection hotplug 650 ms

deglitch time

Minimum system voltage

detection deglitch time

Charger function disabled by I2C, termination not detected,

input power detected and selected. All integrated supplies 200 µ A

and drivers OFF, no load at OUT pin.

,

UVLO

– 3% 2.5 3% V

V(OUT) increasing 120 mV

Falling voltage only 5 ms

LOW_SYS

0.97 1 1.03 V

V(SYS_IN) increasing 50 mV

V(SYS_IN) decreasing, valid only for initial power-up, see

state machine diagram

V(SYS_IN) decreasing, hotplug deglitch time expired 5 ms

Thermal shutdown Increasing junction temperature 165 ° C

Thermal shudown

hysteresis

Power good fault Falling output voltage, applies to all integrated supply outputs.

detection threshold Referenced to the programmed output voltage value

Power good fault Rising output voltage, applies to all integrated supply outputs.

detection hysteresis Referenced to V

Low level input voltage RESET mode set at V( HOT_RESET) < V

High level input voltage HOT reset not active at V( HOT_RESET) > V

Decreasing junction temperature 30 ° C

84% 90% 96%

threshold

PGOOD

HRSTON

HRSTOFF

3% 5% 7%

1.3 V

Hot reset input deglitch 5000 µ s

Low level output voltage IIL= 10 mA, V( RESPWRON ) < V

RSTLO

Pullup current source Internally connected to TRSTPWRON pin 0.9 1 1.2 µ A

Reset timer constant T

= K

RESET

° C

RESET

TRSTPWON

Sequencing delay See sequencing timing diagram 0.24 ms

Sequencing delay See sequencing timing diagram 12 ms

3 µ A

3 µ A

0.4 V

0 0.3 V

1 ms/nF

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

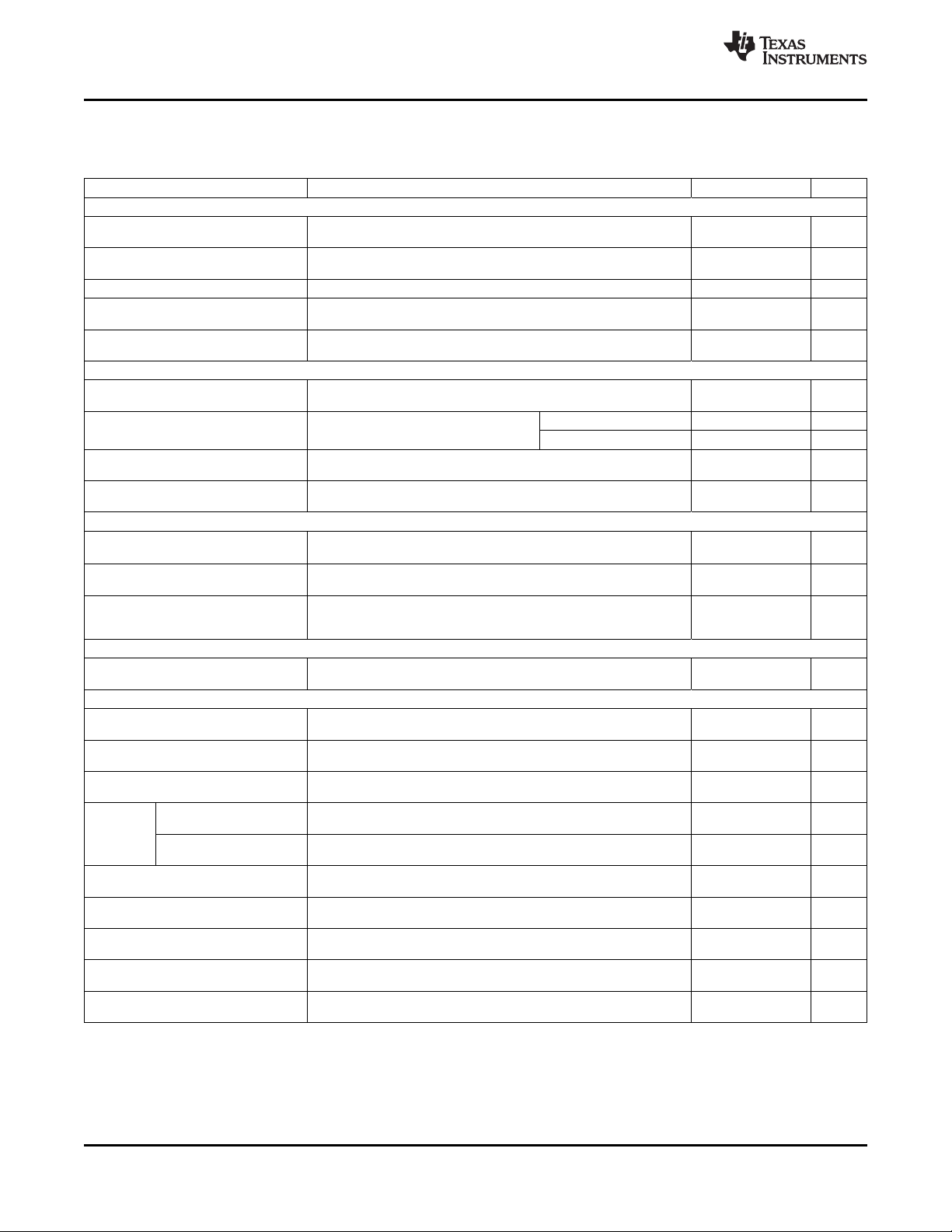

ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VOLTAGE DETECTION THRESHOLDS

V

IN(DT)

V

IN(NDT)

t

DGL(NDT)

V

SUP(DT)

V

SUP(NDT)

Input voltage detection AC detected at V(AC) – V(BAT) > V

threshold USB detected at V(USB) – V(BAT) > V

Input Voltage removal AC not detected at V(AC) – V(BAT) < V

threshold USB not detected at V(USB) – V(BAT) < V

Power not detected deglitch 22.5 ms

Supplement detection

threshold

Supplement not detected

threshold

POWER PATH INTEGRATED MOSFETs CHARACTERISTICS

V

ACDO

V

USBDO

V

BATDODCH

V

BATDOCH

AC switch dropout voltage V

USB switch dropout voltage

Battery switch dropout

voltage, discharge

Battery switch dropout

voltage, charge

POWER PATH INPUT CURRENT LIMIT

I

INP(LIM1)

I

INP(LIM2)

Selected Input current limit,

applies to USB input only

Selected Input current limit,

applies to USB input only

Selected Input current limit,

I

INP(LIM3)

applies to either AC or USB 2.75 A

input

SYSTEM REGULATION VOLTAGE

V

SYS(REG)

Output regulation voltage 4.6 4.7 V

POWER PATH PROTECTION AND RECOVERY FUNCTIONS

V

INOUTSH

R

SH(USBSH)

R

SH(ACSH)

Input-to-output short-circuit

detection threshold

OUT short-circuit recovery

pullup resistor

OUT short-circuit recovery

pullup resistor

Overvoltage detection Rising voltage, overvoltage detected when V(AC) > V

V

OVP

threshold V(USB) > V

Overvoltage detection

hysteresis

V

BATOUTSH

K

BLK(SHBAT)

I

SH(BAT)

R

SHBAT)

R

DCH(BAT)

Battery-to-output short-circuit

detection threshold

Battery-to-ouput short-circuit V

blanking time constant from DPPM pin to AGND1

OUT short-circuit recovery V

pullup current source Internal current source connected between OUT and BAT

BAT short-circuit recovery V

resistor Internal resistor connected from OUT to BAT

BAT pulldown resistor 500 Ω

Battery switch ON at V(BAT) – V(OUT) > V

Battery switch OFF at V(BAT) – V(OUT) < V

= V(AC) – V(OUT); V(AC) = 4.75-V AC input current limit set to 2.75 A

ACDO

(typ), I

V

USBDO

USB input current limit set to 2.75 A (typ)

V(BAT): 3 V → V

= 1 A

O(OUT)

= V(USB) – V(OUT); V(USB) = 4.6 V I(OUT) + I(BAT)= 0.5 A 175 190 mV

, I(BAT) = – 1 A 60 100 mV

CH(REG)

Charger on, V(BAT): 3 V → 4.2 V, I(BAT) = 1 A 60 100 mV

Selected input switch not in dropout, I2C settings : ISET2 = LO,

PSEL = LO

Selected input switch not in dropout, I2C settings: ISET2 = HI, PSEL = LO

Selected input switch not in dropout, I2C settings: ISET2 = HI OR LO,

PSEL = HI

V

reached. Selected input voltage (AC or USB) > 5.1 V

= V(OUT), DPPM loop not active, selected input current limit not

SYS(REG)

AC and USB switches set to OFF if V(OUT) < V

V(OUT) < 1 V, internal resistor connected from USB to OUT 500 Ω

V(OUT) < 1 V, internal resistor connected from AC to OUT 500 Ω

OVP

Falling voltage, relative to detection threshold 0.1 V

BAT switch set to OFF if V(BAT) – V(OUT)> V

< 1V, t

(DPPM)

(BAT)

(BAT)

BLK(SHBAT)

– V

> V

(OUT)

< 1V,

= K

BLK(SHBAT)

,

BATOUTSH

Internal resistor connected from BAT to AGND1 when battery is not detected

by ANLG1

;

IN(DT)

IN(DT)

;

IN(NDT)

IN(NDT)

SUP(DT)

SUP(NDT)

I(OUT) + I(BAT)= 0.1 A 35 45 mV

INOUTSH

or

OVP

BATOUTSH

× C

C

DPPM,

capacitor is connected

DPPM

www.ti.com

190 mV

125 mV

60 mV

20 mV

350 375 mV

80 100 mA

400 500 mA

0.6 V

6 6.5 6.8 V

200 mV

1 mS/nF

10 mA

1 k Ω

8 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

V(OUT)* 1.2

500 kW

I

O(BAT)

+

K

(SET)

V

(SET)

R

SET

I

O(PRECHG)

+

V

(PRECHG)

K

(SET)

R

SET

I

(TERM)

+

V

(TERM)

K

(SET)

R

SET

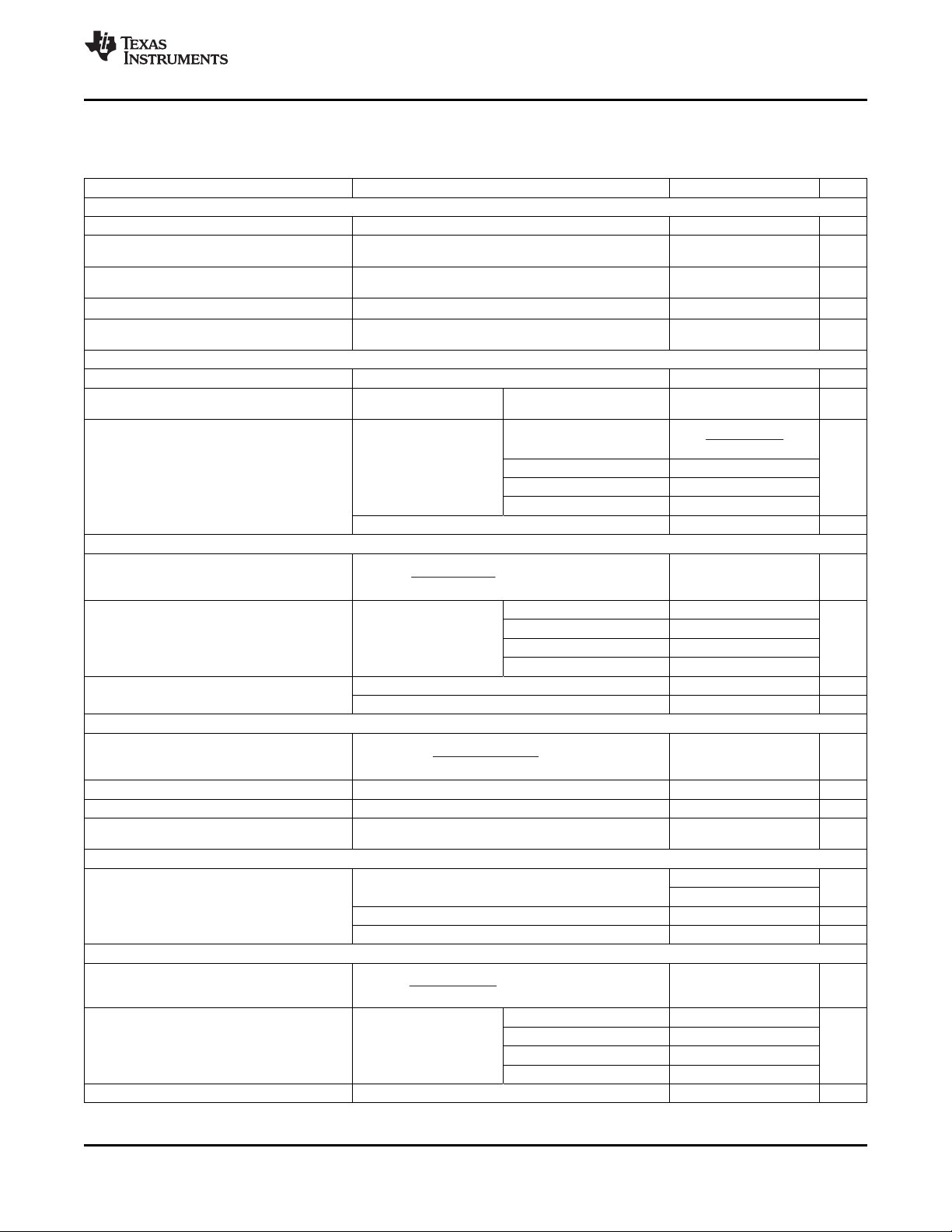

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT (Continued)

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

POWER PATH TIMING CHARACTERISTICS, DPPM AND THERMAL LOOPS NOT ACTIVE, R

t

BOOT

t

SW(ACBAT)

t

SW(USBBAT)

t

SW(PSEL)

t

SW(ACUSB)

Boot-up time Measured from input power detection 120 200 300 ms

Switching from AC to BAT 50 µ s

Switching from USB to BAT 50 µ s

Switching from USB to AC 50 µ s

Switching from AC to USB or USB to

AC

No USB: measured from V(AC) – V(BAT) < V

detected: CE = LO (after CE hold-off time)

No AC: measured from V(USB) – V(BAT) < V

detected: CE = LO (after CE hold-off time)

Toggling I2C PSEL bit

AC power removed or USB power removed 100 µ s

BATTERY REMOVAL DETECTION

V

NOBATID

t

DGL(NOBAT)

Battery ID resistor detection ID resistor not detected at V(OUT) – V(ANLG1) < V

Deglitch time for battery removal

detection

00, V

Set via I2C bits (BATID1,

I

O(ANLG1)

ANLG1 pullup current

BATID2) ADC_WAIT register

01 10

10 50

11 60

Total accuracy 25% 25%

FAST CHARGE CURRENT, V(OUT) > V(BAT) + 0.1 V, V(BAT) > V

LOWV

TMR

: 2.5 V to 4.4 V

(OUT)

= 50 k Ω

IN(NDT)

IN(NDT)

, USB

, USB

NOBATID

0.5 V

0.6 1.2 ms

µ A

I

O(BAT)

V

SET

K

SET

Charge current range 100 1500 mA

Battery charge current set voltage V

Battery charge current set factor

PRECHARGE CURRENT, V(OUT) > V(BAT) + 0.1 V, V

I

O(PRECHG)

V

PRECHG

V

LOWV

t

DGL(PRE)

CHARGE REGULATION VOLTAGE, V(OUT) > V

V

O(BATREG)

CHARGE TERMINATION, V(BAT) > V

I

TERM

V

TERM

t

DGL(TERM)

Precharge current range 10 150 mA

Precharge set voltage V

Precharge to fast-charge transition Fast charge at V(BAT) > V

Deglitch time for fast charge to

precharge transition

O(BATREG)

Battery charge voltage

, VOLTAGE REGULATION MODE SET

RCH

Charge termination current range 10 150 mA

Battery termination detection set V

voltage (ISET1_1, SET1_0) =

Deglitch time for termination detection V(ISET1) < V

11, 100% scaling 2.475 2.5 2.525

V

= V(ISET1),

SET

(ISET1_1, ISET1_0) =

10, 75% scaling 1.875 1.9 1.925

01, 50% scaling 1.225 1.25 1.275

00, 25% scaling 0.575 0.6 0.625

100 mA < I

1 mA < I

< V(BAT) < V

BATSH

PRECHG

Decreasing battery voltage, R

≤ 1 A 350 400 450

O(BAT)

≤ 100 mA 100 400 1000

O(BAT)

, t < t

LOWV

(PRECHG)

= V(ISET1) 220 250 270 mV

LOWV

= 50 k Ω 22.5 ms

TMR

2.8 3 3.2 V

+ 0.1V

Voltage options, selection via I2C

4.2

4.356

Accuracy, TA= 25 ° C – 0.5% 0.5%

Total accuracy – 1% 1%

11, 100% scaling 240 260 280

= V(ISET1),

TERM

10, 75% scaling 145 160 175

01, 50% scaling 90 110 130

00, 25% scaling 40 60 75

, R

TERM

= 50 k Ω 22.5 ms

TMR

V

mV

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT (Continued)

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

BATTERY RECHARGE DETECTION

V

RCH

t

DGL(RCH)

Recharge threshold voltage 80 100 130 mV

Deglitch time for recharge detection R

DPPM FUNCTION

V

DPPM

I

O(DPPM)

K

DPPM

t

DGL(DPPM)

DPPM regulation point range V

DPPM pin current source AC or USB present 95 100 105 µ A

DPPM scaling factor 1.139 1.15 1.162

DPPM de-glitch time 500 µ s

PACK TEMPERATURE SENSING

V

LTF

V

HTF

I

O(TS)

t

DLG(TFAULT)

Low temperture threshold Pack low temperature fault at V(TS) > V

High temperture threshold Pack low temperature fault at V(TS) < V

Temperature sense current source Thermistor bias current 18.8 20 21.2 µ A

Deglitch time for temperature fault R(TMR) = 50 k Ω ,

detection V(TS) > V

CHARGE AND PRECHARGE SAFETY TIMER

t

CHG

K

TMR

t

CHGADD

t

PRECHG

K

PRE

t

PCHGADD

R

TMR

R

TMR(FLT)

Charge safety timer programmed Safety timer range, thermal/DPPM loop not active,

value t

Charge timer set factor 0.313 0.360 0.414 s/ Ω

Total elapsed time when DPPM or fast charge on, t

thermal loop are active t

Precharge safety timer programmed Pre charge safety timer range, thermal/DPPM loop not active,

value t

Precharge timer set factor 0.09 0.1 0.11

Total elapsed time when DPPM or Precharge on, t

thermal loop are active t

External timer resistor limits 30 100 k Ω

Timer fault recovery pullup resistor 1 k Ω

THERMAL REGULATION LOOP

T

THREG

Temperature regulation limit 115 135 ° C

CHARGER THERMAL SHUTDOWN

T

THCHG

T

THCHGHYS

Charger thermal shutdown Charger turned off when TJ> T

Charger thermal shutdown hysteresis 30 ° C

New charge cycle starts if V(BAT) < V

termination was detected

= 50 k Ω 22.5 ms

TMR

= R

(DPPM)

× K

DPPM

x I

DPPMM

O(DPPM)

– V

O(BATREG)

, after

RCH

2.6 4.4 V

Status bit set indicating DPPM loop active after deglitch time,

R

= 50 k Ω

TMR

LTF

HTF

OR V(TS) < V

LTF

= R

CHG

CHG

PRECHG

PRECHG

× K

TMR

TMR

CHGADD

= K

× R

PRE

PCHGADD

HTF

is the maximum add-on time added to

× K

TMR

TMR

is the maximum add-on time added to 2 ×

2.465 2.500 2.535 V

0.485 0.500 0.515 V

18 30 60 min

Internal resistor connected from OUT to BAT after safety timer

timeout

Charge current decreasesd and timer extended when TJ>

T

THREG

THCHG

22.5 ms

3 5 10 hours

2 t

CHG

t

PRECHG

150 ° C

www.ti.com

hours

hours

10 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

ELECTRICAL CHARACTERISTICS – LINEAR REGULATORS

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SELECTABLE OUTPUT VOLTAGE LDO ’ S : LDO1, LDO2

I

= – 1 mA 15

I

Q(LDO12)

I

O(LDO1,2)

Quiescent current, either LDO1 or

LDO2 enabled, LDO0 disabled

I

Q(LDO12)

Output current range 150 mA

Output voltage, selectable via I2C.

Dropout voltage, 150 mA load 300 mV

V

O(LDO1,2)

LDO1, LDO2 output voltage

Total accuracy, V(VIN_LDO02) = 3.65 V – 3% 3%

Line regulation, 100 mA load,

V(VIN_LDO02): V

Load regulation, load: 10 mA → 150 mA

V(VIN_LDO02) > V

P

SR(LDO12)

I

SC(LDO1,2)

R

DCH(LDO1,2)

I

LKG(LDO1,2)

PSRR at 20 kHz 150-mA load at output, V(VIN_LDO02) – V

LDO1 and -2 short-circuit current

limit

Discharge resistor 300 Ω

Output grounded 300 mA

LDO disabled by I2C command

Leakage current LDO off 2 µ A

SIM LINEAR REGULATOR

I

Q(SIM)

I

O(SIM)

Quiescent current Internally connected to OUT pin 20 µ A

Output current range 8 mA

Output voltage, selectable via I2C.

Dropout voltage, 8-mA load 0.2 V

V

O(SIM)

SIM LDO output voltage

Total accuracy, V(OUT): 3.2 V to 4.7 V, 8 mA – 5% 5%

Load regulation, load: 1 mA → 8 mA,

V(OUT) > V

Line regulation, 5 mA load, V(OUT):

V

O(SIM) TYP

I

SC(SIM)

I

LKG(SIM)

Short-circuit current limit Output grounded 20 mA

Leakage current LDO off 1 µ A

PROGRAMMABLE OUTPUT VOLTAGE LDO ’ S: LDO3, LDO4, LDO5

I

Q(LDO35)

I

O(LDO35)

Quiescent current, only one of

LDO3, LDO4, LDO5 is enabled

I

Q(LDO35)

Output current range 100 mA

Output voltage, selectable via I2C

Dropout voltage, 100-mA load 240 mV

V

O(LDO35)

LDO3, LDO4, LDO5 output voltage

Total accuracy, 100 mA load V

Load regulation,

V(VIN_LDO35) > V

0.5 V

Line regulation, 10 mA load,

V(VIN_LDO35): V

I

SC(LDO35)

PSR

(LDO35)

R

DCH(LDO35)

I

LKG(LDO35)

Short-circuit current limit Output grounded 250 mA

PSRR at 10 kHz V(VIN_LDO35) > V

Discharge resistor 400 Ω

LDO is disabled by I2C command

Leakage current LDO off 1 µ A

= I(VIN_LDO02) µ A

(LDO1,2)TYP

O(LDO1,2) TYP

+ 0.5 V

O(SIM) TYP

+ 0.5 V → 4.7 V

= I(VIN_LDO35) 70 µ A

O(LDO35)TYP

O(LDO35)TYP

O(LDO3,5)

(LDO1,2)

I

= – 150 mA 160

(LDO1,2)

Available output voltages:

TYP = 1.25, 1.5, 1.8, 2.5,

+ 0.5 V → 4.7 V

+ 0.5V

= 1 V 40 dB

O(LDO1,2)

– 1% 1%

– 1.5% 1.5%

Available output voltages:

V

O(SIM)TYP

– 3% 3%

– 2% 2%

Available output voltages :

V

O(LDO35)TYP

4.46 V, 25 mV steps

(VIN_LDO35)

= 5 V – 3% 3%

+ load: 1 mA → 50 mA – 1% 1%

+ 0.5 V → 4.7 V

– 1% 1%

+ 1 V, 50 mA load at output 40 dB

V

O(LDO1,2)

2.85, 3, 3.2, 3.3

= 1.224 V to V

= 1.8 or 3

V

V

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

ELECTRICAL CHARACTERISTICS – LINEAR REGULATORS (continued)

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

RTC_OUT LINEAR REGULATOR

I

Q(RTC_OUT)

I

O(RTC_OUT)

V

O(RTC_OUT)

I

SH(RTC_OUT)

I

LKG(RTC_OUT)

LDO0 LINEAR REGULATOR

I

Q(LDO0)

I

O(LDO0)

V

O(LDO0)

PSR

I

SC(LDO0)

I

LKG(LDO0)

LDO_PM LINEAR REGULATOR

I

Q(LD0_PM)

V

O(LDO_PM)

I

LKG(LDOPM)

(LDO0)

Quiescent current for RTC LDO Internally connected to OUT pin 20 µ A

Output current range 8 mA

Output voltage value, selectable via I2C.

Available output voltages:

Dropout voltage, I(RTC_OUT) = – 8 mA 200 mV

RTC_OUT output voltage sleep mode not set

Total accuracy, V(OUT): 2 V to 4.7 V, 8 mA load,

Load regulation, load: 1 mA → 8 mA, 2 V < V(OUT) < 4.7

V

Line regulation, 5 mA load

V(OUT): 2 V → 4.7 V

– 5% 5%

– 3% 3%

– 2% 2%

Short-circuit current limit V(RTC_OUT) = 0 V 20 mA

Leakage current nA

Quiescent current µ A

V(RTC_OUT) = 1.5 V,

V(OUT) = 0 V

Internally connected to VIN_LDO12

pin

TJ= 85 ° C 880

TJ= 25 ° C 250

I(LDO0) = – 1 mA 15

I(LDO0) = – 150 mA 160

Output current range 150 mA

Fixed output voltage value 3.3 V

Dropout voltage, I(LDO0) = – 150 mA 300 mV

Output voltage

Total accuracy – 3% 3%

Line regulation, V(OUT): V

– 100 mA

+ 0.5 → 4.7 V, I(LDO0) =

O(LDO0)

– 1% 1%

Load regulation, I(LDO0) = – 10 mA → – 150 mA – 1.5% 1.5%

PSRR at 20 kHz 150-mA load at output, V(VIN_LDO12) – V

= 1 V 40 dB

O(LDO1,2)

Short-circuit current limit V(LDO0) = 0 V 300 mA

Leakage current LDO off 1 µ A

Output current range 20 mA

Fixed output voltage value, V(OUT) > 4 V 3.3 V

Output voltage Dropout voltage, I(LDOPM) = – 12 mA 0.5 0.7 V

Total accuracy – 5% 5%

Leakage current LDO off 1 µ A

2.6 V or 3.1 V

www.ti.com

V

12 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

ELECTRICAL CHARACTERISTICS – SWITCHED MODE SM1 STEP-DOWN CONVERTER

Over recommended operating conditions (typical values at TJ= 25 ° C), V

(unless otherwise noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

= I(VIN_ SM1), no output load Not switching 10

I

Q(SM1)

I

O(SM1)

V

O(SM1)

R

DSON(PSM1)

I

LKG(PSM1)

R

DSON(NSM1)

I

LKG(PSM1)

I

LIM(SM1)

f

S(SM1)

EFF

(SM1)

t

SS(SM1)

t

DLY(SM1)

Quiescent current for SM1 µ A

Output current range 600 mA

Output voltage, PWM mode

P-channel MOSFET

on-resistance

P-channel leakage current 0.1 µ A

N-channel MOSFET

on-resistance

N-channel leakage current 5 µ A

P- and N-channel current limit 3 V < V(VIN_SM1) < 4.7 V 900 1050 1200 mA

Oscillator frequency PWM mode set 1.3 1.5 1.7 MHz

Efficiency 90%

Soft start ramp time 750 µ s

Converter turn-on delay 170 µ s

Q(SM1)

SM1 OFF, set via I2C 0.1

Output voltage, selectable via I2C, standby OFF 0.6 V to 1.8 V,

V

= V

O(SM1)

Total accuracy, V

V(VIN_SM1) = 3 V to 4.7 V; 0 mA ≤ I

, output voltage range, standby ON 0.6 V to 1.8 V,

SBY(SM1)

O(SM1)TYP

Line regulation, V(VIN_SM1): 3 V → 4.7 V,

I

= 10 mA

O(SM1)

Load regulation, V(VIN_SM1) = 4.7 V,

I

: 60 mA → 540 mA

O(SM1)

V(VIN_SM1) = 3.6 V, 100% duty cycle set 310 500 m Ω

V(VIN_SM1) = 3.6 V, 0% duty cycle set 220 330 m Ω

V(VIN_SM1) = 4.2 V, PWM mode, I

V

= 3 V

O(SM1)

Converter OFF → ON, V

value

GPIO1 pin programmed as SM1 converter enable

control. Measured from V(GPIO1): LO → HI

O(SM1)

O(SM1)

= V

SBY(SM1)

: 5% → 95% of target

O(SM1)

O(SM1)

= 1.24 V, application circuit as in Figure 3

Available output

= 1.24 V,

= 300 mA,

≤ 600 mA

voltages: V

adjustable in 40 mV

steps

Available output

voltages: V

adjustable in 40 mV

steps

– 3% 3%

0.027 %/V

0.139 %/A

O(SM1)TYP

SBY(SM1)

=

=

V

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 13

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

ELECTRICAL CHARACTERISTICS – SWITCHED MODE SM2 STEP-DOWN CONVERTER

Over recommended operating conditions (typical values at TJ= 25 ° C), V

(unless otherwise noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

= I(VIN_ SM2), no output load

I

Q(SM2)

I

O(SM2)

V

O(SM2)

R

DSON(PSM2)

I

LKG(PSM2)

R

DSON(NSM2)

I

LKG(PSM2)

I

LIM(SM2)

f

S(SM2)

EFF

(SM2)

t

SS(SM2)

t

DLY(SM2)

Quiescent current for SM2 µ A

Output current range 600 mA

Output voltage

P-channel MOSFET

on-resistance

P-channel leakage current 0.1 µ A

N-channel MOSFET

on-resistance

N-channel leakage current 5 µ A

P- and N-channel current limit 3 V < V(VIN_SM2) < 4.7 V, TPS65820 900 1050 1200 mA

Oscillator frequency PWM mode set 1.3 1.5 1.7 MHz

Efficiency 90%

Soft start ramp time 750 µ s

Converter turn-on delay GPIO2 pin programmed as SM2 converter enable 170 µ s

Q(SM2)

SM2 OFF, set via I2C 0.1

Output voltage, selectable via I2C, standby OFF

V

= V

O(SM2)

ON V to 3.4 V, adjustable in

Total accuracy, V

V(VIN_SM2) = greater of [3 V or (V

to 4.7 V; 0 mA ≤ I

, output voltage range, standby voltages: V

SBY(SM2)

O(SM2)TYP

O(SM2)

Line regulation, V(VIN_SM2) = greater of %/V

[3 V or (V

to 4.7 V; 0 mA ≤ I

+ 0.3 V)] 0.027

O(SM2)

O(SM2)

Load regulation, V(VIN_SM2) = 4.7 V,

I

: 60 mA → 540 mA

O(SM2)

V(VIN_SM2) = 3.6 V, 100% duty cycle set 310 500 m Ω

V(VIN_SM2) = 3.6 V, 0% duty cycle set 220 330 m Ω

V(VIN_SM2) = 4.2 V, I

V

= 3 V

O(SM2)

Converter OFF → ON, V

value

control. Measured from V(GPIO2): LO → HI

O(SM2)

≤ 600 mA

≤ 600 mA

O(SM2)

O(SM1)

= V

SM2(SBY)

= 300 mA,

: 5% → 95% of target

O(SM2)

www.ti.com

= 1.24 V, application circuit as in Figure 3

Not 10

switching

Available output

voltages: V

1 V to 3.4 V, adjustable

in 80 mV steps

Available output

80 mV steps

= 1.8 V,

+ 0.3 V)] – 3% 3%

O(SM2)TYP

SBY(SM2)

0.139 %/A

=

= 1

V

ELECTRICAL CHARACTERISTICS – GPIOs

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

GPIO1 – 3

V

OL

I

OGPIO

V

IL

I

LKG(GPIO)

14 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Low level output voltage GPIO0 IOL= 20 mA 0.5 V

Low level sink current into GPIO1, 2, 3 V(GPIOn) = V(OUT) 20 mA

Low level input voltage 0.4 V

Input leakage current V(GPIOn) = V(OUT) 1 µ A

Product Folder Link(s): TPS65820

V(OUT)* 1.2

500 kW

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

ELECTRICAL CHARACTERISTICS – ADC

Over recommended operating conditions (typical values at TJ= 25 ° C), V(ADC_REF) =2.535v if external reference voltage is

used,application circuit as in Figure 3 (unless otherwise noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

ANALOG INPUTS

V

RNG(CH1_5)

V

RNG(CH6_8)

C

IN(ADC)

R

INADC(CH1_5)

I

LKGADC(CH1_5)

R

INADC(CH6_8)

I

LKGADC(CH6_8)

V

CH5(ADC)

DC ACCURACY

RES

(ADC)

MCD

(ADC)

INL

(ADC)

DNL

(ADC)

OFF

ZERO(ADC)

OFF

CH(ADC)

GAIN

ADC

GAIN

CH(ADC)

THROUGHPUT SPEED

ADC

CLK

ADC

TCONV

REFERENCE VOLTAGES

V

INTREF

I

SHRT(INTREF)

V

REF(DRIFT)

I

Q(ADC)

I

(ANLG2)

Full scale input range Ch1 to V(ADC

Ch5 _REF)

Full scale input range Ch6 to V

Ch8 × 1.854

Input capacitance (all

channels)

Positive inputs (active clamp), full scale ~ 2.535 V 0 V

Positive inputs (active clamp), full scale ~4.7 V 0 V

INTREF

15 pF

Input resistance (Ch1 to Ch5) 1 M Ω

Leakage current (Ch1 to Ch5) 100 nA

Input resistance (Ch6 to Ch8) 430 540 k Ω

Leakage current (Ch6 to Ch8) 10 µ A

Internal voltage proportional to

junction temperature

TJ= 25 ° C, ADC channel 5 input voltage 1.895 V

Temperature coefficient 6.5 mV/ ° C

Resolution SAR ADC 10 Bits

No missing codes SPECIFIED

Integral linearity error ± 3 LSB

Differential non-linearity error ± 1 LSB

Offset error 5 LSB

Offset error match between

channels

Gain error ± 8 LSB

Difference between the first code transition

(00...00 to 00...01) from the ideal AGND + 1 LSB

5 LSB

Deviation in code from the ideal full scale code

(11 … 111) for the full scale voltage

Gain error match Any two channels 2 LSB

Sampling clock 600 750 900 kHz

Conversion time 44 59 68 µ s

Internal ADC reference voltage 2.53 2.535 2.54 V

Internal reference short-circuit V(ADC_REF) = AGND1, internal reference

limit enabled via I2C

ADC internal reference

temperature drift

ADC Internal reference Measured at OUT pin (internal reference) or

quiescent current ADC_REF pin (external reference)

Sampling, convertion and setting Rs ≤ 200 K for

CH1, CH2, CH3; Rs ≤ 500 Ω for CH6, CH7, CH8

TA= 25 ° C, V(ADC_REF) = V

ADC reference is selected

when internal

INTREF

6 mA

50 100 ppm/ ° C

40 µ A

00 0

ANLG2 pin internal pullup

current source

ADC channel 2 bias current, set via

I2C register ADC_WAIT bits µ A

(ADC_CH2I_D1_1, ADC_CH2I _D2)

01 10

10 50

11 60

Total accuracy, relative to selected value – 25% 25%

00 µ A

ADC channel 1 bias current, set via

I

(ANLG1)

ANLG1 pin internal pullup

current source

I2C register ADC_WAIT bits

(BATIDI_D1, BATIDI _D2)

01 10

10 50

11 60

Total accuracy 10% 10%

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 15

Product Folder Link(s): TPS65820

I

O(SM3)

+

V(SM3REF)

R

FB3

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

www.ti.com

ELECTRICAL CHARACTERISTICS – ADC (continued)

Over recommended operating conditions (typical values at TJ= 25 ° C), V(ADC_REF) =2.535v if external reference voltage is

used,application circuit as in Figure 3 (unless otherwise noted).

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

INTERNAL REFERENCE POWER CONSUMPTION

PD

ACTIVE

PD

ARMED

TRIGGER TIMING CHARACTERISTICS

t

DELAY(TRG)

t

WAIT(TRG)

Power dissipation Conversion active 2.3 mW

Power dissipation Not converting 0.43 mW

Trigger delay time accuracy Time range, set via I2C register ADC_DELAY 0 750 uS

Relative to typical value set via I2C – 20% 20%

Trigger wait time accuracy Time range, set via I2C register ADC_WAIT 0 20.48 mS

Relative to typical value set via I2C – 20% 20%

ELECTRICAL CHARACTERISTICS – LED AND PWM DRIVERS

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SM3 BOOST CONVERTER, WHITE LED CONSTANT CURRENT DRIVER

V

VIN(SM3)

V

OVP3

V

HYS(OVP3)

V

SM3REF

Input Voltage range V(OUT) = 3.3 V 3 4.7 V

Output overvoltage trip OVP detected at V(SM3) > V

Output overvoltage hysteresis OVP not detected at V(SM3) < V

LED current sense threshold 244 252 260 mV

LED current below regulation point at

V(FB3) < V

SM3REF

OVP3

– V

OVP3

HYS(OVP3)

26.5 29 30 V

1.8 V

I

O(SM3)

D

SM3SW

F

REP_SM3

R

DSON(SM3SW

)

I

LKG(SM3SW)

R

DSON(L3)

I

LKG(L3)

I

MAX(L3)

LED current

LED switch duty cycle Duty cycle range via I2C, 256 steps 0.4%

LED switch duty cycle pattern 256 pulses within repetition

repetition rate rate time

LED switch MOSFET

on-resistance

LED switch MOSFET leakage 1 µ A

Power stage MOSFET

on-resistance

Power stage MOSFET leakage 1 µ A

Power stage MOSFET current

limit

PWM DRIVER, PWM OPEN DRAIN OUTPUT

V

OL(PWM)

F

PWM

D

PWM

Low level output voltage I(PWM)= 150 mA 0.5 V

PWM driver frequency

PWM driver duty cycle Duty cycle range set via I2C,

LED_PWM DRIVER, LED_PWM OPEN DRAIN OUTPUT

D

LEDPWM

F

REP(LEDPWM)

LED_PWM driver duty cycle Duty cycle range set via I2C, 256 steps

LED_PWM driver duty cycle 256 pulses within repetition

pattern repetition rate rate time

Current range, Vin = 3.3 V,

Total accuracy, I

O(SM3)

= 10 mA – 10% 10%

0 25 mA

D

SM3SW

= 0% to 99.6%, set

minimum step

SM3_LF_OSC = 0 122

SM3_LF_OSC = 1 183

V(OUT) = 3.6 V; I(SM3SW) = 20 mA 1 2 Ω

V(OUT) = 3.6 V; I(L3) = 200 mA 300 600 m Ω

3 V < V(OUT) < 4.7 V 400 500 600 mA

Frequency range Hz

Set via I2C, F

0.5/1/1.5/2/3/4.5/7.8/15.6

=

PWM

Total accuracy, relative to selected value -20% 20%

D

= 6.25% to 100%,

PWM

6.25% minimum step

D

= 0% to 99.6%,

LEDPWM

0.4% minimum step

SM3_LF_OSC = 0 122

SM3_LF_OSC = 1 180

Hz

Hz

16 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

SYS_IN

L1

SM1

PGND1

PGND2

SM2

L2

AGND0

SM3

FB3

L3

SM3SW

OUT

SIM

OUT

GPIO1

USB

GPIO2

LDO_PM

PWM

AC

RED

BA T

GREEN

BA T

BLUE

TMR

SCLK

ISET1

SDA T

DPPM

INT

TS

RESPWRON

R TC_OUT

TRSTPWON

HOT_RST

LDO1

LDO0

LDO3

LDO35_REF

VIN_LDO35

LDO4

ADC_REF

AGND2

ANLG1

ANLG2

LDO5

GPIO3

GROUNDPAD

AGND1

VIN_LDO02

PGND3

VIN_SM2

VIN_SM1

2

11

8

13

10

12

9

6

7

5

3

4

14

38

41

36

39

37

40

42

34

35

33

32

31

30

27

29

25 282624232219 21201817

LED_PWM

LDO2

48 47 434446 4549505154 5256 5355

1

1615

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

ELECTRICAL CHARACTERISTICS – LED AND PWM DRIVERS (continued)

Over recommended operating conditions (typical values at TJ= 25 ° C), application circuit as in Figure 3 (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

OL(LEDPWM)

V

OH(LEDPWM)

RGB DRIVER, RED/GREEN/BLUE OPEN DRAIN OUTPUTS

t

FLASH(RGB)

t

FLASH(ON)

D

RGB

I

SINK(RGB)

V

OL(RGB)

I

LKG(RGB)

Low level output voltage I(LED_PWM) = 150 mA 0.5 V

High level output voltage 6 V

t

FLASH(RGB)

step, 8 steps

Flashing period

Flashing period range via I2C, 0.5 s minimum s

Total accuracy -20% 20%

Set via I2C, t

Flash on time

Flash on time range, value selectable by I2C 0.1/0.15/0.2/0.25/0.3/0.4/ s

Total accuracy, relative to selected value -20% 20%

D

= 0% to 99.98%, set

Duty cycle Duty cycle range, value selectable via I2C via I2C, 3.23% minimum

RGB

00 (Driver set to OFF)

RGB output sink current V(BLUE) = 2 V, set via I2C mA

V(RED) = V(GREEN) =

RGB_ISET1,0

01 2.4 4 5.6

10 4.8 8 11.2

11 7 12 16.6

Low-level output voltage 0.3 V

Output off leakage current 1 µ A

Output low voltage, 8-mA load, RED/GREEN/BLUE

PINS

V(RED)=V(GREEN)=V(BLUE) = 4.7 V, all drivers

disabled

= 1 to 8 s, set

0.5/0.6 s

step

FLASH(ON)

=

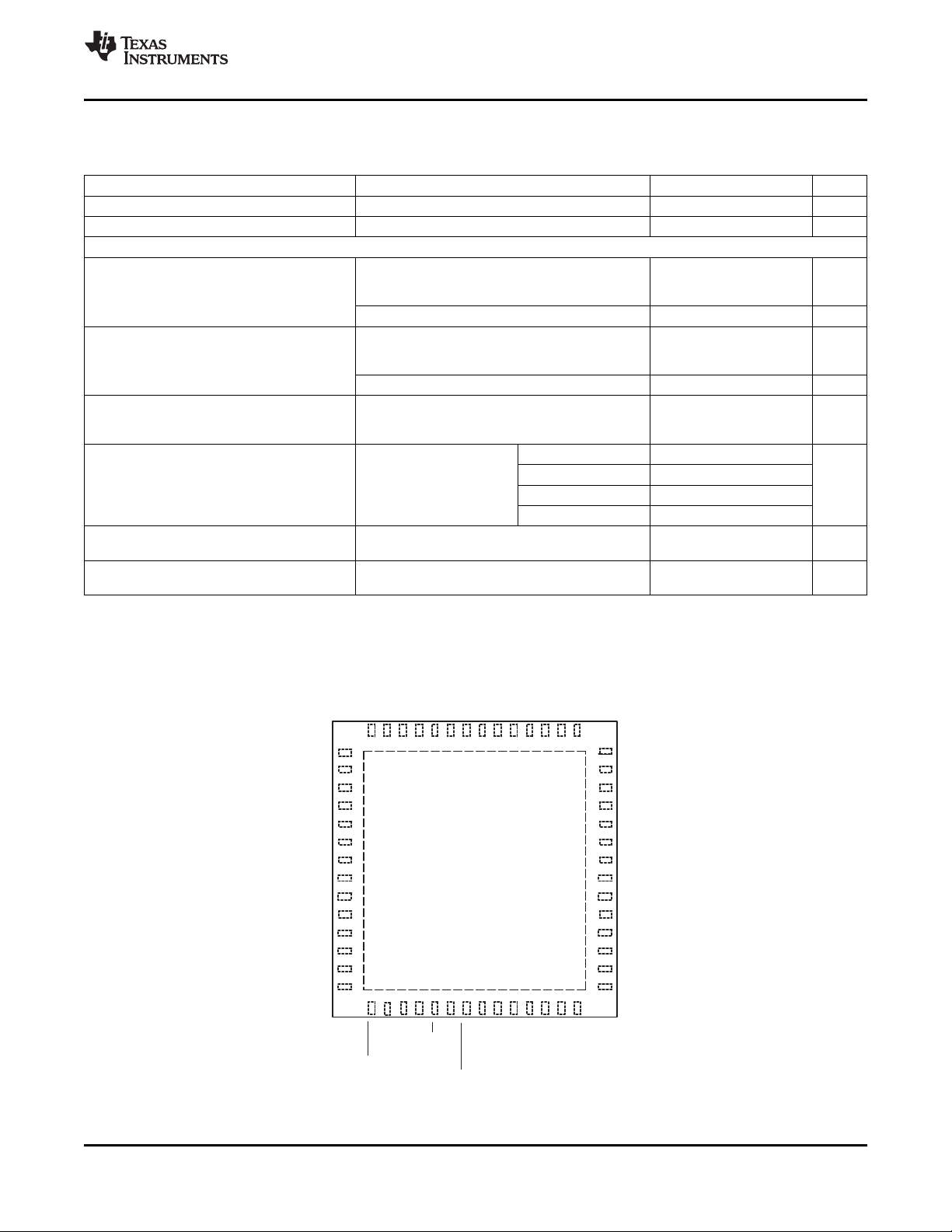

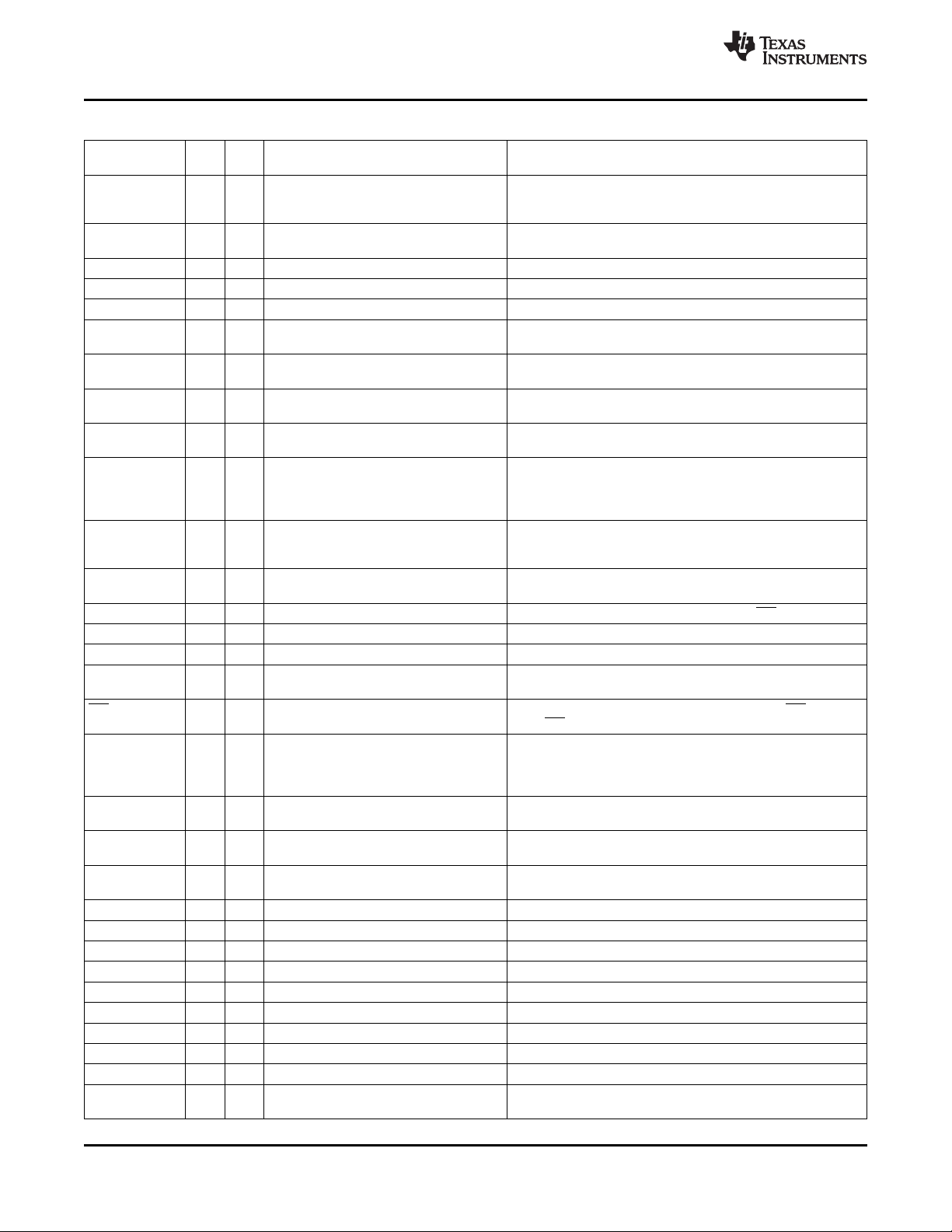

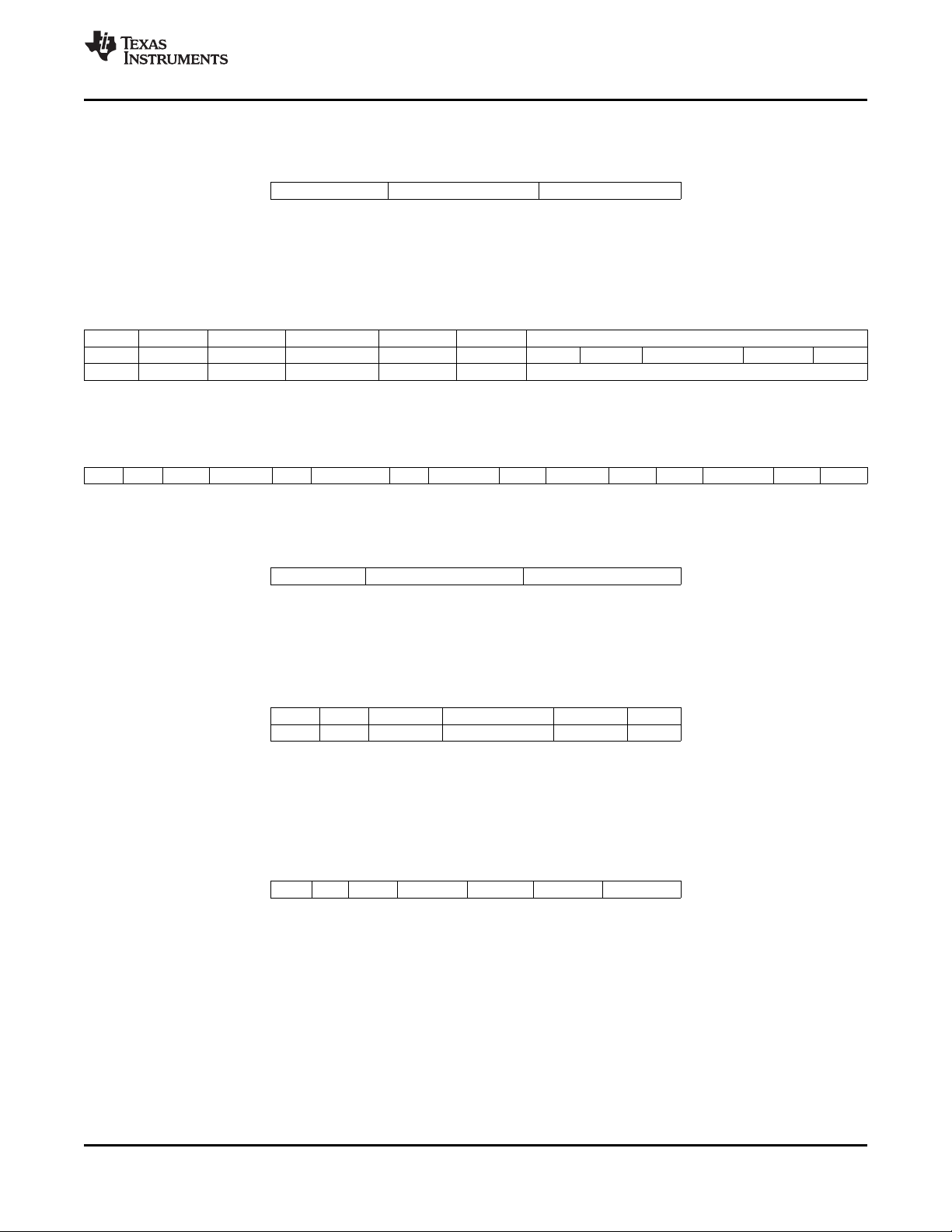

PIN ASSIGNMENT

Product Folder Link(s): TPS65820

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 17

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

www.ti.com

PIN DESCRIPTION, REQUIRED EXTERNAL COMPONENTS

NAME PIN I/O DESCRIPTION EXTERNAL REQUIRED COMPONENTS

AC 7 I Adapter charge input voltage, connect to 1- µ F (minimum) capacitor to AGND1 pin to minimize

AC_DC adapter positive output terminal overvoltage transients during AC power hot-plug events.

(dc voltage)

ADC_REF 22 I/O ADC internal reference filter or ADC 4.7- µ F (minimum) to 10- µ F (maximum) capacitor connected to

external reference input AGND2 pin

AGND0 16 – Analog ground connection Connect to analog ground plane

AGND1 48 Analog ground pin Connect to analog ground plane

AGND2 25 Analog ground pin Connect to analog ground plane

ANLG1 24 I Analog input to ADC, programmable Can be used to monitor additional system or pack parameters

current source output

ANLG2 23 I Analog input to ADC, programmable Can be used to monitor additional system or pack parameters

current source output

BAT 17, I/O Battery power Connect to battery positive terminal. Connect 10- µ F capacitor

18 (minimum) from BAT pin to AGND1 pin

BLUE 1 O Programmable blue driver, open drain Connect to BLUE input of RGB LED

output, current sink output when active.

DPPM 14 I Dynamic power path management External resistor from DPPM pin to AGND1 pin sets the DPPM

set-point regulation threshold. 1 nF (minimum) capacitor to from DPPM

to AGND1 sets BAT to OUT short-circuit blanking delay when

battery is hot-plugged into system

FB3 41 I/O White LED duty cycle switch output, LED External resistor from FB3 pin to PGND3 pin sets LED peak

current setting current. Connect 100-pF (minimum) filter capacitor to PGND3

pin.

HOT_RST 15 I/O Hardware reset input, reset generated Connect to an external push-button switch

when connected to ground

GPIO1 43 I/O General purpose programmable I/O Example: External interrupt request to host ( INT: HI → LO)

GPIO2 53 I/O General purpose programmable I/O example: Set SM1 and SM2 converters in standby mode

GPIO3 54 I/O General purpose programmable I/O Example: ADC conversion start trigger

GREEN 56 O Programmable LED driver, open-drain Connect to GREEN input of RGB LED

output, current sink output when active

INT 19 O Interruption pin, open-drain output Connect 100-k Ω external pullup resistor between INT and

OUT. INT pin is LO when interrupt is requested by TPS65820.

ISET1 11 I Current set point when charging in auto External resistor from ISET1 pin to AGND1 pin sets charge

mode with AC selected. Precharge and current value

charge termination set point for all charge

modes

L1 46 O SM1 synchronous buck converter power 3.3- µ H inductor to SM1 pin

stage output

L2 51 O SM2 synchronous buck converter power 3.3- µ H inductor to SM2 pin

stage output

L3 39 O Drain of the integrated boost power stage 4.7- µ H inductor to OUT pin, external Schottky diode to SM3 pin

switch

LDO_PM 10 O General-purpose LDO output 1- µ F (minimum) capacitor to AGND1 pin

LDO0 32 O LDO0 output, fixed voltage 1- µ F (minimum) capacitor to AGND1

LDO1 37 O LDO1 output 1- µ F (minimum) capacitor to AGND1

LDO2 33 O LDO2 output 1- µ F (minimum) capacitor to AGND1

LDO3 28 O LDO3 output 2.2- µ F (minimum) capacitor to AGND2

LDO35_REF 30 I Linear regulators LDO3 – 5 reference filter 100-nF capacitor to AGND2

LDO4 27 O LDO4 output 2.2- µ F (minimum) capacitor to AGND2

LDO5 26 O LDO5 output 2.2- µ F (minimum) capacitor to AGND2

LED_PWM 36 O PWM driver output, open-drain Can be used to drive a keyboard backlight LED

OUT 8, 9 O Power path output. Connect to system 10- µ F capacitor to AGND1 pin

main power rail (system power bus)

(SEE APPLICATION DIAGRAM)

18 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

TPS65820

www.ti.com

PGND1 45 – SM1 synchronous buck converter power Connect to power ground plane

PGND2 52 – SM1 synchronous buck converter power Connect to power ground plane

PGND3 38 – White LED driver power ground input Connect to a power ground plane

PWM 34 O PWM driver output, open-drain Can be used to drive a vibrator or other external functions

RED 55 O Programmable LED driver, open drain Connect to RED input of RGB LED

RESPWRON 21 O System reset, open-drain output 100-k Ω external pullup resistor to OUT. RESPWRON pin is LO

RTC_OUT 4 O Low-leakage LDO output. Can be 1- µ F (minimum) capacitor to AGND1 pin or supercap

SCLK 2 I I2C interface clock line 2-k Ω pullup resistor to OUT pin

SDAT 3 I/O I2C interface data line 2-k Ω pullup resistor to OUT pin

SIM 5 O General-purpose LDO output 1- µ F (minimum) capacitor to AGND1 pin

SM1 44 I SM1 synchronous buck converter output LC filter: 10- µ F capacitor to PGND1 pin

SM2 49 I SM2 synchronous buck converter output LC filter: 10- µ F capacitor to PGND2 pin

SM3 42 I White LED driver output overvoltage Connect 1- µ F capacitor to PGND3 pin. Connect SM3 pin to the

SM3SW 40 I Integrated white LED duty cycle switch Connect to negative side of external LED ladder

SYS_IN 31 I System power bus low-voltage detection External resistive divider sets minimum system operational

TMR 13 I Charge safety timer program input External resistor from TMR pin to AGND1 pin sets the charge

TRSTPWON 20 I System reset pulse duration setting 100-nF (minimum) capacitor to AGND1. External capacitor

TS 12 I/O Temperature sense input, current source Connect to battery pack thermistor to sense battery pack

USB 6 I USB charge input voltage, connect to 1- µ F (minimum) capacitor to AGND1 pin, to minimize

VIN_LDO35 29 – Input to LDOs 3 to 5 1- µ F (minimum) decoupling capacitor to AGND2

VIN_LDO02 35 – Positive supply input for LDO0, LDO1, 1- µ F (minimum) decoupling capacitor to AGND1

VIN_SM1 47 – SM1 synchronous buck converter positive 10- µ F capacitor to PGND1 pin

VIN_SM2 50 – SM2 synchronous buck converter positive 10- µ F capacitor to PGND2 pin

Exposed 57 – There is an internal electrical connection between the exposed thermal pad and AGNDn pins of the IC. The

thermal pad exposed thermal pad must be connected to the same potential as the AGND1 pin on the printed circuit

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

NAME PIN I/O DESCRIPTION EXTERNAL REQUIRED COMPONENTS

(SEE APPLICATION DIAGRAM)

ground

ground

output, current sink output when active.

when TPS65820 is resetting the system.

connected to a super-capacitor or

secondary cell, if used as a RTC backup

output.

voltage sense

voltage sense

detection positive side of white LED ladder.

input

voltage. TPS65820 enters sleep mode when voltage below

minimum system voltage threshold is detected. 1-nF filter

capacitor to AGND1 recommended.

safety timer time-out value

from TRSTPWON pin to AGND1 pin sets RESPWRON pulse

width.

output temperature

USB port positive power output overvoltage transients during USB power hot-plug events.

LDO2

supply input

supply input

board. Do not use the thermal pad as the primary ground input for the IC. AGNDn pins must be connected

to a clean ground plane at all times.

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 19

Product Folder Link(s): TPS65820

SM1

AC

BAT

OUT

USB

TMR

DPPM

TS

HOT_RST

L1

SM2

L2

L3

SM3

SM3SW

BAT

OUT

7

Battery

PGND1

PGND2

PGND3

FB3

VIN_SM2

VIN_SM1

PWM

LED_PWM

RED

BLUE

GREEN

AGND1

VIN_LDO02

LDO1

LDO0

LDO2

TRSTPWON

SYS_IN

TPS65820

INT

SDAT

SCLK

RESPWRON

AGND2

EXTERNAL HOST

GPIO2

GPIO1

ANLG1

GPIO3

ANLG2

ADC_REF

VIN_LDO35

LDO35_REF

LDO4

LDO3

LDO5

1uF

2.2uF

A1

0.1uF

1nF

210K

100K

AC_DC

ADAPTER

OUTPUT

USB

POWER

GND

GND

+

-

2K

100K

100K

A2

A1

VLDO2

VLDO1

VLDO0

VLDO5

VLDO4

VLDO3

P3

P2

VSM2

VSM1

P1

A1

GND

49.9K

37.4K

100pF

GND

A1 A2 A3

P1 P2

P3

SIM

RTC_OUT

AGND0

A0

VRTC_OUT

ISET1

1K

Supercap

LDO_PM

V

LDO_PM

V

SIM

2K

37

32

35

10

4

5

6

50

45

44

46

47

14

13

12

18

17

11

9

8

48

33

39

40

52

49

51

2

16

31

20

15

25

26

27

28

30

29

42

21

19

3

56

55

36

34

41

38

53

43

1

24

23

54

22

A2

+

-

2.2uF

2.2uF

1uF

4.7uF

4.7uF

4.7uF

0.1uF

1uF

10uF

10uF

2.2uF

1uF

100pF

4.7uH

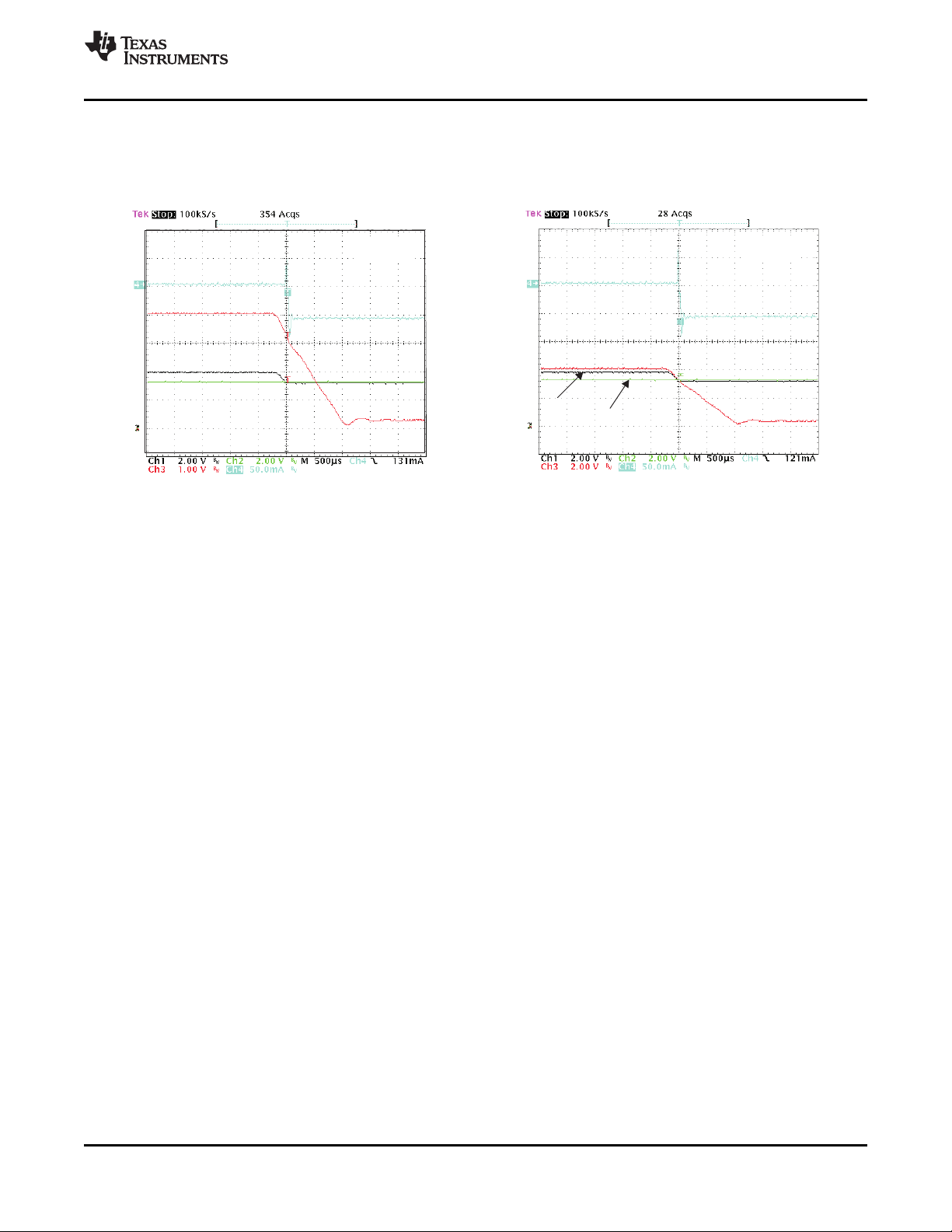

10uF

10uF

10uF

3.3uH

3.3uH

47nF

10uF

22uF

0.22uF

4.7uF

SYSTEM

POWER

BUS

ADC

EXTERNAL

ANALOG

INPUTS

I2C

CONFIGURABLE

GPIO’S

CLOCK

DATA

ALARM

RESET

10

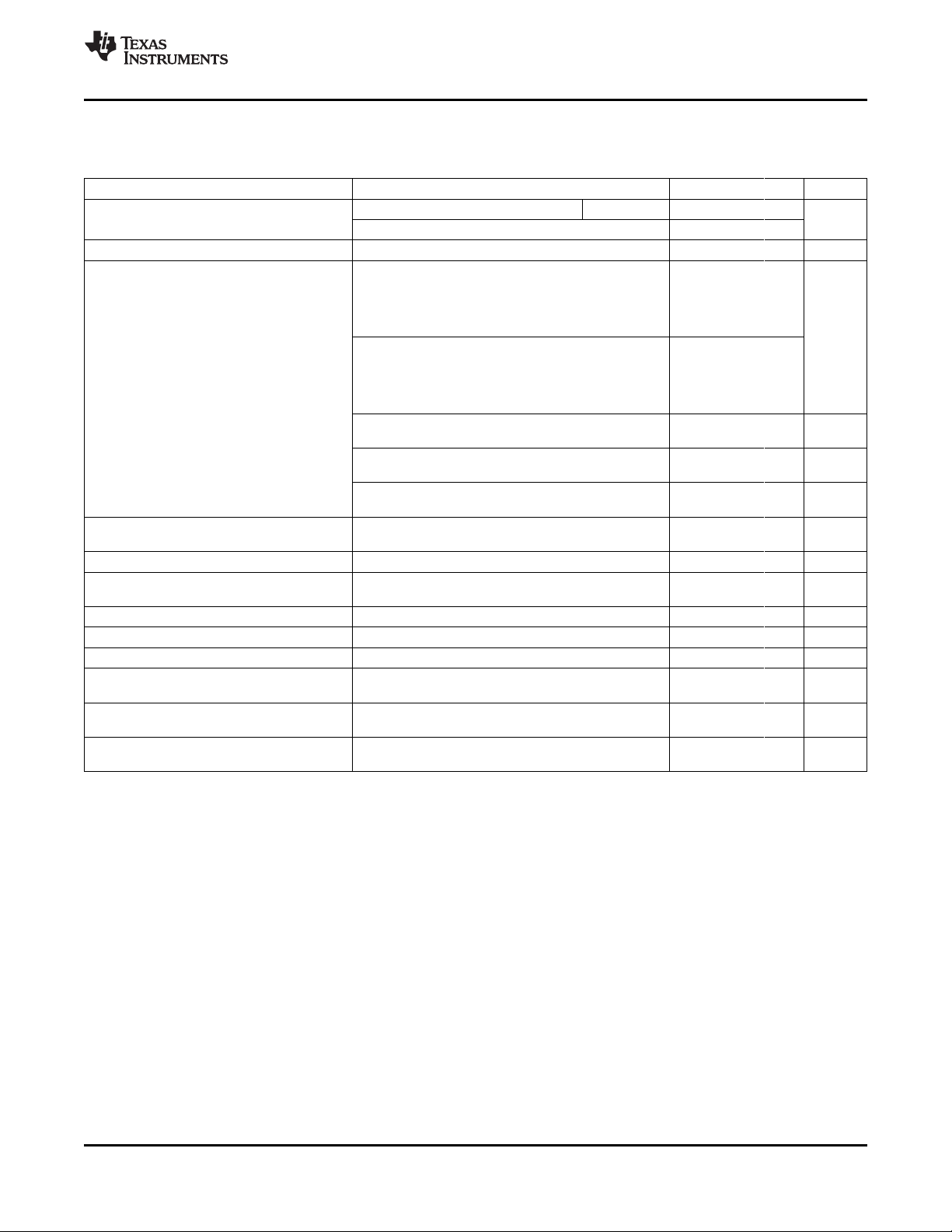

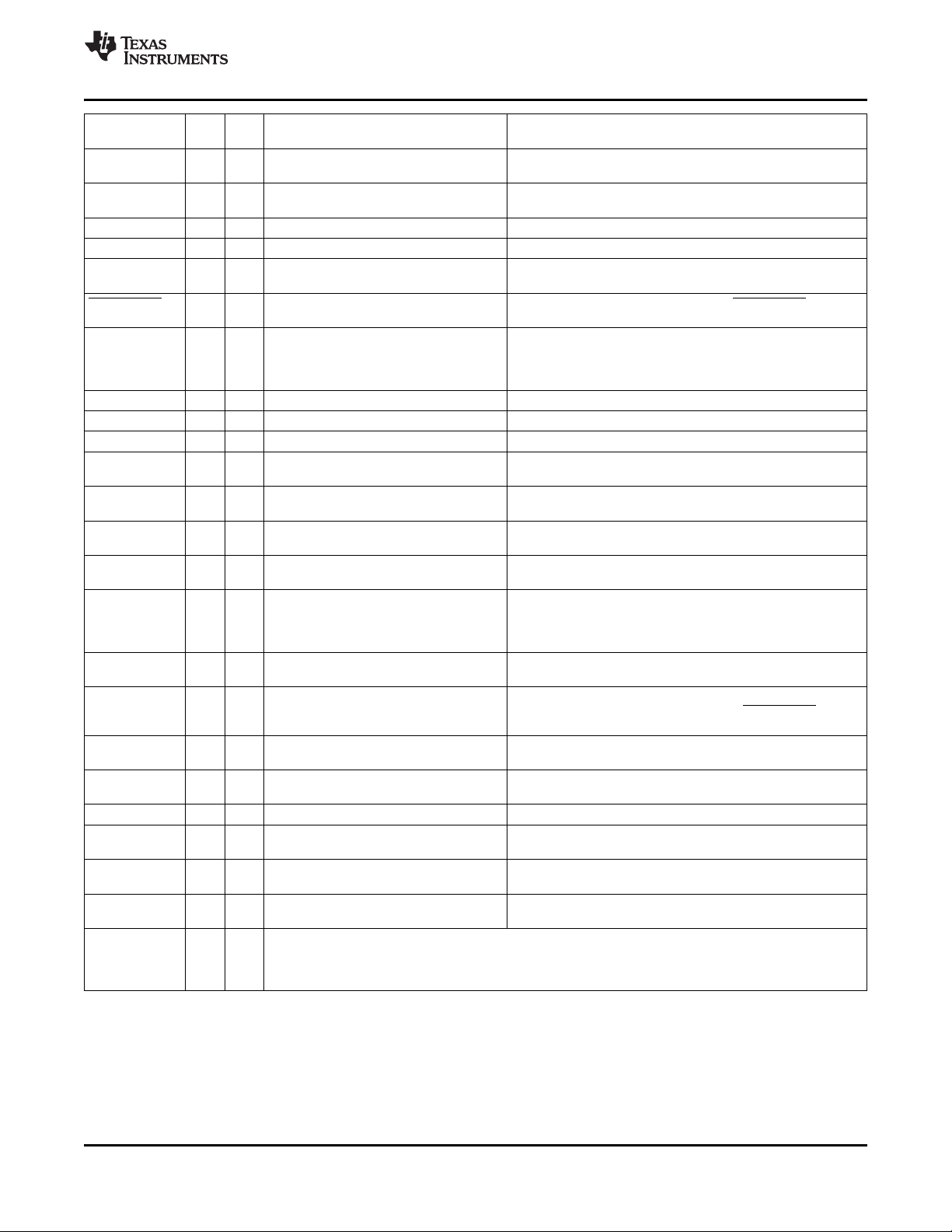

NOTES:

1) RESISTORVALUESINOHMS

2) THEFOLLOWINGPARAMETERS AREPROGRAMMED:

- R

TMR

=49.9K: 6 HOURCHARGESAFETY TIMER,

30 MINPRE-CHARGESAFETY TIMER

- R

SET

=1K: 1A CHARGECURRENT (NOSCALING, INPUTLIMIT=2 .5A),

100mA TERMINATION ANDPRE -CHARGECURRENTS

- R

FB3

=10 OHMS: 25mA WHITELEDCURRENT

- C

TRSTPWON

=100nF : 100mSECRESETPULSEWIDTH

- R

DPPM

=37.4K: V

(DPPM)

=4.3V

3) THECAPACITORVALUESSHOWNINTHE APPLICATIONDIAGRAM

MAY BELARGERTHANTHEMINIMUMREQUIREDVALUESINDICATED

INTHEPINDESCRIPITONTABLE

4) THEVALUESSHOWNINTHE APPLICATIONDIAGRAMMATCHTHE

COMPONENTVALUESUSEDINTHEHPA 129 EVM, SEEDESIGNNOTES

SECTIONFORCOMPONENTSELECTIONDETAILS

VOUT

VOUT

VOUT

VOUT

VOUT

EXTERNAL

PERIPHERALS

VOUT

WHITELEDS

VOUT

VOUT

57

PWRGND

A1

R

SET

R

TMR

R

DPPM

C

TRSTPWON

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C28

1uF

C21

C22

C23

C24

C25

C26

R1

R2

R3

R4

R5

R6

R

FB3

LSM1

LSM2

LSM3

C27

D1

RGBLED

P3

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

APPLICATION DIAGRAM

Figure 3. TPS65820 Application Diagram, Recommended External Components

20 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

www.ti.com

I

BAT

V

USB

V

OUT

V

BAT

USB=5V,

BAT =3.3V

I

BAT

V

AC

V

OUT

V

BAT

AC=5V,

BAT =3.3V

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

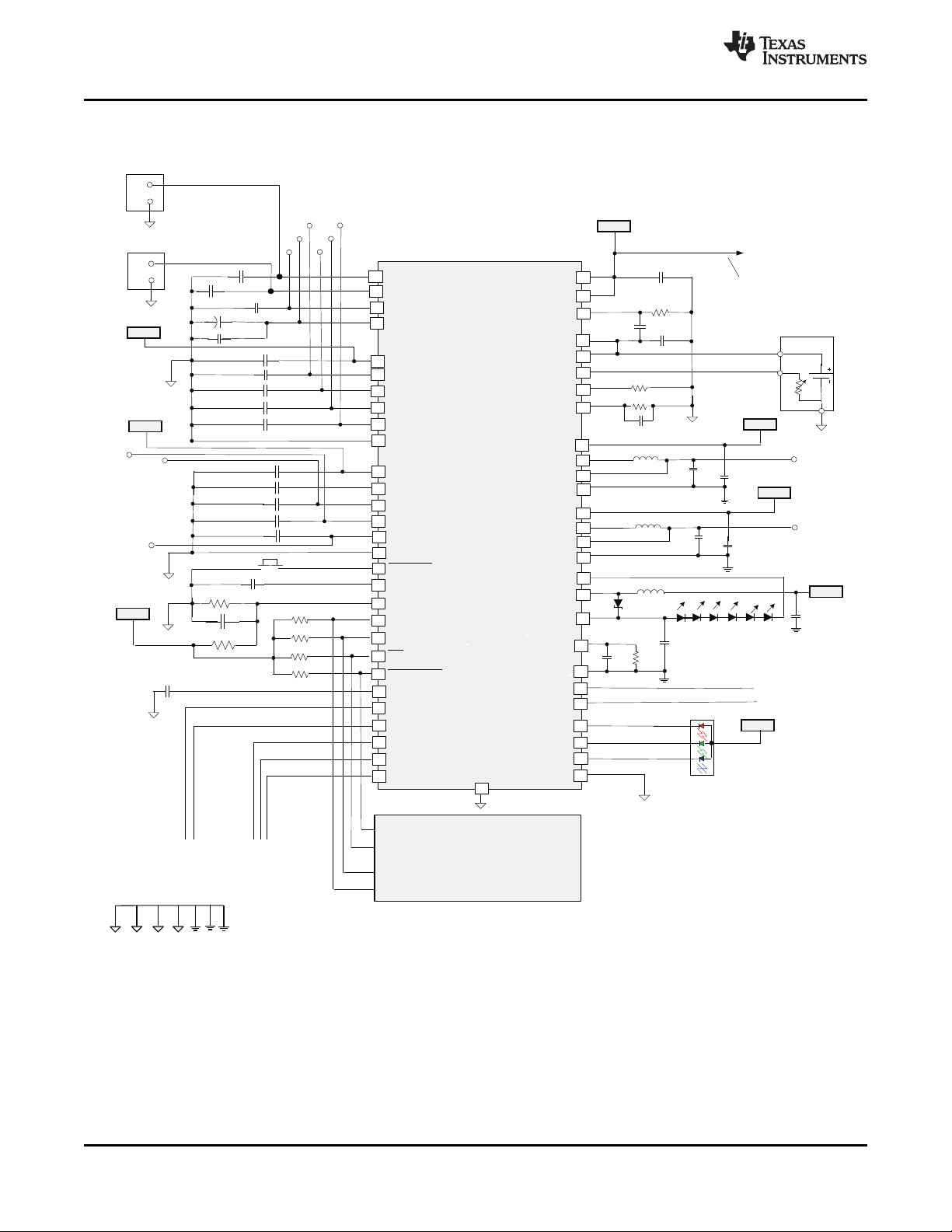

TYPICAL CHARACTERISTICS – POWER PATH MANAGEMENT

Measured with Application Circuit shown in Figure 3 , unless otherwise noted

SWITCHING FROM AC TO BATTERY SWITCHING FROM USB TO BATTERY

ON AC REMOVAL ON AC REMOVAL

Figure 4. Figure 5.

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 21

Product Folder Link(s): TPS65820

0

0.05

0.1

0.15

0.2

0.25

0 20 40 60 80 100 120 140

LineRegulation-%

VIN_LDO02=3.8Vto4.7V,

Load=10mA,

C (LDO02)=1 FOm

T -JunctionTemperature-°C

J

VIN_LDO02=3.65V,

Load=10mA to150mA,

C (LDO02)=1 FOm

-0.850

-0.800

-0.750

-0.700

-0.650

-0.600

-0.550

-0.500

0 20 40 60 80 100 120 140

T -JunctionTemperature-°C

J

LoadRegulation-%

VIN_LDO02=3.3V,

Load=150mA,C =1 F

O(LDO02)

m

70

80

90

100

110

120

130

140

0 20 40 60 80 100 120 140

DropoutVoltage-mV

T -JunctionTemperature-°C

J

VIN_LDO02=3.65V,Load=10mA,

V =3.3V,

O(LDO 0)

V =1.225V

O(LDO 1,2)

1

1.5

2

2.5

3

3.5

0 20 40 60 80 100 120 140

V

-OutputVoltage-V

O

LDO0

LDO1

LDO2

T -JunctionTemperature-°C

J

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

www.ti.com

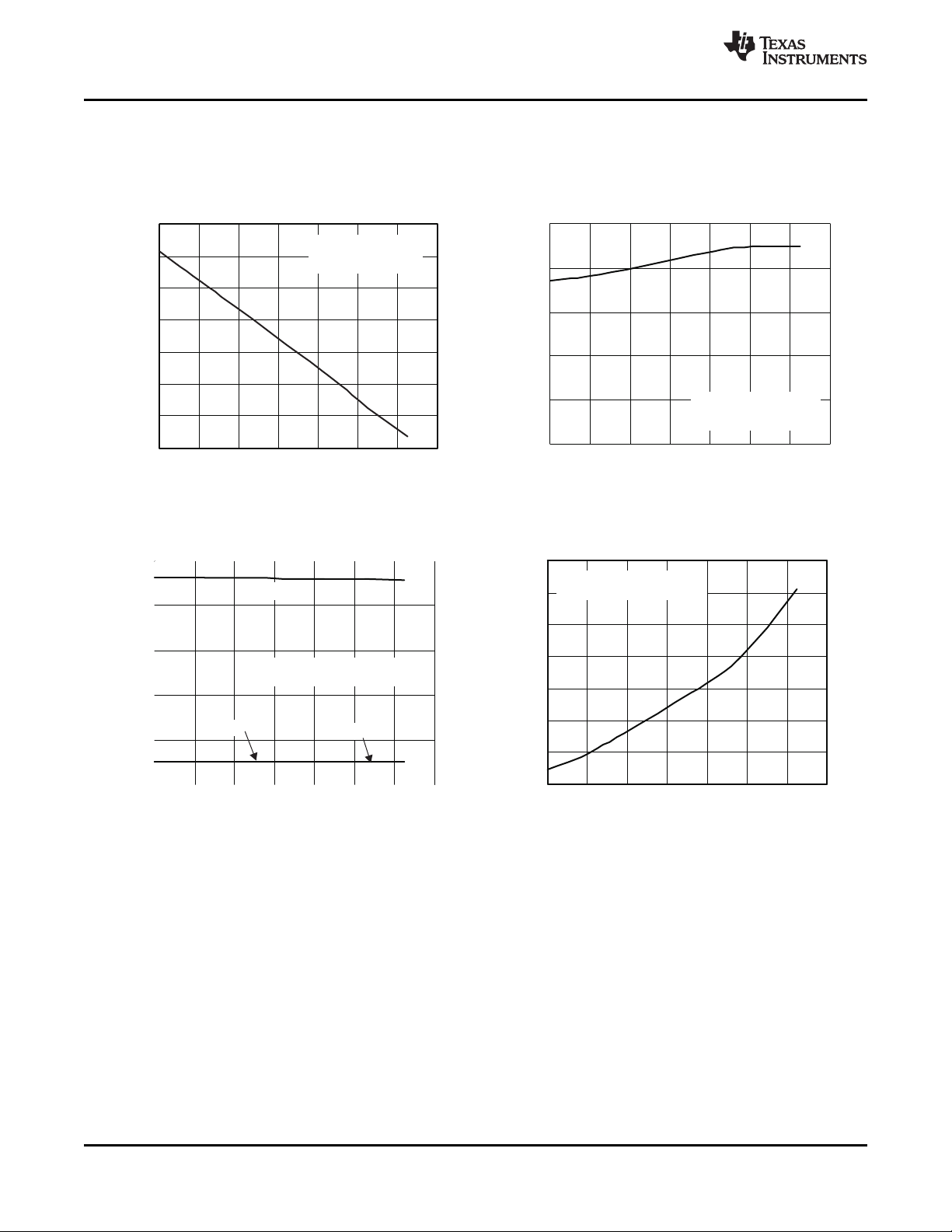

TYPICAL CHARACTERISTICS – LINEAR REGULATORS 0, 1, 2

Measured with Application Circuit shown in Figure 3 , unless otherwise noted

LOAD REGULATION LINE REGULATION

JUNCTION TEMPERATURE JUNCTION TEMPERATURE

OUTPUT VOLTAGE DROPOUT VOLTAGE

JUNCTION TEMPERATURE JUNCTION TEMPERATURE

vs vs

Figure 6. Figure 7.

vs vs

22 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Figure 8. Figure 9.

Product Folder Link(s): TPS65820

VIN_LDO35=3V,

Load=10mA to150mA,

C =1 F

O(LDO 35)

m

-1

-0.95

-0.90

-0.85

-0.80

-0.75

-0.70

-0.65

-0.6

-0.55

-0.5

0 20 40 60 80 100 120 140

LoadRegulation-%

T -JunctionTemperature-°C

J

-0.018

-0.017

-0.016

-0.015

-0.014

-0.013

-0.012

-0.011

-0.010

0 20 40 60 80 100 120 140

LineRegulation-%

VIN_LDO35=3.3Vto4.7V,

Load=100mA,

C (LDO35)=1 FOm

T -JunctionTemperature-°C

J

1.2285

1.229

1.2295

1.23

1.2305

1.231

1.2315

1.232

1.2325

0

20

40 60 80

100 120 140

VIN_LDO35=4.7V,

Load=10mA,

V (LDO35)=1.228V,

C (LDO35)=1 F

O

O

m

T -JunctionTemperature-°C

J

V -OutputVoltage-V

O

90

100

110

120

130

140

0 20 40 60 80 100 120 140

Dropout-mV

VIN_LDO35=3.3V,

Load=150mA,

C (LDO35)=1 FOm

T -JunctionTemperature-°C

J

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

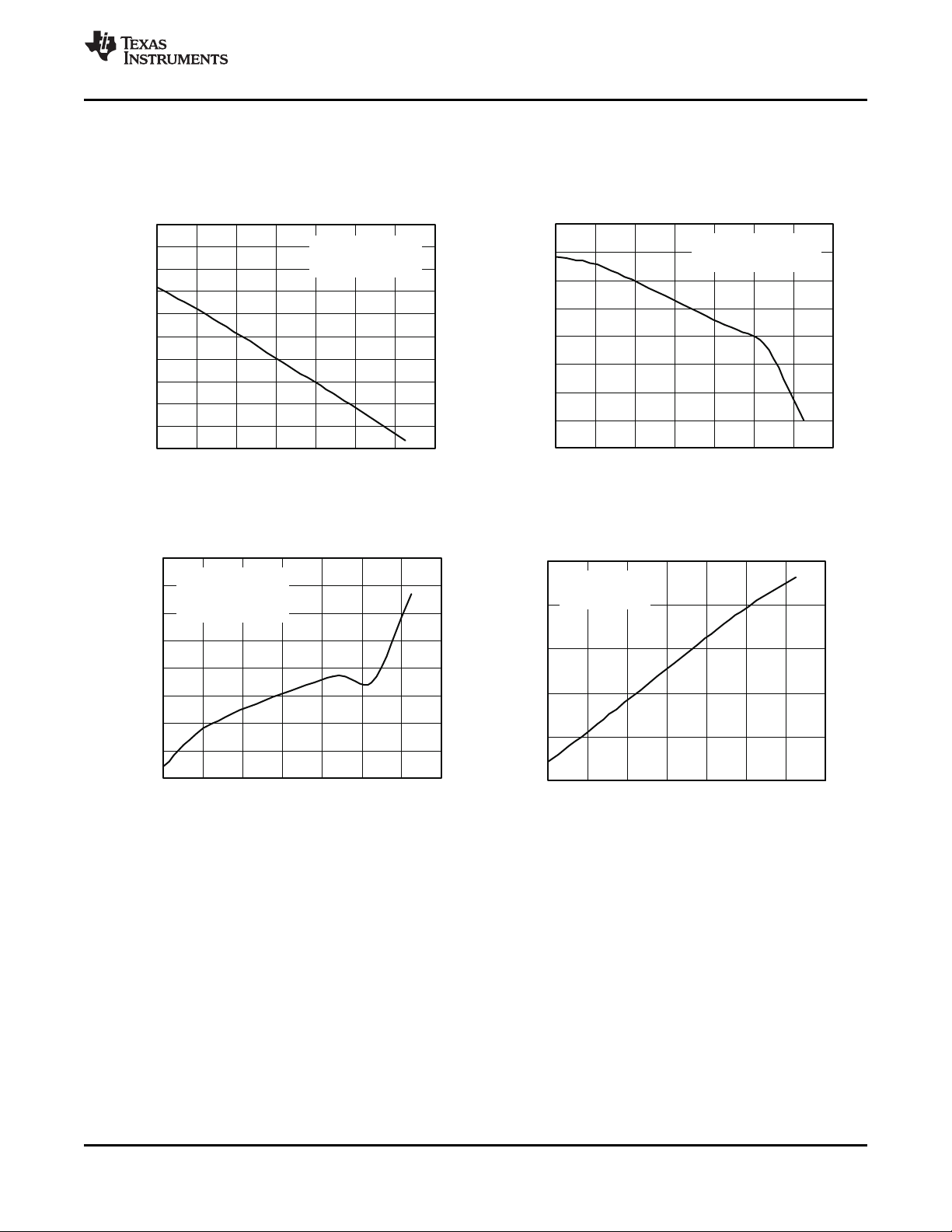

TYPICAL CHARACTERISTICS – LINEAR REGULATORS 3, 4, 5

Measured with Application Circuit shown in Figure 3 , unless otherwise noted

LOAD REGULATION LINE REGULATION

JUNCTION TEMPERATURE JUNCTION TEMPERATURE

OUTPUT VOLTAGE DROPOUT VOLTAGE

JUNCTION TEMPERATURE JUNCTION TEMPERATURE

vs vs

Figure 10. Figure 11.

vs vs

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 23

Figure 12. Figure 13.

Product Folder Link(s): TPS65820

0

10

20

30

40

50

60

70

80

90

100

0 0.1 0.2 0.3 0.4 0.5 0.6

I -OutputCurrent- A

O

Efficiency-%

VIN_SM1=4V,

V (SM1)=1.24V,

L =3.3 H,

C (SM1)=10 F

O

O

m

m

76

78

80

82

84

86

88

90

92

0 0.1 0.2 0.3

0.4

0.5 0.6 0.7

I -OutputCurrent- A

O

Efficiency-%

VIN_SM2=4.6V,

VO(SM2)=1.8V,

L =3.3 H.

C (SM2)=10 FOm

m

AC=5V,

VIN_SM2=4.6V,

V (SM2=1.8V

O

I (SM2)

L =3.3mF,

C (SM2)=10 F

O

O

m

AC=5V,

VIN_SM2=4.6V,

V (SM2=1.8V

O

I (SM2)

L =3.3mF,

C (SM2)=10 F

O

O

m

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

www.ti.com

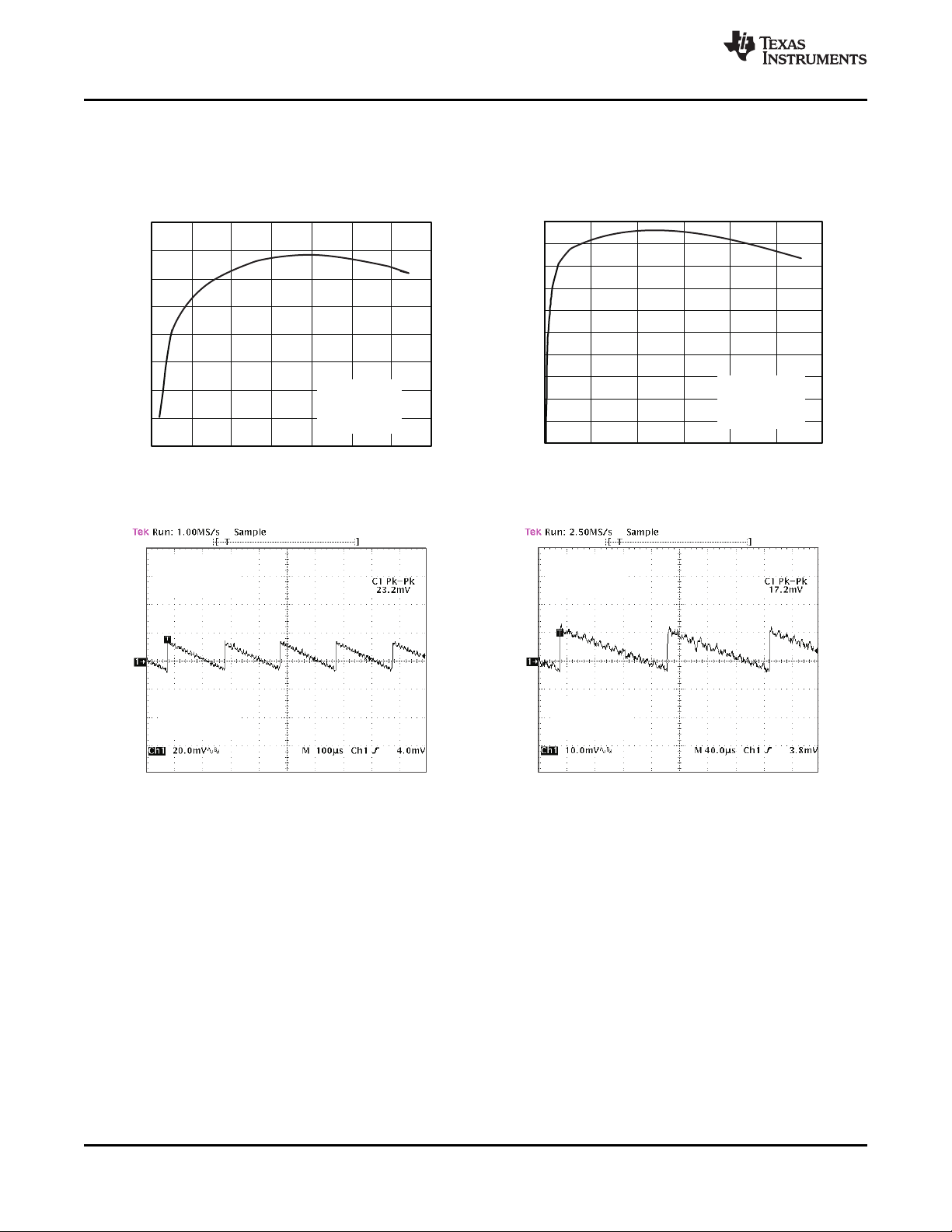

TYPICAL CHARACTERISTICS – SM1 AND SM2 BUCK CONVERTERS

Measured with Application Circuit shown in Figure 3 , unless otherwise noted

EFFICIENCY IN AUTOMATIC EFFICIENCY

PWM/PFM MODE vs OUTPUT CURRENT

Figure 14. Figure 15.

PFM OPERATION PFM LOW RIPPLE OPERATION

PWM MODE

24 Submit Documentation Feedback Copyright © 2006 – 2008, Texas Instruments Incorporated

Figure 16. Figure 17.

Product Folder Link(s): TPS65820

VIN_SM2

VO(SM2)

AC=5V,VIN_SM2=3V(DC)+1V(AC),

V (SM2)=1.8V,I (SM2)=100mA,

L =3.3 F,C (SM1)=10 F,

CH1=VIN_SM2,CH2=V (SM2)

O O

O

O

m m

VO_SM2

I (SM2)

O

AC=5V,

VIN_SM2=4V,

V (SM2)=1.8V,

I (SM2)=0mA to600mA,

L =3.3 F,C (SM1)=10 F,

CH1=VO_SM2,

CH3=I (SM2)

O

O

O

m m

O

SM2Voltage

SM2Current

AC=5V,

VIN_SM2/SM2=4V,

V (SM2)=1.8V,

I (SM2)=600mA,

L =3.3 F,

C (SM1)=10 F

O

O

O

m

m

SM1Voltage

SM1Current

AC=5V,

VIN_SM2/SM2=4V,

V (SM2)=1.8V,

I (SM2)=600mA,

L =3.3 F,

C (SM1)=10 F

O

O

O

m

m

BAT =4V,

DC=0%

L3=4.7 F,

C (SM3)=10 F,

CH1=L3,

CH4=SM3

m

m

O

BAT =4V,DC=0%

L3=4.7 F,C (SM3)=10 F,

CH1=L3,CH4=SM3

m m

O

TPS65820

www.ti.com

.............................................................................................................................................................. SLVS663B – MAY 2006 – REVISED APRIL 2008

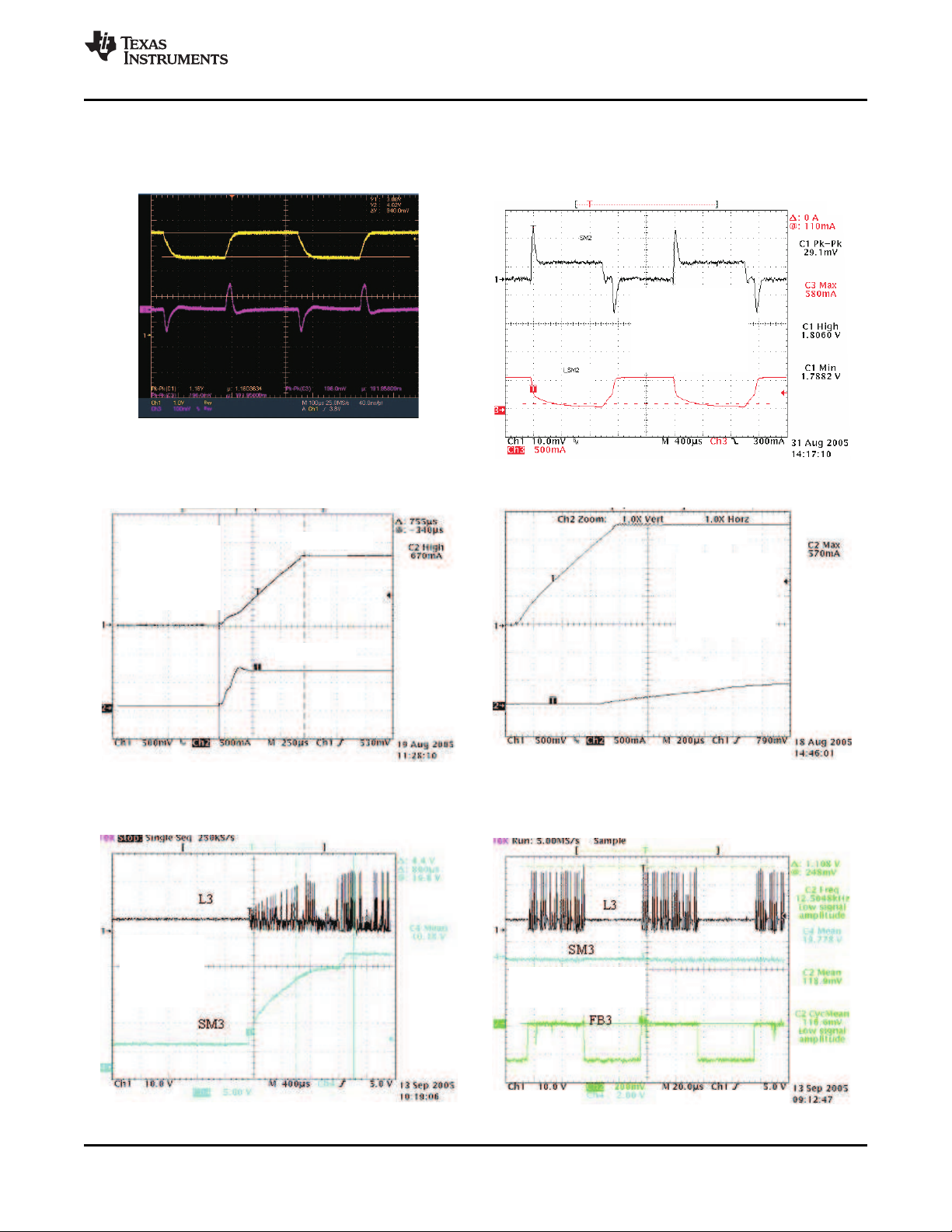

TYPICAL CHARACTERISTICS – DRIVERS

Measured with Application Circuit shown in Figure 3 , unless otherwise noted

LINE TRANSIENT LOAD TRANSIENT

Figure 18. Figure 19.

TRANSIENT - SM1 STARTUP TRANSIENT - SM2 STARTUP

Copyright © 2006 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 25

Figure 20. Figure 21.

SM3 LED CURRENT

SM3 WHITE LED DRIVER vs

SOFT START PWM DUTY CYCLE

Figure 22. Figure 23.

Product Folder Link(s): TPS65820

TPS65820

SLVS663B – MAY 2006 – REVISED APRIL 2008 ..............................................................................................................................................................

www.ti.com

SERIAL INTERFACE

Overview

The TPS65820 is compatible with a host-controlled environment, with internal parameters and status information

accessible via an I2C interface. An I2C communication port provides a simple way for an I2C compatible host to

access system status information and reset fault modes, functioning as a SLAVE port enabling I2C compatible

hosts to WRITE to or to READ from internal registers. The TPS65820 I2C port is a 2-wire bidirectional interface

using SCL (clock) and SDA (data) pins; the SDA pin is open drain and requires an external pullup. The I2C is

designed to operate at SCL frequencies up to 400 kHz. The standard 8 bit command is supported, the CMD part

of the sequence is the 8 bit register address to READ from or to WRITE to.

Register Default Values

The internal TPS65820 registers are loaded during the initial power-up from an internal, non-volatile memory

bank. The power-up default values are described in the sections detailing the registers functionality.

The register contents remain intact as long as OUT pin voltage remains above the internal UVLO threshold,

V

When the OUT pin voltage falls below the VUVLO threshold all register bits are reset to the internal power

UVLO

up default.

I2C Address

The I2C specification contains several global addresses, which the slaves on the bus are required to respond to.

The TPS65820 only responds (ACK) to addresses: 0x90 and 0x91 and does not respond (NACK) to any other

address.

Table 1. TPS65820 I2C Read/Write Address

BYTE BIT

MSB 6 5 4 3 2 1 LSB

TPS65820 I2C WRITE ADDRESS 1 0 0 1 0 0 0 0

TPS65820 I2C READ ADDRESS 1 0 0 1 0 0 0 1

I/O DATA BUS B7 B6 B5 B4 B3 B2 B1 B0

Incremental Read

The TPS65820 does not support incremental read operations. Each register must be accessed in a single read

operation.

I2C Bus Release

The TPS65820 I2C engine does not create START or STOP states on the I2C bus during normal operation.

Sleep Mode Operation

When the sleep mode is set SDAT is held LO by the TPS65820. The overall system operation is not affected, as

in sleep mode all TPS65820 integrated supplies are disabled and no power is available for any external devices

connected to the TPS65820 SDAT pin. When sleep mode ends the SDAT pin is released before the TPS65820

integrated regulated supplies are enabled. See section on System Sequencing and TPS65820 Operating Modes

for additional details on sleep mode operation.

I2C Bus Error Recovery

The I2C bus specification does not define a method to be used when recovering from a host side bus error.

During a read operation the SDA pin can be left in a LO state if the host has not sent enough SCL pulses to

complete a transaction (i.e., host side bus error). The TPS65820 clears any SDA LO condition if 10 SCL pulses

are sent by the host, enabling recovery from host side bus error events.

I2C Communication Protocol