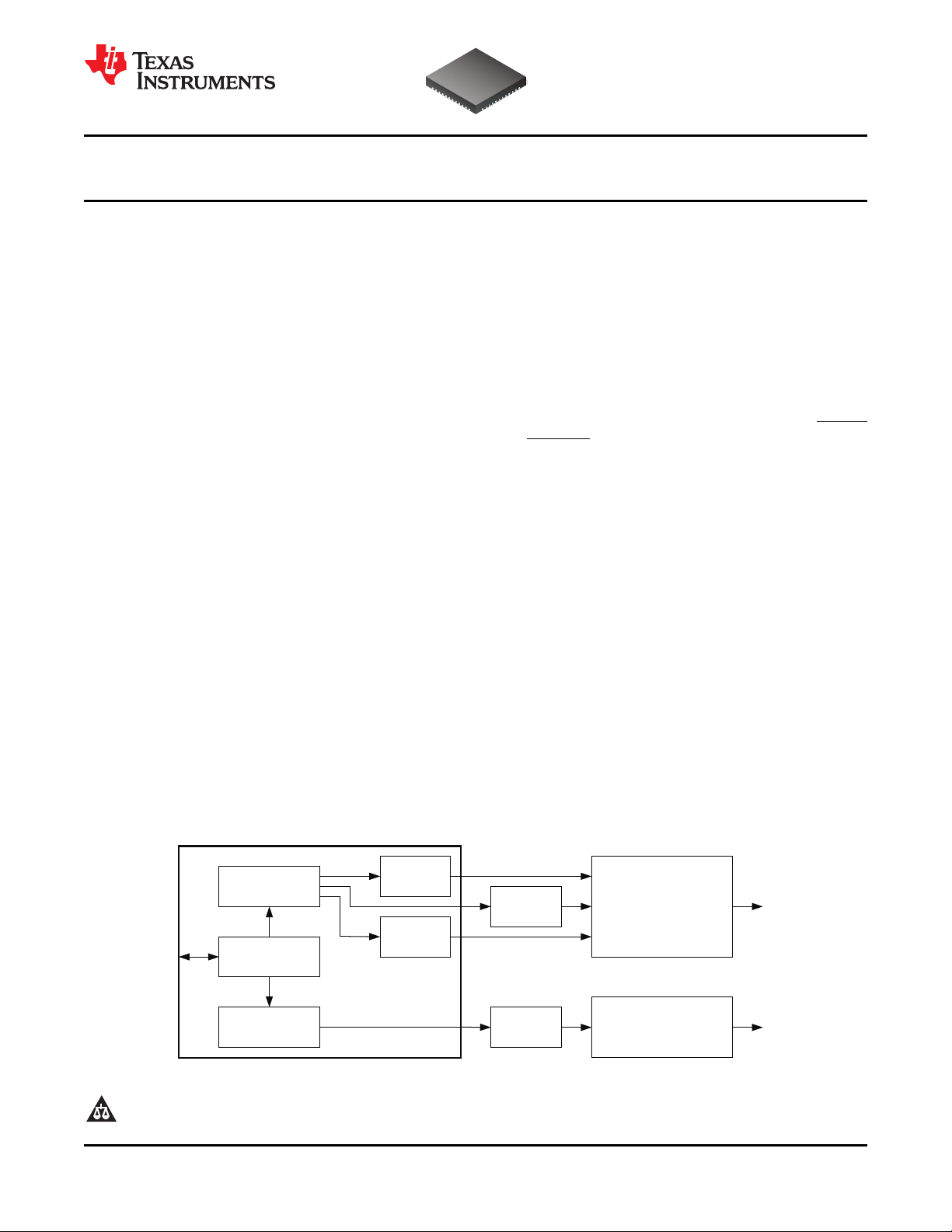

TPS51640

VCC_CPU

VCC_GFX

Processor

3-phase CPU

Controller

IMVP-7

SVID Interface

1-phase GPU

Controller

TPS51601

FET Driver

CPU Power Stage

TPS51601

FET Driver

Internal

FET Driver

Internal

FET Driver

GPU Power Stage

UDG-11062

TPS51640A, TPS59640, TPS59641

www.ti.com

SLUSAQ2 –JANUARY 2012

Dual-Channel (3-Phase CPU/1-Phase GPU) SVID, D-CAP+™ Step-Down Controller for

IMVP-7 V

1

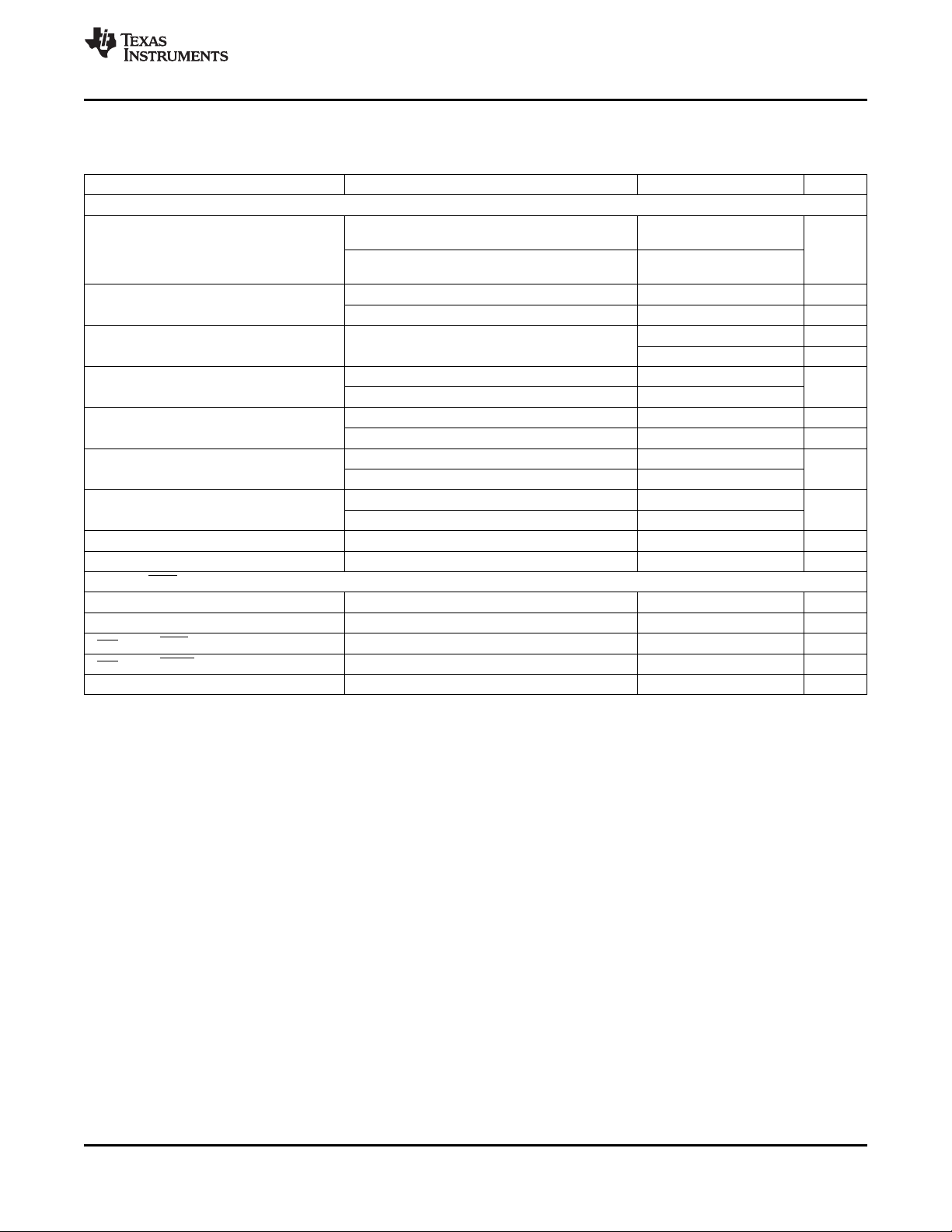

FEATURES

2

• Intel IMVP-7 Serial VID (SVID) Compliant

with Two Integrated Drivers

CORE

• Supports CPU and GPU Outputs

• CPU Channel 1, 2, or 3 Phase

• Single-Phase GPU Channel

• Full IMVP-7 Mobile Feature Set Including

Digital Current Monitor

• 8-Bit DAC with 0.250-V to 1.52-V Output Range

• Optimized Efficiency at Light and Heavy Loads

• V

• V

Overshoot Reduction (OSR)

CORE

Undershoot Reduction (USR)

CORE

• Accurate, Adjustable Voltage Positioning

• 8 Independent Frequency Selections per

Channel (CPU/GPU)

• Patent Pending AutoBalance™ Phase

Balancing

• Selectable 8-Level Current Limit

• 3-V to 28-V Conversion Voltage Range

• Two Integrated Fast FET Drivers w/Integrated

Boost FET

• Internal Driver Bypass Mode for Use with

DrMOS Devices

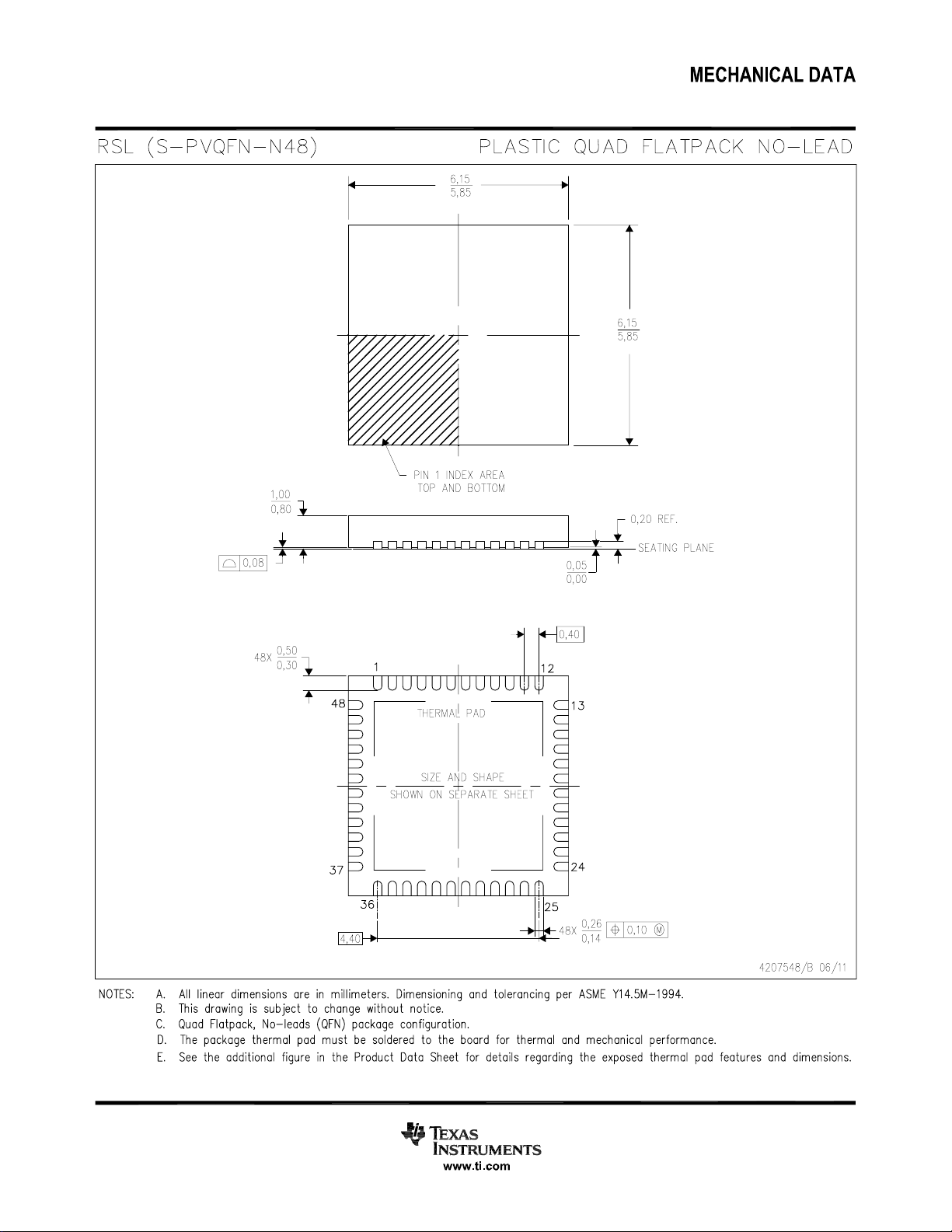

• Small 6 × 6 , 48-Pin, QFN, PowerPAD™

Package

DESCRIPTION

The TPS51640A, TPS59640 and TPS59641 are

dual-channel, fully SVID compliant IMVP-7 step-down

controllers with two integrated gate drivers. Advanced

control features such as D-CAP™+ architecture with

overlapping pulse support (undershoot reduction,

USR) and overshoot reduction (OSR) provide fast

transient response, lowest output capacitance and

high efficiency. All of these controllers also support

single-phase operation for light loads. The full

compliment of IMVP-7 I/O is integrated into the

controllers including dual PGOOD signals, ALERT

and VR_HOT. Adjustable control of V

and voltage positioning round out the IMVP-7

features. In addition, the controllers' CPU channel

includes two high-current FET gate drivers to drive

high-side and low-side N-channel FETs with

exceptionally high speed and low switching loss. The

TPS51601 or TPS51601A driver is used for the third

phase of the CPU and the GPU channel.

The BOOT voltage (V

) on the TPS51640A and

BOOT

TPS59640 is 0 V. The TPS59641 is specifically

designed for a V

level of 1.1 V.

BOOT

These controllers are packaged in a space saving,

thermally enhanced 48-pin QFN. The TPS51640A is

rated to operate from –10°C to 105°C. The

TPS59640 and TPS59641 are rated to operate

from –40°C to 105°C.

CORE

slew rate

APPLICATIONS

• IMVP-7 V

Battery, NVDC or 3 V/5 V/12 V rails

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2D-CAP+, PowerPAD, D-CAP are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Applications for Adapter,

CORE

SIMPLIFIED APPLICATION

Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

(1)(2)

Green (RoHS and

no Sb/Br)

250

2500

V

T

A

PACKAGE PINS ECO PLAN

BOOT

–10°C to 105°C 0

Plastic Quad Flat

Pack (QFN)

–40°C to 105°C

1.1

ORDERING INFORMATION

(V) NUMBER MEDIA QUANTITY

0 48 Tape-and-reel

ORDERABLE TRANSPORT MINIMUM

TPS51640ARSLT 250

TPS51640ARSLR 2500

TPS59640RSLT 250

TPS59640RSLR 2500

TPS59641RSLT

TPS59641RSLTR

(3)

(3)

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(3) Product preview. Not currently available.

ABSOLUTE MAXIMUM RATINGS

(1)(2)

over operating free-air temperature range (unless otherwise noted)

MIN TYP MAX UNIT

VBAT –0.3 32

CSW1, CSW2 –6.0 32 V

CDH1 to CSW1; CDH2 to CSW2; CBST1 to CSW1; CBST2 to CSW2 –0.3 6.0

Input voltage

CTHERM, CCOMP, CF-IMAX, GF-IMAX, GCOMP, GTHERM,

V5DRV, V5

COCP-I, CCSP1, CCSP2, CCSP3, CCSN1, CCSN2, CCSN3, CVFB,

CGFB, V3R3, VR_ON, VCLK, VDIO, SLEWA, GGFB, GVFB, GCSN, –0.3 3.6

GCSP, GOCP-I,

PGND –0.3 0.3

VREF –0.3 1.8

Output voltage CPGOOD, ALERT, VR_HOT, GPGOOD, CIMON, GIMON –0.3 3.6 V

CPWM3, CSKIP, GPWM, GSKIP, CDL1, CDL2 –0.3 6.0

Electrotatic discharge

Operating junction temperature, T

Storage temperature, T

stg

(HBM) QSS 009-105 (JESD22-A114A) 1.5 kV

(CDM) QSS 009-147 (JESD22-C101B.01) 500 V

J

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted.

–0.3 6.0

-40 125 °C

-55 150 °C

V

2 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

THERMAL INFORMATION

THERMAL METRIC

θ

JA

θ

JCtop

θ

JB

ψ

ψ

θ

JCbot

JT

JB

Junction-to-ambient thermal resistance 31.7

Junction-to-case (top) thermal resistance 19.8

Junction-to-board thermal resistance 7.1

Junction-to-top characterization parameter 0.3

Junction-to-board characterization parameter 7.1

Junction-to-case (bottom) thermal resistance 2.1

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(1)

RECOMMENDED OPERATING CONDITIONS

MIN TYP MAX UNIT

VBAT –0.1 28

CSW1, CSW2 –3.0 30

CDH1 to CSW1; CDH2 to CSW2; CBST1 to CSW1; CBST2 to

CSW2

V5DRV, V5 4.5 5.5

V3R3 3.1 3.5

Input voltage CCOMP, GCOMP –0.1 2.5 V

CTHERM, GTHERM 0.1 3.6

CF-IMAX, GF-IMAX, COCP-I, GOCP-I 0.1 1.7

CCSP1, CCSP2, CCSP3, CCSN1, CCSN2, CCSN3, CVFB, CGFB,

GGFB, GVFB, GCSN, GCSP,

VR_ON, VCLK, VDIO, SLEWA, –0.1 3.5

PGND –0.1 0.1

VREF –0.1 1.72

Output voltage V

CIMON, GIMON –0.1 V

CPGOOD, ALERT, VR_HOT, GPGOOD, –0.1 V

CPWM3, CSKIP, GPWM, GSKIP, CDL1, CDL2, –0.1 V

Operating free air temperature, T

A

TPS59640,TPS59641 –40 105

TPS51460A –10 105

–0.1 5.5

–0.1 1.7

SLUSAQ2 –JANUARY 2012

TPS51640A

TPS59640

TPS59641

RSL

48 PINS

UNITS

°C/W

VREF

V3R3

V5

°C

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 3

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

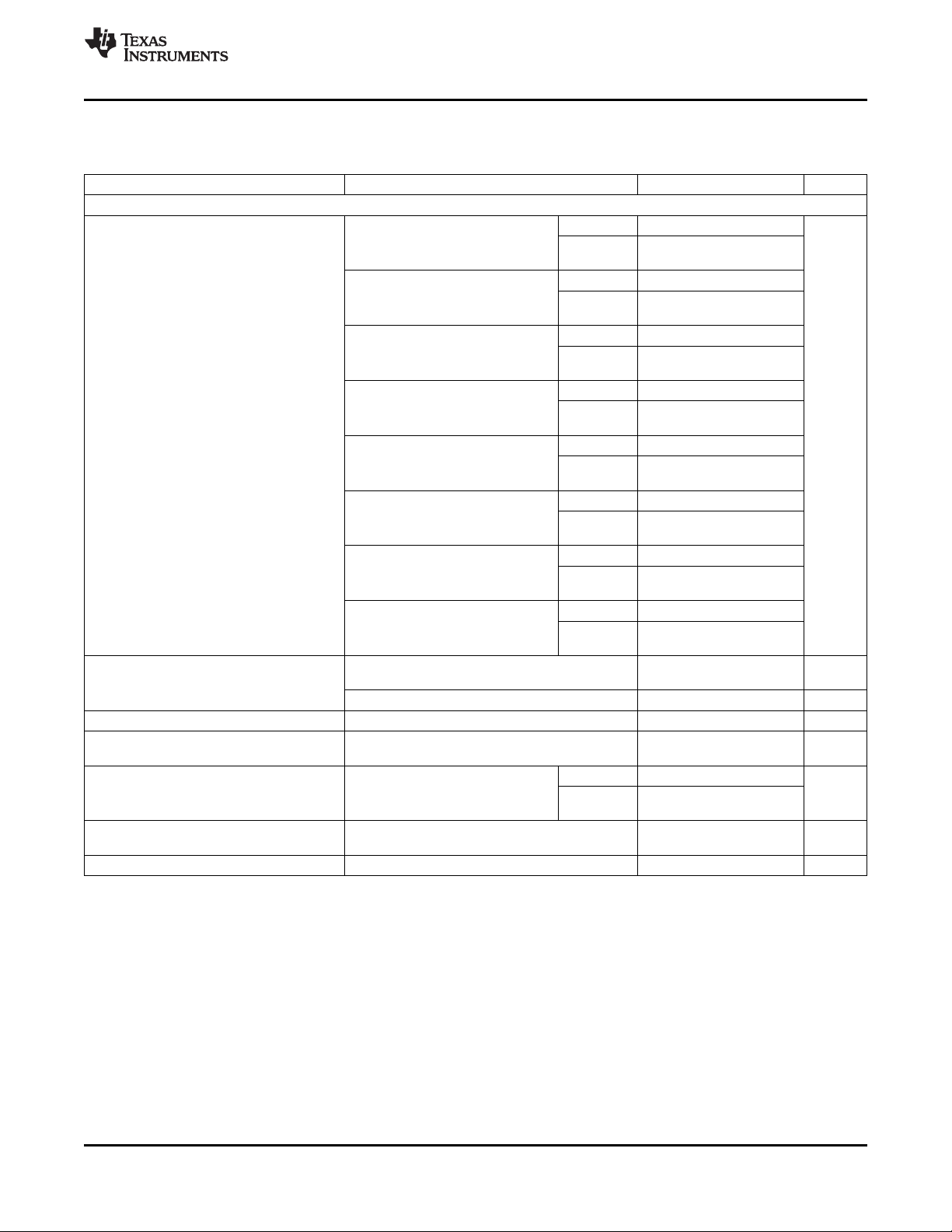

ELECTRICAL CHARACTERISTICS

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SUPPLY: CURRENTS, UVLO AND POWER-ON RESET

I

V5-4

I

V5-3

I

V5-2

I

V5-PS3

I

V5STBY

V

UVLOH

V

UVLOL

I

V3R3

I

V3R3SBY

V

3UVLOH

V

3UVLOL

V5 supply current CPU: 3-phase

active GPU: 1-phase active

V5 supply current CPU: 2-phase

active GPU: 1-phase active

V5 supply current CPU: 1-phase IV5+ I

active GPU: 1-phase active

V5 supply current CPU: 3-phase

active GPU: 1-phase active

V5DRV standby current VR_ON = ‘LO’, IV5+ I

V5 UVLO 'OK' Threshold Ramp up, VR_ON=’HI’, 4.25 4.4 4.5 V

V5 UVLO fault threshold Ramp down, VR_ON = ’HI’, 3.95 4.2 4.3 V

V3R3 supply current SVID bus idle, VR_ON = ‘HI’ 0.5 1.0 mA

V3R3 standby current VR_ON = ‘LO’ 10 µA

V3R3 UVLO 'OK' threshold Ramp up, VR_ON=’HI’, 2.5 2.9 3.0 V

V3R3 UVLO fault threshold Ramp down, VR_ON = ’HI’, 2.4 2.7 2.8 V

IV5+ I

VR_ON = ‘HI’

IV5+ I

VR_ON = ‘HI’, V

VR_ON = ‘HI’, V

IV5+ I

VR_ON = ‘HI’, SetPS = PS3 5.1 mA

(Note: 3-phase CPU goes to 1-phase in PS3)

REFERENCES: DAC, VREF, VBOOT AND DRVL DISCHARGE FOR BOTH CPU AND GPU

V

BOOT

V

VIDSTP

Boot voltage

VID step size 5 mV

0.25 ≤ V

I

V

DAC1

xVFB tolerance no load active

xPU_CORE

0.25 ≤ V

I

xPU_CORE

–40°C ≤ TA≤ 105°C

1.000V ≤ V

I

V

DAC4

V

VREF

V

VREFSRC

V

VREFSNK

V

DLDQ

xVFB tolerance above 1 V VID

VREF Output 4.5 V ≤ VV5≤ 5.5 V, I

VREF output source 0 µA ≤ I

VREF output sink –500 µA ≤ I

DRVL discharge threshold Soft-stop transistor turns on at this point. 200 300 mV

xPU_CORE

1.000V ≤ V

I

xPU_CORE

–40°C ≤ TA≤ 105°C

VOLTAGE SENSE: xVFB AND xGFB FOR BOTH CPU AND GPU

I

xVFB

I

xGFB

A

GAINGND

xVFB input bias current V

xGFB input bias current V

xVFB

xVFB

xGFB/GND gain 1 V/V

CURRENT MONITOR

V

CiMONLK

V

CIMONLO

V

CIMONMID

V

CIMONHI

Zero level current output Σ∆CS = 0 mV, AIMON = 12 × (1+1.27) 35 mV

Low level current output Σ∆CS = 15.6 mV, AIMON = 12 × (1+1.27) 425 mV

Mid level current output Σ∆CS = 31.1 mV, AIMON = 12 × (1+1.27) 850 mV

High level current output Σ∆CS = 62.3 mV, AIMON = 12 × (1+1.27) 1700 mV

ZERO-CROSSING

V

Zx

Inductor zero crossing threshold

voltage

, V

V5DRV

, V

V5DRV

, V

V5DRV

, V

V5DRV

xVFB

= 0 A, 0°C ≤ TA≤ 85°C

xVFB

= 0 A, –6 8.3

xVFB

= 0 A, 0°C ≤ TA≤ 85°C

xVFB

= 0 A, –0.65% 1.0%

VREF

VREF

=2 V, V

=2 V, V

V5DRV

VDAC

VDAC

CCSP3

VDAC

CCSP3

VDAC

= 5.0 V; V

< V

xVFB

< V

xVFB

=3.3 V

< V

xVFB

= V

CCSP2

< V

xVFB

V5DRV

< (V

< (V

< (V

< (V

V3R3

VDAC

VDAC

VDAC

= 3.3 V

VDAC

= 3.3 V; V

+ 100 mV),

+ 100 mV),

+ 100 mV),

+ 100 mV),

TPS59640

TPS51640A

TPS59641 1.1

≤ 0.995V,

≤ 0.995V,

TPS51640A –5 5

TPS59640

TPS59641

≤ 1.520 V,

≤ 1.520 V,

TPS51640A –0.5% 0.5%

TPS59640

TPS59641

= 0 A 1.70 V

VREF

≤ 500 µA –4 –0.1 mV

≤ 0 µA 0.1 4 mV

=0 V 20 40 µA

xGFB

=0 V -40 -20 µA

xGFB

xGFB

= V

PGND

= V

, V

GND

xVFB

6.0 9.0 mA

5.5 mA

4.9 mA

10 20 µA

0 V

0 mV

www.ti.com

= V

CORE

mV

4 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

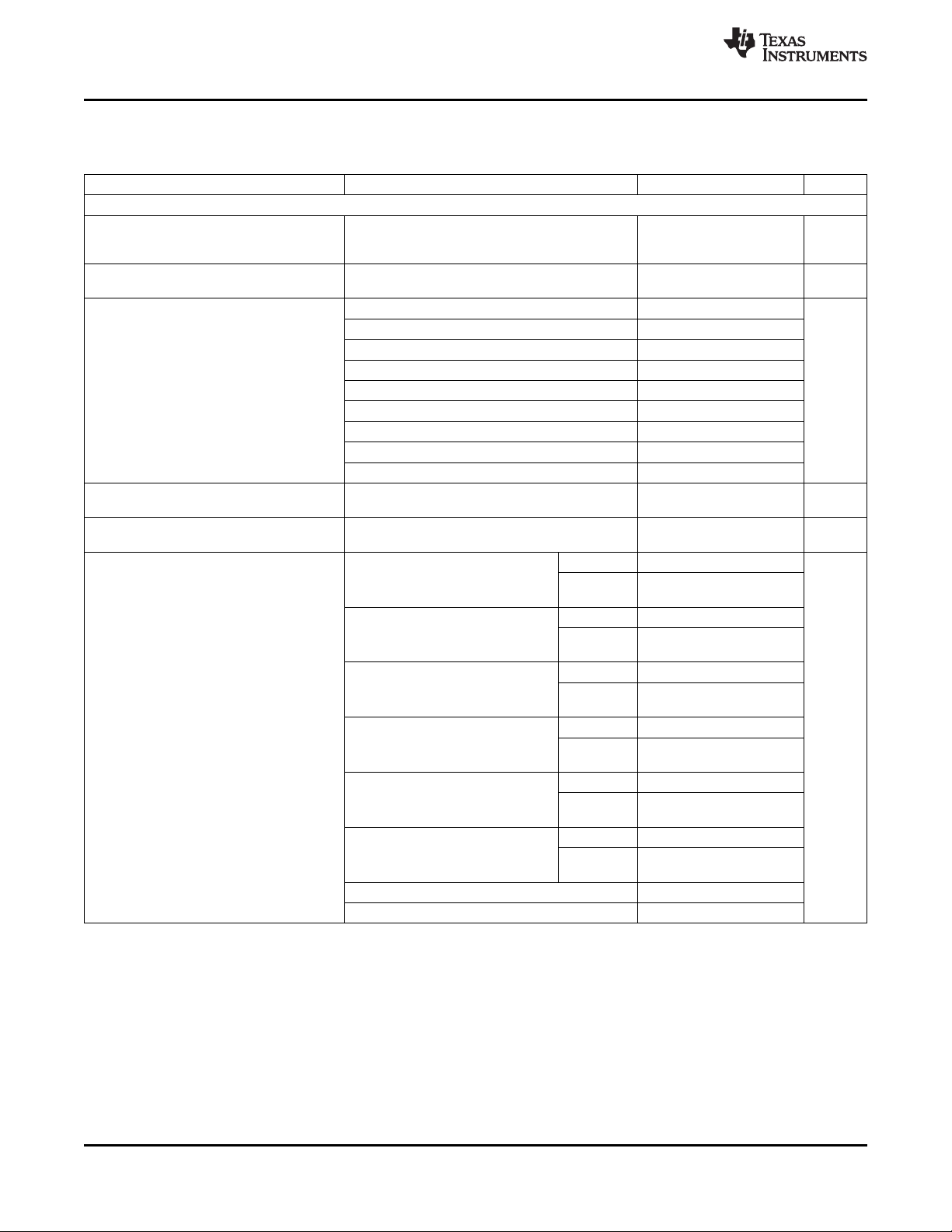

ELECTRICAL CHARACTERISTICS (continued)

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

CURRENT SENSE: OVERCURRENT, ZERO CROSSING, VOLTAGE POSITIONING AND PHASE BALANCING

R

= 20 kΩ

xOCP-I

R

= 24 kΩ

xOCP-I

R

= 30 kΩ

xOCP-I

R

= 39 kΩ

xOCP-I

V

OCPP

V

IMAX

I

CS

I

xVFBDQ

G

M-DROOP

I

BAL_TOL

A

CSINT

OCP voltage (valley current

limit)

R

= 56 kΩ

xOCP-I

R

= 75 kΩ

xOCP-I

R

= 100 kΩ

xOCP-I

R

= 150 kΩ

xOCP-I

IMAX values both channels

V

IMAX_MIN

V

IMAX

V

IMAX_MAX

= 133 mV, value of xIMAX,

= V

REF

= 653mV, value of xIMAX 98 A

CS pin input bias current CSPx and CSNx –1.0 0.2 1.0 µA

xVFB input bias current,

discharge

Droop amplifier

transconductance

Internal current share tolerance –3% +3%

End of soft-stop, xVFB = 100mV 90 125 180 µA

xVFB = 1 V µS

(V

– V

(V

CSP1

CSP3

– V

CSN1

CSN3

Internal current sense gain Gain from CSPx – CSNx to PWM comparator 11.65 12.00 12.30 V/V

V5DRV

× I

MAX

) = (V

) = V

= 5.0 V; V

/ 255

– V

CSP2

OCPP_MIN

CSN2

V3R3

= 3.3 V; V

xGFB

= V

PGND

= V

TPS51640A 5.1 7.0 9.7

TPS59640

TPS59641

4.6 7.0 9.7

TPS51640A 8.1 10.0 12.6

TPS59640

TPS59641

7.6 10.0 13.1

TPS51640A 12.1 14.0 16.7

TPS59640

TPS59641

11.6 14.0 17.2

TPS51640A 17.1 19.0 21.7

TPS59640

TPS59641

16.6 19.0 22.2

TPS51640A 23.1 25.0 27.9

TPS59640

TPS59641

22.6 25.0 28.4

TPS51640A 29.7 32.0 35.0

TPS59640

TPS59641

29.2 32.0 35.5

TPS51640A 37.9 40.0 43.3

TPS59640

TPS59641

37.4 40.0 43.8

TPS51640A 46.8 49.0 52.6

TPS59640

TPS59641

46.2 49.0 53.1

TPS51640A 486 497 518

TPS59640

TPS59641

480 497 518

) =

SLUSAQ2 –JANUARY 2012

, V

xVFB

= V

CORE

GND

mV

20 A

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 5

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

ELECTRICAL CHARACTERISTICS (continued)

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

TIMERS: SLEW RATE, ISLEW, ADDR, ON-TIME AND I/O TIMING

V

t

STARTUP1

SL

STRTSTP

SL

SET

t

PGDDGLTO

t

PGDDGLTU

t

TON_CPU

Start-up time time from VR_ON until the controller responds to 5 ms

xVFB slew soft-start / soft-stop 1.25 1.50 1.75 mV/µs

Slew rate setting V

xPGOOD deglitch time 5 100 µs

xPGOOD deglitch time 150 500 µs

CPU on-time RCF=39 kΩ, V

BOOT

SVID commands

SLEWRATE = 12mV/µs, VR_ON goes ‘HI’,

VR_ON goes ‘LO = ‘Soft-stop’

VSLEWA ≤ 0.30V (Also disables SVID CLK timer) 10.0 12.0 14.5

V

SLEWA

V

SLEWA

0.75 V ≤ V

SLEWA

V

SLEWA

V

SLEWA

V

SLEWA

V

SLEWA

Time from xVFB out of +220 mV VDAC boundary

to xPGOOD low.

Time from xVFB out of –315 mV VDAC boundary

to xPGOOD low.

RCF=20 kΩ, V

(250 kHz)

RCF=24 kΩ, V

(300 kHz)

RCF=30 kΩ, V

(350 kHz)

(400 kHz)

RCF=56 kΩ, V

(450 kHz)

RCF=75 kΩ, V

(500 kHz)

RCF=100 kΩ, V

RCF=150 kΩ, V

V5DRV

> 0 V, SLEWRATE = 12 mV/µs, no faults,

= 0.4 V 3.5 4.0 5.0

= 0.6 V 7.5 8.5 9.5

≤ 0.85 V 10.0 12.0 14.5

SLEWA

= 1.0 V 16 mV/µs

= 1.2 V 20

= 1.4 V 23

= 1.6 V 26

≥ 2.50 V 26

=12 V, V

BAT

=12 V, V

BAT

=12 V, V

BAT

=12 V, V

BAT

=12 V, V

BAT

=12 V, V

BAT

BAT

BAT

= 5.0 V; V

=12 V, V

=12 V, V

= 3.3 V; V

V3R3

DAC

=1.1 V

TPS51640A 270 327 375

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 225 272 320

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 185 235 280

TPS59640

TPS59641

=1.1 V ns

DAC

TPS51640A 160 207 252

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 140 185 231

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 120 167 212

TPS59640

TPS59641

=1.1 V (550 kHz) 109 152 198

DAC

=1.1 V (600 kHz) 105 140 177

DAC

xGFB

= V

PGND

= V

GND

265 327 380

220 272 325

180 235 285

155 207 262

134 185 241

115 167 217

, V

xVFB

= V

www.ti.com

CORE

6 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

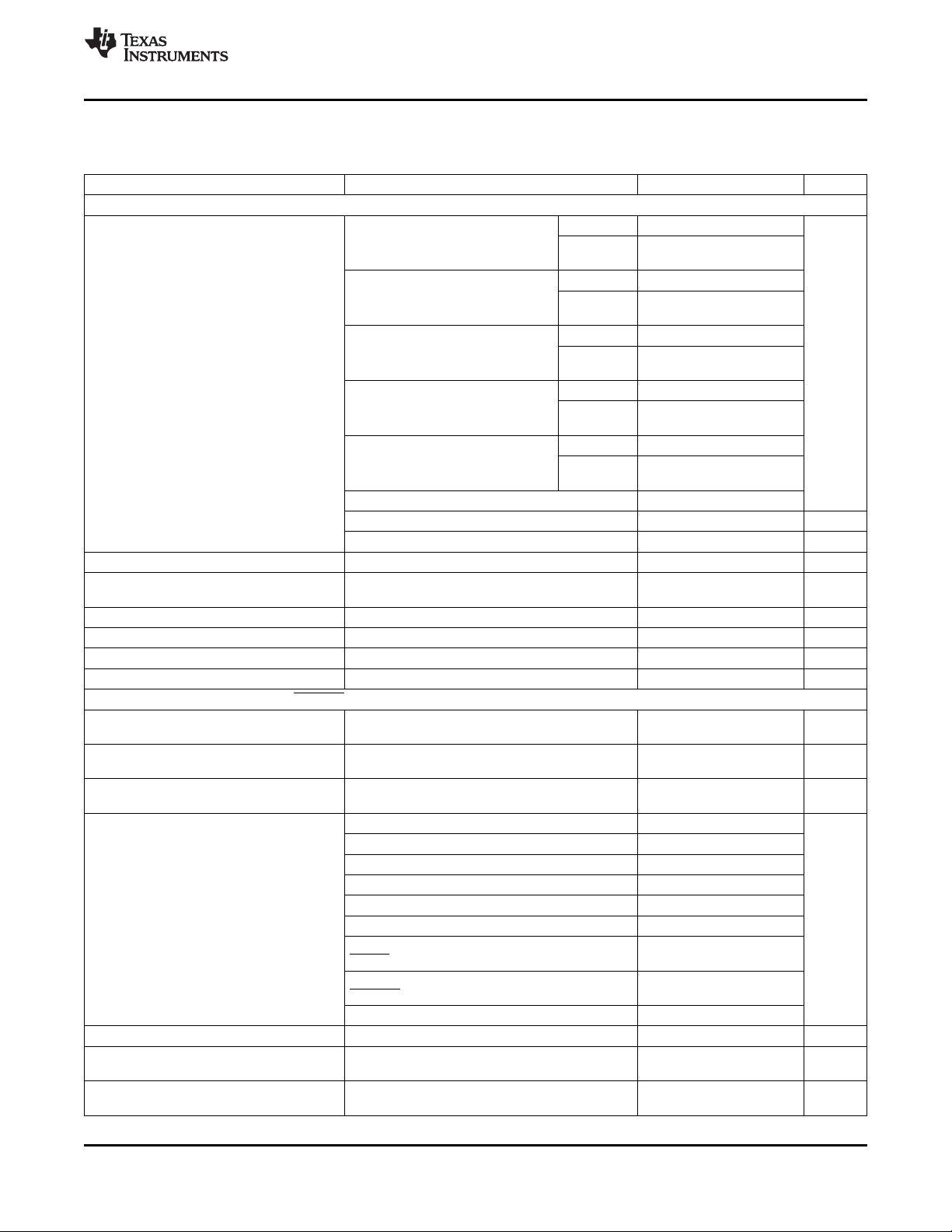

ELECTRICAL CHARACTERISTICS (continued)

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

TIMERS: SLEW RATE, ISLEW, ADDR, ON-TIME AND I/O TIMING (Continued)

RGF=20 kΩ, V

(275 kHz)

RGF=24 kΩ, V

(330 kHz)

RGF=30 kΩ, V

(385 kHz)

t

TON_GPU

t

MIN

t

VCCVID

t

VRONPGD

t

PGDVCC

t

VRTDGLT

R

SFTSTP

PROTECTION: OVP, UVP PGOOD, VR_HOT, ‘FAULTS OFF’ AND INTERNAL THERMAL SHUTDOWN

V

OVPH

V

PGDH

V

PGDL

V

THERM

I

THRM

TH

INT

TH

HYS

GPU on-time

RGF=39 kΩ,V

(440 kHz)

RGF=56 kΩ, V

(495 kHz)

RGF=75 kΩ, V

RGF=100 kΩ, V

RGF=150 kΩ, V

Controller minimum off time Fixed value 150 200 ns

ACK of SetVID-x command to start of voltage

VID change to xVFB change

(1)

ramp

VR_ON low to xPGOOD low 20 50 100 ns

xPGOOD low to xVFB change

(1)

VR_HOT# deglitch time 0.2 0.7 ms

Soft-stop transistor resistance Connect to CVFB, GVFB 550 770 1100 Ω

Fixed OVP voltage threshold

voltage

xPGOOD high threshold 190 220 245 mV

xPGOOD low threshold –348 –315 –280 mV

VCSN1 or VGCSN > V

Measured at the xVFB pin wrt/VID code,

device latches OFF

Measured at the xVFB pin wrt/VID code,

device latches OFF

bit0 of xTHERM register = high 757 783 808

bit1 of xTHERM register also is high 651 680 707

bit2 of xTHERM register also is high 611 638 663

bit3 of xTHERM register also is high 570 598 623

IMVP-7 thermal bit voltage

definition

bit4 of xTHERM register also is high 531 559 583

bit5 of xTHERM register also is high 496 523 548

bit6 of xTHERM register also is high,

ALERT goes low

bit7 of XTHERM register also is high,

VR_HOT goes low

CDLx goes low, CDHx goes low 373 410 425

THERM current Leakage current –5 5 µA

Internal controller thermal

Shutdown

Controller thermal SD

hysteresis

(1)

(1)

Latch off controller 155 °C

Cooling required before converter can be reset 20 °C

V5DRV

BAT

BAT

BAT

BAT

BAT

BAT

BAT

BAT

= 5.0 V; V

=12 V, V

=12 V, V

=12 V, V

=12 V, V

=12 V, V

=12 V, V

=12 V, V

=12 V, V

OVPH

DAC

V3R3

=1.1 V

= 3.3 V; V

TPS51640A 315 347 388

TPS59640

xGFB

= V

TPS59641

DAC

=1.1V

TPS51640A 251 287 330

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 215 245 287

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 180 216 252

TPS59640

TPS59641

DAC

=1.1 V

TPS51640A 160 190 223

TPS59640

TPS59641

=1.1 V (550 kHz) 145 171 210

DAC

=1.1 V (605 kHz) 120 156 205

DAC

=1.1 V (660 kHz) 100 150 201

DAC

for 1 µs, DRVL → ON 1.68 1.72 1.77 V

SLUSAQ2 –JANUARY 2012

= V

, V

PGND

GND

xVFB

= V

CORE

310 347 393

246 287 335

210 245 292 ns

175 216 257

155 190 228

2 µs

100 ns

461 488 513

428 455 481

mV

(1) Specified by design. Not production tested.

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 7

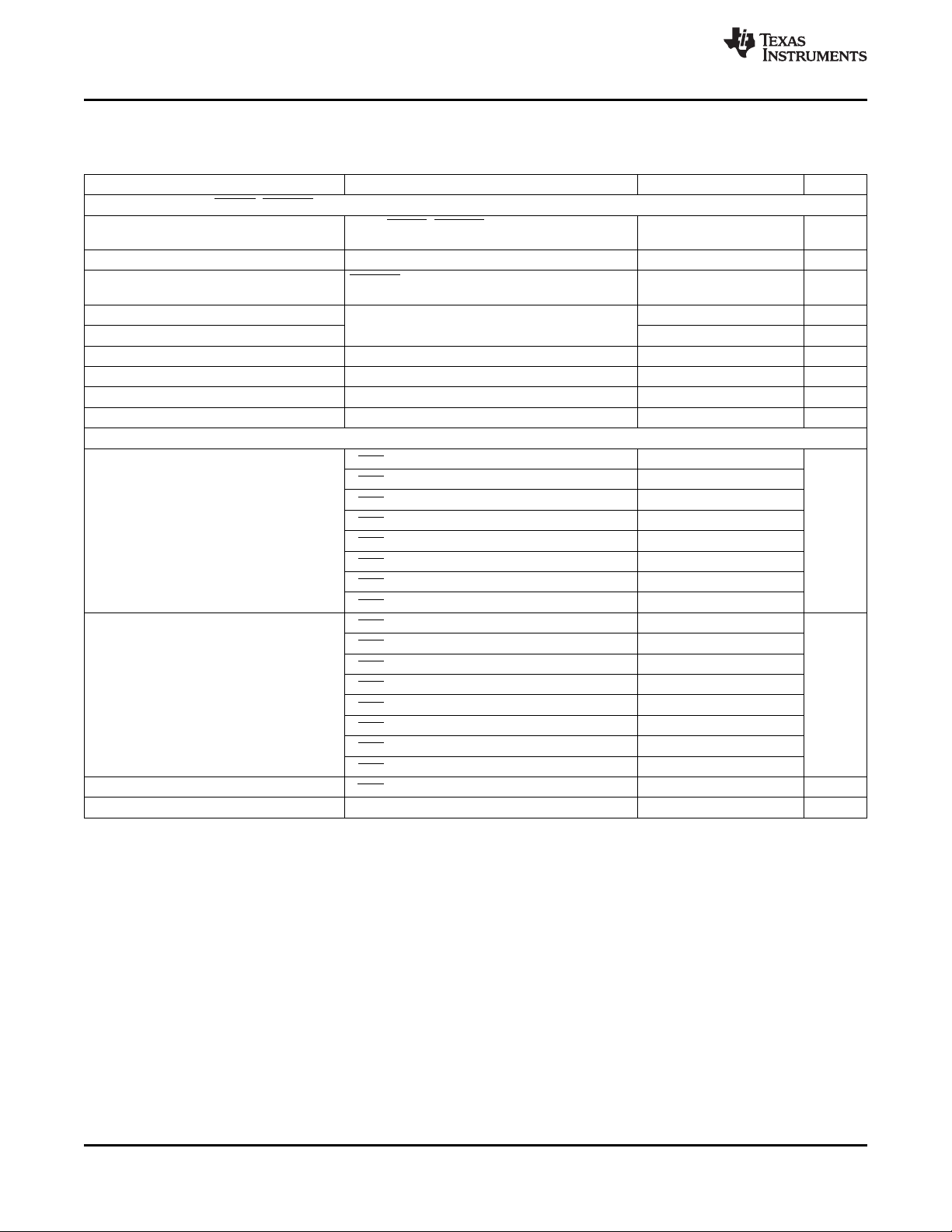

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

ELECTRICAL CHARACTERISTICS (continued)

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

LOGIC (VCLK, VDIO, ALERT, VR_HOT, VR_ON) INTERFACE PINS: I/O VOLTAGE AND CURRENT

R

RSVIDL

R

RPGDL

I

VRTTLK

V

IL

V

IH

V

HYST

V

VR_ONL

V

VR_ONH

I

VR_ONH

Open drain pull down resistance 4 8 13 Ω

Open drain pull down resistance xPGOOD pull-down resistance at 0.31 V 36 50

Open drain leakage current -2 0.2 2 µA

Input logic low 0.45 V

Input logic high 0.65 V

Hysteresis voltage

(1)

VR_ON logic low 0.3 V

VR_ON logic high 0.8 V

I/O 3.3 V leakage Leakage current , V

OVERSHOOT AND UNDERSHOOT REDUCTION (OSR/USR) THRESHOLD SETTING

V

OSR

V

USR

V

OSR_OFF

V

OSRHYS

OSR voltage set mV

USR voltage set mV

OSR OFF setting V

OSR/USR voltage hysteresis

(2) Specified by design. Not production tested.

VDIO, ALERT, VR_HOT, pull-down resistance at

0.31 V

VR_HOT, xPGOOD, Hi-Z leakage,

apply 3.3-V in off state

VCLK, VDIO

R

= 20 kΩ 106

xSKIP

R

= 24 kΩ 156

xSKIP

R

= 30 kΩ 207

xSKIP

R

= 39 kΩ 257

xSKIP

R

= 56 kΩ 308

xSKIP

R

= 75 kΩ 409

xSKIP

R

= 100 kΩ 510

xSKIP

R

= 150 kΩ 610

xSKIP

R

= 20 kΩ 40

xSKIP

R

= 24 kΩ 60

xSKIP

R

= 30 kΩ 75

xSKIP

R

= 39 kΩ 115

xSKIP

R

= 56 kΩ 153

xSKIP

R

= 75 kΩ 190

xSKIP

R

= 100 kΩ 230

xSKIP

R

≥ 150 kΩ = OFF –

xSKIP

at start up 100 300 mV

xSKIP

(2)

All settings 20%

V5DRV

= 5.0 V; V

= 1.1 V 10 25.0 µA

VR_ON

V3R3

= 3.3 V; V

xGFB

= V

PGND

= V

, V

GND

xVFB

0.05 V

www.ti.com

= V

CORE

8 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

over recommended free-air temperature range, VV5= V

(Unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DRIVERS: HIGH-SIDE, LOW-SIDE, CROSS CONDUCTION PREVENTION AND BOOST RECTIFIER

(V

– V

R

DRVH

DRVH ON resistance Ω

(V

(V

(V

V

I

DRVH

t

DRVH

R

DRVL

I

DRVL

t

DRVL

t

NONOVLP

R

DS(on)

I

BSTLK

DRVH sink/source current

(3)

DRVH transition time CDHx 10% to 90% or 90% to 10%, C

DRVL ON resistance Ω

DRVL sink/source current

(3)

DRVL transition time ns

Driver non overlap time ns

BST on-resistance (V

BST switch leakage current V

CDHx

V

CDHx

‘HI’ State, (V

‘LO’ State, (V

V

CDLx

V

CDLx

V

CDLx

V

CDLx

V

CSWx

CDLx falls to 1 V to CDHx rises to 1 V 13 25

VBST

PWM and SKIP OUTPUT: I/O Voltage and Current

V

PWML

V

PWMH

V

SKIPL

V

SKIPH

V

PW(leak)

xPWMy output low level 0.7 V

xPWMy output high level 4.2 V

SKIP output low level 0.7 V

xSKIP output high level 4.2 V

xPWM leakage Tri-state, V = 5 V 0.1 µA

(3) Specified by design. Not production tested.

CBSTx

VBST

CBSTx

DRVH

V5DRV

CSWx

– V

VDRVH

– V

CSWx

– VLL) = 0.25 V

= 2.5 V, (V

= 2.5 V, (V

= 2.5 V, Source 2.7 A

= 2.5 V, Sink 6 A

90% to 10%, C

10% to 90%, C

falls to 1 V to V

– V

VBST

= 34 V, V

V5DRV

= 5.0 V; V

V3R3

= 3.3 V; V

xGFB

) = 5 V, ‘HI’ state,

) = 0.25 V

) = 5 V, ‘LO’ state,

– V

) = 5 V, Source 2.2 A

CSWx

– V

) = 5 V, Sink 2.2 A

CSWx

= 3 nF

CDHx

) = 0.25 V 0.9 2

)= 0.2 V 0.4 1

PGND

= 3 nF 15 40

= 3 nF 15 40

rises to 1 V 13 25

V5DRV

VDRVL

CBSTx

CBSTx

– V

– V

VDRVL

CDLx

CDLx

CDLx

), IF= 5 mA 5 10 20 Ω

=28 V 0.1 1 µA

CSWx

= V

PGND

SLUSAQ2 –JANUARY 2012

= V

, V

xVFB

= V

GND

1.2 2.5

0.8 2.5

15 40 ns

15 40 ns

CORE

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 9

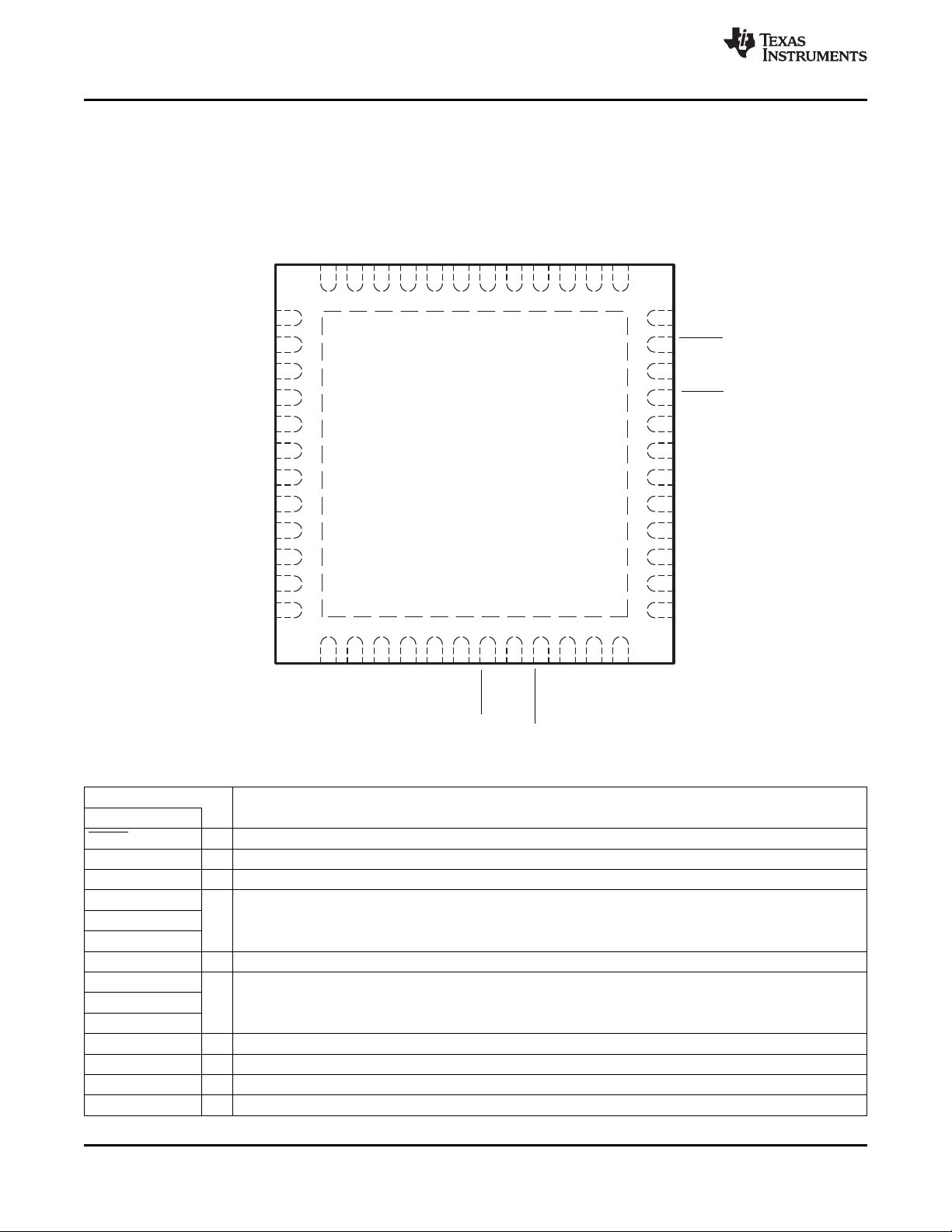

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

36

35

34

33

32

31

30

29

28

27

26

25

48

47

46

45

44

43

42

41

40

39

38

37

CTHERM

COCP-I

CIMON

CCSP1

CCSN1

CCSN2

CCSP2

CCSP3

CCSN3

CVFB

CCOMP

CGFB

CF-IMAX

VREF

V3R3

VR_ON

CPGOOD

VCLK

ALERT

VDIO

VR_HOT

SLEWA

GPGOOD

GF-IMAX

CPWM3

CSKIP

GPWM

GSKIP

GTHERM

GOCP-I

GIMON

GCSP

GCSN

GCOMP

GVFB

GGFB

V5

CDH1

CBST1

CSW1

CDL1

V5DRV

PGND

CDL2

CSW2

CBST2

CDH2

VBAT

TPS51640A

TPS59640

TPS59641

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

www.ti.com

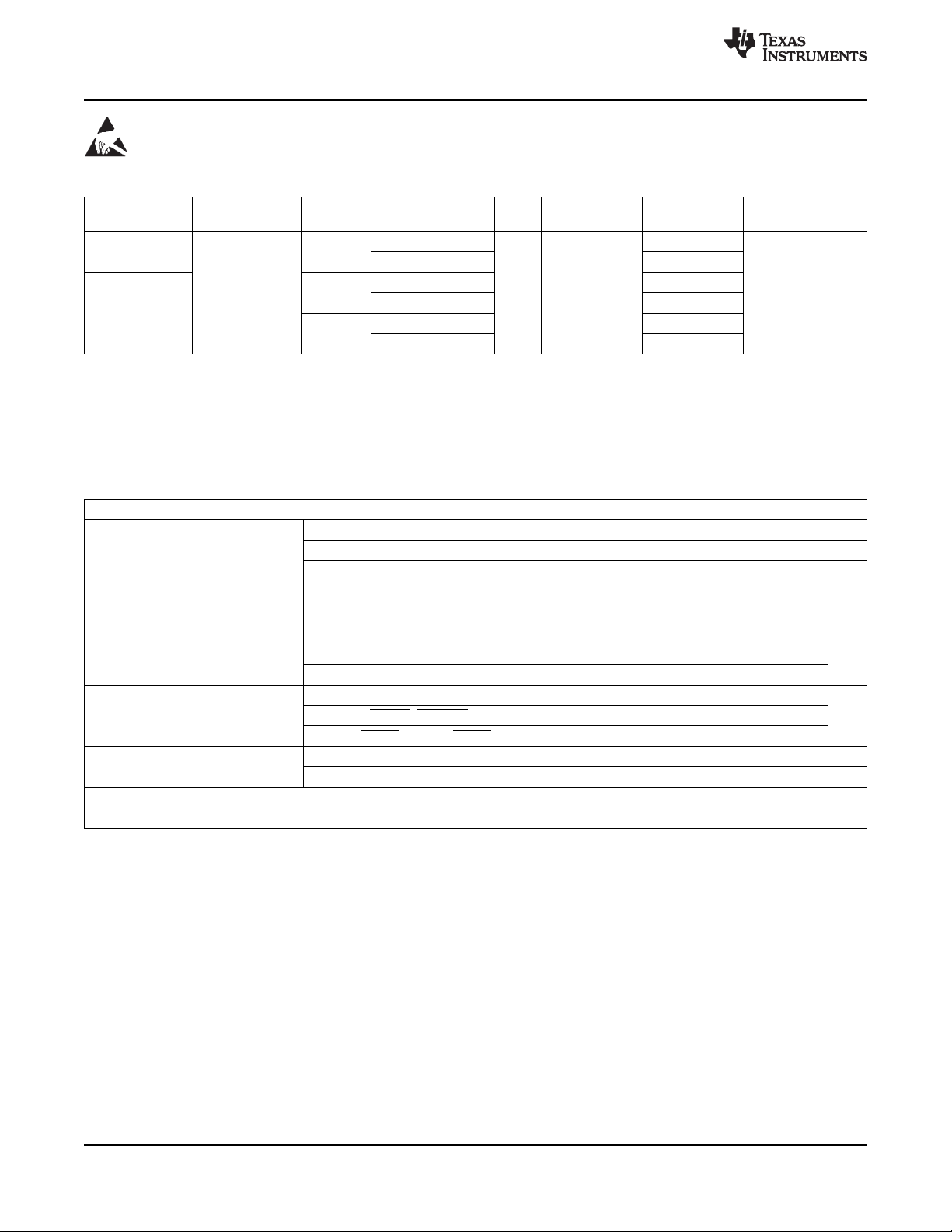

DEVICE INFORMATION

RSL PACKAGE

48 PINS

(TOP VIEW)

PIN FUNCTIONS

PIN

NAME NO.

ALERT 19 O SVID interrupt line, open drain. Route between VCLK and VDIO to prevent cross-talk.

CBST1 46 I Top N-channel FET bootstrap voltage input for CPU phase 1.

CBST2 39 I Top N-channel bootstrap voltage input for CPU phase 2.

CCSN1 5

CCSN2 6 I

CCSN3 9

CCOMP 10 O Output of GM error amplifier for the CPU converter. A resistor to VREF sets the droop gain.

CCSP1 4

CCSP2 7 I or inductor DCR sense network. Tie CCSP3, 2 or 1 (in that order) to V3R3 to disable the phase. Tie CCSP1 to

CCSP3 8

CDH1 47 O Top N-channel FET gate drive output for CPU phase 1.

CDH2 38 O Top N-channel FET gate drive output for CPU phase 2.

CDL1 44 O Synchronous N-channel FET gate drive output for CPU phase 1.

CDL2 41 O Synchronous N-channel FET gate drive output for CPU phase 2.

10 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

I/O DESCRIPTION

Negative current sense inputs for the CPU converter. Connect to the most negative node of current sense

resistor or inductor DCR sense network. CCSN1 has a secondary OVP comparator.

Positive current sense inputs for the CPU converter. Connect to the most positive node of current sense resistor

V3R3 to run the GPU converter only.

www.ti.com

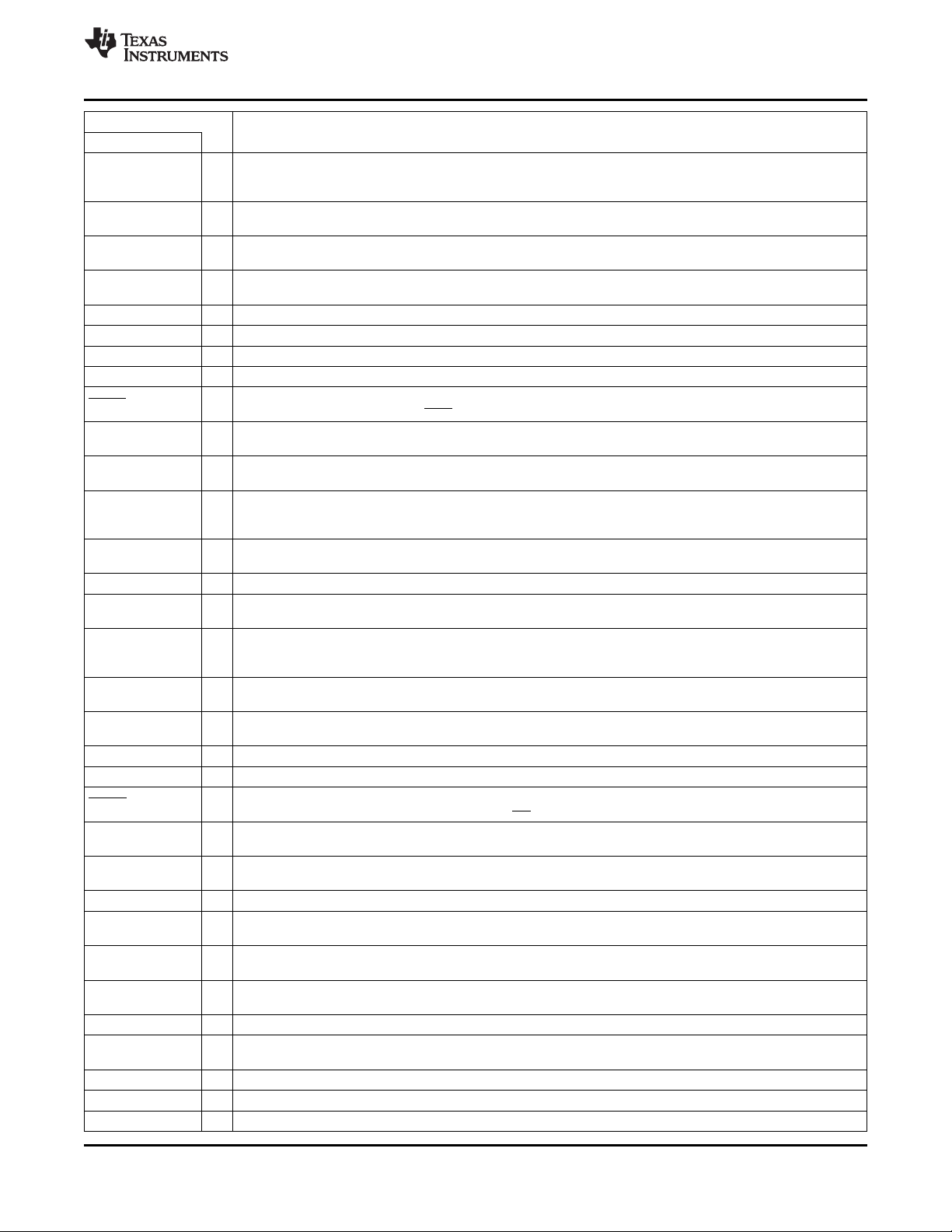

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

PIN

NAME NO.

I/O DESCRIPTION

Voltage divider to VREF. A resistor to GND sets the operating frequency of the CPU converter. The voltage level

CF-IMAX 13 I sets the maximum operating current of the CPU converter. The IMAX value is an 8-bit A/D where V

I

/ 255. Both are latched at start-up.

MAX

CGFB 12 I

CIMON 3 O

COCP-I 2 I

Voltage sense return tied for the CPU converter. Tie to GND with a 10-Ω resistor to close feedback when the

microprocessor is not in the socket.

Analog current monitor output for the CPU converter. V

220-nF capacitor to GND for stability.

Resistor to GND (R

voltage divider to CIMON. Resistor ratio sets the IMON gain (see CIMON pin description).

) selects 1 of 8 OCP levels (per phase, latched at start-up) of the CPU converter. Also,

COCP

= ΣVCS× ACS × (1 + R

CIMON

CIMON/RCOCP

= V

IMAX

REF

). Connect a

CPGOOD 17 O IMVP-7_PWRGD output for the CPU converter. Open-drain.

CSW1 45 I/O Top N-channel FET gate drive return for CPU phase 1.

CSW2 40 I/O Top N-channel FET gate drive return for CPU phase 2.

CPWM3 36 O PWM control for the external driver, 5V logic level.

CSKIP 35 O

CTHERM 1 I/O

CVFB 11 I

Skip mode control of the external driver for the CPU converter. A logic HI = FCCM, LO = SKIP. R to GND selects

1 of 8 OSR/USR levels. 0.1 V < V

< 0.3 V at start-up turns OSR off.

CSKIP

Thermal sensor connection for the CPU converter. A resistor connected to VREF forms a divider with an NTC

thermistor connected to GND.

Voltage sense line tied directly to V

feedback when µP is not in the socket. The soft-stop transistor is on this pin

of the CPU converter. Tie to V

CORE

with a 10-Ω resistor to close

CORE

Negative current sense input for the GPU converter. Connect to the most negative node of current sense resistor

GCSN 28 I or inductor DCR sense network. GCSN has a secondary OVP comparator and includes the soft-stop pull-down

transistor.

GCSP 29 I

Positive current sense input for the GPU converter. Connect to the most positive node of current sense resistor

or inductor DCR sense network. Tie to V3R3 to disable the GPU converter.

GCOMP 27 O Output of gMerror amplifier for the GPU converter. A resistor to VREF sets the droop gain.

GGFB 25 I

Voltage sense return tied for the GPU converter. Tie to GND with a 10-Ω resistor to close feedback when the

microprocessor is not in the socket.

24 I Voltage divider to VREF. R to GND sets the operating frequency of the GPU converter. The voltage level sets

GF-IMAX the maximum operating current of the GPU converter. The IMAX value is an 8-bit A/D where V

I

/ 255. Both are latched at start-up.

MAX

GIMON

GOCP-I

30 O Analog current monitor output for the GPU converter. V

220-nF capacitor to GND for stability.

31 I Voltage divider to GIMON. Resistor ratio sets the IMON gain (see GIMON pin). Resistor to GND (R

1 of 8 OCP levels (per phase, latched at start-up) of the GPU converter.

GIMON

= V

ISENSE

× (1 + R

GIMON/RGOCP

= V

IMAX

REF

). Connect a

GOCP

×

) selects

GPGOOD 23 O IMVP-7_PWRGD output for the GPU converter. Open-drain.

GPWM 34 O PWM control for the external driver, 5-V logic level.

GSKIP

GTHERM

GVFB

33 O Skip mode control of the external driver for the GPU converter, 5-V logic level. Logic HI = FCCM, LO = SKIP. R

to GND selects 1 of 8 OSR/USR levels. 0.1 V < V

< 0.3 V at start-up turns OSR off.

GSKIP

32 I/O Thermal sensor input for the GPU converter. A resistor connected to VREF forms a divider with an NTC

thermistor connected to GND.

26 I Voltage sense line tied directly to V

when the microprocessor is not in the socket. The soft-stop transistor is on this pin

of the GPU converter. Tie to V

GFX

with a 10-Ω resistor to close feedback

GFX

PGND 42 – Synchronous N-channel FET gate drive return.

SLEWA

V5

V5DRV

22 I The voltage at start-up sets 1 of 7 slew rates for both converters. The SLOW rate is SLEWRATE/4. Soft-start

and soft-stop rates are SLEWRATE/8. This value is latched at start-up. Tie to GND to disable SCLK timer.

48 I 5-V power input for analog circuits; connect through resistor to 5-V plane and bypass to GND with ≥1 µF ceramic

capacitor

43 I Power input for the gate drivers; connected with an external resistor to V5F; decouple with a ≥2.2 µF ceramic

capacitor.

V3R3 15 I 3.3-V power input; bypass to GND with ≥1 µF ceramic cap.

VBAT

37 I Provides VBAT information to the on-time circuits for both converters. A 10-kΩ series resistor protects the

adjacent pins from inadvertent shorts due to solder bridges or mis-probing during test.

VCLK 18 I SVID clock. 1-V logic level.

VDIO 20 I/O SVID digital I/O line. 1-V logic level.

VREF 14 O 1.7-V, 500-µA reference. Bypass to GND with a 0.22-µF ceramic capacitor.

×

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 11

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

www.ti.com

PIN

NAME NO.

VR_ON 16 I IMVP-7 VR enable; 1V I/O level; 100-ns de-bounce. Regulator enters controlled soft-stop when brought low.

VR_HOT

PAD GND – Thermal pad and analog circuit reference; tie to a quiet area in the system ground plane with multiple vias.

I/O DESCRIPTION

21 O IMVP-7 thermal flag open drain output – active low. Typically pulled up to 1-V logic level through 56 Ω. Fall time

< 100 ns. 1-ms de-glitch using consecutive 1-ms samples.

12 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

0.80

0.85

0.90

0.95

1.00

1.05

Output Voltage (V)

VIN= 9 V

VIN= 20 V

Nominal

Specified Maximum

Specified Minimum

V

VID

= 1.05 V

0 10 20 90 100

Output Current (A)

30 40 50 70 8060

0.500

0.525

0.575

0.600

0.625

0.675

0.700

0 2 4 18 20

Output Current (A)

Output Voltage (V)

6 8 10 14 1612

VIN= 9 V

VIN= 20 V

Nominal

Specified Maximum

Specified Minimum

V

VID

= 0.6 V

0.550

0.650

65

75

80

85

90

Efficiency (%)

V

VID

= 0.6 V

70

VIN= 9 V

VIN= 20 V

0 2 4 18 20

Output Current (A)

6 8 10 14 1612

65

75

80

85

90

95

Efficiency (%)

V

VID

= 1.05 V

70

VIN= 9 V

VIN= 20 V

0 10 20 90 100

Output Current (A)

30 40 50 70 8060

0

100

150

200

350

400

Frequency (Hz)

50

0 10 20 90 100

Output Current (A)

30 40 50 70 8060

RCF= 24 kW

PS0, V

VID

= 1.05 V, VIN= 9 V

PS0, V

VID

= 1.05 V, VIN= 20 V

PS1, V

VID

= 1.05 V, VIN= 20 V

PS1, V

VID

= 1.05 V, VIN= 9 V

250

300

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

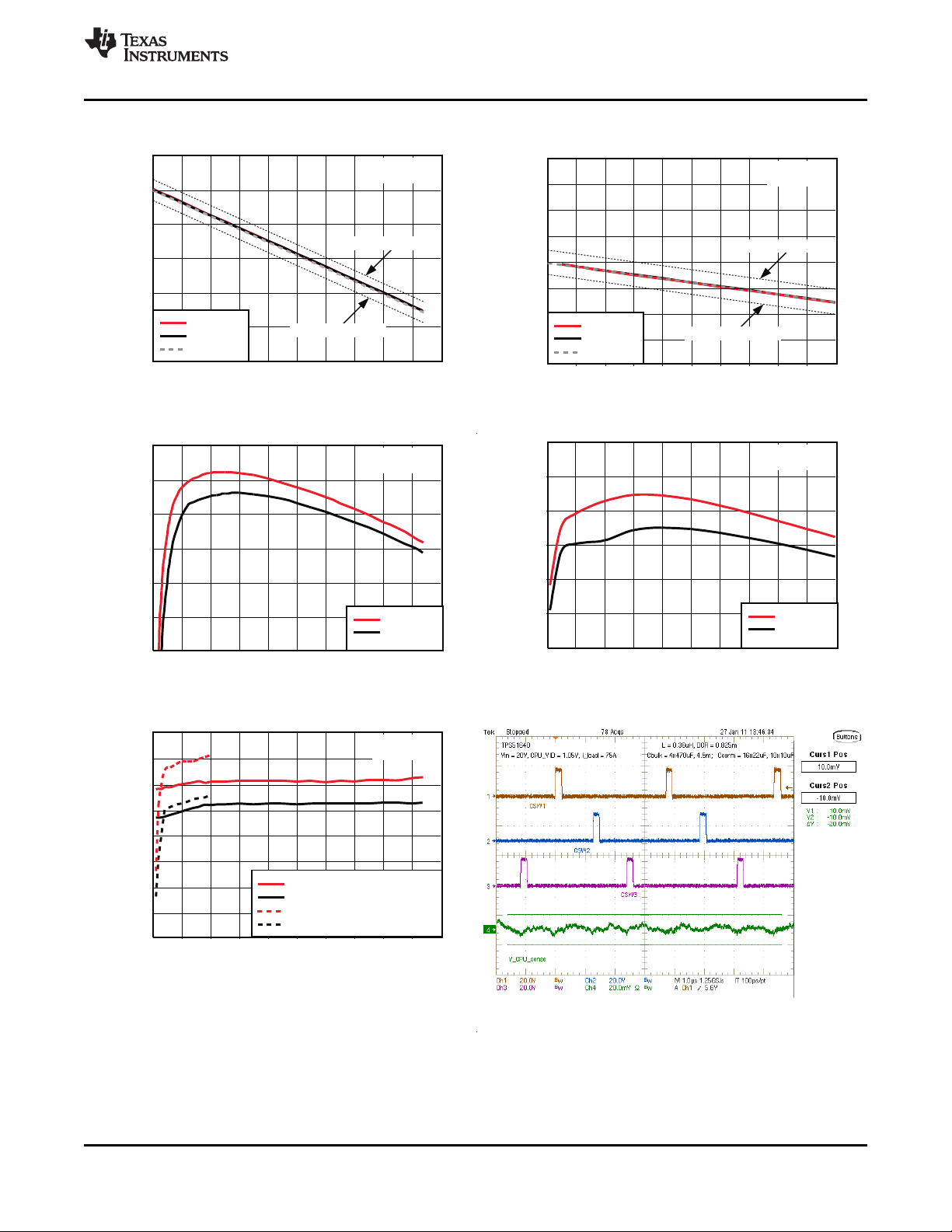

3-Phase Configuration, 94-A CPU

Figure 1. Output Voltage vs. Load Current in PS0 Figure 2. Output Voltage vs. Load Current in PS1

Figure 3. Efficiency vs. Load Current in PS0 Figure 4. Efficiency vs. Load Current in PS1

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 13

Figure 5. Frequency vs Load-Current (PS0 and PS1) Figure 6. Switching Ripple in PS0, VIN= 20 V

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

3-Phase Configuration, 94-A CPU (continued)

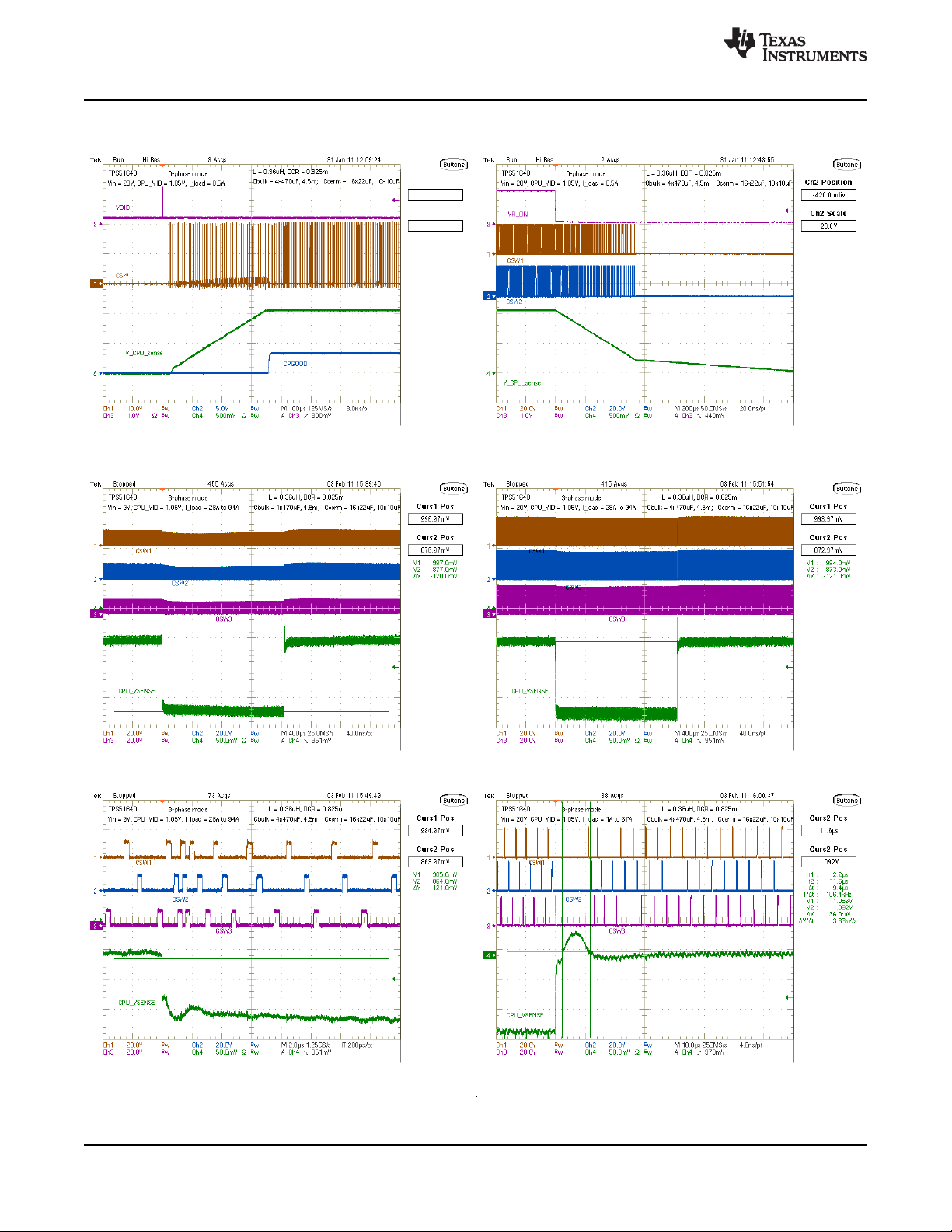

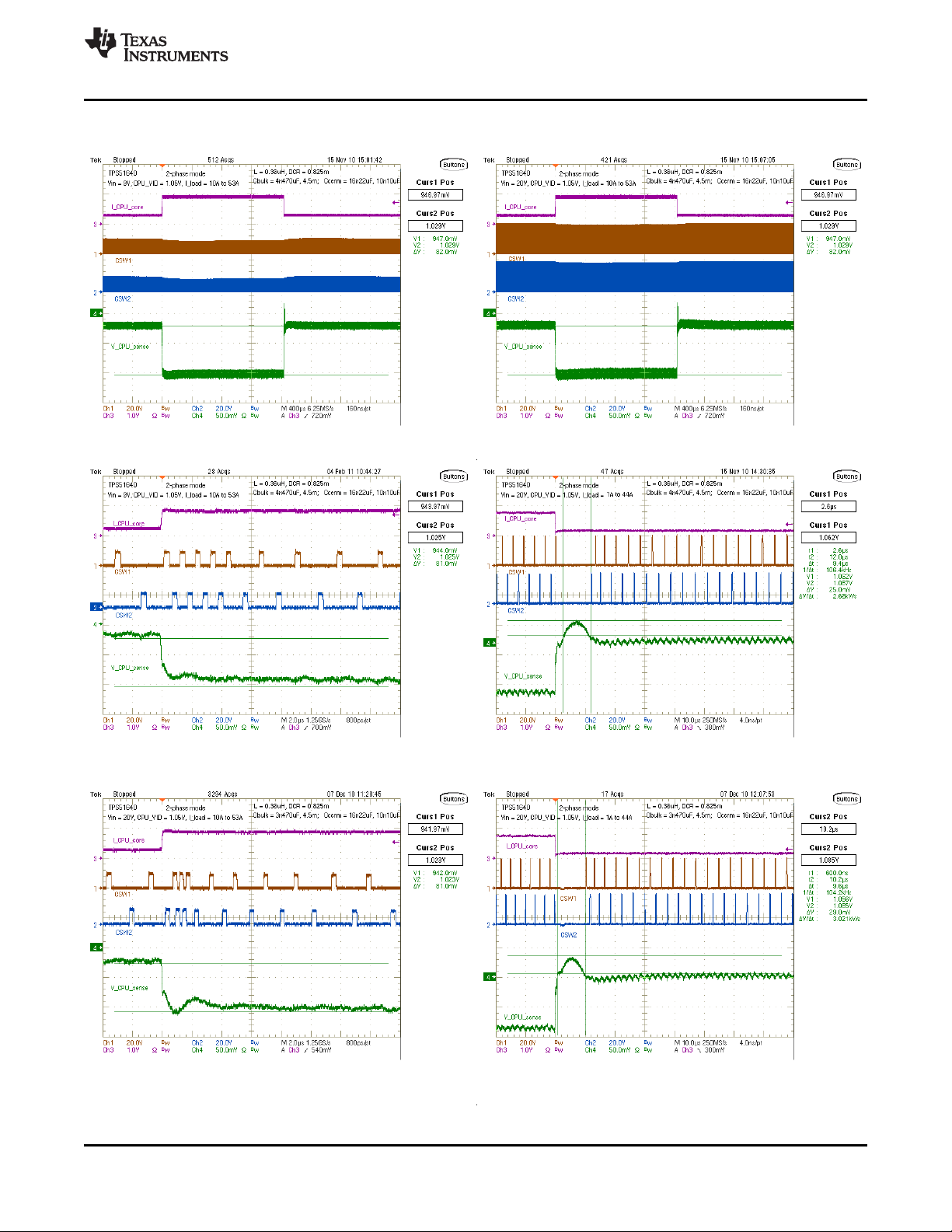

Figure 7. Start-Up and PGOOD Figure 8. Soft-Stop

(TPS51640A and TPS59640 Only)

www.ti.com

Figure 9. Load Transient, VIN= 9 V, Load step = 66 A Figure 10. Load Transient, VIN= 20 V, Load step = 66 A

Figure 11. Load Insertion, VIN= 9 V, Load step = 66 A Figure 12. Load Release, VIN= 20 V, Load step = 66 A

14 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

100 1000 10000 100000 1000000

−50

−40

−30

−20

−10

0

10

20

30

40

50

−225

−180

−135

−90

−45

0

45

90

135

180

225

Frequency (Hz)

Magnitude (dB)

Phase (°)

Gain

Phase

3−Phase CPU

V

OUT

= 1.05 V

I

OUT

~ 20 A

0.0005

0.001

0.0015

0.002

0.0025

0.003

0.0035

0.004

0.0045

-80

-60

-40

-20

0

20

40

60

80

100 1 k 10 k 100 k 1 M

Frequency (Hz)

Z

OUT

Magnitude (W)

Z

OUT

Phase (°)

Magnitude

Target

Phase

CPU

3-Phase

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

3-Phase Configuration, 94-A CPU (continued)

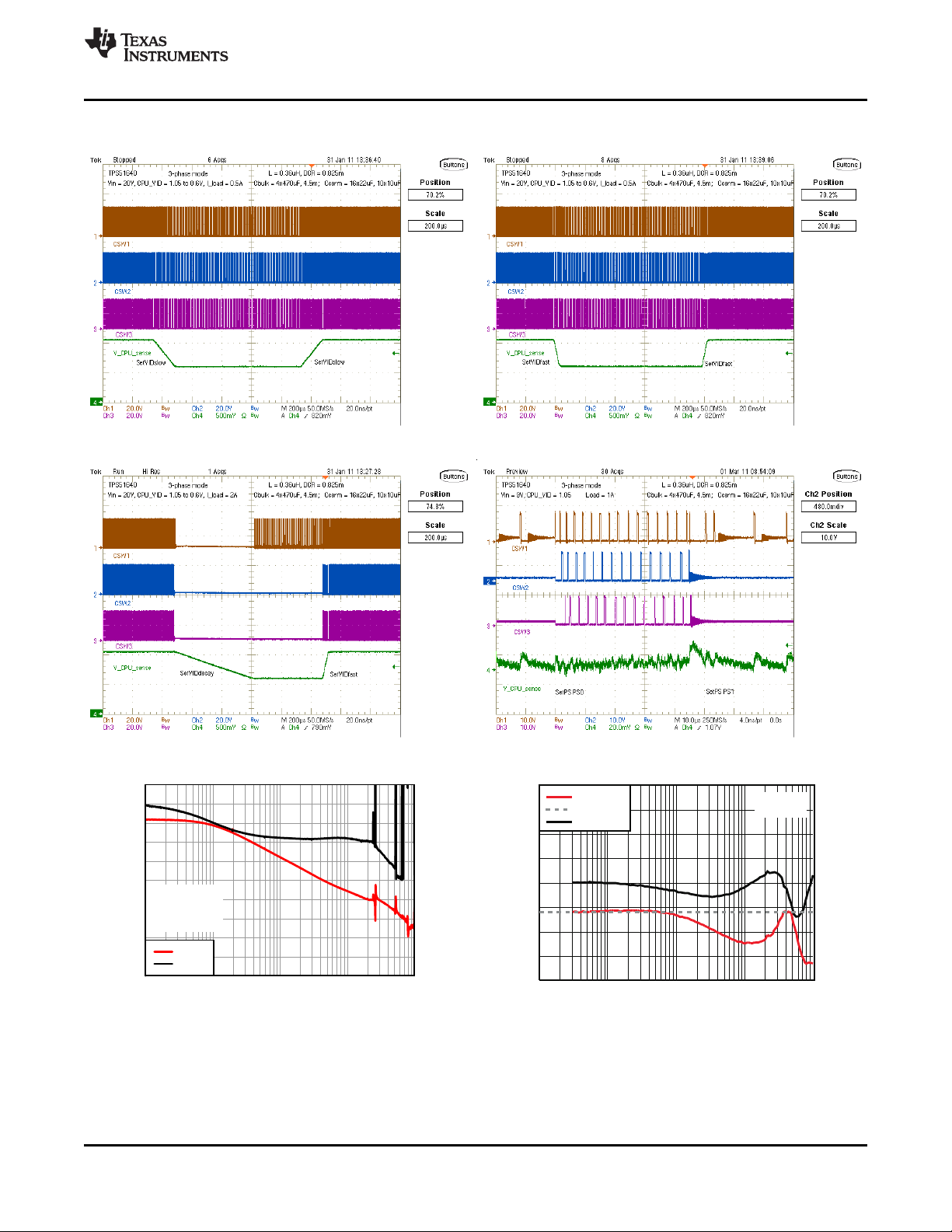

Figure 13. Dynamic VID: SetVID-Slow/SetVID-Slow Figure 14. Dynamic VID: SetVID-Fast/SetVID-Fast

Figure 15. SetVID-Decay/SetVID-Fast Figure 16. PS Change PS0 to PS1 Toggle

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 15

Figure 17. CPU Bode Plot Figure 18. Output Impedance

0.80

0.85

0.90

0.95

1.00

1.05

1.10

Output Voltage (V)

0 10 20

Output Current (A)

30 40 50 60

V

VID

= 1.05 V

VIN= 9 V

VIN= 20 V

Nominal

Specified Maximum

Specified Minimum

65

75

80

85

90

95

Efficiency (%)

70

0 5 10 50 55

Output Current (A)

15 20 25 40 4535

VIN= 9 V

VIN= 20 V

V

VID

= 1.05 V

30

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

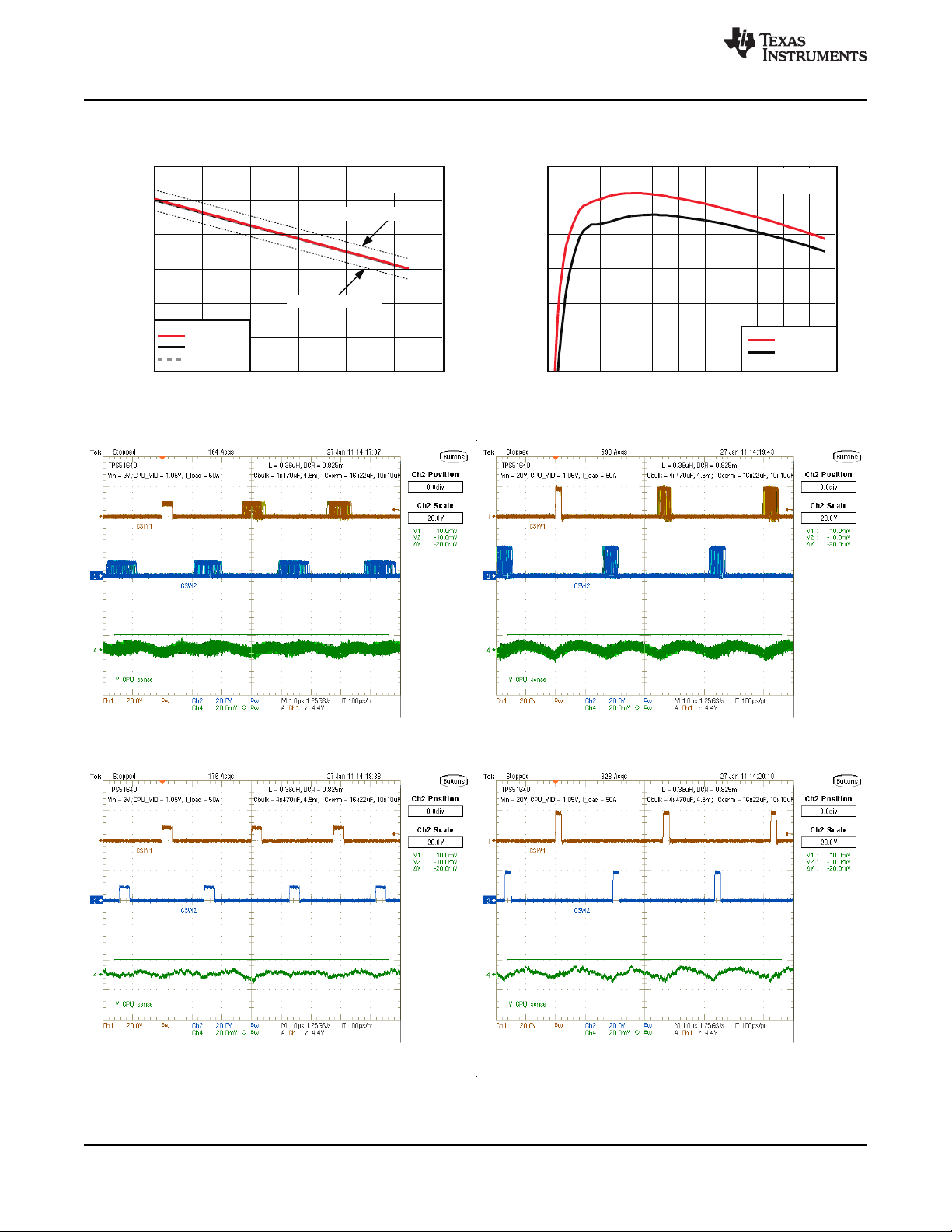

TYPICAL CHARACTERISTICS

2-Phase Configuration, 53-A CPU

Figure 19. Output Voltage Vs. Load Current in PS0 Figure 20. Efficiency Vs. Load Current in PS0

www.ti.com

Figure 21. Switching Ripple in PS0 (Persistence), Figure 22. Switching Ripple in PS0 (Persistence),

16 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

Figure 23. Switching Ripple in PS0, VIN= 9 V Figure 24. Switching Ripple in PS0, VIN= 20 V

VIN= 9 V VIN= 20 V

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

2-Phase Configuration, 53-A CPU (continued)

Figure 25. Load Transient, VIN= 9 V, Load Step = 43 A Figure 26. Load Transient, VIN= 20 V, Load Step = 43 A

Figure 27. Load Insertion, VIN= 9 V, Load Step = 43 A, Figure 28. Load Release, VIN= 20 V, Load Step = 43 A,

Figure 29. Load Insertion, VIN= 9 V, Load Step = 43 A, Figure 30. Load Release,VIN= 20 V, Load Step = 43 A,

OSR/USR Setting 39 kΩ (Reduced Output Capacitance) OSR/USR Setting 39 kΩ (Reduced Output Capacitance)

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 17

OSR/USR Setting 150 kΩ) OSR/USR Setting 150 kΩ)

0.0005

0.001

0.0015

0.002

0.0025

0.003

0.0035

0.004

0.0045

-80

-60

-40

-20

0

20

40

60

80

100 1 k 10 k 100 k 1 M

Frequency (Hz)

Z

OUT

Magnitude (W)

Z

OUT

Phase (°)

Magnitude

Target

Phase

CPU

2-Phase

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

2-Phase Configuration, 53-A CPU (continued)

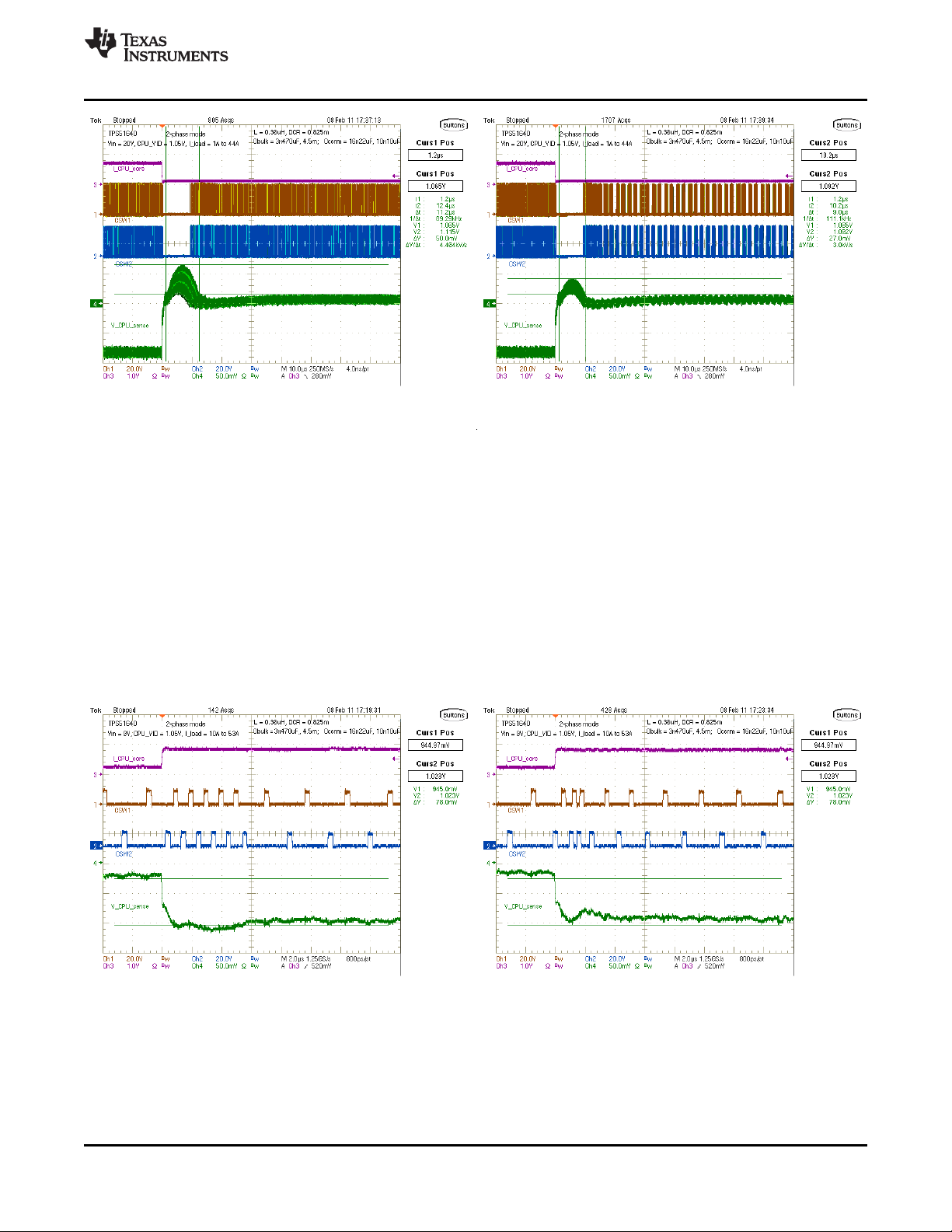

Figure 31. Dynamic VID: SetVID-Slow/SetVID-Slow Figure 32. Dynamic VID: SetVID-Fast/SetVID-Fast

www.ti.com

Figure 33. Dynamic VID: SetVID-Decay/SetVID-Fast, Figure 34. Dynamic VID: SetVID-Decay/SetVID-Fast,

Figure 35. PS Change PS0 to PS1 Toggle Figure 36. Output Impedance

18 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

I

= 2 A I

LOAD

LOAD

= 0.5 A

1.050

1.100

1.125

1.150

1.175

1.200

1.250

Output Voltage (V)

0 5 10

Output Current (A)

20 25 30 35

V

VID

= 1.23 V

VIN= 9 V

VIN= 20 V

Nominal

Specified Maximum

Specified Minimum

15

1.225

1.075

0.500

0.525

0.575

0.600

0.625

0 2 4 18 20

Output Current (A)

Output Voltage (V)

6 8 10 14 1612

0.550

0.650

VIN= 9 V

VIN= 20 V

Nominal

Specified Maximum

Specified Minimum

V

VID

= 0.6 V

75

80

85

90

95

Efficiency (%)

70

VIN= 9 V

VIN= 20 V

V

VID

= 1.23 V

0 5 10

Output Current (A)

20 25 30 3515

55

70

75

85

90

95

Efficiency (%)

60

0 2 4 18 20

Output Current (A)

6 8 10 14 1612

VIN= 9 V

VIN= 20 V

V

VID

= 0.6 V

80

65

0

100

150

200

350

400

Frequency (Hz)

50

0 5 10

Output Current (A)

3515 25 3020

250

300

RGF= 30 kW

PS0, V

VID

= 1.23 V, VIN= 9 V

PS0, V

VID

= 1.23 V, VIN= 20 V

PS1, V

VID

= 0.06 V, VIN= 20 V

PS1, V

VID

= 0.06 V, VIN= 9 V

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

1-Phase Configuration, 33-A GPU

Figure 37. Output Voltage Vs. Load Current in PS0 Figure 38. Output Voltage Vs. Load Current in PS1

Figure 39. Efficiency Vs. Load Current in PS0 Figure 40. Efficiency Vs. Load Current in PS1

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 19

Figure 41. Frequency Vs. Load Current Figure 42. Switching Ripple in PS0

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

1-Phase Configuration, 33-A GPU (continued)

Figure 43. Start-Up and PGOOD Figure 44. Soft-Stop

(TPS51640A and TPS59640 Only)

www.ti.com

Figure 45. Load Transient, VIN= 9 V, Load Step = 20 A Figure 46. Load Transient, VIN= 20 V, Load Step = 20 A

Figure 47. Load Insertion, VIN= 9V, Load Step = 20 A Figure 48. Load Release, VIN= 20 V, Load Step = 20 A

20 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

100 1000 10000 100000 1000000

−50

−40

−30

−20

−10

0

10

20

30

40

50

−225

−180

−135

−90

−45

0

45

90

135

180

225

Frequency (Hz)

Magnitude (dB)

Phase (°)

Gain

Phase

GPU

V

OUT

= 1.05 V

I

OUT

~ 10 A

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS

1-Phase Configuration, 33-A GPU (continued)

Figure 49. Dynamic VID: SetVID-Slow/SetVID-Slow Figure 50. Dynamic VID: SetVID-Fast/SetVID-Fast

Figure 51. Dynamic VID: SetVID-Decay/SetVID-Fast, Figure 52. Dynamic VID: SetVID-Decay/SetVID-Fast,

I

= 0.5 A I

LOAD

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 21

Figure 53. Bode Plot

LOAD

= 2 A

11CVFB

12CGFB

4CCSP1

5CCSN1

6CCSP2

7CCSN2

14VREF

16VR_ON

17CPGOOD

18VCLK

19ALERT

20VDIO

21VR_HOT

23GPGOOD

22

SLEWA

3

CIMON

30

GIMON

1

CTHE RM32GTHERM

2

COCP-I

31

GOCP-I

13

CF-IMAX

24

GF-IMAX

26

GVFB

25

GGFB29GCSP

28

GCSN

27

GCOM P

+

+

DAC0

+

+

Acs

Acs

8CCSP3

9CCSN3

+

Acs

?

Current

Sharing

Circuitry

Gm

A

10

CCOMP

Ramp

Comparator

SVID

Interface

DAC0

and

DAC1

OSR/USR

Phase

Manager

CPWM1

CPWM2

CPWM3

+

+

On-Time

1

On-Time

2

On-Time

3

CF-IMAX

ISHARE

CLK

CLK1

CLK2

CLK3

CPU

Logic Protection

and Status Circuitry

GPU

Logic Protection

and Status Circuitry

COCP

CPx

CVD

ISUM

IS1

IS2

IS3

+

+

Gm

A

GVD

DAC1

+

Acs

+

+

CLK

Smart

Driver

Smart

Driver

Error

Amplifier

Integrator

Error

Amplifier

Integrator

On-Time

GOCP

GPx

GVD

1GFx

Ramp

Comparator

43 V5DRV

46 CBST1

47 CDH1

42 PGND

39

CBST2

38 CDH2

45 CSW1

44 CDL1

40 CSW2

41 CDL2

36 CPWM3

35 CSKIP

33 GSKIP

34 GPWM

VBAT

GF-IMAX

DAC0

DAC1

IS3

IS2

IS1

+

+

+

Pad

GND15V3R348V5

GPWM

USR

OSR

UDG-11271

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

TYPICAL CHARACTERISTICS (TPS59641 ONLY)

www.ti.com

Figure 54. Startup to V

Voltage and ALERT Figure 55. Startup to V

BOOT

Voltage and CPGOOD,

BOOT

GPGOOD

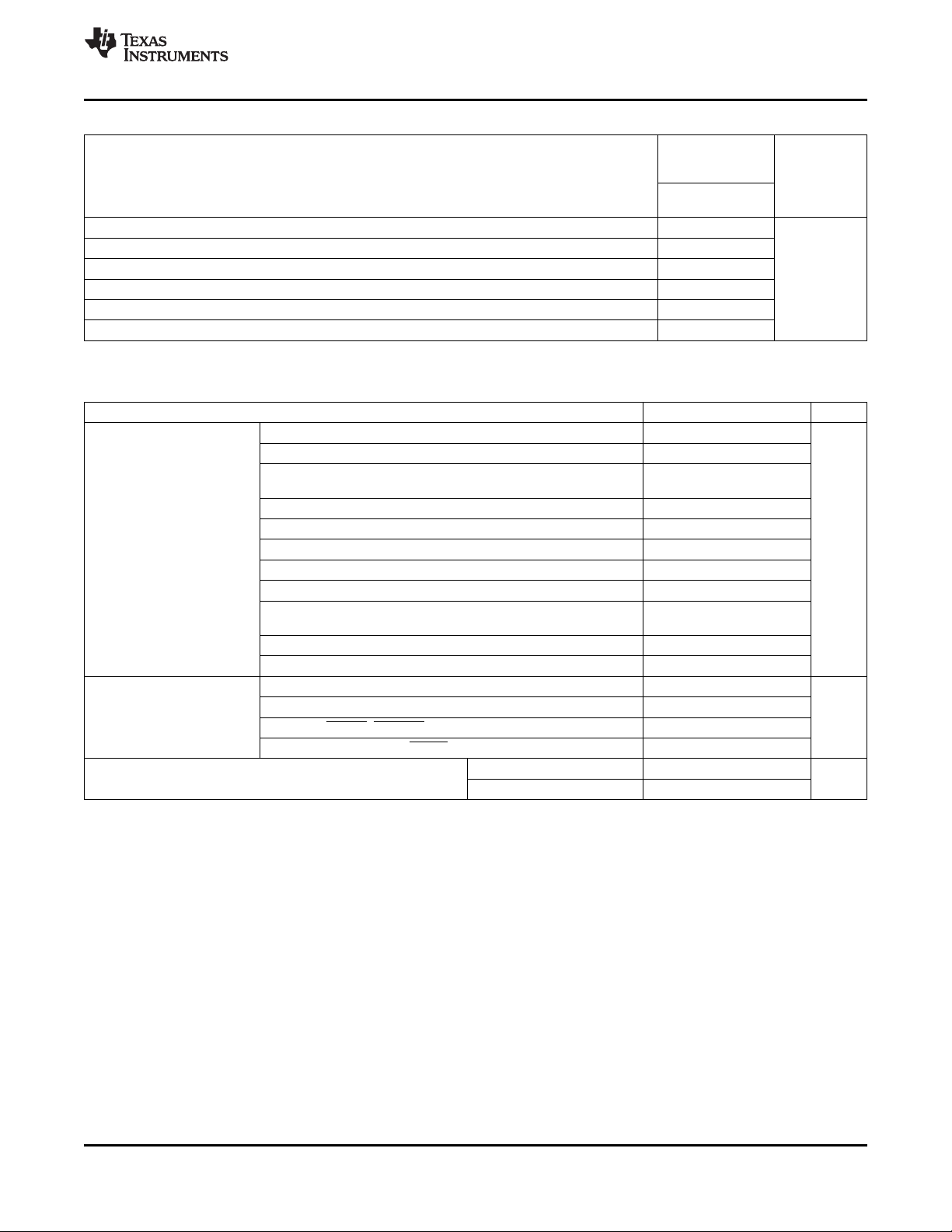

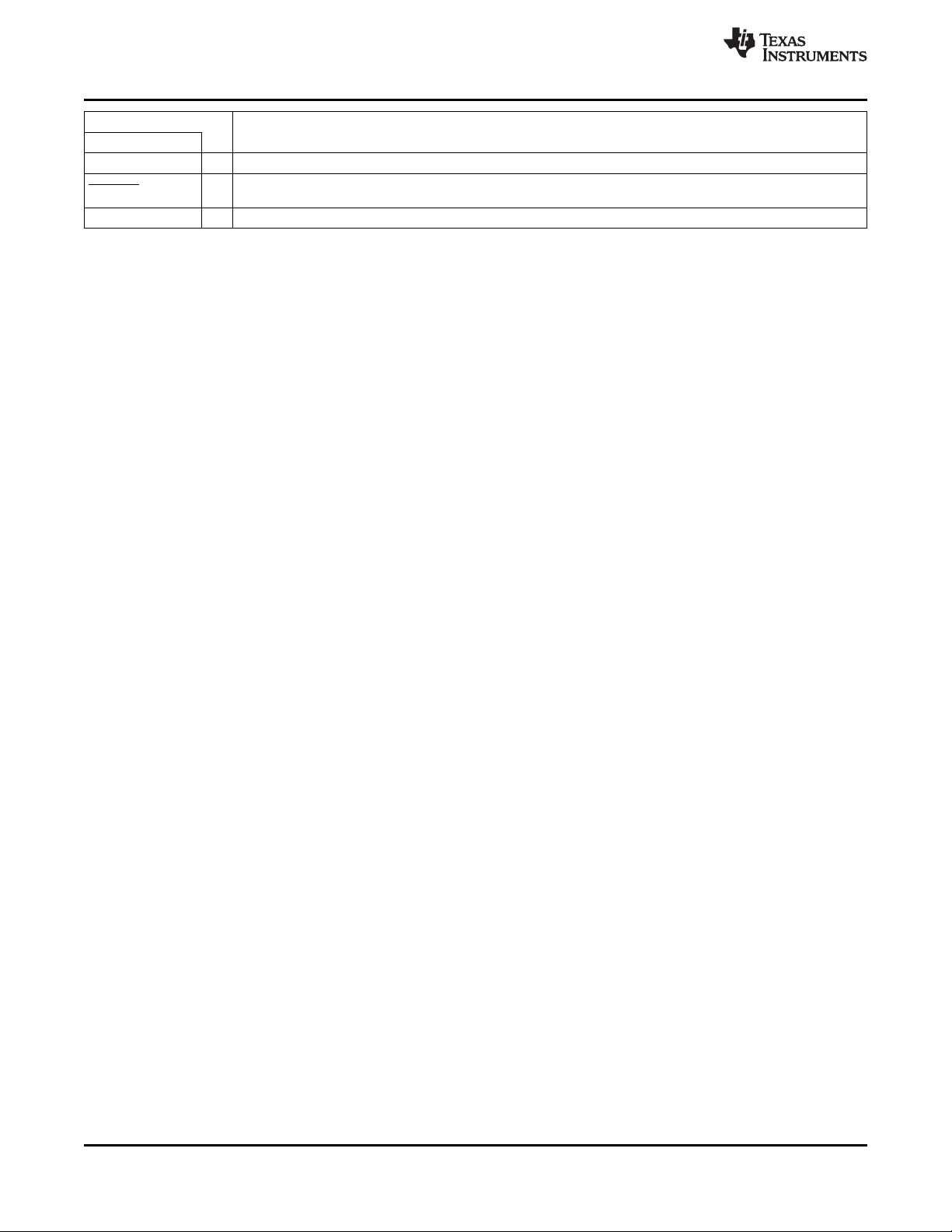

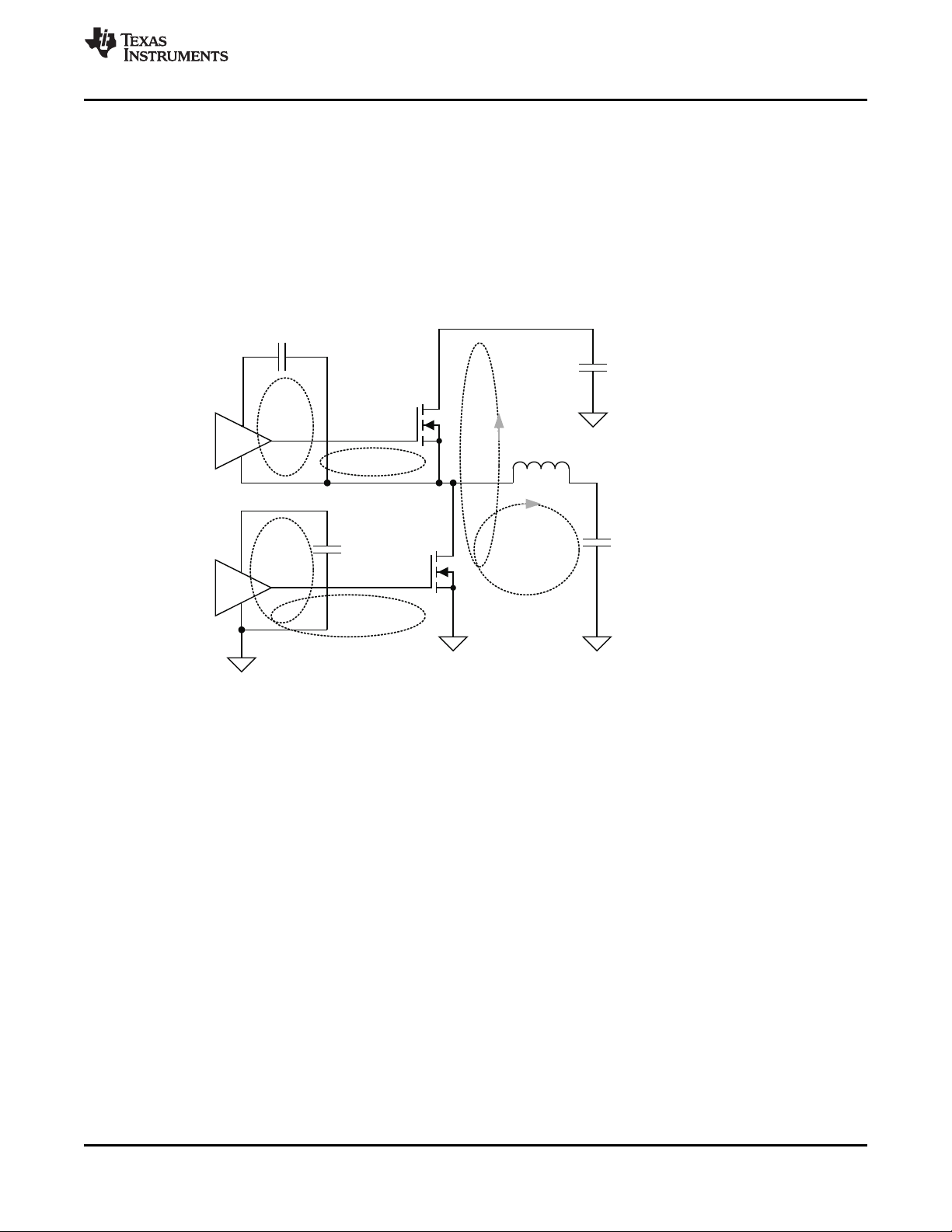

FUNCTIONAL BLOCK DIAGRAM

22 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

CPU_VSNS

CCSP3

CCSP2

CCSN1

CCSP1

COCP-I

GFX_VSNS

GSCP

GIMON

V5

GIMON

VREF

GPGOOD

VDIO

ALERT

CPGOOD

VR_ON

GPWM

VCLK

VREF

VREF

COCP

-I

VBAT

CSKIP

SVID:ALERT

SVID:CLK

VIN

CCSP

2

CCSN

1

3R3V

VREF

VR_HOT

VCLK

VREF

CPU_GSNS

VREF

CCSN2

CCSN3

GSKIP

CIMON

VDIO

CPWM

3

CIMON

VREF

SVID:DATA

VIN

CCSN

2

CCSP

1

GFX_GSNS

GSCN

GOCP-I

V5DRV

+

ALERT

V5DRV

V5

I_TDC

= 21.5A

I_TDC

= 52A

GOCP

-I

VREF

VREF

To CPU SVID

Loadline

= 1.9mohm

Frequency setting

= 300

kHz

I_cc_max

= 33A

I_CC_max

= 94A

I_DYN

_max

= 66A

2

1

VCC_CORE

VREF

VCCIO

VCCIO

GFX

: GT2

CPU

: QC

Min. Over Current Limit

= 112

A

2

1

Loadline

= 3.9mohm

Frequency setting

= 385

kHz

I_DYNAMIC

= 20.2A

Note

:

VR_HOT

, CPGOOD and GPGOOD are open drain outputs

.

If used

, they would need pull

-up resistors

.

Min. Over Current Limit

= 37A

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

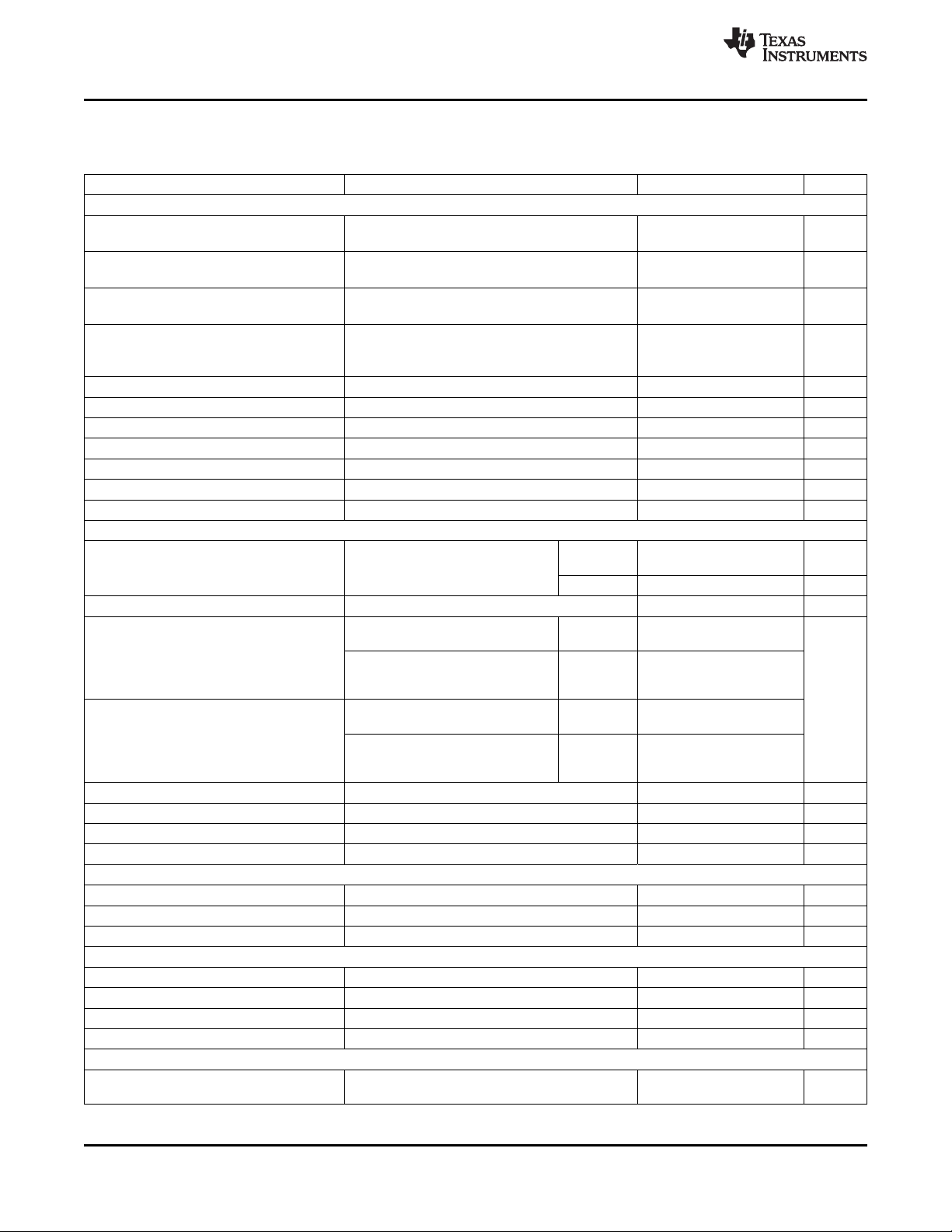

APPLICATION INFORMATION

Figure 56. Application for 3-Phase CPU, 1-Phase GPU with Inductor DCR Current Sense (Controller with

2 internal drivers, 1st and 2nd Phase CPU Power)

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 23

GSKIP

GPWM V5

GCSN

VIN

+

GCSP

21

VGFX_CORE

CSKIP

CPWM3 V5

VCC_CORE

GCSN

VIN

21

GCSP

+

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Figure 57. Application for 3-Phase CPU, 1-Phase GPU with Inductor DCR Current Sense continued

(External driver, 3rd Phase CPU Power)

www.ti.com

Figure 58. Application for 3-Phase CPU, 1-Phase GPU with Inductor DCR Current Sense continued

(External driver, GPU Power)

24 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

CPU_VSNS

CCSP2

CCSN1

CCSP1

COCP-I

V5

VREF

VDIO

ALERT

CPGOOD

VR_ON

VCLK

VREF

COCP

-I

VBAT

SVID:ALERT

SVID:CLK

VIN

CCSP

2

CCSN

1

3R3V

VREF

VR_HOT

VCLK

VREF

3R3V

CPU_GSNS

VREF

CCSN2

3R3V

CIMON

VDIO

CIMON

VREF

SVID:DATA

VIN

CCSN

2

CCSP

1

V5DRV

+

ALERT

V5DRV

V5

I_TDC

= 36A

To CPU SVID

Loadline

= 1.9mohm

Frequency setting

= 300

kHz

I_CC_max

= 53A

I_DYN

_max

= 43A

2

1

VCC_CORE

VREF

VCCIO

VCCIO

CPU

: SV

Note

:

VR_HOT and CPGOOD are open drain outputs

.

If used

, they would need pull

-up resistors

.

Min. Over Current Limit

= 65A

2

1

GFX

: External

. GPU Not used

Note

:

R19 = 39k (OSR

/USR

)

if 3x470

uF bulk is used

www.ti.com

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Figure 59. Application for Inductor DCR Current Sense Application Diagram for 2-Phase CPU and GPU

Disabled

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 25

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Table 1. Key External Component Recommendations

FUNCTION MANUFACTURER COMPONENT NUMBER

High-side MOSFET Texas Instruments CSD17302Q5A

Low-side MOSFET Texas Instruments CSD17303Q5

Powerblock MOSFET Texas Instruments CSD87350Q5D

Panasonic ETQP4LR36AFC

NEC-Tokin

Inductors

TOKO

ALPS GLMDR3601A

Panasonic EEFLXOD471R4

Bulk Output Capacitors Sanyo 2TPLF470M4E

KEMET T528Z477M2R5AT

Murata GRM21BR60J106KE19L

Ceramic Output Capacitors

NTC Thermistors

Sense Resistors

Murata GRM21BR60J226ME39L

Panasonic ECJ2FB0J106K

Panasonic ECJ2FB0J226K

Murata

Panasonic ERTJ1VS104F, ERTJ0ES104F

Vishay WSK0612L7500FEA

Stackpole CSSK0612FTL750

www.ti.com

MPCH1040LR36,

MPCG1040LR36

FDUE1040J-H-R36,

FCUL1040xxR36

NCP15WF104F03RC,

NCP18WF104F03RC

DETAILED DESCRIPTION

Functional Overview

The TPS51640A, TPS59640, and TPS59641 are a DCAP+™ mode adaptive on-time controllers.

The output voltage is set using a DAC that outputs a reference in accordance with the 8-bit VID code defined in

Intel IMVP-7 PWM Specification document. In adaptive on-time converters, the controller varies the on-time as a

function of input and output voltage to maintain a nearly constant frequency during steady-state conditions. In

conventional voltage-mode constant on-time converters, each cycle begins when the output voltage crosses to a

fixed reference level. However, in these devices, the cycle begins when the current feedback reaches an error

voltage level which corresponds to the amplified difference between the DAC voltage and the feedback output

voltage. In the case of two-phase or three-phase operation, the current feedback from all the phases is summed

up at the output of the internal current-sense amplifiers.

This approach has two advantages:

• The amplifier DC gain sets an accurate linear load-line; this is required for CPU core applications.

• The error voltage input to the PWM comparator is filtered to improve the noise performance.

In addition, the difference of the DAC-to-output voltage and the current feedback goes through an integrator to

give a more or less linear load-line even at light loads where the inductor current is in discontinuous conduction

mode (DCM).

In a steady-state condition, the phases of the TPS51640A, TPS59640, and TPS59641 switch 180°

phase-displacement for two-phase mode and 120° phase-displacement for three-phase mode. The phase

displacement is maintained both by the architecture (which does not allow both high-side gate drives to be on in

any condition except transients) and the current ripple (which forces the pulses to be spaced equally). The

controller forces current sharing adjusting the on-time of each phase. Current balancing requires no user

intervention, compensation, or extra components.

26 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

User Selections

After the 5-V and the 3.3-V power are applied to the controller, the controller must be enabled by the VR_ON

signal going high to the VCCIO logic level. At this time, the following information is latched and cannot be

changed anytime during operation. The ELECTRICAL CHARACTERISTICS table defines the values of each of

the selections.

• Operating Frequency. The resistor from CF-IMAX pin to GND sets the frequency of the CPU channel. The

resistor from GF-IMAX to GND sets the frequency of the GPU channel. See the ELECTRICAL

CHARACTERISTICS table for the resistor settings corresponding to each frequency selection. It is to be

noted that the operating frequency is a quasi-fixed frequency in the sense that the ON time is fixed based on

the input voltage (at the VBAT pin) and output voltage (set by VID). The OFF time varies based on various

factors such as load and power-stage components.

• Maximum Current Limit (I

voltage on the CF-IMAX pin. The I

the GF-IMAX pin.

• Overcurrent Protection (OCP) Level. The resistor from COCP-I to GND sets the OCP level of the CPU

channel. The resistor from GOCP-I to GND sets the OCP level of the GPU channel.

• Current Monitor (IMON) Gain and Voltage. The resistor from CIMON to COCP-I sets the CIMON gain and

the CIMON voltage for the CPU channel. The resistor from GIMON to GOCP-I sets the GIMON gain and the

GIMON voltage for the GPU channel.

• Overshoot Reduction (OSR) and Undershoot Reduction (USR) Levels. The resistor from the CSKIP pin

to GND sets the OSR and USR for the CPU channel. The resistor from the GSKIP pin to GND sets the OSR

and USR level for GPU channel. The OSR can be disabled for CPU and/or GPU by setting a voltage of

approximately 200 mV on the corresponding xSKIP pin. This is accomplished by connecting a resistor from

VREF to the xSKIP pin.

• Slew Rate. The SetVID-Fast slew rate is set by the voltage on the SLEWA pin. The rate is the same for both

the CPU and GPU channels. The SetVID-Slow is ¼ of the SetVID-Fast rate.

) Information. The I

CC(max)

CC(max)

CC(max)

information of the CPU, which can be set by the

information of the GPU channel, which can be set by the voltage on

SLUSAQ2 –JANUARY 2012

CPU

(Active Phases)

GPU

(Active Phases)

Table 2. Key Selections Summary

SELECTION

RESISTANCE (kΩ)

20 Lowest Lowest

24

30

39

56

75

100

150 Highest Highest

(1) See ELECTRICAL CHARACTERISTICS table for complete settings and values.

FREQUENCY OCP OSR / USR

Rising Rising Rising

(1)

Table 3. Active Channels and Phases

CCSP1 CCSN1 CCSP2 CCSN2 CCSP3 CCSN3 GCSP CGSN

3 CS CS CS CS CS CS n/a n/a

2 CS CS CS CS 3.3 V GND n/a n/a

1 CS CS 3.3 V GND GND GND n/a n/a

OFF 3.3 V GND GND GND GND GND n/a n/a

1 n/a n/a n/a n/a n/a n/a CS CS

OFF n/a n/a n/a n/a n/a n/a 3.3 V GND

Least overshoot,

least undershoot

Maximum overshoot,

maximum undershoot

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 27

SW_CLK

V

COMP

Phase 1

Phase 2

Phase 3

I

SUM

V

CORE

Time

UDG-11031

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

PWM Operation

Referring to the FUNCTIONAL BLOCK DIAGRAM and Figure 60, in continuous conduction mode, the converter

operates as shown in Figure 60.

www.ti.com

Figure 60. D-CAP+ Mode Basic Waveforms

Starting with the condition that the hig-side FETs are off and the low-side FETs are on, the summed current

feedback (I

) is higher than the error amplifier output (V

SUM

COMP

). I

falls until it reaches the V

SUM

COMP

level, which

contains a component of the output ripple voltage. The PWM comparator senses where the two waveform values

cross and triggers the on-time generator. This generates the internal SW_CLK. Each SW_CLK corresponds to

one switching ON pulse for one phase.

During single-phase operation, every SW_CLK generates a switching pulse on the same phase. Also, I

SUM

voltage corresponds to just a single-phase inductor current.

During multi-phase operation, the SW_CLK is distributed to each of the phases in a cycle. Using the summed

inductor current and then cyclically distributing the ON-pulses to each phase automatically yields the required

interleaving of 360/N, where N is the number of phases.

Current Sensing

The TPS51640A, TPS59640 and TPS59641 provide independent channels of current feedback for every phase.

This increases the system accuracy and reduces the dependence of circuit performance on layout compared to

an externally summed architecture. The current sensing topology can be Inductor DCR Sensing, which yields the

best efficiency, or Resistor Current Sensing, which provides the most accuracy across wide temperature range.

DCR sensing can be optimized by using a NTC thermistor to reduce the variation of current sense with

temperature.

The pins CCSP1, CCSN1, CCSP2, CCSN2 and CCSP3, CCSN3 are used for the three phases of the CPU

channel. The pins GCSP and GCSN are used for the single-phase GPU channel.

28 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

V

DROOP

V

VID

V

DROOP

= RLLx I

CC

Slope of Loadline R

LL

I

CC

UDG-11032

( )

´ ´

= ´ =

´

CS CC

CS eff

DROOP LL CC

DROOP M

R A I

V R I

R G

www.ti.com

Setting the Load-line (DROOP)

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Figure 61. Load Line

where

• ACS is the gain of the current sense amplifier

• R

is the effective current sense resistance, whether a sense resistor or inductor DCR is used

CS(eff)

• ICCis the load current

• R

is the value of resistor from the DROOP pin to VREF

DROOP

• GMis the gain of the droop amplifier (1)

Load Transients

When there is a sudden load increase, the output voltage immediately drops. This is reflected as a rising voltage

on the COMP pin. This forces the PWM pulses to come in sooner and more frequent which causes the inductor

current to rapidly increase. As the inductor current reaches the new load current, a steady-state operating

condition is reached and the PWM switching resumes the steady-state frequency.

When there is a sudden load release, the output voltage rises. This is reflected as a falling voltage on the COMP

pin. This delays the PWM pulses until the inductor current reaches the new load current level. At that point,

switching resumes and steady-state switching continues.

For simplicity, neither Figure 62, nor Figure 63 show the ripple on the Output V

nor the COMP waveform.

CORE

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 29

LOAD

V

CORE

I

SUM

COMP

SW_CLK

Phase 1

Phase 2

Phase 3

UDG-11034

LOAD

V

CORE

I

SUM

COMP

SW_CLK

Phase 1

Phase 2

Phase 3

Time

UDG-11033

UDG-11035

+ 10.8 V –

12 V

L

– 1.2 V +

1.2 V

C

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Figure 62. Operating Waveforms During Load Figure 63. needs a title

Transient

Overshoot Reduction (OSR)

In low duty-cycle synchronous buck converters, an overshoot condition results from the output inductor having a

too little voltage (V

In Figure 64, a single phase converter is shown for simplicity. In an ideal converter, with typical input voltage of

12 V and 1.2-V output, the inductor has 10.8 V (12 V – 1.2 V) to respond to a transient load increase, but only

1.2 V with which to respond once the load releases.

) with which to respond to a transient load release.

CORE

www.ti.com

Figure 64. Synchronous Converter

When the overshoot reduction feature is enabled, the output voltage increases beyond a value that corresponds

to a voltage difference between the ISUM voltage and the COMP voltage, exceeding the specified OSR voltage

specified in the ELECTRICAL CHARACTERISTICS. At that instant, the low-side drivers are turned OFF. When

the low-side driver is turned OFF, the energy in the inductor is partially dissipated by the body diodes. As the

overshoot reduces, the low-side drivers are turned ON again.

Figure 65 shows the overshoot without OSR. Figure 66 shows the overshoot with OSR. The overshoot reduces

by approximately 23 mV. This shows that reduced output capacitance can be used while continuing to meet the

specification. Note the low-side driver turning OFF briefly during the overshoot.

30 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

Figure 65. 43-A Load Transient Release Without Figure 66. 43-A Load Transient Release With OSR

OSR Enabled. Enabled

Undershoot Reduction (USR)

When the transient load increase becomes quite large, it becomes difficult to meet the energy demanded by the

load especially at lower input voltages. Then it is necessary to quickly increase the energy tin the inductors

during the transient load increase. This is achieved in these devices by enabling pulse overlapping. In order to

maintain the interleaving of the multi-phase configuration and yet be able to have pulse-overlapping during

load-insertion, the undershoot reduction (USR) mode is entered only when necessary. This mode is entered

when the difference between COMP voltage and ISUM voltage exceeds the USR voltage level specified in the

ELECTRICAL CHARACTERISTICS table.

Figure 67 shows the performance with undershoot reduction. Figure 68 shows the performance without

undershoot reduction and that it is possible to eliminate undershoot by enabling the undershoot reduction. This

allows reduced output capacitance to be used and still meet the specification.

When the transient condition is over, the interleaving of the phases is resumed. For Figure 67, note the

overlapping pulses for Phase 1 and Phase 2 with USR enabled.

SLUSAQ2 –JANUARY 2012

Figure 67. Performance for a 43-A Load Transient Figure 68. Performance for a 43-A Load Transient

Release Without USR Enabled Release With USR Enabled

A single-phase GPU operates in a similar way, but instead of pulse-overlap in multi-phase CPU, there is pulse

stretching to provide the needs of the transient load increase when USR is enabled.

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 31

+

37VBAT

4CCSP1

5CCSN1

Current

Amplifier

5 ms

Filter

I

AVG

+

V

DAC

R

T(on)

C

T(on)

PWM1

+

K x (I1-I

AVG

)

+

7CCSP2

6CCSN2

Current

Amplifier

5 ms

Filter

I

AVG

+

V

DAC

R

T(on)

C

T(on)

PWM2

+

K x (I2-I

AVG

)

Averaging

Circuit

I

AVG

+

8CCSP3

9CCSN3

Current

Amplifier

5 ms

Filter

I

AVG

+

V

DAC

R

T(on)

C

T(on)

PWM3

+

K x (I3-I

AVG

)

UDG-11036

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

AutoBalance™ Current Sharing

The basic mechanism for current sharing is to sense the average phase current, then adjust the pulse width of

each phase to equalize the current in each phase. (See Figure 69.)

The PWM comparator (not shown) starts a pulse when the feedback voltage meets the reference. The VBAT

voltage charges C

reference, normally the DAC voltage (V

The circuit operates in the following fashion, using Figure 69 as the block diagram. First assume that the 5-µs

averaged value of I1 = I2 = I3. In this case, the PWM modulator terminates at V

is delivered to the system. If instead, I1 > I

Phase 1 is shortened, reducing the current in Phase 1 to compensate. If I1 < I

produced, again compensating on a pulse-by-pulse basis.

t(ON)

through R

. The pulse is terminated when the voltage at C

t(ON)

DAC

).

, then an offset is subtracted from V

AVG

matches the t

t(ON)

, and the normal pulse width

DAC

, and the pulse width for

DAC

, then a longer pulse is

AVG

www.ti.com

(ON)

Figure 69. Schematic Representation of AutoBalance Current Sharing

Dynamic VID and Power-State Changes

In IMVP-7, there are 3 basic types of VID changes:

• SetVID-Fast

• SetVID-Slow

• SetVID-Decay

SetVID-Fast change and a SetVID-Slow change automatically puts the power state in PS0. A SetVID-Decay

change automatically puts the power state in PS2.

32 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

The CPU operates in the maximum phase mode when it is in PS0. This means when the CPU channel of the

controller is configured as 3-phase, all 3 phases are active in PS0. When configured in 2-phase mode, the two

phases are active in PS0. But in PS1, PS2 and PS3, the operation is in single-phase mode. Additionally, the

CPU channel in PS0 mode operates in forced continuous conduction mode (FCCM). But in PS1, PS2 and PS3,

the CPU channel operates in diode emulation (DE) mode for additional power savings and higher efficiency.

The single-phase GPU section always operates in diode emulation (DE) mode in all PS states.

The slew rate for a SetVID-Fast is the slew rate set at the SLEWA pin. This slew rate is defined in the

ELECTRICAL CHARACTERISTICS table. The SetVID-Slow is ¼ of the SetVID-Fast slew rate. On a

SetVID-Decay the output voltage decays by the rate of the load current or 1/8 of the slew rate whichever is

slower.

Additionally, on a SetVID-Fast change for a VID-up transition, the gain of the gMamplifier is increased to speed

up the response of the output voltage to meet the Intel timing requirement. So, it is possible to observe an

overshoot at the output voltage on a VID-up transition. This overshoot is allowed by the Intel specification.

XXX

Table 4. VID (continued)

Table 4. VID

VID VID VID VID VID VID VID VID

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0 00 0.000

0 0 0 0 0 0 0 1 01 0.250

0 0 0 0 0 0 1 0 02 0.255

0 0 0 0 0 0 1 1 03 0.260

0 0 0 0 0 1 0 0 04 0.265

0 0 0 0 0 1 0 1 05 0.270

0 0 0 0 0 1 1 0 06 0.275

0 0 0 0 0 1 1 1 07 0.280

0 0 0 0 1 0 0 0 08 0.285

0 0 0 0 1 0 0 1 09 0.290

0 0 0 0 1 0 1 0 0A 0.295

0 0 0 0 1 0 1 1 0B 0.300

0 0 0 0 1 1 0 0 0C 0.305

0 0 0 0 1 1 0 1 0D 0.310

0 0 0 0 1 1 1 0 0E 0.315

0 0 0 0 1 1 1 1 0F 0.320

0 0 0 1 0 0 0 0 10 0.325

0 0 0 1 0 0 0 1 11 0.330

0 0 0 1 0 0 1 0 12 0.335

0 0 0 1 0 0 1 1 13 0.340

0 0 0 1 0 1 0 0 14 0.345

0 0 0 1 0 1 0 1 15 0.350

0 0 0 1 0 1 1 0 16 0.355

0 0 0 1 0 1 1 1 17 0.360

0 0 0 1 1 0 0 0 18 0.365

0 0 0 1 1 0 0 1 19 0.370

0 0 0 1 1 0 1 0 1A 0.375

0 0 0 1 1 0 1 1 1B 0.380

0 0 0 1 1 1 0 0 1C 0.385

0 0 0 1 1 1 0 1 1D 0.390

0 0 0 1 1 1 1 0 1E 0.395

0 0 0 1 1 1 1 1 1F 0.400

HEX V

DAC

0 0 1 0 0 0 0 0 20 0.405

0 0 1 0 0 0 0 1 21 0.410

0 0 1 0 0 0 1 0 22 0.415

0 0 1 0 0 0 1 1 23 0.420

0 0 1 0 0 1 0 0 24 0.425

0 0 1 0 0 1 0 1 25 0.430

0 0 1 0 0 1 1 0 26 0.435

0 0 1 0 0 1 1 1 27 0.440

0 0 1 0 1 0 0 0 28 0.445

0 0 1 0 1 0 0 1 29 0.450

0 0 1 0 1 0 1 0 2A 0.455

0 0 1 0 1 0 1 1 2B 0.460

0 0 1 0 1 1 0 0 2C 0.465

0 0 1 0 1 1 0 1 2D 0.470

0 0 1 0 1 1 1 0 2E 0.475

0 0 1 0 1 1 1 1 2F 0.480

0 0 1 1 0 0 0 0 30 0.485

0 0 1 1 0 0 0 1 31 0.490

0 0 1 1 0 0 1 0 32 0.495

0 0 1 1 0 0 1 1 33 0.500

0 0 1 1 0 1 0 0 34 0.505

0 0 1 1 0 1 0 1 35 0.510

0 0 1 1 0 1 1 0 36 0.515

0 0 1 1 0 1 1 1 37 0.520

0 0 1 1 1 0 0 0 38 0.525

0 0 1 1 1 0 0 1 39 0.530

0 0 1 1 1 0 1 0 3A 0.535

0 0 1 1 1 0 1 1 3B 0.540

0 0 1 1 1 1 0 0 3C 0.545

0 0 1 1 1 1 0 1 3D 0.550

0 0 1 1 1 1 1 0 3E 0.555

0 0 1 1 1 1 1 1 3F 0.560

0 1 0 0 0 0 0 0 40 0.565

0 1 0 0 0 0 0 1 41 0.570

0 1 0 0 0 0 1 0 42 0.575

SLUSAQ2 –JANUARY 2012

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 33

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Table 4. VID (continued) Table 4. VID (continued)

0 1 0 0 0 0 1 1 43 0.580 0 1 1 1 0 0 1 1 73 0.820

0 1 0 0 0 1 0 0 44 0.585 0 1 1 1 0 1 0 0 74 0.825

0 1 0 0 0 1 0 1 45 0.590 0 1 1 1 0 1 0 1 75 0.830

0 1 0 0 0 1 1 0 46 0.595 0 1 1 1 0 1 1 0 76 0.835

0 1 0 0 0 1 1 1 47 0.600 0 1 1 1 0 1 1 1 77 0.840

0 1 0 0 1 0 0 0 48 0.605 0 1 1 1 1 0 0 0 78 0.845

0 1 0 0 1 0 0 1 49 0.610 0 1 1 1 1 0 0 1 79 0.850

0 1 0 0 1 0 1 0 4A 0.615 0 1 1 1 1 0 1 0 7A 0.855

0 1 0 0 1 0 1 1 4B 0.620 0 1 1 1 1 0 1 1 7B 0.860

0 1 0 0 1 1 0 0 4C 0.625 0 1 1 1 1 1 0 0 7C 0.865

0 1 0 0 1 1 0 1 4D 0.630 0 1 1 1 1 1 0 1 7D 0.870

0 1 0 0 1 1 1 0 4E 0.635 0 1 1 1 1 1 1 0 7E 0.875

0 1 0 0 1 1 1 1 4F 0.640 0 1 1 1 1 1 1 1 7F 0.880

0 1 0 1 0 0 0 0 50 0.645 1 0 0 0 0 0 0 0 80 0.885

0 1 0 1 0 0 0 1 51 0.650 1 0 0 0 0 0 0 1 81 0.890

0 1 0 1 0 0 1 0 52 0.655 1 0 0 0 0 0 1 0 82 0.895

0 1 0 1 0 0 1 1 53 0.660 1 0 0 0 0 0 1 1 83 0.900

0 1 0 1 0 1 0 0 54 0.665 1 0 0 0 0 1 0 0 84 0.905

0 1 0 1 0 1 0 1 55 0.670 1 0 0 0 0 1 0 1 85 0.910

0 1 0 1 0 1 1 0 56 0.675 1 0 0 0 0 1 1 0 86 0.915

0 1 0 1 0 1 1 1 57 0.680 1 0 0 0 0 1 1 1 87 0.920

0 1 0 1 1 0 0 0 58 0.685 1 0 0 0 1 0 0 0 88 0.925

0 1 0 1 1 0 0 1 59 0.690 1 0 0 0 1 0 0 1 89 0.930

0 1 0 1 1 0 1 0 5A 0.695 1 0 0 0 1 0 1 0 8A 0.935

0 1 0 1 1 0 1 1 5B 0.700 1 0 0 0 1 0 1 1 8B 0.940

0 1 0 1 1 1 0 0 5C 0.705 1 0 0 0 1 1 0 0 8C 0.945

0 1 0 1 1 1 0 1 5D 0.710 1 0 0 0 1 1 0 1 8D 0.950

0 1 0 1 1 1 1 0 5E 0.715 1 0 0 0 1 1 1 0 8E 0.955

0 1 0 1 1 1 1 1 5F 0.720 1 0 0 0 1 1 1 1 8F 0.960

0 1 1 0 0 0 0 0 60 0.725 1 0 0 1 0 0 0 0 90 0.965

0 1 1 0 0 0 0 1 61 0.730 1 0 0 1 0 0 0 1 91 0.970

0 1 1 0 0 0 1 0 62 0.735 1 0 0 1 0 0 1 0 92 0.975

0 1 1 0 0 0 1 1 63 0.740 1 0 0 1 0 0 1 1 93 0.980

0 1 1 0 0 1 0 0 64 0.745 1 0 0 1 0 1 0 0 94 0.985

0 1 1 0 0 1 0 1 65 0.750 1 0 0 1 0 1 0 1 95 0.990

0 1 1 0 0 1 1 0 66 0.755 1 0 0 1 0 1 1 0 96 0.995

0 1 1 0 0 1 1 1 67 0.760 1 0 0 1 0 1 1 1 97 1.000

0 1 1 0 1 0 0 0 68 0.765 1 0 0 1 1 0 0 0 98 1.005

0 1 1 0 1 0 0 1 69 0.770 1 0 0 1 1 0 0 1 99 1.010

0 1 1 0 1 0 1 0 6A 0.775 1 0 0 1 1 0 1 0 9A 1.015

0 1 1 0 1 0 1 1 6B 0.780 1 0 0 1 1 0 1 1 9B 1.020

0 1 1 0 1 1 0 0 6C 0.785 1 0 0 1 1 1 0 0 9C 1.025

0 1 1 0 1 1 0 1 6D 0.790 1 0 0 1 1 1 0 1 9D 1.030

0 1 1 0 1 1 1 0 6E 0.795 1 0 0 1 1 1 1 0 9E 1.035

0 1 1 0 1 1 1 1 6F 0.800 1 0 0 1 1 1 1 1 9F 1.040

0 1 1 1 0 0 0 0 70 0.805 1 0 1 0 0 0 0 0 A0 1.045

0 1 1 1 0 0 0 1 71 0.810 1 0 1 0 0 0 0 1 A1 1.050

0 1 1 1 0 0 1 0 72 0.815 1 0 1 0 0 0 1 0 A2 1.055

www.ti.com

34 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated

TPS51640A, TPS59640, TPS59641

www.ti.com

Table 4. VID (continued) Table 4. VID (continued)

1 0 1 0 0 0 1 1 A3 1.060 1 1 0 1 0 0 1 1 D3 1.300

1 0 1 0 0 1 0 0 A4 1.065 1 1 0 1 0 1 0 0 D4 1.305

1 0 1 0 0 1 0 1 A5 1.070 1 1 0 1 0 1 0 1 D5 1.310

1 0 1 0 0 1 1 0 A6 1.075 1 1 0 1 0 1 1 0 D6 1.315

1 0 1 0 0 1 1 1 A7 1.080 1 1 0 1 0 1 1 1 D7 1.320

1 0 1 0 1 0 0 0 A8 1.085 1 1 0 1 1 0 0 0 D8 1.325

1 0 1 0 1 0 0 1 A9 1.090 1 1 0 1 1 0 0 1 D9 1.330

1 0 1 0 1 0 1 0 AA 1.095 1 1 0 1 1 0 1 0 DA 1.335

1 0 1 0 1 0 1 1 AB 1.100 1 1 0 1 1 0 1 1 DB 1.340

1 0 1 0 1 1 0 0 AC 1.105 1 1 0 1 1 1 0 0 DC 1.345

1 0 1 0 1 1 0 1 AD 1.110 1 1 0 1 1 1 0 1 DD 1.350

1 0 1 0 1 1 1 0 AE 1.115 1 1 0 1 1 1 1 0 DE 1.355

1 0 1 0 1 1 1 1 AF 1.120 1 1 0 1 1 1 1 1 DF 1.360

1 0 1 1 0 0 0 0 B0 1.125 1 1 1 0 0 0 0 0 E0 1.365

1 0 1 1 0 0 0 1 B1 1.130 1 1 1 0 0 0 0 1 E1 1.370

1 0 1 1 0 0 1 0 B2 1.135 1 1 1 0 0 0 1 0 E2 1.375

1 0 1 1 0 0 1 1 B3 1.140 1 1 1 0 0 0 1 1 E3 1.380

1 0 1 1 0 1 0 0 B4 1.145 1 1 1 0 0 1 0 0 E4 1.385

1 0 1 1 0 1 0 1 B5 1.150 1 1 1 0 0 1 0 1 E5 1.390

1 0 1 1 0 1 1 0 B6 1.155 1 1 1 0 0 1 1 0 E6 1.395

1 0 1 1 0 1 1 1 B7 1.160 1 1 1 0 0 1 1 1 E7 1.400

1 0 1 1 1 0 0 0 B8 1.165 1 1 1 0 1 0 0 0 E8 1.405

1 0 1 1 1 0 0 1 B9 1.170 1 1 1 0 1 0 0 1 E9 1.410

1 0 1 1 1 0 1 0 BA 1.175 1 1 1 0 1 0 1 0 EA 1.415

1 0 1 1 1 0 1 1 BB 1.180 1 1 1 0 1 0 1 1 EB 1.420

1 0 1 1 1 1 0 0 BC 1.185 1 1 1 0 1 1 0 0 EC 1.425

1 0 1 1 1 1 0 1 BD 1.190 1 1 1 0 1 1 0 1 ED 1.430

1 0 1 1 1 1 1 0 BE 1.195 1 1 1 0 1 1 1 0 EE 1.435

1 0 1 1 1 1 1 1 BF 1.200 1 1 1 0 1 1 1 1 EF 1.440

1 0 0 0 0 0 0 C0 1.205 1 1 1 1 0 0 0 0 F0 1.445

1 1 0 0 0 0 0 1 C1 1.210 1 1 1 1 0 0 0 1 F1 1.450

1 1 0 0 0 0 1 0 C2 1.215 1 1 1 1 0 0 1 0 F2 1.455

1 1 0 0 0 0 1 1 C3 1.220 1 1 1 1 0 0 1 1 F3 1.460

1 1 0 0 0 1 0 0 C4 1.225 1 1 1 1 0 1 0 0 F4 1.465

1 1 0 0 0 1 0 1 C5 1.230 1 1 1 1 0 1 0 1 F5 1.470

1 1 0 0 0 1 1 0 C6 1.235 1 1 1 1 0 1 1 0 F6 1.475

1 1 0 0 0 1 1 1 C7 1.240 1 1 1 1 0 1 1 1 F7 1.480

1 1 0 0 1 0 0 0 C8 1.245 1 1 1 1 1 0 0 0 F8 1.485

1 1 0 0 1 0 0 1 C9 1.250 1 1 1 1 1 0 0 1 F9 1.490

1 1 0 0 1 0 1 0 CA 1.255 1 1 1 1 1 0 1 0 FA 1.495

1 1 0 0 1 0 1 1 CB 1.260 1 1 1 1 1 0 1 1 FB 1.500

1 1 0 0 1 1 0 0 CC 1.265 1 1 1 1 1 1 0 0 FC 1.505

1 1 0 0 1 1 0 1 CD 1.270 1 1 1 1 1 1 0 1 FD 1.510

1 1 0 0 1 1 1 0 CE 1.275 1 1 1 1 1 1 1 0 FE 1.515

1 1 0 0 1 1 1 1 CF 1.280 1 1 1 1 1 1 1 1 FF 1.520

1 1 0 1 0 0 0 0 D0 1.285

1 1 0 1 0 0 0 1 D1 1.290

1 1 0 1 0 0 1 0 D2 1.295

SLUSAQ2 –JANUARY 2012

Copyright © 2012, Texas Instruments Incorporated Submit Documentation Feedback 35

TPS51640A, TPS59640, TPS59641

SLUSAQ2 –JANUARY 2012

Gate Driver

The TPS51640A, TPS59640, and TPS59641 incorporate two internal strong, high-performance gate drives with

adaptive cross-conduction protection. These drivers are for two phases in the CPU channel. The third phase of

the CPU and the single-phase GPU channel require external drivers.