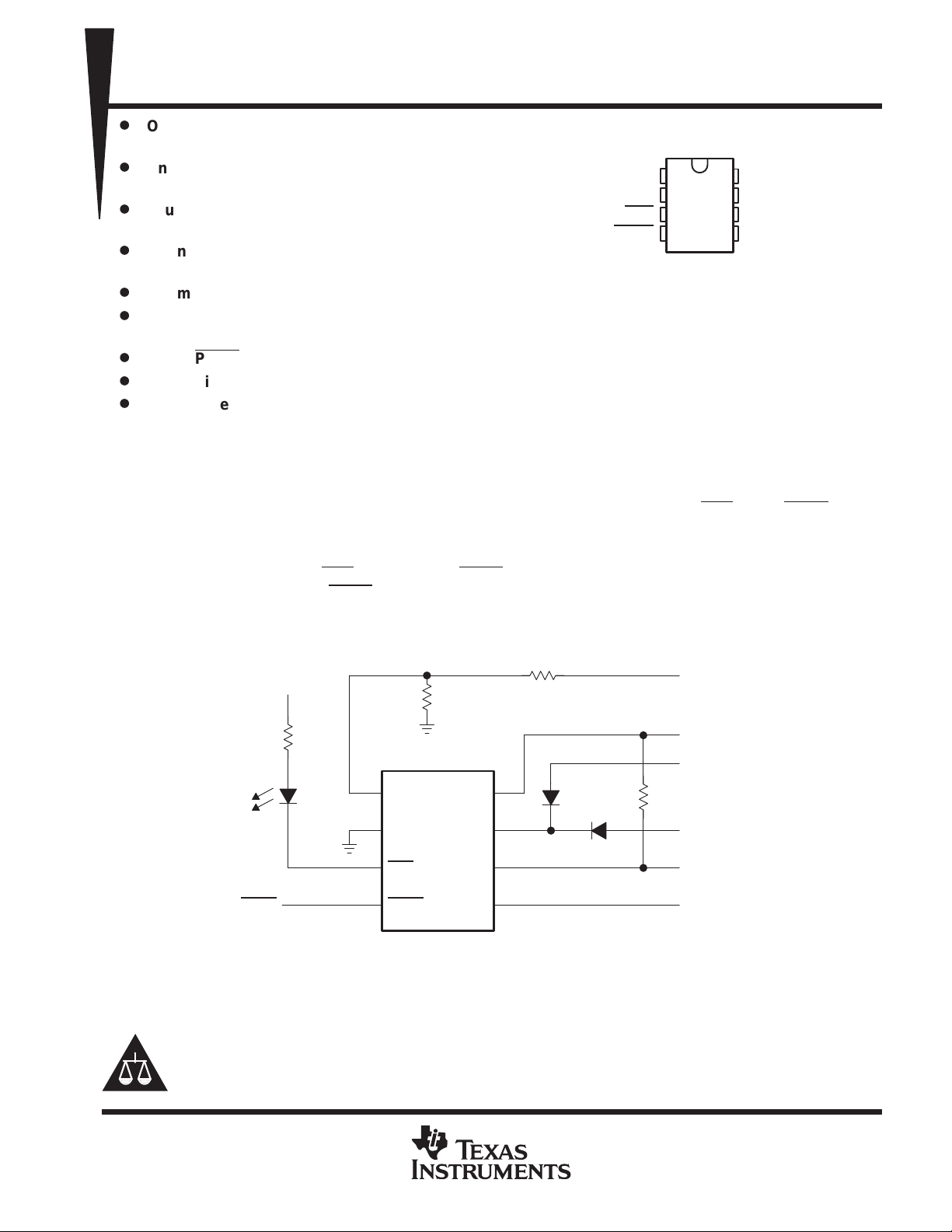

TPS5510

3-CHANNEL POWER SUPPLY SUPERVISOR

SLVS168 – JULY 1998

D

Over Voltage Protection and Lock Out for

5 V, 3.3 V, and 12 V

D

Under Voltage Protection and Lock Out for

5 V and 3.3 V

D

Fault Protection Output with Open Drain

Output Stage

D

Open Drain Power Good Output Signal for

D OR P PACKAGE

(TOP VIEW)

PGI

1

GND

FPO

PSON

2

3

4

PGO

8

V

7

CC

VS5

6

5

VS33

Power Good Input, 5 V and 3.3 V

D

300 ms Power Good Delay

D

75 ms Delay for 5-V and 3.3-V Short-Circuit

Turn On Protection

D

38 ms PSON Control Debounce

D

73 µs Width Noise Deglitches

D

Wide Power Supply Voltage Range

from 4 V to 15 V

description

The TPS5510 is designed to minimize external components of personal computer switching power supply

systems. It provides protection circuits, power good indicator, fault protection output (FPO

OVP (Over Voltage Protection) monitors 5 V, 3.3 V, and 12 V (12 V OV detects via V

Voltage Protection) monitors 5 V and 3.3 V. When an OV or UV condition is detected, the PGO (power good

output) is asserted low and FPO

will be enabled 75 ms after PSON

is latched high. PSON from low to high resets the protection latch. UVP function

is set low and debounced.

), and a PSON control.

terminal). UVP (Under

CC

Power good feature monitors PGI, 5 V and 3.3 V and issues a power good signal when they are ready.

The TPS5510 is characterised for operation from T

5 V

SB

TPS5510

1

PGI

2

GND

3

FPO

PSON

4

PSON

= –40°C to 125°C junction temperature.

J

0.5 V

Drop

PGO

V

CC

VS5

VS33

8

7

6

5

PGI

PGO

12 V

V

SB

5 V

3.3 V

Figure 1. TPS5510 Typical Application

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1998, Texas Instruments Incorporated

1

TPS5510

3-CHANNEL POWER SUPPLY SUPERVISOR

SLVS168 – JULY 1998

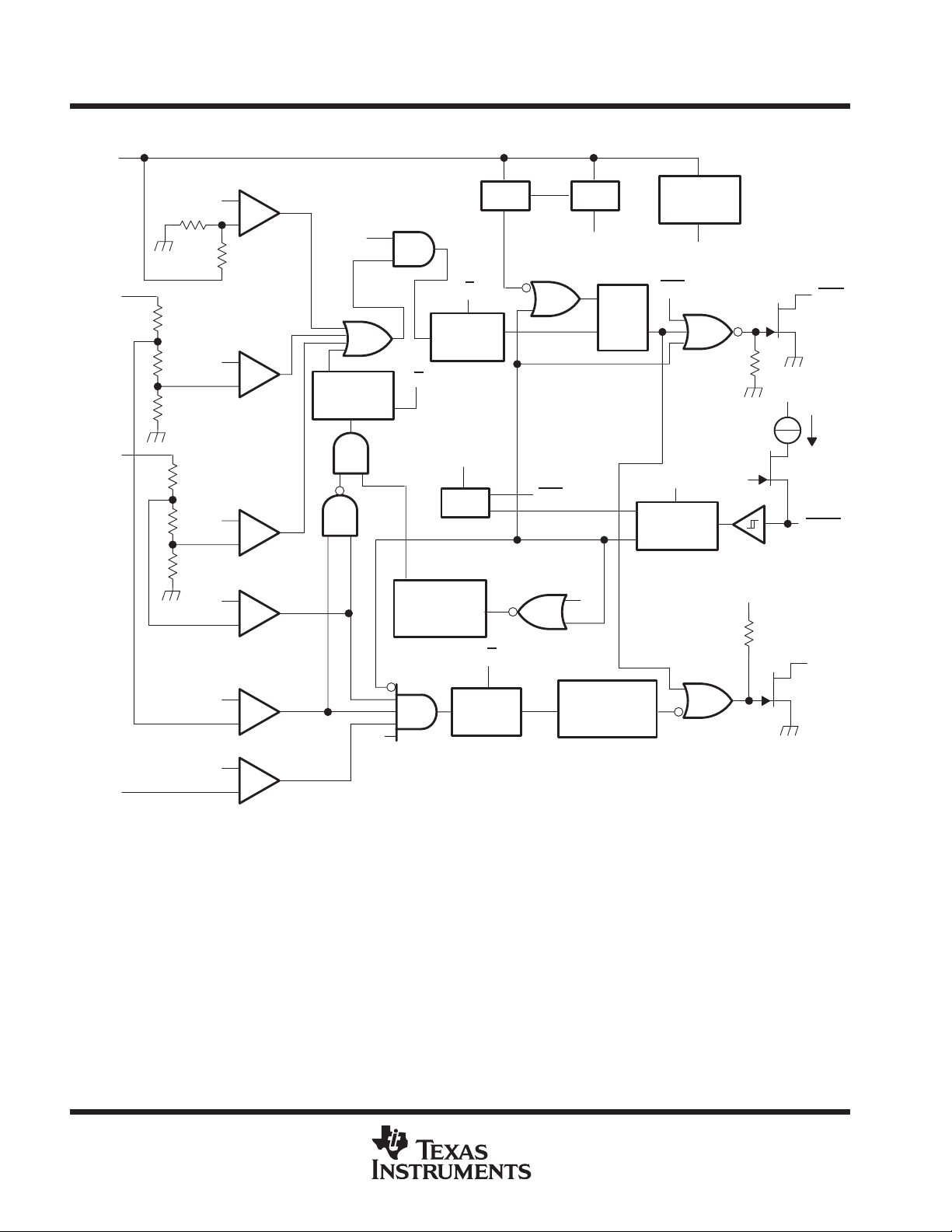

functional block diagram

V

CC

VS5

VS33

Vref

Vref

RI = 100 kΩ

Vref

RI = 100 kΩ

Vref

Vref

–

+

RI = 200 kΩ

5 OV

–

+

3.3 OV

–

+

–

3.3 UV

+

–

5 UV

+

12 OV

RST

73 µs

Debounce

R

75 ms

Delay

Counter

Reset

R

73 µs

Debounce

Reset

OSC

EN

73 µs

Debounce

POR Vreg

V

CCI

R

Derminent

RTT

RST

R

R

EN

= 3.6 V

R

S

Reset

Latch

300 ms

Delay

Counter

RTT

Q

Reset

38 ms

Debounce

Bandgap

Reference

Vref

1.192 V

V

150 µA

CCI

V

V

CC

Pull-High

Resistor

FPO

CC

PSON

PGO

RST

Vref

PGI

2

–

+

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I/O

DESCRIPTION

Output voltage, V

Output sink current, I

3-CHANNEL POWER SUPPLY SUPERVISOR

Terminal Functions

TERMINAL

NAME NO.

VS33 5 I 3.3 V over/under voltage protection input pin

VS5 6 I 5 V over/under voltage protection input pin

GND 2 Ground

FPO 3 O Inverted fault protection output, open drain output stage

PGI 1 I Power good input signal pin

PGO 8 O Power good output signal pin, open drain output stage

PSON 4 I ON/OFF control input pin

V

CC

7 I Supply voltage/12 V over voltage protection input pin

DISSIPATION RATING TABLE

PACKAGE

P 1092 mW 8.74 mW/°C 218 mW

D 730 mW 5.84 mW/°C 146 mW

TA ≤ 25°C

POWER RATING

OPERATING FACTOR

ABOVE TA = 25°C

TPS5510

SLVS168 – JULY 1998

TA = 125°C

POWER RATING

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

Supply voltage, V

Output voltage, V

Output voltage, V

Supply current, I

, (see Note1) 16 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

(FPO) 16 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

(PGO) 8 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

†

1 mA

Continuous total power dissipation see Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating junction temperature range, T

Storage temperature range, T

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

–40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

J

Lead temperature, 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are with respect to the device GND terminal.

recommended operating conditions

TEST CONDITIONS MIN TYP MAX UNIT

Supply voltage, V

Input voltage, V

p

Operating junction temperature, T

p

Supply voltage rising time, t

NOTE 2: VCC rising and falling slew rate must be less then 14 V/ms.

CC

I

O

J

O(sink)

r

PSON, VS5, VS33, PGI 7 V

FPO 15 V

PGO 7 V

FPO 30 mA

PGO 10 mA

4 15 V

–40 125 °C

See Note 2 1 ms

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TPS5510

V

L

(FPO)

V

Under-voltage threshold

V

3-CHANNEL POWER SUPPLY SUPERVISOR

SLVS168 – JULY 1998

electrical characteristics, VCC = 5 V, TJ = full range. (unless otherwise specified)

over voltage protection

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VS33 3.9 4.1 4.3

Over-voltage threshold

I

Leakage current (FPO) V(FPO) = 5 V 5 µA

LKG

ow level output voltage

OL

PGI and PGO

Input threshold voltage (PGI) 1.141 1.192 1.242 V

Short circuit protection delay time 3.3 V, 5 V 49 75 114 ms

I

Leakage current (PGO) PGO = 5 V 5 µA

LKG

V

Low level output voltage (PGO) Sink current = 10 mA 0.4 V

OL

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VS5 5.7 6.1 6.5

V

CC

I

= 10 mA 0.3

sink

I

= 30 mA 0.7

sink

VS33 2.71 2.83 2.95

VS5 4.1 4.3 4.47

13.3 13.8 14.3

V

PSON control

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Input pull-up current PSON = 0 V 150 µA

High-level input voltage 2.4 V

Low-level input voltage 1.2 V

total device

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

Supply current PSON = 5 V 1 mA

CC

switching characteristics, VCC = 5 V, TJ = full range

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

Delay time (PGI to PGO) 200 300 450 ms

d

t

De-bounce time (PSON) 24 38 57 ms

b

Noise deglitch time 47 73 110 µs

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

timing chart

V

CC

Reset

R

PSON

S

Q

FPO

TPS5510

3-CHANNEL POWER SUPPLY SUPERVISOR

SLVS168 – JULY 1998

PGI

3.3 V

5 V

12 V

PGO

PSON

ON

t

d

PG OFF delay

AC

OFF

t

d

t

d

t

b

Protect Occur

t

b

PSON

OFF

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...