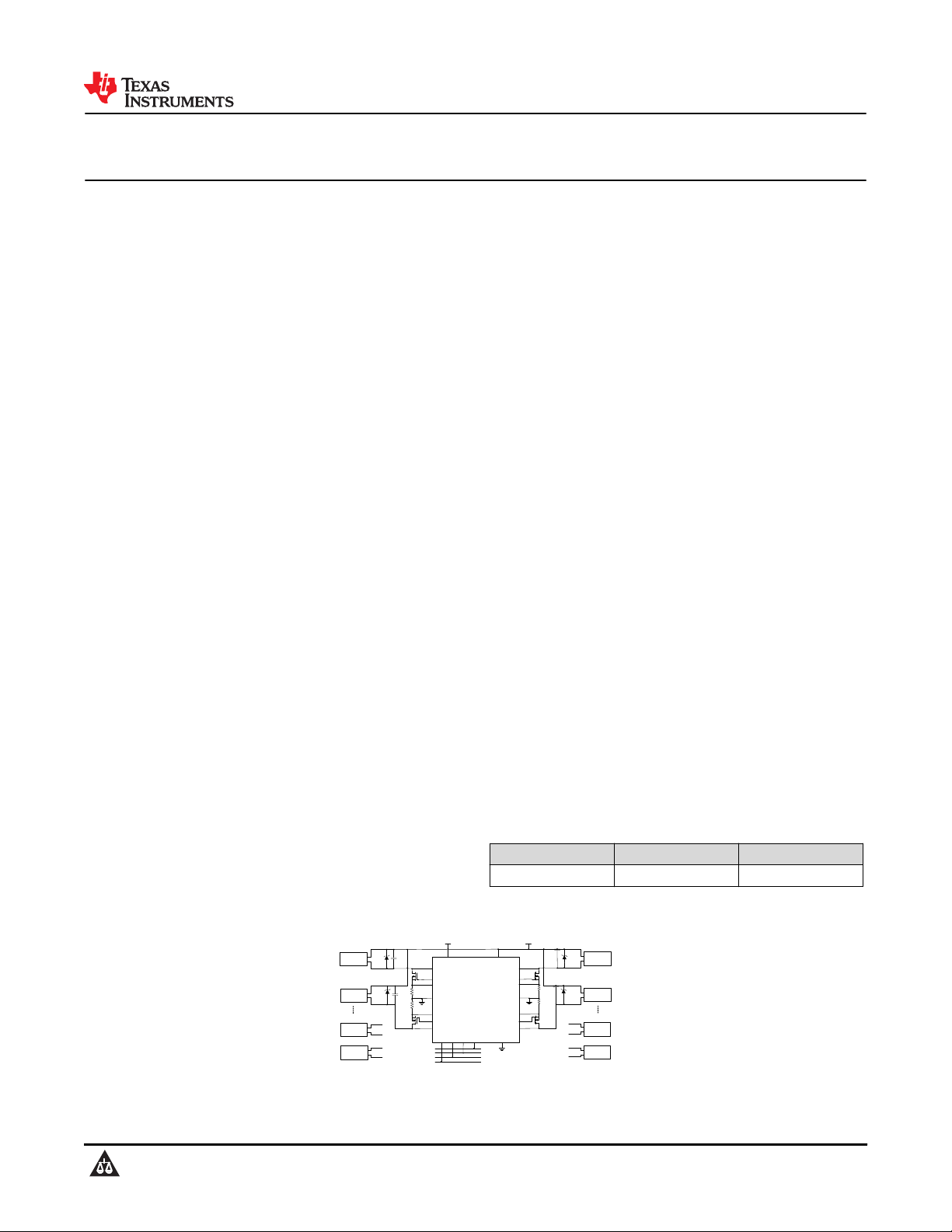

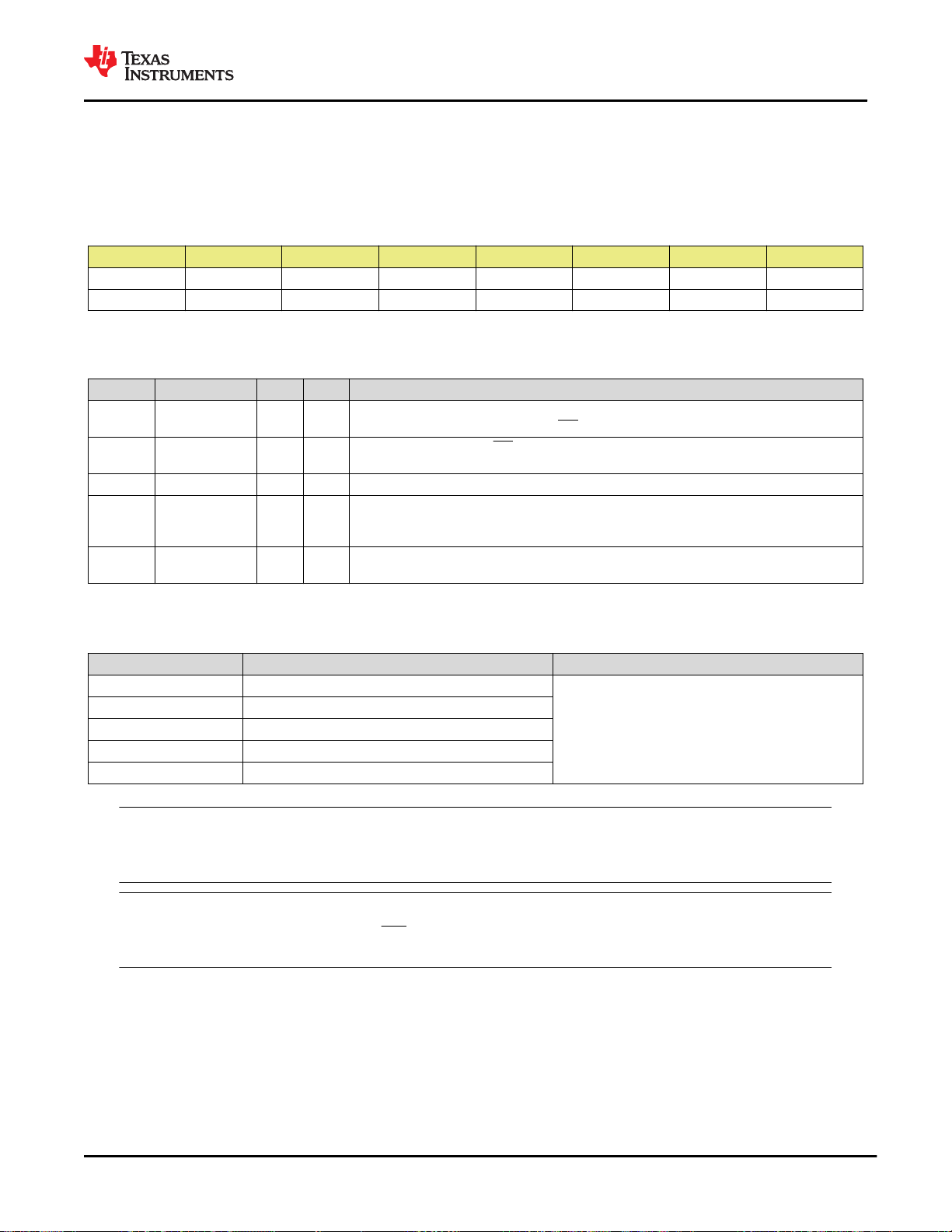

VPWR

TPS23882

+54V

2P Port #5

0.1uF

100V

0.1uF

100V

2P Port #6

SEN6

GAT6

DRAIN6

KSENSEC

0.200:

SEN5

GAT5

DRAIN5

0.200:

VDD

+3.3V

SEN2

GAT2

DRAIN2

KSENSEA

SEN1

GAT1

DRAIN1

Note: Only four channels shown

Alt A RJ45 & XFrmr

Alt A RJ45 & XFrmr

2P Port #7

2P Port #8

Alt A RJ45 & XFrmr

Alt A RJ45 & XFrmr

SCL

INT

SDAO

SDAI

I2C Bus

2P Port #1

0.1uF

100V

0.1uF

100V

2P Port #2

0.200:

0.200:

Alt A

RJ45 & XFrmr

Alt ARJ45 & XFrmr

2P Port #3

2P Port #4

Alt ARJ45 & XFrmr

Alt ARJ45 & XFrmr

GND

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882 Type-3 2-Pair 8-Channel PoE 2 PSE Controller with SRAM and 200 mΩ

R

SENSE

TPS23882

TPS23882

1 Features

• IEEE 802.3bt PSE solution for PoE 2 Type-3 2-Pair

Power Over Ethernet applications

• Compatible with TI's FirmPSE system firmware

• SRAM Programmable memory

• Programmable power limiting accuracy ±3%

• 200-mΩ Current sense resistor

• Legacy PD capacitance measurement

• Selectable 2-pair port power allocations

– 4 W, 7 W, 15.4 W, or 30 W

• Dedicated 14-bit integrating current ADC per port

– Noise immune MPS for DC disconnect

– 2% Current sensing accuracy

• 1- or 3-Bit fast port shutdown input

• Auto-class discovery and power measurement

• Never Fooled 4-Point detection

• Inrush and operational foldback protection

• 425-mA and 1.25-A Selectable current limits

• Port re-mapping

• 8-Bit or 16-bit I2C communication

• Flexible processor controlled operating modes

– Auto, semi auto and manual / diagnostic

• Per Port voltage monitoring and telemetry

• –40°C to +125°C Temperature operation

2 Applications

• Video recorder (NVR, DVR, and so forth)

• Small business switch

• Campus and branch switches

3 Description

The TPS23882 is an 8-channel power sourcing

equipment (PSE) controller engineered to insert

power onto Ethernet cables in accordance with the

IEEE 802.3bt standard. The PSE controller can detect

powered devices (PDs) that have a valid signature,

complete mutual identification, and apply power.

The TPS23882 improves on the TPS2388 with

reduced current sense resistors, SRAM

programmability, programmable power limiting,

capacitance measurement, and compatibility with TI's

FirmPSE system firmware (see Device Comparison

Table).

Programmable SRAM enables in-field firmware

upgradability over I2C to ensure IEEE compliance and

interoperability with the latest PoE enabled devices.

Dedicated per port ADCs provide continuous port

current monitoring and the ability to perform parallel

classification measurements for faster port turn on

times. A 1.25-A port current limit and adjustable

power limiting allows for the support of non-standard

applications above 60-W sourced. The 200-mΩ

current sense resistor and external FET architecture

allow designs to balance size, efficiency, thermal and

solution cost requirements.

Port remapping and pin-to-pin compatibility with the

TPS2388, TPS23880, and TPS23881 devices eases

migration from previous generation PSE designs and

enables interchangeable 2-layer PCB designs to

accommodate different system PoE power

configurations.

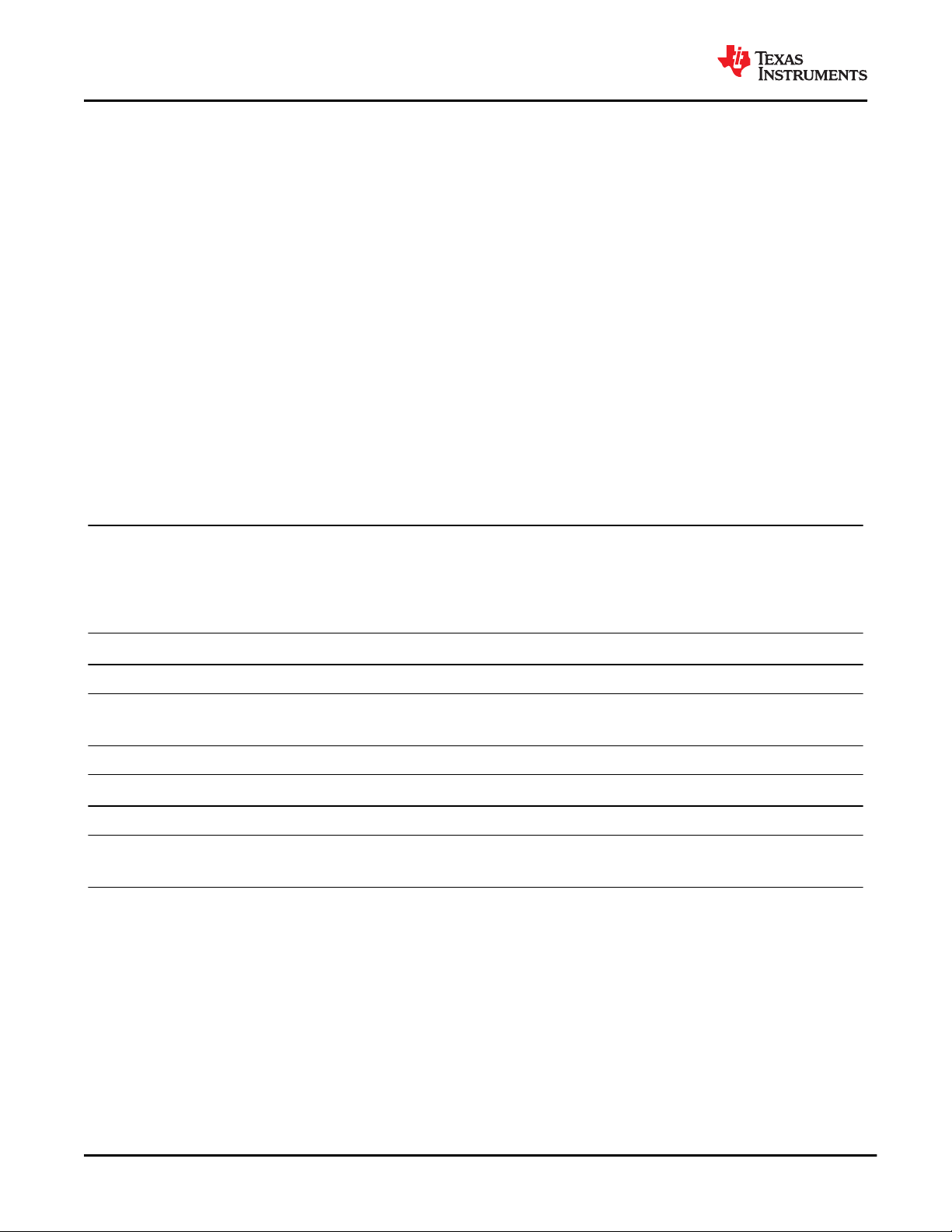

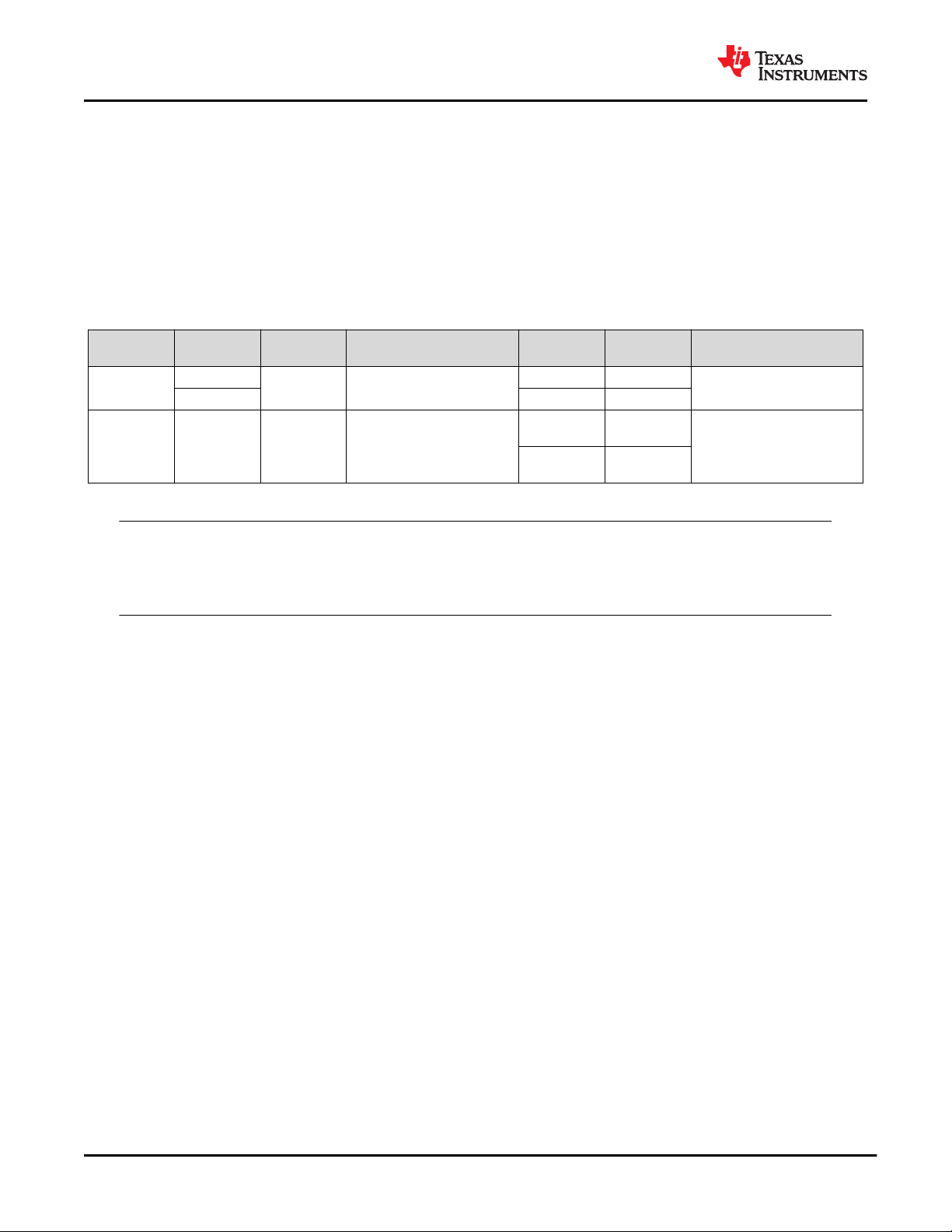

Device Information

PART NUMBER PACKAGE BODY SIZE (NOM)

TPS23882 VQFN (56) 8.00 mm × 8.00 mm

(1)

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

Copyright © 2020 Texas Instruments Incorporated

intellectual property matters and other important disclaimers. PRODUCTION DATA.

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

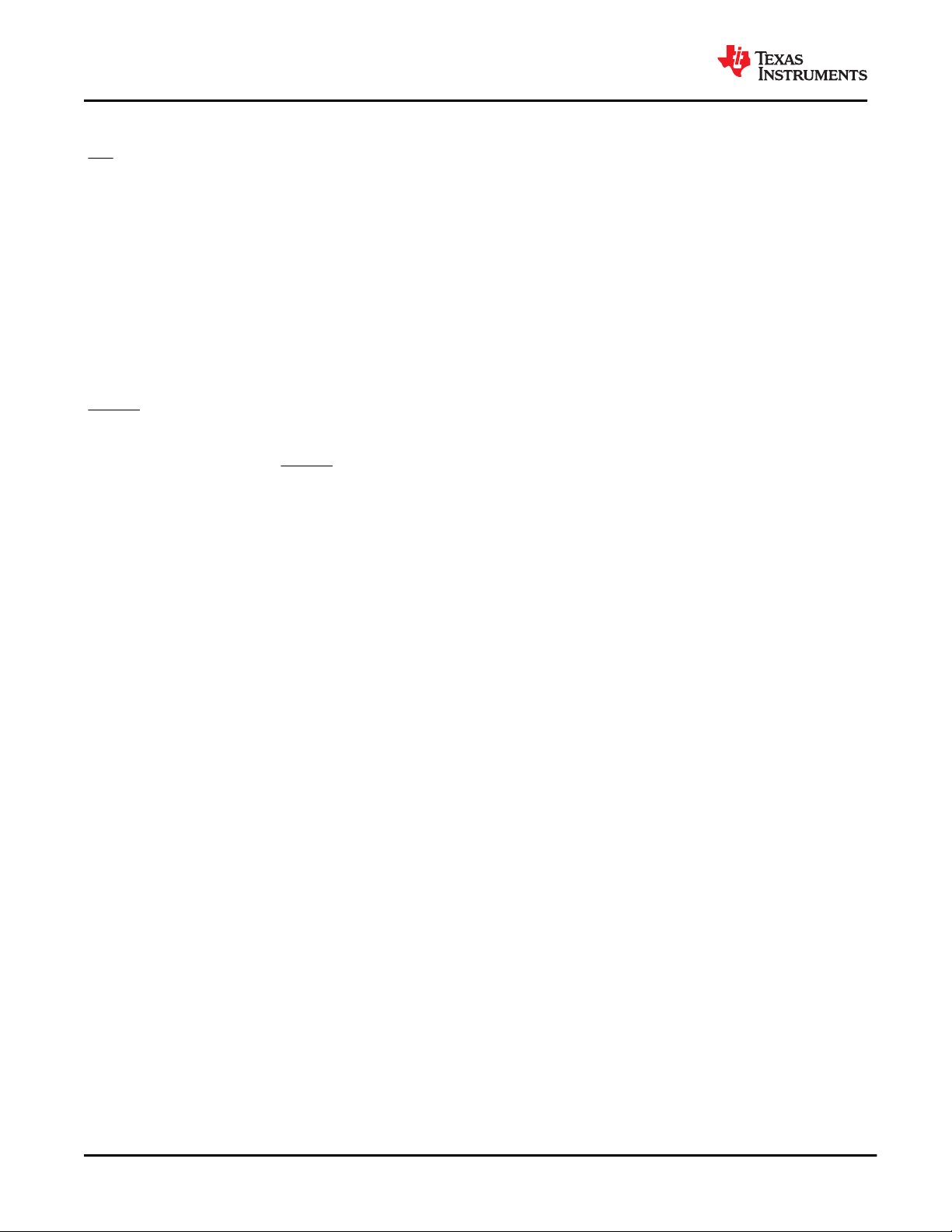

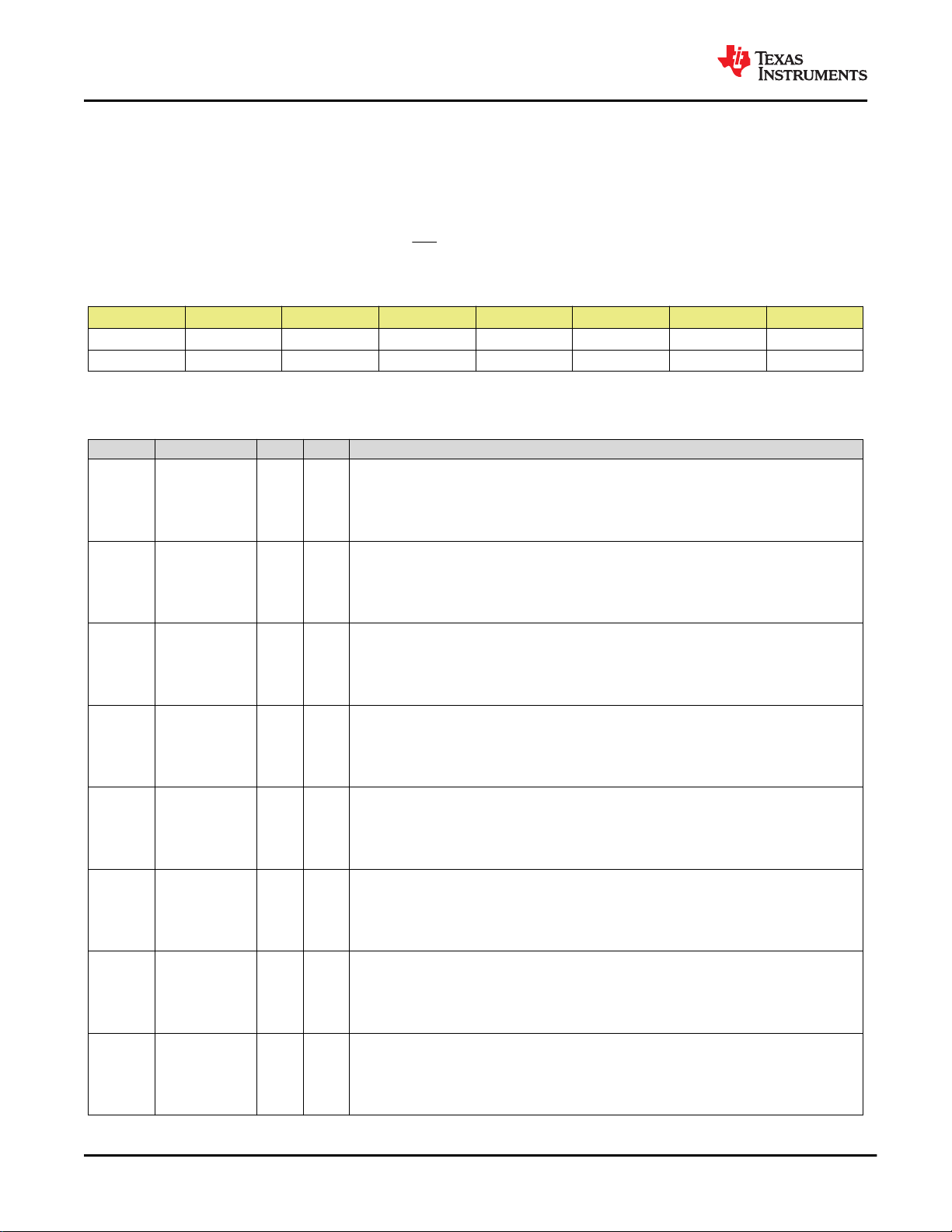

Simplified Schematic

Product Folder Links: TPS23882

Submit Document Feedback

1

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Device Comparison Table............................................... 3

6 Pin Configuration and Functions...................................4

6.1 Detailed Pin Description..............................................5

7 Specifications.................................................................. 7

7.1 Absolute Maximum Ratings........................................ 7

7.2 ESD Ratings............................................................... 7

7.3 Recommended Operating Conditions.........................7

7.4 Thermal Information....................................................7

7.5 Electrical Characteristics.............................................8

7.6 Typical Characteristics..............................................14

8 Parameter Measurement Information.......................... 19

8.1 Timing Diagrams.......................................................19

9 Detailed Description......................................................21

9.1 Overview................................................................... 21

9.2 Functional Block Diagram......................................... 25

9.3 Feature Description...................................................26

9.4 Device Functional Modes..........................................28

www.ti.com

2

9.5 I

C Programming...................................................... 29

9.6 Register Maps...........................................................32

10 Application and Implementation.............................. 102

10.1 Application Information......................................... 102

10.2 Typical Application................................................ 104

11 Power Supply Recommendations............................110

11.1 VDD.......................................................................110

11.2 VPWR....................................................................110

12 Layout......................................................................... 111

12.1 Layout Guidelines..................................................111

12.2 Layout Example.................................................... 112

13 Device and Documentation Support........................113

13.1 Documentation Support........................................ 113

13.2 Receiving Notification of Documentation Updates 113

13.3 Support Resources............................................... 113

13.4 Trademarks........................................................... 113

13.5 Electrostatic Discharge Caution............................ 113

13.6 Glossary................................................................ 113

14 Mechanical, Packaging, and Orderable

Information.................................................................. 113

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision C (May 2020) to Revision D (August 2020) Page

• Updated the numbering format for tables, figures and cross-references throughout the document...................1

Changes from Revision B (October 2019) to Revision C (May 2020) Page

• Deleted Autonomous operation description throughout data sheet for clarification ...........................................4

• Changed Gate 1-8 MAX voltage from 12 to 13 V in the Absolute Maximum Ratings table ...............................7

Changes from Revision A (September 2019) to Revision B (December 2019) Page

• Fixed typo in device number on first page ......................................................................................................... 1

Changes from Revision * (August 2019) to Revision A (September 2019) Page

• Changed from Advance Information to Production Data ................................................................................... 1

• First Public Release............................................................................................................................................1

2 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

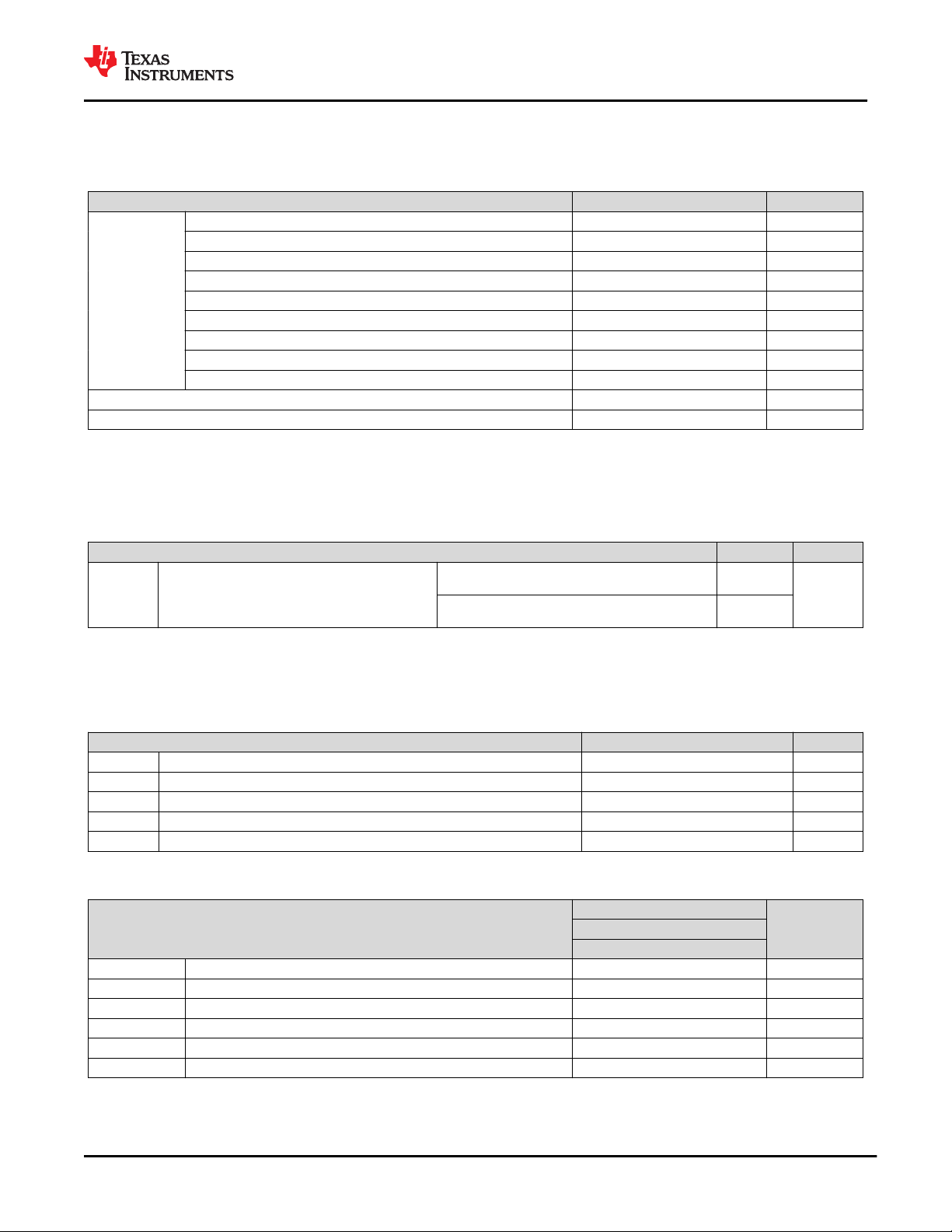

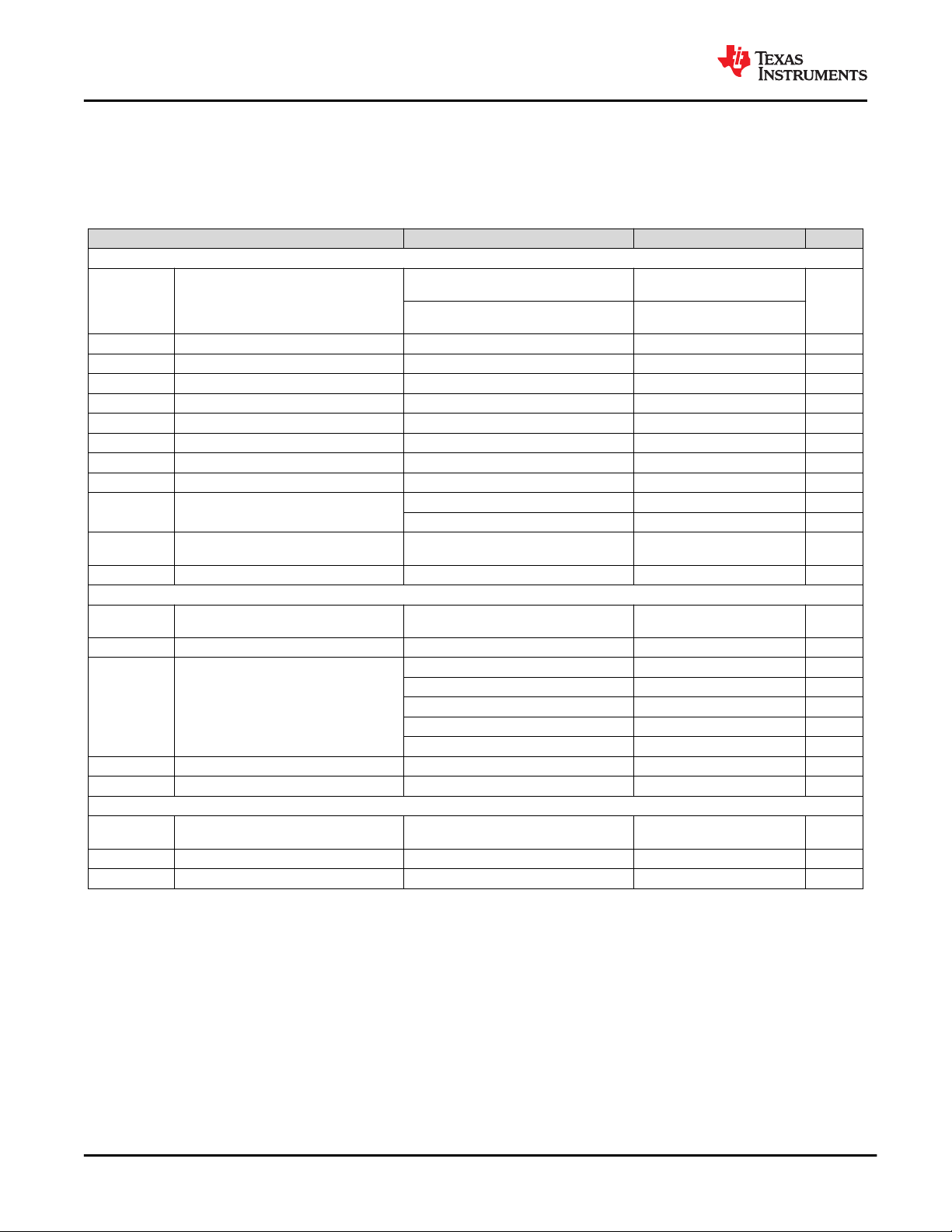

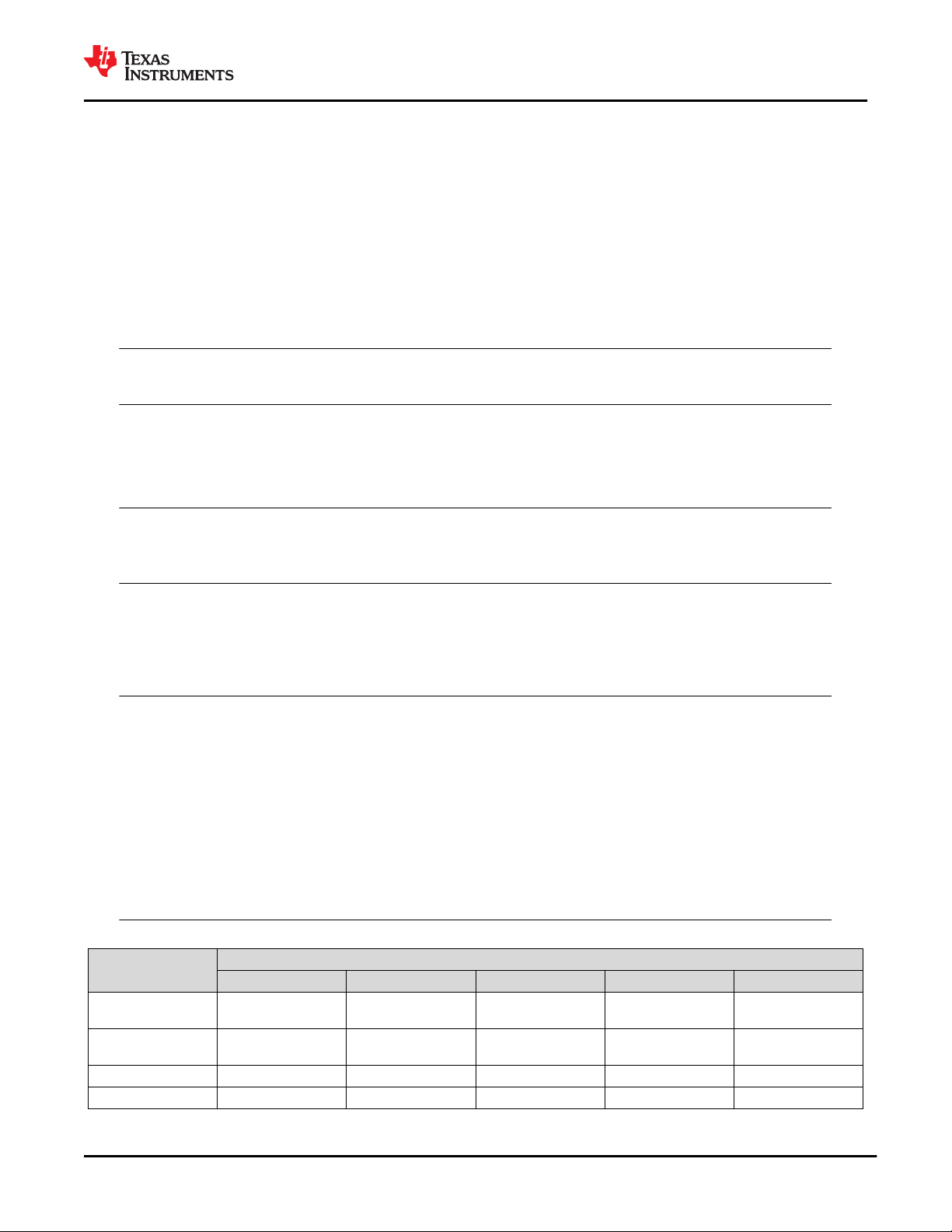

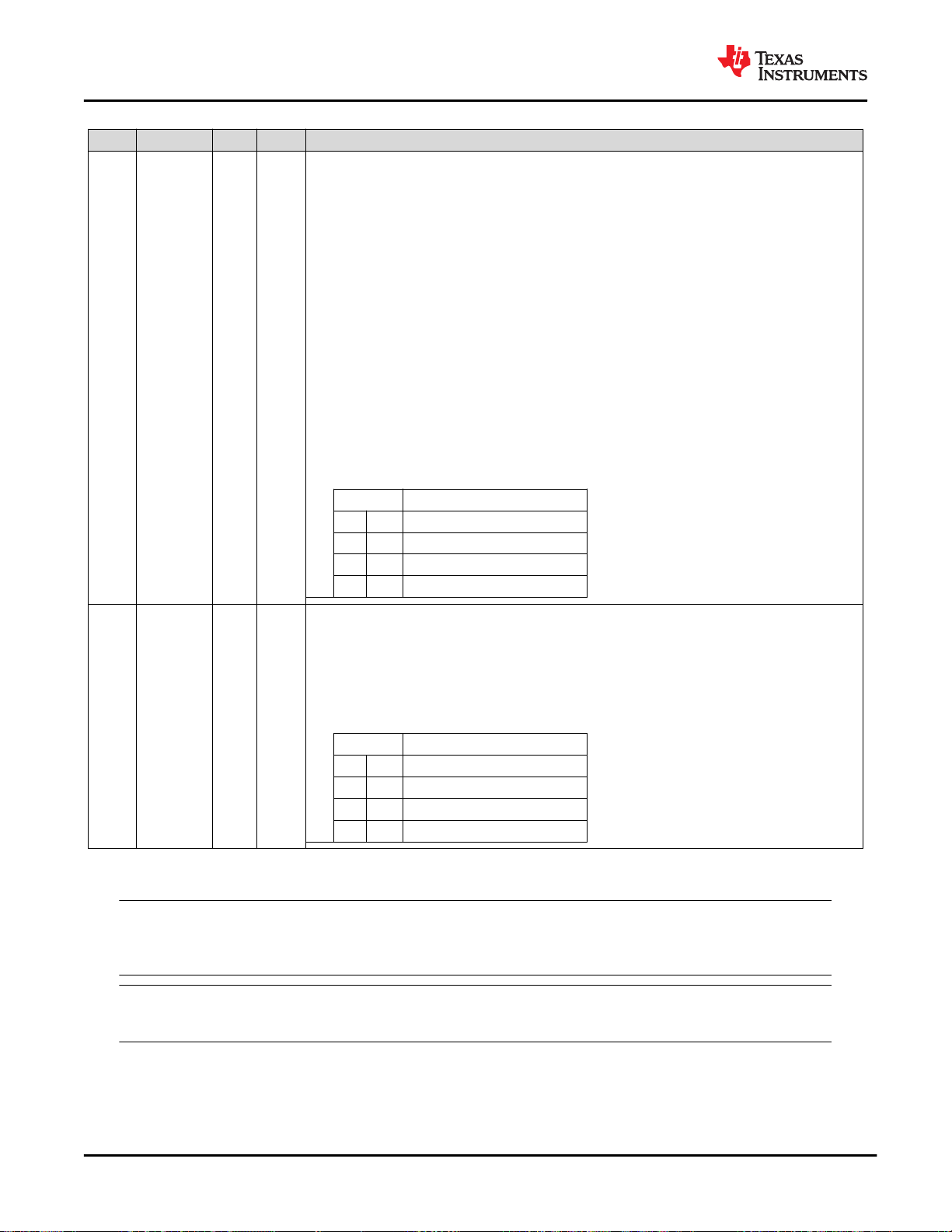

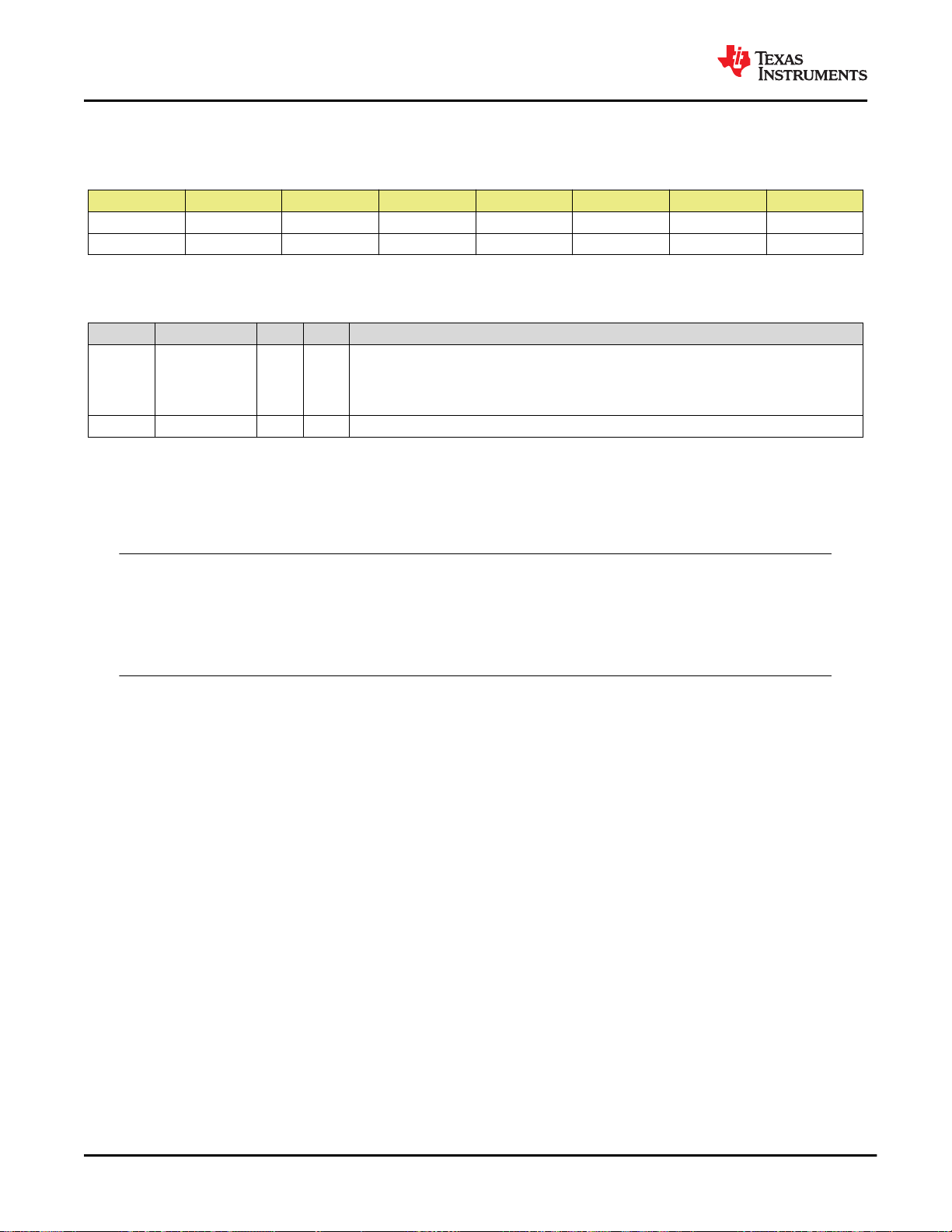

5 Device Comparison Table

Table 5-1 summarizes the primary differences between the available 2-Pair PSE devices.

KEY FEATURES TPS23880 TPS23881 TPS23882

TPS23882

Compatible with TI's FirmPSE system

firmware

Pin to Pin compatible Yes Yes Yes

Number of PSE Channels 8 8 8

Supported IEEE 802.3 PSE Types

R

SENSE

2-Pair P

4-Pair P

90+ W 4-pair P

programable ranges 0.5 W to 54 W 2 W to 65 W 2 W to 65 W

CUT

programable ranges 0.5 W to 108 W 4 W to 127 W N/A

CUT

accuracy ±3.0 % ±2.5 % N/A

CUT

Channel capacitance measurement

range

ULA Packaging No Yes (TPS23881A) N/A

I2C Programmable SRAM Memory 16 kB 16 kB 16 kB

Table 5-1. 2-Pair PSE Key Feature Comparisons

KEY FEATURES TPS23861 TPS2388 TPS23881 TPS23882

Compatible with TI's FirmPSE

system firmware

Pin to Pin compatible N/A Yes Yes Yes

Number of PSE Channels 4 8 8 8

Supported IEEE 802.3 PSE

Types

R

SENSE

2-Pair P

ranges

T

MPS

programable

CUT

I

CUT

Port Current Limit (1x / 2x) 425 mA / 1060 mA 425 mA / 1060 mA 425 mA / 1250 mA 425 mA / 1250 mA

Channel capacitance

measurement range

PD Autoclass Discovery and

Power Measurement

I2C Programmable SRAM

Memory

N/A N/A Yes Yes

PoE 1

802.3at Type 1 or 2

0.255 Ω 0.255 Ω 0.200 Ω 0.200 Ω

N/A

adjustable up to 920

mA

15 ms 15 ms 3 ms 3 ms

N/A N/A 1 µF to 12 µF 1 µF to 12 µF

N/A N/A Yes Yes

N/A N/A 16 kB 16 kB

N/A Yes Yes

PoE 2

802.3bt Type 3 or 4

(2 or 4 Pair)

PoE 2

802.3bt Type 3 or 4

(2 or 4 Pair)

802.3bt Type 3 (2-Pair)

0.255 Ω 0.200 Ω 0.200 Ω

N/A 1 µF to 12 µF 1 µF to 12 µF

PoE 1

802.3at Type 1 or 2

PoE 2

802.3bt Type 3 or 4

(2 or 4 Pair)

N/A

I

adjustable up to 920

CUT

2 W to 65 W 2 W to 65 W

mA

PoE 2

PoE 2

802.3bt Type 3 (2-Pair)

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

3

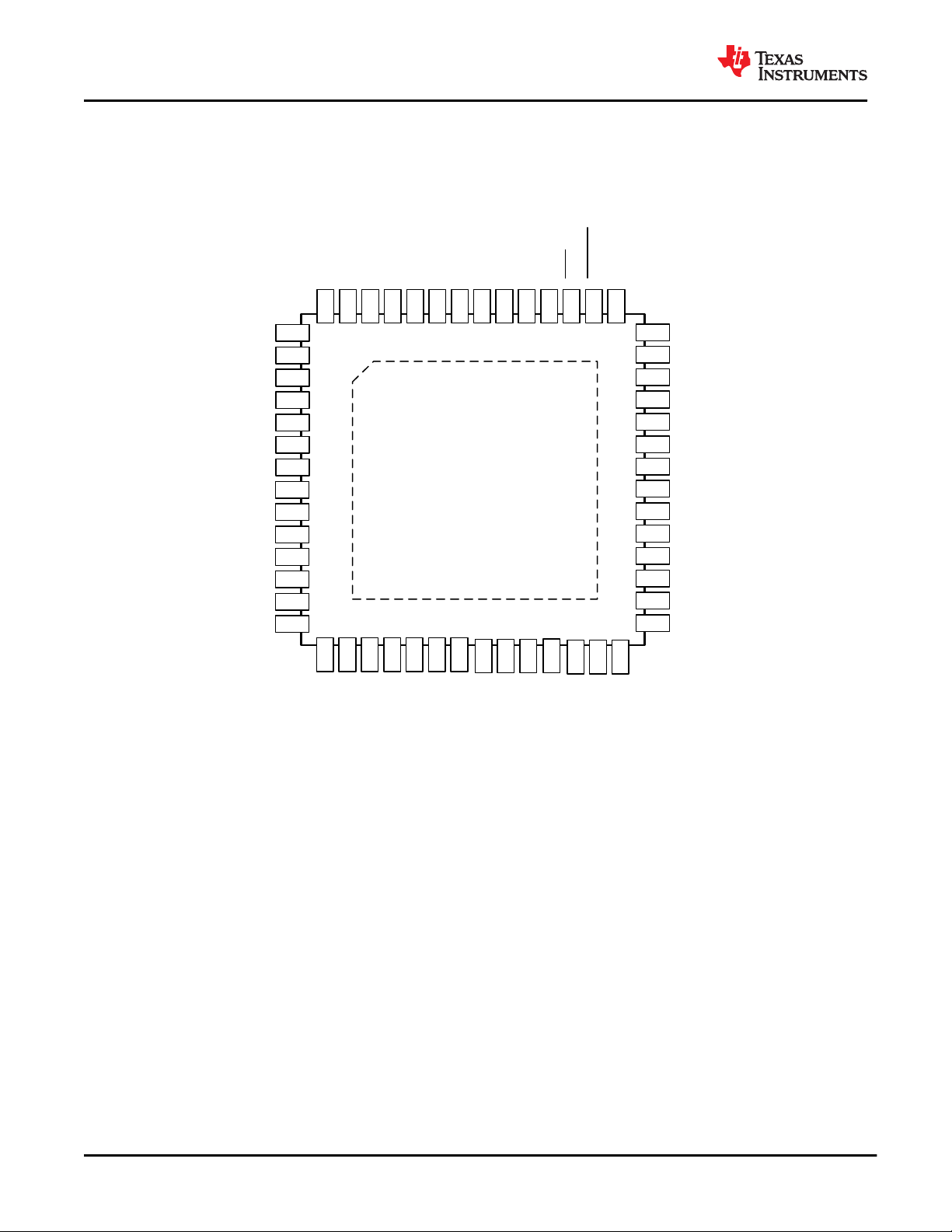

8

9

10

11

12

13

14

DRAIN3

DRAIN4

GAT4

SEN4

15

16

17

18

19

20

21

NC

NC

SEN3

OSS

SDAO

56

55

54

53

52

51

50

NC

NC

TEST4

AGND

NC

SCL

A4

A3

SDAI

35

34

33

32

31

30

29

VPWR

22

23

24

NC

TEST1

TEST2

1

2

3

4

5

6

7

DRAIN1

KSENSA

DRAIN2

GAT2

SEN2

SEN1

25

TEST3

26

27

28

TEST0

NC

NC

42

41

40

39

38

37

36

A2

A1

49

48

47

46

45

44

43

INT

DGND

RESET

VDD

TEST5

GAT1

GAT3

KSENSB

DRAIN6

DRAIN5

GAT5

SEN5

SEN6

DRAIN8

KSENSD

DRAIN7

GAT7

SEN7

SEN8

GAT8

GAT6

KSENSC

Thermal Pad

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

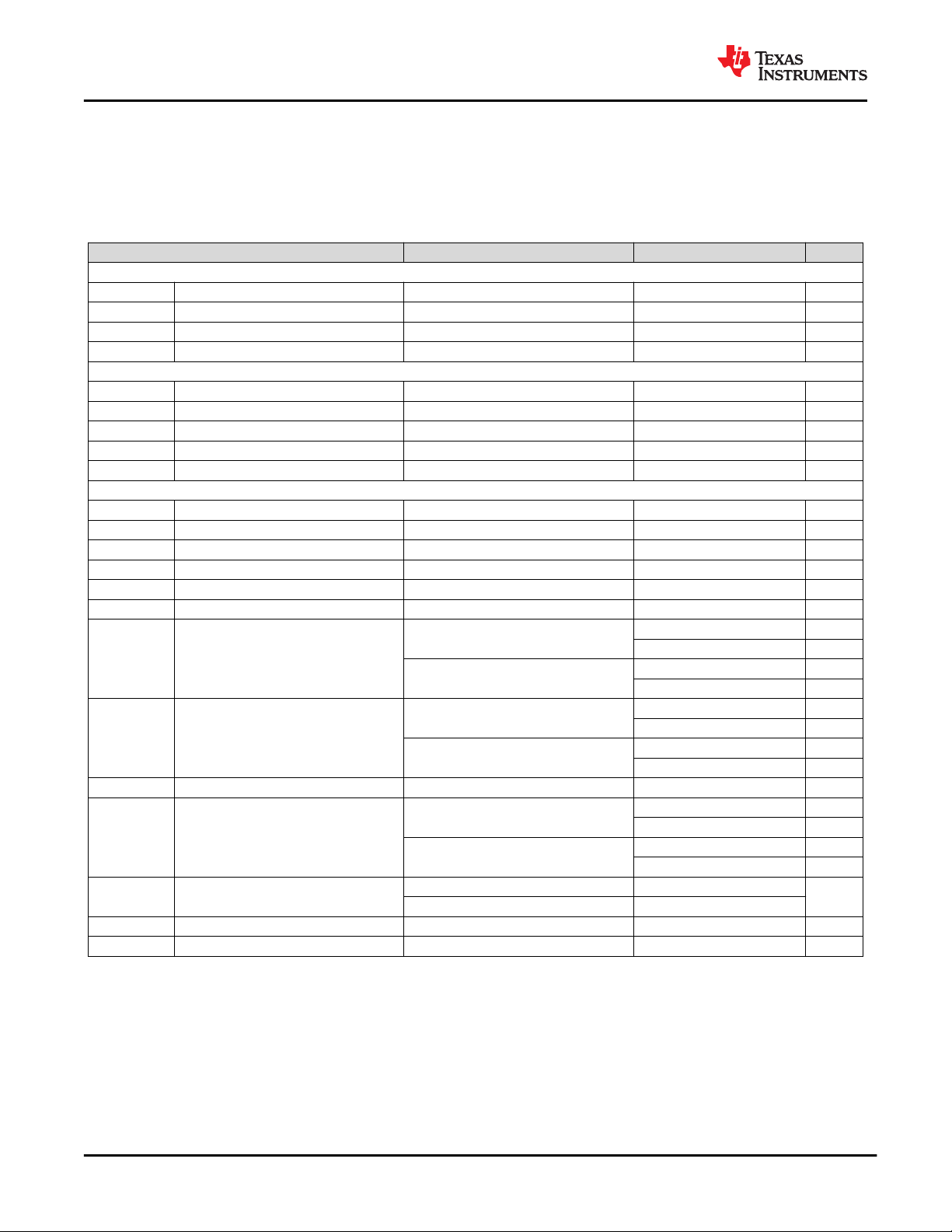

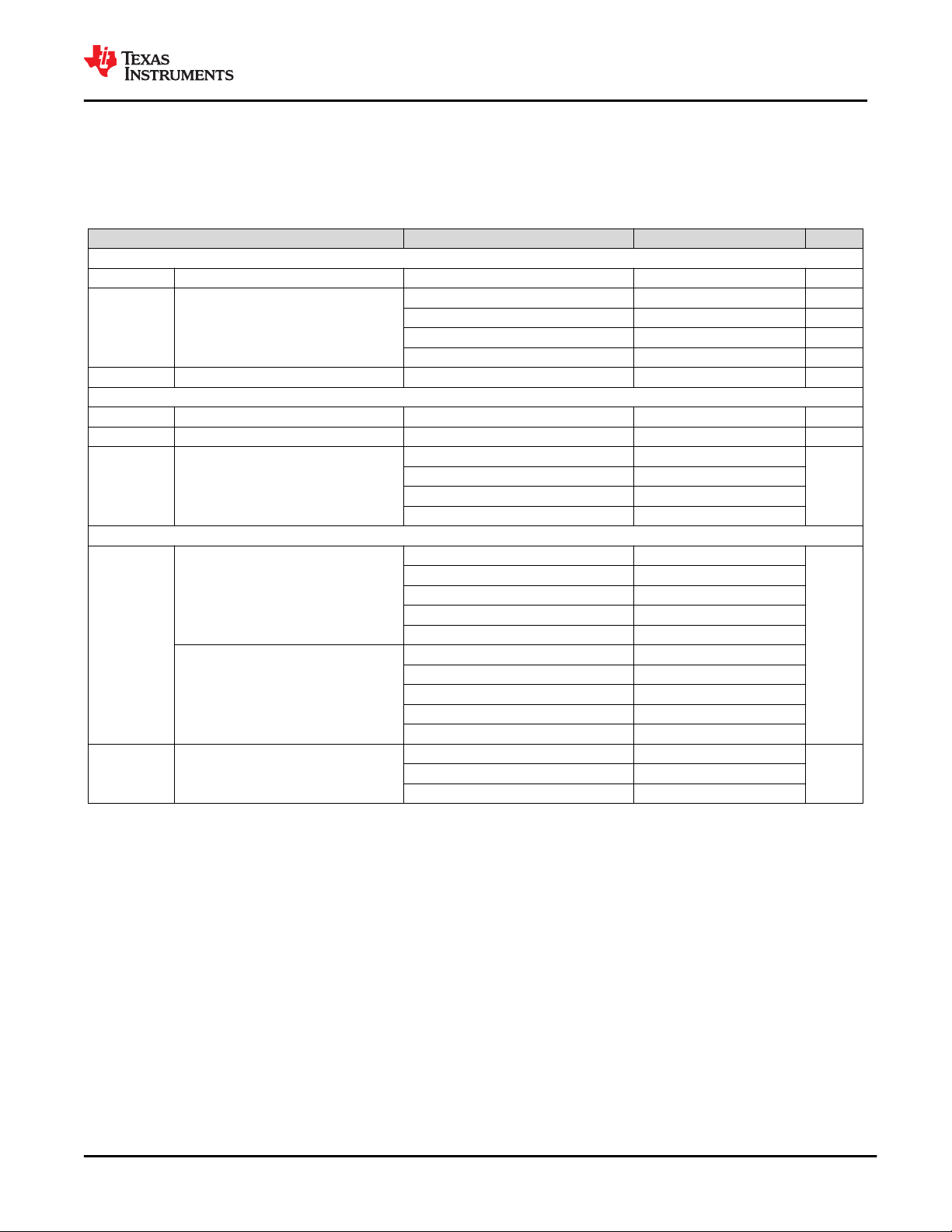

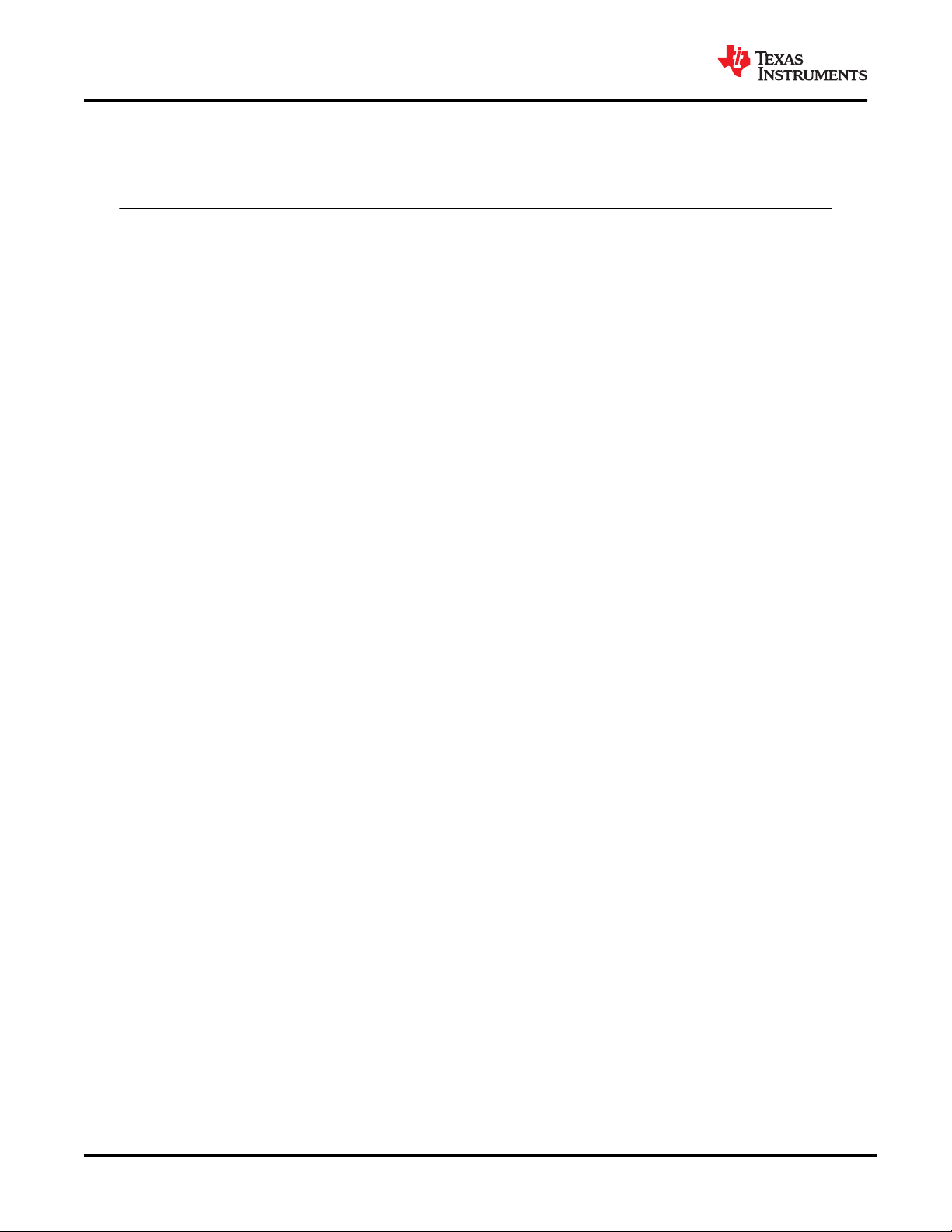

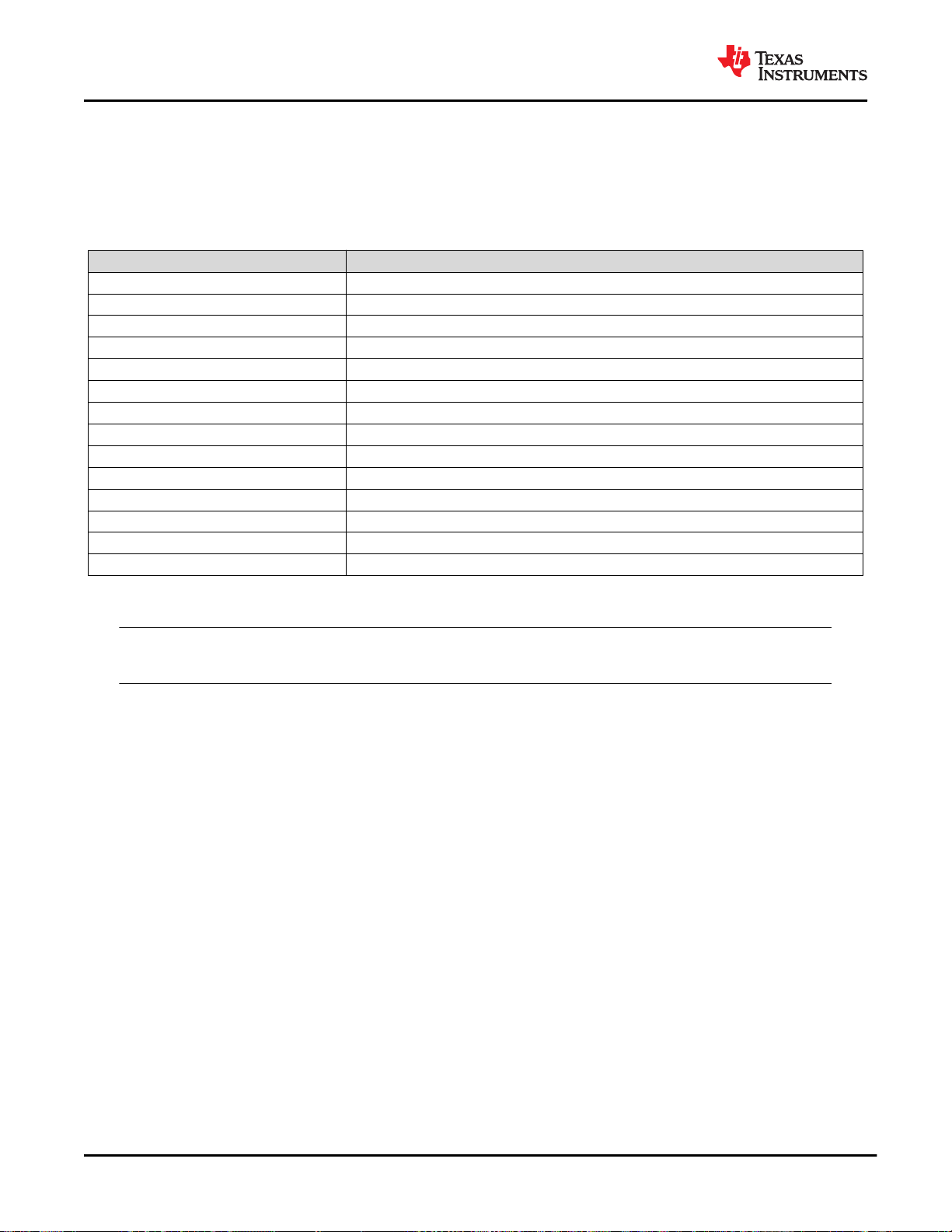

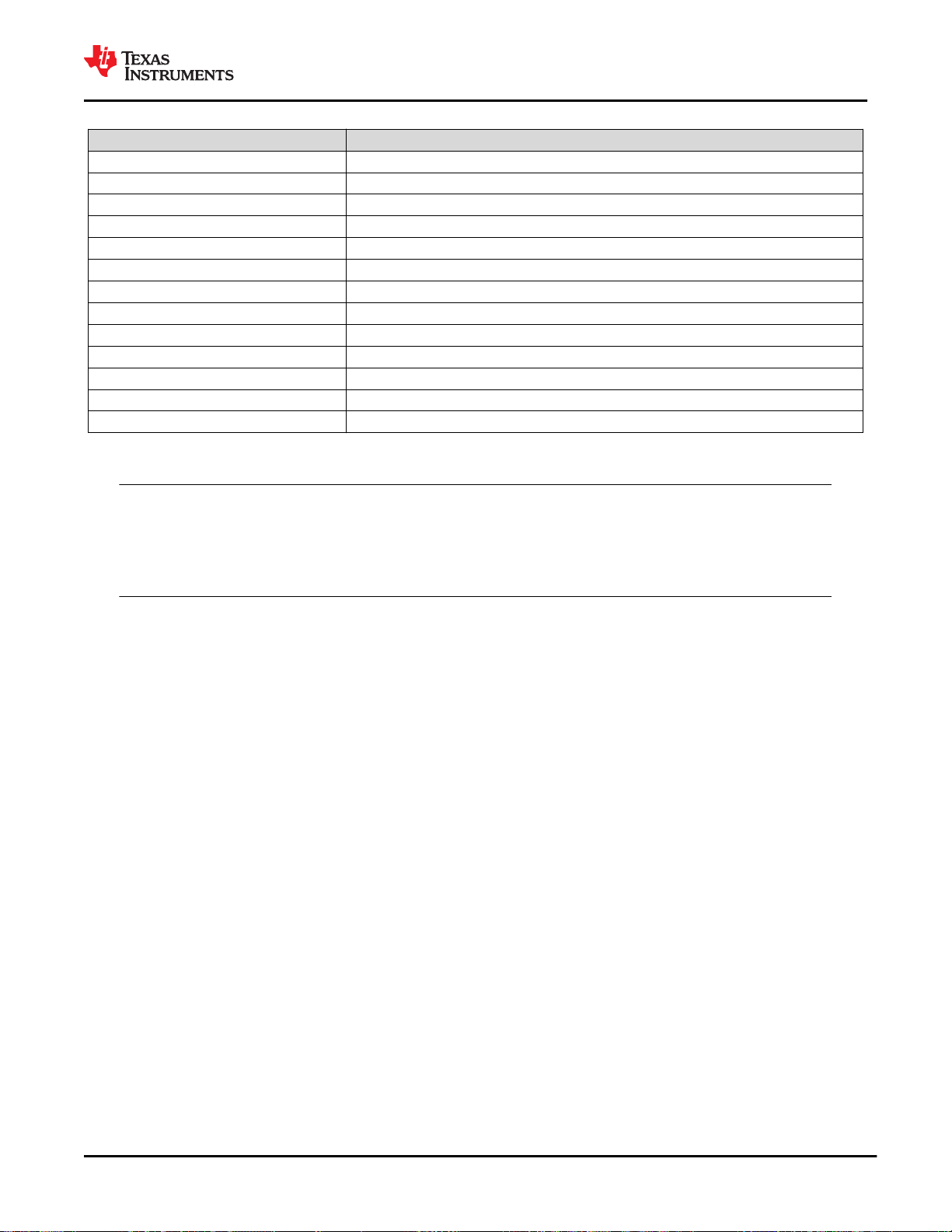

6 Pin Configuration and Functions

www.ti.com

Figure 6-1. RTQ Package With Exposed Thermal Pad 56-Pin VQFN Top View

4 Submit Document Feedback

Product Folder Links: TPS23882

Copyright © 2020 Texas Instruments Incorporated

www.ti.com

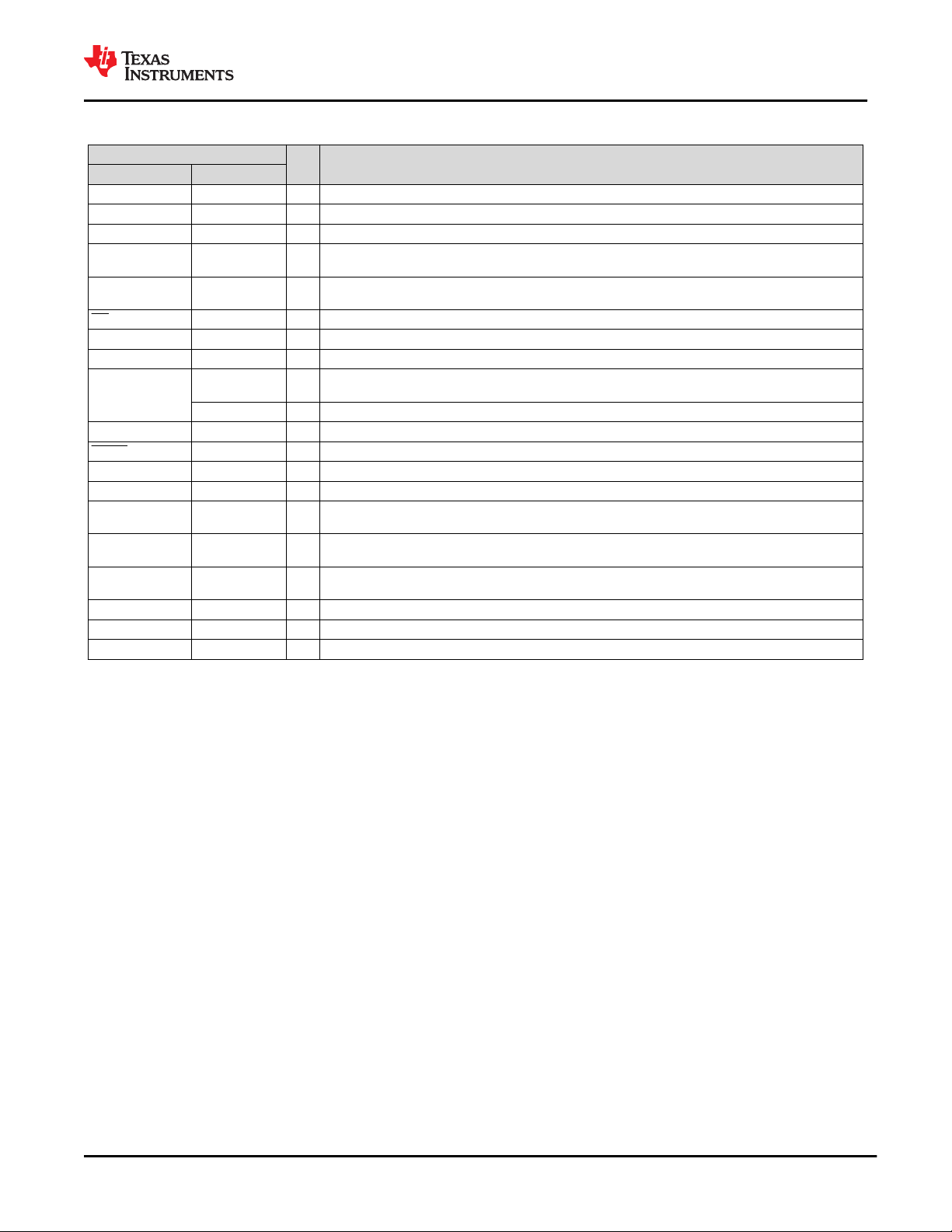

Pin Functions

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

PIN

NAME NO.

A1-4 48–51 I I2C A1-A4 address lines. These pins are internally pulled up to VDD.

AGND 21 — Analog ground. Connect to GND plane and exposed thermal pad.

DGND 46 — Digital ground. Connect to GND plane and exposed thermal pad.

DRAIN1-8

GAT1-8

INT 45 O Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.

KSENSA/B 4, 11 I Kelvin point connection for SEN1-4

KSENSC/D 32, 39 I Kelvin point connection for SEN5-8

NC

OSS 56 I Channel 1-8 fast shutdown. This pin is internally pulled down to DGND.

RESET 44 I Reset input. When asserted low, the TPS23882 is reset. This pin is internally pulled up to VDD.

SCL 53 I Serial clock input for I2C bus.

SDAI 54 I Serial data input for I2C bus. This pin can be connected to SDAO for non-isolated systems.

SDAO 55 O

SEN1-8

TEST0-5

Thermal pad — — The DGND and AGND terminals must be connected to the exposed thermal pad for proper operation.

VDD 43 — Digital supply. Bypass with 0.1 µF to DGND pin.

VPWR 17 — Analog 54-V positive supply. Bypass with 0.1 µF to AGND pin.

3, 5, 10, 12, 31,

33, 38, 40

1, 7, 8, 14, 29, 35,

36, 42

15, 16, 18, 19 O

22, 27, 28, 52 — No connect pin. Leave open.

2, 6, 9, 13, 30, 34,

37, 41

20, 23, 24, 25, 26,

47

I/O DESCRIPTION

I Channel 1-8 output voltage monitor.

O Channel 1-8 gate drive output.

No connect pins. These pins are internally biased at 1/3 and 2/3 of VPWR in order to control the voltage

gradient from VPWR. Leave open.

Serial data output for I2C bus. This pin can be connected to SDAI for non-isolated systems. This output is opendrain.

I Channel 1-8 current sense input.

I/O Used internally for test purposes only. Leave open.

6.1 Detailed Pin Description

The following descriptions refer to the pinout and the functional block diagram.

DRAIN1-DRAIN8: Channels 1-8 output voltage monitor and detect sense. Used to measure the port output

voltage, for port voltage monitoring, port power good detection and foldback action. Detection probe currents

also flow into this pin.

The TPS23882uses an innovative 4-point technique to provide reliable PD detection and avoids powering an

invalid load. The discovery is performed by sinking two different current levels via the DRAINn pin, while the PD

voltage is measured from VPWR to DRAINn. If prior to starting a new detection cycle the port voltage is >2.5 V,

an internal 100-kΩ resistor is connected in parallel with the port and a 400-ms detect backoff period is applied to

allow the port capacitor to be discharged before the detection cycle starts.

There is an internal resistor between each DRAINn pin and VPWR in any operating mode except during

detection or while the port is ON. If the port n is not used, DRAINn can be left floating or tied to GND.

GAT1-GAT8: Channels 1-8 gate drive outputs are used for external N-channel MOSFET gate control. At port

turn on, it is driven positive by a low current source to turn the MOSFET on. GATn is pulled low whenever any of

the input supplies are low or if an overcurrent timeout has occurred. GATn is also pulled low if the port is turned

off by use of manual shutdown inputs. Leave floating if unused.

For improved design robustness, the current foldback functions limit the power dissipation of the MOSFET

during low resistance load or short-circuit events and during the inrush period at port turn on. There is also fast

overload protection comparator for major faults like a direct short that forces the MOSFET to turn off in less than

a microsecond.

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

5

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

The circuit leakage paths between the GATn pin and any nearby DRAINn pin, GND or Kelvin point connection

must be minimized (< 250 nA), to ensure correct MOSFET control.

INT: This interrupt output pin asserts low when a bit in the interrupt register is asserted. This output is opendrain.

KSENSA, KSENSB, KSENSC, KSENSD: Kelvin point connection used to perform a differential voltage

measurement across the associated current sense resistors.

Each KSENS is shared between two neighbor SEN pins as following: KSENSA with SEN1 and SEN2, KSENSB

with SEN3 and SEN4, KSENSC with SEN5 and SEN6, KSENSD with SEN7 and SEN8. To optimize the

measurement accuracy, ensure proper PCB layout practices are followed.

OSS: Fast shutdown, active high. This pin is internally pulled down to DGND, with an internal 1-µs to 5-µs

deglitch filter.

The turn off procedure is similar to a port reset using Reset command (1Ah register). The 3-bit OSS function

allows for a series of pulses on the OSS pin to turn off individual or multiple ports with up to 8 levels of priority.

RESET: Reset input, active low. When asserted, the TPS23882 resets, turning off all ports and forcing the

registers to their power-up state. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter.

The designer can use an external RC network to delay the turn-on. There is also an internal power-on-reset

which is independent of the RESET input.

SCL: Serial clock input for I2C bus.

SDAI: Serial data input for I2C bus. This pin can be connected to SDAO for non-isolated systems.

SDAO: Open-drain I2C bus output data line. Requires an external resistive pull-up. The TPS23882 uses

separate SDAO and SDAI lines to allow optoisolated I2C interface. SDAO can be connected to SDAI for nonisolated systems.

A4-A1: I2C bus address inputs. These pins are internally pulled up to VDD. See Section 9.6.2.13 for more

details.

SEN1-8: Channel current sense input relative to KSENSn (see KSENSn description). A differential measurement

is performed using KSENSA-D Kelvin point connection. Monitors the external MOSFET current by use of a

0.200-Ω current sense resistor connected to GND. Used by current foldback engine and also during

classification. Can be used to perform load current monitoring via ADC conversion.

When the TPS23882 performs the classification measurements, the current flows through the external

MOSFETs. This avoids heat concentration in the device and makes it possible for the TPS23882 to perform

classification measurements on multiple ports at the same time. For the current limit with foldback function, there

is an internal 2-µS analog filter on the SEN1-8 pins to provide glitch filtering. For measurements through an

ADC, an anti-aliasing filter is present on the SEN1-8 pins. This includes the port-powered current monitoring,

port policing, and DC disconnect.

If the port is not used, tie SENn to GND.

VDD: 3.3-V logic power supply input.

VPWR: High voltage power supply input. Nominally 54 V.

AGND and DGND: Ground references for internal analog and digital circuitry respectively. Not connected

together internally. Both pins require a low resistance path to the system GND plane. If a robust GND plane is

used to extract heat from the device's thermal pad, these pins may be connected together through the thermal

pad connection on the pcb.

6 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

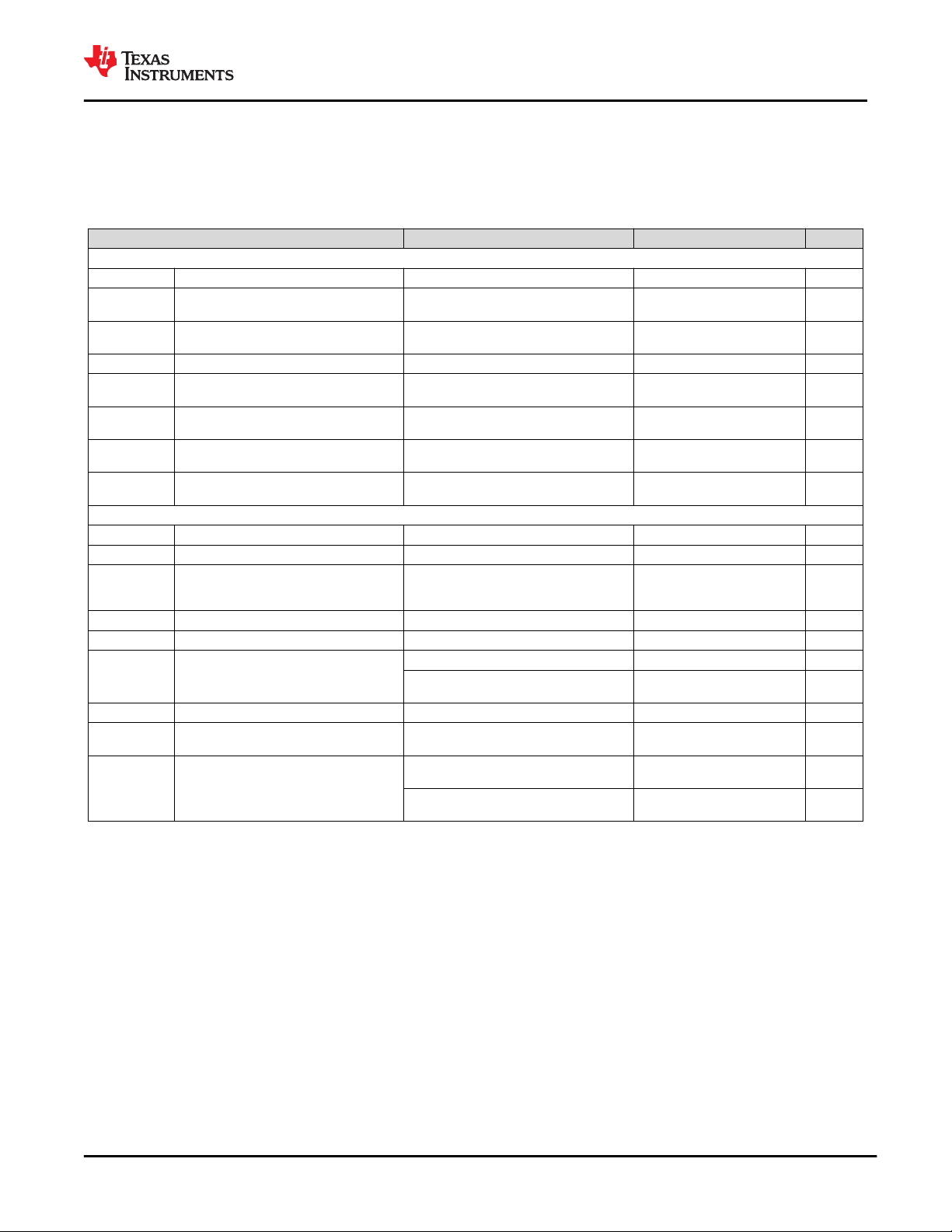

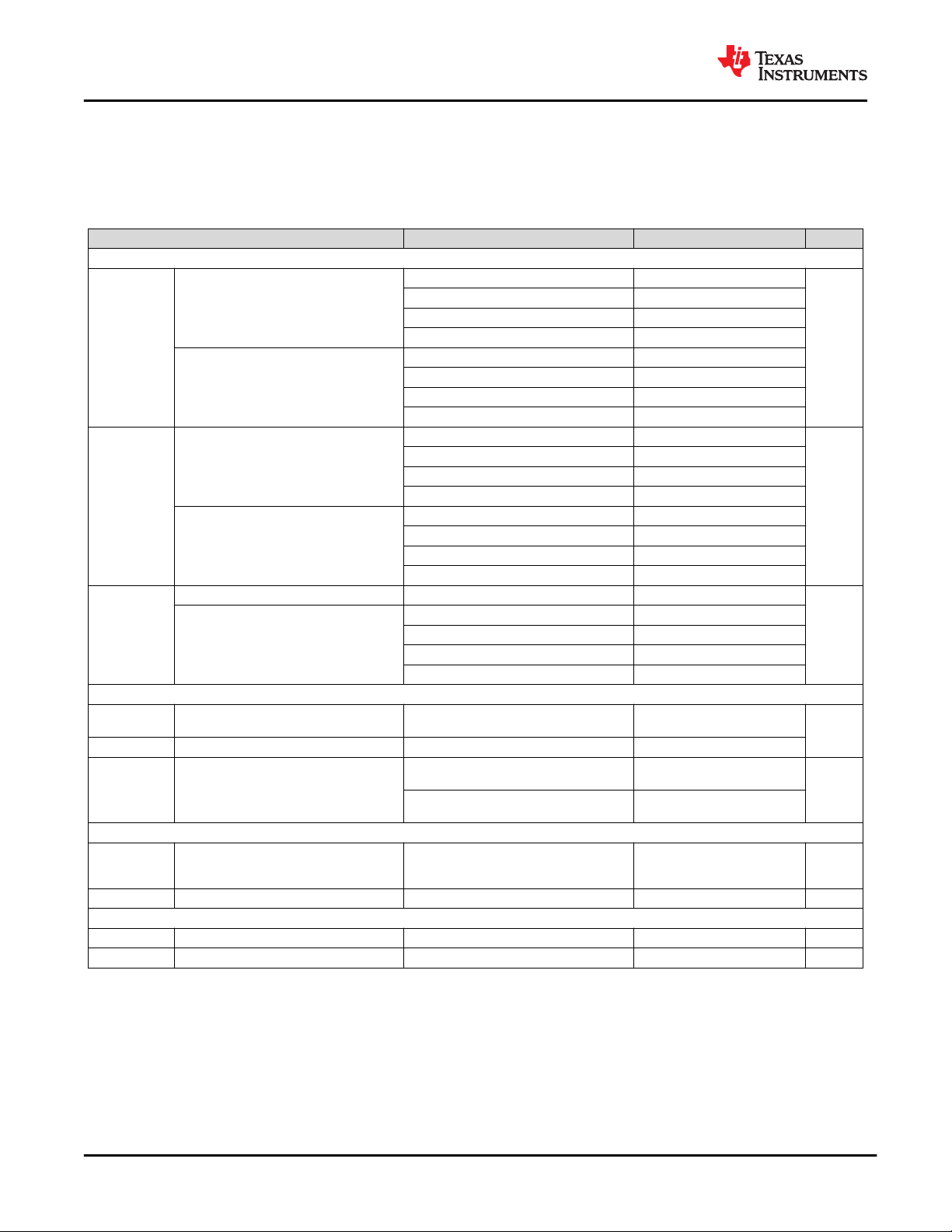

7 Specifications

7.1 Absolute Maximum Ratings

TPS23882

over operating free-air temperature range (unless otherwise noted)

VPWR –0.3 70 V

VDD –0.3 4 V

OSS, RESET, A1-A4 –0.3 4 V

SDAI, SDAO, SCL, INT –0.3 4 V

Voltage SEN1-8, KSENSA, KSENSB, KSENSC, KSENSD –0.3 3 V

GATE1-8 –0.3 13 V

DRAIN1-8 –0.3 70 V

AGND-GDND –0.3 0.3 V

Sink Current

Lead Temperature 1/6mm from case for 10 seconds 260 °C

T

stg

INT, SDA 20 mA

Storage temperature –65 150 °C

(1) Stresses beyond those listed underAbsolute Maximum Rating may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

7.2 ESD Ratings

(1)

MIN MAX UNIT

V

(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC

JS-001, all pins

Charged device model (CDM), per JEDEC

specificationJESD22-C101, all pins

(1)

(2)

(1) JEDEC documentJEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC documentJEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

V

V

f

T

SCL

VDD

VPWR

J

Voltage Slew rate on VPWR 1 V/µs

I2C Clock Frequency 400 kHz

Junction temperature –40 125 °C

3 3.3 3.6 V

44 54 57 V

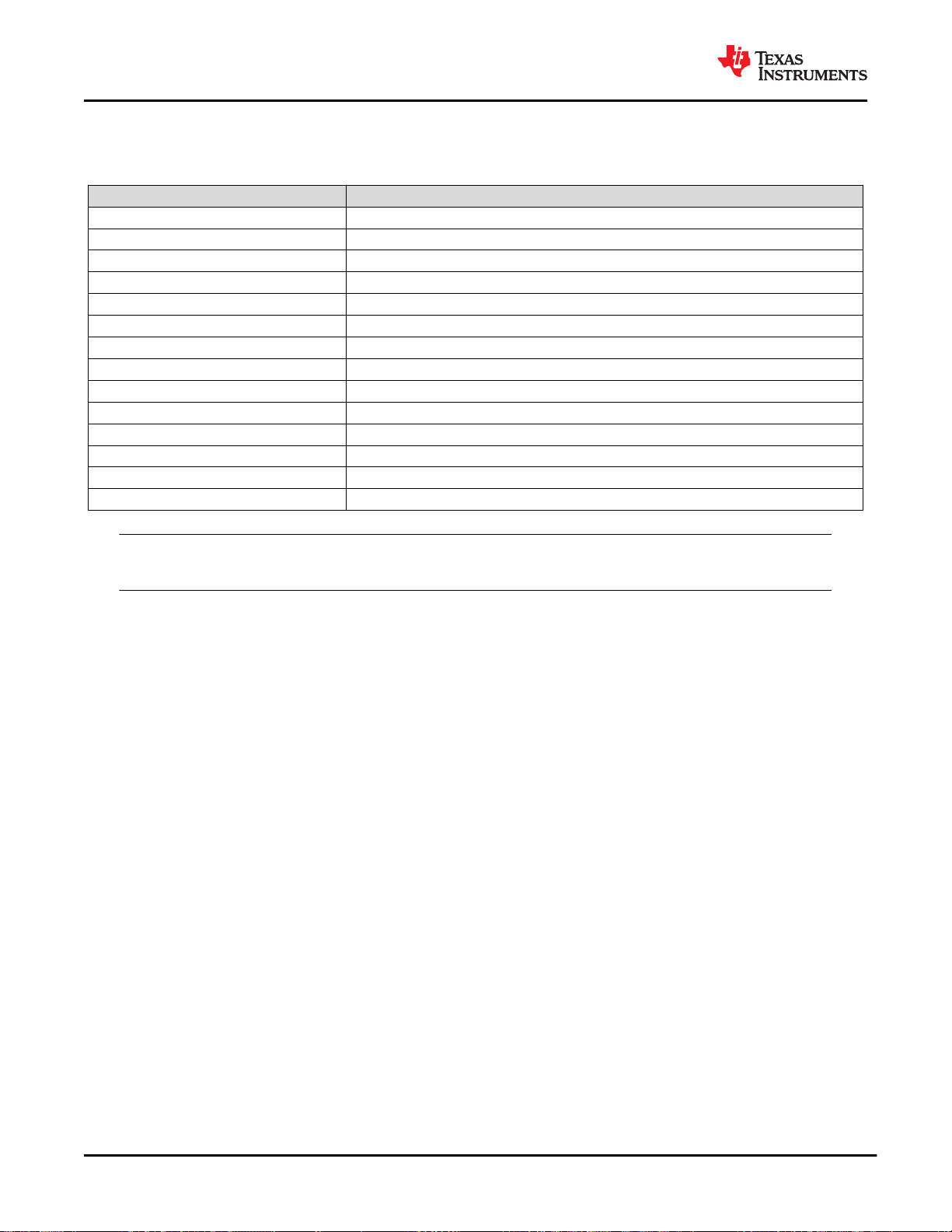

7.4 Thermal Information

TPS23882

R

θJA

R

θJC(top)

R

θJB

Ψ

JT

Ψ

JB

R

θJC(bot)

THERMAL METRIC

Junction-to-ambient thermal resistance 25.3 °C/W

Junction-to-case (top) thermal resistance 9.7 °C/W

Junction-to-board thermal resistance 3.7 °C/W

Junction-to-top characterization parameter 0.2 °C/W

Junction-to-board characterization parameter 3.7 °C/W

Junction-to-case (bottom) thermal resistance 0.5 °C/W

(1)

RTQ Package (VQFN)

56 PINS

VALUE

±2000

± 500

UNIT

V

UNIT

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

Product Folder Links: TPS23882

7

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

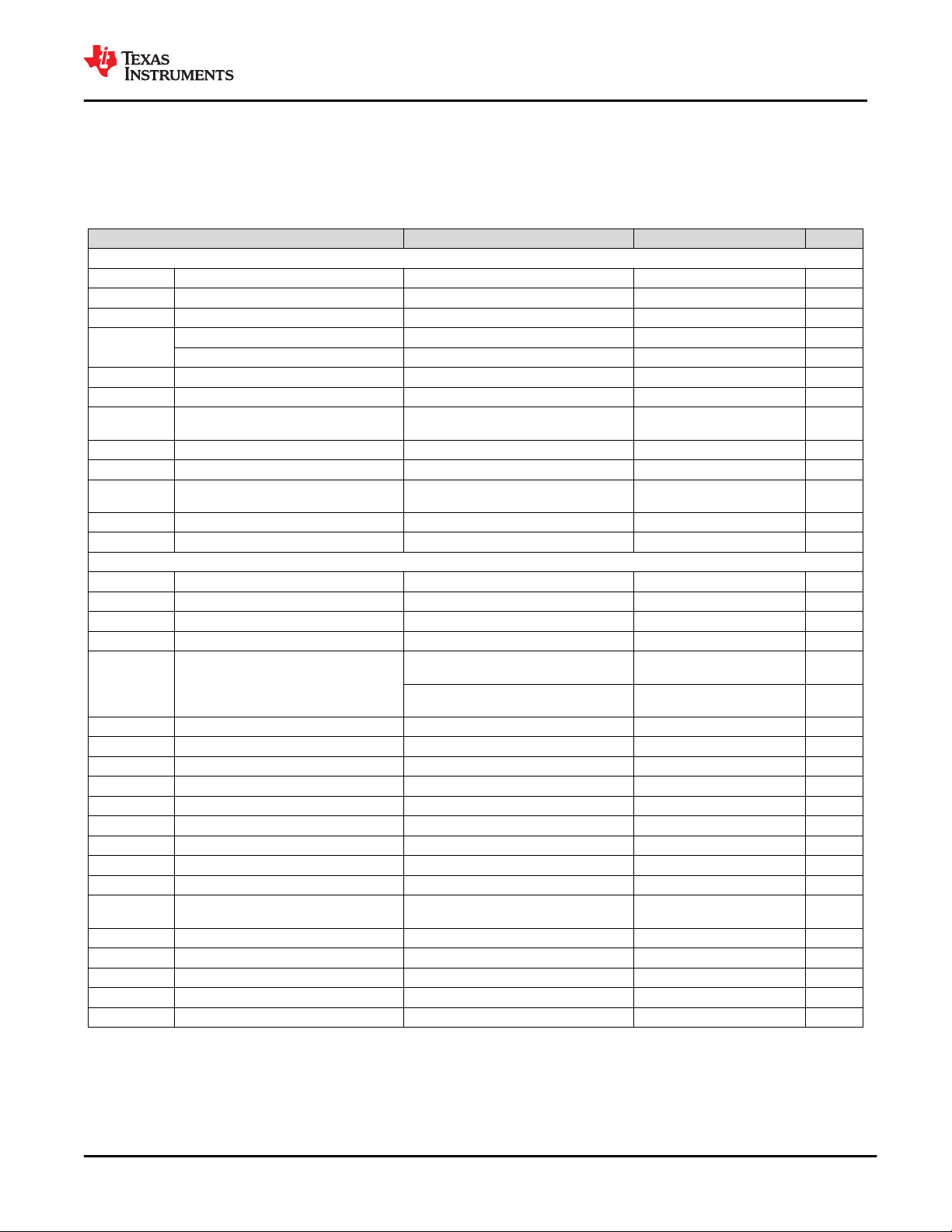

7.5 Electrical Characteristics

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

INPUT SUPPLY VPWR

I

VPWR

V

UVLOPW_F

V

UVLOPW_R

V

PUV_F

INPUT SUPPLY VDD

I

VDD

V

UVDD_F

V

UVDD_R

V

UVDD_HYS

V

UVW_F

A/D CONVERTERS

T

CONV_I

T

CONV_V

T

INT_CUR

T

INT_DET

T

INT_channelV

T

INT_inV

δV/V

Channel

δI/I

Channel

δR/R

Channel

I

bias

VPWR Current consumption VVPWR = 54 V 10 12.5 mA

VPWR UVLO falling threshold Check internal oscillator stops operating 14.5 17.5 V

VPWR UVLO rising threshold 15.5 18.5 V

VPWR Undervoltage falling threshold VPUV threshold 25 26.5 28 V

VDD Current consumption 6 12 mA

VDD UVLO falling threshold For channel deassertion 2.1 2.25 2.4 V

VDD UVLO rising threshold 2.45 2.6 2.75 V

Hysteresis VDD UVLO 0.35 V

VDD UVLO warning threshold VDD falling 2.6 2.8 3 V

Conversion time All ranges, each channel 0.64 0.8 0.96 ms

Conversiontime All ranges, each channel 0.82 1.03 1.2 ms

Integration time, Current Each channel, channel ON current 82 102 122 ms

Integration time, Detection 13.1 16.6 20 ms

Integration time, Channel Voltage channel powered 3.25 4.12 4.9 ms

Integration time, Input Voltage 3.25 4.12 4.9 ms

Input voltage conversion scale factor and

accuracy

Powered Channel voltage conversion scale

factor and accuracy

Voltage reading accuracy –2.5 2.5 %

Powered Channel current conversion scale

factor and accuracy

Current reading accuracy

Resistance reading accuracy 15 kΩ ≤ R

Sense Pin bias current Channel ON or during class –2.5 0 µA

VVPWR = 57 V

VVPWR = 44 V

VVPWR - VDRAINn = 57 V

VVPWR - VDRAINn = 44 V

Channel current = 770 mA

Channel Current = 100 mA

Channel Current =100 mA –3 3

Channel Current =770 mA –2 2

Channel

≤ 33 kΩ, C

≤ 0.25 µF –7 7 %

Channel

15175 15565 15955 Counts

55.57 57 58.43 V

11713 12015 12316 Counts

42.89 44 45.10 V

15175 15565 15955 Counts

55.57 57 58.43 V

11713 12015 12316 Counts

42.89 44 45.10 V

8431 8604 8776 Counts

754.5 770 785.4 mA

1084 1118 1152 Counts

97 100 103 mA

%

8 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

7.5 Electrical Characteristics (continued)

TPS23882

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

GATE 1-8

V

GOH

I

GO-

I

GO short-

I

GO+

t

D_off_OSS

t

OSS_OFF

t

P_off_CMD

t

P_off_RST

DRAIN 1-8

V

PGT

V

SHT

R

DRAIN

AUTOCLASS

t

Class_ACS

t

AUTO_PSE1

t

AUTO

t

AUTO_window

P

AC

Gate drive voltage V

Gate sinking current with Power-on Reset,

OSS detected or channel turnoff command

Gate sinking current with channel short-circuit

Gate sourcing current V

Gate turnoff time from 1-bit OSS input

Gate turnoff time from 3-bit OSS input

Gate turnoff time from channel turnoff

command

Gate turnoff time with /RESET

Power-Good threshold Measured at V

Shorted FET threshold Measured at V

, I

GATEn

V

GATEn

V

GATEn

V

SENn

GATEn

From OSS to VGATEn < 1 V,

VSENn = 0 V, MbitPrty = 0

From Start bit falling edge to VGATEn < 1 V,

VSENn = 0 V, MbitPrty = 1

= -1 µA 10 12.5 V

GATE

= 5 V 60 100 190 mA

= 5 V,

≥ V

short

(or V

short2X

if 2X mode)

60 100 190 mA

= 0 V, default selection 39 50 63 µA

1 5 µs

72 104 µs

From Channel off command (POFFn = 1) to

V

< 1 V, V

GATEn

From /RESET low to V

V

SENn

DRAINn

DRAINn

= 0 V

GATEn

< 1 V, V

SENn

= 0

1 5 µs

1 2.13 3 V

4 6 8 V

300 µs

Any operating mode except during detection

Resistance from DRAINn to VPWR

or while the Channel is ON, including in

80 100 190 kΩ

device RESET state

Start of Autoclass Detection Measured from the start of Class 90 100 ms

Measured from the end of Inrush 1.4 1.6 s

Start of Autoclass Power Measurement

Measured from setting the MACx bit while

channel is already powered

10 ms

Duration of Autoclass Power Measurement 1.7 1.8 1.9 s

Autoclass Power Measurement Sliding

Window

Autoclass Channel Power conversion scale

factor and accuracy

VPWR = 52 V, VDRAINn = 0 V,

Channel current = 770 mA

VPWR = 50 V, VDRAINn = 0 V,

Channel current = 100 mA

0.15 0.3 s

76 80 84 Counts

9 10 11

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

9

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

7.5 Electrical Characteristics (continued)

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DETECTION

I

DISC

ΔI

DISC

V

det_open

R

REJ_LOW

R

REJ_HI

R

ACCEPT

R

SHORT

R

OPEN

t

DET

t

DET_BOFF

t

DET_DLY

CLASSIFICATION

V

CLASS

I

CLASS_Lim

I

CLASS_TH

t

LCE

t

CLE2/3

MARK

V

MARK

I

MARK_Lim

t

ME

First and 3rd detection points

Detection current

2nd – 1st detection currents VVPWR - VDRAINn = 0 V 98 110 118 µA

Open circuit detection voltage Measured as VVPWR - VDRAINn 23.5 26 29 V

Rejected resistance low range 0.86 15 kΩ

Rejected resistance high range 33 100 kΩ

Accepted resistance range 19 25 26.5 kΩ

Shorted Channel threshold 360 Ω

Open Channel Threshold 400 kΩ

Detection Duration Time to complete a detection 275 350 425 ms

Detect backoff pause between discovery

attempts

Detection delay

Capacitance Measurement Cport = 10uF 8.5 10 11.5 uF

Classification Voltage

Classification Current Limit VVPWR - VDRAINn = 0 V 65 75 90 mA

Classification Threshold Current

Classification Duration (1st Finger) From detection complete 95 105 ms

Classification Duration (2nd & 3th Finger) From Mark complete 6.5 12 ms

Mark Voltage

Mark Sinking Current Limit VVPWR - VDRAINn = 0 V 60 75 90 mA

Mark Duration 6 12 ms

VVPWR - VDRAINn = 0 V

2nd and 4th detection points VVPWR VDRAINn = 0 V

VVPWR - VDRAINn > 2.5 V 300 400 500 ms

VVPWR - VDRAINn < 2.5 V 20 100 ms

From command or PD attachment to Channel

detection complete

VVPWR - VDRAINn, VSENn ≥ 0 mV

I

≥ 180 µA

channel

Class 0-1 5 8 mA

Class 1-2 13 16 mA

Class 2-3 21 25 mA

Class 3-4 31 35 mA

Class 4-Class overcurrent 45 51 mA

4 mA ≥ I

VVPWR - VDRAINn

Channel

≥ 180 µA

145 160 190

µA

235 270 300

590 ms

15.5 18.5 20.5 V

7 10 V

10 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

7.5 Electrical Characteristics (continued)

TPS23882

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DC DISCONNECT

V

IMIN

t

MPDO

t

MPS

PORT POWER POLICING

δP

CUT/PCUT

δP

CUT/PCUT

t

OVLD

PORT CURRENT INRUSH

V

Inrush

t

START

DC disconnect threshold 0.8 1.3 1.8 mV

TMPDO = 00 320 400 ms

PD Maintain Power signature dropout time

limit

PD Maintain Power Signature time for validity 2.5 3 ms

PCUT tolerance POL ≤ 15W 0 5 10 %

PCUT tolerance 15W < POL < 60W 0 3 6 %

PCUT time limit

IInrush limit, ALTIRNn = 0

IInrush limit, ALTIRNn = 1

Maximum current limit duration in start-up

TMPDO = 01 75 100 ms

TMPDO = 10 150 200 ms

TMPDO = 11 600 800 ms

TOVLD = 00 50 70

TOVLD = 01 25 35

TOVLD = 10 100 140

TOVLD = 11 200 280

VVPWR - VDRAINn = 1 V 19 30 41

VVPWR - VDRAINn = 10 V 19 30 41

VVPWR - VDRAINn = 15 V 33 44 55

VVPWR - VDRAINn = 30 V 80 90

VVPWR - VDRAINn = 55 V 80 90

VVPWR - VDRAINn = 1 V 19 30 41

VVPWR - VDRAINn = 10 V 36 47 58

VVPWR - VDRAINn = 15 V 53 64 75

VVPWR - VDRAINn = 30 V 80 90

VVPWR - VDRAINn = 55 V 80 90

TSTART = 00 50 70

TSTART = 10 100 140

ms

mV

msTSTART = 01 25 35

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

11

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

7.5 Electrical Characteristics (continued)

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

PORT CURRENT FOLDBACK

VDRAINn = 1 V 80 90

ILIM 1X limit, 2xFB = 0 and ALTFBn = 0

V

LIM

ILIM 1X limit, 2xFB = 0 and ALTFBn = 1

ILIM 2X limit, 2xFB = 1 and ALTFBn = 0

V

LIM2X

ILIM 2X limit, 2xFB = 1 and ALTFBn = 1

ILIM time limit 2xFBn = 0 55 60 65

t

LIM

SHORT CIRCUIT DETECTION

V

short

V

short2X

t

D_off_SEN

CURRENT FAULT RECOVERY (BACKOFF) TIMING

t

ed

δI

fault

THERMAL SHUTDOWN

2xFBn = 1

I

threshold in 1X mode and during

SHORT

inrush

I

threshold in 2X mode 280 320

SHORT

Gate turnoff time from SENn input

Error delay timing. Delay before next attempt

to power a channel following power removal

due to error condition

Duty cycle of I

Shutdown temperature Temperature rising 135 146 °C

Hysteresis 7 °C

with current fault 5.5 6.7 %

channel

VDRAINn = 15 V 80 90

VDRAINn = 30 V 51 58 65

VDRAINn = 50 V 23 30 37

VDRAINn = 1 V 80 90

VDRAINn = 25 V 80 90

VDRAINn = 40 V 45 51 57

VDRAINn = 50 V 23 30 37

VDRAINn = 1 V 245 250 262

VDRAINn = 10 V 164 180 196

VDRAINn = 30 V 51 58 64

VDRAINn = 50 V 23 30 37

VDRAINn = 1 V 245 250 262

VDRAINn = 20 V 139 147 155

VDRAINn = 40 V 45 51 57

VDRAINn = 50 V 23 30 37

TLIM = 00 55 60 65

TLIM = 01 15 16 17

TLIM = 10 10 11 12

TLIM = 11 6 6.5 7

205 245

2xFBn = 0, VDRAINn = 1 V

From VSENn pulsed to 0.425 V.

2xFBn = 1, VDRAINn = 1 V

From VSENn pulsed to 0.62 V.

P

, I

or I

CUT

LIM

fault Semi-auto mode 0.8 1 1.2 s

Inrush

0.9

0.9

mV

mV

ms

mV

µs

12 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

7.5 Electrical Characteristics (continued)

TPS23882

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V,V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

,DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

DIGITAL I/O (SCL, SDAI, A1-A4, /RESET, OSS unless otherwise stated)

V

IH

V

IL

V

IT_HYS

V

OL

R

pullup

R

pulldown

t

FLT_INT

T

RESETmin

T

bit_OSS

t

OSS_IDL

t

r_OSS

t

f_OSS

I2C TIMING REQUIREMENTS

t

POR

f

SCL

t

LOW

t

HIGH

t

fo

C

I2C

C

I2C_SDA

t

SU,DATW

t

HD,DATW

t

HD,DATR

t

fSDA

t

rSDA

t

r

t

f

t

BUF

t

HD,STA

t

SU,STA

t

SU,STO

t

DG

t

WDT_I2C

Digital input High 2.1 V

Digital input Low 0.9 V

Input voltage hysteresis 0.17 V

Digital output Low SDAO at 9mA 0.4 V

Digital output Low /INT at 3mA 0.4 V

Pullup resistor to VDD /RESET, A1-A4, TEST0 30 50 80 kΩ

Pulldown resistor to DGND OSS, TEST1, TEST2 30 50 80 kΩ

Fault to /INT assertion

Time to internally register an Interrupt fault,

from Channel turn off

50 500 µs

/RESET input minimum pulse width 5 µs

3-bit OSS bit period MbitPrty = 1 24 25 26 µs

Idle time between consecutive shutdown code

transmission in 3-bit mode

MbitPrty = 1 48 50 µs

Input rise time of OSS in 3-bit mode 0.8 V → 2.3 V, MbitPrty = 1 1 300 ns

Input fall time of OSS in 3-bit mode 2.3 V → 0.8 V, MbitPrty = 1 1 300 ns

Device power-on reset delay 20 ms

SCL clock frequency 10 400 kHz

LOW period of the clock 0.5 µs

HIGH period of the clock 0.26 µs

SDAO output fall time

SDAO, 2.3 V → 0.8 V, Cb = 10 pF, 10 kΩ pullup to 3.3 V

SDAO, 2.3 V → 0.8 V, Cb = 400 pF, 1.3 kΩ

pull-up to 3.3 V

10 50 ns

10 50 ns

SCL capacitance 10 pF

SDAI, SDAO capacitance 6 pF

Data setup tme (Write operation) 50 ns

Data hold time (Write operation) 0 ns

Data hold time (Read operation) 150 400 ns

Input fall times of SDAI 2.3 V → 0.8 V 20 120 ns

Input rise times of SDAI 0.8 V → 2.3 V 20 120 ns

Input rise time of SCL 0.8 V → 2.3 V 20 120 ns

Input fall time of SCL 2.3 V → 0.8 V 20 120 ns

Bus free time between a STOP and START

condition

0.5 µs

Hold time After (Repeated) START condition 0.26 µs

Repeated START condition setup time 0.26 µs

STOP condition setup time 0.26 µs

Suppressed spike pulse width, SDAI and SCL 50 ns

I2C Watchdog trip delay 1.1 2.2 3.3 sec

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

13

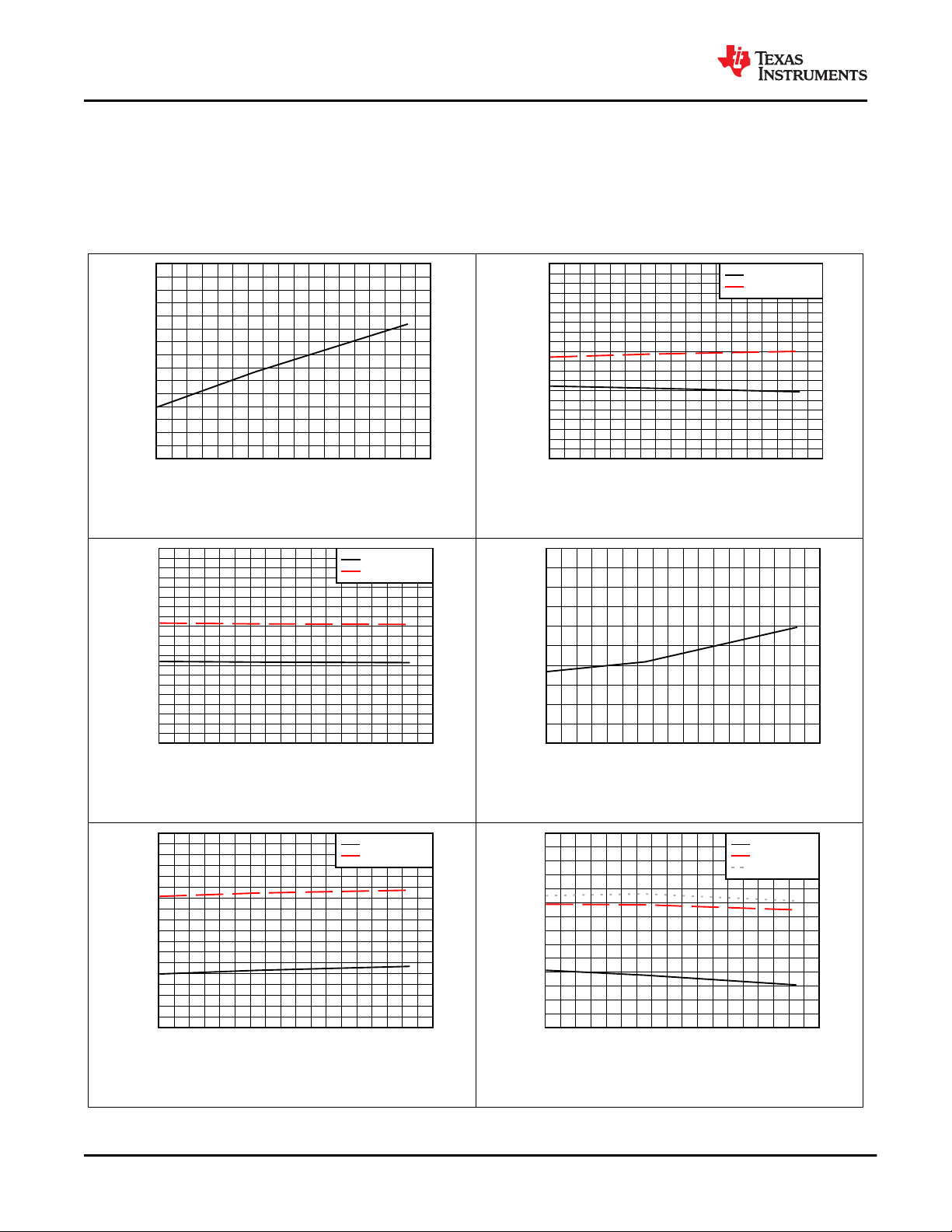

Temperature (qC)

I

VPWR

(mA)

-40 -20 0 20 40 60 80 100 120 140

6.8

7

7.2

7.4

7.6

7.8

8

8.2

8.4

8.6

8.8

9

9.2

9.4

9.6

9.8

D001

Temperature (qC)

V

VPWR

(V)

-40 -20 0 20 40 60 80 100 120 140

14

14.5

15

15.5

16

16.5

17

17.5

18

18.5

19

D002

VUVLO_Falling

VUVLO_Rising

Temperature (qC)

V

VPWR

(V)

-40 -20 0 20 40 60 80 100 120 140

24

24.6

25.2

25.8

26.4

27

27.6

28.2

28.8

29.4

30

D003

VPUV_Falling

VPUV_Rising

Temperature (qC)

I

VDD

(mA)

-40 -20 0 20 40 60 80 100 120 140

3.5

3.75

4

4.25

4.5

4.75

5

5.25

5.5

5.75

6

D004

Temperature (qC)

V

VDD

(V)

-40 -20 0 20 40 60 80 100 120 140

2

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

D005

VDUV_Falling

VDUV_Rising

Temperature (qC)

I

SENSE

( PA)

-40 -20 0 20 40 60 80 100 120 140

-1.2

-1.1

-1

-0.9

-0.8

-0.7

-0.6

-0.5

-0.4

-0.3

-0.2

-0.1

0

0.1

0.2

D006

Classification

Port On

Port Off

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

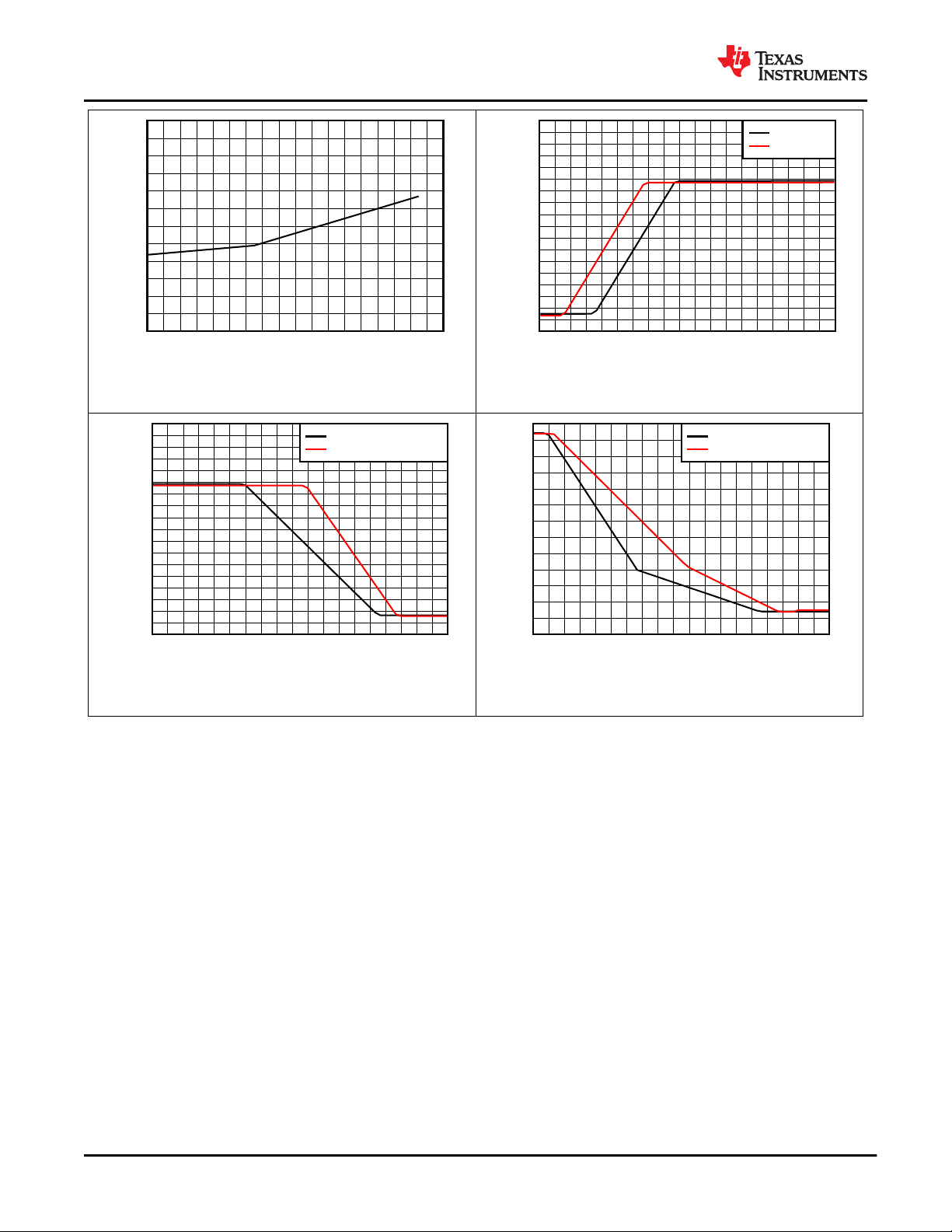

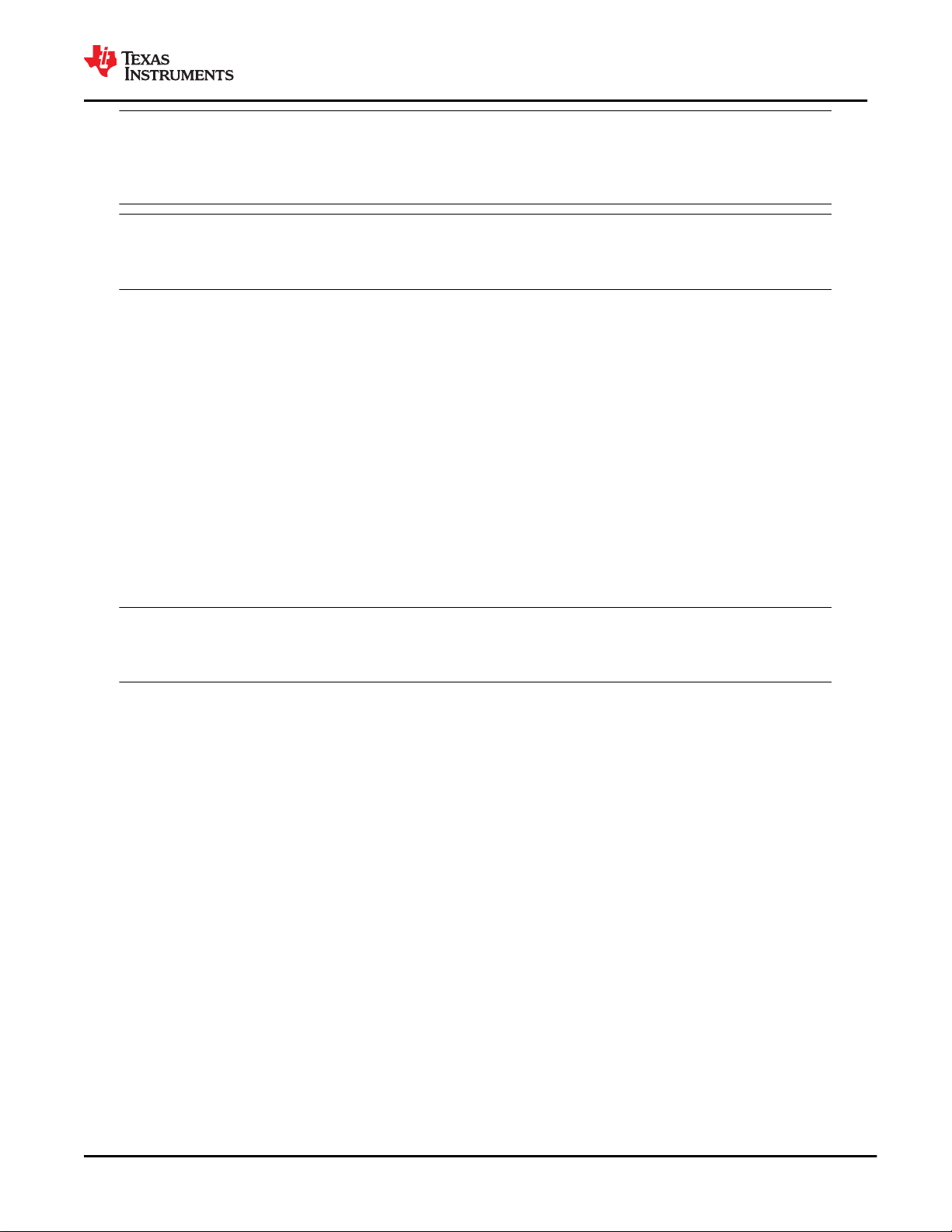

7.6 Typical Characteristics

www.ti.com

Conditions are –40 < TJ < 125 °C unless otherwise noted.V

= 3.3 V, V

VDD

VPWR

= 54 V, V

DGND

= V

AGND

, DGND,

KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0.

Positive currents are into pins. RS = 0.200 Ω, to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to

KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with

respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

Figure 7-1. VPWR Current Consumption vs

Temperature

Figure 7-2. VPWR UVLO Thresholds vs

Temperature

Figure 7-3. VPUV Thresholds vs Temperature

Figure 7-5. VDUV Thresholds vs Temperature

14 Submit Document Feedback

Figure 7-4. VDD Current Consumption vs

Temperature

Figure 7-6. SENSE Pin Bias Current vs

Temperature

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

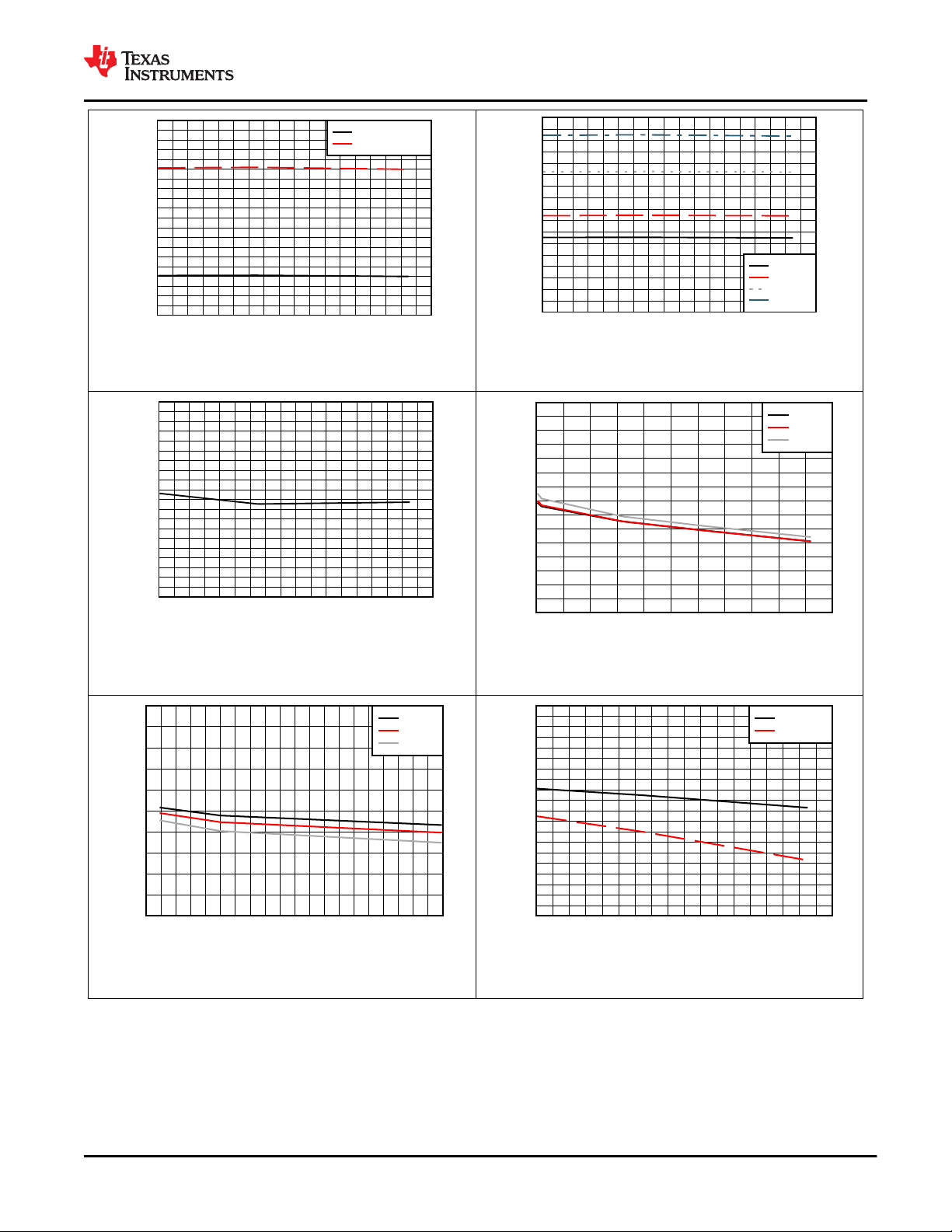

Temperature (qC)

I

DRAIN

(PA)

-40 -20 0 20 40 60 80 100 120 140

120

140

160

180

200

220

240

260

280

300

320

D007

Idiscovery_low

Idiscovery_high

Temperature (qC)

R

DET

(k:)

-40 -20 0 20 40 60 80 100 120 140

2

6

10

14

18

22

26

30

34

D008

15 k:

19 k:

26.5 k:

33 k:

Temperature (qC)

V

PORT

(V)

-40 -20 0 20 40 60 80 100 120 140

24

24.2

24.4

24.6

24.8

25

25.2

25.4

25.6

25.8

26

D009

I

CLASS

(mA)

V

CLASS

(V)

0 5 10 15 20 25 30 35 40 45 50 55

18

18.1

18.2

18.3

18.4

18.5

18.6

18.7

18.8

18.9

19

19.1

19.2

19.3

19.4

19.5

D010

-40 qC

25 qC

125 qC

I

MARK

(mA)

V

MARK

(V)

0 0.4 0.8 1.2 1.6 2 2.4 2.8 3.2 3.6 4

8.5

8.6

8.7

8.8

8.9

9

9.1

9.2

9.3

9.4

9.5

D011

-40 qC

25 qC

125 qC

Temperature (qC)

I

LIM

(mA)

-40 -20 0 20 40 60 80 100 120 140

70

70.8

71.6

72.4

73.2

74

74.8

75.6

76.4

77.2

78

D012

Class I

LIM

Mark I

LIM

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

Figure 7-7. Discovery Currents vs Temperature

Figure 7-9. Discovery Open Circuit Voltage vs

Temperature

Figure 7-8. Discovery Resistance Measurement vs

Temperature

Figure 7-10. Classification Voltage vs I

CLASS

and

Temperature

Figure 7-11. Mark Voltage vs I

Copyright © 2020 Texas Instruments Incorporated

Temperature

MARK

and

Figure 7-12. Classification and Mark Current Limit

Product Folder Links: TPS23882

vs Temperature

Submit Document Feedback

15

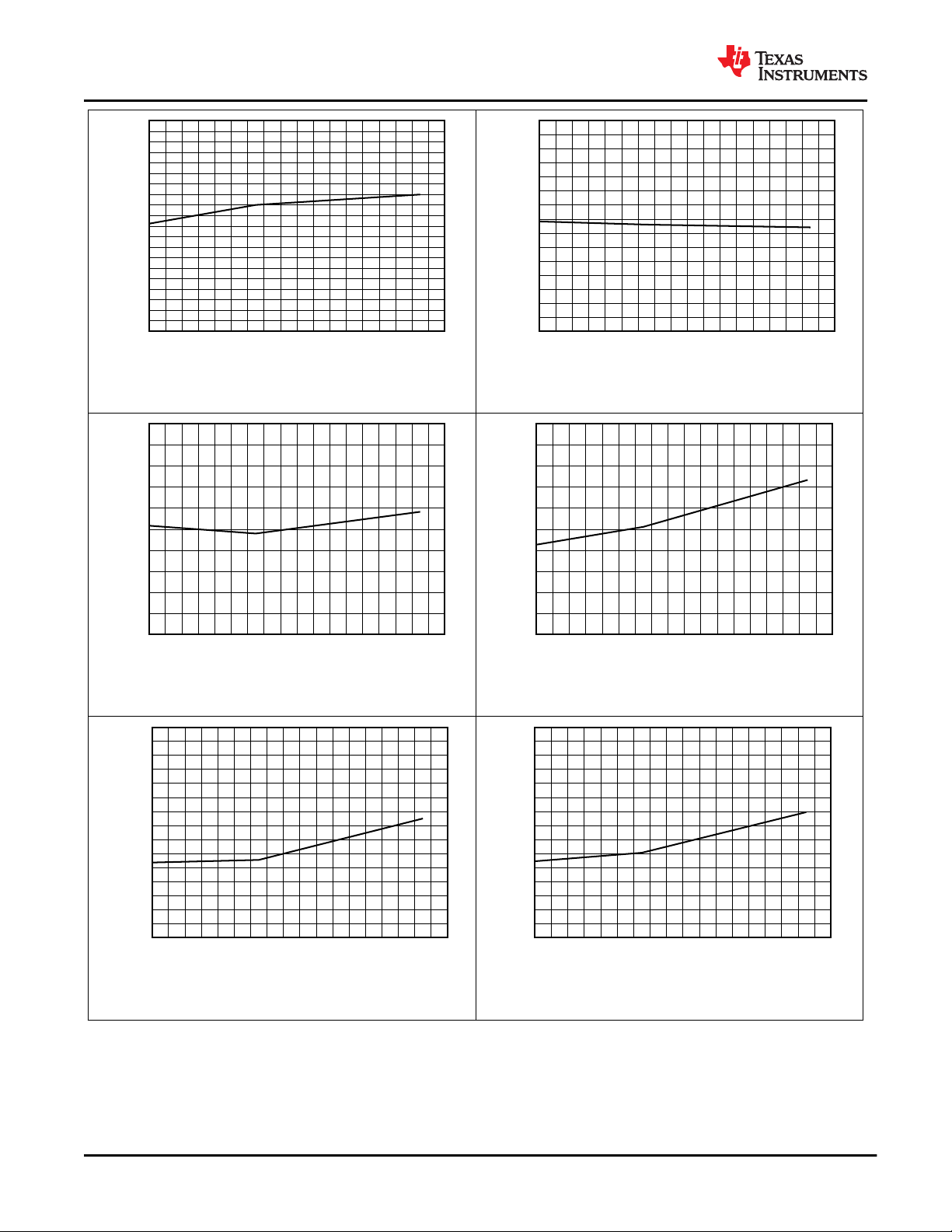

Temperature (qC)

V

PORT

(V)

-40 -20 0 20 40 60 80 100 120 140

1.8

1.86

1.92

1.98

2.04

2.1

2.16

2.22

2.28

2.34

2.4

D013

Temperature (qC)

V

GATE

(V)

-40 -20 0 20 40 60 80 100 120 140

11.3

11.32

11.34

11.36

11.38

11.4

11.42

11.44

11.46

11.48

11.5

11.52

11.54

11.56

11.58

11.6

D014

Temperature (q C)

Port Voltage (V)

-40 -20 0 20 40 60 80 100 120 140

56.5

56.6

56.7

56.8

56.9

57

57.1

57.2

57.3

57.4

57.5

D015

Temperature (qC)

VPWR Voltage (V)

-40 -20 0 20 40 60 80 100 120 140

56.5

56.6

56.7

56.8

56.9

57

57.1

57.2

57.3

57.4

57.5

D016

Temperature (qC)

I

PORT

Measurement (mA)

-40 -20 0 20 40 60 80 100 120 140

99.5

99.6

99.7

99.8

99.9

100

100.1

100.2

100.3

100.4

100.5

100.6

100.7

100.8

100.9

101

D017

Temperature (qC)

I

PORT

Measurement (mA)

-40 -20 0 20 40 60 80 100 120 140

765

766

767

768

769

770

771

772

773

774

775

776

777

778

779

780

D018

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

Figure 7-13. Power Good Threshold vs

Temperature

Figure 7-15. Port Voltage ADC Measurement vs

Temperature

Figure 7-14. Gate Voltage (Port On) vs Temperature

Figure 7-16. VPWR Voltage ADC Measurement vs

Temperature

Figure 7-17. Port Current ADC Measurement

(100mA) vs Temperature

16 Submit Document Feedback

Product Folder Links: TPS23882

Figure 7-18. Port Current ADC Measurement

(770mA) vs Temperature

Copyright © 2020 Texas Instruments Incorporated

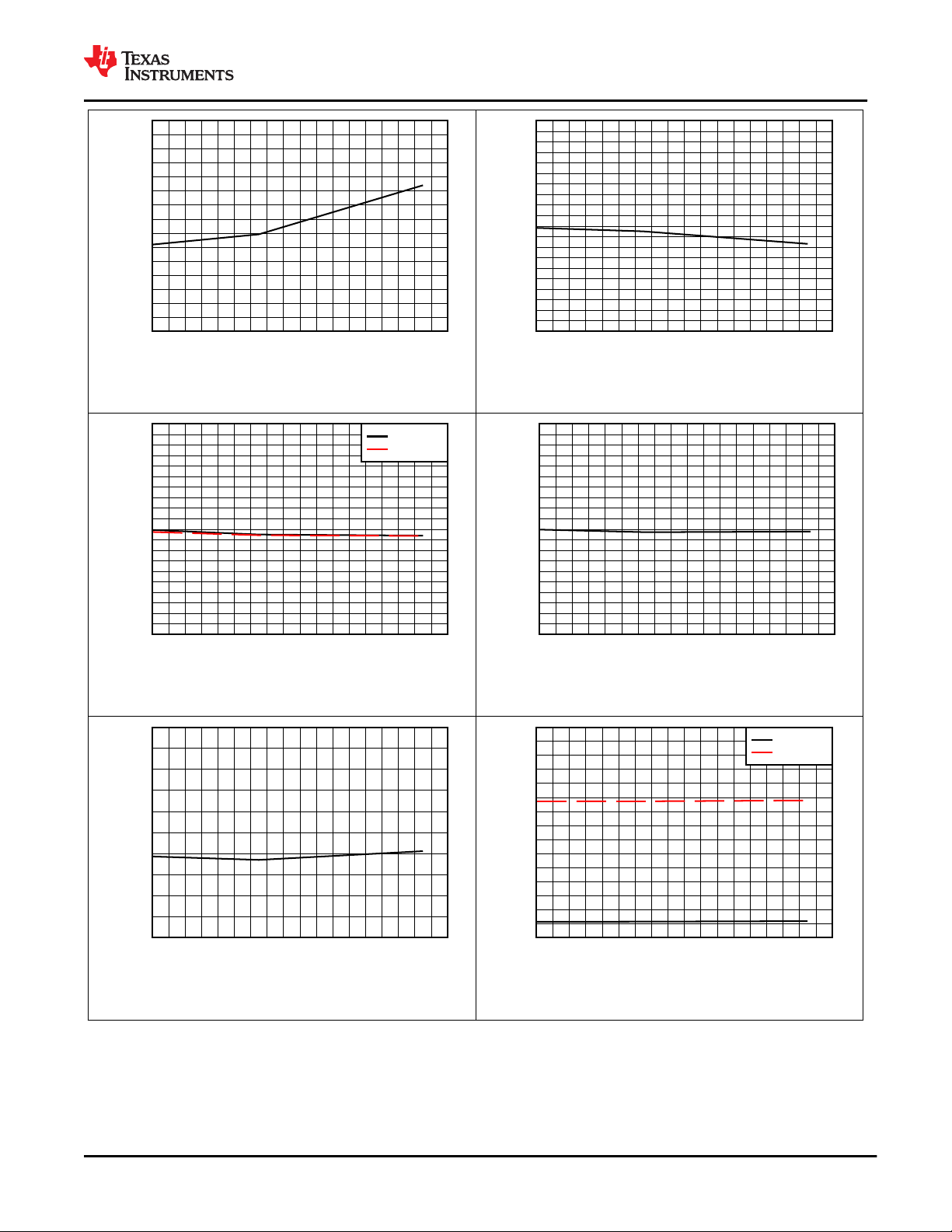

Temperature (qC)

I

PORT

Measurement (A)

-40 -20 0 20 40 60 80 100 120 140

0.995

0.996

0.997

0.998

0.999

1

1.001

1.002

1.003

1.004

1.005

1.006

1.007

1.008

1.009

1.01

D019

Temperature (qC)

P

PCUT

(W)

-40 -20 0 20 40 60 80 100 120 140

30

30.2

30.4

30.6

30.8

31

31.2

31.4

31.6

31.8

32

D020

Temperature (qC)

I

LIM-Inrush

(mA)

-40 -20 0 20 40 60 80 100 120 140

418

418.8

419.6

420.4

421.2

422

422.8

423.6

424.4

425.2

426

D023

2xFBn = 0

2xFBn = 1

Temperature (qC)

I

LIM

(mA)

-40 -20 0 20 40 60 80 100 120 140

418

418.8

419.6

420.4

421.2

422

422.8

423.6

424.4

425.2

426

D024

Temperature (qC)

I

LIM

(A)

-40 -20 0 20 40 60 80 100 120 140

1.24

1.241

1.242

1.243

1.244

1.245

1.246

1.247

1.248

1.249

1.25

D025

Temperature (qC)

I

Port

(A)

-40 -20 0 20 40 60 80 100 120 140

1

1.05

1.1

1.15

1.2

1.25

1.3

1.35

1.4

1.45

1.5

1.55

1.6

1.65

1.7

1.75

D026

2xFBn = 0

2xFBn = 1

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

Figure 7-19. Port Current ADC Measurement (1 A)

vs Temperature

Figure 7-21. Inrush Current Limit vs Temperature

Figure 7-20. PCut Threshold (30W) vs Temperature

Figure 7-22. 1x Mode (2xFBn = 0) Current Limit vs

Temperature

Figure 7-23. 2x Mode (2xFBn = 1) Current Limit vs

Temperature

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Figure 7-24. I

Threshold vs Temperature

SHORT

Submit Document Feedback

17

Temperature (qC)

R

VPWR-DRAIN

(k:)

-40 -20 0 20 40 60 80 100 120 140

100

101

102

103

104

105

106

107

108

109

110

111

112

D027

V

PORT

(V)

I

PORT

(A)

0 6 12 18 24 30 36 42 48 54

0.1

0.15

0.2

0.25

0.3

0.35

0.4

0.45

0.5

0.55

D028

ALTIRn = 0

ALTIRn = 1

V

DRAIN

(V)

I

PORT

(A)

0 6 12 18 24 30 36 42 48 54

0.1

0.15

0.2

0.25

0.3

0.35

0.4

0.45

0.5

0.55

D029

2xFBn =0, ALTFBn = 0

2xFBn =0, ALTFBn = 1

V

DRAIN

(V)

I

PORT

(A)

0 6 12 18 24 30 36 42 48 54

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

D030

2xFBn =1, ALTFBn = 0

2xFBn =1, ALTFBn = 1

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

Figure 7-25. R

(VPWR to DRAIN) vs

OFF

Temperature

Figure 7-27. 1x Mode (2xFBn = 0) Current Foldback

vs Drain Voltage

Figure 7-26. Inrush Current Foldback vs Port

Voltage

Figure 7-28. 2x Mode (2xFBn = 1) Current Foldback

vs Drain Voltage

18 Submit Document Feedback

Product Folder Links: TPS23882

Copyright © 2020 Texas Instruments Incorporated

t

fSDA

t

fo

Repeated

Start Condition

t

LOW

t

SU,DAT

t

HD,DAT

SCL

SDAI/

SDAO

t

r

t

f

t

rSDA

t

HIGH

Start Condition

Stop Condition

Start Condition

t

SU,STO

t

HD,STA

t

SU,STA

t

BUF

SEN

GATE

0 V

0 V

V

LIM

V

CUT

t

OVLD

www.ti.com

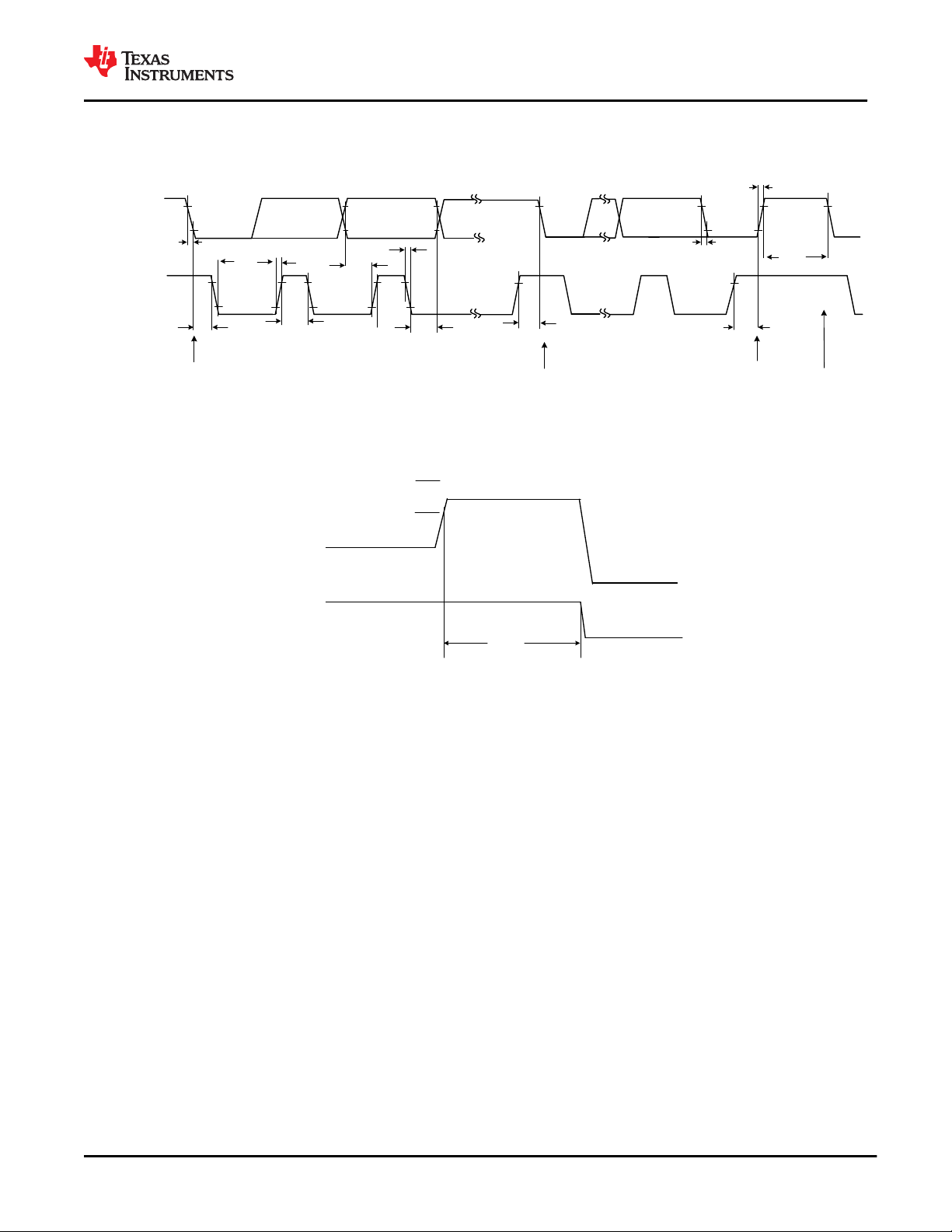

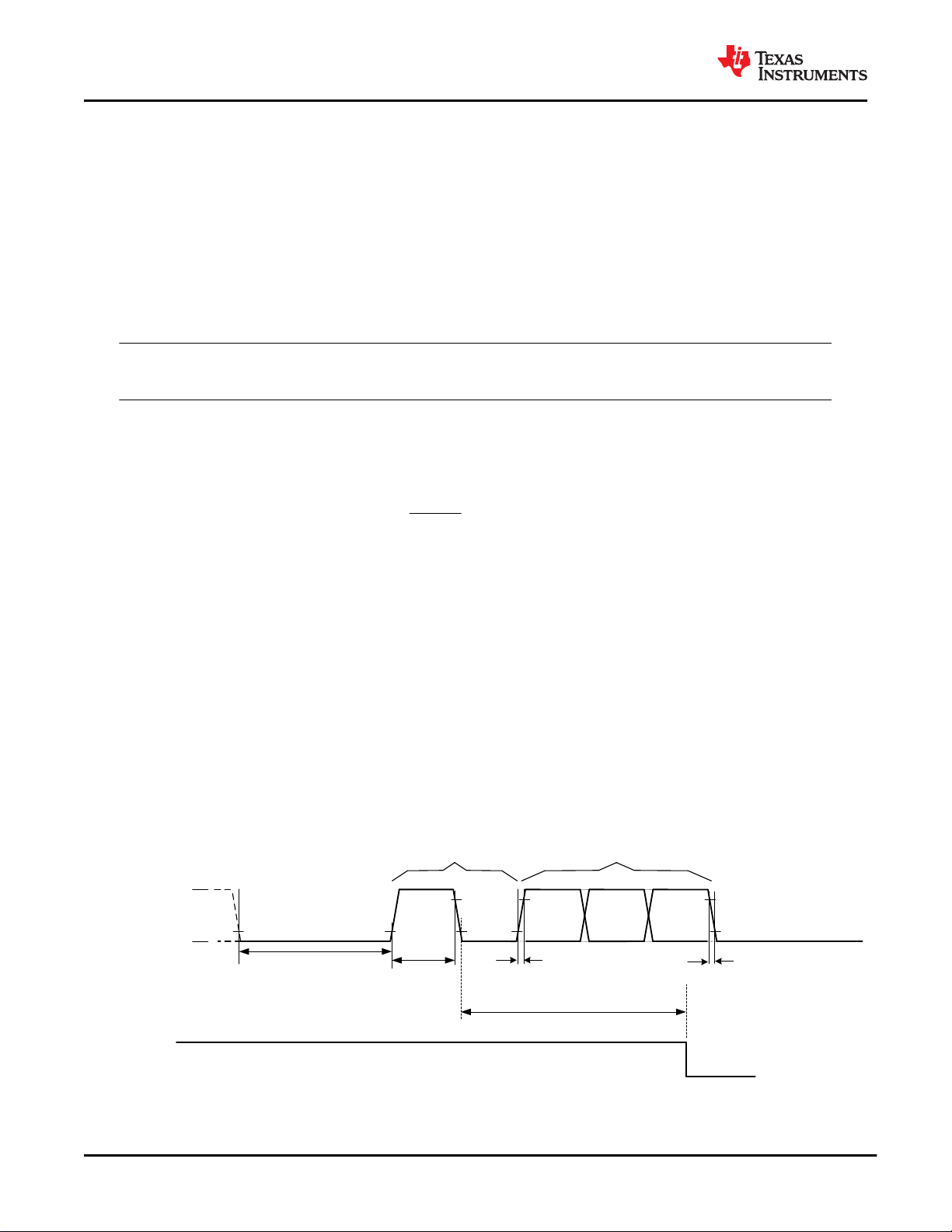

8 Parameter Measurement Information

8.1 Timing Diagrams

Figure 8-1. I2C Timings

SPACE

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

Figure 8-2. Overcurrent Fault Timing

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

19

t

pon

V

PORT

0 V

Four-point

detection

t

DET

t

CLE-1

Class

V

CLASS

V

MARK

Mark

Port turn-on

t

pon

V

PORT

0 V

Four-point

detection

t

DET

t

CLE-1

t

ME

Class

V

CLASS

V

MARK

Mark

Port turn-on

t

CLE

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

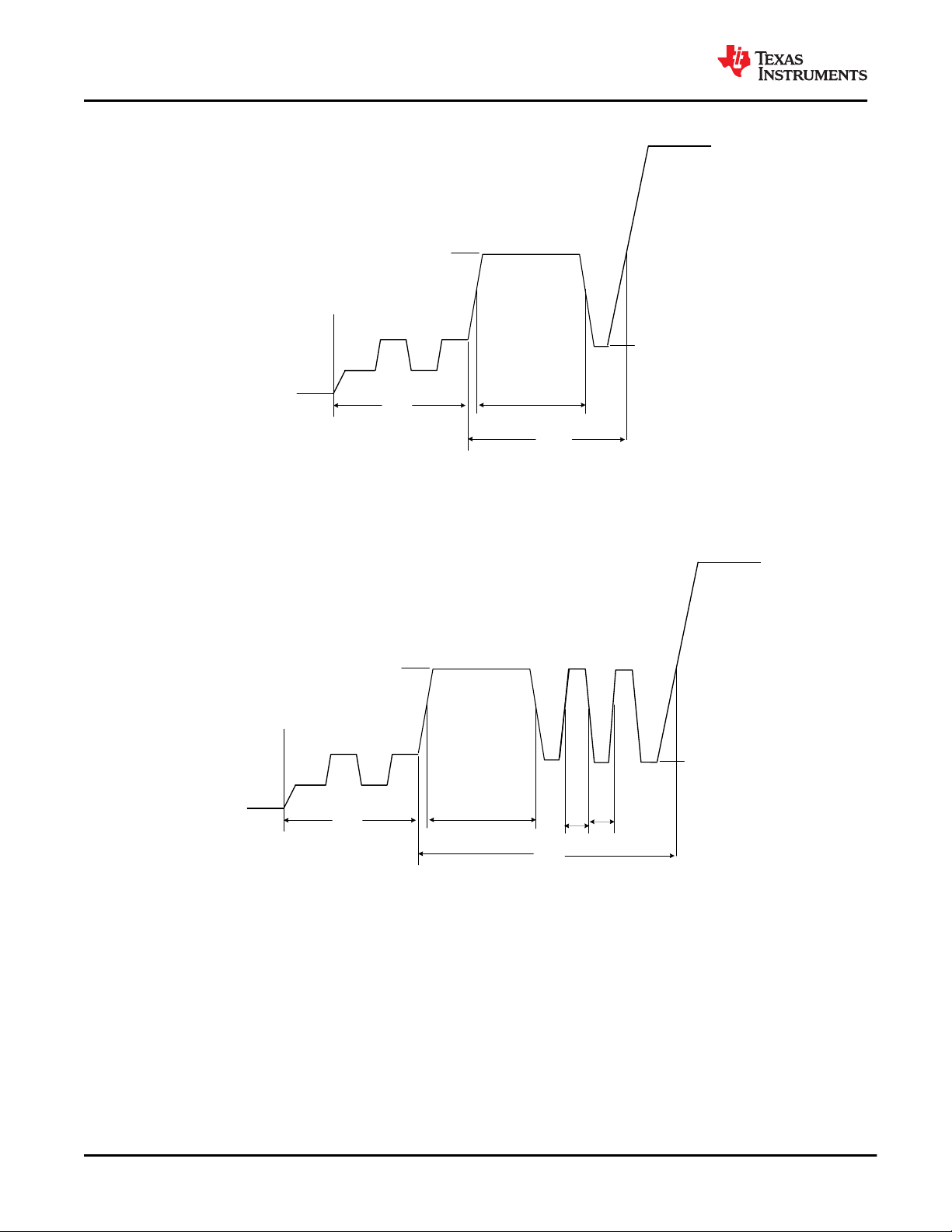

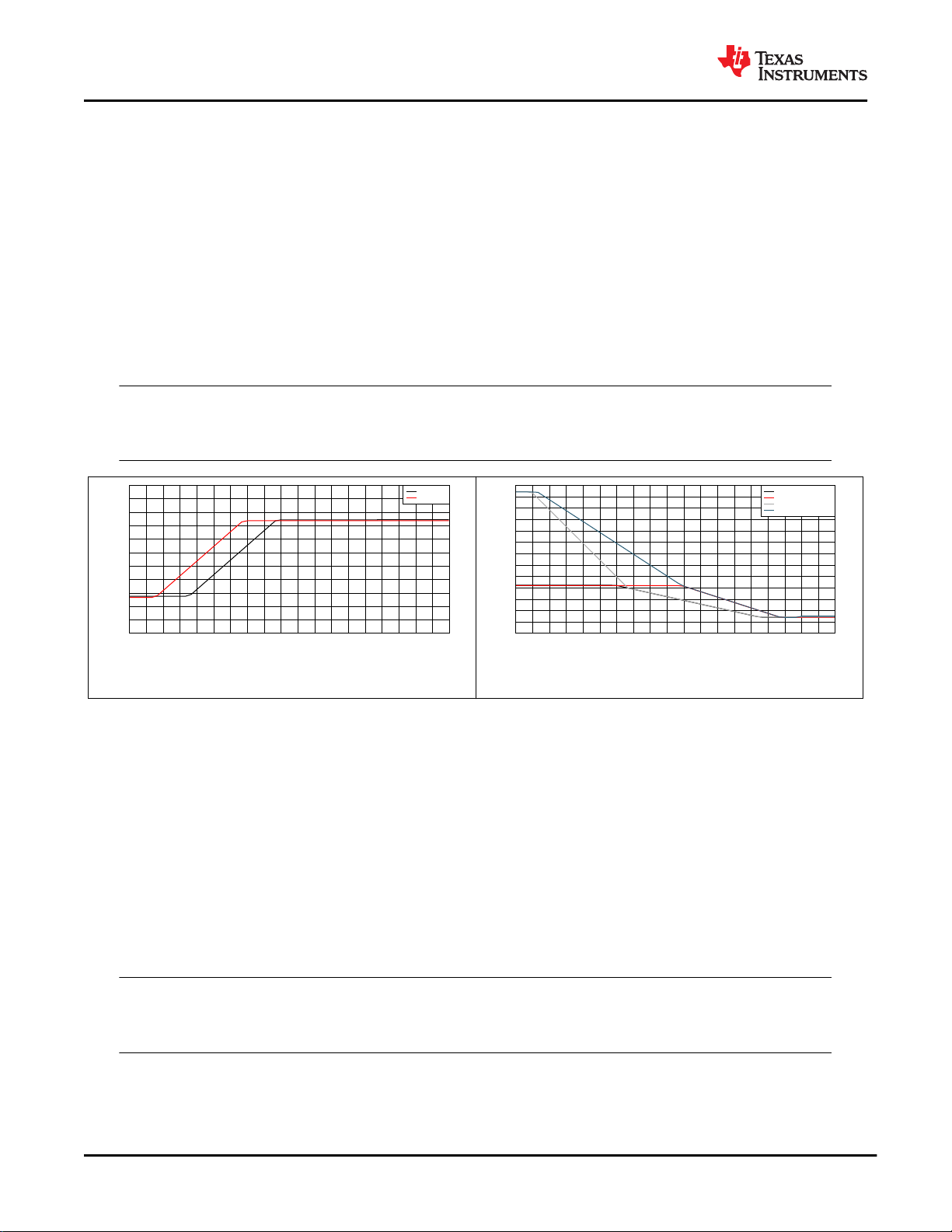

Figure 8-3. 2-Pair Detection, 1-Event Classification and Turn On

SPACE

www.ti.com

Figure 8-4. 2-Pair Detection, 3-Event Classification and Turn On

SPACE

20 Submit Document Feedback

Product Folder Links: TPS23882

Copyright © 2020 Texas Instruments Incorporated

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

9 Detailed Description

9.1 Overview

The TPS23882 is an eight-channel PSE for Power over Ethernet applications. Each of the eight channels

provides detection, classification, protection, and shutdown in compliance with the IEEE 802.3bt standard.

Basic PoE features include the following:

• Performs high-reliability 4-point load detection

• Performs multi-finger classification including the 100-ms long first class finger for Autoclass discovery and to

identify as a 802.3bt complainant PSE

• Enables power with protective fold-back current limiting, and an adjustable P

• Shuts down during faults such as overcurrent or outputs shorts

• Performs a maintain power signature function to ensure power is removed if the load is disconnected

• Undervoltage lockout occurs if VPWR falls below V

(typical 26.5 V).

PUV_F

Enhanced features include the following:

• Programable SRAM memory

• Dedicated 14-bit integrating current ADCs per port

• Port re-mapping capability

• 8- and 16-bit access mode selectable

• 1- and 3-bit port shutdown priority

threshold

CUT

9.1.1 Operating Modes

9.1.1.1 Auto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated

each time a detection or classification occurs. The port power is automatically turned on based on the Power

Allocation settings in register 0x29 if a valid classification is measured.

9.1.1.2 Semiauto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated

each time a detection or classification occurs. The port power is not automatically turned on. A Power Enable

command is required to turn on the port.

9.1.1.3 Manual/Diagnostic

The use of this mode is intended for system diagnostic purposes only in the event that ports cannot be

powered in accordance with the IEEE 802.3bt standard from Semiauto or Auto modes.

The port performs the functions as configured in the registers. There is no automatic state change. Singular

detection and classification measurements will be performed when commanded. Ports will be turned on

immediately after a Power Enable command without any detection or classification measurements. Even though

multiple classification events may be provided, the port voltage will reset immediately after the last finger,

resetting the PD.

9.1.1.4 Power Off

The port is powered off and does not perform a detection, classification, or power-on. In this mode, Status and

Enable bits for the associated port are reset.

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

21

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

9.1.2 PoE Compliance Terminology

With the release of the IEEE 802.3bt standard, compliant PoE equipment has expanded to include four different

"Types" of devices that support power over 2-Pair or 4-Pair, in either Single or Dual signature configurations, with

classifications ranging from 0 to 8. Different manufactures have used varying terminology over time to describe

their equipment capabilities, and it can become difficult to identify how to correctly categorize and brand a

particular piece of equipment. For this reason and in conjunction with the Ethernet Alliance (EA), the industry

leading providers of PoE equipment and devices have agreed to transition to using the "PoE 1" and "PoE 2"

banding per the table below Table 9-1.

SPACE

Table 9-1. Summary Table of PoE Compliance Terminology

Brand /

Acronym

PoE 1

PoE 2 802.3bt 145 Power over Ethernet

(1) "DS" is used to designate "Dual Signature" PDs

IEEE

Standard

802.3af

802.3at 2 0 - 4

Clause Clause Title Types Classes EA Certified Logo

33

Power over Ethernet over 2-

Pairs

1 0 - 3

3

4

1 - 6, or 1-4

7 - 8, or 5

DS

DS

Gen 1 Class 1-4

(1)

Gen 2 Class 1-8

(1)

Note

By design PoE 2 PSEs are fully interoperable with any existing PoE 1 equipment, and although not all

functionality may be enabled, PoE 2 PDs connected to PoE 1 PSEs are required to limit their power

consumption to the PSE presented power capabilities see Power Allocation and Power Demotion.

9.1.3 PoE 2 Type-3 2-Pair PoE

Upon release of the new IEEE 802.3bt standard, the IEEE introduced two new "Types" of PoE equipment. The

addition of Type-3 and Type-4 equipment are most commonly associated with the addition of 4-Pair PoE and

their available power increases of to up to 90 W sourced from a PSE port. However, the new PoE 2 Type-3

designation also applies to new 2-Pair PoE equipment as well. Most notably, the new 802.3bt standard supports

a reduced T

time (6 ms vs. 60 ms) and a new feature called Autoclass, and by definition any device that

MPS

supports these new features is designated as Type-3 equipment even if power is only provided over 2-pairs (one

alternative pairset) in an ethernet cable. Since the TPS23882 supports these new features including its use of

the 100ms long first class finger to identify itself as an IEEE 802.3bt PSE, it is officially classified as a Type-3

PSE even through power delivery is limited to 2-pair.

Please note that as the 802.3at standard created "type-2" equipment that was fully interoperable with the

previous PoE 1 Type-1 (802.3af) equipment, any new 802.3bt Type-3 equipment including the TPS23882 is fully

operable with any existing PoE 1 Type-1 (.af) and Type-2 (.at) equipment.

SPACE

22 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

9.1.4 Requested Class versus Assigned Class

The requested class is the classification the PSE measures during mutual identification prior to turnon, whereas

the assigned class is the classification level the channel was powered on with based on the power allocation

setting in register 0x29h. In most cases where the power allocation equals or exceeds the requested class, the

requested and assigned classes will be the same. However, in the case of power demotion, these values will

differ.

For example: If a 4-pair Class 8 PD is connected to a 30 W (Class 4) configured PSE port, the requested class

reports "Class 8", while the assigned class reports "Class 4".

The requested classification results are available in registers 0x0C-0F

The assigned classification results are available in registers 0x4C-4F

Note

There is no Assigned Class assigned for ports/channels powered out of Manual/Diagnostic mode.

9.1.5 Power Allocation and Power Demotion

The Power Allocation settings in register 0x29 sets the maximum power level a port will power on. Settings for

each Class level from 2-pair 4 W (Class 1) up to 2-pair 30 W (Class 4) have been provided to maximize system

design flexibility.

Note

The Power Allocation settings in register 0x29 do not set the power limit for a given port. The port and

channel power limiting is configured with the 2P (registers 0x1E- x 21) policing registers

During a turn on attempt, if a PD presents a classification level greater than the power allocation setting for a

port, the TPS23882 limits the number of classification fingers presented to the PD prior to turn on based on the

power allocation settings in register 0x29. This behavior is called Power Demotion as it is the number of fingers

presented to the PD that sets the maximum level of power the PD is allowed to draw before the PSE is allowed

to disable it.

Note

The IEEE 802.3 standard requires PDs that are power demoted by a PSE to limit their total power

draw below the Type/class level set by the number of fingers presented by the PSE during mutual

identification.

In a 2-pair system, Power demotion is limited to either 30 W (3-fingers) or 15.4 W (1-finger) as there is

no other physical means of indicating to a PD over the physical layer that less than 15.4 W is

available.

If register 0x29 is configured for either 4 W (class 1) or 7 W (Class 2), and a Class 3 or higher device

is connected, the port will not be powered and a Start Fault will be reported along with an "Insufficient

Power" indication provided in register 0x24.

Table 9-2. 2-Pair Power Demotion Table

Power Allocation

Register 0x29

2-Pair 4 W Class 1

2-Pair 7 W Class 1 Class 2

2-Pair 15.5 W Class 1 Class 2 Class 3 Class 3 Class 3

2-Pair 30 W Class 1 Class 2 Class 3 Class 4 Class 4

Class 1 PD Class 2 PD Class 3 PD Class 4 PD Class 5+ PDs

Assigned Class Value (based on the PD connected at the port)

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Start Fault

Insufficient Power

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

23

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

9.1.6 Programmable SRAM

The TPS23882 device has been designed to include programmable SRAM that accommodates future firmware

updates to support interoperability and/or compliance issues that may arise as new equipment is introduced in

conjunction with the release of the IEEE 802.3bt standard.

Note

The latest version of firmware and SRAM release notes may be accessed from the TI mySecure

Software webpage.

The SRAM Release Notes and ROM Advisory document includes more detailed information regarding

any know issues and changes that were associated with each firmware release.

Upon power up, it is recommended that the TPS23882 device's SRAM be programmed with the latest version of

SRAM code via the I2C to ensure proper operation and IEEE complaint performance. All I2C traffic other than

those commands required to program the SRAM should be deferred until after the SRAM programming

sequences are completed.

For systems that include multiple TPS23882 devices, the 0x7F "global" broadcast I2C address may be used to

programmed all of the devices at the same time.

For more detailed instructions on the SRAM programing procedures please refer to Section 9.6.2.67 and the

How to Load TPS2388x SRAM Code document on TI.com.

24 Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

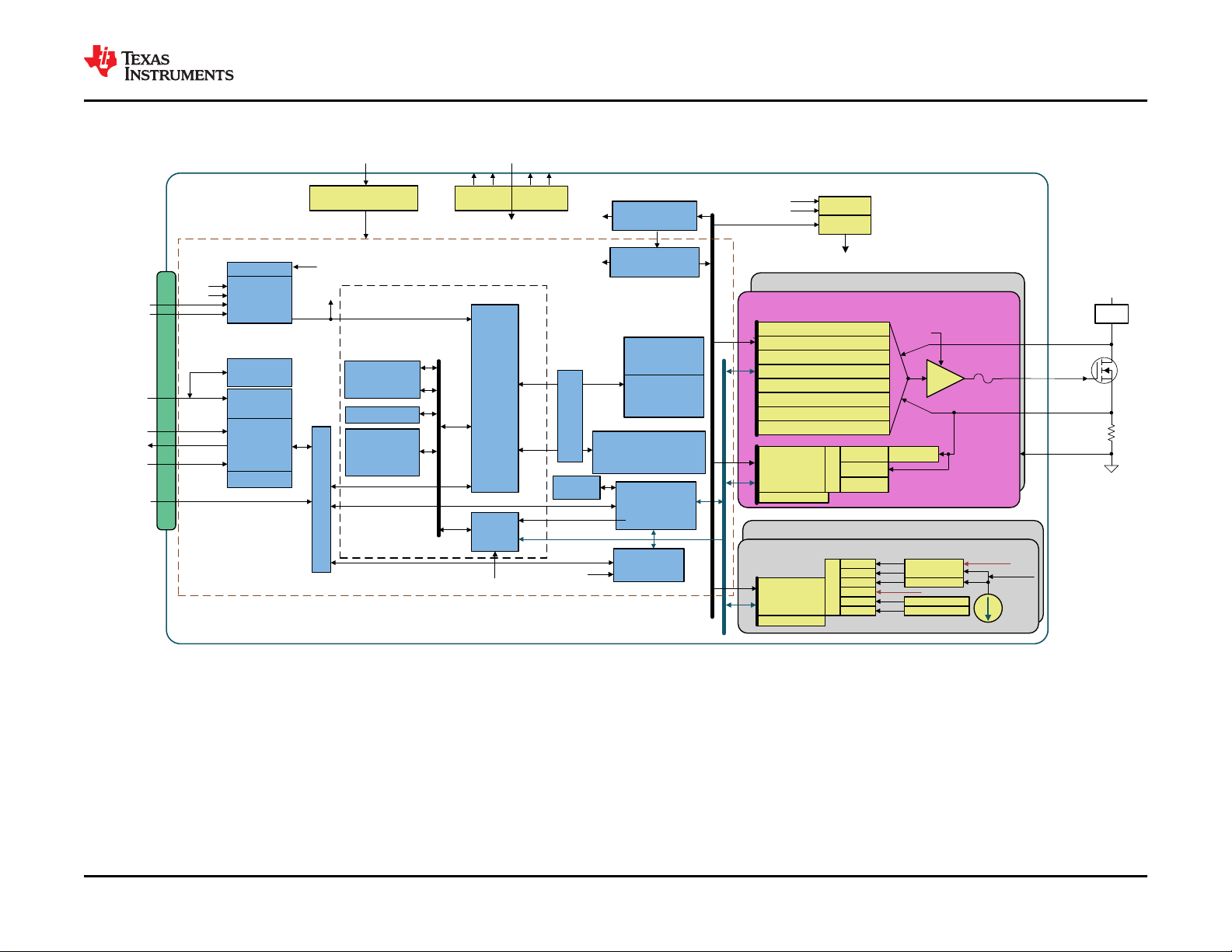

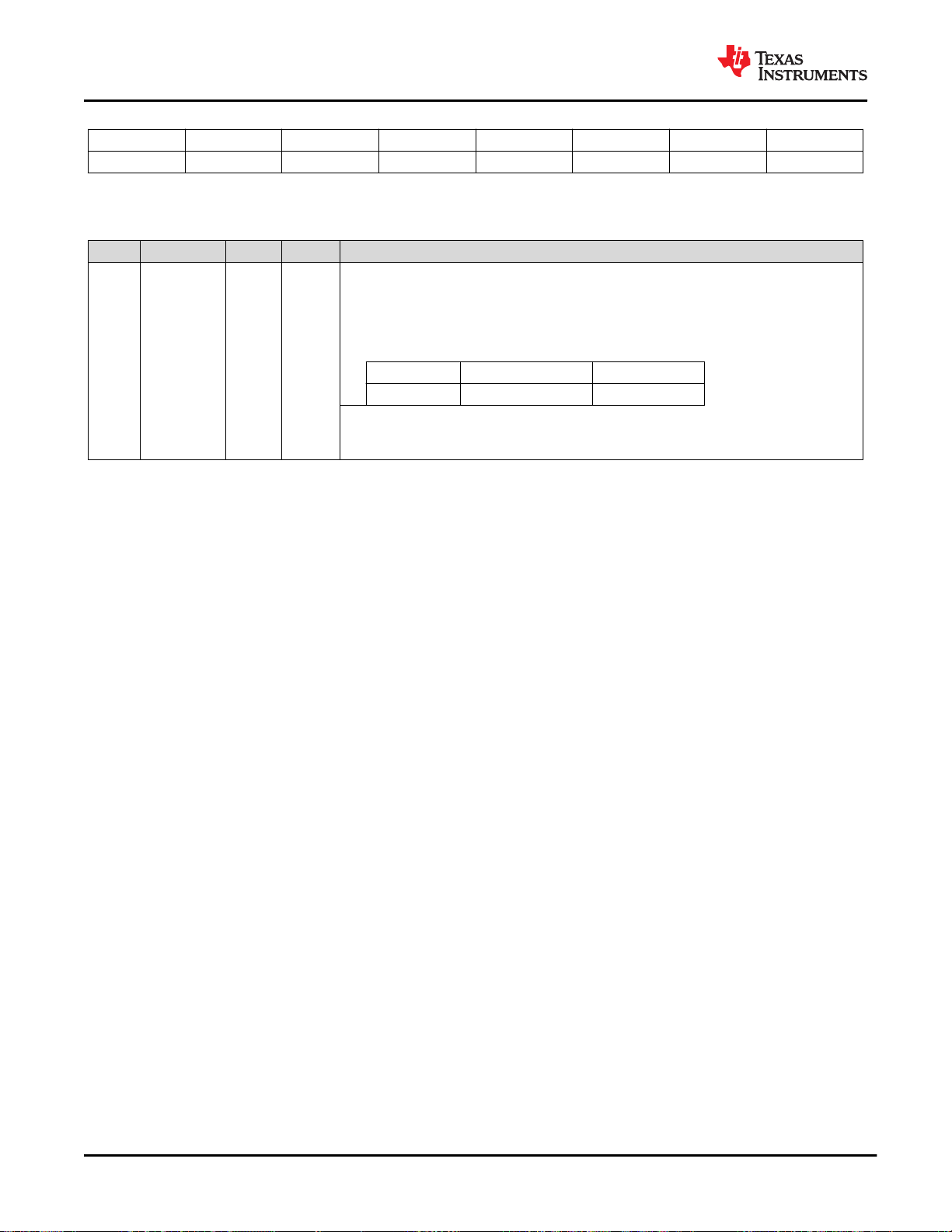

Common Functions for Ports 5-8

Common Functions for Ports1-4

Port 2-8 Analog Control Functions

Port 1 Analog Control Functions

RANGE

SELECT

14 Bit ADC

(Current)

2X Power

ICLASS

Internal Rails

Good

Temp

VEE

Vds

BIT

4:1 MUX

PTAT DIODES

Analog BIT MUX

RANGE SELECT

14 Bit ADC

(Voltage)

Variable Averager

Vdisco

PORT DIFF

AMP

Vport

Foldback Schedulers

Fast Ishort Protection

dv/dt ramping control

Rapid Overload recovery

GATEx

Enable

SENx

Ilim

320Hz LPFIPORT

BIT

DISCRETE IO CONDITIONERS

RST

to blks

CPU Watchdog

Register File

I2C Interface

External Data

Memory Bus

CPU

Interrupt

Controller

7 bit address

Select

Timers

SFR

BUS

MCU

Scan + Digital

Test

SCL Watchdog

CPU SRAM

ROM

IRAM

Bus

Prog

Mem

Bus

Memory BIST

Bus IF

Analog TRIM

Class Current Limit

Class Port Voltage Control

Variable Averager

SDAI

SDAO

SCL

Firmware Controlled

Update from register File

LDO

UVLO

VDD

Internal Oscillator

RESETB

OSS

RST Block

PG

CLK OK

Clock Distribution

DRAINx

KSENSEx

CLK

to blks

CLK OK

PG

OSS

INT

A1-A4

OSS/

POR

VPWR

IDET

FW Registers

SFR

With BIST

REMAP

Fuse-able

Disconnect

VPWR

VPWR Divider

VPWR

NC

VPWR

1/3

1/3 2/3

2/3

NC NCNC

SRAM

Load at Power

up into holding

latches

VDD

Program Memory

Gm

DRIVER

R

SENSE

GND

PD

LOAD

V48

V48

DRAIN1-4

www.ti.com

9.2 Functional Block Diagram

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

25

IDLE

START bits

SC 2

one-bit

duration

t

bit_OSS

t

OSS_IDL

3.3 V

0 V

SC 1

OSS

SC 0

Shutdown Code

GATE

t

OSS_OFF

IDLE

t

r_OSS

t

f_OSS

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

9.3 Feature Description

9.3.1 Port Remapping

The TPS23882 provides port remapping capability, from the logical ports to the physical channels and pins.

The remapping is between any channel of a 4-port group (1 to 4, 5 to 8).

The following example is applicable to 0x26 register = 00111001, 00111001b.

• Logical port 1 (5) ↔ Physical channel 2 (6)

• Logical port 2 (6) ↔ Physical channel 3 (7)

• Logical port 3 (7) ↔ Physical channel 4 (8)

• Logical port 4 (8) ↔ Physical channel 1 (5)

Note

The device ignores any remapping command unless all four ports are in off mode.

If the TPS23882 receives an incorrect configuration, it ignores the incorrect configuration and retains the

previous configuration. The ACK is sent as usual at the end of communication. For example, if the same

remapping code is received for more than one port, then a read back of the Re-Mapping register (0x26) would

be the last valid configuration.

Note that if an IC reset command (1Ah register) is received, the port remapping configuration is kept unchanged.

However, if there is a Power-on Reset or if the

a default value.

RESET pin is activated, the Re-Mapping register is reinitialized to

9.3.2 Port Power Priority

The TPS23882 supports 1- and 3-bit shutdown priority, which are selected with the MbitPrty bit of General Mask

register (0x17).

The 1-bit shutdown priority works with the Port Power Priority (0x15) register. An OSSn bit with a value of 1

indicates that the corresponding port is treated as low priority, while a value of 0 corresponds to a high priority.

As soon as the OSS input goes high, the low-priority ports are turned off.

The 3-bit shutdown priority works with the Multi Bit Power Priority (0x27/28) register, which holds the priority

settings. A port with “000” code in this register has highest priority. Port priority reduces as the 3-bit value

increases, with up to 8 priority levels. See Figure 9-1.

The multi bit port priority implementation is defined as the following:

• OSS code ≤ Priority setting (0x27/28 register): Port is disabled

• OSS code > Priority setting (0x27/28 register): Port remains active

26 Submit Document Feedback

Figure 9-1. Multi Bit Priority Port Shutdown if Lower-Priority Port

Product Folder Links: TPS23882

Copyright © 2020 Texas Instruments Incorporated

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

Note

Prior to setting the MbitPrty bit from 0 to 1, make sure the OSS input is in the idle (low) state for a

minimum of 200 µs, to avoid any port misbehavior related to loss of synchronization with the OSS bit

stream.

Note

The OSS input has an internal 1-µs to 5-µs deglitch filter. From the idle state, a pulse with a longer

duration is interpreted as a valid start bit. Ensure that the OSS signal is noise free.

9.3.3 Analog-to-Digital Converters (ADC)

The TPS23882 features 10 multi-slope integrating converters. Each of the first eight converters is dedicated to

current measurement for one channel and operate independently to perform measurements during classification

and when the channel is powered on. When the channel is powered, the converter is used for current (100-ms

averaged) monitoring, power policing, and DC disconnect. Each of the last two converters are shared within a

group of four channels for discovery (16.6-ms averaged), port powered voltage monitoring, power-good status,

and FET short detection. These converters are also used for general-purpose measurements including input

voltage (1 ms) and die temperature.

The ADC type used in the TPS23882 differs from other similar types of converters in that the ADCs continuously

convert while the input signal is sampled by the integrator, providing inherent filtering over the conversion period.

The typical conversion time of the current converters is 800 µs, while the conversion time is 1 ms for the other

converters. Powered-device detection is performed by averaging 16 consecutive samples which provides

significant rejection of noise at 50-Hz or 60-Hz line frequency. While a port is powered, digital averaging provides

a channel current measurement integrated over a 100-ms time period. Note that an anti-aliasing filter is present

for powered current monitoring.

Note

During powered mode, current conversions are performed continuously. Also, in powered mode, the

t

timer must expire before any current or voltage ADC conversion can begin.

START

9.3.4 I2C Watchdog

An I2C Watchdog timer is available on the TPS23882 device. The timer monitors the I2C, SCL line for clock

edges. When enabled, a timeout of the watchdog resets the I2C interface along with any active ports. This

feature provides protection in the event of a hung software situation or I2C bus hang-up by slave devices. In the

latter case, if a slave is attempting to send a data bit of 0 when the master stops sending clocks, then the slave

my drive the data line low indefinitely. Because the data line is driven low, the master cannot send a STOP to

clean up the bus. Activating the I2C watchdog feature of the TPS23882 clears this deadlocked condition. If the

timer of two seconds expires, the ports latch off and the WD status bit is set. Note that WD Status will be set

even if the watchdog is not enabled. The WD status bit may only be cleared by a device reset or writing a 0 to

the WDS status bit location. The 4-bit watchdog disable field shuts down this feature when a code of 1011b is

loaded. This field is preset to 1011b whenever the TPS23882 is initially powered. See I2C WATCHDOG Register

for more details.

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

Submit Document Feedback

27

V

PORT

(V)

I

PORT

(A)

0 3 6 9 12 15 18 21 24 27 30 33 36 39 42 45 48 51 54 57

0

0.05

0.1

0.15

0.2

0.25

0.3

0.35

0.4

0.45

0.5

0.55

D100

ALTIRn = 0

ALTIRn = 1

V

DRAIN

(V)

I

PORT

(A)

0 3 6 9 12 15 18 21 24 27 30 33 36 39 42 45 48 51 54 57

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

D200

2xFBn =0, ALTFBn = 0

2xFBn =0, ALTFBn = 1

2xFBn =1, ALTFBn = 0

2xFBn =1, ALTFBn = 1

TPS23882

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

www.ti.com

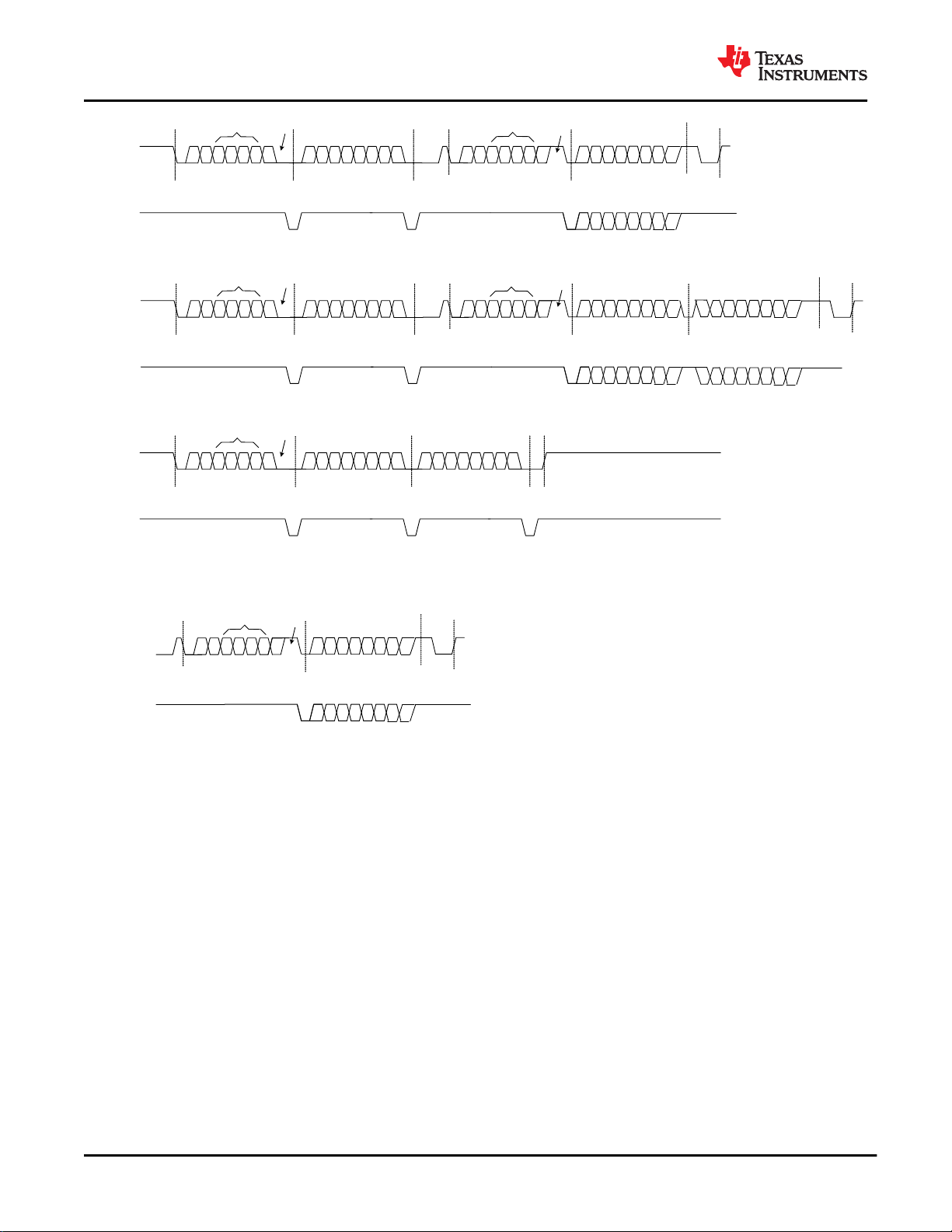

9.3.5 Current Foldback Protection

The TPS23882 features two types of foldback mechanisms for complete MOSFET protection.

During inrush, at channel turn on, the foldback is based on the channel voltage as shown in Figure 9-2. Note that

the inrush current profile remains the same, regardless of the state of the 2xFBn bits in register 0x40.

After the channel is powered and the Power Good is valid, a dual-slope operational foldback is used, providing

protection against partial and total short-circuit at port output, while still being able to maintain the PD powered

during normal transients at the PSE input voltage. Note that setting the 2xFBn bit selects the 2× curve and

clearing it selects the 1× curve. See Figure 9-3.

In addition to the default foldback curves, the TPS23882 has individually enabled alternative foldback curves for

both inrush and powered operation. These curves have been designed to accommodate certain loads that do

not fully comply with the IEEE standard and requires additional power to be turned on or remain powered. See

Figure 9-2 and Figure 9-3.

Note

If using the Alternative Foldback curves (ALTIRn or ALTFBn = 1), designers need to account for the

additional power dissipation that can occur in the FETs under these conditions.

Figure 9-2. Foldback During Inrush (at Port Turn

On): I

LIM

vs V

9.4 Device Functional Modes

9.4.1 Detection

To eliminate the possibility of false detection, the TPS23882 uses a TI proprietary 4-point detection method to

determine the signature resistance of the PD device. A false detection of a valid 25-kΩ signature can occur with

2-point detection type PSEs in noisy environments or if the load is highly capacitive.

Detection 1 and Detection 2 are merged into a single detection function which is repeated. Detection 1 applies I1

(160 μA) to a channel, waits approximately 60 ms, then measures the channel voltage (V1) with the integrating

ADC. Detection 2 then applies I2 (270 μA) to the channel, waits another approximately 60 ms, then measures

the channel voltage again (V2). The process is then repeated a second time to capture a third (V3) and fourth

(V4) channel voltage measurements. Multiple comparisons and calculations are performed on all four

measurement point combinations to eliminate the effects of a nonlinear or hysteretic PD signature. The resulting

channel signature is then sorted into the appropriate category.

The detection resistance measurement result is also available in the Channel Detect Resistance

registers (0x44 - 0x47).

9.4.2 Classification

Hardware classification (class) is performed by supplying a voltage and sampling the resulting current. To

eliminate the high power of a classification event from occurring in the power controller chip, the TPS23882 uses

the external power FET for classification.

28 Submit Document Feedback

port

Figure 9-3. Foldback When the Port is Already ON:

I

vs V

LIM

drain

Note

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS23882

www.ti.com

SLVSF21D – AUGUST 2019 – REVISED AUGUST 2020

TPS23882

During classification, the voltage on the gate node of the external MOSFET is part of a linear control loop. The