Page 1

www.ti.com

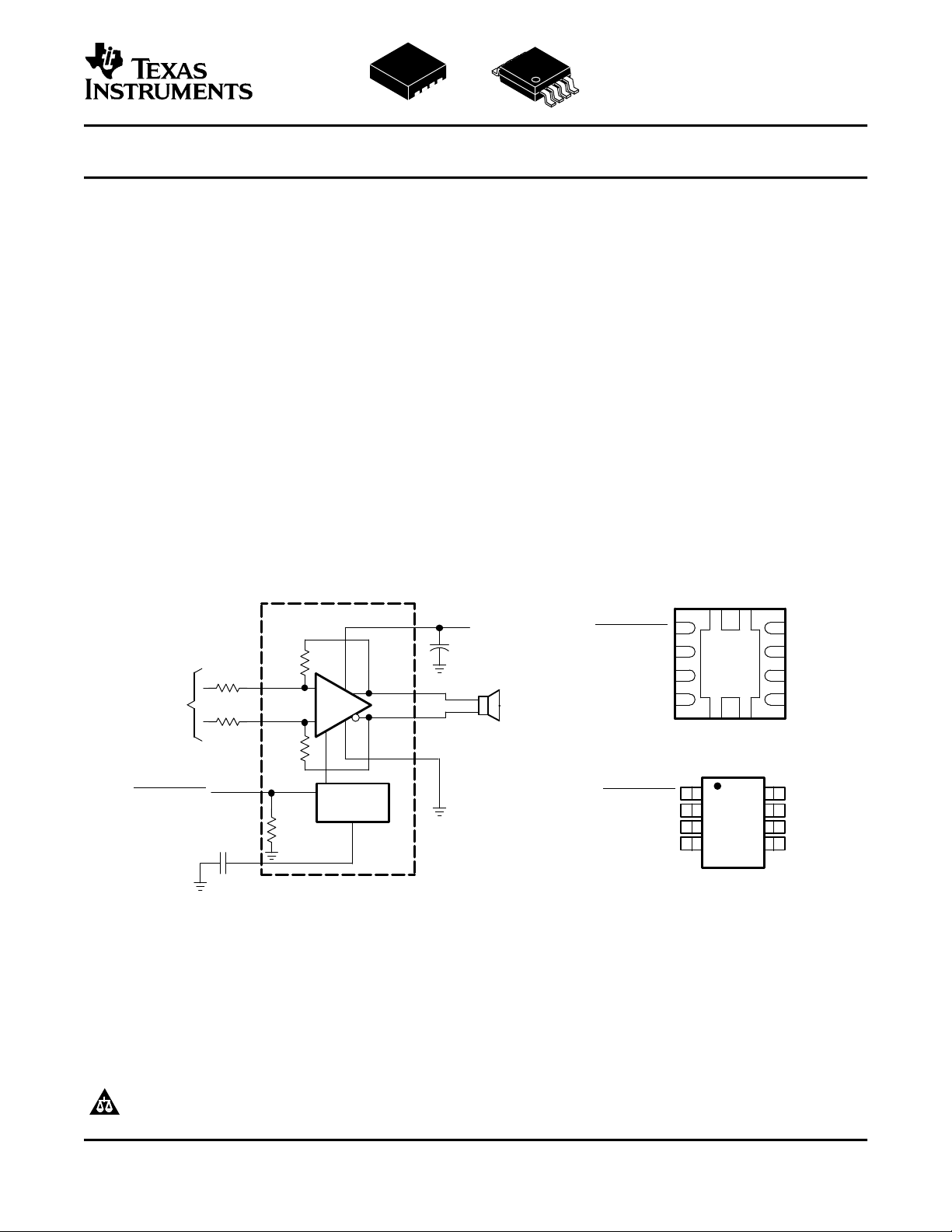

APPLICATION CIRCUIT

_

+

V

DD

V

O+

V

O-

GND

6

5

8

7

To Battery

C

s

Bias

Circuitry

IN-

IN+

4

3

2

+

-

In From

DAC

SHUTDOWN

R

I

R

I

1

C

(BYPASS)

(1)

DGN PACKAGE

(TOP VIEW)

1

2

3

4

8

7

6

5

SHUTDOWN

BYPASS

IN+

IN-

V

O-

GND

V

DD

V

O+

100 kΩ

40 kΩ

40 kΩ

8

SHUTDOWN

BYPASS

IN+

IN-

V

O-

GND

V

DD

V

O+

8-PIN QFN (DRB) PACKAGE

(TOP VIEW)

7

6

5

1

2

3

4

(1)

C

(BYPASS)

is optional.

3.1-W MONO FULLY DIFFERENTIAL AUDIO POWER AMPLIFIER

FEATURES APPLICATIONS

• Designed for Wireless or Cellular Handsets

and PDAs

• 3.1 W Into 3Ω From a 5-V Supply at

THD = 10% (Typ)

• Low Supply Current: 4 mA Typ at 5 V

• Shutdown Current: 0.01 µA Typ

• Fast Startup With Minimal Pop

• Only Three External Components

– Improved PSRR (-80 dB) and Wide Supply

Voltage (2.5 V to 5.5 V) for Direct Battery

Operation

– Fully Differential Design Reduces RF

Rectification

– -63 dB CMRR Eliminates Two Input

Coupling Capacitors

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

• Ideal for Wireless Handsets, PDAs, and

Notebook Computers

DESCRIPTION

The TPA6211A1 is a 3.1-W mono fully-differential

amplifier designed to drive a speaker with at least

3-Ω impedance while consuming only 20 mm

printed-circuit board (PCB) area in most applications.

The device operates from 2.5 V to 5.5 V, drawing

only 4 mA of quiescent supply current. The

TPA6211A1 is available in the space-saving

3-mm × 3-mm QFN (DRB) and the 8-pin MSOP

(DGN) PowerPAD™ packages.

Features like -80 dB supply voltage rejection from

20 Hz to 2 kHz, improved RF rectification immunity,

small PCB area, and a fast startup with minimal pop

makes the TPA6211A1 ideal for PDA/smart phone

applications.

2

total

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 2003–2004, Texas Instruments Incorporated

Page 2

www.ti.com

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

These devices have limited built-in ESD protection. The leads should be shorted together or the device

placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

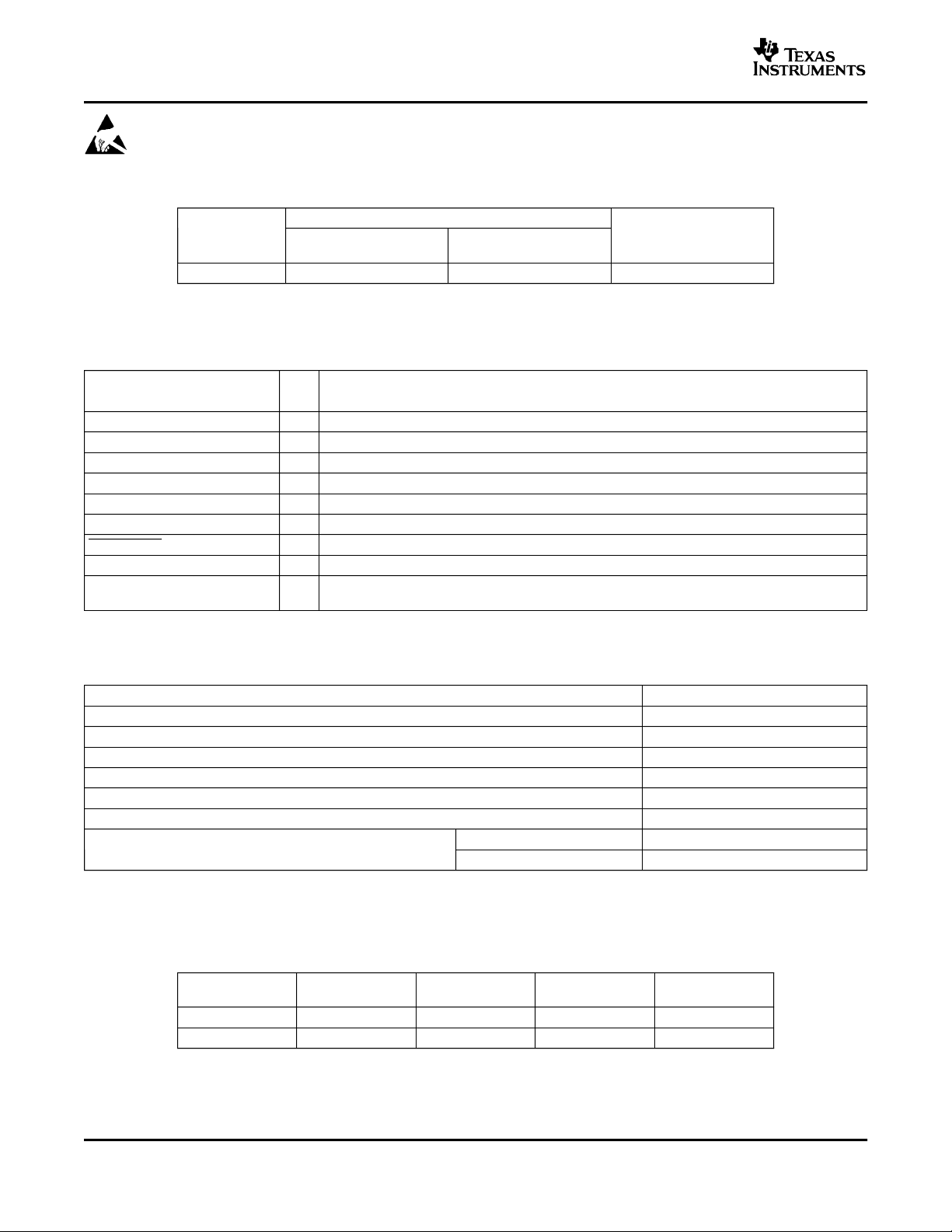

ORDERING INFORMATION

PACKAGED DEVICES

T

A

SMALL OUTLINE MSOP PowerPAD™

(DRB) (DGN)

-40°C to 85°C TPA6211A1DRB TPA6211A1DGN TPA6211A1EVM

(1) The DGN and DRB are available taped and reeled. To order taped and reeled parts, add the suffix R

to the part number (TPA6211A1DGNR or TPA6211A1DRBR).

Terminal Functions

TERMINAL

NAME DRB, DGN

IN- 4 I Negative differential input

IN+ 3 I Positive differential input

V

DD

V

O+

6 I Power supply

5 O Positive BTL output

GND 7 I High-current ground

V

O-

8 O Negative BTL output

SHUTDOWN 1 I Shutdown terminal (active low logic)

BYPASS 2 Mid-supply voltage, adding a bypass capacitor improves PSRR

Thermal Pad - -

I/O DESCRIPTION

Connect to ground. Thermal pad must be soldered down in all applications to properly secure

device on the PCB.

(1)

EVALUATION MODULES

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted

V

Supply voltage -0.3 V to 6 V

DD

V

Input voltage -0.3 V to V

I

Continuous total power dissipation See Dissipation Rating Table

T

Operating free-air temperature -40°C to 85°C

A

T

Junction temperature -40°C to 150°C

J

T

Storage temperature -65°C to 85°C

stg

Lead temperature 1,6 mm (1/16 Inch) from case for 10 seconds

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(1)

UNIT

DD

DRB 260°C

DGN 235°C

PACKAGE DISSIPATION RATINGS

PACKAGE

DGN 2.13 W 17.1 mW/°C 1.36 W 1.11 W

DRB 2.7 W 21.8 mW/°C 1.7 W 1.4 W

(1) Derating factor based on high-k board layout.

TA≤ 25°C DERATING TA= 70°C TA= 85°C

POWER RATING FACTOR

(1)

POWER RATING POWER RATING

+ 0.3 V

2

Page 3

www.ti.com

38 k

R

I

40 k

R

I

42 k

R

I

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

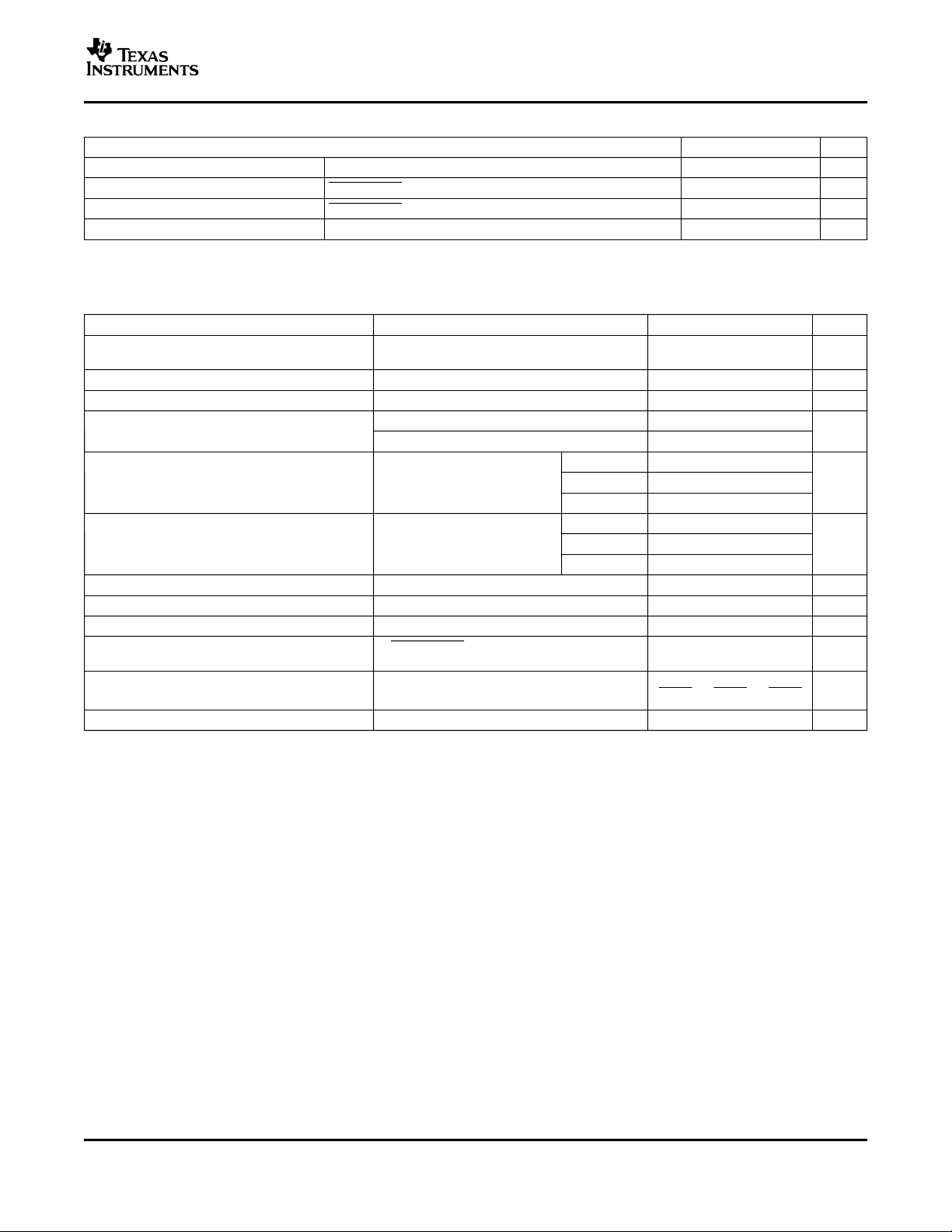

RECOMMENDED OPERATION CONDITIONS

MIN TYP MAX UNIT

V

Supply voltage 2.5 5.5 V

DD

V

High-level input voltage SHUTDOWN 1.55 V

IH

V

Low-level input voltage SHUTDOWN 0.5 V

IL

T

Operating free-air temperature -40 85 °C

A

ELECTRICAL CHARACTERISTICS

TA= 25°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

OS

PSRR Power supply rejection ratio V

V

IC

CMRR Common mode rejection ratio dB

| IIH| High-level input current, shutdown V

| IIL| Low-level input current, shutdown V

I

Q

I

(SD)

Output offset voltage (measured

differentially)

Common mode input range V

Low-output swing V

High-output swing V

Quiescent current V

Supply current 0.01 1 µA

VI= 0 V differential, Gain = 1 V/V, V

= 2.5 V to 5.5 V -85 -60 dB

DD

= 2.5 V to 5.5 V 0.5 VDD-0.8 V

DD

V

= 5.5 V, VIC= 0.5 V to 4.7 V -63 -40

DD

V

= 2.5 V, VIC= 0.5 V to 1.7 V -63 -40

DD

RL= 4 Ω, Gain = 1 V/V,

= VDD, V

IN+

V

= 0 V, V

IN+

= 0 V or V

IN-

= V

IN-

DD

RL= 4 Ω, Gain = 1 V/V,

= VDD, V

IN+

V

= V

IN-

DD

= 5.5 V, VI= 5.8 V 58 100 µA

DD

= 5.5 V, VI= -0.3 V 3 100 µA

DD

= 2.5 V to 5.5 V, no load 4 5 mA

DD

V(SHUTDOWN) ≤ 0.5 V, V

RL= 4Ω

IN-

V

IN+

= 0 V or V

= 0 V

= 2.5 V to 5.5 V,

DD

= 5.5 V -9 0.3 9 mV

DD

V

= 5.5 V 0.45

DD

= 3.6 V 0.37 V

DD

V

= 2.5 V 0.26 0.4

DD

V

= 5.5 V 4.95

DD

= 3.6 V 3.18 V

DD

V

= 2.5 V 2 2.13

DD

Gain RL= 4Ω V/V

Resistance from shutdown to GND 100 kΩ

3

Page 4

www.ti.com

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

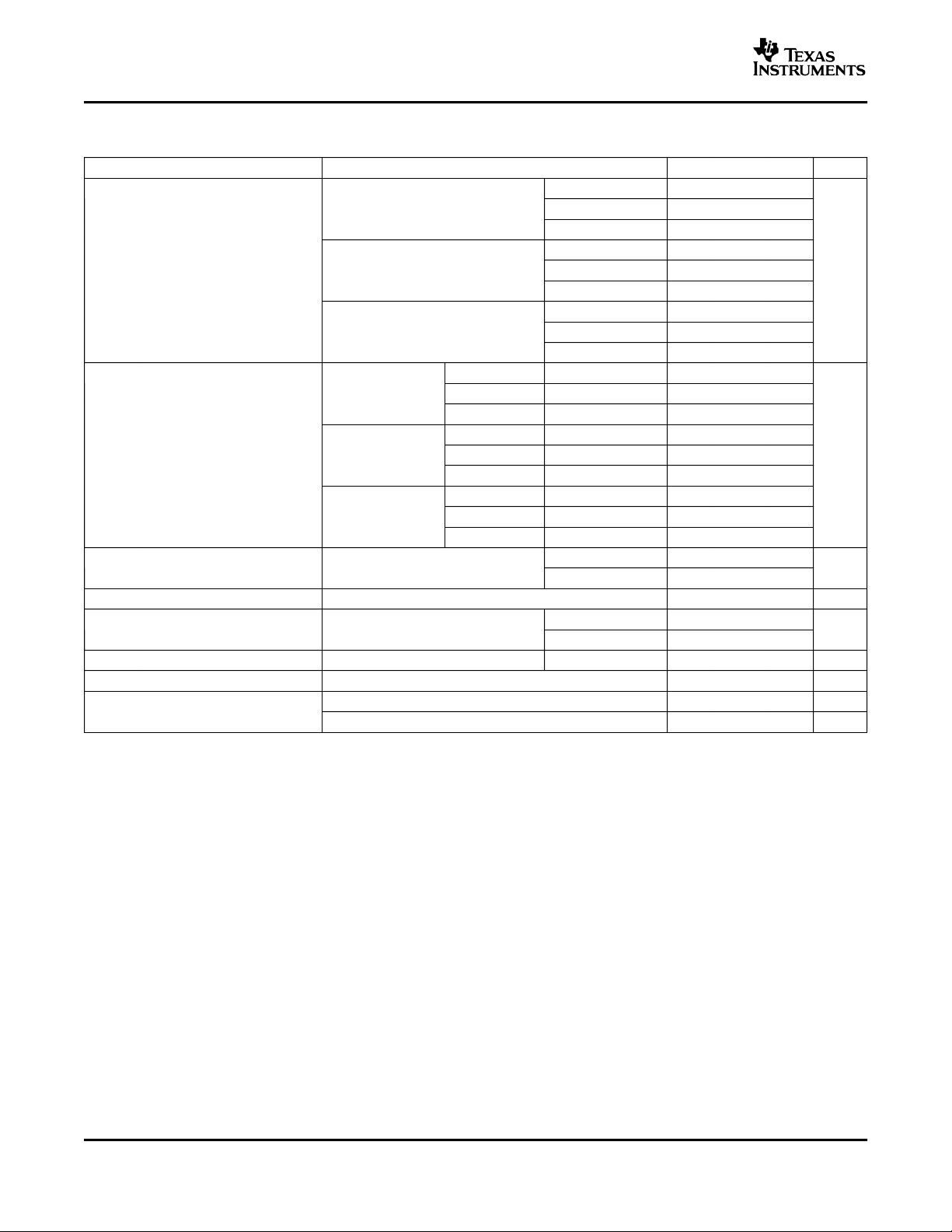

OPERATING CHARACTERISTICS

TA= 25°C, Gain = 1 V/V

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

THD + N= 1%, f = 1 kHz, RL= 3 Ω V

P

THD+N f = 1 kHz, RL= 4 Ω PO= 0.7 W V

k

SVR

SNR Signal-to-noise ratio V

V

CMRR Common mode rejection ratio V

Z

Output power THD + N= 1%, f = 1 kHz, RL= 4 Ω V

O

THD + N= 1%, f = 1 kHz, RL= 8 Ω V

PO= 2 W V

f = 1 kHz, RL= 3 Ω PO= 1 W V

PO= 300 mW V

PO= 1.8 W V

Total harmonic distortion plus

noise

PO= 300 mW V

PO= 1 W V

f = 1 kHz, RL= 8 Ω PO= 0.5 W V

PO= 200 mW V

V

= 3.6 V, Inputs ac-grounded with

Supply ripple rejection ratio dB

Output voltage noise µV

n

Input impedance 38 40 44 kΩ

I

Start-up time from shutdown

DD

Ci= 2 µF, V

= 5 V, PO= 2 W, RL= 4 Ω 105 dB

DD

V

= 3.6 V, f = 20 Hz to 20 kHz,

DD

Inputs ac-grounded with Ci= 2 µF

= 3.6 V, VIC= 1 V

DD

V

= 3.6 V, No C

DD

V

= 3.6 V, C

DD

= 200 mV

(RIPPLE)

BYPASS

BYPASS

pp

pp

= 0.1 µF 27 ms

V

= 5 V 2.45

DD

= 3.6 V 1.22

DD

V

= 2.5 V 0.49

DD

V

= 5 V 2.22

DD

= 3.6 V 1.1 W

DD

V

= 2.5 V 0.47

DD

V

= 5 V 1.36

DD

= 3.6 V 0.72

DD

V

= 2.5 V 0.33

DD

= 5 V 0.045%

DD

= 3.6 V 0.05%

DD

= 2.5 V 0.06%

DD

= 5 V 0.03%

DD

= 3.6 V 0.03%

DD

= 2.5 V 0.04%

DD

= 5 V 0.02%

DD

= 3.6 V 0.02%

DD

= 2.5 V 0.03%

DD

f = 217 Hz -80

f = 20 Hz to 20 kHz -70

No weighting 15

A weighting 12

f = 217 Hz -65 dB

4 µs

RMS

4

Page 5

www.ti.com

0

0.5

1

1.5

2

2.5

3

3.5

2.5 3 3.5 4 4.5 5

VDD - Supply Voltage - V

- Output Power - WP

O

f = 1 kHz

Gain = 1 V/V

PO = 3 Ω, THD 10%

PO = 4 Ω, THD 10%

PO = 3 Ω, THD 1%

PO = 4 Ω, THD 1%

PO = 8 Ω, THD 1%

PO = 8 Ω, THD 10%

RL - Load Resistance - Ω

- Output Power - WP

O

0

0.5

1

1.5

2

2.5

3

3.5

3 8 13 18 23 28

VDD = 5 V , THD 1%

VDD = 2.5 V , THD 10%

VDD = 2.5 V , THD 1%

VDD = 5 V , THD 10%

VDD = 3.6 V , THD 10%

VDD = 3.6 V , THD 1%

f = 1 kHz

Gain = 1 V/V

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

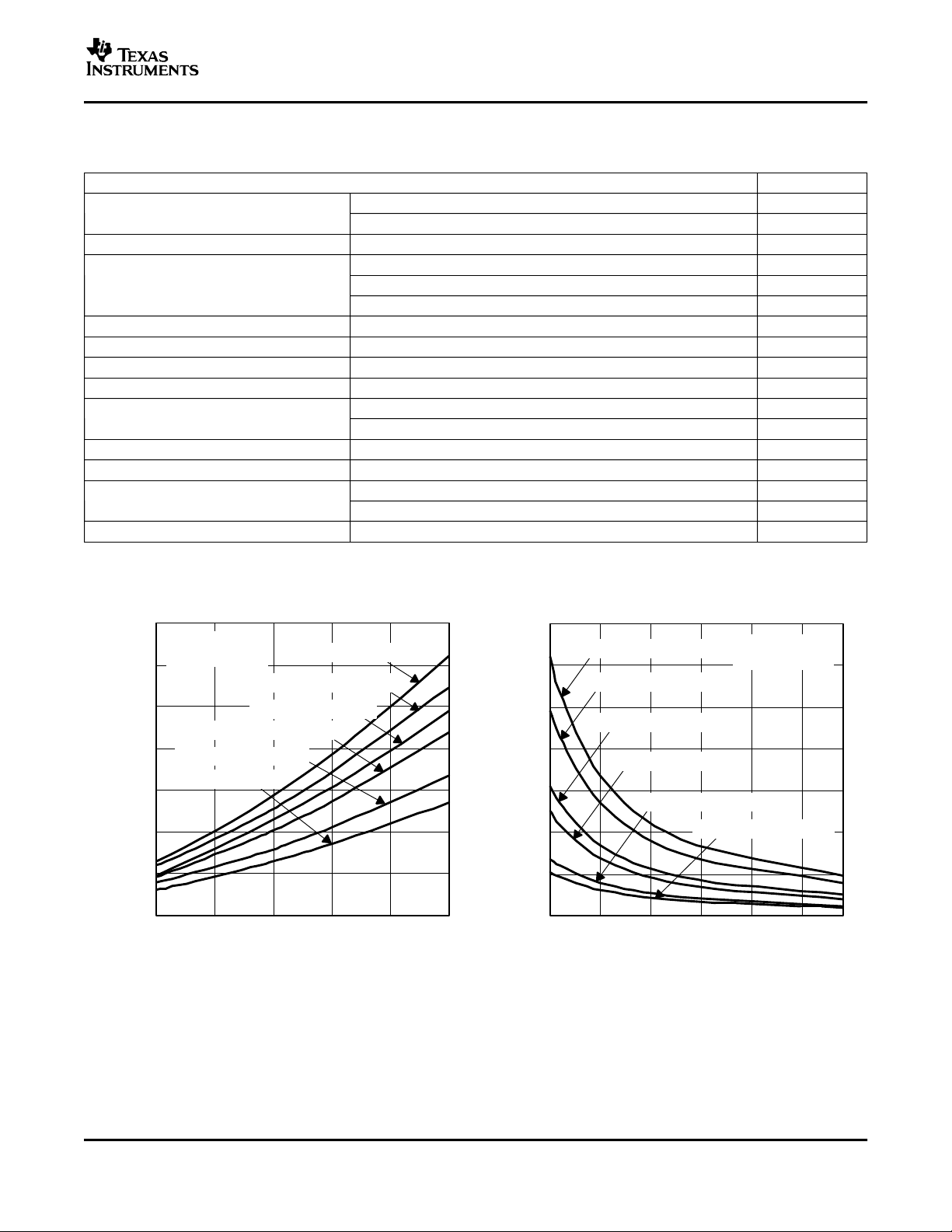

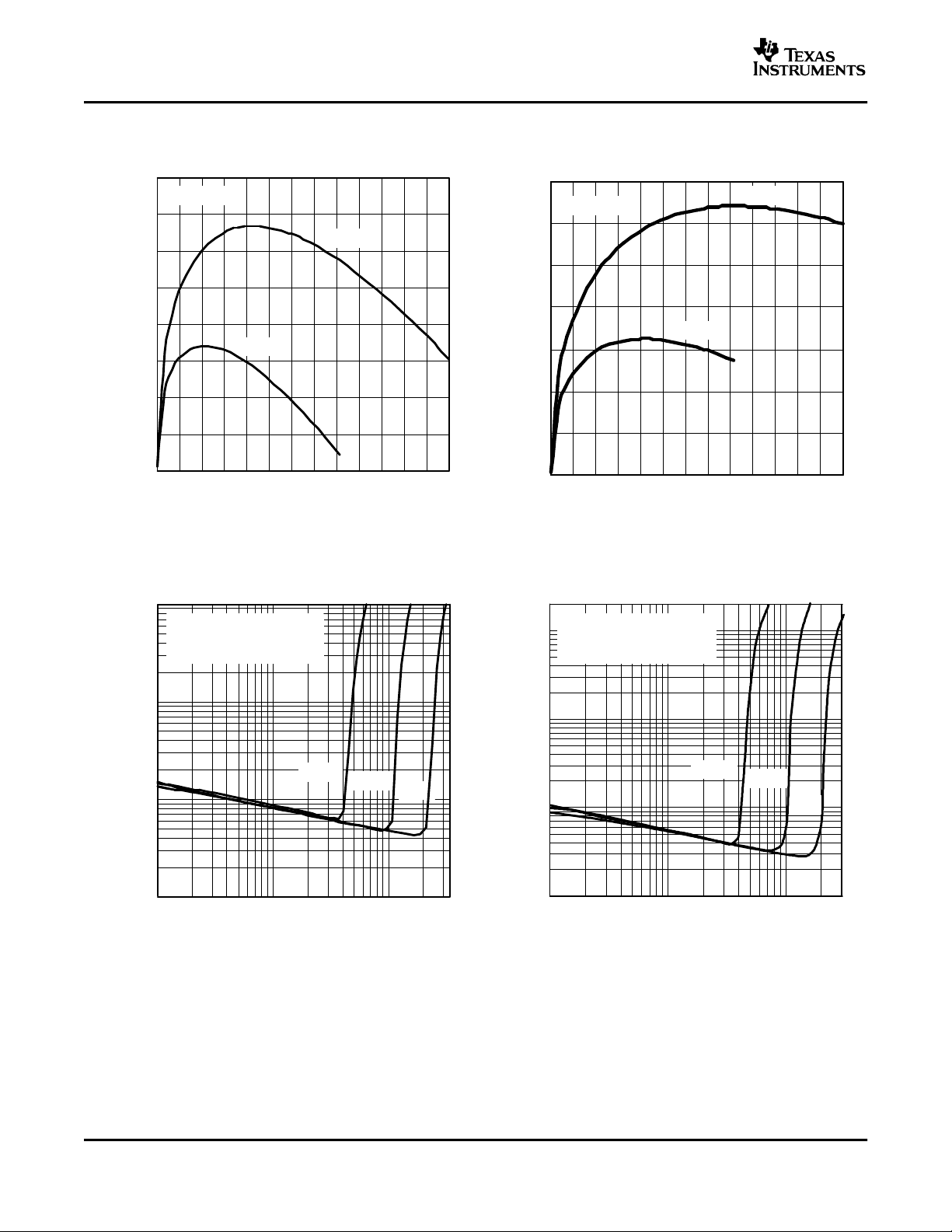

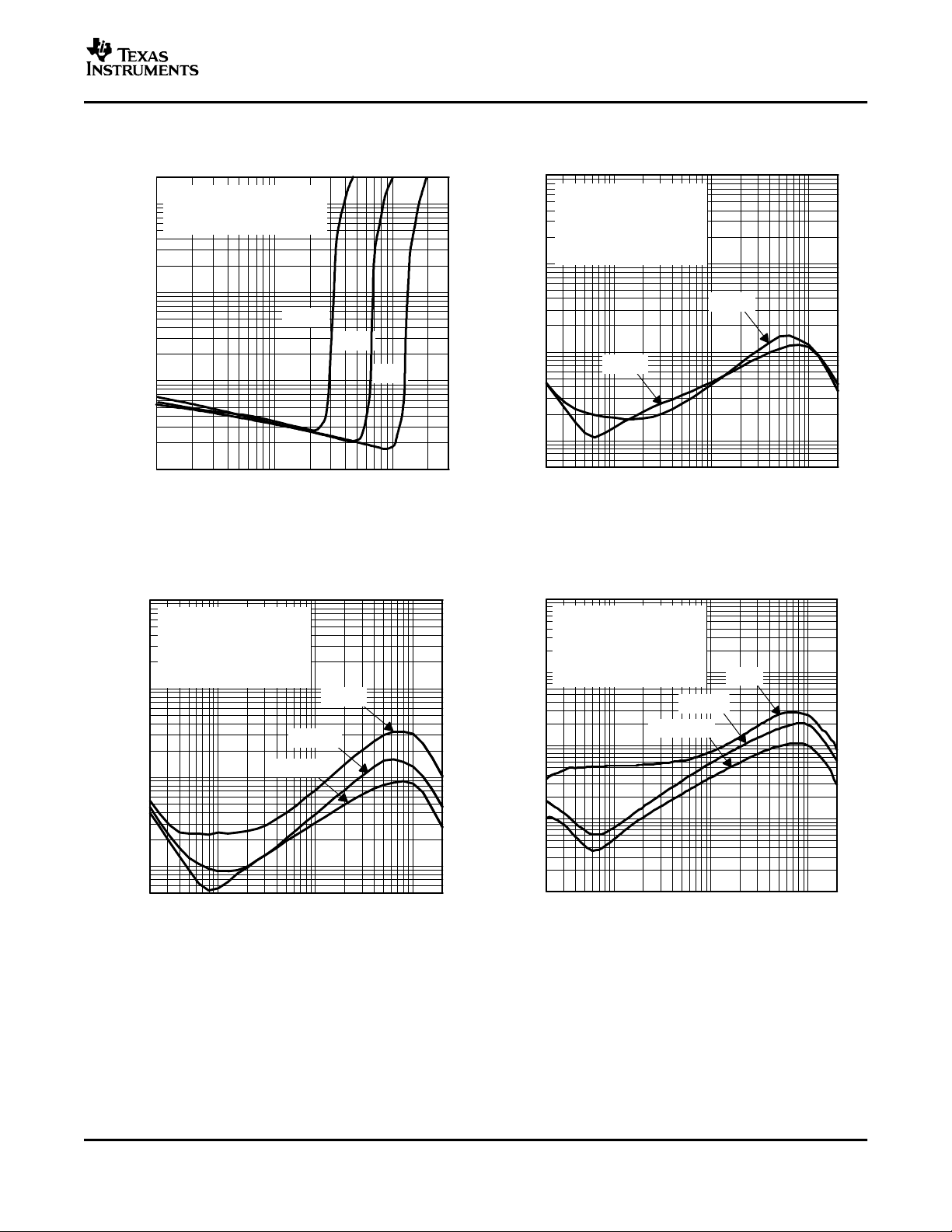

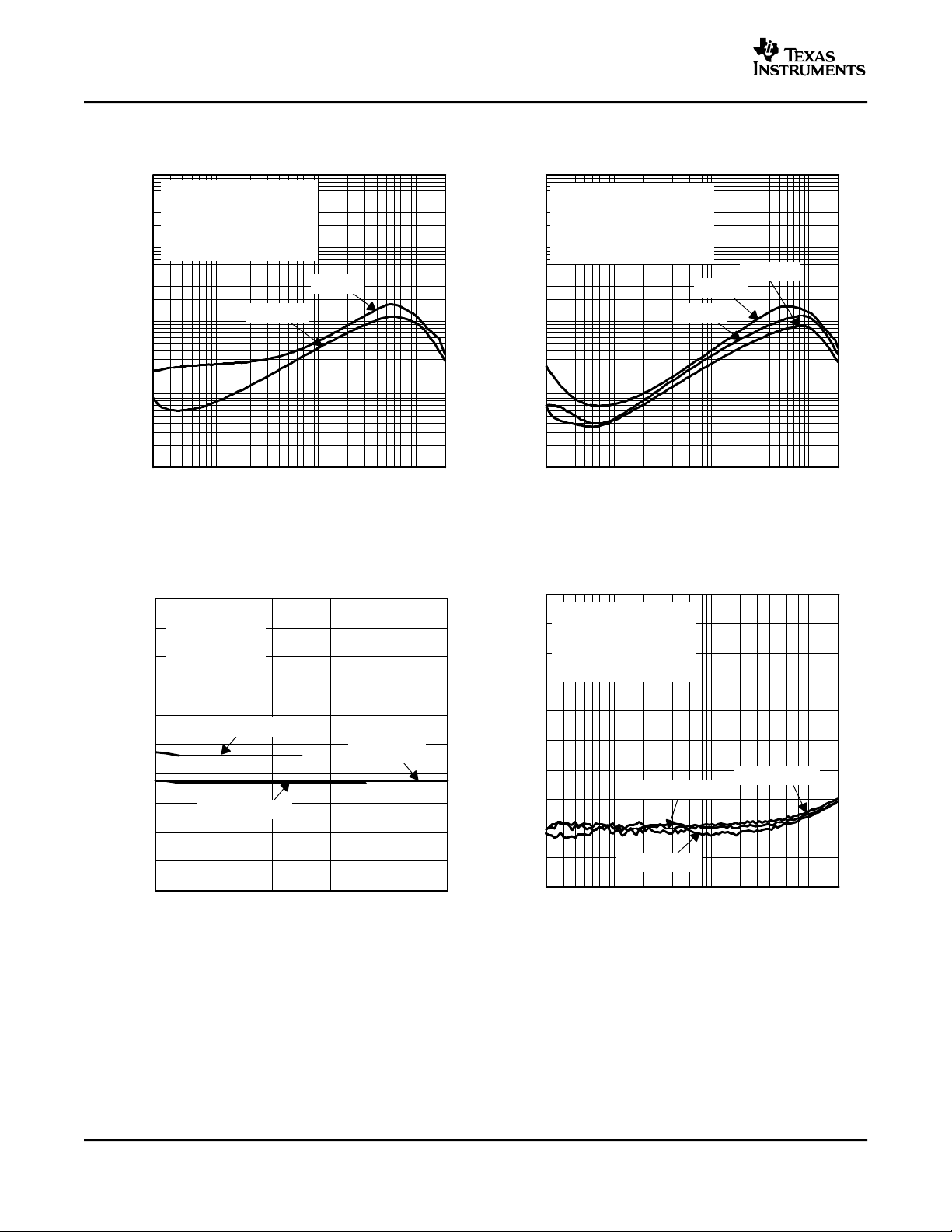

TYPICAL CHARACTERISTICS

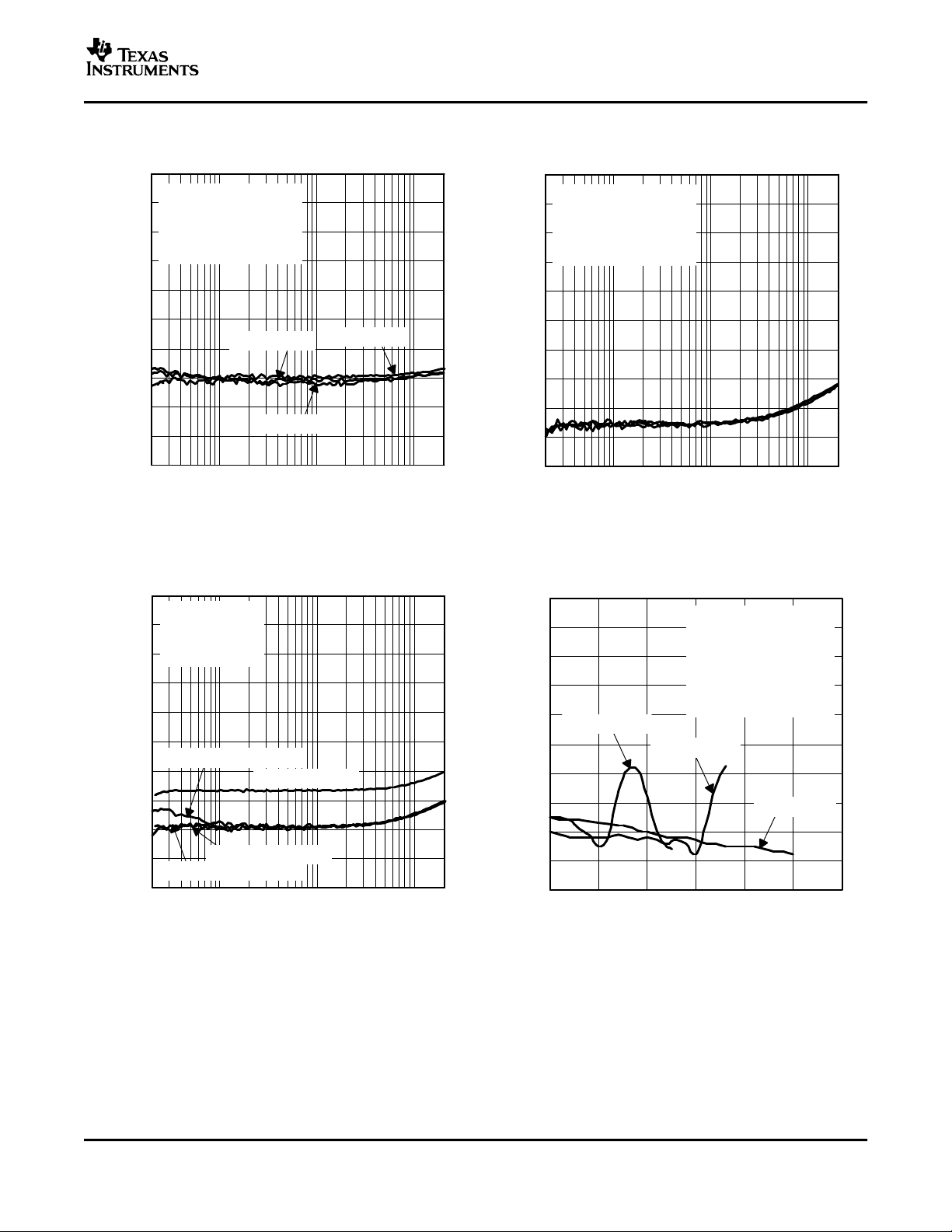

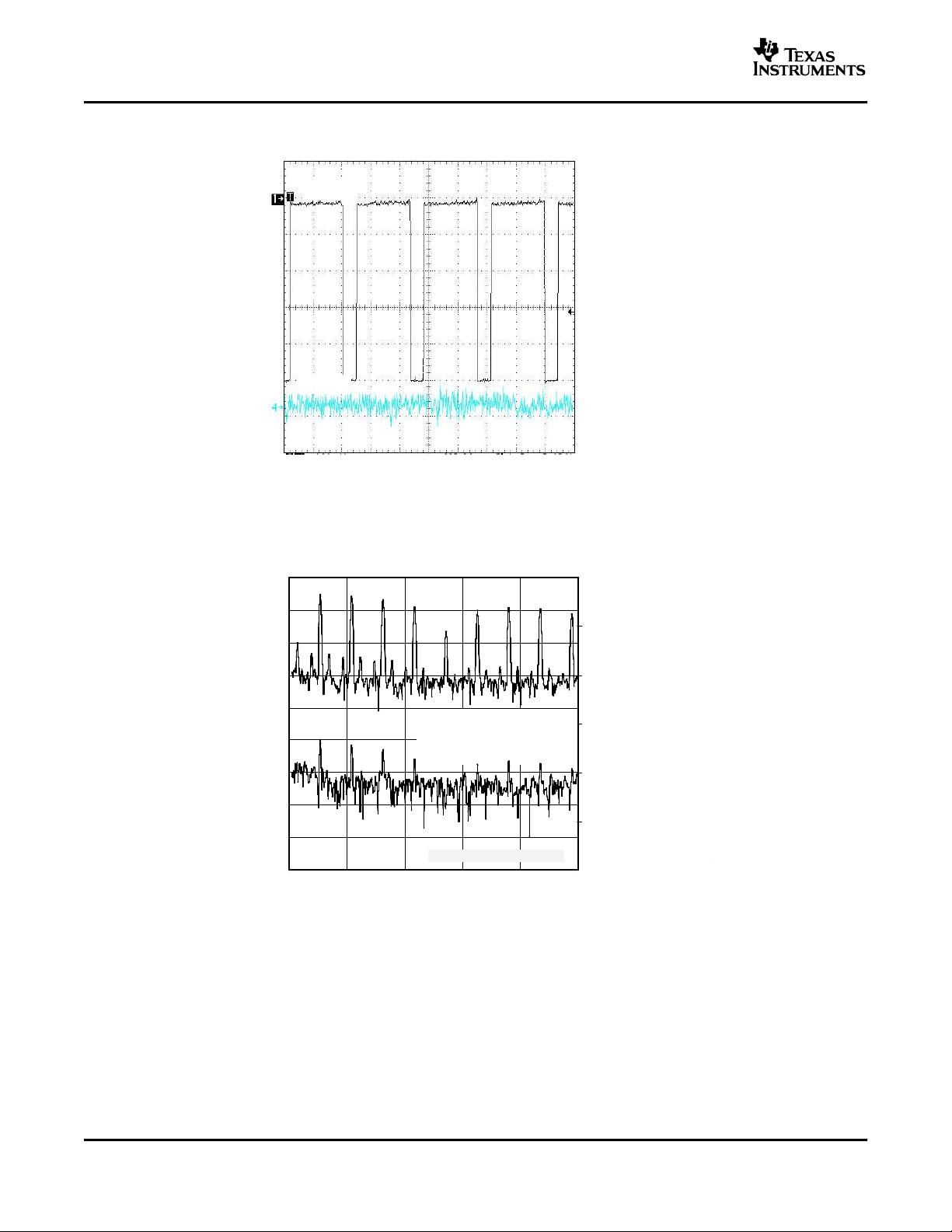

Table of Graphs

P

O

P

D

Output power

Power dissipation vs Output power 3, 4

THD+N Total harmonic distortion + noise vs Frequency 8-12

K

SVR

K

SVR

Supply voltage rejection ratio vs Frequency 14, 15, 16, 17

Supply voltage rejection ratio vs Common-mode input voltage 18

GSM Power supply rejection vs Time 19

GSM Power supply rejection vs Frequency 20

CMRR Common-mode rejection ratio

Closed loop gain/phase vs Frequency 23

Open loop gain/phase vs Frequency 24

I

DD

Supply current

Start-up time vs Bypass capacitor 27

vs Supply voltage 1

vs Load resistance 2

vs Output power 5, 6, 7

vs Common-mode input voltage 13

vs Frequency 21

vs Common-mode input voltage 22

vs Supply voltage 25

vs Shutdown voltage 26

TPA6211A1

FIGURE

OUTPUT POWER OUTPUT POWER

vs vs

SUPPLY VOLTAGE LOAD RESISTANCE

Figure 1. Figure 2.

5

Page 6

www.ti.com

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0 0.3 0.6 0.9 1.2 1.5 1.8

VDD = 3.6 V

4 Ω

8 Ω

PO - Output Power - W

- Power Dissiaption - WP

D

0

0.2

0.4

0.6

0.8

1

1.2

1.4

0 0.3 0.6 0.9 1.2 1.5 1.8

VDD = 5 V

4 Ω

8 Ω

PO - Output Power - W

- Power Dissiaption - WP

D

0.01

10

0.02

0.05

0.1

0.2

0.5

1

2

5

20m 350m 100m 200m 500m 1 2

PO - Output Power - W

THD+N - Total Harmonic Distortion + Noise - %

RL = 3 Ω

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V

2.5 V

3.6 V

5 V

0.01

20

0.02

0.05

0.1

0.2

0.5

1

2

5

10

10m 320m 50m 100m 200m 500m 1 2

PO - Output Power - W

THD+N - Total Harmonic Distortion + Noise - %

2.5 V

3.6 V

5 V

RL = 4 Ω

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

POWER DISSIPATION POWER DISSIPATION

vs vs

OUTPUT POWER OUTPUT POWER

Figure 3. Figure 4.

TOTAL HARMONIC DISTORTION + NOISE TOTAL HARMONIC DISTORTION + NOISE

vs vs

OUTPUT POWER OUTPUT POWER

6

Figure 5. Figure 6.

Page 7

www.ti.com

0.005

10

0.01

0.02

0.05

0.1

0.2

0.5

1

2

5

20 20k50 100 200 500 1k 2k 5k 10k

f - Frequency - Hz

THD+N - Total Harmonic Distortion + Noise - %

1 W

2 W

VDD = 5 V ,

RL = 3 Ω,

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V ,

CI = 2 µF

0.01

20

0.02

0.05

0.1

0.2

0.5

1

2

5

10

10m 320m 50m 100m 200m 500m 1 2

PO - Output Power - W

THD+N - Total Harmonic Distortion + Noise - %

2.5 V

3.6 V

5 V

RL = 8 Ω

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V

0.001

10

0.002

0.005

0.01

0.02

0.05

0.1

0.2

0.5

1

2

5

20 20k50 100 200 500 1k 2k 5k 10k

0.5 W

0.1 W

1 W

f - Frequency - Hz

THD+N - Total Harmonic Distortion + Noise - %

VDD = 3.6 V ,

RL = 4 Ω,

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V ,

CI = 2 µF

0.005

10

0.01

0.02

0.05

0.1

0.2

0.5

1

2

5

20

20k

50 100 200 500

1k 2k 5k 10k

f - Frequency - Hz

THD+N - Total Harmonic Distortion + Noise - %

2 W

1.8 W

1 W

VDD = 5 V ,

RL = 4 Ω,

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V ,

CI = 2 µF

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

TOTAL HARMONIC DISTORTION + NOISE TOTAL HARMONIC DISTORTION + NOISE

vs vs

OUTPUT POWER FREQUENCY

Figure 7. Figure 8.

TOTAL HARMONIC DISTORTION + NOISE TOTAL HARMONIC DISTORTION + NOISE

vs vs

FREQUENCY FREQUENCY

Figure 9. Figure 10.

7

Page 8

www.ti.com

0.001

10

0.002

0.005

0.01

0.02

0.05

0.1

0.2

0.5

1

2

5

20 20k50 100 200 500 1k 2k 5k 10k

0.4 W

0.28 W

f - Frequency - Hz

THD+N - Total Harmonic Distortion + Noise - %

VDD = 2.5 V ,

RL = 4 Ω,

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V ,

CI = 2 µF

0.001

10

0.002

0.005

0.01

0.02

0.05

0.1

0.2

0.5

1

2

5

20 20k50 100 200 500 1k 2k 5k 10k

f - Frequency - Hz

THD+N - Total Harmonic Distortion + Noise - %

0.1 W

0.6 W

0.25 W

VDD = 3.6 V ,

RL = 8 Ω,

,

C

(BYPASS)

= 0 to 1 µF,

Gain = 1 V/V ,

CI = 2 µF

f - Frequency - Hz

+0

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

20 20k50 100 200 500 1k 2k 5k 10k

k

SVR

- Supply Voltage Rejection Ratio - dB

VDD = 3.6 V

VDD = 2.5 V

VDD = 5 V

RL = 4 Ω,

,

C

(BYPASS)

= 0.47 µF,

Gain = 1 V/V ,

CI = 2 µF,

Inputs ac Grounded

0.04

0.042

0.044

0.046

0.048

0.05

0.052

0.054

0.056

0.058

0.06

0 1 2 3 4 5

f = 1 kHz

PO = 200 mW,

RL = 1 kHz

VIC - Common Mode Input Voltage - V

THD+N - Total Harmonic Distortion + Noise - %

VDD = 3.6 V

VDD = 5 V

VDD = 2.5 V

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

TOTAL HARMONIC DISTORTION + NOISE TOTAL HARMONIC DISTORTION + NOISE

vs vs

FREQUENCY FREQUENCY

Figure 11. Figure 12.

TOTAL HARMONIC DISTORTION + NOISE SUPPLY VOLTAGE REJECTION RATIO

vs vs

COMMON MODE INPUT VOLTAGE FREQUENCY

8

Figure 13. Figure 14.

Page 9

www.ti.com

f - Frequency - Hz

+0

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

20 20k50 100 200 500 1k 2k 5k 10k

k

SVR

- Supply Voltage Rejection Ratio - dB

VDD = 3.6 V

VDD = 2.5 V

RL = 4 Ω,

,

C

(BYPASS)

= 0.47 µF,

Gain = 5 V/V ,

CI = 2 µF,

Inputs ac Grounded

VDD = 5 V

f - Frequency - Hz

+0

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

20 20k50 100 200 500 1k 2k 5k 10k

k

SVR

- Supply Voltage Rejection Ratio - dB

RL = 4 Ω,

,

C

(BYPASS)

= 0.47 µF,

CI = 2 µF,

VDD = 2.5 V to 5 V

Inputs Floating

k

SVR

− Supply Voltage Rejection Ratio − dB

f − Frequency − Hz

+0

−100

−90

−80

−70

−60

−50

−40

−30

−20

−10

20 20k50 100 200 500 1k 2k 5k 10k

RL = 4 Ω,

,

C

I

= 2 µF,

Gain = 1 V/V ,

VDD = 3.6 V

C

(BYPASS)

= 0.47 µF

C

(BYPASS)

= 1 µF

C

(BYPASS)

= 0.1 µF

No C

(BYPASS)

−100

−90

−80

−70

−60

−50

−40

−30

−20

−10

0

0 1 2 3 4 5 6

VDD = 5 V

VDD = 3.6 V

VDD = 2.5 V

DC Common Mode Input − V

k

SVR

− Supply Voltage Rejection Ratio − dB

RL = 4 Ω,

,

C

I

= 2 µF,

Gain = 1 V/V ,

C

(BYPASS)

= 0.47 µF

VDD = 3.6 V ,

f = 217 Hz,

Inputs ac Grounded

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

SUPPLY VOLTAGE REJECTION RATIO SUPPLY RIPPLE REJECTION RATIO

vs vs

FREQUENCY FREQUENCY

Figure 15. Figure 16.

SUPPLY VOLTAGE REJECTION RATIO SUPPLY VOLTAGE REJECTION RATIO

vs vs

FREQUENCY DC COMMON MODE INPUT

Figure 17. Figure 18.

9

Page 10

www.ti.com

C1

Frequency

217 Hz

C1 − Duty

20%

C1 Pk−Pk

500 mV

Ch1 100 mV/div

Ch4 10 mV/div

2 ms/div

V

DD

V

OUT

Voltage − V

t − Time − ms

R

L

= 8 Ω

C

I

= 2.2 µF

C

(BYPASS)

= 0.47 µF

−180

−160

−140

−120

−100

0 400 800 1200 1600 2000

−150

−100

−50

0

f − Frequency − Hz

− Supply Voltage − dBVV

DD

VDD Shown in Figure 19,

RL = 8 Ω,

CI = 2.2 µF,

Inputs Grounded

− Output Voltage − dBV

V

O

C

(BYPASS)

= 0.47 µF

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

GSM POWER SUPPLY REJECTION

vs

TIME

Figure 19.

10

GSM POWER SUPPLY REJECTION

vs

FREQUENCY

Figure 20.

Page 11

www.ti.com

f - Frequency - Hz

+0

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

20 20k50 100 200 500 1k 2k 5k 10k

CMRR - Common-Mode Rejection Ratio - dB

VDD = 2.5 V

RL = 4 Ω,

,

VIC = 200 mV V

p-p

,

Gain = 1 V/V ,

VDD = 5 V

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

VDD = 5 V

VDD = 2.5 V

VDD = 3.5 V

VIC - Common Mode Input Voltage - V

CMRR - Common Mode Rejection Ratio - dB

RL = 4 Ω,

,

Gain = 1 V/V ,

dc Change in V

IC

-80

-70

-60

-50

-40

-30

-20

-10

0

10

20

30

40

-180

-150

-120

-90

-60

-30

0

30

60

90

120

150

180

1 100 10 k 100 k 1 M 10 M1 k

f - Frequency - Hz

Gain - dB

Phase - Degrees

Gain

Phase

VDD = 5 V

RL = 8 Ω

AV = 1

10

−40

−30

−20

−10

0

10

20

30

40

50

60

70

80

90

100

−180

−150

−120

−90

−60

−30

0

30

60

90

120

150

180

VDD = 5 V ,

RL = 8 Ω

Gain

Phase

100 1 k 10 k 100 k 1 M

f − Frequency − Hz

Phase − Degrees

Gain − dB

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

COMMON MODE REJECTION RATIO COMMON-MODE REJECTION RATIO

vs vs

FREQUENCY COMMON-MODE INPUT VOLTAGE

Figure 21. Figure 22.

CLOSED LOOP GAIN/PHASE OPEN LOOP GAIN/PHASE

vs vs

FREQUENCY FREQUENCY

Figure 23. Figure 24.

11

Page 12

www.ti.com

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5

TA = 25°C

TA = -40°C

TA = 125°C

VDD = 5 V

VDD - Supply Voltage - V

I

DD

- Supply Current - mA

0.00001

0.0001

0.001

0.01

0.1

1

10

0

1

2 3 4 5

VDD = 3.6 V

VDD = 5 V

VDD = 2.5 V

Voltage on SHUTDOWN

Terminal - V

I

DD

- Supply Current - mA

0

50

100

150

200

250

300

0 0.2 0.4 0.6 0.8 1

C

(Bypass)

- Bypass Capacitor - µF

Start-Up Time - ms

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

SUPPLY CURRENT SUPPLY CURRENT

vs vs

SUPPLY VOLTAGE SHUTDOWN VOLTAGE

Figure 25. Figure 26.

START-UP TIME

vs

BYPASS CAPACITOR

12

Figure 27.

Page 13

www.ti.com

_

+

V

DD

V

O+

V

O−

GND

6

5

8

7

To Battery

C

s

IN−

IN+

4

3

+

−

In From

DAC

R

I

R

I

40 kΩ

40 kΩ

(1)

C

(BYPASS)

is optional

Bias

Circuitry

2

SHUTDOWN

1

C

(BYPASS)

(1)

100 kΩ

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

APPLICATION INFORMATION

• Mid-supply bypass capacitor, C

FULLY DIFFERENTIAL AMPLIFIER

The TPA6211A1 is a fully differential amplifier with

differential inputs and outputs. The fully differential

amplifier consists of a differential amplifier and a

common- mode amplifier. The differential amplifier

ensures that the amplifier outputs a differential voltage that is equal to the differential input times the

gain. The common-mode feedback ensures that the

common-mode voltage at the output is biased around

V

/2 regardless of the common- mode voltage at the

DD

input.

Advantages of Fully Differential Amplifiers

• Input coupling capacitors not required: A fully

differential amplifier with good CMRR, like the

TPA6211A1, allows the inputs to be biased at

voltage other than mid-supply. For example, if a

DAC has a lower mid-supply voltage than that of Figure 28 through Figure 31 show application schethe TPA6211A1, the common-mode feedback matics for differential and single-ended inputs. Typical

circuit compensates, and the outputs are still values are shown in Table 1 .

biased at the mid-supply point of the TPA6211A1.

The inputs of the TPA6211A1 can be biased from Table 1. Typical Component Values

0.5 V to V

outside of that range, input coupling capacitors

are required.

- 0.8 V. If the inputs are biased

DD

required: The fully differential amplifier does not

require a bypass capacitor. Any shift in the

mid-supply voltage affects both positive and

negative channels equally, thus canceling at the

differential output. Removing the bypass capacitor slightly worsens power supply rejection ratio

(k

), but a slight decrease of k

SVR

acceptable when an additional component can be

eliminated (See Figure 17 ).

• Better RF-immunity: GSM handsets save power

by turning on and shutting off the RF transmitter

at a rate of 217 Hz. The transmitted signal is

picked-up on input and output traces. The fully

differential amplifier cancels the signal much

better than the typical audio amplifier.

APPLICATION SCHEMATICS

COMPONENT VALUE

R

I

(1)

(BYPASS)

C

S

C

I

is optional.

(1) C

C

(BYPASS)

TPA6211A1

40 kΩ

0.22 µF

1 µF

0.22 µF

(BYPASS)

SVR

, not

may be

Figure 28. Typical Differential Input Application Schematic

13

Page 14

www.ti.com

_

+

V

DD

V

O+

V

O−

GND

6

5

8

7

To Battery

C

s

IN−

IN+

4

3

R

I

R

I

40 kΩ

40 kΩ

+

−

C

I

C

I

(1)

C

(BYPASS)

is optional

Bias

Circuitry

2

SHUTDOWN

1

C

(BYPASS)

(1)

100 kΩ

IN

C

I

C

I

_

+

V

DD

V

O+

V

O−

GND

6

5

8

7

To Battery

C

s

IN−

IN+

4

3

R

I

R

I

40 kΩ

40 kΩ

(1)

C

(BYPASS)

is optional

Bias

Circuitry

2

SHUTDOWN

1

C

(BYPASS)

(1)

100 kΩ

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Figure 29. Differential Input Application Schematic Optimized With Input Capacitors

14

Figure 30. Single-Ended Input Application Schematic

Page 15

www.ti.com

_

+

V

DD

V

O+

V

O−

GND

6

5

8

7

To Battery

C

s

IN−

IN+

4

3

R

I

R

I

40 kΩ

40 kΩ

+

−

C

I

C

I

C

F

C

F

C

a

C

a

R

a

R

a

(1)

C

(BYPASS)

is optional

Bias

Circuitry

2

SHUTDOWN

1

C

(BYPASS)

(1)

100 kΩ

Gain = RF/R

I

f

c

1

2 RIC

I

-3 dB

f

c

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Figure 31. Differential Input Application Schematic With Input Bandpass Filter

Selecting Components

Resistors (R

The input resistor (R

)

I

) can be selected to set the gain

I

of the amplifier according to equation 1.

The internal feedback resistors (R

40 kΩ.

Resistor matching is very important in fully differential

amplifiers. The balance of the output on the reference

voltage depends on matched ratios of the resistors.

CMRR, PSRR, and the cancellation of the second

harmonic distortion diminishes if resistor mismatch

occurs. Therefore, 1%-tolerance resistors or better

are recommended to optimize performance.

Bypass Capacitor (C

BYPASS

) and Start-Up Time

The internal voltage divider at the BYPASS pin of this

device sets a mid-supply voltage for internal references and sets the output common mode voltage to

V

/2. Adding a capacitor filters any noise into this

DD

pin, increasing k

time of V

The larger the capacitor, the slower the rise time.

and V

O+

. C

SVR

when the device exits shutdown.

O-

(BYPASS)

also determines the rise

) are trimmed to

F

(1)

Input Capacitor (C

)

I

The TPA6211A1 does not require input coupling

capacitors when driven by a differential input source

biased from 0.5 V to V

- 0.8 V. Use 1% tolerance

DD

or better gain-setting resistors if not using input

coupling capacitors.

In the single-ended input application, an input capacitor, CI, is required to allow the amplifier to bias the

input signal to the proper dc level. In this case, CIand

R

form a high-pass filter with the corner frequency

I

defined in Equation 2 .

(2)

15

Page 16

www.ti.com

f

c(HPF)

1

2 10 k C

I

C

I

1

2 10 k f

c(HPF)

C

I

1

2 RIf

c

f

c(LPF)

1

2 RaC

a

C

a

1

2 1kΩ f

c(LPF)

f

c(LPF)

1

2 RFC

F

where RFis the internal 40 k resistor

f

c(LPF)

1

2 40 k C

F

C

F

1

2 40 k f

c(LPF)

9 dB

f

c(HPF)

= 100 Hz

12 dB

AV

+20 dB/dec

−40 dB/dec

−20 dB/dec

f

f

c(LPF)

= 10 kHz

f

c(HPF)

1

2 RIC

I

where RIis the input resistor

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

The value of C

is an important consideration. It Substituting RIinto equation 6.

I

directly affects the bass (low frequency) performance

of the circuit. Consider the example where R

I

kΩ and the specification calls for a flat bass response

down to 100 Hz. Equation 2 is reconfigured as

Equation 3 .

In this example, C

is 0.16 µF, so the likely choice

I

ranges from 0.22 µF to 0.47 µF. Ceramic capacitors

are preferred because they are the best choice in

preventing leakage current. When polarized capacitors are used, the positive side of the capacitor faces

the amplifier input in most applications. The input dc

level is held at V

/2, typically higher than the source

DD

dc level. It is important to confirm the capacitor

polarity in the application.

Band-Pass Filter (R

, Ca, and Ca)

a

It may be desirable to have signal filtering beyond the

one-pole high-pass filter formed by the combination of

C

and RI. A low-pass filter may be added by placing

I

a capacitor (C

) between the inputs and outputs,

F

forming a band-pass filter.

An example of when this technique might be used

would be in an application where the desirable

pass-band range is between 100 Hz and 10 kHz, with

a gain of 4 V/V. The following equations illustrate how

the proper values of C

and CIcan be determined.

F

is 10

(8)

Therefore,

(3)

Substituting 100 Hz for f

and solving for CI:

c(HPF)

(9)

CI= 0.16 µF

At this point, a first-order band-pass filter has been

created with the low-frequency cutoff set to 100 Hz

and the high-frequency cutoff set to 10 kHz.

The process can be taken a step further by creating a

second-order high-pass filter. This is accomplished by

placing a resistor (R

path. It is important to note that R

) and capacitor (C

a

must be at least

a

a

) in the input

10 times smaller than RI; otherwise its value has a

noticeable effect on the gain, as R

and R

a

are in

I

series.

Step 3: Additional Low-Pass Filter

R

must be at least 10x smaller than RI,

a

Set R

= 1 kΩ

a

(10)

Therefore,

Step 1: Low-Pass Filter

Therefore,

Substituting 10 kHz for f

C

= 398 pF

F

Step 2: High-Pass Filter

Since the application in this case requires a gain of

4 V/V, RImust be set to 10 kΩ.

and solving for CF:

c(LPF)

(11)

Substituting 10 kHz for f

C

= 160 pF

(4)

a

and solving for Ca:

c(LPF)

Figure 32 is a bode plot for the band-pass filter in the

previous example. Figure 31 shows how to configure

(5)

(6)

the TPA6211A1 as a band-pass filter.

Figure 32. Bode Plot

(7)

16

Page 17

www.ti.com

V

(rms)

V

O(PP)

2 2

Power

V

(rms)

2

R

L

R

L

2x V

O(PP)

V

O(PP)

-V

O(PP)

V

DD

V

DD

f

c

1

2 RLC

C

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Decoupling Capacitor (C

)

S

The TPA6211A1 is a high-performance CMOS audio

amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion

(THD) is as low as possible. Power-supply decoupling

also prevents oscillations for long lead lengths between the amplifier and the speaker. For higher

frequency transients, spikes, or digital hash on the

line, a good low equivalent-series-resistance (ESR)

ceramic capacitor, typically 0.1 µF to 1 µF, placed as

close as possible to the device V

DD

lead works best.

For filtering lower frequency noise signals, a 10-µF or

greater capacitor placed near the audio power amplifier also helps, but is not required in most applications

because of the high PSRR of this device.

USING LOW-ESR CAPACITORS

Low-ESR capacitors are recommended throughout

this applications section. A real (as opposed to ideal)

capacitor can be modeled simply as a resistor in

series with an ideal capacitor. The voltage drop

across this resistor minimizes the beneficial effects of

the capacitor in the circuit. The lower the equivalent

value of this resistance the more the real capacitor

behaves like an ideal capacitor.

DIFFERENTIAL OUTPUT VERSUS SINGLE-ENDED OUTPUT

Figure 33 shows a Class-AB audio power amplifier

(APA) in a fully differential configuration. The

TPA6211A1 amplifier has differential outputs driving

both ends of the load. One of several potential

benefits to this configuration is power to the load. The

differential drive to the speaker means that as one

side is slewing up, the other side is slewing down,

and vice versa. This in effect doubles the voltage

swing on the load as compared to a

ground-referenced load. Plugging 2 × V

power equation, where voltage is squared, yields 4×

the output power from the same supply rail and load

impedance Equation 12 .

into the

O(PP)

Figure 33. Differential Output Configuration

In a typical wireless handset operating at 3.6 V,

bridging raises the power into an 8-Ω speaker from a

singled-ended (SE, ground reference) limit of 200

mW to 800 mW. This is a 6-dB improvement in sound

power—loudness that can be heard. In addition to

increased power, there are frequency-response concerns. Consider the single-supply SE configuration

shown in Figure 34 . A coupling capacitor (C

C

required to block the dc-offset voltage from the load.

This capacitor can be quite large (approximately 33

µF to 1000 µF) so it tends to be expensive, heavy,

occupy valuable PCB area, and have the additional

drawback of limiting low-frequency performance. This

frequency-limiting effect is due to the high-pass filter

network created with the speaker impedance and the

coupling capacitance. This is calculated with

Equation 13 .

(12)

) is

(13)

For example, a 68-µF capacitor with an 8-Ω speaker

would attenuate low frequencies below 293 Hz. The

BTL configuration cancels the dc offsets, which eliminates the need for the blocking capacitors.

Low-frequency performance is then limited only by

the input network and speaker response. Cost and

PCB space are also minimized by eliminating the

bulky coupling capacitor.

17

Page 18

www.ti.com

R

L

C

C

V

O(PP)

V

O(PP)

V

DD

-3 dB

f

c

V

(LRMS)

V

O

I

DD

I

DD(avg)

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Figure 34. Single-Ended Output and Frequency

Response

An easy-to-use equation to calculate efficiency starts

out as being equal to the ratio of power from the

power supply to the power delivered to the load. To

accurately calculate the RMS and average values of

power in the load and in the amplifier, the current and

voltage waveform shapes must first be understood

(see Figure 35 ).

Increasing power to the load does carry a penalty of

increased internal power dissipation. The increased

dissipation is understandable considering that the

BTL configuration produces 4× the output power of

the SE configuration.

FULLY DIFFERENTIAL AMPLIFIER EFFICIENCY AND THERMAL INFORMATION

Class-AB amplifiers are inefficient, primarily because

of voltage drop across the output-stage transistors.

The two components of this internal voltage drop are

the headroom or dc voltage drop that varies inversely

to output power, and the sinewave nature of the

output. The total voltage drop can be calculated by

subtracting the RMS value of the output voltage from

V

. The internal voltage drop multiplied by the

DD

average value of the supply current, IDD(avg), determines the internal power dissipation of the amplifier.

Figure 35. Voltage and Current Waveforms for

BTL Amplifiers

Although the voltages and currents for SE and BTL

are sinusoidal in the load, currents from the supply

are different between SE and BTL configurations. In

an SE application the current waveform is a

half-wave rectified shape, whereas in BTL it is a

full-wave rectified waveform. This means RMS conversion factors are different. Keep in mind that for

most of the waveform both the push and pull transistors are not on at the same time, which supports the

fact that each amplifier in the BTL device only draws

current from the supply for half the waveform. The

following equations are the basis for calculating

amplifier efficiency.

18

Page 19

www.ti.com

Efficiency of a BTL amplifier

P

L

P

SUP

Where:

P

L

VLrms

2

R

L

, and V

LRMS

V

P

2

, therefore, P

L

V

P

2

2R

L

PL = Power delivered to load

P

SUP

= Power drawn from power supply

V

LRMS

= RMS voltage on BTL load

RL = Load resistance

VP = Peak voltage on BTL load

IDDavg = Average current drawn from the power supply

VDD = Power supply voltage

η

BTL

= Efficiency of a BTL amplifier

and

P

SUP

VDDIDDavg

and

IDDavg

1

0

V

P

R

L

sin(t) dt

1

V

P

R

L

[cos(t)]

0

2V

P

R

L

Therefore,

P

SUP

2 VDDV

P

R

L

substituting PL and P

SUP

into equation 6,

Efficiency of a BTL amplifier

V

P

2

2 R

L

2 VDDV

P

R

L

V

P

4 V

DD

VP 2 PLR

L

Where:

BTL

2 PLR

L

4 V

DD

Therefore,

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Output Power Efficiency Internal Dissipation Power From Supply Max Ambient Temperature

(W) (%) (W) (W) (°C)

0.5 27.2 1.34 1.84 85

1 38.4 1.60 2.60 76

2.45 60.2 1.62 4.07 75

3.1 67.7 1.48 4.58 82

0.5 31.4 1.09 1.59 85

(1) DRB package

(2) Package limited to 85°C ambient

1 44.4 1.25 2.25 85

2 62.8 1.18 3.18 85

2.8 74.3 0.97 3.77 85

0.5 44.4 0.625 1.13 85

1 62.8 0.592 1.60 85

1.36 73.3 0.496 1.86 85

1.7 81.9 0.375 2.08 85

Table 2. Efficiency and Maximum Ambient Temperature vs Output Power

5-V, 3-Ω Systems

5-V, 4-Ω BTL Systems

5-V, 8-Ω Systems

(14)

(15)

(1)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

19

Page 20

www.ti.com

(9)

θ

JA

1

Derating Factor

1

0.0218

45.9°CW

TAMax TJMax θJAP

Dmax

150 45.9(1.27) 91.7°C

P

Dmax

2V

2

DD

2

R

L

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

Table 2 employs Equation 15 to calculate efficiencies

for four different output power levels. Note that the

efficiency of the amplifier is quite low for lower power

levels and rises sharply as power to the load is

increased resulting in a nearly flat internal power

dissipation over the normal operating range. Note that

the internal dissipation at full output power is less

than in the half power range. Calculating the efficiency for a specific system is the key to proper

power supply design. For a 2.8-W audio system with

4-Ω loads and a 5-V supply, the maximum draw on

the power supply is almost 3.8 W.

A final point to remember about Class-AB amplifiers

is how to manipulate the terms in the efficiency

equation to the utmost advantage when possible.

Note that in Equation 15 , V

This indicates that as V

DD

is in the denominator.

DD

goes down, efficiency goes

up.

A simple formula for calculating the maximum power

dissipated, P

, may be used for a differential

Dmax

output application:

P

for a 5-V, 4-Ω system is 1.27 W.

Dmax

The maximum ambient temperature depends on the

heat sinking ability of the PCB system. The derating

factor for the 3 mm x 3 mm DRB package is shown in

the dissipation rating table. Converting this to θJA:

(17)

Given θJA, the maximum allowable junction temperature, and the maximum internal dissipation, the maximum ambient temperature can be calculated with

Equation 18 . The maximum recommended junction

temperature for the TPA6211A1 is 150°C.

(18)

Equation 18 shows that the maximum ambient temperature is 91.7°C (package limited to 85°C ambient)

at maximum power dissipation with a 5-V supply.

Table 2 shows that for most applications no airflow is

required to keep junction temperatures in the specified range. The TPA6211A1 is designed with thermal

protection that turns the device off when the junction

(16)

temperature surpasses 150°C to prevent damage to

the IC. In addition, using speakers with an impedance

higher than 4-Ω dramatically increases the thermal

performance by reducing the output current.

20

Page 21

www.ti.com

0.65 mm

0.38 mm

Solder Mask: 1.4 mm x 1.85 mm centered in package

0.7 mm

1.4 mm

Make solder paste a hatch pattern to fill 50%

3.3 mm

1.95 mm

0.33 mm plugged vias (5 places)

TPA6211A1

SLOS367B – AUGUST 2003 – REVISED AUGUST 2004

PCB LAYOUT

Use the following land pattern for board layout with the 8-pin QFN (DRB) package. Note that the solder paste

should use a hatch pattern to fill solder paste at 50% to ensure that there is not too much solder paste under the

package.

Figure 36. TPA6211A1 8-Pin QFN (DRB) Board Layout (Top View)

21

Page 22

PACKAGE OPTION ADDENDUM

www.ti.com

18-Apr-2006

PACKAGING INFORMATION

Orderable Device Status

TPA6211A1DGN ACTIVE MSOP-

(1)

Package

Type

Power

Package

Drawing

Pins Package

Qty

Eco Plan

DGN 8 80 Green (RoHS &

no Sb/Br)

PAD

TPA6211A1DGNG4 ACTIVE MSOP-

Power

DGN 8 80 Green (RoHS &

no Sb/Br)

PAD

TPA6211A1DGNR ACTIVE MSOP-

Power

DGN 8 2500 Green (RoHS &

no Sb/Br)

PAD

TPA6211A1DGNRG4 ACTIVE MSOP-

Power

DGN 8 2500 Green (RoHS &

no Sb/Br)

PAD

TPA6211A1DRB ACTIVE SON DRB 8 121 Green (RoHS &

no Sb/Br)

TPA6211A1DRBG4 ACTIVE SON DRB 8 121 Green (RoHS &

no Sb/Br)

TPA6211A1DRBR ACTIVE SON DRB 8 3000 Green (RoHS &

no Sb/Br)

TPA6211A1DRBRG4 ACTIVE SON DRB 8 3000 Green (RoHS &

no Sb/Br)

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in

a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Lead/Ball Finish MSL Peak Temp

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

(3)

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check

http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements

for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered

at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and

package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame

retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder

temperature.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the

accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on

incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited

information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI

to Customer on an annual basis.

Addendum-Page 1

Page 23

PACKAGE MATERIALS INFORMATION

www.ti.com

TAPE AND REEL INFORMATION

11-Mar-2008

*All dimensions are nominal

Device Package

TPA6211A1DGNR MSOP-

Power

TPA6211A1DRBR SON DRB 8 3000 330.0 12.4 3.3 3.3 1.1 8.0 12.0 Q2

Type

PAD

Package

Drawing

DGN 8 2500 330.0 12.4 5.3 3.4 1.4 8.0 12.0 Q1

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0 (mm) B0 (mm) K0 (mm) P1

(mm)W(mm)

Pin1

Quadrant

Pack Materials-Page 1

Page 24

PACKAGE MATERIALS INFORMATION

www.ti.com

11-Mar-2008

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TPA6211A1DGNR MSOP-PowerPAD DGN 8 2500 358.0 335.0 35.0

TPA6211A1DRBR SON DRB 8 3000 346.0 346.0 29.0

Pack Materials-Page 2

Page 25

Page 26

Page 27

Page 28

Page 29

Page 30

Page 31

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Clocks and Timers www.ti.com/clocks Digital Control www.ti.com/digitalcontrol

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

RF/IF and ZigBee® Solutions www.ti.com/lprf Video & Imaging www.ti.com/video

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2008, Texas Instruments Incorporated

Wireless www.ti.com/wireless

Loading...

Loading...