Page 1

ADVANCE INFORMATION

User's Guide

SLAU756–January 2018

TPA3220 Evaluation Module Micro

This user's guide describes the characteristics, operation, and use of the TPA3220 Evaluation Module

Micro. A complete printed-circuit board (PCB) description, schematic diagram, and bill of materials (BOM)

are also included.

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

1

Page 2

ADVANCE INFORMATION

www.ti.com

Contents

1 Quick Start (BTL MODE) ................................................................................................... 3

2 Setup By Mode .............................................................................................................. 5

3 Hardware Configuration .................................................................................................... 7

4 EVM Design Documents ................................................................................................. 13

5 Schematic and Bill of Materials........................................................................................... 15

List of Figures

1 Output Configuration BTL .................................................................................................. 3

2 EVM Board (Top Side) ..................................................................................................... 4

3 EVM Board (Bottom Side) ................................................................................................. 4

4 Output Configuration PBTL - 4 Inductors................................................................................. 5

5 Filter Frequency Response .............................................................................................. 11

6 TPA3220EVM-Micro Top Composite Assembly ....................................................................... 13

7 TPA3220EVM-Micro Bottom Composite Assembly ................................................................... 13

8 TPA3220EVM-Micro Board Dimensions ................................................................................ 14

9 TPA3220EVM-MICRO Schematic 1..................................................................................... 15

10 TPA3220EVM-MICRO Schematic 2 ..................................................................................... 16

1 Jumper and Switch Configurations (BTL Mode)......................................................................... 4

2 Jumper and Switch Configurations (PBTL Mode) ....................................................................... 6

3 Fault and Clip Overtemperature Status .................................................................................. 7

4 Frequency Adjust Master Mode Selection ............................................................................... 7

5 HEAD and AD Mode Selection ............................................................................................ 8

6 Output Mode and Modulation Mode Selection........................................................................... 8

7 Default Mode Configuration ............................................................................................... 9

8 LDO Mode Configuration .................................................................................................. 9

9 Non-5-V Supply Configuration ........................................................................................... 10

10 External 5-V Supply Mode Configuration .............................................................................. 10

11 AIB Connector (J3) Pinout ............................................................................................... 12

12 Bill of Materials ............................................................................................................. 17

Trademarks

CoilCraft is a trademark of CoilCraft, Inc.

All other trademarks are the property of their respective owners.

List of Tables

2

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 3

Class-D

Amplifier

OUT-A

OUT-B

OUT-C

OUT-D

ADVANCE INFORMATION

www.ti.com

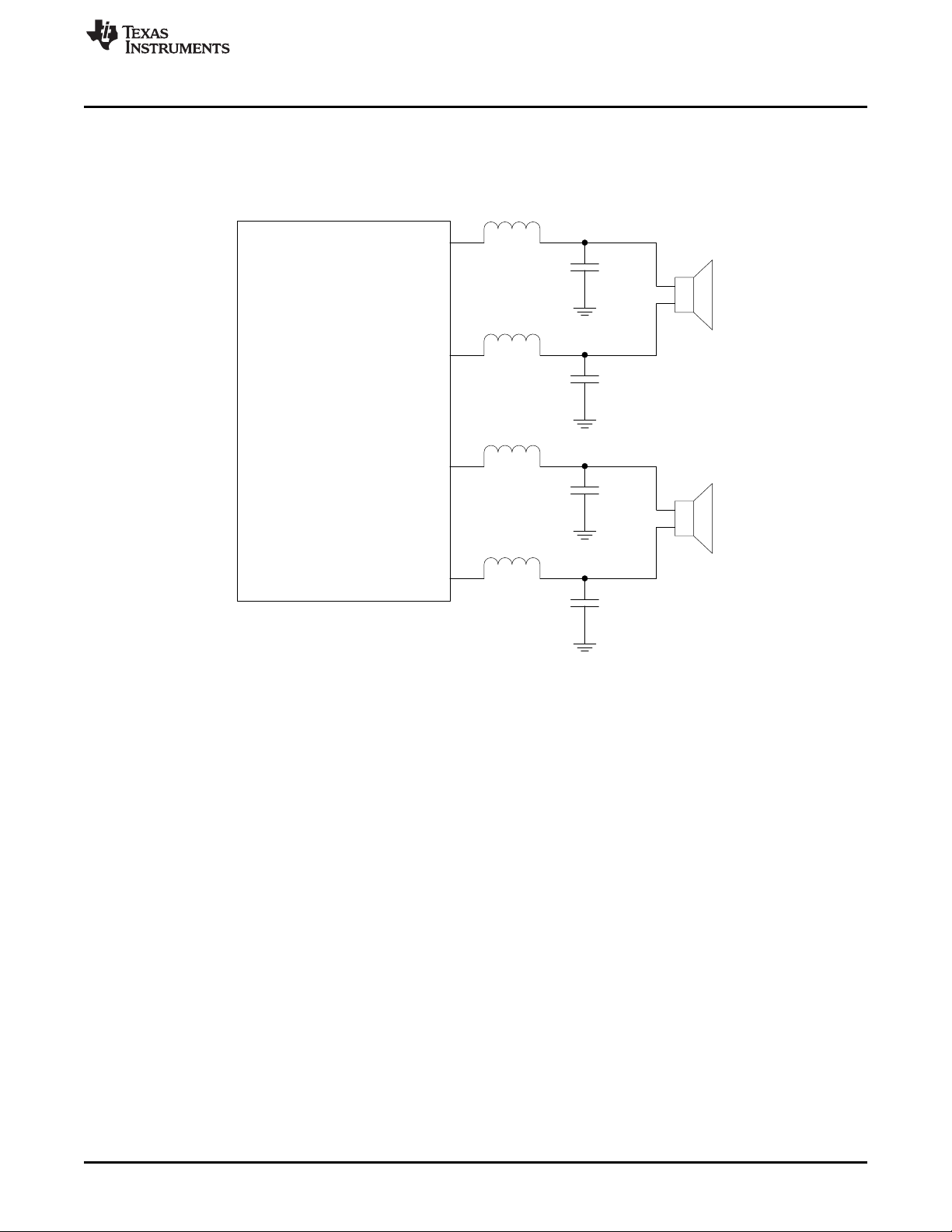

1 Quick Start (BTL MODE)

The following section describes the necessary hardware, connections, configuration, and steps to quick

start the EVM into BTL mode with stereo audio playing out of two speakers.

Figure 1 illustrates the BTL mode output configuration

Quick Start (BTL MODE)

1.1 Required Hardware

The following hardware is required for this EVM:

• TPA3220EVM-Micro

• Power supply 5–14 A, 12–30 VDC

• Two 2–8 Ω speaker or resistor loads (ensure speaker or load is appropriately sized for required

wattage output)

• Four 12–20 AWG wires

• One XLR to 3.5-mm audio jack

• Analog output audio source

Figure 1. Output Configuration BTL

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

3

Page 4

ADVANCE INFORMATION

Quick Start (BTL MODE)

1.2 Connections and Board Configuration

Figure 2 and Figure 3 illustrate the top and bottom of the EVM.

Figure 2. EVM Board (Top Side) Figure 3. EVM Board (Bottom Side)

Use the following steps when connecting and configuring the board in BTL MODE:

1. Ensure the power supply is OFF. Connect the power supply positive terminal to J6 PVDD and negative

terminal to J6 GND.

2. Connect the left channel speaker, power resistor load (3–8 Ω) to the TPA3220EVM-Micro positive

output terminal (J4 OUT1+) and other side of the speaker, power resistor to the TPA3220EVM-Micro

negative output terminal (J4 OUT1–).

3. Connect the right channel speaker, power resistor load (3–8 Ω) to the TPA3220EVM-Micro positive

output terminal (J5 OUT2+) and other side of the speaker, power resistor to the TPA3220EVM-Micro

negative output terminal (J5 OUT2–).

4. Check to make sure that the power supply is only connected to J6 and speakers are connected to J4

or J5 only, as their colors are the same.

5. Input Configuration:

a. Differential Inputs: Depopulate R3 and R13

b. Single-Ended Inputs: Populate R3 and R13

c. Audio Interface Board Input: Populate R1, R2, R11, and R12

6. Ensure that RESET S1 is in the lower position of RESET.

7. Check Table 1 for all necessary jumper and switch configurations.

www.ti.com

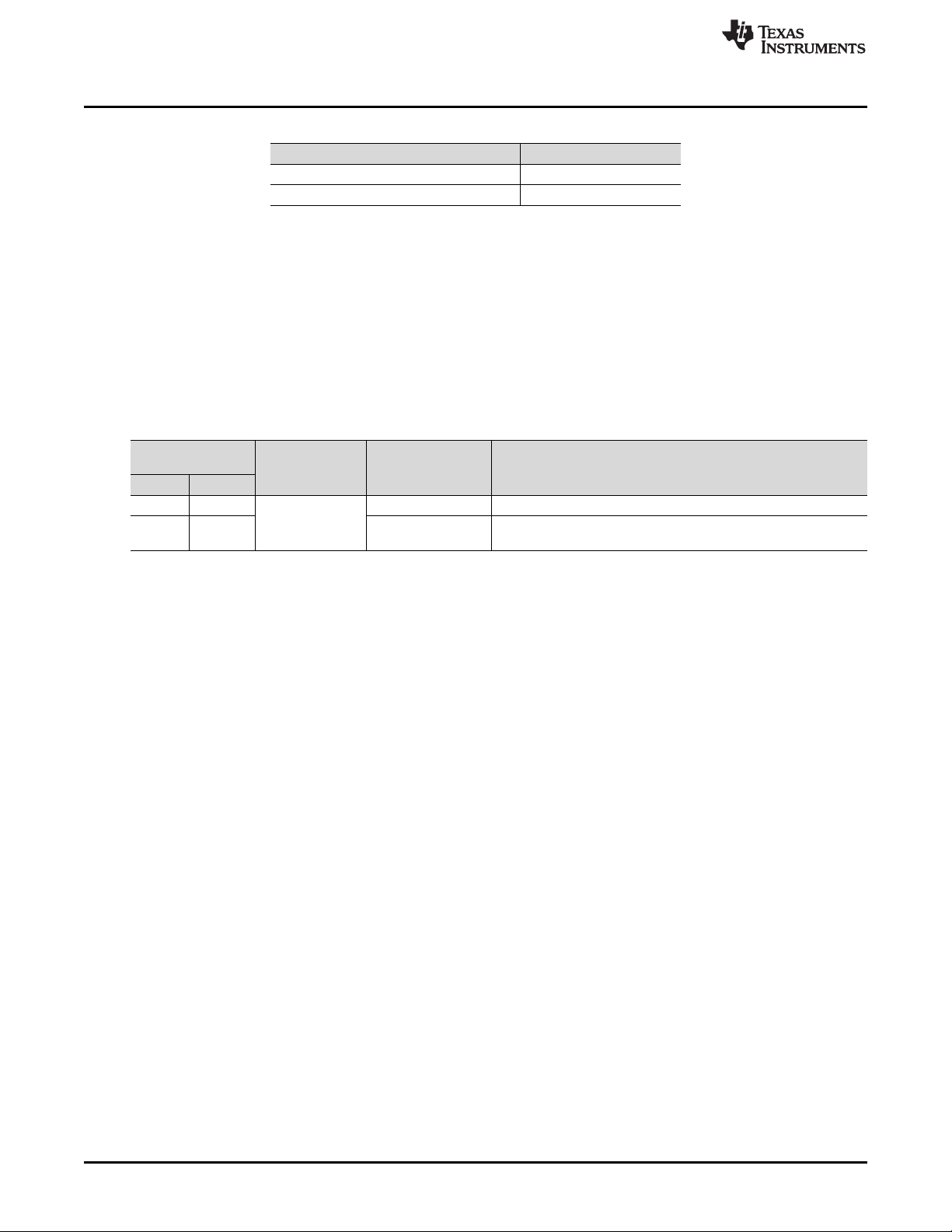

Table 1. Jumper and Switch Configurations (BTL Mode)

Component Component Description Configuration for BTL

R28, R31 Gain/SLV Select MSTR-34dB

R3, R13 Input DIFF or SE Select SE = Populate

DIFF = Remove

R1, R2, R11,

R12

R27, R29 HEAD or AD Mode Select HEAD = Populate R27, Remove R29

R22, R26 PBTL or BTL Select Remove

S1 RESET Control RESET

R25 FREQ_ADJ MASTER MODE = 480kHz

4

TPA3220 Evaluation Module Micro

AIB Input Select Populated

AD = Remove R27, Populate R29

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 5

Class-D

Amplifier

OUT-A

OUT-B

OUT-C

OUT-D

ADVANCE INFORMATION

www.ti.com

1.3 Power-Up

Ensure that required connections and configurations have been checked. The TPA3220EVM-Micro board

can now be powered on.

1. Enable the power supply at 12 V to 30 V and ensure that LED D2 illuminates. LEDs D1 and D3 should

not be illuminated.

2. Switch S1 out of RESET. The FAULT LED (D1) should blink once quickly, then remain unilluminated.

3. Note that the EVM does not have volume control, configure your analog input for a reasonable audio

level before beginning audio playback.

4. Enable audio input playback and the EVM should begin driving audio out of the left and right speakers.

If resistor loads are used for testing instead of speakers, they will now be energized.

2 Setup By Mode

The following sections describe the setup and configuration for each output mode. The TPA3220DDV

EVM-Micro allows for two output modes: Stereo BTL and Mono PBTL.

2.1 BTL MODE (Stereo - 2 Speaker Outputs)

This mode is the same as described in Quick Start (BTL MODE) .

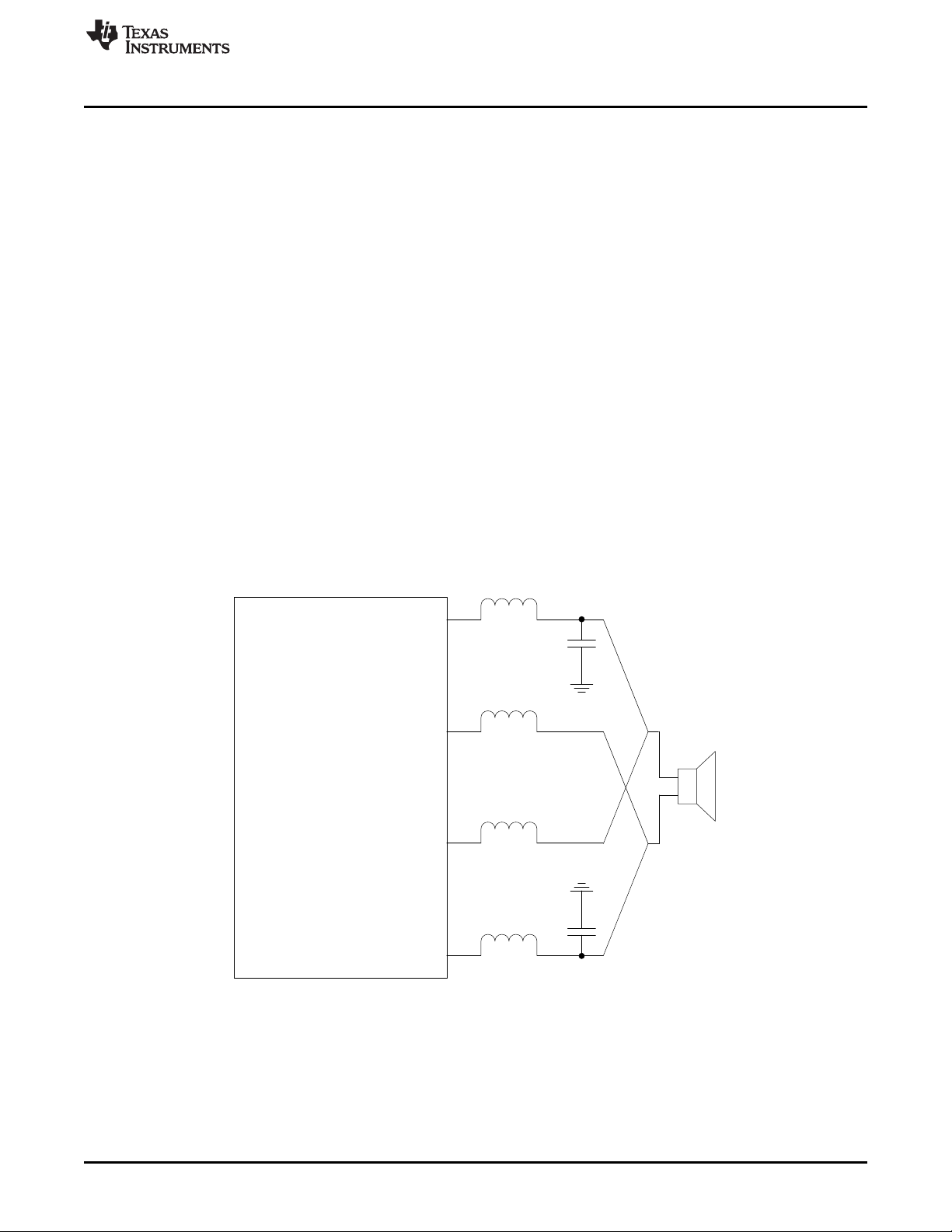

2.2 PBTL MODE (Mono – 1 Speaker Output)

This mode provides one speaker output that is more powerful than each BTL output and is useful when

mono audio is to be played or when more power is needed.

Figure 4 illustrates the PBTL mode output configuration with 4 inductors.

Quick Start (BTL MODE)

Figure 4. Output Configuration PBTL - 4 Inductors

2.2.1 Connections and Board Configuration

Use the following steps when connecting and configuring the board in BTL MODE:

1. Ensure the power supply is OFF. Connect the positive terminal of the power supply to J6 PVDD and

negative terminal to J6 GND.

2. Connect one channel speaker, power resistor load (2–8 Ω) to the TPA3220EVM-Micro positive output

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

5

Page 6

ADVANCE INFORMATION

Setup By Mode

terminal (J4 OUT1+) and other side of the speaker, power resistor to the TPA3220EVM-Micro negative

output terminal (J4 OUT1–).

3. Use a wire to connect J5 OUT2+ to J4 OUT1+, then use another wire to connect J5 OUT2– to J4

OUT1–. This forms a parallel connection of both OUTx+ to one side of the speaker and a parallel

connection of both OUTx– to the other side of the speaker.

4. Check to make sure that the power supply is connected to J6 only and speakers are connected to J4

or J5 only, as their colors are the same.

5. Input Configuration:

a. Differential Inputs: Depopulate R3 and R13

b. Single-Ended Inputs: Populate R3 and R13

c. Audio Interface Board Input: Populate R1, R2, R11, and R12

6. Ensure that RESET S1 is in the lower position of RESET.

7. Check Table 2 for all jumper and switch configurations necessary.

www.ti.com

Table 2. Jumper and Switch Configurations (PBTL Mode)

Component Component Description Configuration for PBTL

R28, R31 Gain/SLV Select MSTR-34dB

R3, R13 Input DIFF or SE Select SE = Populate

DIFF = Remove

R1, R2, R11, R12 AIB Input Select Populated

R27, R29 HEAD or AD Mode Select HEAD = Populate R27, Remove R29

AD = Remove R27, Populate R29

R22, R26 PBTL or BTL Select Populate

S1 RESET Control RESET

R25 FREQ_ADJ MASTER MODE = 480 kHz

2.2.2 Power-Up

Ensure that required connections and configurations have been checked. The TPA3220EVM-Micro board

can now be powered on.

1. Enable the power supply at 12 V to 30 V and ensure that LED D2 illuminates. LEDs D1 and D3 should

not be illuminated.

2. Switch S1 out of RESET. The FAULT LED (D1) should blink once quickly, then remain unilluminated.

3. Note that the EVM does not have volume control, configure your analog input for a reasonable audio

level before beginning audio playback.

4. Enable audio input playback and the EVM should begin driving audio out of the left and right speakers.

If resistor loads are used for testing instead of speakers, they will now be energized.

6

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 7

ADVANCE INFORMATION

www.ti.com

3 Hardware Configuration

3.1 Indicator Overview (CLIP_OTW and FAULT)

The TPA3220EVM-Micro is equipped with LED indicators that illuminate when the FAULT or CLIP_OTW

pin goes low. See Table 3 and TPA3220 100-W Peak HD-Audio, Analog-Input, Class-D for more details.

Table 3. Fault and Clip Overtemperature Status

FAULT LED

Status

ON ON Overtemperature (OTE) or overload (OLP) or undervoltage (UVP). Junction

ON OFF Overload (OLP) or undervoltage (UVP). Junction temperature lower than 125°C

OFF ON Junction temperature higher than 125°C (OTE warning)

OFF OFF Junction temperature lower than 125°C and no OLP or UVP faults (normal

CLIP_OTW LED Status Description

temperature higher than 125°C (OTE warning)

operation)

3.2 PWM Frequency Adjust

The TPA3220EVM-Micro allows for three oscillator frequency options by external configuration of the

FREQ_ADJ pin. The frequency adjust can be used to reduce interference problems while using a radio

receiver tuned within the AM band. These values should be chosen such that the nominal and the lower

value switching frequencies together results in the fewest cases of interference throughout the AM band.

The oscillator frequency can be selected by the value of the FREQ_ADJ resistor connected to GND in

master mode according to Table 4.

Hardware Configuration

Table 4. Frequency Adjust Master Mode Selection

FREQ_ADJ (R25, R) Resistor Value PWM Frequency

Master MODE 49.9 kΩ 600 kHz

Master MODE 30 kΩ 533 kHz

Master MODE 10 kΩ 480 kHz

Slave MODE Pull up to 5 V N/A

Selecting Slave Mode configures the OSC_I/O pins as inputs to be slaved from an external differential

clock. In a master or slave system, interchannel delay is automatically set up between the switching

phases of the audio channels, which can be illustrated by no idle channels switching at the same time.

This will not influence the audio output, but only the switch timing to minimize noise coupling between

audio channels through the power supply. This will optimize audio performance and result in better

operating conditions for the power supply. The inter-channel delay will be set up for a slave device

depending on the polarity of the OSC_I/O connection such that slave mode 1 is selected by connecting

the OSC_I/O of the master device with the OSC_I/O of the slave device with the same polarity (+ to +

and – to –), while slave mode 2 is selected by connecting the OSC_I/Os with the inverse polarity (+ to –

and – to +).

3.3 Modulation Modes (AD Mode and HEAD Mode)

The TPA3220EVM-Micro supports both AD modulation as well as HEAD modulation. In AD mode, each of

the two half-bridge outputs are continuously switching. AD mode is the default mode for the

TPA3220EVM-Micro. The EVM also supports HEAD mode modulation. HEAD mode also switches both

half-bridge outputs but also optimizes the switching for lower power loss at idle as well as increased EMI

performance at cost of some performance. The device accomplishes this by reducing its duty cycle at idle

and while playing small signals. At higher output levels HEAD mode will also reduce the switching on one

of the half bridges. The modulation mode can be controlled through jumper J6 on the EVM as follows:

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

7

Page 8

ADVANCE INFORMATION

Hardware Configuration

More information on the differences between HEAD mode and AD mode as well as performance data is

found in TPA3220 100-W Peak HD-Audio, Analog-Input, Class-D .

3.4 Output Mode Selection

The TPA3220 does not use discrete mode pins and therefore relies solely on the states of the IN2_M and

IN2_P pins. Connecting the IN2_M and IN2_P pins to regular high output impedance audio outputs by

removing J7 and J8 puts the TPA3220 into BTL mode (2 × stereo outputs). Tying the IN2_M and IN2_P

pins to GND by populating R22 and R26 puts the TPA3220 into PBTL mode (1 × mono output). This is

summarized in Table 6:

Table 6. Output Mode and Modulation Mode Selection

Input Resistors

R22 and R26

IN2_M IN2_P

OUT OUT 1N / 2N + 1 2 × BTL Stereo BTL output configuration

IN IN 1 × PBTL Mono paralleled BTL configuration. Connect OUT1+ to OUT2+

Input Mode

Table 5. HEAD and AD Mode Selection

Resistors State (R27, R29) Modulation Mode

R27 = Populate, R29 = Remove AD Mode

R27 = Remove, R29 = Populate HEAD Mode

Output

Configuration

Description

and OUT1– to OUT2–.

www.ti.com

3.5 EVM Power Tree

The TPA3220EVM-Micro includes a few options for power configuration so that various input types can be

evaluated.

3.5.1 TPA3220 Supplies

The TPA3220 device has a few power supplies which each have their own voltage range and rules.

Details for each supply are as shown:

• PVDD – This is the main device supply which accepts from 7 V to 30 V. Power output of the device is

derived solely from PVDD and therefore it is important to configure this supply according to the chosen

output configuration and load. Complete details are included in TPA3220 100-W Peak HD-Audio,

Analog-Input, Class-D .

• VDD – This supply is used for the non-PVDD power of the device for blocks such as the front-end and

control circuitry. The TPA3220 internal 5-V LDO is also powered by this pin. VDD can be powered by 5

V directly if using the TPA3220 with the internal regulator OFF. In this case, tie the GVDD and AVDD

pins directly to VDD through R18 and remove R16. When the internal regulator is used, VDD must be

between 7 V and PVDD through R16. GVDD and AVDD are only 5-V tolerant, so R18 must be

removed.

• GVDD and AVDD – These pins are used for the gate drive and analog supply of the device. These

pins accept only 5 V. When the internal regulator is used, these pins are fed internal to the device, no

external connection is necessary. When the internal regulator is OFF.

8

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 9

ADVANCE INFORMATION

www.ti.com

3.5.2 TPA3220EVM-Micro Power Options

3.5.2.1 Default Mode

This is the default configuration of TPA3220EVM-Micro. In this configuration, the TPA3220 utilizes the

onboard buck converter to bring down PVDD to 5 V.

Table 7 shows how to configure TPA3220EVM-Micro into this mode.

Table 7. Default Mode Configuration

Component Component Description Configuration for LDO Mode

R16 PVDD to VDD Connector Populate

R18 5 V to VDD Connector Remove

R14 5 V to GVDD Connector Populate

D4 Buck Input Component Populate

L4, C31, R38 Buck Output Components Populate

R40 Voltage Divider for RESET Remove

3.5.2.2 PVDD Only (12 V to 30 V) LDO Mode

This power mode is the default setup when the board is tested and shipped. The user can connect any

valid supply voltage to J1 and the onboard LDOs will generate the required non-PVDD voltages. PVDD

itself always connects directly to the TPA3220 PVDD pins. Setup for this mode is the same as described

in Quick Start (BTL MODE) .

Table 8 shows how to configure the TPA3220EVM-Micro into this mode.

Hardware Configuration

Table 8. LDO Mode Configuration

Component Component Description Configuration for LDO Mode

R16 PVDD to VDD Connector Populate

R18 5 V to VDD Connector Remove

R14 5 V to GVDD Connector Populate

D4 Buck Input Component Remove

L4, C31, R38 Buck Output Components Remove

R40 Voltage Divider for RESET Remove

3.5.2.3 PVDD (12 V to 30 V) and One Non-5-V Supply

This power mode is useful for certain applications where a system has one higher voltage used for PVDD

and a second lower voltage that may be used for device pullups and other supplies (VDD, GVDD, and

AVDD).

Special consideration must be taken for the RESET pin. The RESET pin needs to have a 5-V input. In

order to do this R40 must be installed to create a voltage divider network that will drop the voltage down to

5 V.

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

9

Page 10

ADVANCE INFORMATION

Hardware Configuration

Table 9 shows how to configure TPA3220EVM-Micro into this mode.

Table 9. Non-5-V Supply Configuration

Component Component Description Configuration for External Non-5-V

R16 PVDD to VDD Connector Populate

R18 5 V to VDD Connector Remove

R14 5 V to GVDD Connector Remove

D4 Buck Input Component Remove

L4, C31, R38 Buck Output Components Remove

R40 Voltage Divider for RESET Populate

3.5.2.4 PVDD (12 V to 30 V) and External 5-V Supply

This power mode is most useful for systems in which a 5-V supply is already available due to additional

circuitry like an MCU or wireless module. On the EVM, this is also the preferred way to measure efficiency

of the TPA3220 device.

Table 10 shows how to configure TPA3220EVM-Micro into this mode.

Table 10. External 5-V Supply Mode Configuration

Component Component Description Configuration for External 5-V

R16 PVDD to VDD Connector Remove

R18 5 V to VDD Connector Populate

R14 5 V to GVDD Connector Populate

D4 Buck Input Component Remove

L4, C31, R38 Buck Output Components Remove

R40 Voltage Divider for RESET Remove

www.ti.com

Mode

Mode

10

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 11

ADVANCE INFORMATION

www.ti.com

3.6 LC Response and Overview

Included near the output of the TPA3220 device are four output LC filters. These output filters filter the

pulse-width modulation (PWM) output, leaving only the audio content at high power, which is fed to the

speakers. The board uses a CoilCraft™ 7-µH inductor and a 0.68-µF film capacitor to form this LC filter.

Using the equations listed in LC Filter Design , the low-pass filter cutoff is calculated as follows in

Equation 1:

Hardware Configuration

(1)

3.7 Reset Circuit and POR

The TPA3220EVM-Micro includes RESET supervision so that the TPA3220 device will remain in reset

until all power rails are up and stable. The RESET supervisor also ensures that the device will be put into

reset if one of the power rails experiences a brown out. This circuit, combined with the RESET switch (S1)

help ensure that the TPA3220 can be placed in reset easily, as needed, or automatically if there is a

power supply issue.

SLAU756–January 2018

Submit Documentation Feedback

Figure 5. Filter Frequency Response

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

11

Page 12

ADVANCE INFORMATION

Hardware Configuration

3.8 Analog-Input-Board Connector (J3)

The Analog-Input-Board (AIB) connector allows for cross compatibility with several Analog Plug-in

Modules (APMs) offered by TI. This generic connector provides access to common board connections

such as analog input, analog output, Fault and overtemperature warning (OTW) error reporting, common

board voltages (12 V, 3.3 V, and so forth), and EVM reset. These plug-in modules allow for an applicationspecific front end to be plugged into the TPA3220EVM-Micro with ease. Examples of plug-in modules

include front ends for guitar amplifier, karaoke, wireless sub-woofer, and front-end audio crossover.

Table 11 provides the details for the AIB connector pinouts.

Table 11. AIB Connector (J3) Pinout

Pin # Function Description Audio EVM

1 Amp Out A Speaker-level output from audio class-D EVM (SE or one side of BTL) O

2 Amp Out B Speaker-level output from audio class-D EVM (SE or one side of BTL) O

3 PVDD PVDD voltage supply from audio Class-D EVM (variable voltage depending on

Class-D EVM use)

4 GND Ground reference between audio plug-in module and audio class-D EVM 5 NC - 6 NC - 7 3.3 V 3.3-V supply from EVM; used for powering Audio Plug-in Module O

8 3.3 V 3.3-V supply from EVM; used for powering Audio Plug-in Module O

9 12 V 12-V supply from EVM; used for powering Audio Plug-in Module O

10 EN and RESET Assert enable and reset control for audio class-D EVM (active low) I

11 Analog IN_A Analog audio Input A (analog in EVM), Data In I2S Bus (digital in EVM) I

12 NC - 13 Analog IN_B Analog audio Input B (analog in EVM), Data In I2S Bus (digital in EVM) I

14 CLIP_OTW Clipping detection, overtemperature warning, or both from audio class-D EVM

(active low)

15 Analog IN_C Analog audio Input C (analog in EVM), Data In I2S Bus (digital in EVM) I

16 FAULT Fault detection from audio Class-D EVM (Active Low) O

17 Analog IN_D Analog audio Input D (analog in EVM), Data In I2S Bus (digital in EVM) I

18 NC - 19 NC - 20 NC - 21 GND Ground reference between audio plug-in module and audio class-D EVM 22 GND Ground reference between audio plug-in module and audio class-D EVM 23 NC - 24 NC - 25 NC - 26 NC - 27 Amp Out C Speaker-level output from audio class-D EVM (SE or one side of BTL) O

28 Amp Out D Speaker-level output from audio class-D EVM (SE or one side of BTL) O

www.ti.com

Input/Output

O

O

12

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 13

ADVANCE INFORMATION

www.ti.com

4 EVM Design Documents

This section contains the EVM board layouts, schematics, and bill of materials (BOM).

4.1 TPA3220EVM-Micro Board Layouts

Figure 6 and Figure 7 illustrate the EVM board layouts.

EVM Design Documents

Figure 6. TPA3220EVM-Micro Top Composite Assembly

Figure 7. TPA3220EVM-Micro Bottom Composite Assembly

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

13

Page 14

ADVANCE INFORMATION

EVM Design Documents

4.2 TPA3220EVM-Micro Board Layouts

Figure 8 shows the EVM board dimensions.

www.ti.com

Image shown is not actual scale.

Figure 8. TPA3220EVM-Micro Board Dimensions

14

TPA3220 Evaluation Module Micro

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 15

IN1P

IN2P

AUDIO

BOARD

IN2+_AIB

IN1-_AIB

IN1+_AIB

FROM DUT

OTW_CLIP

FAULT

GND

ALIGNMENT

HEADER

AIB

RESET-SW

RESET

INTERFACE

RST-AIB

3.3V

GND GND

PVDD

TO DUT

TO DUT

1

3

56

4

2

7

910

8

12 11

14 13

16 15

18 17

20 19

22 21

24 23

26 25

28 27

J3

3.3V

IN2+_HPJ

IN1+_HPJ

3

2

1

J1

SJ-3523-SMT

GND

GND

IN2M

TO DUT

GND

IN1M

TO DUT

GND

IN2-_AIB

3.3V

5V

1

2

J2

1.00k

R6

0R4

DNP

10.0k

R10

100k

R7

100k

R8

0

R3

0

R13

0R5

0R9

0R1

DNP

0R2

DNP

0R11

DNP

0R12

DNP

1uF

C1

1uF

C2

1uF

C3

1uF

C4

Copyright © 2018, Texas Instruments IncorporatedCopyright © 2018, Texas Instruments Incorporated

ADVANCE INFORMATION

www.ti.com

5 Schematic and Bill of Materials

This section contains the EVM schematic images and the BOM.

5.1 Schematic

Figure 9 and Figure 10 illustrate the EVM schematics.

Schematic and Bill of Materials

Figure 9. TPA3220EVM-MICRO Schematic 1

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

15

Page 16

GNDGND GND

GND

VCC

9

SS

7

SW

1

FB

6

RTN

5

VIN

10

BST

2

RON/SD

8

DAP

11

ISEN

3

SGND

4

U2

LM5010ASD/NOPB

PVDD

5V

GND

GND

GND

GND

3.3V

OUTPUT

2

GND

1

IN

3

OUTPUT

4

U3

TLV1117-33IDCY

GND

5V

PVDD

1

2

J6

GND GND

GND

Green

D2

5V

5V

GND

PVDD

GND

PVDD

GNDGND

GNDGND

RESET

GND

GVDD

GND

IN1_P

IN1_M

IN2_M

IN2_P

VDD

GVDD

GND

GND

6

4

5

13

S1

RESET

GND

RESET-SW RESET

TO AIB

RESET-SW

AVDD

GND

HEAD

GAIN/SLV

VDD

AVDD

GAIN/SLV

GND

MSTR-30dB

AVDD

PVDD

GVDD

5V

5V

5V

IN1P

IN1M

IN2P

IN2M

FROM ANALOG

IN1_P

IN1_M

IN2_P

IN2_M

FRONT END

GND

GND

GND

GND

GND

GND

5V

5V

GND

VDD

1

CMUTE

17

IN1_P

8

IN1_M

9

FREQ_ADJ

14

OSCM

12

OSCP

13

GND

5

GND

6

AVDD

21

HEAD

11

IN2_P

15

IN2_M

16

RESET

10

FAULT

4

GAIN/SLV

2

OTW_CLIP

3

GVDD

22

BST1_P

44

BST1_M

43

BST2_M

23

BST2_P

24

GND

42

GND

41

GND

25

GND

26

GND

34

GND

33

OUT1_P

40

OUT1_P

39

OUT1_M

35

OUT2_P

32

OUT2_M

27

OUT2_M

28

PVDD

38

PVDD

37

PVDD

36

PVDD

31

PVDD

30

PVDD

29

GND

18

GND

19

GND

20

GND

7

GND

45

TPA3220DDWR

U1

GND

GND

OUT2_M

OUT1_P

OUT1_M

FAULT

OTW_CLIP

OUT2_P

FREQ_ADJ

5V

Orange

D3

CLIP_OTW

MONITORS

FAULT

TO AIB

OTW_CLIP

FAULT

Red

D1

FAULT

CLIP_OTW

5V

OUT2_M

OUT2_P

1

2

J5

GND GND

OUT1+

OUT1_P

OUT1_M

OUT1-

1

2

J4

GND GND

21

4 3

7µH

L1

21

4 3

7µH

L3

1000µF

C12

1000µF

C7

0.68µF

C17

0.68µF

C18

0.68µF

C24

0.68µF

C25

100µH

L4

OUT2+

OUT2-

100uF

C33

0R36

DNP

0R37

DNP

100pF

C23

100pF

C22

100pF

C15

100pF

C9

0.1uF

C13

0.1uF

C8

0.1uF

C19

0.033uFC14

0.033uFC16

0.033uFC20

0.033uFC21

0.047uF

C28

50V

1uF

C5

50V

1uF

C6

50V

1uF

C10

50V

1uF

C11

0.1uF

C38

50V

50V

1uF

C37

0.033uF

C26

D4

3A

0.1uF

C30

0R18

0R16

DNP

0R14

10uH

L2

5600pF

C31

D5

1A

47.0k

R27

50V

2.2uF

C29

50V

10uF

C35

50V

10uF

C36

10uF

C32

100

R24

100

R21

100

R17

100

R15

0

R29

DNP

0

R26

DNP

0

R23

DNP

0

R22

DNP

0

R20

DNP

47.0k

R32

1.00k

R38

1.00k

R39

499

R33

3.32

R19

820

R30

820

R34

10.0k

R25

0.47uF

C27

0.022uF

C34

0

R40

DNP

GND

39.0k

R31

100k

R28

121k

R35

Copyright © 2018, Texas Instruments Incorporated

ADVANCE INFORMATION

Schematic and Bill of Materials

16

TPA3220 Evaluation Module Micro

www.ti.com

Figure 10. TPA3220EVM-MICRO Schematic 2

Copyright © 2018, Texas Instruments Incorporated

SLAU756–January 2018

Submit Documentation Feedback

Page 17

ADVANCE INFORMATION

www.ti.com

Schematic and Bill of Materials

5.2 Bill of Materials

Table 12 displays the EVM BOM.

Table 12. Bill of Materials

Designator Qty Value Description Package Reference Part Number Manufacturer

!PCB1 1 Printed Circuit Board AMPS037 Any

C1, C2, C3, C4 4 1uF CAP, CERM, 1 uF, 16 V, ±10%, X7R, 0603 0603 EMK107B7105KA-T Taiyo Yuden

C5, C6, C10, C11, C37 5 1uF CAP, CERM, 1 uF, 50 V, ± 10%, X7R, 0603 0603 UMK107AB7105KA-T Taiyo Yuden

C7, C12 2 1000uF CAP, AL, 1000 µF, 50 V, ±20%, TH D13xL25mm 860010678024 Wurth Elektronik

C8, C13, C19, C30, C38 5 0.1uF CAP, CERM, 0.1 uF, 50 V, ±10%, X7R, 0603 0603 C0603C104K5RACTU Kemet

C9, C15, C22, C23 4 100pF CAP, CERM, 100 pF, 50 V, ±5%, C0G/NP0, 0603 0603 GRM1885C1H101JA01D Murata

C14, C16, C20, C21, C26 5 0.033uF CAP, CERM, 0.033 uF, 25 V, ±10%, X7R, 0603 0603 GRM188R71E333KA01D Murata

C17, C18, C24, C25 4 0.68uF CAP, Film, 0.68 µF, 40 VAC/63 VDC,±10%, AEC-Q200 Grade 1, 2220

SMD

C27 1 0.47uF CAP, CERM, 0.47 uF, 25 V, ±10%, X5R, 0603 0603 GRM188R61E474KA12D Murata

C28 1 0.047uF CAP, CERM, 0.047 uF, 25 V, ±10%, X7R, 0402 0402 GRM155R71E473KA88D Murata

C29 1 2.2uF CAP, CERM, 2.2 uF, 50 V, ±10%, X5R, 0603 0603 GRM188R61H225KE11D Murata

C31 1 5600pF CAP, CERM, 5600 pF, 50 V, ±10%, X7R, 0603 0603 GRM188R71H562KA01D Murata

C32 1 10uF CAP, CERM, 10 uF, 16 V, ±20%, X5R, 0603 0603 GRM188R61C106MAALD Murata

C33 1 100uF CAP, CERM, 100 uF, 6.3 V, ±20%, X5R, 1206 1206 GRM31CR60J107ME39L Murata

C34 1 0.022uF CAP, CERM, 0.022 uF, 50 V, ±10%, X7R, 0603 0603 C0603C223K5RACTU Kemet

C35, C36 2 10uF CAP, CERM, 10 uF, 50 V, ±10%, X5R, 1206 1206 GRM31CR61H106KA12L Murata

D1 1 Red LED, Red, SMD Red 0805 LED LTST-C170KRKT Lite-On

D2 1 Green LED, Green, SMD LED_0805 LTST-C171GKT Lite-On

D3 1 Orange LED, Orange, SMD LED_0805 LTST-C170KFKT Lite-On

D4 1 100V Diode,Schottky, 100 V, 3 A, SMA SMA SK310A-TP Micro Commercial

D5 1 100V Diode,Schottky, 100 V, 1 A, SMA SMA B1100-13-F Diodes Inc.

H1, H2, H3, H4 4 Bumpon, Hemisphere, 0.44 X 0.20, Clear Transparent Bumpon SJ-5303 (CLEAR) 3M

J1 1 Audio Jack, 3.5mm, Stereo, R/A, SMT Audio Jack SMD SJ-3523-SMT CUI Inc.

J2 1 Header, 100mil, 2x1, Gold, TH Sullins 100mil, 1x2, 230 mil

J3 1 Receptacle, 100mil, 14x2, Gold, TH 14x2 Receptacle SSW-114-01-G-D Samtec

J4, J5, J6 3 Terminal Block, 2x1, 5mm, Green, TH Terminal Block, 2x1, 5mm, TH 1935776 Phoenix Contact

L1, L3 2 7uH Inductor, Shielded, Ferrite, 7 µH, 6.5 A, .0066 ohm, AEC-Q200 Grade 1,

SMD

L2 1 10uH Inductor, Wirewound, 10 uH, 0.08 A, 0.36 ohm, SMD 0603 GLFR1608T100M-LR TDK

L4 1 100uH Inductor, Shielded, Ferrite, 100 µH, 0.9 A, 0.611 ohm, SMD 6x6m VLS6045EX-101M TDK

R3, R5, R9, R13 4 0 RES, 0, 5%, 0.1 W, 0603 0603 ERJ-3GEY0R00V Panasonic

R6 1 1.00k RES, 1.00 k, 1%, 0.1 W, 0402 0402 ERJ-2RKF1001X Panasonic

2220 LDEDD3680KA5N00 Kemet

Components

above insulator

15.5x14mm UA8013-ALD Coilcraft

PBC02SAAN Sullins Connector

Solutions

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

TPA3220 Evaluation Module Micro

17

Page 18

ADVANCE INFORMATION

Schematic and Bill of Materials

www.ti.com

Table 12. Bill of Materials (continued)

Designator Qty Value Description Package Reference Part Number Manufacturer

R7, R8 2 100k RES, 100 k, 1%, 0.0625 W, 0402 0402 RC0402FR-07100KL Yageo America

R10 1 10.0k RES, 10.0 k, 1%, 0.1 W, 0402 0402 ERJ-2RKF1002X Panasonic

R14, R18 2 0 RES, 0, 5%, 0.125 W, 0805 0805 ERJ-6GEY0R00V Panasonic

R15, R17, R21, R24 4 100 RES, 100, 1%, 0.1 W, 0603 0603 RC0603FR-07100RL Yageo America

R19 1 3.32 RES, 3.32, 1%, 0.1 W, 0603 0603 RC0603FR-073R32L Yageo America

R25 1 10.0k RES, 10.0 k, 1%, 0.1 W, 0603 0603 ERJ-3EKF1002V Panasonic

R27, 1 47.0k RES, 47.0 k, 1%, 0.1 W, 0603 0603 RC0603FR-0747KL Yageo America

R28 1 100k RES, 100 k, 0.5%, 0.1 W, 0603 0603 RT0603DRE07100KL Yageo America

R30, R34 2 820 RES, 820, 1%, 0.063 W, 0402 0402 RC0402FR-07820RL Yageo America

R31 1 39.0k RES, 39.0 k, 1%, 0.1 W, 0603 603 RC0603FR-0739KL Yageo America

R32 1 47.0k RES, 47.0 k, 1%, 0.0625 W, 0402 0402 RC0402FR-0747KL Yageo America

R33 1 499 RES, 499, 0.1%, 0.063 W, AEC-Q200 Grade 0, 0402 0402 ERA-2AEB4990X Panasonic

R35 1 121k RES, 121 k, 1%, 0.125 W, 0805 0805 ERJ-6ENF1213V Panasonic

R38, R39 2 1.00k RES, 1.00 k, 1%, 0.1 W, 0603 0603 RC0603FR-071KL Yageo America

S1 1 Switch, SPDT, On-On, 2 Pos, TH Switch, 7x4.5mm 200USP1T1A1M2RE E-Switch

U1 1 35-W Stereo, 100-W Peak HD-Audio, Analog-Input, Class-D Amplifier,

U2 1 High Voltage 1A Step Down Switching Regulator, 10-pin LLP, Pb-Free SDC10A LM5010ASD/NOPB Texas Instruments

U3 1 FIXED LOW-DROPOUT VOLTAGE REGULATOR, DCY0004A DCY0004A TLV1117-33IDCY Texas Instruments

FID1, FID2, FID3 0 Fiducial mark. There is nothing to buy or mount. N/A N/A N/A

R1, R2, R11, R12, R36,

R37

R4, R16 0 0 RES, 0, 5%, 0.125 W, 0805 0805 ERJ-6GEY0R00V Panasonic

R20, R22, R23, R26, R29 0 0 RES, 0, 5%, 0.1 W, 0603 0603 ERJ-3GEY0R00V Panasonic

R40 0 0 RES, 0, 5%, 0.063 W, 0402 0402 RC0402JR-070RL Yageo America

0 0 RES, 0, 5%, 0.1 W, 0603 0603 RC0603JR-070RL Yageo America

DDW0044D (TSSOP-44)

DDW0044D TPA3220DDWR Texas Instruments

18

TPA3220 Evaluation Module Micro

SLAU756–January 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Page 19

STANDARD TERMS FOR EVALUATION MODULES

1. Delivery: TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, and/or

documentation which may be provided together or separately (collectively, an “EVM” or “EVMs”) to the User (“User”) in accordance

with the terms set forth herein. User's acceptance of the EVM is expressly subject to the following terms.

1.1 EVMs are intended solely for product or software developers for use in a research and development setting to facilitate feasibility

evaluation, experimentation, or scientific analysis of TI semiconductors products. EVMs have no direct function and are not

finished products. EVMs shall not be directly or indirectly assembled as a part or subassembly in any finished product. For

clarification, any software or software tools provided with the EVM (“Software”) shall not be subject to the terms and conditions

set forth herein but rather shall be subject to the applicable terms that accompany such Software

1.2 EVMs are not intended for consumer or household use. EVMs may not be sold, sublicensed, leased, rented, loaned, assigned,

or otherwise distributed for commercial purposes by Users, in whole or in part, or used in any finished product or production

system.

2 Limited Warranty and Related Remedies/Disclaimers:

2.1 These terms do not apply to Software. The warranty, if any, for Software is covered in the applicable Software License

Agreement.

2.2 TI warrants that the TI EVM will conform to TI's published specifications for ninety (90) days after the date TI delivers such EVM

to User. Notwithstanding the foregoing, TI shall not be liable for a nonconforming EVM if (a) the nonconformity was caused by

neglect, misuse or mistreatment by an entity other than TI, including improper installation or testing, or for any EVMs that have

been altered or modified in any way by an entity other than TI, (b) the nonconformity resulted from User's design, specifications

or instructions for such EVMs or improper system design, or (c) User has not paid on time. Testing and other quality control

techniques are used to the extent TI deems necessary. TI does not test all parameters of each EVM.

User's claims against TI under this Section 2 are void if User fails to notify TI of any apparent defects in the EVMs within ten (10)

business days after delivery, or of any hidden defects with ten (10) business days after the defect has been detected.

2.3 TI's sole liability shall be at its option to repair or replace EVMs that fail to conform to the warranty set forth above, or credit

User's account for such EVM. TI's liability under this warranty shall be limited to EVMs that are returned during the warranty

period to the address designated by TI and that are determined by TI not to conform to such warranty. If TI elects to repair or

replace such EVM, TI shall have a reasonable time to repair such EVM or provide replacements. Repaired EVMs shall be

warranted for the remainder of the original warranty period. Replaced EVMs shall be warranted for a new full ninety (90) day

warranty period.

3 Regulatory Notices:

3.1 United States

3.1.1 Notice applicable to EVMs not FCC-Approved:

FCC NOTICE: This kit is designed to allow product developers to evaluate electronic components, circuitry, or software

associated with the kit to determine whether to incorporate such items in a finished product and software developers to write

software applications for use with the end product. This kit is not a finished product and when assembled may not be resold or

otherwise marketed unless all required FCC equipment authorizations are first obtained. Operation is subject to the condition

that this product not cause harmful interference to licensed radio stations and that this product accept harmful interference.

Unless the assembled kit is designed to operate under part 15, part 18 or part 95 of this chapter, the operator of the kit must

operate under the authority of an FCC license holder or must secure an experimental authorization under part 5 of this chapter.

3.1.2 For EVMs annotated as FCC – FEDERAL COMMUNICATIONS COMMISSION Part 15 Compliant:

CAUTION

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not

cause harmful interference, and (2) this device must accept any interference received, including interference that may cause

undesired operation.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to

operate the equipment.

FCC Interference Statement for Class A EVM devices

NOTE: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of

the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is

operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not

installed and used in accordance with the instruction manual, may cause harmful interference to radio communications.

Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to

correct the interference at his own expense.

Page 20

FCC Interference Statement for Class B EVM devices

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of

the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential

installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance

with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference

will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which

can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more

of the following measures:

• Reorient or relocate the receiving antenna.

• Increase the separation between the equipment and receiver.

• Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

• Consult the dealer or an experienced radio/TV technician for help.

3.2 Canada

3.2.1 For EVMs issued with an Industry Canada Certificate of Conformance to RSS-210 or RSS-247

Concerning EVMs Including Radio Transmitters:

This device complies with Industry Canada license-exempt RSSs. Operation is subject to the following two conditions:

(1) this device may not cause interference, and (2) this device must accept any interference, including interference that may

cause undesired operation of the device.

Concernant les EVMs avec appareils radio:

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation

est autorisée aux deux conditions suivantes: (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit

accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Concerning EVMs Including Detachable Antennas:

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser)

gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type

and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for

successful communication. This radio transmitter has been approved by Industry Canada to operate with the antenna types

listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated.

Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited

for use with this device.

Concernant les EVMs avec antennes détachables

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et

d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage

radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope

rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante. Le

présent émetteur radio a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés dans le

manuel d’usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne

non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de

l'émetteur

3.3 Japan

3.3.1 Notice for EVMs delivered in Japan: Please see http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_01.page 日本国内に

輸入される評価用キット、ボードについては、次のところをご覧ください。

http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_01.page

3.3.2 Notice for Users of EVMs Considered “Radio Frequency Products” in Japan: EVMs entering Japan may not be certified

by TI as conforming to Technical Regulations of Radio Law of Japan.

If User uses EVMs in Japan, not certified to Technical Regulations of Radio Law of Japan, User is required to follow the

instructions set forth by Radio Law of Japan, which includes, but is not limited to, the instructions below with respect to EVMs

(which for the avoidance of doubt are stated strictly for convenience and should be verified by User):

1. Use EVMs in a shielded room or any other test facility as defined in the notification #173 issued by Ministry of Internal

Affairs and Communications on March 28, 2006, based on Sub-section 1.1 of Article 6 of the Ministry’s Rule for

Enforcement of Radio Law of Japan,

2. Use EVMs only after User obtains the license of Test Radio Station as provided in Radio Law of Japan with respect to

EVMs, or

3. Use of EVMs only after User obtains the Technical Regulations Conformity Certification as provided in Radio Law of Japan

with respect to EVMs. Also, do not transfer EVMs, unless User gives the same notice above to the transferee. Please note

that if User does not follow the instructions above, User will be subject to penalties of Radio Law of Japan.

Page 21

【無線電波を送信する製品の開発キットをお使いになる際の注意事項】 開発キットの中には技術基準適合証明を受けて

いないものがあります。 技術適合証明を受けていないもののご使用に際しては、電波法遵守のため、以下のいずれかの

措置を取っていただく必要がありますのでご注意ください。

1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用

いただく。

2. 実験局の免許を取得後ご使用いただく。

3. 技術基準適合証明を取得後ご使用いただく。

なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします。

上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。 日本テキサス・イ

ンスツルメンツ株式会社

東京都新宿区西新宿6丁目24番1号

西新宿三井ビル

3.3.3 Notice for EVMs for Power Line Communication: Please see http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page

電力線搬送波通信についての開発キットをお使いになる際の注意事項については、次のところをご覧ください。http:/

/www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page

3.4 European Union

3.4.1 For EVMs subject to EU Directive 2014/30/EU (Electromagnetic Compatibility Directive):

This is a class A product intended for use in environments other than domestic environments that are connected to a

low-voltage power-supply network that supplies buildings used for domestic purposes. In a domestic environment this

product may cause radio interference in which case the user may be required to take adequate measures.

4 EVM Use Restrictions and Warnings:

4.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT

LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS.

4.2 User must read and apply the user guide and other available documentation provided by TI regarding the EVM prior to handling

or using the EVM, including without limitation any warning or restriction notices. The notices contain important safety information

related to, for example, temperatures and voltages.

4.3 Safety-Related Warnings and Restrictions:

4.3.1 User shall operate the EVM within TI’s recommended specifications and environmental considerations stated in the user

guide, other available documentation provided by TI, and any other applicable requirements and employ reasonable and

customary safeguards. Exceeding the specified performance ratings and specifications (including but not limited to input

and output voltage, current, power, and environmental ranges) for the EVM may cause personal injury or death, or

property damage. If there are questions concerning performance ratings and specifications, User should contact a TI

field representative prior to connecting interface electronics including input power and intended loads. Any loads applied

outside of the specified output range may also result in unintended and/or inaccurate operation and/or possible

permanent damage to the EVM and/or interface electronics. Please consult the EVM user guide prior to connecting any

load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, even with the inputs and outputs kept within the specified allowable ranges, some circuit

components may have elevated case temperatures. These components include but are not limited to linear regulators,

switching transistors, pass transistors, current sense resistors, and heat sinks, which can be identified using the

information in the associated documentation. When working with the EVM, please be aware that the EVM may become

very warm.

4.3.2 EVMs are intended solely for use by technically qualified, professional electronics experts who are familiar with the

dangers and application risks associated with handling electrical mechanical components, systems, and subsystems.

User assumes all responsibility and liability for proper and safe handling and use of the EVM by User or its employees,

affiliates, contractors or designees. User assumes all responsibility and liability to ensure that any interfaces (electronic

and/or mechanical) between the EVM and any human body are designed with suitable isolation and means to safely

limit accessible leakage currents to minimize the risk of electrical shock hazard. User assumes all responsibility and

liability for any improper or unsafe handling or use of the EVM by User or its employees, affiliates, contractors or

designees.

4.4 User assumes all responsibility and liability to determine whether the EVM is subject to any applicable international, federal,

state, or local laws and regulations related to User’s handling and use of the EVM and, if applicable, User assumes all

responsibility and liability for compliance in all respects with such laws and regulations. User assumes all responsibility and

liability for proper disposal and recycling of the EVM consistent with all applicable international, federal, state, and local

requirements.

5. Accuracy of Information: To the extent TI provides information on the availability and function of EVMs, TI attempts to be as accurate

as possible. However, TI does not warrant the accuracy of EVM descriptions, EVM availability or other information on its websites as

accurate, complete, reliable, current, or error-free.

Page 22

6. Disclaimers:

6.1 EXCEPT AS SET FORTH ABOVE, EVMS AND ANY MATERIALS PROVIDED WITH THE EVM (INCLUDING, BUT NOT

LIMITED TO, REFERENCE DESIGNS AND THE DESIGN OF THE EVM ITSELF) ARE PROVIDED "AS IS" AND "WITH ALL

FAULTS." TI DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, REGARDING SUCH ITEMS, INCLUDING BUT

NOT LIMITED TO ANY EPIDEMIC FAILURE WARRANTY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS

FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE

SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

6.2 EXCEPT FOR THE LIMITED RIGHT TO USE THE EVM SET FORTH HEREIN, NOTHING IN THESE TERMS SHALL BE

CONSTRUED AS GRANTING OR CONFERRING ANY RIGHTS BY LICENSE, PATENT, OR ANY OTHER INDUSTRIAL OR

INTELLECTUAL PROPERTY RIGHT OF TI, ITS SUPPLIERS/LICENSORS OR ANY OTHER THIRD PARTY, TO USE THE

EVM IN ANY FINISHED END-USER OR READY-TO-USE FINAL PRODUCT, OR FOR ANY INVENTION, DISCOVERY OR

IMPROVEMENT, REGARDLESS OF WHEN MADE, CONCEIVED OR ACQUIRED.

7. USER'S INDEMNITY OBLIGATIONS AND REPRESENTATIONS. USER WILL DEFEND, INDEMNIFY AND HOLD TI, ITS

LICENSORS AND THEIR REPRESENTATIVES HARMLESS FROM AND AGAINST ANY AND ALL CLAIMS, DAMAGES, LOSSES,

EXPENSES, COSTS AND LIABILITIES (COLLECTIVELY, "CLAIMS") ARISING OUT OF OR IN CONNECTION WITH ANY

HANDLING OR USE OF THE EVM THAT IS NOT IN ACCORDANCE WITH THESE TERMS. THIS OBLIGATION SHALL APPLY

WHETHER CLAIMS ARISE UNDER STATUTE, REGULATION, OR THE LAW OF TORT, CONTRACT OR ANY OTHER LEGAL

THEORY, AND EVEN IF THE EVM FAILS TO PERFORM AS DESCRIBED OR EXPECTED.

8. Limitations on Damages and Liability:

8.1 General Limitations. IN NO EVENT SHALL TI BE LIABLE FOR ANY SPECIAL, COLLATERAL, INDIRECT, PUNITIVE,

INCIDENTAL, CONSEQUENTIAL, OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THESE

TERMS OR THE USE OF THE EVMS , REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF

SUCH DAMAGES. EXCLUDED DAMAGES INCLUDE, BUT ARE NOT LIMITED TO, COST OF REMOVAL OR

REINSTALLATION, ANCILLARY COSTS TO THE PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, RETESTING,

OUTSIDE COMPUTER TIME, LABOR COSTS, LOSS OF GOODWILL, LOSS OF PROFITS, LOSS OF SAVINGS, LOSS OF

USE, LOSS OF DATA, OR BUSINESS INTERRUPTION. NO CLAIM, SUIT OR ACTION SHALL BE BROUGHT AGAINST TI

MORE THAN TWELVE (12) MONTHS AFTER THE EVENT THAT GAVE RISE TO THE CAUSE OF ACTION HAS

OCCURRED.

8.2 Specific Limitations. IN NO EVENT SHALL TI'S AGGREGATE LIABILITY FROM ANY USE OF AN EVM PROVIDED

HEREUNDER, INCLUDING FROM ANY WARRANTY, INDEMITY OR OTHER OBLIGATION ARISING OUT OF OR IN

CONNECTION WITH THESE TERMS, , EXCEED THE TOTAL AMOUNT PAID TO TI BY USER FOR THE PARTICULAR

EVM(S) AT ISSUE DURING THE PRIOR TWELVE (12) MONTHS WITH RESPECT TO WHICH LOSSES OR DAMAGES ARE

CLAIMED. THE EXISTENCE OF MORE THAN ONE CLAIM SHALL NOT ENLARGE OR EXTEND THIS LIMIT.

9. Return Policy. Except as otherwise provided, TI does not offer any refunds, returns, or exchanges. Furthermore, no return of EVM(s)

will be accepted if the package has been opened and no return of the EVM(s) will be accepted if they are damaged or otherwise not in

a resalable condition. If User feels it has been incorrectly charged for the EVM(s) it ordered or that delivery violates the applicable

order, User should contact TI. All refunds will be made in full within thirty (30) working days from the return of the components(s),

excluding any postage or packaging costs.

10. Governing Law: These terms and conditions shall be governed by and interpreted in accordance with the laws of the State of Texas,

without reference to conflict-of-laws principles. User agrees that non-exclusive jurisdiction for any dispute arising out of or relating to

these terms and conditions lies within courts located in the State of Texas and consents to venue in Dallas County, Texas.

Notwithstanding the foregoing, any judgment may be enforced in any United States or foreign court, and TI may seek injunctive relief

in any United States or foreign court.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2018, Texas Instruments Incorporated

Page 23

IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated (‘TI”) technical, application or other design advice, services or information, including, but not limited to,

reference designs and materials relating to evaluation modules, (collectively, “TI Resources”) are intended to assist designers who are

developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you

(individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of

this Notice.

TI’s provision of TI Resources does not expand or otherwise alter TI’s applicable published warranties or warranty disclaimers for TI

products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections,

enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your

applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications

(and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You

represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1)

anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that

might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you

will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any

testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include

the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO

ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY

RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or

endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED “AS IS” AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR

REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO

ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL

PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT

LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF

DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL,

COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR

ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services.

These include; without limitation, TI’s standard terms for semiconductor products http://www.ti.com/sc/docs/stdterms.htm), evaluation

modules, and samples (http://www.ti.com/sc/docs/sampterms.htm).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2018, Texas Instruments Incorporated

Page 24

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Texas Instruments:

TPA3220EVM-MICRO

Loading...

Loading...