Page 1

ThunderLAN

TNETE100A, TNETE110A, TNETE211

Programmer’s

Guide

October 1996 Network Business Products

Page 2

Printed in U.S.A., October 1996

L411001–9761 revisionA

SPWU013A

Page 3

Page 4

ThunderLAN

t

Programmer’s Guide

TNETE100A, TNETE1 10A, TNETE211

Manufacturing Part Number: L411001-9761 revision A

Literature Number: SPWU013A

October 1996

Page 5

Running Title—Attribute Reference

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

IMPORTANT NOTICE

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1996, Texas Instruments Incorporated

ii

Page 6

About This Manual

The

implementations of ThunderLAN networking hardware:

-

-

-

How to Use This Manual

The goal of this book is to assist you in the development of drivers for the

ThunderLAN controllers. This document contains the following chapters:

-

Preface

Read This First

ThunderLAN Programmer’s Guide

TNETE100A Ethernett controller

TNETE110A Ethernet controller

TNETE211 100 VG-AnyLAN physical media interface (PMI)

Chapter 1, ThunderLAN Overview, describes some Texas

Instruments-specific hardware features. These include the enhanced

media independent interface (MII), which passes interrupts from an

attached physical interface (PHY) to the host.

assists you in using the following

-

Chapter 2, ThunderLAN Registers, shows how to access the various

ThunderLAN registers and how to use these registers to access external

devices attached to ThunderLAN.

-

Chapter 3, Initializing and Resetting, discusses how to initialize and reset

the controller and the attached PHYs.

-

Chapter 4, Interrupt Handling, describes what happens when interrupts

occur and how to correct failure conditions.

-

Chapter 5, List Structures, describes how to pass data to ThunderLAN

using a system of linked list structures.

-

Chapter 6, Transmitting and Receiving Frames, explains the format and

procedure for transmitting and receiving, as well as the linked list structure

required.

-

Chapter 7, Physical Interface, discusses the features of ThunderLAN

which support IEEE 802.3- and 802.12-compliant devices.

iii

Page 7

Notational Conventions

Notational Conventions

This document uses the following conventions:

-

-

Related Documentation

Information Technology Local and Metropolitan Area Networks–Part 12:

MAC Parameters, Physical Layer, Medium Attachment Units and

PCI Local Bus Specification, Revision 2.0

ThunderLAN Adaptive Performance Optimization Technical Brief

XL24C02 Data Sheet,

Program listings, program examples, and interactive displays are shown

in a special font. Examples use a bold version of the special font for

emphasis. Here is a sample program listing:

11 0005 0001 .field 1, 2

12 0005 0003 .field 3, 4

13 0005 0006 .field 6, 3

14 0006 .even

A lower case ‘x’ in a number indicates that position can be anything (don’t

care). Here are some examples:

J

0x00

J

0x0004

J

0x4000501

Demand-Priority Access Method, Physical Layer and Repeater

Specifications for 100-Mb/s Operation,

Draft 8.0 of the Revision

Marked for Technical changes of IEEE Standard 802.12.

Repeater for 100-Mb/s Operation,

Draft 5.0 of the Supplement to 1993

version of ANSI/IEEE Std. 802.3: Carrier Sense Multiple Access with

Collision Detection (CSMA/CD) Access Method & Physical Layer

Specifications.

is the specification which

ThunderLAN is designed to meet. T o obtain copies, contact PCI Special

Interest Group, P .O. Box 14070, Portland, OR 97214, 1–800–433–5177.

(Texas

Instruments literature number SPWT089) discusses specific buffering

and pacing techniques for improving adapter performance by adjusting

the resources and transmit procedures to achieve optimal transmission

rate and minimal CPU use.

EXEL Microelectronics, 1993, which contains the

device specifications for the XL24C02 2M-bit electrically erasable

EPROM.

iv

Page 8

If Y ou Need Assistance / Trademarks

If You Need Assistance. . .

-

World-Wide Web Sites

TI Online http://www.ti.com

Semiconductor PIC http://www.ti.com/sc/docs/pic/home.htm

Networking Home Page http://www.ti.com/sc/docs/network/nbuhomex.htm

-

North America, South America, Central America

Product Information Center (PIC) (972) 644-5580

TI Literature Response Center U.S.A. (800) 477-8924

Software Registration/Upgrades (214) 638-0333 Fax: (214) 638-7742

U.S.A. Factory Repair/Hardware Upgrades (713) 274-2285

U.S. Technical Training Organization (972) 644-5580

Networking Hotline Fax: (713) 274-4027

-

Europe, Middle East, Africa

European Product Information Center (EPIC) Hotlines:

Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32 Email: epic@ti.com

Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68

English +33 1 30 70 11 65

Francais +33 1 30 70 11 64

Italiano +33 1 30 70 11 67

EPIC Modem BBS +33 1 30 70 11 99

European Factory Repair +33 1 93 22 25 40

Europe Customer Training Helpline Fax: +49 81 61 80 40 10

-

Asia-Pacific

Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200

-

Japan

Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)

+03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813-3457-1259

-

Documentation

When making suggestions or reporting errors in documentation, please include the following information that is on the title

page: the full title of the book, the publication date, and the literature number.

Mail: Texas Instruments Incorporated Email: comments@books.sc.ti.com

Technical Documentation Services, MS 702

P.O. Box 1443

Houston, Texas 77251-1443

Note: When ordering documentation from a Literature Response Center, please specify the literature number of the

book.

Email:TLANHOT@micro.ti.com

Read This First

v

Page 9

Trademarks

Trademarks

Ethernet is a trademark of Xerox Corporation.

ThunderLAN and Adaptive Performance Optimization are trademarks of Texas Instruments

Incorporated.

vi

Page 10

Contents

Contents

1 ThunderLAN Overview 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 ThunderLAN Architecture 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Networking Protocols 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 PCI Interface 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1 PCI Cycles 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2 Byte Ordering 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 ThunderLAN Registers 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Register Addresses 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 PCI Configuration Space 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Host Registers 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Internal Registers 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 MII PHY Registers 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 External Devices 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 BIOS ROM 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 LEDs 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 EEPROM 2-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.4 ThunderLAN EEPROM Map 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Initializing and Resetting 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Initializing 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Finding the Network Interface Card (NIC) 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Finding the Controller in Memory and I/O Space 3-4. . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 Finding Which Interrupt was Assigned 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 Turning on the I/O Port and Memory Address Decode 3-6. . . . . . . . . . . . . . . . . . . .

3.1.5 Recovering the Silicon Revision Value 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.6 Setting the PCI Bus Latency Timer 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Resetting 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Hardware Reset 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Software Reset 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Interrupt Handling 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Loading and Unloading an Interrupt Service Routine (ISR) 4-2. . . . . . . . . . . . . . . . . . . . . . .

4.2 Prioritizing Adapter Interrupts 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Acknowledging Interrupts (Acking) 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Interrupt Type Codes 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

Page 11

Contents

4.4.1 No Interrupt (Invalid Code). Int_type = 000b 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Tx EOF Interrupt. Int_type = 001b 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 Statistics Overflow Interrupt. Int_type = 010b 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4 Rx EOF Interrupt. Int_type = 011b 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.5 Dummy Interrupt. Int_type = 100b 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.6 Tx EOC Interrupt. Int_type = 101b 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.7 Network Status Interrupt. Int_type = 110b and Int_Vec = 00h 4-9. . . . . . . . . . . . . .

4.4.8 Adapter Check Interrupt. Int_type = 110b and Int_Vec

≠ 00h 4-10. . . . . . . . . . . . .

4.4.9 Rx EOC Interrupt. Int_type = 111b 4-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 List Structures 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 List Management 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 CSTAT Field Bit Requirements 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 One-Fragment Mode 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Receive List Format 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Transmit List Format 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Transmitting and Receiving Frames 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Frame Format 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.1 Receive (Rx) Frame Format 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.2 Transmit (Tx) Frame Format 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 GO Command 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 Starting Frame Reception (Rx GO Command) 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.2 Starting Frame Transmission (Tx GO Command) 6-6. . . . . . . . . . . . . . . . . . . . . . . .

7 Physical Interface (PHY) 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 MII-Enhanced Interrupt Event Feature 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Nonmanaged MII Devices 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Bit-Rate Devices 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 PHY Initialization 7-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Register Definitions A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 PCI Configuration Registers A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.1 PCI Autoconfiguration from External 24C02 Serial EEPROM A-3. . . . . . . . . . . . . .

A.1.2 PCI Vendor ID Register (@ 00h) Default = 104Ch A-4. . . . . . . . . . . . . . . . . . . . . . .

A.1.3 PCI Device ID Register (@ 02h) Default = 0500h A-4. . . . . . . . . . . . . . . . . . . . . . . .

A.1.4 PCI Command Register (@ 04h) A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.5 PCI Status Register (@ 06h) A-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.6 PCI Base Class Register (@ 0Bh) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.7 PCI Subclass Register (@ 0Ah) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.8 PCI Program Interface Register (@ 09h) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.9 PCI Revision Register (@ 08h) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.10 PCI Cache Line Size Register (@ 0Ch) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.11 PCI Latency Timer Register (@ 0Dh) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.12 PCI I/O Base Address Register (@ 10h) A-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

Page 12

Contents

A.1.13 PCI Memory Base Address Register (@ 14h) A-8. . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.14 PCI BIOS ROM Base Address Register (@ 30h) A-8. . . . . . . . . . . . . . . . . . . . . . . .

A.1.15 PCI NVRAM Register (@ 34h) A-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.16 PCI Interrupt Line Register (@ 3Ch) A-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.17 PCI Interrupt Pin Register (@ 3Dh) A-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.18 PCI Min_Gnt (@ 3Eh) and Max_Lat (@ 3Fh) Registers A-10. . . . . . . . . . . . . . . . . .

A.1.19 PCI Reset Control Register (@ 40h) A-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1.20 CardBus CIS Pointer (@ 28h) A-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Adapter Host Registers A-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.1 Host Command Register–HOST_CMD @ Base_Address + 0 (Host) A-12. . . . . .

A.2.2 Channel Parameter Register–CH_PARM @ Base_Address + 4 (Host) A-17. . . .

A.2.3 Host Interrupt Register–HOST_INT @ Base_Address + 10 (Host) A-18. . . . . . . .

A.2.4 DIO Address Register–DIO_ADR @ Base_Address + 8 (Host) A-19. . . . . . . . . . .

RAM Addressing A-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.5 DIO Data Register–DIO_DATA @ Base_Address + 12 (Host) A-20. . . . . . . . . . . .

A.3 Adapter Internal Registers A-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.1 Network Command Register–NetCmd @ 0x00 (DIO) A-23. . . . . . . . . . . . . . . . . . .

A.3.2 Network Serial I/O Register–NetSio @ 0x00 (DIO) A-24. . . . . . . . . . . . . . . . . . . . .

A.3.3 Network Status Register–NetSts @ 0x00 (DIO) A-25. . . . . . . . . . . . . . . . . . . . . . . .

A.3.4 Network Status Mask Register–NetMask @ 0x00 (DIO) A-26. . . . . . . . . . . . . . . . .

A.3.5 Network Configuration Register–NetConfig @ 0x04 (DIO) A-27. . . . . . . . . . . . . . .

A.3.6 Manufacturing Test Register–ManTest @ 0x04 (DIO) A-29. . . . . . . . . . . . . . . . . . .

A.3.7 Default PCI Parameter Registers–@ 0x08–0x0C (DIO) A-29. . . . . . . . . . . . . . . . .

A.3.8 General Address Registers–Areg_0-3 @ 0x10–0x24 (DIO) A-30. . . . . . . . . . . . . .

A.3.9 Hash Address Registers–HASH1/HASH2 @ 0x28–0x2C (DIO) A-31. . . . . . . . . .

A.3.10 Network Statistics Registers–@ 0x30–0x40 (DIO) A-32. . . . . . . . . . . . . . . . . . . . . .

A.3.11 Adapter Commit Register–Acommit @ 0x40 (DIO) (Byte 3) A-34. . . . . . . . . . . . . .

A.3.12 LED Register–LEDreg @ 0x44 (DIO) (Byte 0) A-35. . . . . . . . . . . . . . . . . . . . . . . . .

A.3.13 Burst Size Register–BSIZEreg @ 0x44 (DIO) (Byte 1) A-36. . . . . . . . . . . . . . . . . .

A.3.14 Maximum Rx Frame Size Register–MaxRx @ 0x44 (DIO) (Bytes 2+3) A-37. . .

A.3.15 Interrupt Disable Register - INTDIS @ 0x48 (DIO) (BYTE 0) A-38. . . . . . . . . . . . .

A.4 10Base-T PHY Registers A-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4.1 PHY Generic Control Register–GEN_ctl @ 0x0 A-40. . . . . . . . . . . . . . . . . . . . . . . .

A.4.2 PHY Generic Status Register–GEN_sts @ 0x1 A-42. . . . . . . . . . . . . . . . . . . . . . . .

A.4.3 PHY Generic Identifier–GEN_id_hi/GEN_id_lo @ 0x2/0x3 A-44. . . . . . . . . . . . . . .

A.4.4 Autonegotiation Advertisement Register–AN_adv @ 0x4 A-45. . . . . . . . . . . . . . . .

A.4.5 Autonegotiation Link Partner Ability Register–AN_lpa @ 0x5 A-46. . . . . . . . . . . . .

A.4.6 Autonegotiation Expansion Register–AN_exp @ 0x6 A-47. . . . . . . . . . . . . . . . . . .

A.4.7 ThunderLAN PHY Identifier High/Low–TLPHY_id @ 0x10 A-48. . . . . . . . . . . . . . .

A.4.8 ThunderLAN PHY Control Register–TLPHY_ctl @ 0x11 A-49. . . . . . . . . . . . . . . . .

A.4.9 ThunderLAN PHY Status Register–TLPHY_sts @ 0x12 A-50. . . . . . . . . . . . . . . . .

Contents

ix

Page 13

Contents

B TNETE211 100VG-AnyLAN Demand Priority Physical Media Independent (PMI) Interface B-1

B.1 100VG-AnyLAN Training B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2 TNETE211 Register Descriptions B-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2.1 PHY Generic Control Register–GEN_ctl @ 0x0 B-7. . . . . . . . . . . . . . . . . . . . . . . . .

B.2.2 PHY Generic Status Register –GEN_sts @ 0x1 B-8. . . . . . . . . . . . . . . . . . . . . . . . .

B.2.3 PHY Generic Identifier–GEN_id_hi/GEN_id_lo @ 0x2/0x3 B-9. . . . . . . . . . . . . . . .

B.2.4 ThunderLAN PHY Identifier High/Low–TLPHY_id @ 0x10 B-9. . . . . . . . . . . . . . . .

B.2.5 ThunderLAN PHY Control Register–TLPHY_ctl @ 0x11 B-9. . . . . . . . . . . . . . . . . .

B.2.6 ThunderLAN PHY Status Register–TLPHY_sts @ 0x12 B-11. . . . . . . . . . . . . . . . .

C TNETE100PM/TNETE1 10PM C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 14

Figures

Figures

1–1 The ThunderLAN Controller 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 PCI Bus Byte Assignment 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 How ThunderLAN Registers are Addressed 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 The PCI Configuration Space Registers 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Configuration EEPROM Data Format 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Host Registers 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Internal Registers 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 MII PHY Registers 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Adapter Check Interrupt Fields 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 List Pointers and Buffers 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Linked List Management Technique 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Receive List Format – One_Frag = 0 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Receive List Format – One_Frag = 1 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Receive CSTAT Request Fields 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Receive CSTAT Complete Fields 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Transmit List Format 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Transmit CSTAT Request Fields 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Transmit CSTAT Complete Fields 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Token Ring Logical Frame Format (Rx) 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Ethernet Logical Frame Format (Rx) 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Token Ring Logical Frame Format (Tx) 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Ethernet Logical Frame Format (Tx) 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 100VG-AnyLAN Support Through ThunderLAN’s Enhanced 802.3u MII 7-2. . . . . . . . . . . . . .

7–2 MII Frame Format: Read 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 MII Frame Format: Write 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Assertion of Interrupt Waveform on the MDIO Line 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Waveform Showing Interrupt Between MII Frames 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 PCI Configuration Register Address Map A-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 Configuration EEPROM Data Format A-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–3 Host Interface Address Map A-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–4 ADAPTER Internal Register Map A-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–5 Default PCI Parameter Register A-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–6 Ethernet Error Counters A-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–7 Demand Priority Error Counters A-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–8 10Base-T PHY Registers A-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 802.12 Training Frame Format B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–2 Training Flowchart B-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 TNETE211 Registers B-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xi

Page 15

Tables

Tables

2–1 ThunderLAN EEPROM Map 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Adapter Check Bit Definitions 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Adapter Check Failure Codes 4-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Relevance of Error Status Bits for Adapter Check Failure Codes 4-13. . . . . . . . . . . . . . . . . . .

5–1 Receive Parameter List Fields 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Receive CSTAT Request Bits 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Receive CSTAT Complete Bits 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Transmit Parameter List Fields 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Transmit CSTAT Request Bits 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Transmit CSTAT Complete Bits 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 ThunderLAN MII Pins (100M-bps CSMA/CD) 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Possible Sources of MII Event Interrupts 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 PCI Command Register Bits A-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 PCI Status Register Bits A-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–3 PCI NVRAM Register Bits A-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–4 PCI Reset Control Register Bits A-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–5 Host_CMD Register Bits A-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–6 HOST_INT Register Bits A-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–7 DIO_ADR Register Bits A-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–8 Network Command Register Bits A-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–9 Network Serial I/O Register Bits A-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–10 Network Status Register Bits A-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–11 Network Status Mask Register Bits A-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–12 Network Configuration Register Bits A-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–13 MAC Protocol Selection Codes A-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–14 Ethernet Error Counters A-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–15 Demand Priority Error Counters A-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–16 Adapter Commit Register Bits A-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–17 Burst Size Register Bits A-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–18 Demand Priority Error Counters A-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–19 PHY Generic Control Register Bits A-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–20 PHY Generic Status Register Bits A-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–21 Autonegotiation Advertisement Register Bits A-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–22 Autonegotiation Link Partner Ability Register Bits A-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–23 Autonegotiation Expansion Register Bits A-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–24 ThunderLAN PHY Control Register Bits A-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

Page 16

Tables

A–25 ThunderLAN PHY Status Register Bits A-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–1 PHY Generic Control Register Bits B-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–2 PHY Generic Status Register Bits B-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–3 ThunderLAN PHY Control Register Bits B-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B–4 ThunderLAN PHY Status Register Bits B-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xiii

Page 17

xiv

Page 18

Running Title—Attribute Reference

Chapter 1

ThunderLAN Overview

The ThunderLAN family consists of highly integrated, single-chip networking

hardware. It uses a high-speed architecture that provides a complete peripheral component interconnect (PCI)- to-10Base-T/AUI (adapter unit interface)

Ethernet solution. It allows the flexibility to handle 100M-bps Ethernet protocols as the user’s networking requirements change.

The TNETE100A, one implementation of the ThunderLAN architecture, is an

intelligent protocol network interface. Modular support for the 100 Base-T

(IEEE 802.3u) and 100VG-AnyLAN (IEEE 802.12) is provided via a media

independent interface (MII). The TNETE110A is the same device without the

MII and is 10M bps only . ThunderLAN uses a single driver suite to support multiple networking protocols.

ThunderLAN architecture was designed to achieve the following goals:

-

High performance with low use of host CPU

-

Simplicity of design

-

Ease of upgrade to higher speed networks

-

Freedom of choice of network protocol

ThunderLAN allows a simple system design by integrating a PCI controller, an

internal first in, first out (FIFO) buffer , a LAN controller, and a 10Base-T physical interface (PHY).

Topic Page

1.1 ThunderLAN Architecture 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Networking Protocols 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 PCI Interface 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter Title—Attribute Reference

1-1

Page 19

ThunderLAN Architecture

1.1 ThunderLAN Architecture

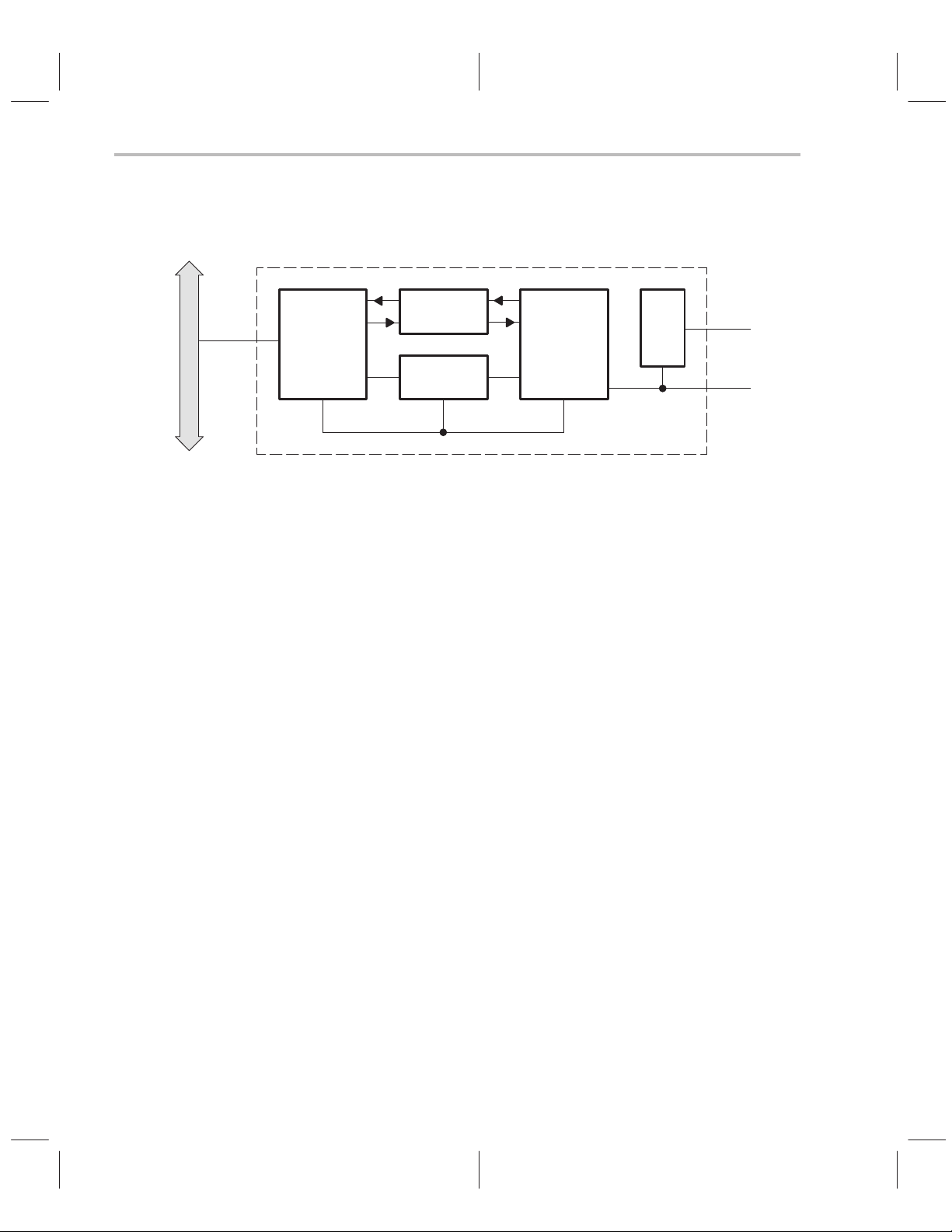

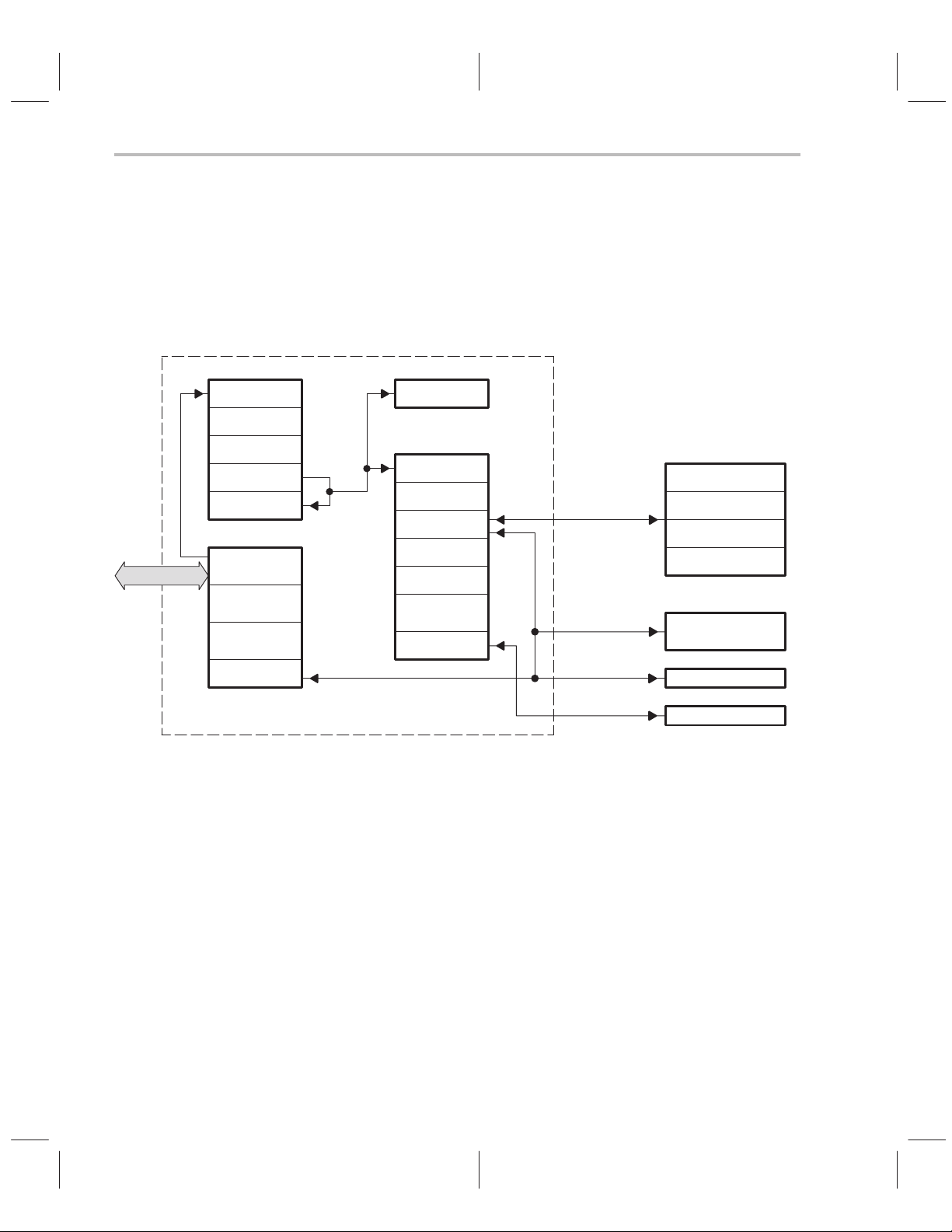

Figure 1–1.The ThunderLAN Controller

PCI Bus

PCI

controller

An integrated PHY provides interface functions for 10Base-T carrier sense

multiple access/collision detect (CSMA/CD) (Ethernet). A MII is used to communicate with the integrated PHY. The PHY is an independent module from

the rest of the ThunderLAN controller. This allows the PHY to be reset and

placed in a power-down mode.

FIFO

registers

Multiplexed

SRAM

LAN

controller

PHY

LAN

802.3

100M-bps

MII

The PCI controller is responsible for direct memory accesses (DMAs) to and

from the host memory . It is designed to relieve the host from time-consuming

data movements, thereby reducing use of the host CPU. The PCI interface

supports a 32-bit data path.

ThunderLAN supports two transmit and one receive channels. The demand

priority protocol supports two frame priorities: normal and priority. The two

transmit channels provide independent host channels for these two priority

types. CSMA/CD protocols only support a single frame priority, but the two

channels can be used to prioritize network access, if needed. All received

frames pass through the single receive channel.

ThunderLAN’s multiplexed SRAM is 3.375K bytes in size. This allows it to support one 1.5K byte FIFO for receive, two 0.75K byte FIFOs for the two transmit

(Tx) channels, and three 128-byte lists (see section 5.1, List Management). In

one-channel mode, the two Tx channels are combined, giving a single 1.5Kbyte FIFO for a single Tx channel. Supporting 1.5K byte of FIFO per channel

allows full frame buffering of Ethernet frames. PCI latency is such that a minimum of 500 bytes of storage is required to support 100M-bps LANs. (Refer to

PCI Local Bus Specification,

the

revision 2.0, section 3.5, Latency).

ThunderLAN’s industry-standard MII permits ease of upgrade. External devices can be connected to the MII and managed, if they support the two-wire

management interface. PHY layer functions for 100M-bps CSMA/CD and demand priority are connected to the MII.

1-2

Page 20

1.2 Networking Protocols

The MII also allows freedom in choosing a networking protocol. It allows the

use of standard 100M bps CSMA/CD PHY chips. ThunderLAN uses these signal lines to interface to an external 100M bps demand priority PHY . This gives

ThunderLAN the flexibility necessary to handle 10Base-T, 10Base-2,

10Base-5 AUI, 100Base-TX, 100Base-T4, 100Base-FX, and 100VG-AnyLAN

today, while supporting emerging technologies.

ThunderLAN is designed to simplify the software used to transmit frames, receive frames, and service the PHY events. It accomplishes this by integrating

time-consuming tasks into the controller. These tasks include:

-

The DMA of data into and out of the controller

-

A simplified, interrupt-driven frame buffer management technique

-

The elimination of PHY register polling through MII interrupts

DMA of data is handled through list structures. ThunderLAN’s method of handling data through list structures has parallels with the method used in Texas

Instruments TI380 COMMprocessors. There are some differences, such as

the use of a 0 forward pointer.

Networking Protocols

ThunderLAN is designed to meet

its PCI interface standards.

PCI Local Bus Specification

, revision 2.0 for

ThunderLAN Overview

1-3

Page 21

PCI Interface

1.3 PCI Interface

1.3.1 PCI Cycles

The PCI local bus is a high-performance, 32- or 64-bit bus with multiplexed address and data lines. The bus is designed to be a medium between highly integrated peripheral controller components such as ThunderLAN, add-in boards,

and processor/memory systems.

ThunderLAN executes the following cycles when it acts as the PCI bus master.

The hexadecimal number shown is the bus command encoded in the PC/

BE[3::0]# signals.

-

0x7h–memory write

-

0xCh–memory read multiple

-

0xEh–memory read line

ThunderLAN responds to the following PCI cycles when acting in slave mode

on the PCI bus:

-

0x2h–I/O read

-

0x3h–I/O write

-

0x6h–memory read

-

0x7h–memory write

-

0xAh–configuration read

-

0xBh–configuration write

-

0xCh–memory read multiple

-

0xEh–memory read line

-

0xFh–memory write and invalidate

1-4

Future versions of ThunderLAN may not be limited to these PCI cycles. T exas

Instruments reserves the right to add or delete any cycles to the ThunderLAN

PCI controller. When designing a system, ensure that the attached interface

to ThunderLAN is fully compliant with the

PCI Local Bus Specification

.

Page 22

1.3.2 Byte Ordering

PCI Interface

ThunderLAN follows the

ferring data on the PCI bus. The PCI bus data is transferred on the P AD[31::0]

lines. PAD31 is the most significant bit, and PAD0 is the least significant bit.

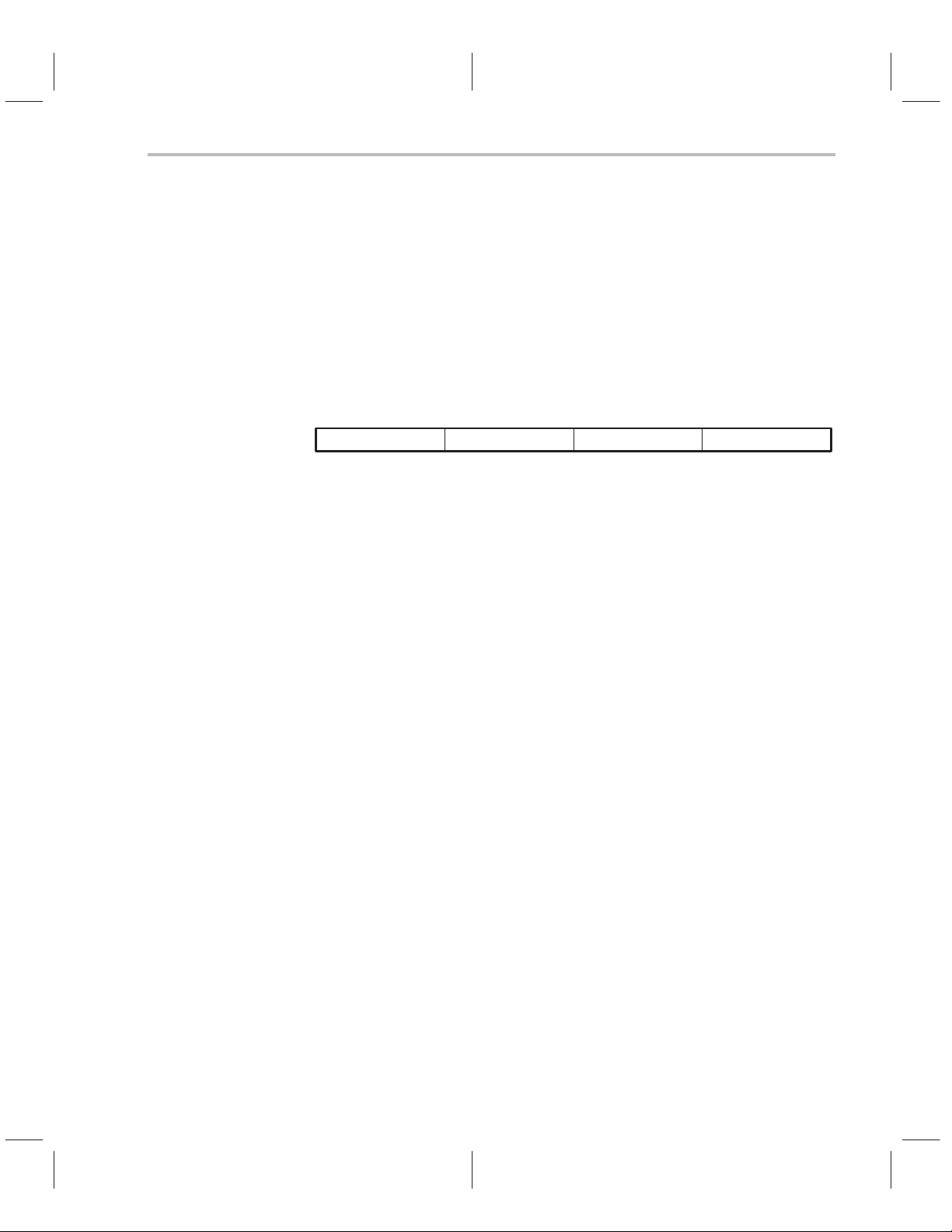

The 32 data lines are enough to transfer four bytes per data cycle. Byte 0 is

the LSbyte and byte 3 is the MSbyte. Byte 0 uses bits 0–7, byte 1 uses bits

8–15, byte 2 uses bits 16–23, byte 3 uses bits 24–31.

Figure 1–2. PCI Bus Byte Assignment

31

ThunderLAN uses the full four bytes per data cycle. The only exception is when

the data to be transferred is not octet aligned. In this case, the PCI controller

might not transfer the full four bytes on the first cycle. ThunderLAN deasserts

the IRDY signal only once, if needed, to synchronize the PCI bus to the internal

64-bit architecture. The deassertion of IRDY occurs on the third cycle of the

PCI bus. ThunderLAN does not deassert IRDY for the rest of the transfer unless the PCI bus asserts the TRDY signal.

PCI Local Bus Specification

convention when trans-

07815162324

Byte 0Byte 1Byte 2Byte 3

ThunderLAN Overview

1-5

Page 23

1-6

Page 24

Chapter 2

ThunderLAN Registers

ThunderLAN uses a variety of registers to perform its networking functions.

These include peripheral component interface (PCI) registers, host registers,

internal direct input/output (DIO) registers, media independent interface (MII)

registers, and physical interface (PHY) registers. Access to these is a requirement for setting up the ThunderLAN controller and any of the PHY devices attached to the MII. They must be accessed as well for transmission, initiation,

and reception of data. Other activities which require the user to understand

ThunderLAN’s register spaces include determining the cause of event-driven

interrupts and how to clear them and diagnostic functions. This chapter explains register configurations and discusses control of these spaces through

code examples.

Topic Page

2.1 Register Addresses 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 PCI Configuration Space 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Host Registers 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Internal Registers 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 MII PHY Registers 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 External Devices 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1

Page 25

Register Addresses

2.1 Register Addresses

The following figure shows the various register spaces provided by ThunderLAN. It also shows how a driver uses ThunderLAN’s registers to interface to

external devices such as PHYs, BIOS ROMs, and EEPROMs.

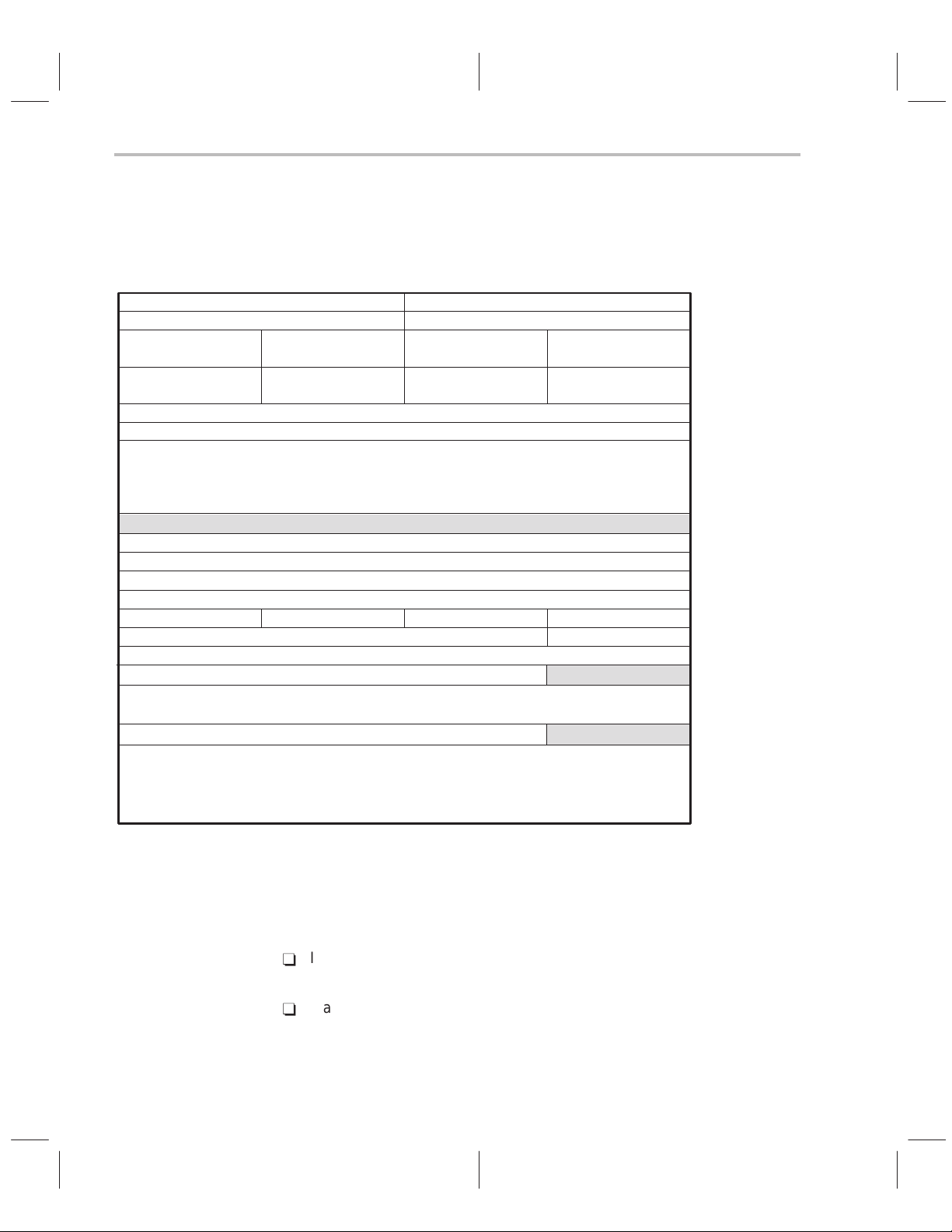

Figure 2–1. How ThunderLAN Registers are Addressed

ThunderLAN

Host registers

SRAM

Internal/DIO registers

NetCmd

NetSts

NetSio

AREG0–3

HASH

Statistics

registers

LEDreg

PCI

HOST CMD

CH PARM

HOST INT

DIO ADR

DIO DATA

PCI registers

I/O base

address

Memory

base address

BIOS ROM

base address

PCI NVRAM

MDIO/MDCLK

EDIO/EDCLK

MII/PHY registers

Generic

Autonegotiation

Reserved

PHY specific

Serial EEPROM

BIOS ROM

2-2

LED IF

LED

One block of registers, the host registers, appear at a programmable place in

memory or port address space, directly on the PCI bus. The beginning address

is determined by the value written into the PCI configuration space base address registers. Once the base register’s address is determined, ThunderLAN

reads and writes to these registers like ordinary memory or I/O ports. Since the

ThunderLAN devices are directly connected to the PCI, there is no external

decode logic that generates a chip select—all the decode is done internally.

ThunderLAN’s internal/DIO registers are accessed via the DIO_ADR and

DIO_DA TA registers in the host register group. An address is placed in the host

DIO_ADR register , and the data to be read or written to the DIO register is read

or written to the DIO_DA TA register. The internal/DIO register space is referenced indirectly via the host registers to minimize the amount of host address

space required to support the ThunderLAN controller. External devices and

their data are also reached via indirect reference through the host registers

Page 26

Register Addresses

and PCI configuration registers to make control of the system possible through

the one PCI interface.

An EEPROM, required by the PCI, can be written to at manufacture time

through the PCI_NVRAM register, which is located in the host register space.

The EEPROM can also be accessed through the NetSio register which is located in the internal/DIO register space. Control registers on the PHY side of

the MII management interface can be similarly written and read through the

NetSio register.

A BIOS ROM can be enabled via the BRE bit in the PCI BIOS ROM base address register, and its chip selected address dynamically assigned via a base

register in the configuration space. The BRE bit points to a valid address in the

ROM address space which causes two byte-address strobe cycles (EALE,

EXLE) and a read before the PCI cycle is completed.

ThunderLAN Registers

2-3

Page 27

PCI Configuration Space

2.2 PCI Configuration Space

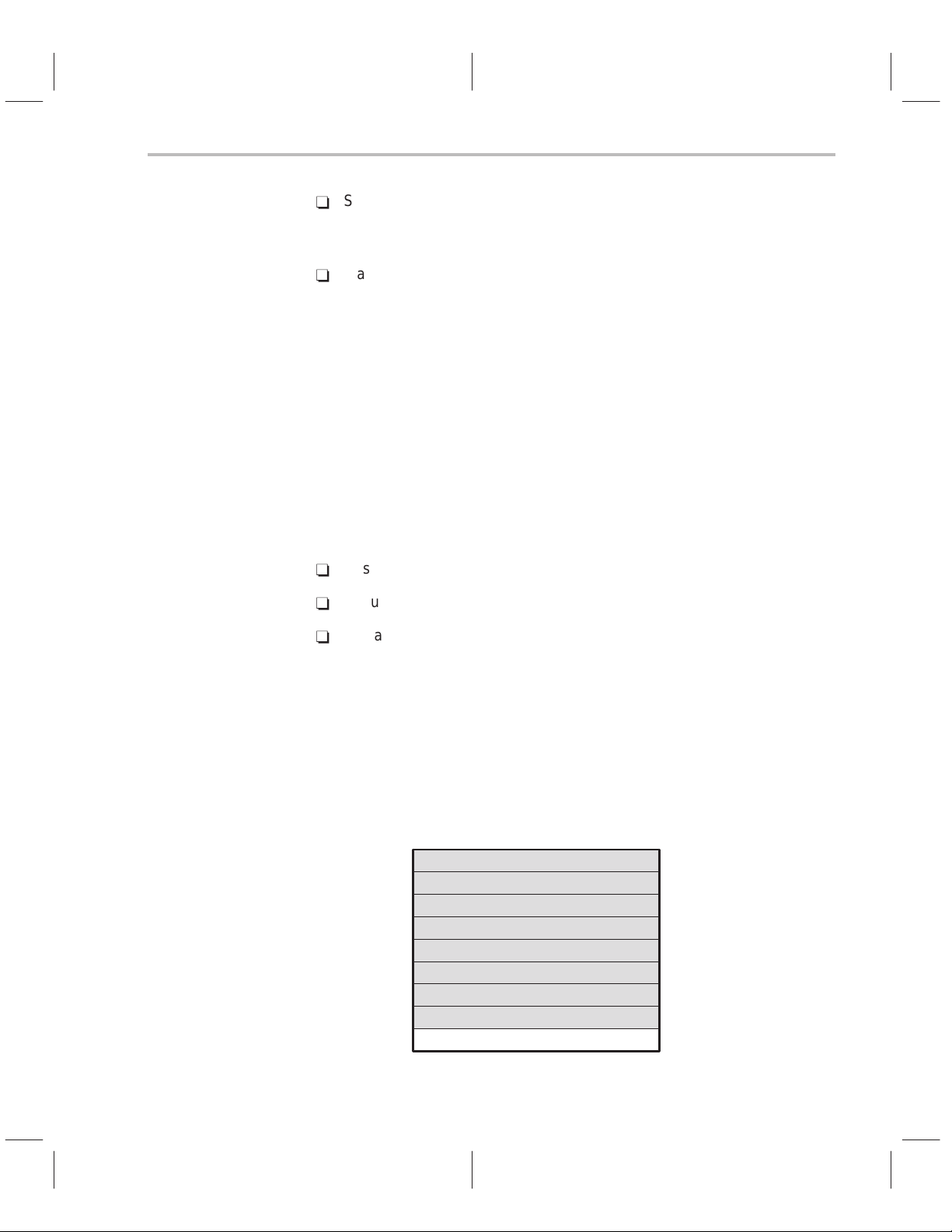

Figure 2–2.The PCI Configuration Space Registers

Base class

(02h)

Reserved

Vendor IDDevice ID

Status Command

Subclass

Reserved

(00h)(00h)

I/O base address

Memory base address

Reserved (00h)

Cardbus CIS Pointer

Reserved (00h)

BIOS ROM base address

Reserved (00h)

Reserved (00h)

Reserved (00h)

Reserved (00h)

Reserved (00h)

Reserved (00h)

Program interface

(00h)

Latency

timer

Int pin(01h)Min_GntMax_Lat

Byte 0Byte 1Byte 2Byte 3

Revision

Cache line

size

Interrupt line

Reset control

IntDis

031

read only

00h

read/write

04h

read only

08h

read/write

0Ch

read/write

10h

read/write

14h

18h

28h

2Ch

read/write

30h

34h

38h

read/write

3Ch

read/write

40h

44h

48h

read only

2-4

Reserved (00h)

Reserved (00h)

PCI NVRAM

B4h

read only

FFh

Register configuration space information fields are needed to identify a board

in a slot to a driver. The functional purpose of the board, the manufacturer , the

revision, and several bus requirements can be obtained by inspecting these

parameters. The PCI configuration space uses these registers which are

called out in the

-

Identify the ThunderLAN controller. This includes setting the interrupt as-

PCI Local Bus Specification.

These enable the PCI system to:

signed to ThunderLAN.

-

Map the host registers using either the I/O base address register or the

memory base address register. The driver uses the address contained in

these registers to access ThunderLAN’s internal registers.

Page 28

PCI Configuration Space

-

Set up the PCI bus. Several PCI bus options can be selected through

these registers, including latency and grant. (Refer to

ification,

-

Map a BIOS ROM using the BIOS ROM base address register

subsection 3.5)

PCI Local Bus Spec-

Many of the registers in the PCI configuration space are accessed with PCI

BIOS calls. Refer to the

PCI Local Bus Specification,

chapter 6, for the commands supported by your specific PCI BIOS. Some operating systems (O/Ss)

provide BIOS call support. Your operating system’s user’s guide contains

these specific BIOS support routines.

The PCI specification requires that a bus-resident device respond to bus cycle

codes reserved for reading and writing to configuration space. See the

Local Bus Specification

document for more information on how these short,

PCI

slot-dependent address spaces appear to the host processor. The shaded

registers in Figure 2–3 can be autoloaded from an external serial EEPROM.

Check the following before accessing the PCI configuration space:

-

Ensure that there is a PCI BIOS present or other support for BIOS calls.

-

Ensure that the BIOS is the right revision.

-

Use a PCI BIOS call to find all attached devices on the PCI bus. Make sure

that you are talking to the right device on the PCI bus.

Attaching a pullup resistor to the EDIO pin allows the board designer to automatically read an EEPROM after reset to determine the contents of the first

eight bytes, shown shaded below. If the host attempts to read any of the configuration space during the time the adapter is reading the EEPROM, ThunderLAN rejects the request by signaling target-retry.

Figure 2–3. Configuration EEPROM Data Format

Vendor ID LSByte

Vendor ID MSByte

Device ID LSByte

Device ID MSByte

Revision

Subclass

Min_Gnt

Max_Lat

Checksum

Address

C0h

C1h

C2h

C3h

C4h

C5h

C6h

C7h

C8h

ThunderLAN Registers

2-5

Page 29

PCI Configuration Space

Normally , access to the configuration space is limited to the operating system.

On power-up, the vendor ID, device ID, revision, subclass, Min_Gnt, and

Max_Lat registers are loaded with default values. Vendor-specific data is

loaded into these registers by placing the data into the EEPROM, which is read

at the end of reset if autoload is enabled with a pullup resistor on the EDIO pin.

If the data read from the EEPROM has a checksum error, values are fetched

from the default PCI parameter registers, which are located at addresses

0x08h to 0x0Fh in the internal/DIO registers space.

Some fields in the configuration space like the bits in the memory base address

register and the I/O base address register, which indicate the space size allocation required to access the host registers, are hardwired in the ThunderLAN controllers. Some of the allowed PCI configuration space values like base

registers beyond the basic I/O and memory base registers are not implemented because no other entities are supported by this PCI interface other than the

network function.

To find register information, you must first identify the PCI function ID:

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// PCIFindDevice – Find PCI device

//

// Parameters:

// DeviceID WORD The device ID

// VendorID WORD The vendor ID

// Index WORD index (normally 0, use when more than

1 device)

// pDev WORD* Where to put the device id

//

// Return val:

// int 0 if successful. see std return codes in

header

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

WORD PciFindDevice(

WORD deviceID,

WORD vendorID,

WORD Index,

WORD *pDev)

{

union REGS r;

2-6

Page 30

PCI Configuration Space

r.h.ah = PCI_FUNCTION_ID;

r.h.al = FIND_PCI_DEVICE;

r.x.cx = DeviceID;

r.x.dx = VendorID;

r.x.si = Index;

int86(PCI_INT, &r, &r);

*pDev = (WORD)r.x.bx;

return (int)r.h.ah;

}

This code returns the function ID that is used to request reads and writes to

the ThunderLAN PCI configuration space; this varies from installation to installation, based on hardware implementation and slot. This ID is necessary to determine where ThunderLAN is. The device ID indicates a networking card, and

the vendor ID is the manufacturer code. These values can be overlaid in the

configuration space with values from the EEPROM during the autoconfiguration. These should be available to the driver software either in the BIOS ROM

or on machine-readable media supplied with the network board(s).

The following example reads a byte of a PCI register:

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// PciRdByte() – Read a byte from PCI configuration space

//

// Parameters:

// devid WORD pci device identifier

// addr WORD config address

//

// Return val:

// BYTE value read

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

BYTE PciRdByte(WORD devid, WORD addr)

{

union REGS r;

r.h.ah = PCI_FUNCTION_ID; /* PCI_FUNCTION_ID

0xB1 */

r.h.al = READ_CONFIG_BYTE; /* READ_CONFIG_WORD

0x09 */

r.x.bx = devid;

ThunderLAN Registers

2-7

Page 31

PCI Configuration Space

r.x.di = addr;

int86(PCI_INT, &r, &r); /* PCI_INT 0x1A */

return (r.x.cx & 0xFF);

}

Normally , the constants in this routine (the values assigned to ah, al, and the

opcode for the int86 call) are assigned in the header file for the C code. Their

values are inserted as comments to enable the reader to resolve the actual values that are used. The device ID, devid, is known to the driver and is used with

another PCI O/S call to find the base addresses needed for this call.

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// PciRdWord() – PCI read config word

//

// Parameters:

// devid WORD pci device number

// addr WORD address to read

//

// Return val:

// WORD value read

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

WORD PciRdWord(WORD devid, WORD addr)

{

union REGS r;

r.h.ah = PCI_FUNCTION_ID;

r.h.al = READ_CONFIG_WORD;

r.x.bx = devid;

r.x.di = addr;

int86(PCI_INT, &r, &r);

return(r.x.cx);

}

2-8

This code passes an address >10 if the driver regards the host registers as

memory locations (ThunderLAN’s first base address register is hardwired as

a memory base register), or >14 if the driver treated the host registers as an

I/O block (ThunderLAN’s second base register is hardwired as an I/O base

register). For the I/O port, the following C instruction could be used to put a value into the DIO_ADR host register:

outpw(base_addr+OFF_DIO_ADDR,value);

OFF_DIO_ADDR is a constant for the header file. A memory transfer instruction is used if memory space is used instead of I/O space.

Page 32

2.3 Host Registers

Figure 2–4. Host Registers

ThunderLAN implements the host registers shown above. These are the primary control points for ThunderLAN. Through the host registers, a driver can:

-

Reset the ThunderLAN controller

-

Start transmit and receive channels

-

Handle interrupts: Acknowledge interrupts, turn certain kinds of interrupts

on or off, or pace interrupts with the host

-

Access the internal registers

-

Access the internal SRAM for diagnostic purposes

HOST_CMD

CH_PARM

DIO_DATA

Host Registers

Base address

offset

0151631

+0

+4

DIO_ADRHOST_INT

+8

+12

HOST_CMD register gives commands to the ThunderLAN controller. It is

The

used in conjunction with the CH_PARM register to start the transmit and receive processes (Tx GO/Rx GO). It is also used in conjunction with the

HOST_INT register to acknowledge (ack) interrupts. Through HOST_CMD,

interrupt pacing can be selected.

The CH_PARM register is used to give the physical addresses of a transmit

or receive list to ThunderLAN’s direct memory access (DMA) controller . ThunderLAN uses the address in the CH_PARM register to DMA data into or out

of its FIFOs. In an adapter check, an error condition where ThunderLAN must

be reset, CH_PARM contains information on the nature of the error.

HOST_INT register contains information on the type of interrupt that was

The

given to the host processor. It is also used with the CH_P ARM register to indicate adapter checks. HOST_INT is designed to make interrupt handling routines simple and powerful. The last two significant bits are set to 0 so that this

register may be used as a table offset in a jump table. The bit definitions are

mapped to the most significant word (MSW) of the HOST_CMD

register. This

allows acknowledging of interrupt operations by simply taking the value in

HOST_INT and writing it to HOST_CMD.

The DIO_ADR and DIO_DA TA registers work in tandem to allow accesses to

the internal DIO registers and SRAM. The value in DIO_ADR selects the register or memory locations to be accessed.

ThunderLAN Registers

2-9

Page 33

Host Registers

To enable reads of adjacent addresses without reposting the address, bit 15

of the DIO_ADR register can be set, which causes the address to be post-incremented by 4 after each access of the DIO_DA TA register. This function is

useful when reading the statistics or reading the internal SRAM. Autoincrementing while reading the FIFO memory causes a move to the same part of

the next 68-bit word; it does not move to the next part of the same 68-bit word.

The two least significant bits (LSBs) of the DIO_ADR must be expressly set

to get to the various parts of each 68-bit entity.

The host registers are addressed either as memory or I/O ports. The PCI configuration space has locations for the O/S to assign up to six memory or I/O

base addresses. The depth of the space requested for each base register implemented is determined by the number of bits, starting at the LSBs, whose

values are fixed. The O/S writes to the rest of the bits (with the assumption that

the fixed positions are equal to 0) at the beginning address of that block.

As an example, the LSB determines whether the base register is a memory

(0) or an I/O space (1) base register. ThunderLAN’s PCI interface reserves

memory I/O space by implementing an I/O and a memory configuration base

register, both with the four LSBs in these registers fixed to indicate the field

width requested be reserved in the respective address space for the host register block (four quad words or 16 bytes). The rest of the bits of a base register

are filled in by the O/S after all the space requests are considered.

2-10

Assigning space in this way assures that all starts of fields are naturally aligned

to long words or better. It is important to note that by the time either the BIOS

code or driver code is allowed to run, the O/S has queried the card and assigned the base addresses. The host registers can be accessed equally in

both address spaces on host processor systems that support both.

Some processors only support memory spaces; in these cases the I/O spaces

are assigned a 0, which is not a valid base register value for a peripheral. The

driver must check for a 0 base offset value before using the I/O method of

accessing the ThunderLAN registers. The base offset must be constant between host processor resets, but can be different for each execution of the program. All host register accesses are done relative to the value found in the respective configuration base register.

The unimplemented base registers in the configuration space return all 0s on

32

a read. This is equivalent to requesting a 2

-byte data space—all of the avail-

able address space in a 32-bit address system. PCI interprets an all-bits-fixed

situation as not implemented.

Page 34

2.4 Internal Registers

Figure 2–5. Internal Registers

Internal Registers

Byte 3

NetMask

Default

device ID

MSbyte

Default

Max_Lat

Areg_0

(23 to 16)

Areg_1

(39 to 32)

Areg_1

(7 to 0)

Areg_2

(23 to 16)

Areg_3

(39 to 32)

Areg_3

(7 to 0)

Tx underrun

Rx overrun

Code error

frames

Acommit

Byte 2

NetSts

Default

device ID

LSbyte

Default

Min_Lat

Areg_0

(31 to 24)

Areg_1

(47 to 40)

Areg_1

(15 to 8)

Areg_2

(31 to 24)

Areg_3

(47 to 40)

Areg_3

(15 to 8)

CRC error

frames

Carrier loss

errors

Byte 1

NetSio

Default

vendor ID

MSbyte

Default

Subclass

Areg_0

(39 to 32)

Areg_0

(7 to 0)

Areg_1

(23 to 16)

Areg_2

(39 to 32)

Areg_2

(7 to 0)

Areg_3

(23 to 16)

HASH1

HASH2

Good Tx frames

Good Rx frames

Multicollision Tx framesSingle collision Tx frames

Late

collisions

NetConfigMan Test

vendor ID

revision

(47 to 40)

(31 to 24)

(47 to 40)

(31 to 24)

Deferred Tx

frames

Excessive

collisions

Byte 0

NetCmd

Default

LSbyte

Default

Areg_0

Areg_0

(15 to 8)

Areg_1

Areg_2

Areg_2

(15 to 8)

Areg_3

LEDregBSIZEregMaxRx

DIO address

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

0x20

0x24

0x28

0x2C

0x30

0x34

0x38

0x3C

0x40

0x44

The internal registers are used less often than the host registers. They are

used for:

-

Setting diagnostic options, such as loopback (wrap) and copy all frames

-

Setting network options. This is usually a one-time operation at initialization.

ThunderLAN Registers

2-11

Page 35

Internal Registers

-

Setting commit levels and PCI burst levels

-

Interfacing via the management interface to the PHY registers

-

Determining status interrupts

-

Setting eight bytes of default PCI configuration data if the EEPROM

checksum is bad

-

Setting the various unicast and multicast addresses

-

Providing network statistics

-

Setting the LEDs and implementing a BIOS ROM

The NetCmd

register is used to set many of the diagnostic modes such as

wrap, copy short frames (CSF), copy all frames (CAF), no broadcast

(NOBRX), duplex, and token ring frame formats. It also includes a reset bit,

which is used to allow changes in the NetConfig register for additional network

configuration options.

,

NetSio, the network serial I/O register

is used to control the MDIO/MDCLK

management interface. It is also used to communicate with an EEPROM, using the EDIO/EDCLK serial interface. This register can also enable or disable

PHY interrupts.

2-12

NetSts and NetMask registers work in tandem to determine the nature of

The

a status interrupt. The bits in the NetMask register are used to mask whether

the status flags in NetSts cause interrupts or not.

NetConfig register sets network configuration options during reset. This

The

register can only be written to when ThunderLAN is in reset (NRESET = 0). It

allows the controller to receive CRCs (RxCRC), pass errored frames (PEF),

use a one-fragment list on receive (refer to subsection 5.3, One-Fragment

Mode, for more information), use a single transmit channel, enable the internal

PHY, and select the network protocol (CSMA/CD or demand priority).

The AREG registers allow ThunderLAN to recognize any four 48-bit IEEE 802

address. This includes specific, group, local, or universal addresses. They can

be Ethernet or token ring addresses. The HASH registers allow group addressed frames to be accepted on the basis of a hashing table.

The statistics registers hold the appropriate network counters, including good

Tx and Rx frames, collisions, deferred frames, and error counters. The LEDs

are controlled through the

LEDreg register, which directly controls the values

output on the LED lines EAD[7::0]. All are, therefore, software programmable.

LEDreg can also be used to implement a BIOS ROM. The

Acommit register

Page 36

Internal Registers

is used to set the network transmit commit level. The BSIZEreg register is used

to set the bus burst size on both Tx and Rx frames.

The internal registers are accessed via the DIO_DATA and DIO_ADR host

registers. DIO_ADR holds the DIO address of the register. The data is then

read from or written to DIO_DATA.

Before one can write to an internal register, one must find the proper address

for the host registers to use as pointers to the internal register block, and decide whether to use the memory pointer or the I/O port pointer value. Following

is an example of x86 C code to access a byte from an internal register using

the I/O port pointer value:

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// DioRdByte() – Read byte from adapter internal register

//

// Parameters:

// base_addr WORD base address of TLAN internal registers

// addr WORD offset of register to read

//

// Return val:

// BYTE value read

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

BYTE DioRdByte(WORD base_addr, WORD addr)

{

outpw(base_addr+OFF_DIO_ADDR, addr);

return(inp((base_addr+OFF_DIO_DATA) + (addr&3)));

}

The address of the register being read is determined by the calling program

and is passed to this routine as a parameter, along with the the I/O base address. An output is executed to the DIO_ADR host register as part of setting

up the pointer address. In x86 architectures, there are separate instructions

for 16-bit port writes and 8-bit port writes; the 16-bit version is used to write all

the address field’s 16 bits in one operation. Internally , this causes the data from

the internal register at that address to be deposited in the DIO_DA T A host register. A byte read of the data register gets the LSbyte (addr&3). A more sophisticated routine honors the address of the byte specifically requested and sees

that those eight bits are shifted down to a byte to be returned. If you want to

read a whole word from one of the internal registers (32 bits), you could perform two 16-bit reads and merge the values to be returned as a 32-bit value

like this:

ThunderLAN Registers

2-13

Page 37

Internal Registers

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// DioRdDword() – read 32 bits from internal TLAN register

//

// Parameters:

// base_addr WORD base address of TLAN internal registers

// addr WORD address to read

//

// Return val:

// DWORD value read

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

DWORD DioRdDword(WORD base_addr, WORD addr)

{

DWORD data;

addr &= 0x3fff;

outpw(base_addr+OFF_DIO_ADDR, addr);

data = ((DWORD)inpw(base_addr+OFF_DIO_DATA))&0x0000ffffl;

data |= ((DWORD)inpw(base_addr+OFF_DIO_DATA+2)) << 16l;

return(data);

}

2-14

Page 38

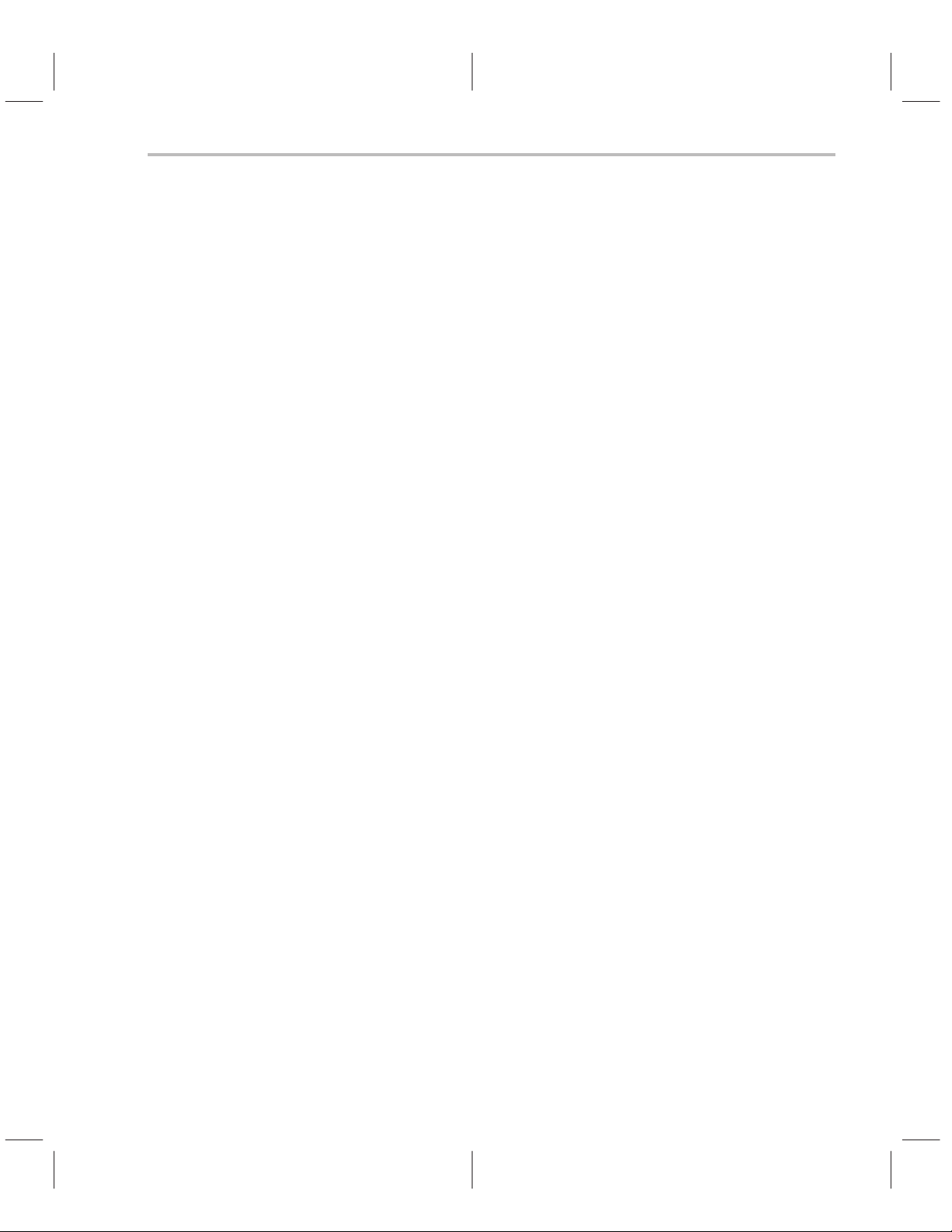

2.5 MII PHY Registers

Figure 2–6. MII PHY Registers

Register

MII PHY Registers

Description

Control

Status

PHY identifier

PHY identifier

AN advertisement

AN link-partner ability

AN expansion

AN next page transmit

Reserved

Reserved

Reserved

Vendor-specific registers

Vendor-specific registers

Vendor-specific registers

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

through

0x0F

0x10

through

0x1F

PHY generic control register

PHY generic status register

PHY generic identifier (high)

PHY generic identifier (low)

Autonegotiation advertisement

Autonegotiation link-partner ability

Autonegotiation expansion

Autonegotiation next page transmit

Reserved by IEEE 802.3

Vendor-specific registers

The 802.3 standard specifies a basic set of registers that must be present.

These include a control register at 0x00 and a status register at 0x01. An extended set from 0x02 through 0x1F can also be implemented. Within the extended set, 0x02 through 0x07 are defined and 0x08 through 0x0F are reserved. The area between 0x10 and 0x1F can be used for vendor-specific applications. The basic set of registers is shown in dark gray above. The extended registers are shown in lighter gray and white. The light gray registers

are those defined by 802.3, and the white registers are vendor-specific. The

register specification for the internal 10Base-T PHY in ThunderLAN controllers is shown in Appendix A. We have also included the register specification

for the TNETE21 1 100VG-AnyLAN physical media interface (PMI) in Appendix B.

The PHY registers are accessed to:

-

Initialize the PHY, bring it in and out of reset, and isolate it from the MII

-

Set PHY options, such as duplex and loopback

-

Determine the type of speed and protocol supported by the PHY

-

Conduct autonegotiation, if supported

-

Select any vendor-specific options

The control register (GEN_ctl in ThunderLAN products) controls PHY options

such as reset, loopback, duplex, and autonegotiation enable. It also powers

down and isolates the PHY from the MII.

ThunderLAN Registers

2-15

Page 39

MII PHY Registers

The status register (GEN_sts in ThunderLAN products) includes bits to identify

the technology supported by the PHY. This technology includes protocol and

duplex abilities. It indicates link, jabber, and autoconfiguration completion. Bit

0 of the status register also indicates whether the extended register set is supported.

The PHY identifier registers (GEN_id_hi/GEN_id_lo in ThunderLAN products)

contain an identifier code for the silicon revision and the silicon manufacturer.

Registers 0x04 thru 0x07 are used in the autonegotiation process. They include the autonegotiation advertisement, autonegotiation link partner ability,

autonegotiation expansion, and autonegotiation next page registers (AN_adv ,

AN_lpa, AN_exp respectively).

In the vendor-specific area, T exas Instruments has implemented a TLPHY_id

register. This register is used to identify ThunderLAN-specific PHY devices.

ThunderLAN also implements a specific control register, TLPHY_ctl, and status register, TLPHY_sts. The particulars of these registers change from PHY

to PHY. Please refer to Appendix A for the PHY that you are using.

Writing to a register in a PHY through the management interface involves writ-

,

ing data and clock bits into NetSio

an internal register, which uses the pointer

host registers. The data unit to or from a PHY register is always 16 bits.

The NetSio register uses three bits to drive the MDIO/MDCLK MII manage-

ment interface. These bits are MCLK, MTXEN, and MDA TA. These bits directly

control the voltages present in the management interface and function like

this:

-

MCLK directly controls the MDCLK signal. Setting MCLK in NetSio high

causes a logic 1 to appear on the MDCLK pin. Setting MCLK in the NetSio

register low causes a logic 0 to appear on the MDCLK pin.

-

MTXEN controls the direction of the MDIO pin.

J

When MTXEN is high, MDIO is driven with the value written on

MDATA.

J

When MTXEN is low, MDATA mirrors the MDIO line.

Multiple PHYs can be attached to one MII. PHYs are selected through an address which can be in a range from 0x00 to 0x1F. Some vendors’ PHYs have

pins that can be pulled up or down to indicate the PHY address. In order for

a particular PHY to be addressed, the driver must know the PHY address beforehand.

ThunderLAN’s internal PHY for 10Base-T can only support two addresses.

When used in conjunction with the rest of the ThunderLAN device, the address

2-16

Page 40

MII PHY Registers

is 0x1F. When the internal PHY for 10Base-T is used in a standalone mode,

that is, when run from another controller through the MII pins, it is at address

0x00. These are the only two addresses allowed for the internal PHY.

The 100VG-AnyLAN PMI device, the TNETE211, is used to attach 802.12

physical media dependent (PMD) devices to ThunderLAN’s MII. The

TNETE21 1 has five external pins (DEVSEL[4::0]) that program the address to

which it will respond. If multiple PHYs are used, each must be installed with

a unique address.

Before reading or writing to any PHY register, the MII serial interface must be

synchronized. This involves a one-time write of 32, 1 bits on the MDIO pin.

Once this is done, an access can be done with a two-bit start delimiter, then

a two-bit op code (for read or write), followed by five bits of PHY address, five

bits of register address, two bits of turnaround time in case the PHY is going

to write to the data line, and 16 bits of data.

The synchronization code could be done this way:

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

// MIISync() – send MII synchronization pattern to all

// possible MII interfaces

//

// Parameters:

// base_addr base address on TLAN internal registers

//

// Return val:

// none

//––––––––––––––––––––––––––––––––––––––––––––––––––––––––

void MIISync(WORD base_addr)

{

register int i;

clr(MTXEN);

where clr is a macro to set a bit to 0 in the NetSio internal register. In this case,

bit MTXEN in NetSio is cleared.

#define clr(x)

DioWrByte(base_addr,Net_Sio,(BYTE)(DioRd

Byte(base_addr,Net_Sio)&~x))

When the output enable bit is cleared and the PHYs have just been turned on,

none of them outputs data. The value on the data line is determined by the pull-

ThunderLAN Registers

2-17

Page 41

MII PHY Registers

up resistor, which is recommended to be attached to this line. The MII devices

should see 1s.

An alternate way to give the PHYs a series of 1s, is to:

set(MDATA)

set(MTXEN)

clr(MCLK);

//delay here

DioRdByte(base_addr,Net_Sio);

set(MCLK);

Where MCLK is a constant for the third LSB (in the internal NetSio register)

and is defined as:

//delay

DioRdByte(base_addr,Net_Sio);

set(NMRST);

This is the command to set a bit to 0 in the internal NetSio register. In this case,

the MCLK bit in NetSio is set. Set could be defined this way:

#define set(x)

DioWrByte(base_addr,Net_Sio,(BYTE)(DioRdByte

(base_addr,Net_Sio) |x))

The routine to synchronize the PHYs is part of the startup code. The controller

at this point is held in reset due to the drivers writing a 1 to the Ad_Rst bit, bit

15 in the HOST_CMD register, or a reset being received on power-up through

the PCI system. Setting the NMRST bit to 0 places the MII bus in a reset state.

for (i = 0;i < 32;i++)

togLH(MCLK);

The command togLH is a combination of the clr and set commands on the

passed parameter and is defined this way:

#define togLH(x) {clr(x); \

set(x);}

}

togLH is repeated 32 times to give PHYs the 32, 1 data bits that they need to

get synchronized. Note that the clock line is left in the high state at the end of

the loop.

2-18