TMS320TCI6487 DSP Platform

Technology for Innovators

TM

Product Bulletin

Key Benefits

• Multi-standard SOC platform

•• SOC baseband solution for

TD-SCDMA, WiMAX,

cdma2000 and UMTS Tx

• Scalable platform

•• Modular design is ideal for

pico, micro and macro BTS

• Quick time to market

•• Software-programmable

solutions with the reuse of

existing software leads to a

shorter development cycle

• Cost optimization

•• Functional integration leads to

lower system cost and

eliminates the need for

accelerator ASICs

flexibility, the 3 Mbytes of L2

SRAM/cache can be configured in

multiple ways, such as 1/1/1 Mbytes

or 1.5/1/0.5 Mbytes, among the three

DSP cores. To support wireless

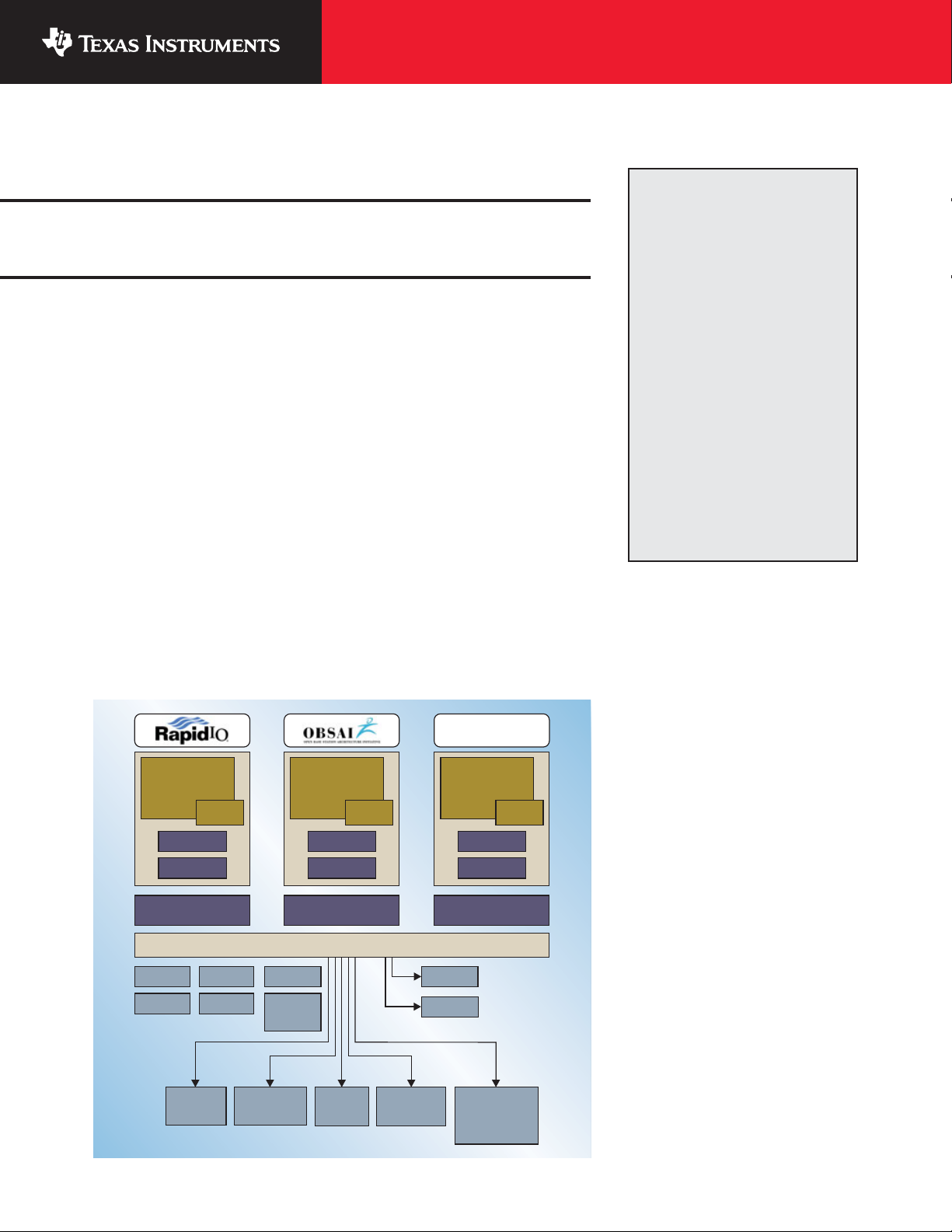

Figure 1. TCI6487 DSP Block Diagram

TCI6487 DSP Architecture

The TCI6487 high-performance DSP

has three independent DSP subsystems. At the heart of each subsystem

is a 1.0-GHz C64x+ DSP core. For

The TMS320TCI6487 (TCI6487) device is a very high-performance DSP

designed specifically for wireless infrastructure baseband applications. With

a high level of functional integration and a high channel density supported on

a single device, the TCI6487 DSP offers a modular and scalable design with

a small footprint. The TCI6487 DSP is therefore an ideal solution for pico,

micro and macro BTS and enables an SOC baseband solution for UMTS, TDSCDMA, WiMAX and cdma2000 applications. OEMs can accelerate their

channel card development with the use of the TCI6487 DSP, since it offers a

software-programmable solution and allows for the reuse of existing C64x

TM

and C64x+TMDSP code. Advanced features such as MIMO, beamforming

and Parallel Interface Cancellation (PIC) can be easily supported without

the need for any hardware redesign.

GPIO

PLL

IC

2

Timers Others

Boot

ROM

McBSP

Antenna

Interface

EDMA 3.0 with Switch Fabric

DDR2

IF

C64x+

Core

TM

C64x+

Core

C64x+

Core

L1 Data L1 Data L1 Data

L1 Prog L1 Prog L1 Prog

L2 Memory L2 MemoryL2 Memory

RSA RSA RSA

10/100/1000

Ethernet

Serial

RapidIO

VCP2

TCP2

CPRI

Common Public Radio Interface

applications, the DSP contains a

number of specialized coprocessors:

• Viterbi Decoder Coprocessor

(VCP2)

• Turbo Code Decoder Coprocessor

(TCP2)

• Rake Search/Spread Accelerator

(RSA)

The RSA is a tightly coupled

coprocessor that can be used to

accelerate CDMA chip-rate processing. Another important feature of

the device is its support of standard

interfaces such as serial RapidIO

(SRIO), Gigabit Ethernet, DDR2

and McBSP. The TCI6487 also

supports the OBSAI and CPRI

antenna interfaces, with up to six

configurable links at a maximum

rate of 3.072 Gbps (OBSAI) and

2.4576 Gbps (CPRI).

The EDMA 3.0 switch-fabric

engine supports high-bandwidth,

low-latency internal communications.

The EDMA manages communications between peripherals, memories,

accelerators and DSP cores.

Interfaces

TCI6487 supports standard antenna,

network, device and interdevice

communication interfaces as well as

a high-speed interface to communicate with external memory:

Antenna Interface

Six configurable (full-duplex) links

in either OBSAI or CPRI modes that

can support a variety of data rates.

Supports OBSAI/CPRI daisy chaining between DSPs.

• OBSAI—614.4-Mbps, 1.2288-Gbps,

2.4576-Gbps link rates supported

• CPRI—768-Mbps, 1.536-Gbps,

3.072-Gbps link rates supported

Key Features

• 3.0 GHz of total raw DSP

processing power

• A total of 3 Mbytes of total on-chip

L2 SRAM/cache

• Standard C64x+TMDSP core

•• Enables reuse of existing DSP

software

• RSA on all three DSP cores

•• Enables high-performance

transmit chip-rate processing

•• Enables high-performance RACH

preamble detection solution

• Industry-leading 65-nm silicon

technology

•• Enables a high level of functional

integration on a single device

•• Enables a high-channel-density

solution

• Software-programmable resources

•• Enables the reuse of MIPS and

memory resources on the DSP for

various types of functionality

• Standard interfaces

•• SGMII Gigabit Ethernet, DDR2,

two serial RapidIO (SRIO) links,

McBSP, I2C, GPIO

• Debug interface

•• EMU/trace

• Antenna interfaces

•• OBSAI and CPRI standards-

compliant antenna interface

Advanced Features

Supported/Enabled

•MIMO

• Fixed and adaptive beamforming

(on both uplink and downlink)

• Parallel interference cancellation

Network Interface

• 10/100/1000 Ethernet (SGMII)

Interdevice Communication

• SRIO—Two 1x lanes at a rate of

1.25, 2.5 or 3.125 Gbps each

• SRIO daisy chain capability

between TCI6487 DSPs

•• Multiple TCI6487 DSPs on a

card can be interconnected via

an SRIO daisy chain

•• Hardware packet-forwarding

mechanism supports passing

data through the daisy chain to

a specific TCI6487 DSP

• McBSP—Two McBSP links, each

at 100 Mbps

• McBSP can be used for multichannel clocked serial

communications

•I

2

C—One I2C link at 400 kbps

•I

2

C can be used for communication links between integrated

circuits or for peripheral devices

on an embedded system

Memory Interface

• DDR2-400 to DDR2-667 support

TCI6487 DSP Applications

The TCI6487 DSP offers a very highdensity “all-DSP” SOC baseband

solution that is easily scalable for pico,

micro and macro BTS applications for

multiple standards.

General Characteristics

• Supports pico to macro via the

TCI6487 scalable architecture

• Supports various radio topologies

including:

••

TD-SCDMA, WiMAX, cdma2000

and UMTS Tx

•• ASIC-plus-DSP implementations

for UMTS

• Code compatible with C64x and

C64x+ platforms

TD-SCDMA Solution

• Support for TD-SCDMA chip rate and

symbol rate (baseband on chip)

• Up to 3 carriers/69 users with SCJD

per device

• Up to 2 carriers with MCJD per

device

WiMAX (802.16e) Solution

• Supports implementation of

software-based (Tx/Rx) modems

• 3 sectors (5 MHz) or 1 sector (10 MHz)

per device

GSM Solution

• High-density BTS baseband on a chip

• 10 EDGE-enabled carriers (all soft)

cdma2000 Solution

• Complete baseband on a chip

• 144 users (macro)

UMTS Macro BTS—Tx Only

• 92 users per device (voice)

• Includes softer handover

Other UMTS Capabilities

• High-density RACH solution

•• 6-antenna RACH preamble

detection and 3-sector, 20-km or

6-sector, 10-km PD

• HSUPA (E-DCH)

•• 1 sector of E-DCH

• HSDPA (3 sectors)

••

Symbol rate and MAC-HS

RSA

Multiply

and

Accumulate

EFI

EFI

1-Bit I,

1-Bit Q

32-Bit I,

32-Bit Q

MIMO and

beamforming

enabled

24 antenna

streams

384 channels

DSP

Subsystem

OVSF and PN

Code Generation

Modulation

Apply Closed-Loop Gain

Apply Power-Control Gain

L2 Memory

(User Symbols)

Transmit Chip-Rate Accelerator

Using RSA

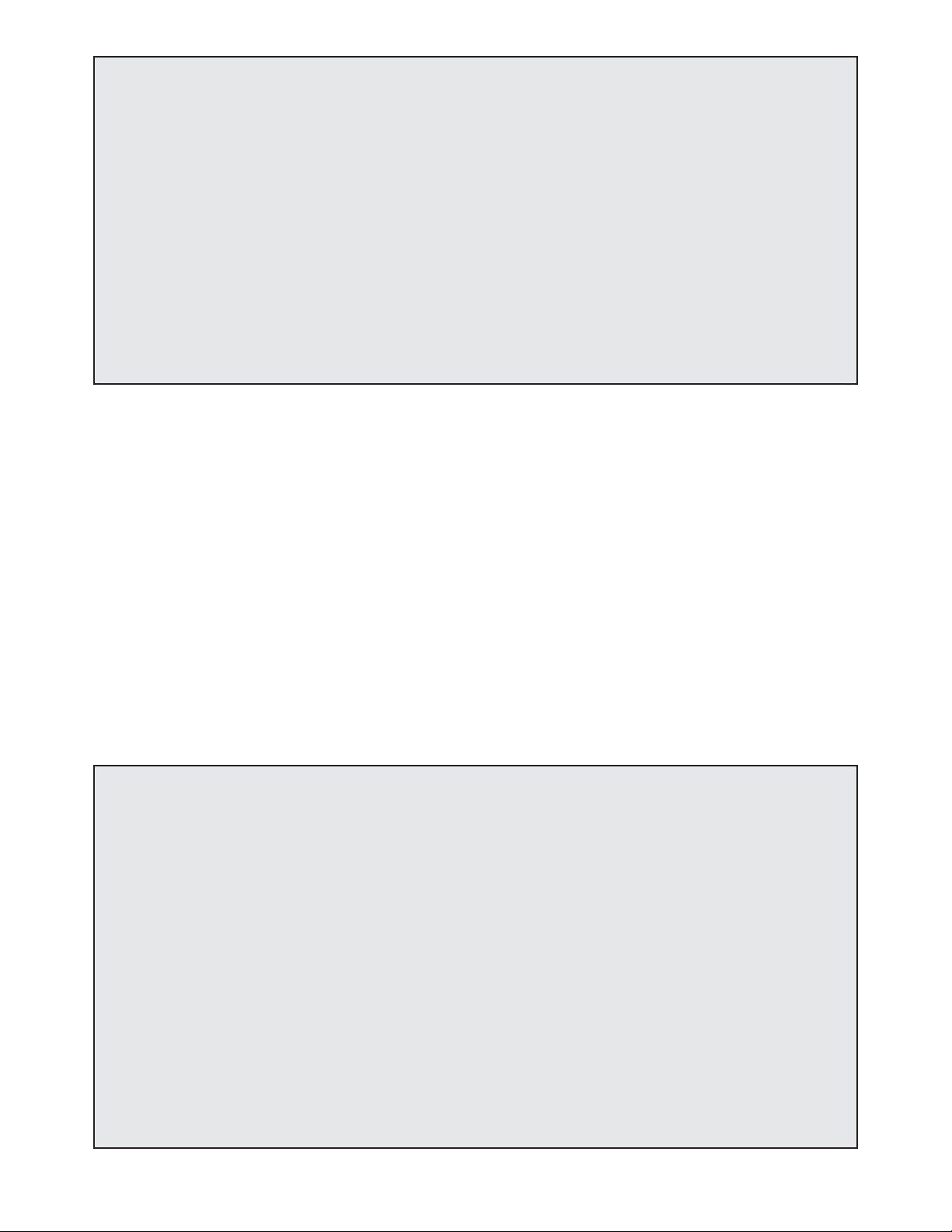

Transmit chip-rate processing is

implemented by DSP subsystem and

its associated RSA extensions. The

DSP core generates both OVSF and

PN codes and provides the multiplied result of these two codes as

input to the RSA. The modulated

user symbols are also provided as

input to the RSA. The RSA applies

the code values to the modulated

symbols to achieve spreading and

scrambling. It is also capable of

carrying out the stream aggregation

functionality.

Figure 2 shows the functional

split of transmit chip-rate processing between the DSP subsystem

and the RSA extension.

SmartReflexTMTechnology

The increased processing demands

of today’s advanced wireless networks

have also increased power consumption. To solve this problem, Texas

Instruments (TI) has implemented

a new power- and performancemanagement technology called

SmartReflex

TM

in the TCI6487 DSP.

This technology closely monitors

circuit speed and dynamically adjusts

voltages to meet exact performance

Figure 2. Transmit Chip-Rate Processing Using RSA

requirements. As a result, minimum

power is used for each operating

frequency, thereby reducing the

amount of heat produced by the

device. This provides the flexibility

to add multiple TCI6487 devices on

a single card while still meeting the

designer’s power budget.

Advanced 65-nm Platform

The TCI6487 is built on the latest

cutting-edge technology, the new

65-nm process node. This process

technology doubles the transistor

density of the previous 90-nm

process, shrinking equivalent designs

and boosting transistor performance.

This allows the TCI6487 to perform

at a level that is an order of magnitude higher than the previous

process node at a fraction of the

power consumption.

WiMAX Application

The TCI6487 is an ideal solution for

the WiMAX platform and is a natural

extension of TI’s leadership portfolio

of wireless infrastructure products.

The TCI6487 DSP plus WiMAXoptimized baseband software

provides a compelling solution for

customers. In addition, TI can provide a complete digital and analog

solution for OEMs to develop products for the WiMAX infrastructure

market. TI’s WiMAX solutions

leverage its legacy products and

future-proof new designs for other

emerging OFDMA applications.

A complete 10-MHz, 2-antenna,

3-sector solution can be implemented with only three TCI6487

DSPs where each sector can support

a full 10-MHz band with 2x2 MIMO

(see Figure 3). An SRIO switch is

added to accommodate an FPGA to

perform a CTC decoder function.

The TCI6487 improves the cost and

power per channel by accelerating

key components of baseband processing like matrix math processing.

For More Information

To learn more about the

TMS320TCI6487 DSP—or other

wireless solutions from TI—visit

www.ti.com/wi

SDRAM

SDRAM

SDRAM

Antenna

Interface

RF

Card

OBSAI/CPRI

SGMII

Switch

FPGA

CTC Decoder

DDR2

SRIO

SRIO

SRIOSRIO

SRIO

DDR2

DDR2

SRIO

Switch

MAC

Processor

TMS320TCI6487

TMS320TCI6487

TMS320TCI6487

SGMII

FPGA

Figure 3. WiMAX 10-MHz, 3-Sector Solution

SPRT405

© 2006 Texas Instruments Incorporated

Printed in U.S.A. by (Printer, City, State)

Printed on recycled paper

Technology for Innovators, the black/red banner, C64x, C64x+ and SmartReflex

are trademarks of Texas Instruments. All other trademarks are the property of

their respective owners.

TI Worldwide Technical Support

Internet

TI Semiconductor Product Information Center

Home Page

support.ti.com

TI Semiconductor KnowledgeBase Home Page

support.ti.com/sc/knowledgebase

Product Information Centers

Americas

Phone +1(972) 644-5580

Fax +1(972) 927-6377

Internet/Email support.ti.com/sc/pic/americas.htm

Europe, Middle East, and Africa

Phone

Belgium (English) +32 (0) 27 45 54 32

Finland (English) +358 (0) 9 25173948

France +33 (0) 1 30 70 11 64

Germany +49 (0) 8161 80 33 11

Israel (English) 180 949 0107

Italy 800 79 11 37

Netherlands (English) +31 (0) 546 87 95 45

Russia +7 (4) 95 98 10 701

Spain +34 902 35 40 28

Sweden (English) +46 (0) 8587 555 22

United Kingdom +44 (0) 1604 66 33 99

Fax +(49) (0) 8161 80 2045

Internet support.ti.com/sc/pic/euro.htm

Japan

Fax International +81-3-3344-5317

Domestic 0120-81-0036

Internet/Email International support.ti.com/sc/pic/japan.htm

Domestic www.tij.co.jp/pic

Asia

Phone

International +886-2-23786800

Domestic Toll-Free Number

Australia 1-800-999-084

China 800-820-8682

Hong Kong 800-96-5941

India +91-80-41381665 (Toll)

Indonesia 001-803-8861-1006

Korea 080-551-2804

Malaysia 1-800-80-3973

New Zealand 0800-446-934

Philippines 1-800-765-7404

Singapore 800-886-1028

Taiwan 0800-006800

Thailand 001-800-886-0010

Fax +886-2-2378-6808

Email tiasia@ti.com or ti-china@ti.com

Internet support.ti.com/sc/pic/asia.htm

A062706

Important Notice: The products and services of Texas Instruments

Incorporated and its subsidiaries described herein are sold subject to TI’s

standard terms and conditions of sale. Customers are advised to obtain the

most current and complete information about TI products and services

before placing orders. TI assumes no liability for applications assistance,

customer’s applications or product designs, software performance, or

infringement of patents. The publication of information regarding any other

company’s products or services does not constitute TI’s approval, warranty

or endorsement thereof.

Loading...

Loading...