Page 1

TMS320F28xx/28xxx DSCs

模拟接口设计综述

应用报告

ZHCA063–2008年5

月

摘要

本应用报告提供了一个

TMS320F28xx/28xxx

数字信号控制器的设计参考指南,主要内容有:模数转

换器的 配置、设 定 相关的 寄 存器、响 应对应的 中断和电 路 板设计参 考等。本 指导书对 于 第一次接 触

TMS320C2000™

数字信号处理器

(DSP)

,和很少使用模拟器件的软件工程师来说是很有用的。本指导书包

含了许多系统设计时需要考虑的难点问题,主要有:采样频率的设定、高效地从数字信号变换到系统数据

存储器的输入通道序列、输入驱动电路和滤波电路、电源供给和校准等。为了更好地利用数字信号控制器

(DSC)——TMS320F28xx/28xxxx

系列中的模数转换器

(ADC)

来进行设计,我们从不同文档中节选许多信息

编成方便的设计指南。相关的代码是在

F280x eZdsp™

开发板上运行的,这些代码也可以广泛作为使用此

ADC

新设计的软件框架。

在本指导书中涉及到的附属项目和源代码在下面的地址中都能下载

:

http://www-s.ti.com/sc/techlit/spraap6.zip

目录

1

简介

2

2

模数转换模块的结构和描述

3

3

模数转换器的准备和运行

4

4 F2823x和F2833x

系列的

DMA

功能和校准功能

12

5

原理图和布线设计

16

6

模数转换器的校准

18

7

附加支持

18

8

参考文献

19

附录

A F280xx和F281x

的差异

20

Pradeep Shinde

图目录

1

模数转换器简化模块图

3

2 TMS320F280xx

芯片的模数转换器引脚连接原理图

5

3

模拟输入引脚的阻抗模式

(F280xx) 5

4

典型的模数转换器输入引脚缓冲/驱动电路

6

5

模数转换器的时钟级联

8

6

连续模式下的同步和采样频率

9

7

通过

PIE

多路使用模数转换器中断

11

8

简化的硬件状态机

14

9

地址控制器

14

10

设计例子

1:

放置器件

17

11

设计例子2:走线/铺铜

17

12

模数转换器转换传递函数关系

18

表目录

A-1 F280xx 和 F281x

外设差异

20

TMS320F28xx/28xxx DSCs

模拟接口设计综述

1ZHCA063–2008年5

月

Page 2

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

2

ZHCA063–2008年5

月

简介

TMS320F28x DSC’s

具有

16-

通道,

12-

位的模数转换器,可以让设计者像使用多种嵌入式设备一样,直接把

模拟信号连接到处理芯片上。在

TMS320F28xxDSCs

上,增强型

ADC

外设具有12位分辨率,并且能获得每秒

加速到

12.5兆(MSPS)

的采样速度(一般的芯片是

6.25 MSPS和 3.75 MSPS

),并且通过流水线结构可以监控

模拟信号(如图1)。另外的特性,例如16通道的多路复用、自动定序,双采样和保持

(S/H)

电路和多路中断

表,这些都使得使用者在嵌入式控制和数据记录应用中非常方便。为了发挥外设接口的灵活性,必须正确配

置

ADC

,可以通过建立和配置不同的电路得到具体的方法。为了实现最佳性能,必须理解和设置需要的采样

比、利用自动定序器来定位通道,同时进行中断配置以读取结果。本文已经包含了利用

DSP/BIOS™

的软件核

函数(TI为

TMS320™DSP

设计的实时操作系统)的方案,此指导书也讨论了电路板设计的一些问题和系统设

计时需要注意的事项。

TMS320F281x, TMS320F280xx, TMS320F2804x

和较新的

TMS320F2832x

系列上的

ADC

外设基本上具有

相同的结构,而

F280xx和F281x

系列芯片上

ADC

的外设在规格上,具有很少不同的参数,这些在附件A中

都有详细说明。本应用报告采用

F280xx

设备的信息,利用不同的图解走查了相关的设置。附属的代码也是

针对

F280xx

芯片的,但是也可以移植到

F281x

芯片上。更多的细节可以参考

数据转换手册

(SLAA013) [1]

和

TMS320F2809,TMS320F2808,TMS320F2806,TMS320F2802,TMS320F2801,TMS320C2802

,

TMS320C2801和TMS320F2801x DSP

数据手册

(SPRS230) [2]。

如果想得到更多组件信息和寄存器细节可以

参考

TMS320x280x, 2801x, 2804x

模数转换器(

ADC

)参考指南

(SPRU716) [4],

TMS320x2833x

模数转换器

模式

(ADC) Module

(SPRU812) [18]

和

TMS320x281x DSP

模数转换器参考指南

(SPRU060) [5].

更多关于系统

控制和中断参考的信息,可以参考

缓冲运算放大器到

ADC

电路集

(SLOA098) [6]

。

如果你对

ADC

的参数和术语不是很熟悉,那么参考

数字转换器

(SLAA013) [1]

。

1

简介

Page 3

TMS320F28xx/28xxx DSCs

模拟接口设计综述

3ZHCA063–2008年5

月

www.ti.com.cn

2 Architecture and Description of ADC Module

Ch�Set�(CONV00)

Ch�Set�(CONV01)

Ch�Set�(CONV02)

Ch�Set�(CONV03)

Ch�Set�(CONV07)

State

Pointer

MAX�CONV1

Ch�Set�(CONV08)

Ch�Set�(CONV09)

Ch�Set�(CONV10)

Ch�Set�(CONV11)

Ch�Set�(CONV15)

State

Pointer

MAX�CONV2

Sequence Arbiter

12-Bit A/D

Converter

SOC EOC

S/H-A

S/H-B

MUX

Select

ADCINA0

ADCINA1

ADCINA7

MUX

Select

ADCINB0

ADCINB1

ADCINB7

4

SOC1 EOC1

44

Note:�Possible�values:

Channel�Select�=�0-15

MAX�CONV1�=�0-7

MAX�CONV2�=�0-7

Software

ePWM_SOC_A

External�Pin

(XINT2_ADCSOC)

Start-of-sequence

Trigger

SEQ1 SEQ2

SOC2 EOC2

MUX

12

ADCRESULT0

ADCRESULT1

ADCRESULT7

12

Result

Select

Result

MUX

ADCRESULT8

ADCRESULT9

ADCRESULT15

12

Result

Select

Result

MUX

12

12

Software

ePWM_SOC_B

Start-of-sequence

Trigger

ADC�start�of�conversion�(SOC)�trigger�sources

4

Analog�MUX

www.ti.com

Architecture and Description of ADC Module

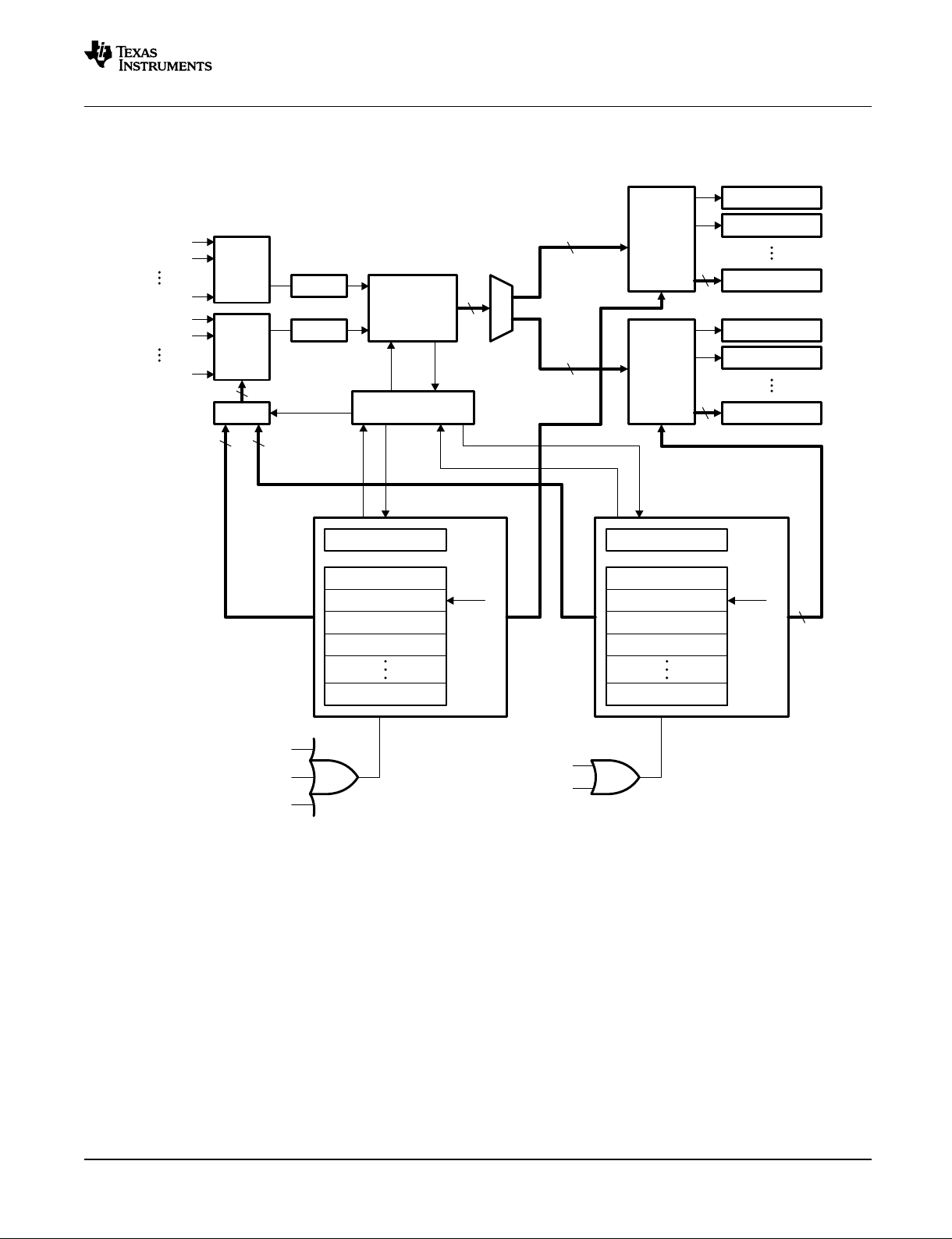

Figure 1 illustrates a simplified block diagram of the ADC architecture.

2

模数转换器模块的结构和描述

图1 显示了

ADC

结构的精简模块图

图

1. ADC

结构的精简模块图

2.1

主要模块和它们的功能

两个8通道的多路复用器(A和B)扩展了模拟输入到16位通道,每一个

MUX

模块都有它自己的采样保值电路

(S/

H-A和S/H-B)

,这种双

MUX和S/H

使同时采样成为可能,例如,从A和B模块的每一个通道在同一个实体中采

样,读取电压和电流值,然后计算出瞬时功率。

12

位的

ADC

核是模数转换器的

管路

。序列发生器仲裁保持输入信号与

ADC

相接,包括在同步模式下。

双自动序列发生器

(SEQ1和SEQ2 )

可以随机选择序列,决定哪一个

ADC

通道和

ADC

的核相连接,这样就减少

了重复

ADC

操作带来的

CPU

过热问题。每8个状态的序列发生器在预订的程序单独转换成8个通道,并且序列

发生器1和序列发生器2可以级联形成单16通道的序列发生器。

模数转换模块的结构和描述

Page 4

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

4

ZHCA063–2008年5

月

可以利用

ADCMAXCONV

寄存器设置每个序列的转换数目(每个序列发生器上限是8个,如果级联的就是

16

)。图1显示了四个不同的外置信号,它们可以作为序列发生器

1(SEQ1)

的开始转换

(SOC)

的触发器,也可

以利用软件或脉冲宽度调制

(PWM)

设置序列发生器

2(SEQ2)

的触发器。

该模块有16个结果寄存器

(ADCRESULT0 – ADCRESULT15)

,这些寄存器在开始转换成系统存储之前,保存

着模数转换器的计数,任何输入通道

(ADCINxx)

,在序列里都可能被分配给每一次转换,这样就可以很方便

重复或者跳过任何通道和通道数在

ADCRESULTn

寄存器中的序列。

每一个序列的结束

(EOS)

都会产生三个不同的中断信号

ADCINT,SEQ1INT和SEQ2INT

,这些中断信号可以

把从结果寄存器中的数据转移到系统存储器中。有关

ADC

的操作的中断服务程序

(ISR)

只有

CPU

可以干涉,

这样在完成转换中就减少了

CPU

的消耗。更多的有关自动转换序列的细节,可以参考

TMS320x280x, 2801x,

2804x DSP

模数转换器参考指南

(SPRU716) [4]

和

TMS320x281x DSP

模数转换器参考指南

(SPRU060) [5].

关键说明

在进行设置之前,首先要审查一下说明,必须确保你对这些数据转换的术语比较熟悉,在这个简短关键要注

意的是,采样频率和输入模拟信号的范围,增益和偏离误差是下一阶段要考虑的重要参数,必须对它们进行

有效地处理才能使系统正常。

在

F280x/F280xx

芯片上的最大采样频率是

12.5/6.25/3.75 MSPS 而F281x

芯片为

12.5 MSPS

。

在

F280x/F2801x

芯片上最大模数转换器的时钟为

25/12.5/6.25 MHz

而在

F281x

芯片上为

25 MHz

输入信号的范围是

0 V to 3.0 V

,偏移误差和增益误差与其它的模数转换器一样。

更多的细节 可 以 参 考 其它详细说明,或参 考 下 列 芯 片的电气部分:

TMS320F2 8 0 9 , TMS320F280 8 ,

TMS320F2806, TMS320F2802, TMS320F2801, TMS320C2802, TMS320C2801, 和TMS320F2801x

DSPs

数据手册

(SPR S230) [2],

TMS3 2 0F2810,T M S320F28 11, T MS320F 2 812 , TMS 3 20C2810,

TMS320C2811,TMS320C2812

数字信号处理数据手册

(SPRS174) [3]

和

TMS320F28335, TMS320F28334,

TMS320F28332, TMS320F28235, TMS320F28234, TMS320F28232

数字信号控制数据手册

(SPRS439) [19].

•

•

•

2.2

硬件设置

在

ADC

硬件设计方面,有两个主要的方面:

为了实现

ADC

的一定功能,添加的无源器件。

处理模拟输入信号的电路。在第5部分有许多有关完成原理图和电路板设计的内容

•

•

3.1

ADC

的设定和操作

在这一部分将要讨论设计问题。在硬件方面,需要考虑的是外围被动器件,也就是为了实现一些功能而添加

的器件,同样为实现功能的模拟输入信号与

ADC

输入引脚相连接的问题也是非常重要的。电源供电和外部参

考电压在

3.2.2

部分讨论。

3

模数转换器的准备和运行

Page 5

TMS320F28xx/28xxx DSCs

模拟接口设计综述

5ZHCA063–2008年5

月

www.ti.com.cn

3.1.1 Required External Components for the ADC

ADCINA[7:0]

ADCINB[7:0]

ADCLO

ADCREFIN

ADCRESEXT

ADCREFP

ADCREFM

V

DD1A18

V

DD2A18

V

SS1AGND

V

SS2AGND

V

DDA2

V

SSA2

V

DDAIO

V

SSAIO

Analog�Input�0�V�to�3�V�with�respect�to ADCLO

Connect�to�analog�ground

Float�or�ground�if�internal�reference�is�used

2.2�µF

(A)

2.2�µF

(A)

22�K�

ADC Analog�Power�Pin�(1.8�V)

ADC Analog�Power�Pin�(1.8�V)

ADCREFP and ADCREFM

should�not�be�loaded�by

external�circuitry

ADC Analog�Ground�Pin

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�I/O�Ground�Pin

ADC�16-Channel

Analog�Inputs

ADC�External�Current

Bias�Resistor

ADC�Reference�Positive�Output

ADC�Reference�Medium�Output

ADC�Power

ADC Analog�and

Reference�I/O�Power

3.1.2 Analog Input Signal Interface

Source

Signal

AC

R

8

ADCIN0

C

10�pF

p

R

1�k

on

�

C

1.64�pF

h

28x�DSP

Switch

www.ti.com

ADC Set-Up and Operation

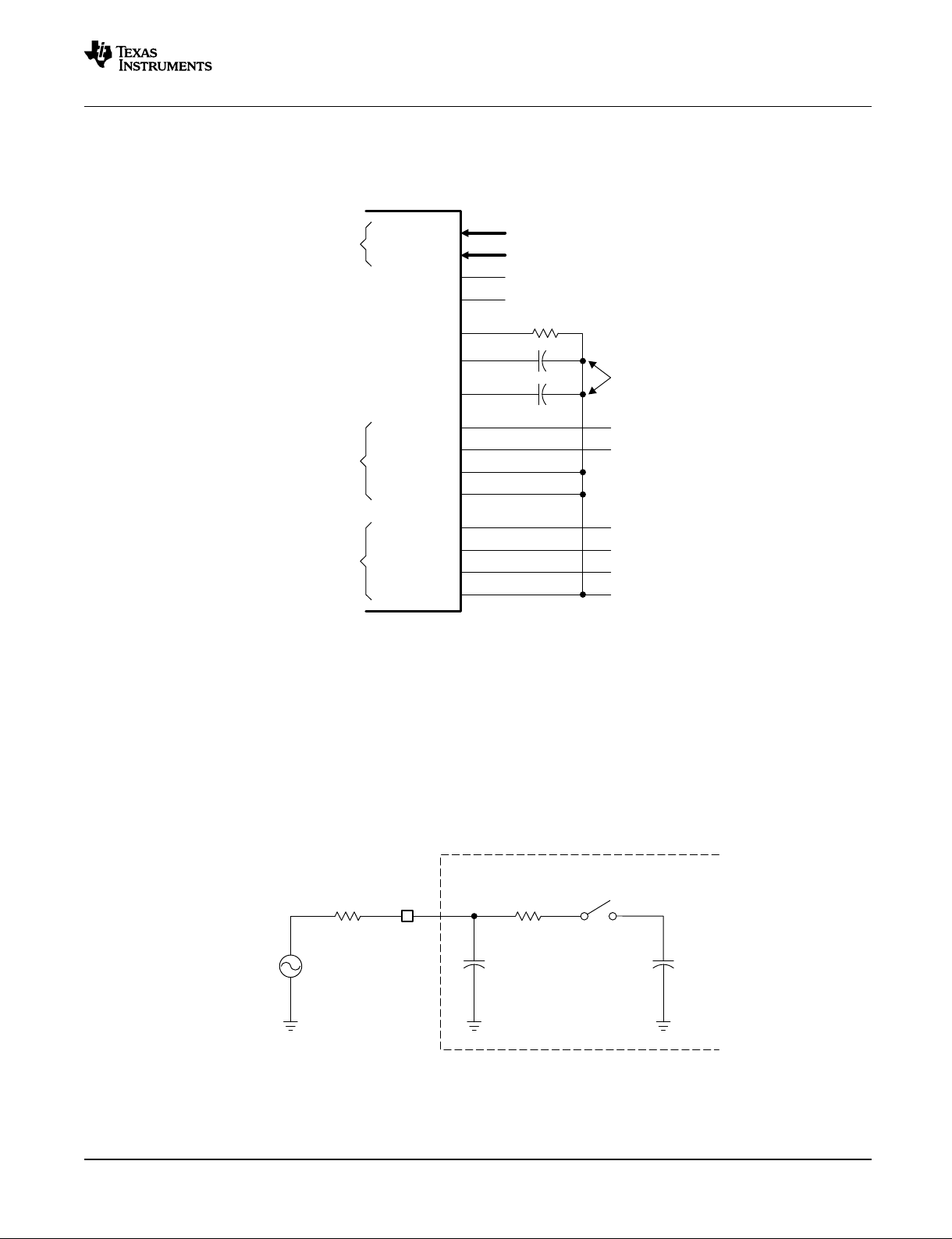

Few external components are required for biasing of internal band gap reference and filtering noise on

reference voltage signals. Figure 2, reproduced from F280xx data sheets, shows these parts and their

connections.

Figure 2. ADC Pin Connections for TMS320F280xx

These pins must be connected as shown above. The F281x devices require different values for these

parts (Appendix A).

The next step is to design the hardware interface connecting the input analog signals to the ADCINxx

pins. Note that each input analog signal sees the load from the ADCIN pin as shown in Figure 3. Chis the

sample capacitor and Ronis the ON resistance of the multiplexer path. Cpis the parasitic capacitance

associated with the ADCIN pin.

3.1.1 Required External Components for the ADC

ADCINA[7:0]

ADCINB[7:0]

ADCLO

ADCREFIN

ADCRESEXT

ADCREFP

ADCREFM

V

DD1A18

V

DD2A18

V

SS1AGND

V

SS2AGND

V

DDA2

V

SSA2

V

DDAIO

V

SSAIO

Analog�Input�0�V�to�3�V�with�respect�to ADCLO

Connect�to�analog�ground

Float�or�ground�if�internal�reference�is�used

2.2�µF

(A)

2.2�µF

(A)

22�K�

ADC Analog�Power�Pin�(1.8�V)

ADC Analog�Power�Pin�(1.8�V)

ADCREFP and ADCREFM

should�not�be�loaded�by

external�circuitry

ADC Analog�Ground�Pin

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�I/O�Ground�Pin

ADC�16-Channel

Analog�Inputs

ADC�External�Current

Bias�Resistor

ADC�Reference�Positive�Output

ADC�Reference�Medium�Output

ADC�Power

ADC Analog�and

Reference�I/O�Power

www.ti.com

ADC Set-Up and Operation

Few external components are required for biasing of internal band gap reference and filtering noise on

reference voltage signals. Figure 2, reproduced from F280xx data sheets, shows these parts and their

connections.

模数转换器需要的外部器件

为了偏置内部带宽间隔的参考和实现参考电压信号的滤波,需要添加一些外部器件。图2,显示了

F280xx

数

据手册中这一部分的连接和器件。

3.1.1

图

2. TMS320F280xx

芯片的

ADC

的引脚连接

这些引脚必须按照上面图来连接,对于

F281x

芯片需要不同的值,在附件A中可以看到。

模拟信号输入接口

这一步是设计输入模拟信号和

ADCINxx

引脚连接的硬件接口,需要注意的是,每一个输入的模拟信号都被看

作是

ADCIN

引脚的负载,如图3所示,

C

h

是

采样

电容,

R

on

是多路复用的导通电阻,

C

p

是和

ADCIN

引脚连接的

寄生电容。

3.1.2

图

3.

模拟输入阻抗模型

(F280xx)

模数转换器的准备和运行

Page 6

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

6

ZHCA063–2008年5

月

_

+

V

IN

R

IN

C

IN

S1

R

SW

S2

C

SH

V

SH

V

PS

Op Amp

www.ti.com

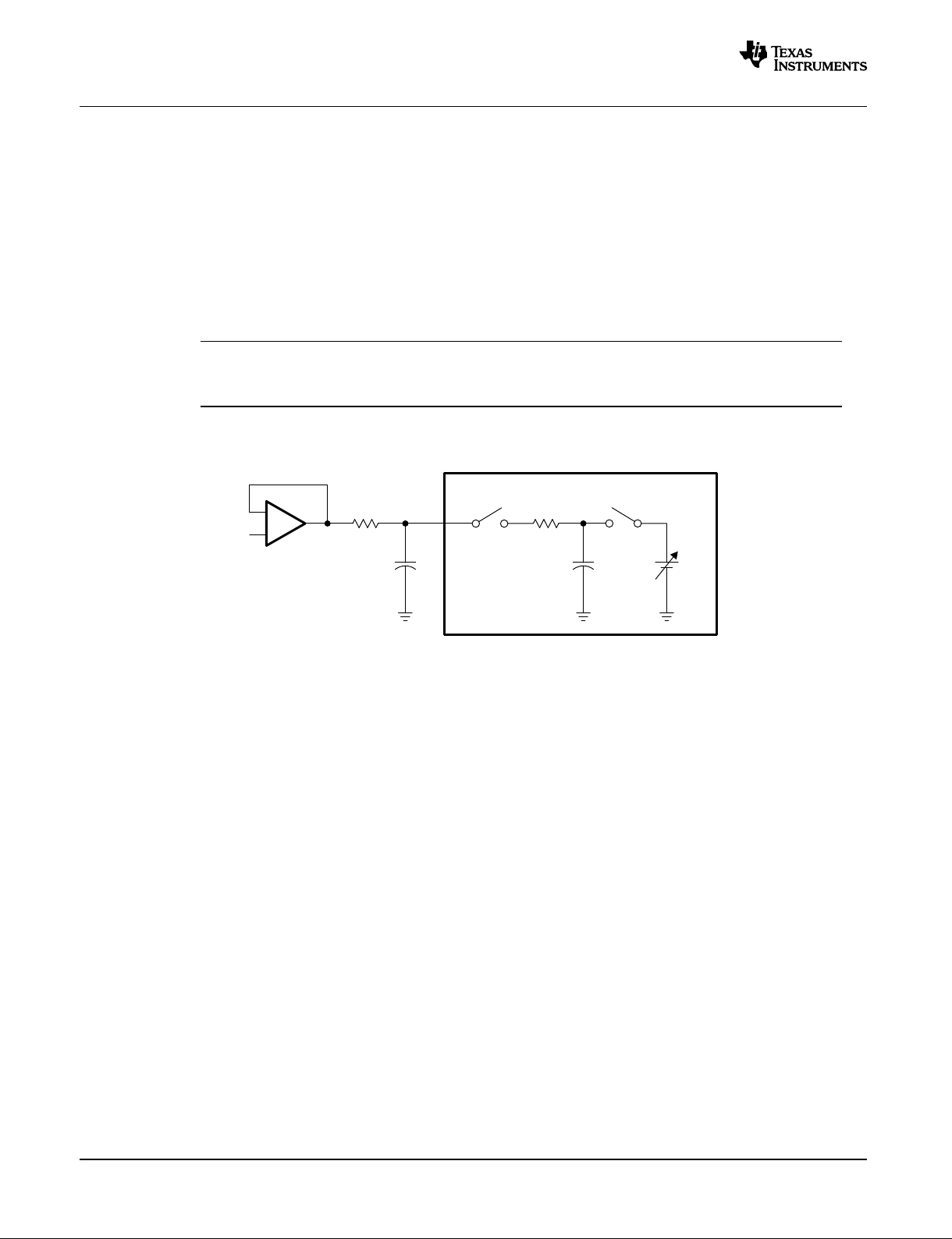

For every conversion, the S/H switch is closed for a period equivalent to (ACQ_PS + 1) × ADCCLK cycles.

During this period, the sample capacitor Chis charged to the voltage on the ADCIN pin that is connected

through MUX. The source impedance of this analog signal should be as low as possible and remain stable

when it is being sampled. The external driver and filter circuit has to be designed considering the above

circuit and component values. The higher the source impedance, the higher the ACQ_PS (sample time)

value number should be set. The goal is to charge the S/H capacitor to the voltage equal to the VINvalue;

with less than one-half least significant bit (LSB) in error.

It is a good practice to use an op-amp driver circuit for signal conditioning of input analog signals and as a

buffer. It provides low/stable output impedance and can be configured as filter or level shifter; it also

protects the ADC inputs. Figure 4 shows a commonly used ADC driver circuit configuration for DC and

low-frequency signals. The voltage range of an analog signal should be restricted between 0 V and 3.0 V.

Note: First, the analog signals travel through a multiplexer network. Any voltage out of 0 V-3.0 V

range will bias the multiplexer in an undesired way, giving incorrect values for other channels

as long as the out-of-range voltage remains.

For achieving good accuracy, the sample capacitor should be charged to within LSB of the final value.

首先模拟信号穿过多路复用网络,任何超过

0 V-3.0 V

范围的电压会产生不可想象的偏移,只要电

压值超过范围,其他通道的值就是错误的。

注释:

对每一次转换,取样/保持开关在

(ACQ_PS + 1)

×

ADCCLK

时间内是关闭的,在这段时间内,采样电容Ch在

充电,电容上的电压即

ADCIN

引脚上电压,并且这个引脚和

MUX

连接。模拟信号上的源阻抗应该尽量低并且

当开始采样的时候保持稳定。外部驱动和滤波电路必须按照上面的电路和器件的数值来进行设计。源阻抗越

高,就需要把

ACQ_PS(

采样时间)的值设置越高,目的是要改变采样/保持电容的电压和

V

IN

值相等,不过同时

会带来小于

1/2LSB

错误信号。

利用运算放大器驱动电路对输入模拟信号进行处理同时作为缓冲,是一个很好方法,它提供了低而稳定的输

出阻抗,并且可以配置成滤波器或电平移动电路,同时还可以保护

ADC

的输入。图4显示了一般针对直流、

低频信号

ADC

驱动电路的配置,模拟信号的电压范围被严格控制在0V到

3.0 V

。

为了得到准确地好的结果,采样电容应该控制在最终

LSB

值的有效范围内。

运算放大器独立于模数转换器,对采样电容来说是一个低阻抗源,可以配置成一个整体的增益缓冲。外部

R

IN

,

C

IN

引脚形成了低通滤波,独立于

ADC的R

IN

在采样期间是起放大作用的,

CIN

有助于信号的稳定。

V

PS

是上次采样值,理想情况下是零,如果反复采样的话,就可能是上次采样的值。

R

SW

是

MUX

的导通电阻,

在采集时,S1关闭,S2打开。采集电容

CSH(1.64 pF)

通过开关电阻

RSW (1 kW)和RIN (

通常不会超过

50 W)

进行

充电。充电电容按照下面的公式计算。

对于由

RSW 和C

SH

构成的RC电路来说,置位的时间是

9ns

,这个时间远远小于在

12.5MSPS

条件下的最小采样

窗口

40 ns

的时间,然而,这个时间远远大于外部的RC电路所消耗的时间。为了满足

ACQ_PS

或低采样频率,

同时满足设计时采样率的需要,置位时间应该设置为较高的值。

建议的运算放大器采用TI公司的

OPA340和OPA350

,它们由单电源供电,具有很高的精度。

_

+

V

IN

R

IN

C

IN

S1

R

SW

S2

C

SH

V

SH

V

PS

Op Amp

t

V (t) = V ( - e )

c IN

�

www.ti.com

For every conversion, the S/H switch is closed for a period equivalent to (ACQ_PS + 1) × ADCCLK cycles.

During this period, the sample capacitor Chis charged to the voltage on the ADCIN pin that is connected

through MUX. The source impedance of this analog signal should be as low as possible and remain stable

when it is being sampled. The external driver and filter circuit has to be designed considering the above

circuit and component values. The higher the source impedance, the higher the ACQ_PS (sample time)

value number should be set. The goal is to charge the S/H capacitor to the voltage equal to the VINvalue;

with less than one-half least significant bit (LSB) in error.

It is a good practice to use an op-amp driver circuit for signal conditioning of input analog signals and as a

buffer. It provides low/stable output impedance and can be configured as filter or level shifter; it also

protects the ADC inputs. Figure 4 shows a commonly used ADC driver circuit configuration for DC and

low-frequency signals. The voltage range of an analog signal should be restricted between 0 V and 3.0 V.

Note: First, the analog signals travel through a multiplexer network. Any voltage out of 0 V-3.0 V

range will bias the multiplexer in an undesired way, giving incorrect values for other channels

as long as the out-of-range voltage remains.

For achieving good accuracy, the sample capacitor should be charged to within LSB of the final value.

Figure 4. Typical Buffer/Driver Circuit for ADCIN

The op-amp isolates the ADC and acts as a low-impedance source to charge the sample capacitor; it can

be configured as a unity gain buffer. External RINand CINform a low-pass filter. RINisolates the ADC from

the amplifier during sampling; CINhelps in signal stability.

VPSis the residue from a previous sample. Ideally it would be zero, but if you are sampling back-to-back, it

approaches the previously sampled value. RSWis the on-resistance of MUX. During acquisition, S1 is

closed, S2 is open. The sampling capacitor CSH(1.64 pF) is charged through the switch resistor R

SW

(1 kΩ) and RIN(should not exceed 50 Ω, typically). The action of charging the capacitor is shown in

following equation.

软件设置

首先要按照系统的需要,设置

ADC

的相关配置,包括采样频率、选取输入序列通道和

ADC

中断管理等。上述

操作需要通过一些寄存器来设置,附件的代码文件包含了完整的设定程序。

3.2

图

4. ADCIN

典型的缓冲/驱动电路

模数转换器的准备和运行

Page 7

TMS320F28xx/28xxx DSCs

模拟接口设计综述

7ZHCA063–2008年5

月

www.ti.com.cn

设置

ADC

寄存器

最基础的设置是采样速率、选择/设置自动序列、选择采样的模式、选择开始转换信号和设置序列发生器的通

道。例如第16位结果寄存器存有这样一个值,目的是为了使输入通道按照你想要的顺序,同时为了记住每个

序列需要转换的数量。这一部分讨论了如何设置这些参数,解释了

EOS

的中断,这些中断是为了

CPU

以最小

的代价同步把

ADC

计数从结果寄存器中传到系统数据存储器

(RAM)

中。

ADC

的操作是在后台执行,没有消耗

任何

CPU

,主要是因为自动时钟的功能。如果想得到更详细的

ADC

外设寄存器的信息可以参考

F281x

芯片的

TMS320x281x DSP

模数转换器

(ADC)

参考指南

(SPRU060) [5]

和针对

F280xx

芯片的

TMS320x280x, 2801x,

2804x

模数转换器参考指南

(ADC) (SPRU716) [4]

。

3.2.1

ADC

上电和参考电压的选择

在所有的

F28xx/F28xxx

芯片的复位时,

ADC

内部带隙和参考电路都处于电源关闭状态。

ADC

模块的时钟输入是无效的。带隙是参考电路和模数转换器可以一起上电,在关闭时,可以同时关掉。然

而,对

F281x

芯片,带隙参考需要首先上电,紧接着是

ADC

复位上电。

内部带隙参考电压的电路有百万分之

50 (PPM)/

℃的温度稳定性。如果系统需要更精确的温度变化时,则需要

采用具有很大温度稳定性的外部电压参考源。外部电压参考源电路在转换期间提供了足够的驱动和低噪声环

境,典型的原理图在

TMS320x281x DSP

模数转换器参考指南

(

SPRU060) [5]

,中可以看到。

模数转换器的上电顺序如下:

1.

使能模数转换器时钟。设置

PCLKCR1

寄存器的

ADCENCLK位= 1

。

2.

如果需要,设置外部

V

REF

。

对于

F280xx

设备,

ADCREFIN

输入电压

(1.024 V, 1.500 V, 或 2.048 V)

代替了内部BG电压。内部BG电压是用来

产生

REFP/REFM

信号,在模数转换器转换期间要使用到。

ADCREFSEL

寄存器的两个

REF_SEL

位的值设置如下

:

= 00

内部参考电压(默认

)

= 01

外部参考电压

2.048 V

= 10

外部参考电压

1.500 V

= 11

外部参考电压

1.024 V

F281x

设备:让

EXTREF (ADCCTRL3) = 1

逻辑上不连接

REFP/REFM

,用户可使用外部参考电压。如果

ADCREFP

引脚接

2.0 V,ADCREFM

引脚接

1.0 V, ADCREFP – ADCREFM

之间的电势差应该是

1.00 ± 0.01 V

。

3.2.2

对于

F280xx和F281x

芯片,不管外部参考电压是多少,

ADC

模拟输入的电压范围仍然是

0 V to 3 V

注释:

在

ADC

上电之后,对

F280xx

芯片允许有

5 ms延时 (对F281x

芯片有

10 ms延时)

,这样以便于

REFP

和

REFN

引脚上的外部电容在适当时充电,在这段期间

ADC

的计数是不准确的。

注释:

3. 给ADC

上电,需要设置

ADCTRL3

寄存器中的

ADCBGRFDN和ADCPWDN位= 1

。

模数转换器的准备和运行

Page 8

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

8

ZHCA063–2008年5

月

3.2.3 Setting the ADC Clock Frequency and Sampling Rate

No�PLL

PLL

HISPCP

HSPCLK

ADCENCLK

PCLKCR[3]

ADCLKPS

CPS

ADC�CLK

ACQ_PS

SH

Clock/

Pulse

XCLKIN

ADC Set-Up and Operation

www.ti.com

With up to 16 analog input signals, the sampling rate can be decided based on the signal with the highest

frequency per the Nyquist theory or any other system-level considerations. The parameters used in the

sample rate calculations are the ADC clock and the sample time (acquisition) window. Also, setting of the

sampling mode (simultaneous or sequential) affects the sample rate, due to specific architecture. Note that

the sampling/acquisition period has a consideration of the drive circuit behind the ADC input pin. A wider

window period helps to cancel the effect of variation in source impedance.

Figure 5 shows the blocks which derive the ADC clock and sample pulse.

设置模数转换器的时钟频率和采样频率

如果是16上限的模拟信号输入,采样频率主要是根据信号中由奈奎斯特理论决定的最高频率或者是其它系

统级的需要而定,在采样率计算中要使用的参数有:

ADC

的时钟和采样时间窗口。采样模式(同步或者是顺

序)的设定影响采样率,主要是因为具体的相关结构。需要注意的是在采样期间需要考虑

ADC

输入引脚的驱

动电路,一个宽窗口时间有助于降低源阻抗变化的影响。图5显示了驱动模数转换器的时钟和采样脉冲的时

钟。

3.2.3

图

5. ADC

时钟级联

模数转换器的

CLK

决定了基本的转换时间,下面是如何设置期望值的例子

:

ADC

时钟

:

PLCCR

寄存器组的

DIV[3:0]

位设置了

XCLKIN

的乘法器。最高的

SYS

时钟是

XCLKIN × 5 (对F281x/F2823x/

F2833x

芯片是

150 MHz

,对

F280x

芯片是

100 MHz

而对

F2801x

芯片是

60 MHz)

。

高速外设时钟寄存器

(HISPCP)

组的高速外设时钟

(HSPCLK)

位,为

SYSCLKOUT(CPU

时钟)设置分频而得到

HSPCLK

,需要注意的是

F281x

系列产生的

PWM

外设利用

HSPCLK

信号作为它的时钟源,因此,下游的时

钟分频器被用来正确地设置

ADC

的时钟,而对

F280xx

芯片则不是这样。

ADCTRL3

寄存器的

ADCCLKPS和ADCTRL1

寄存器的

CPS

,为

HSPCLK

得到最终的

ADC

时钟频率提供了分

频。

设置

PCLKCR0

寄存器的

ADC

的时钟使能位

(ADCENCLK)

等于1。

设置

ADC

时钟小于或等于最大值。对于

F281x

设备是

25 MHz

,对于

F280xx

设备是

12.5/6.25 MHz

。

紧接着,选定

取样窗口

,对

S/H

电路来说就是采样时间。

ADCTRL1

寄存器的

ACQ_PS

位定义了这个时间为

(1+Acqps)* t

c(ADCCLK)

。最后的采样率是采样时间、采样模数(顺序或同步)和

ADC

时钟的总和。

图6显示了顺序采样的时间顺序,时间图是下列芯片的电气部分的节选

:

TMS320F2809, TMS320F2808,

TMS320F2806, TMS320F2802,TMS320F2801, TMS320C2802, TMS320C2801, and TMS320F2801x DSPs

数据手册

(SPRS230) [2]

,

TMS320F2810, TMS320F2811, TMS320F2812,TMS320C2810, TMS320C2811,

TMS320C2812

数字信号处理数据手册

(SPRS174) [3]

,

和

TMS320F28335, TMS320F28334, TMS320F28332

,

TMS320F28235,TMS320F28234,TMS320F28232

数字信号控制数据手册

(SPRS439) [19].

这些定时器包含下列信息

:

在

2.5tc(ADCCLK)

之后首先从

SOC

触发器的

–ve

边开始,设置

S/H

脉冲为有效。

S/H

时间是

(1 + Acqps) * t

c(ADCCLK)

对顺序采样模式

:

从

S/H

脉冲的

–ve

边开始,第一个结果出现在

(1 + Acqps) * t

c(ADCCLK)

后续结果在每一次

(2 + Acqps) * t

c(ADCCLK)

出现。

•

•

•

•

•

•

•

•

-

-

模数转换器的准备和运行

Page 9

TMS320F28xx/28xxx DSCs

模拟接口设计综述

9ZHCA063–2008年5

月

www.ti.com.cn

Sample�n

Sample�n+1

Sample�n+2

Analog�Input�on

Channel Ax�or�Bx

ADC�Clock

Sample�and

Hold�SH�Pulse

SMODE�Bit

ADC�Event

Trigger�From�EV

or�Other�Sources

t

d(SH)

t

dachx_n

t

dachx_n+1

t

SH

www.ti.com

ADC Set-Up and Operation

• For the simultaneous sampling mode:

– The first result for the A0 channel appears at (4 + Acqps) * t

c(ADCCLK)

, from the –ve edge of the S/H

pulse

– The first result for the B0 channel appears at (5 + Acqps) * t

c(ADCCLK)

, from the –ve edge of the S/H

pulse

– Successive results for Ax and Bx channels appear at every (3 + Acqps) * t

c(ADCCLK)

Note: If the system design does not really demand, do not set the ADCCLK for the highest

frequency and ACQ_PS as 0 unless you have proper signal conditioning/buffer circuitry at

the ADC input. Setting lower frequency and higher acquisition time results in achieving

accurate and stable ADC counts.

对于同步采样模式

:

从

S/H

脉冲的

–ve

边开始,A0通道的第一个结果出现在

(4 + Acqps) * t

c(ADCCLK)

。

从

S/H

脉冲的

–ve

边开始,B0通道第一个结果出现在

(5 + Acqps) * t

c(ADCCLK)

。

后续的Ax和Bx通道的结果出现在

(3 + Acqps) * t

c(ADCCLK)

。

•

-

-

-

如果不是实际需要,不要把

ADCCLK

设置成为最高的频率,把

ACQ_PS

设置为0,除非在模数

转换器输入引脚具有合适的信号环境电路。为获取准确和稳定

ADC

计数,请设置低频和高的

采样时间。

注释:

同 步 采 样 模 式 的 时 序 图 看 起 来 不 尽 相 同 , 它 是 节 选 自 在 下 列 芯 片 的 电 器 部 分

:

T M S 3 2 0 F 2 8 0 9

、

TMS320F2808、 TMS320F2806、 TMS320F2802、 TMS320F2801、TMS320C2802、TMS320C2801、

TMS320F28 01x DSPs

数据手册

(S PRS230 ) [ 2]

、

TMS320F28 10、TMS320F28 11、 TMS320F 2812

TMS320C2810, TMS320C2811, TMS320C2812

数字信号处理数据手册

(SPRS174) [3]

、

TMS320F28335

、

TMS320F28334、TMS320F28332、TMS320F28235、TMS320F28234、TMS320F28232

数字信号控制器数

据手册

(DSCs)

(SPRS439) [19]

。

设置序列发生器1和序列发生器

2

下一个重要的部分是双序列发生器的设置,当上升到16位转换时,对于每一个序列开始触发器都是利用

SEQ1

和

SEQ2

自动处理的。这样的安排在所有的转换同时处于后台运行时,节省了

CPU

的开销。这两个序列可以被

设定为一个16位转换器序列(级联的),或两个每个8位的序列。任何输入引脚

(ADCINAx 和 ADCINBx)

的信

号都可以被认为是每一次转换,在序列结束

(EOS)

时,

ADCINT, SEQ1INT, 或SEQ2INT

产生中断,这个中断就

把读到得信息写到系统数据存储器中。

SEQ1/SEQ2

设置要求和相关的参数如下

:

ADCTRL1

寄存器的

SEQ_CASC

决定了双顺序

(0)

或级联的模式

(1)

。

在一个序列中,设置

ADCMAXCONV

寄存器为最大的转换数目(也就是说,

ADCMAXCONV

值是0对应1序

列,1对应2序列)。

在每次转换时

(CONVnn)

,通过设置

ADCCHSELSEQ1到ADCCHSELSEQ4

寄存器来设置

ADC

的输入通道

(ADCINAx and ADCINBx)

。

•

•

•

3.2.4

图

6.

顺序模式的时序和采样频率

模数转换器的准备和运行

Page 10

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

10

ZHCA063–2008年5

月

作为软件触发器,当

ADCTRL2的 SOC_SEQ1或SOC_SEQ2= 1

时,序列发生器将会被触发。为了把序列

开始和

PWM

或外部事件同步,可以选择有条件设置,通过

PWM

或者在

GPIO

引脚上的外部脉冲来完成。

对

PWM

触发器,

ADC SOC

使能

(SOCAEN和/或SOCBEN)

以及在这

PWM

外设的

ETSEL

寄存器内的

SOC

触

发器

(SOCASEL 和/或 SOCBSEL)

限定选择必须被设置,注意在序列中的第一通道是在

2.5

个模数时钟周期

后采样。

通过设置

ADCTRL1

寄存器

CONT_RUN

位=1,可利用

SEQ_OVRD

位来确定模数转换器继续转换通道。这

样可使模拟输出连续转换。通过设置这位=0,序列操作处于开关模式,序列在

EOS

到达时停止,在

SOC

触发时开始。

回顾和序列相关的

ADCTRL2

寄存器数据设置参数,注意到

SOC_SEQ1、SOC_SEQ2

和相关选择触发信号

开始序列位。每一个触发信号把所有的通道集转换为一个序列,然而,这些信号没有被用做所有通道或者

一个特定通道的开始信号。

•

•

•

顺序和同时采样模式

由于信号需要同时被采集(如电压和电流),应选择同时采样模式。然后,利用

S/H-A和S/H-B

的采样保持电

路,在Ax和Bx输入端的信号可以同时被采集,通道的选择是双向的,例如

A0/B0,A1/B1

等,而不是

A2/B4

或

A6/B2

等。

计数结果在

ADCRESULT0/ADCRESULT1

成双存储,同

3.3.2

部分提到过的一样,采样频率的计算依赖于选择

同时或顺序采样模式。如果想了解更多的信息,可以参考具体芯片的模数转换器的说明部分,设置

ADCTRL3

寄存器的

SMODE_SEL

位=0是选择顺序模式,相反如果选择同时模式,就设为1。

模数转换器中断和利用外部中断扩展期模块设置中断

每个转换计数的结果存在

ADCRESULTn

寄存器中,而这个寄存器是通过序列设置的。

注意计数结果是存在寄存器的

[15:4]

位中,同时这些计数结果也被存在具有数据右对齐(即

[11:0]

位)的微

ADC(0xB00)

寄存器组中。系统的主要电路在任何时候都能读入这些值,并且在每一次序列期间更新一次,一

旦在每次序列的最后通道完成转换之后,便会产生一个中断,每一次序列结束都利用中断同步把

ADC

计数从

ADCRESULTn

寄存器中转到系统存储器中。这些中断是

ADCINT, SEQ1INT和SEQ2INT

(对

F281x

设备,只是

ADCINT

中断)。它们从外设中断扩展模块(

PIE

)得到中断,这些中断从其它外设连接到

CPU

上。

3.3

3.2.5

模数转换器的准备和运行

Page 11

TMS320F28xx/28xxx DSCs

模拟接口设计综述

11ZHCA063–2008年5

月

www.ti.com.cn

(Flag)

IFR(12:1)

INT1

INT2

INT11

INT12

(Enable)

IER(12:1)

MUX

Global

Enable

INTM

1

0

CPU

(Enable)

MUX

INTx

PIEACKx

(Enable�Flag)

(Flag)

PIEIERx(8:1) PIEIFRx(3:1)

INTx.1

INTx.2

INTx.3

INTx.4

INTx.5

INTx.6

INTx.7

INTx.8

From

Peripherals

or�External

Interrupts

www.ti.com

ADC Set-Up and Operation

图

7.

通过外部中断扩展器模块设置多路模数转换中断

PIE

模块通过多路复用技术,把许多中断源糅合在一个小的中断输入集里,

ADC

中断的是通过

PIE

寄存器来设

置的。为了完备期间,下面的讲述这个过程。对

PIE

模块结构熟悉的读者可以跳过这一部分。可以参考图7中

的

PIE

结构和具体数据手册的

PIE

表,

F28xxx

芯片的每一个外设可以产生有效的多路复用中断信号。这些中断

在一个外设时钟中产生,在

CPU

模块中处理,并且在

PIE

模块中复用为具有选择/读等控制的

12 INTx

线。这些

中断分成8组,每一组都映射成12根

CPU

中断线

(INT1 to INT12)

中的一根,

96

个中断的每一个都有自己的中

断向量,并且在

RAM

模块中保存着,也可以被重写。简而言之,总共的96个中断源被减少到12个中断信号,

可以与12个与门连接(每一个是通过

PIEACKx

信号来设置的,

x = 1 至 12),CPU

模块对12个中断信号都有不

同的标识和使能,图7显示了这些外设中断控制信号和它们的逻辑电平。

模数转换器的准备和运行

Page 12

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

12

ZHCA063–2008年5

月

逐步配置

PIE

寄存器

设置中断: 在

PIE

模块中的每一个中断都可以使能/失效。当一个具体的外设设置了中断,也就是

PIEIFRx

标识寄存器为

1(PIEIFRx.y = 1)

,意味着

PIE

模式识别了这个有中断源发过来的中断信号,并且这个中中断

需要处理。其中位的设置不是手动的,当清除

PIEIFR和PIEIER

位时,需要遵循三个主要规则。在取回中

断向量处理程序的地址期间,

PIEIFR

寄存器位被清理为0,如果用户需要手工设置,只有在中断服务程序

中来清除

PIEIFR

位。

发出需要

CPU

的中断请求: 把中断请求发给

CPU

,在

PIEIERx

寄存器中的相应的位就置为1,利用这个位的

信息选择中断,紧接着是中断处理。

选择中断:对于从

PIE

组发给

CPU

的中断请求中,

PIEACKx

必须清零。如果还有其它中断的条件成立,那

么作为一个

INTx

信号传给

CPU

中断逻辑。

设置中断标志:

CPU

的中断标志被中断信号设置为1,也就是在

CPU

级别上挂起了

INTx

。当硬件中断正在

被执行时,或中断寄存器指令正在运行时,对应的

IFR

位被清零,所有的其它

IFR

位在复位时被清零。

执行

INTx

中断:为了执行

INTx

中断,把在

IER

寄存器中的对应位赋值为1。和

IFR

一样,当硬件中断在服务

时,或者当中断寄存器指令在运行时,相对应的

IER

位被清为零,在复位时,所有的

IER

位都被清为零。

设置全局使能开关为1:设置全局使能开关,

INTM为1

;主要是通过一个汇编指令。在状态寄存器中,这

是一个全局的可屏蔽中断位。如果需要更多的详细信息,可以参考

TMS320C28x DSP CPU

和指令集参考

指南

(SPRU430) [9]

。当

CPU

执行中断服务程序时,

INTM

的当前值在堆栈中保存着,返回中断时,

INTM

从堆栈中取回。

1.

2.

3.

4.

5.

6.

3.3.1

ADC

中断

这一部分主要讨论

ADC

的外设的中断。所有的三个中断

(ADCINT, SEQ1INT和SEQ2INT)

都被归为

INT1

中断,

并且利用

CPU

的中断

INT1

来处理。此外

ADC

的状态和标识寄存器继续跟踪悬挂的中断,当这些中断被启用

时,

INT_SEQ1_CLR和INT_SEQ2_CLR

位需要清零,便于为下一次中断服务,进而使下一次中断没有被漏

掉。和

PIE/CPU

中断处理模块不一样的是,在这些外设对应的中断状态寄存器中,中断标记位必须被手动清

零。如果两个

SEQ1INT、SEQ2INT

都被使用了,那么它们就都是

CPU

模块的

INT1

组。在选择模块中,只允许

它们中的一个使用

PIEIER1

使能位。例如,首先设置

PIEIER1.1=1

,允许序列1中断,一旦它被执行,打开它

并设置

PIEIER1.2 = 1

,则允许序列2中断。

3.3.2

利用

DSP/BIOS™

如果项目使用

DSP/BIOS

,那么

ADC

的基本的功能仍然一样,唯一设置差别是

ADC

中断配置的差异——它们

是利用

DSP/BIOS

工具中

DSP/BIOS

表来配置的。

3.3.3

F2823x和F2833x

系列的直接存储存取(

DMA

)和校准功能

当把

ADC

的结果从结果缓存寄存器

(ADCRESULTn)

转移到系统存储器中时,在

F2823x和F2833x

系列中会通过

添加

DMA

控制器来解决高吞吐量瓶颈的问题。也就是说,在利用序列中断进行数据采集期间,没有必要消耗

CPU

处理的周期。在处理

ADC

的数据中

,DMA

外设具有很大的帮助。

F2823x和F2833x

芯片也包含了模数偏差

修正寄存器(

ADCOFFTRIM

)(如同在第6部分在

F280x

中描述的一样)和

ADC_cal()

子程序,这些被编程写

入在TI公司的保留

OTP

存储器中。自动导入程序会自行调用

ADC_cal()

子程序,而应用程序也可以调用。

4

模数转换器的准备和运行

Page 13

TMS320F28xx/28xxx DSCs

模拟接口设计综述

13ZHCA063–2008年5

月

www.ti.com.cn

直接存储存取

DMA

外设的综述

DMA

模式是一个基于事件的原理,需要外设中断出发器来打开

DMA

的传输,总共有6个

DMA

通道并且每一

个通道为了不同的触发源被独立配置。当

DMA

传输开始或者结束时,每一通道也产生自己的

PIE

中断通知

CPU

,在了六个通道中,通道1被认为是最高的优先级,比其它的通道的优先级都高,这是

ADC

变换的最大

特点。利用通道1最高的优先级模式,确保从每一个触发器数据都被传递。

DMA

具有唯一个状态机并且紧密

连接地址控制逻辑,地址控制逻辑允许在传输期间重新安排数据块,就如同在缓冲之间处理乒乓数据一样。

一旦

ADC

(模数转换器)连接,

SEQ1INT 或SEQ2INT

信号就被设置成对任何通道的

DMA

触发源,除了

ADC

存储映射结果寄存器外,下列的存储器资源也和

DMA

总线连接:

XINTF Zones 0, 6 & 7

L4 SARAM

L5 SARAM

L6 SARAM

L7 SARAM

有关于

DMA

管道时许的附加细节,吞吐率和

DMA

状态图,可以参考

TMS320x2833x(DMA

)模式的参考指

南

(SPRUFB8) [17]

。

•

•

•

•

•

4.1

DMA

传递控制器

图8显示了一个简单的状态机流,当收到一个触发时

(SEQ1 或 2

中断),内循环传递一个数据组。这是一次传

递的最小数据量,它的大小被定义成为

BURST_SIZE

寄存器。对于

ADC

,它对应着在一个序列中一次传完的

数据数量。外部循环定义了在整个传递中,每次传递了多少个组,它的大小被定义为

16-bit TRANSFER_SIZE

寄存器。一旦每一次传递的

CPU

中断产生,并且在传递的开始和结束,通过

MODE.CHx

位来配置。这一位被

用来产生一个单通道,而不是独占

DMA

总线。

组的源地址和目的地址通过

SRC_ADDR和DST_ADDR

寄存器来保存,在组循环期间,每一个字被传递后,一

个从

BURST_STEP

寄存发出的信号值就传送给有效的

SRC/DST_ADDR

寄存器。

这个特性使得在一个传输时间内,可以把每个

ADC

通道的计数值保存在各自的目录文件中。

4.2

F2823x和F2833x

系列的

DMA

功能和校准功能

Page 14

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

14

ZHCA063–2008年5

月

Moved

“Burst_Size”

Words

?

No

Yes

Add�Burst�Step

to Address

Pointer

Read/Write�Data

Point�Where

CH1�can�Interrupt

Other�Channels

Moved

“Transfer_Size”

Bursts

?

No

Add�Transfer

Step�to Address

Pointer

Wait�for�Event

to�Start/Continue

Transfer

Point�Where�Other

Pending�Channels

are�Serviced

End�Transfer

Yes

0x0004

0x0002

Burst_Size*

*�Size�registers�are�N–1

5�Words/Burst

3�Bursts/Transfer

0x00000B00

ADDR.shadow

BURST_STEP

0x0001

0xFFFC

(–4)

Source�Registers

0x0000F000

ADDR.shadow

BURST_STEP

0x0003

0xFFF5

(–11)

Destination�Registers

CH0

CH1

CH2

CH3

CH4

CH0

CH1

CH2

CH3

CH4

CH0

CH1

CH2

CH3

CH4

ADC�Result�Registers

0x0B00

0x0B01

0x0B02

0x0B03

0x0B04

Time

CH0

0xF000

CH00xF001

CH00xF002

CH10xF003

CH10xF004

CH10xF005

CH20xF006

CH20xF007

CH20xF008

CH30xF009

CH30xF00A

CH30xF00B

CH40xF00C

CH40xF00D

CH40xF00E

L7�RAM

DMA and Calibration Functionality in F2823x and F2833x Families

www.ti.com

Figure 8. Simplified Hardware State Machine Flow

For example, if you set ADC for five conversions (from five channels) using Sequencer 1 and use DMA

triggered by SEQ1INT, then store three consecutive sequences in a data buffer:

• BURST_SIZE = 4 (5 words/burst)

• TRANSFER_SIZE = 2 (3 bursts/transfer)

By creating the address offset, using BURST_STEP and TRANSFER_STEP for source registers and

destination registers, the data can be arranged in consecutive bins as shown in Figure 9.

Moved

“Burst_Size”

Words

?

No

Yes

Add�Burst�Step

to Address

Pointer

Read/Write�Data

Point�Where

CH1�can�Interrupt

Other�Channels

Moved

“Transfer_Size”

Bursts

?

No

Add�Transfer

Step�to Address

Pointer

Wait�for�Event

to�Start/Continue

Transfer

Point�Where�Other

Pending�Channels

are�Serviced

End�Transfer

Yes

DMA and Calibration Functionality in F2823x and F2833x Families

www.ti.com

图

8.

简化的硬件状态机器流

例如,如果利用序列1为5个通道设置了

ADC

,并且利用

SEQ1INT

设置

DMA

触发器,那么就可以在数据缓冲

中连续存储三个结果:

BURST_SIZE = 4 (5字/组)

TRANSFER_SIZE = 2 (3 组/

传递

)

通过产生地址偏移,利用

BURST_STEP和TRANSFER_STEP

作为源寄存器和目的寄存器可以把数据放置在连

贯的目录文件中,如图9中所示。

•

•

图

9.

地址控制器

F2823x和F2833x

系列的

DMA

功能和校准功能

Page 15

TMS320F28xx/28xxx DSCs

模拟接口设计综述

15ZHCA063–2008年5

月

www.ti.com.cn

在每次传递之后,还有一种修改现行地址指针的方法,就是下载封装地址到现行的地址指针中,当一定数

量的组通过源/目的变换大小的寄存器完成时,地址交换也就产生了。每一个

DMA

通道包含两个交换地址指

针,

SRC_BEG_ADDR和DST_BEG_ADDR

,这两个指针允许源和目的地址相互独立交换,就像

SRC_ADDR

和

DST_ADDR

寄存器一样,在交换开始时,现行的

SRC/DST_BEG_ADDR

寄存器就从备用寄存器装载数据,当

一定数量的数组产生时,两部分交换程序就发生了。

适当的有效

SRC/DST_BEG_ADDR

寄存器,随着被包含在

SRC/DST_WRAP_STEP

寄存器的信号值而增加。

一个新的有效

SRC/DST_BEG_ADDR

寄存器被存入到一个有效的

SRC/DST_ADDR

寄存器中。

另 外 , 为 了 建 立 下 一 步 的 交 换 时 间 , 轮 询 次 数

S R C / DST _ W R A P _ C O U N T

寄 存 器 重 新 载 入

S R C /

DST_WRAP_SIZE

寄存器的值,这就允许在一个简单的传递中,通道可以被多次进行封装。由于融合前面的

第一次触发,这样还允许通道在一个简单的转换中访问多个缓冲。

DMA

包含了两个有效的和隐藏的连续地址

指针。当一个

DMA

传递开始时,隐藏的寄存器设置就从有效的寄存器地址复制过来。这就允许在

DMA

对有

效的寄存器工作时,为了下一次传递、编程时隐藏的寄存器值,在不破坏

DMA

通道执行的情况下可以执行乒

乓缓冲。封装函数允许把数据存在具有大地址的两个缓冲中,也就是说,一个在单片机内部

RAM

中,一个是

在另外的外部

RAM

中。

•

•

ADC

同步特征

当

ADC

在具有序列重写功能使能的连续转换模式下运行时,

DMA

提供了在硬件上和

ADC

序列中断同步的一种

方法。在这种模式下,

ADC

没有在每个序列最后重新设置序列指针,也就可以连续转换

ADC

通道。因为

DMA

不知道序列指针指向哪个

ADC

结果寄存器,

DMA和ADC

不同步是很可能发生的。

正因为这个原因,当

ADC

在这种模式下配置好之后,在

RESULT0

寄存器序列开始时,会产生一个事件触发

器,这样就给

DMA

提供了一个同步信号。

DMA

等待转移开始或同步信号与封装程序连接,如果没有得到同

步信号同时转移未开时,封装程序就会再一次产生同步信号。

ADC

强制运行

当外设触发器收到

DMA

信号后,

CONTROL

寄存器的

PERINTFLG

位就被设置了,当每一个通道开始时,它的

值就被清空。然而,如果在脉冲串开始并且

PERINTFLG

仍被设置,另一个来自同一个外设的触发器就已经到

来,那它的值就会丢失。这种情况可以设置

CONTROL

寄存器中

OVERFLG

位,通过强制中断,通道就产生了

PIE

中断。对于利用

DMA

来传递

ADC

数据的代码,可以参考

adc_dma

例子

C2833x/C2823x C/C++

头文件和外

设

(SPRC530) [16].

ADC

校准

F2823x和F2833x

芯片包含有

ADC_cal()

子程序, 这些子程序早已经移植到了TI公司的测试存储器中。对于

F280x

芯片附加有

ADC

的偏差寄存器。根目录

ROM

自动调用

ADC_cal()

子程序,利用特定的校准数据来初始化

ADCREFSEL和ADCOFFTRIM

寄存器。在有规律操作期间,校准程序自动进行,用户不需要做任何事情。注

意,这样可以让

ADC_cal

子程序使

ADC

达到数据手册上的所说性能规范。为了进一步降低偏差和增益误差,

需要增加在第6部分提到的校准程序,有两种不同的调用

ADC_cal()

子程序的方法,在

TMS320x2833x

模数转

换器模式的参考指南

(SPRU812) [18]

中有详细的解释。

4.2.1

4.3

4.4

F2823x和F2833x

系列的

DMA

功能和校准功能

Page 16

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

16

ZHCA063–2008年5

月

原理图和电路板的设计

为了得到需要的结果、统一地操作和把总转换偏差最小化,必须要注意原理图的设计和电路板的布线。设计

F28xx

芯片

ADC

的模式,必须以牺牲高速的数字信号作为代价。这些设计是一个个相互关联的,有一些器件

用户可能没有使用。然而,在很坏的噪声环境中,依据这些指导来操作是很好的选择。

5

从

F28xx/F28xxx ADCs

设备得到更好的电路板设计性能

任何没有使用的

ADC

的输入引脚连接到模拟地上,它们被认为是输入引脚并且

CMOS

芯片的开路引脚会从

引脚的周围得到电压噪声。确保任何数字信号引脚都不要连接到模拟地。

用在模拟转换器输入引脚上的电压应该严格限制在

0 V–3 V

,如果在任何通道上,超过了这个范围,就会

暂时影响到其他通道的转换。如果用于输入模拟信号的数字电路需要使用任何高的电压(5V)供电, 在

连接到模数转换器的输入引脚之前,推荐采用缓冲状态缩放信号使之小于

3 V

。

如果检测到直流电压高于

3.0 V

,把电阻分压器和运算放大器相连,电阻分压器直接和模数转换器的输入

引脚相连接,就打破了低电源阻抗的需求,并且会产生大的转换计数误差。

在

DSP

处理电路中,需要在和其它所有芯片连接的每一个电源引脚放置一个

0.1mF

去藕电容,并且使用

高质量的陶瓷电介质电容,这些电介质具有更好的高频性能。

任何一个所有不使用的引脚都认为是输出引脚,并且不连接它们或者设置它们为输入引脚,也可以外接一

个很大的下拉电阻(

3–10 kW

)。

把模数转换器的逻辑输出引脚连接到

V

SSA

或利用短而宽的通铺连接。

•

•

•

•

•

•

5.1

供电的参考意见

把模拟

3.3V

干线和数字

3.3V

干线分开,特别是在模拟

3.3 V

干线负载比较大时,最好是采用一个完全分开

的电源稳压器来给模拟

3.3 V

供电。

LDO

型的稳压器可以认为是转换开关。在

CPU

最高速运行时,最大耐压应该在5%之内,而且脉冲的波动

在

20 mV

以下。

分开的模拟地常被用来连接所有的模拟信号,在模拟地和数字地交叉点一般用星型连接。应该在模拟

3.3V

干线上放置一个滤波电容或在模拟稳压器上放置一个滤波电容,主要是为了确保从任何数字信号返回的电

流没有流进模拟地线路层。

推荐的上电顺序是核供电应该首先上电,紧接着是

I/O

口,然后是模拟供电。

ADC

输入引脚的输入电压应

该在模拟器件上电之后再使用。

如果使用外部参考电压,应使用稳定的

V

REF

提供电压,这样在运行期间不会由于电路板噪声或电源噪声

而引起变化,在每一个

VREF

干线上应该采用各自的运算放大器作为缓冲级。在每一个参考线上,应设

置

1 nF和10 mF

低共振电容,目的是为了避免干扰不要和任何信号连接。一个典型的原理图在可以参考

TMS320x281x DSP

模数转换器参考指南

(SPRU060) [5]

。

•

•

•

•

•

5.2

原理图和布线设计

Page 17

TMS320F28xx/28xxx DSCs

模拟接口设计综述

17ZHCA063–2008年5

月

www.ti.com.cn

5.3 Board Layout

www.ti.com

Schematic and Board Design

The expected performance can be achieved only with a good board layout. There are many books,

application reports, and documents describing the best practices. A few of the recommendations are

shown below.

• Place all the external components close to the ADC-related pins. Particular care should be taken to

place the components for external reference voltage close to the ADCREFP and ADCREFM pins.

• The board layout should have no digital lines crossing, particularly if this DSP interfaces to a motor and

power electronics board. Avoid routing analog signals in the area that have switching digital activity,

like clock oscillator, data/address buses, etc.

• Use ground plane and power plane.

• Use single point and wide trace to connect analog and digital ground planes.

• Pay attention to the trace width and length for low level analog signals. Use wider tracks to minimize

inductance and reduce noise pickup.

• It is recommended that a separate ground plane be used. That keeps the ADC return paths at low

impedances. If the ground plane is not possible, using wide and short traces for ground return are

recommended. Poor ground can affect system performance in unpredictable ways, sometimes not

even indicating that poor ground problems exist.

Figure 10. Layout Example 1: Component Placement

布线

只有好的布线才能得到理想的功能,有许多书籍、应用报告和文档都描述了很好的方法。下面推荐其中一些,

把外部器件紧靠相关的

ADC

芯片引脚放置。在放置外部参考电压时,一定要靠近

ADCREFP和ADCREFM

引脚。

特别是在

DSP

接口和电动机、电器板连接时,电路板数字走线应该避免交叉。在具有数字开关有效的区

域,避免模拟回路的产生,如时钟晶振、数字/地址总线等。

使用地线层和电源层。

与模拟地层和数字地层连接时,采用利用单点、宽的通道。

低电平的模拟信号要注意走线的宽度和长度。利用宽的走线来减少电感和噪声。

推荐使用分隔的地层,目的是为了保持

ADC

的路径具有较低的电感。如果没有可能把地线层分开,可利用宽

的短的走线。差的地线层会随机影响系统的性能,有时候,一些问题就是由于地线层没有走好线而引起的。

•

•

•

•

•

•

5.3

图

10.

布线例

1:

器件放置

图

11.

布线例

2:

走线/铺铜

5.3 Board Layout

www.ti.com

Schematic and Board Design

The expected performance can be achieved only with a good board layout. There are many books,

application reports, and documents describing the best practices. A few of the recommendations are

shown below.

• Place all the external components close to the ADC-related pins. Particular care should be taken to

place the components for external reference voltage close to the ADCREFP and ADCREFM pins.

• The board layout should have no digital lines crossing, particularly if this DSP interfaces to a motor and

power electronics board. Avoid routing analog signals in the area that have switching digital activity,

like clock oscillator, data/address buses, etc.

• Use ground plane and power plane.

• Use single point and wide trace to connect analog and digital ground planes.

• Pay attention to the trace width and length for low level analog signals. Use wider tracks to minimize

inductance and reduce noise pickup.

• It is recommended that a separate ground plane be used. That keeps the ADC return paths at low

impedances. If the ground plane is not possible, using wide and short traces for ground return are

recommended. Poor ground can affect system performance in unpredictable ways, sometimes not

even indicating that poor ground problems exist.

原理图和布线设计

Page 18

www.ti.com.cn

TMS320F28xx/28xxx DSCs

模拟接口设计综述

18

ZHCA063–2008年5

月

6 ADC Calibration

Digitized�Signal

Ideal�Signal

Analog�Signal

Actual�Gain

Ideal�Gain

Offset

Controlled�by

INL/DNL Specs

ADC Calibration

www.ti.com

Like all ADCs, the inherent gain and offset errors are associated with the F28xx/F28xxx ADC. The

maximum values for both types of error for F280x/F280xx devices are ± 60 LSB. The F281x ADC has a

maximum offset error of ± 80 LSB and a maximum gain error of ± 200 LSB. The F2823x/F2833x devices

have lower error number: max offset error of ± 15 LSB and max gain error of ± 30 LSB.Figure 12

describes the impact of these errors on actual counts. Some applications may require correcting them to

improve the accuracy, (i.e., to improve the effective number of bits (ENOB)).

模数转换器校准

和其它的模数转换器一样,

F28xx/F28xxx

模数转换器具有固定的增益和偏移误差,

F280x/F280xx

这两种类型

的误差最大值是±

60 LSB

,而

F281x

模数转换器具有最大±

80 LSB

偏移误差和最大±

200 LSB

的增益误差。

F2823x/F2833x

芯片具有低的误差: 最大偏移误差是±

15 LSB

,最大增益误差是±

30 LSB

。图12描述了这

些误差对实际线路的影响。一些应用会为了提高精度而校准它们(比如提高有效位

(ENOB)

)。

6

图

12.

模数转换器转换传递函数关系

F280x、F2823x和F2833x

系列

ADC

支持通过

ADCOFFTRIM

进行偏移纠正,具有9位信号值来调整正负偏移,

在模拟信号运行时,保留了本身的模数转换器的范围。于此相反的是,在数字调整偏移时,丢失了

ADC

的输

出范围,另外在

F280xx

芯片中,偏移误差不需要外部电路来纠正。

一种基于软件标定的方法可以处理这种情况。

更详细的有关校准方法的信息可以参考

F2810, F2811, F2812

模数转换器校准

(SPRA989) [10] (对 F281x) 和

TMS320280x 、 TMS320F2801x ADC

模数转换器校准

(

SPRAAD8) [11] (for F280xx)

。这些文档也包含了相关

的代码。

附加的支持文档

这一部分将要讨论个别软件包,在开始设计和当

ADC

具有良好性能的时候,这些软件包是非常有用的。

7

关于过滤器的文档库

在数字信号处理中,一般对数字信号采用数字滤波。

下载

TMS320C28x

过滤库

- SPRC082

(http://www-s.ti.com/sc/techlit/sprc082.zip) [12]

,它针对

TMS320C28x™

芯片,提供了过滤库的代码,包括了数字滤波模式的两种类型:有限脉冲响应

(FIR)

和无限脉冲响应

(IIR)

。这

个代码的主要特点是采用了

DMA

控制器结构,这种结构在一个

CPU

周期中计算了两个信号,在压缩代码中也

具有详细的完整解释。

7.1

模数转换器的校准

Page 19

TMS320F28xx/28xxx DSCs

模拟接口设计综述

19ZHCA063–2008年5

月

www.ti.com.cn

举例的代码

一个补充的例子项目可以从下面地址得到:

下载

C281x C/C++

载头文件和外设使用例子

SPRC097

(http://

www-s.ti.com/sc/techlit/sprc097.zip) [13] (F281x

芯片),

下载

:C280x, C2801x C/C++

头文件和外设使用例子

SPRC191

(http://www-s.ti.com/sc/techlit/sprc191.zip) [14] (F280xx

芯片),

下载

: C2804x C/C++

头文件和外设

使用例子

- SPRC324

(http://www-s.ti.com/sc/techlit/sprc324.zip) [15] (F2804x

芯片

).

7.2

参考文献

数据转换的理解

(SLAA013).

TMS320F2809, TMS320F2808, TMS320F2806, TMS320F2802, TMS320F2801,

TMS320C2802,TMS320C2801和 TMS320F2801x DSPs

数据手册

(SPRS230)

TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811,TMS320C2812

数字信号

处理数据手册

(SPRS174)

TMS320x280x, 2801x, 2804x DSP

模数转换器参考指南

(SPRU716)

TMS320x281x DSP

模数转换器参考指南

(ADC)

(SPRU060)

Buffer Op Amp to ADC Circuit Collection

(SLOA098)

模数转换器术语的详细说明和性能特征

(SBAA147)

了解

TMS320F2808, F2806 and F2801

模数转换器的嵌入式控制应用

(SPRP297)

TMS320C28x DSP CPU and

指令系统集的参考手册

(SPRU430)

F2810, F2811, F2812

模数转换器校准

(SPRA989)

TMS320280x and TMS320F2801x

模数转换器校准

(SPRAAD8)

下载

TMS320C28x

滤波库

- SPRC082

(http://www-s.ti.com/sc/techlit/sprc082.zip)

下载

C281x C/C++

头文件和外设使用实例

SPRC097

(http://www-s.ti.com/sc/techlit/sprc097.zip)

下载

: C280x, C2801x C/C++

头文件和外设使用实例

SPRC191

(http://www-s.ti.com/sc/techlit/sprc097.zip)

下载

: C2804x C/C++

头文件和外设使用实例

- SPRC324

(http://www-s.ti.com/sc/techlit/sprc324.zip)

下载

: C2833x/C2823x C/C++

头文件和外设使用实例

(SPRC530)

TMS320x2833x

直接存储器存取

(DMA)

模块参考指南

(SPRUFB8)

TMS320x2833x

模数转换器

(ADC)

模块参考指南

(SPRU812)

TMS320F28335, TMS320F28334, TMS320F28332, TMS320F28235, TMS320F28234,

TMS320F28232

数字信号控制器

(DSCs)

数据手册

(SPRS439)

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

8

参考文献

Page 20

www.ti.com

Table A-1 shows the differences between the following ADC peripherals.

Table A-1. F280xx and F281x Peripheral Differences

Parameter F280x/F280xx F281x F2823x/F2833x

Maximum sampling rate 3.75 MSPS - For F2801x and 12.5 MSPS 12.5 MSPS

60 MHz F280x devices

6.25 MSPS – For F280x

12.5 MSPS – For F2809x and

F28044

Maximum ADC clock 12.5 MHz 25 MHz 25 MHz

frequency

PWM time-base Uses SYSCLKOUT (CPU clock) Uses HSPCLK which is also used by the Uses SYSCLKOUT (CPU clock)

ADC

Reference Voltage A single voltage reference of Two reference voltages: A single voltage reference of 1.024 V

1.024 V or 1.500 V or 2.048 V V

REFP

= 2 V and V

REFM

= 1 V, such or 1.500 V or 2.048 V

that ADCREFP – ADCREFM = 1 V

RefP/RefM capacitors 2.2 µF 10 µF 2.2 µF

RESETXT resistor 22 kΩ 24.9 kΩ for ADC clock between 22 k-Ω

1– 18.75 MHz

20 kΩ for ADC clock between 18.75 – 25

MHz

Overall Max gain error ± 60 LSB (with internal Ref) ± 200 LSB (with internal Ref) ± 30 LSB (with internal Ref)

± 50 LSB (with external Ref), if

ADCREFP – ADCREFM = 1 V ± .1%

Max offset error ± 60 LSB ± 80 LSB ± 15 LSB

Offset correction register OFFTRIM register available No such register OFFTRIM register available. Also

includes ADC calibration routine in

OTP memory.

Number of interrupts 3 1 3

Results registers Dual-mapped to zero wait state One set of 16 registers, holding counts in the Dual-mapped to zero wait state data

data space and right-justified field [15:4] space and right justified. They are

connected to DMA as well.

Power supply Two pins removed from 3.3-V Similar to F280x, but core supply

node to voltage is 1.9 V.

1.8 V, reducing analog power

consumption to half

附录

A F280xx和F281x

差异

在

F280xx和F281x

芯片上模数转换器模块的差异

表

A-1

现实了下列模数转换器外设的差异

A.1

A-1. F280xx 和F281x

外设的差异

Page 21

Safe Harbor Statement:

This publication may contain forward-looking statements that involve a number of risks and uncertainties. These “forwardlooking statements” are intended to qualify for the safe harbor from liability established by the Private Securities Litigation

Reform Act of 1995. These forward-looking statements generally can be identified by phrases such as TI or its management

“believes,” “expects,” “anticipates,” “foresees,” “forecasts,” “estimates” or other words or phrases of similar import.

Similarly, such statements herein that describe the company’s products, business strategy, outlook, objectives, plans,

intentions or goals also are forward-looking statements. All such forward-looking statements are subject to certain risks and

uncertainties that could cause actual results to differ materially from those in forward-looking statements. Please refer to TI’

s most recent Form 10-K for more information on the risks and uncertainties that could materially affect future results of

operations. We disclaim any intention or obligation to update any forward-looking statements as a result of developments

occurring after the date of this publication.

Trademarks:

The platform bar is a trademark of Texas Instruments. All other trademarks are

the property of their respective owners.

Real World Signal Processing, the balck/red banner, C2000, C24x, C28x, Code

Composer Studio, Excalibur, Just Plug It In graphic, MicroStar BGA, MicroStar

Junior, OHCI-Lynx, Power+ Logic, PowerPAD, SWIFT, TMS320, TMS320C2000,

TMS320C24x, TMS320C28x, TMS320C6000, TPS40K, XDS510 and XDS560

are trademarks of Texas Instruments. All other trademarks are the property of

their respective owners.

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and

other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the

latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject

to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.

Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by

government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications

using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design

and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible

or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such

use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge

and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of

TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI.

Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical

applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically

designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers

acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they

are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated

by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in

automotive applications, TI will not be responsible for any failure to meet such requirements.

IMPORTANT NOTICE

相关产品链接

:

DSP -

数字信号处理器

http:// www.ti.com.c n/dsp

电源管理

http:// www.ti.com.c n/power

放大器和线性器 件

http:// www.ti.com.c n/amplifier s

接口

http:// www.ti.com.c n/interfac e

模拟开关和多路 复用器

http:// www.ti.com.c n/analogsw itches

逻辑

http:// www.ti.com.c n/logic

RF/IF和ZigBee

®

解决方案

www.ti.com .cn/radiofre

RFID系统http:// www.ti.com.c n/rfidsys

数据转换器

http:// www.ti.com.c n/dataconv erters

时钟和计时器

http:// www.ti.com.c n/clockand timers

标准线性器件

http:// www.ti.com.c n/standardl inearde

温度传感器和监 控器

http:// www.ti.com.c n/temperat uresensors

微控制器

(MCU) h ttp://www.ti .com.cn/mi crocontrollers

相关应用链接

:

安防应用

http:// www.ti.com.c n/security

工业应用

http:// www.ti.com.c n/industri al

计算机及周边

http:// www.ti.com.c n/computer

宽带网络

http:// www.ti.com.c n/broadband

汽车电子

http:// www.ti.com.c n/automoti ve

视频和影像

http:// www.ti.com.c n/video

数字音频

http:// www.ti.com.c n/audio

通信与电信

http:// www.ti.com.c n/telecom

无线通信

http:// www.ti.com.c n/wireless

消费电子

http:// www.ti.com.c n/consumer

医疗电子

http:// www.ti.com.c n/medical

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Following are URLs where you can obtain information

on other Texas Instruments products and application

solutions:

样片及品质信息

免费样片索取

您是否正没日没夜的忙于工作而又急需一块免费的TI产品

样片?那就请立刻登录TI样片中心,马上申请吧!

数千种器件,极短的递送时间,高效的反馈速度:

8000

多种器件及各种封装类型任君选择

一周

7*24

小时网上随时申请

两个工作日内得到反馈

已经有成千上万的客户通过申请样片,优质高效地完成

了产品设计。

立即注册

my.TI

会员,申请免费样片,只需短短几天,样片

将直接寄到您所指定的地址。

http://www.ti.com.cn/freesample

电话 支持——如果您需要帮助如何选择样片器件,敬请致

电中国产品信息中心

800-820-8682

或访问

•

•

•

•

www.ti.com.cn/support www.ti.com.cn/quality

品质保证

持续不断的专 注于品质及可靠 性是

T I

对

客户承诺的一部分。

1995

年,TI的半导

体群品质系统计划开始实施。该全面的品

质系统的使用可满足并超越全球客户及业

界的需求。

TI

深愔促 进业界标准 的重要性, 并一直致力 于美国

(U. S)

及国际性自发标准的调整。作为活跃于诸多全球性的业界

协会的一员,以及TI对环境保护负有强烈的使命感,TI引

领其无铅

(lead[Pb]-free)

计划,并逐渐成为了该方向的领

导者。该计划始于上世纪80年代,旨在寻求产品的可替代

原料 ,时至今日,绝大多数的TI产品 均可提供无铅及绿色

(Green)

的封装。

如果您对“无铅”抱有任何疑问,敬请访问:

ZHCA063

Page 22

重 重 要 要 声 声 明 明

德 州 仪 器 (TI) 及 其 下 属 子 公 司 有 权 在 不 事 先 通 知 的 情 况 下 , 随 时 对 所 提 供 的 产 品 和 服 务 进 行 更 正 、 修 改 、 增 强 、 改 进 或 其 它 更 改 ,

并 有 权 随 时 中 止 提 供 任 何 产 品 和 服 务 。 客 户 在 下 订 单 前 应 获 取 最 新 的 相 关 信 息 , 并 验 证 这 些 信 息 是 否 完 整 且 是 最 新 的 。 所 有 产 品 的

销 售 都 遵 循 在 订 单 确 认 时 所 提 供 的 TI 销 售 条 款 与 条 件 。

TI 保 证 其 所 销 售 的 硬 件 产 品 的 性 能 符 合 TI 标 准 保 修 的 适 用 规 范 。 仅 在 TI 保 修 的 范 围 内 , 且 TI 认 为 有 必 要 时 才 会 使 用 测 试 或 其 它 质

量 控 制 技 术 。 除 非 政 府 做 出 了 硬 性 规 定 , 否 则 没 有 必 要 对 每 种 产 品 的 所 有 参 数 进 行 测 试 。

TI 对 应 用 帮 助 或 客 户 产 品 设 计 不 承 担 任 何 义 务 。 客 户 应 对 其 使 用 TI 组 件 的 产 品 和 应 用 自 行 负 责 。 为 尽 量 减 小 与 客 户 产 品 和 应 用 相 关

的 风 险 , 客 户 应 提 供 充 分 的 设 计 与 操 作 安 全 措 施 。

TI 不 对 任 何 TI 专 利 权 、 版 权 、 屏 蔽 作 品 权 或 其 它 与 使 用 了 TI 产 品 或 服 务 的 组 合 设 备 、 机 器 、 流 程 相 关 的 TI 知 识 产 权 中 授 予 的 直 接

或 隐 含 权 限 作 出 任 何 保 证 或 解 释 。 TI 所 发 布 的 与 第 三 方 产 品 或 服 务 有 关 的 信 息 , 不 能 构 成 从 TI 获 得 使 用 这 些 产 品 或 服 务 的 许 可 、 授

权 、 或 认 可 。 使 用 此 类 信 息 可 能 需 要 获 得 第 三 方 的 专 利 权 或 其 它 知 识 产 权 方 面 的 许 可 , 或 是

可 。

对 于

TI

的 数 据 手 册 或 数 据 表 , 仅 在 没 有 对 内 容 进 行 任 何 篡 改 且 带 有 相 关 授 权 、 条 件 、 限 制 和 声 明 的 情 况 下 才 允 许 进 行 复 制 。 在 复 制

信 息 的 过 程 中 对 内 容 的 篡 改 属 于 非 法 的 、 欺 诈 性 商 业 行 为 。

TI

对 此 类 篡 改 过 的 文 件 不 承 担 任 何 责 任 。

在 转 售 TI 产 品 或 服 务 时 , 如 果 存 在 对 产 品 或 服 务 参 数 的 虚 假 陈 述 , 则 会 失 去 相 关 TI 产 品 或 服 务 的 明 示 或 暗 示 授 权 , 且 这 是 非 法 的 、

欺 诈 性 商 业 行 为 。

可 访 问 以 下

TI

URL

地 址 以 获 取 有 关 其 它

对 此 类 虚 假 陈 述 不 承 担 任 何 责 任 。

TI

产 品 和 应 用 解 决 方 案 的 信 息 :

产 产 品 品

放大器

http://www.ti.com.cn/amplifiers

数据转换器

DSP

接 口

逻 辑

电源管理

微 控 制 器

http://www.ti.com.cn/dataconverters

http://www.ti.com.cn/dsp

http://www.ti.com.cn/interface

http://www.ti.com.cn/logic

http://www.ti.com.cn/power

http://www.ti.com.cn/microcontrollers

应 应 用 用

音 频

汽 车

宽 带

数 字 控 制

光 纤 网 络

安 全

电 话

视 频 与 成 像

无 线

http://www.ti.com.cn/audio

http://www.ti.com.cn/automotive

http://www.ti.com.cn/broadband

http://www.ti.com.cn/control

http://www.ti.com.cn/opticalnetwork

http://www.ti.com.cn/security

http://www.ti.com.cn/telecom

http://www.ti.com.cn/video

http://www.ti.com.cn/wireless

TI

的 专 利 权 或 其 它 知 识 产 权 方 面 的 许

邮 寄 地 址 : Texas

Instruments,

Post

Copyright © 2006, Texas Instruments Incorporated

Office

Box

655303,

Dallas,

Texas

75265

Loading...

Loading...