Page 1

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

1 高性能片上系统 (SoC)

1.1 特性

123

• 高性能Davinci 数字媒体处理器

– 高达 1GHz 的 ARM® Cortex™-A8 RISC MPU

– 高达 2000 ARM®Cortex™-A8 MIPS

– 高达 750MHz C674x™ VLIW DSP

– 6000 / 4500 C674x™ MIPS/ MFLOPS

– 与C67x+™、C64x+™ 具有完全的软件兼容性

• ARM® Cortex™-A8 内核

– ARMv7 架构

• 顺序 (In-Order)、双发射 (Dual-Issue)、超标

量微处理器内核

• NEON™ 多媒体架构

• 支持整数和浮点

• Jazelle® RCT 执行环境

• ARM® Cortex™-A8 内存架构

– 32k 字节指令及数据高速缓存

– 512 k 字节 L2 高速缓存

– 64k 字节 RAM、48k 字节引导 ROM

• TMS320C674x™ 浮点 VLIW DSP

– 64 个通用寄存器 (32 位)

– 6 个 ALU(32 / 40位) 功能单元

• 支持 32 位整数、SP (IEEE 单精度 / 32

位) 和 DP (IEEE 双精度 / 64 位)浮点

• 每个时钟支持多达 4 个 SP 加法,每两个时钟

支持 4 个 DP 加法

• 每个周期支持多达两个浮点 (SP 或 DP) 倒

数逼近或平方根运算

– 两个乘法功能单元

• 所支持的混合精度 IEEE 浮点乘法高达:

• C674x 两级内存架构

– 每个时钟 2 SP x SP -> SP

– 每两个时钟 2 SP x SP -> DP

– 每三个时钟 2 SP x DP -> DP

– 每四个时钟 2 DP x DP -> DP

• 定点乘法支持每个时钟周期 2个 32 x 32 位乘

法运算、4 个 16 x 16 位乘法运算 (包括复

数乘法) 或 8 个 8 x 8 位乘法运算

– 具有 EDC 的 32k 字节 L1P RAM / 高速缓存

– 32k 字节 L1D RAM / 高速缓存

– 采用 ECC 的 256k 字节 L2 统一映射 RAM / 高

ZHCS057–MARCH 2011

TMS320DM814x DaVinci™

数字媒体处理器

查询样品: TMS320DM8148, TMS320DM8147

速缓存

• DSP / EDMA 内存管理单元 (DEMMU)

– 将 C674x DSP 和 EDMA TC 内存存取映射至系

统地址

• 128k 字节片上内存控制器 (OCMC) RAM

• 成像子系统 (ISS)

– 摄像机传感器连接

• 用于素材 (高达 16 位) 及 BT.656/BT.1120

(8 / 16 位) 的并行连接

– 用于处理来自摄像机传感器的图像/视频数据的图

像传感器接口 (ISIF)

– 图像尺寸调节器 (Resizer)

• 将图像/视频尺寸从 1/16x 重设为 8x

• 同时生成两个不同的变尺寸输出

• 可编程高分辨率视频图像协处理 (HDVICP v2) 引擎

– 编码、解码、代码转换操作

– H.264、MPEG2、VC1、MPEG4、SP /

ASP、JPEG / MJPEG

• 媒体控制器

– 用于控制 HDVPSS、HDVICP2 和 ISS

• SGX530 3D 图形引擎

– 可提供高达 18 MPoly/sec 的多边形生成速率

– 通用型可扩缩渲染引擎

– 具有 Direct3D Mobile、OpenGL ES 1.1 和

2.0、OpenVG 1.0、OpenMax API支持能力

– 高级几何 DMA 驱动型操作

– 可编程 HQ 图像抗混叠处理

• 字节序 (Endianness)

– ARM / DSP 指令/数据——小端 (Little Endian)

• HD 视频处理子系统 (HDVPSS)

– 两个148.5MHz HD 视频捕获输入

• 一个 16 / 24 位输入,可拆分为两个 8 位 SD

捕获端口

• 一个8 / 16 /24 位输入

• 仅一个 8位输入

– 两个148.5MHz HD 视频显示输出

• 一个 16 / 24 / 30位输出和一个 16 / 24 位输出

– 复合或 S 视频模拟输出

– 可支持MacroVision®

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2DSP/BIOS, XDS are trademarks of Texas Instruments.

3All other trademarks are the property of their respective owners.

PRODUCT PREVIEW information concerns products in the formative

or design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right English Data Sheet: SPRS647

to change or discontinue these products without notice.

© 2011, Texas Instruments Incorporated

Page 2

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

– 数字

– 高级视频处理功能,例如:扫描/格式/速率转换 • 双控制器局域网 (DCAN) 模块

– 3 个图形层及组合器 – CAN Version 2 Part A、B

• 双 32 位 LPDDR / DDR2 / DDR3 SDRAM 接口 • 4 个集成电路间 (I2C BUS™) 端口

– 支持高达 LPDDR-400、DDR2-667 和 • 6 个多通道音频串行端口 (McASP)

– 总共有多达 8 个 x8 器件 2 GB的总地址空间

– 动态内存管理器 (DMM)

• 通用内存控制器 (GPMC)

– 8 / 16 位多路复用地址/数据总线

– 512M 字节的总地址空间在多达 8 条片选线之间

– 至 NOR 闪存、NADN 闪存 (具有 BCH / 汉明

– 位于 GPMC 外部的错误定位器模块 (ELM) 负责

– 灵活的异步协议控制,用于至

• 增强型直接存储器存取 (EDMA) 控制器

– 4 个传输控制器

– 64 / 8 个独立的 DMA / QDMA 通道

• 具有双 10/100/1000 Mbps 外部接口 (I/F) 的以太网

开关 (EMAC SW)

– 符合 IEEE 802.3 标准 (仅 3.3V I/O)

– MII / RMII / GMII / RGMII 媒体独立接口 (I/F)

– 管理数据 I/O (MDIO) 模块

– 复位隔离

– IEEE-1588 时间戳和工业以太网协议

• 具有集成型 PHY 的双 USB 2.0 端口

– USB 2.0 高速/全速客户机

– UCB 2.0 高速/全速/低速主机,或 OTG

– 支持端点 0-15

• 一个具有集成型 PHY 的 PCI Express 2.0 端口

– 具有一条 5.0 GT/s 线道的单端口

– 可配置为根联合体 (root complex) 或端点

• 8 个 32 位通用定时器 (定时器 1~8)

• 1 个系统看门狗定时器 (WDT 0)

• 6 个可配置的 UART / IrDA / CIR 模块

– 具有调制解调器控制信号的 UART0

– 支持高达 3.6864Mbps 的 UART0 / 1 / 2

– 支持高达 12Mbps 的 UART3 / 4 / 5

– SIR、MIR、FIR (4.0 MBAUD) 及CIR

• 4 个串行外设接口 (SPI) [高达 48MHz]

– 各具有 4 条片选线

• 3 个 MMC / SD / SDIO 串行接口 [高达48MHz]

HDMI 1.3 发送器 – 3 个接口支持高达1 / 4 / 8 位模式

DDR3-667 的内存

• 可编程多区内存映射及交错

• 实现了高效 2D 成组存取 (Block Accesses)

• 支持 0°、90°、180° 或 270° 取向的平铺对象

和镜像

• 优化了交错存取

进行分配

误码检测功能)、SRAM 和伪 SRAM 的无缝接

口

提供用于 NAND 的高达 16 位 / 512 字节的硬

件ECC

FPGA、CPLD、ASIC 等的接口

www.ti.com.cn

– 两个 10 通道串化器发送/接收端口

– 四个 4 通道串化器发送/接收端口

– 具有用于 S/PDIF 的 DIT 能力 (所有端口)

• 多通道缓冲串行端口 (McBSP)

– 高达 48MHz 的发送/接收时钟

– 两个时钟区和两个串行数据引脚

– 支持 TDM、I2S 及相似的格式

• 具有集成型 PHY 的串行 ATA (SATA) 3.0 Gbps 控

制器

– 至一个硬盘驱动器的直接接口

– 来自多达 32 个入口的硬件辅助本机命令排队

(NCQ)

– 支持端口乘法器和基于命令的交换

• 实时时钟 (RTC)

– 一次性或周期性中断发生

• 多达 128 个通用 I/O (GPIO) 引脚

• 一个具有 128 个硬件信号标志 (Hardware

Semaphores) 的自旋锁模块 (Spin Lock Module)

• 一个具有 12 个邮箱的邮箱模块

• 片上 ARM ROM 引导加载程序 (RBL)

• 电源、复位和时钟管理

– SmartReflex™ 技术 (Level 2b)

– 多个独立的内核电源域 (power domain)

– 多个独立的内核电压域 (voltage domain)

– 每个电压域可支持 3 个工作点 (OPP120 / 100 /

50)

– 针对子系统及外设的时钟启用/停用控制

• 用于调试的 32KB 嵌入式跟踪缓冲器 (Embedded

Trace Buffer™ [ETB™] ) 和 5 引脚跟踪接口

• 可兼容 IEEE-1149.1 (JTAG)

• 684 引脚无铅型 BGA 封装 (CYE 后缀),0.8mm

焊球间距,并采用 Via Channel™ 技术来降低PCB

成本

• 45nm CMOS 工艺技术

• 适合通用 I/O 的1.8V / 3.3V 双电压缓冲器

• 应用:

– HD 会议电视——Skype 端点

– 视频监控 DVR、IP 网络摄像机

– 数字标牌

– 媒体播放器/适配器

– 移动医疗成像

– 网络投影机

– 家用音频/视频设备

2 高性能片上系统 (SoC) 版权 © 2011, Texas Instruments Incorporated

Page 3

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

1.2 说明

TMS320DM814xDaVinci™ 数字媒体处理器是高度集成的可编程平台,它利用 TI 的DaVinci技术来满足下列

应用的处理要求:HD 会议电视——Skype 端点、视频监控DVR、IP 网络摄像机、数字标牌、媒体播放器/

适配器、移动医疗成像、网络投影机以及家用音频/视频设备,等等。

凭借全集成化混合处理器解决方案所具有的极大灵活性,该器件使得原始设备制造商 (OEM) 和原始设计制

造商 (ODM) 能够将拥有稳健的操作系统支持、丰富的用户界面以及高处理性能的设备迅速投放市场。 另

外,这款器件还将可编程视频及音频处理与高度集成的外设集 (peripheral set) 组合在了一起。

TMS320DM814x DaVinci™ 数字媒体处理器还使 OEM 和 ODM 拥有了新的处理器可扩缩性及软件重用性水

平。 对于在设计中使用 AM387x、并发现有机会制作一款具有附加功能的相似产品的 OEM 或 ODM 而言,

他们可以升级 (scale up) 为采用由德州仪器 (TI) 提供的引脚兼容和软件兼容的TMS320C6A814x 或

TMS320DM814x 处理器。 TMS320C6A814x Integra™ DSP+ARM 处理器给 AM38x 上的硬件增添了一个

强大的 C674x™ DSP 内核,而 TMS320DM814x DaVinci™ 数字媒体处理器则将一个视频编码器/解码器添

加至TMS320C6A814x 上已有的硬件。 此外,对于已经使用了AM387x、C6A814x 或 DM814x,并发现需

要速度更快的 ARM 和/或 DSP内核性能的 OEM 或 ODM 来说,他们可以升级至具有较高内核速度且软件兼

容的 AM389x、TMS320C6A816x 或 TMS320DM816x 器件。

可编程性由一个具有 Neon™ 扩展的 ARM Cortex™ A8 RISC CPU、TI C674x VLIW 浮点 DSP 内核、及高

分辨率视频/成像协处理器提供。 ARM 使得开发人员能够将控制功能与在 DSP 和协处理器上进行编程的

A/V 算法分离开来,从而降低了系统软件的复杂程度。 具有 Neon™ 浮点扩展的 ARM Cortex A8 32 位

RISC 微处理器包括: 32K 字节 (KB) 的指令高速缓存; 32KB 的数据高速缓存; 512KB 的 L2 高速缓

存;48KB 的引导 ROM;和 64KB 的 RAM。

ZHCS057–MARCH 2011

丰富的外设集提供了控制外围设备以及与外部处理器进行通信的能力。 如需了解每个外设的详细信息,请参

见本文件中的有关章节以及相关联的外设参考指南。 外设集包括:HD 视频处理子系统;具有 MII / RMII /

GMII / RGMII 和 MDIO 接口的双端口千兆位以太网 MAC (10/100/1000 Mbps),可支持 IEEE-1588 时间戳

和工业以太网协议;两个具有集成型 2.0 PHY 的 USB 端口; PCIe x1 GEN2 兼容型接口;两个10 通道串

化器 McASP 音频串行端口 (具有 DIT 模式); 4 个四通道串化器 McASP 音频串行端口 (具有 DIT 模

式);一个 McBSP 多通道缓冲串行端口;6 个可支持 IrDA 和 CIR 的 UART; 4 个 SPI 串行接口;3 个

MMC / SD / SDIO 串行接口;4 个 I2C 主/从接口;1 个并行相机接口 (CAM);多达 128 个通用 IO

(GPIO); 8 个 32 位通用定时器;系统看门狗定时器;双 LPDDR / DDR2 /DDR3 SDRAM 接口;灵活的 8 /

16位异步存储器接口;2 个控制器局域网 (DCAN) 模块; 1 个自旋锁; 邮箱;以及串行硬盘驱动器接口

(SATA 300)。

TMS320DM814x DaVinci™ 数字媒体处理器还包括一个高分辨率视频/成像协处理器 2 (HDVICP2) 和一个

SGX530 3D 图形引擎(以分担许多原本由 DSP 内核所承担的视频和成像处理任务),从而使得能够将更多

的 DSP 处理性能用于通用视频及成像算法。 此外,它还拥有一整套用于 ARM 及 DSP 的开发工具。这些

开发工具包括 C 语言编译器、用于简化程序设计和调度的 DSP 汇编优化器以及旨在将可视性引入源代码执

行的 Microsoft® Windows™ 调试程序界面。

C674x DSP 内核是 TMS320C6000™ DSP 平台中的新型高性能浮点 DSP 系列。 C674x 浮点 DSP 处理器

采用具有 EDC 的 32KB L1 程序内存和 32KB 的 L1 数据内存。 多达 32KB 的 L1P 可被配置为程序高速缓

存。 剩余的是不可高速缓存的无等待状态程序内存。 多达 32KB 的 L1P 可被配置为程序高速缓存。 剩余的

是不可高速缓存的无等待状态程序内存。 DSP 具有带 ECC 的 256KB L2 RAM,它可被规定为 SRAM、L2

高速缓存或此二者的某种组合。 所有的 C674x L3 及片存储器存取均通过一个 MMU 来选定路由。

版权 © 2011, Texas Instruments Incorporated 高性能片上系统 (SoC) 3

Page 4

PRODUCTPREVIEW

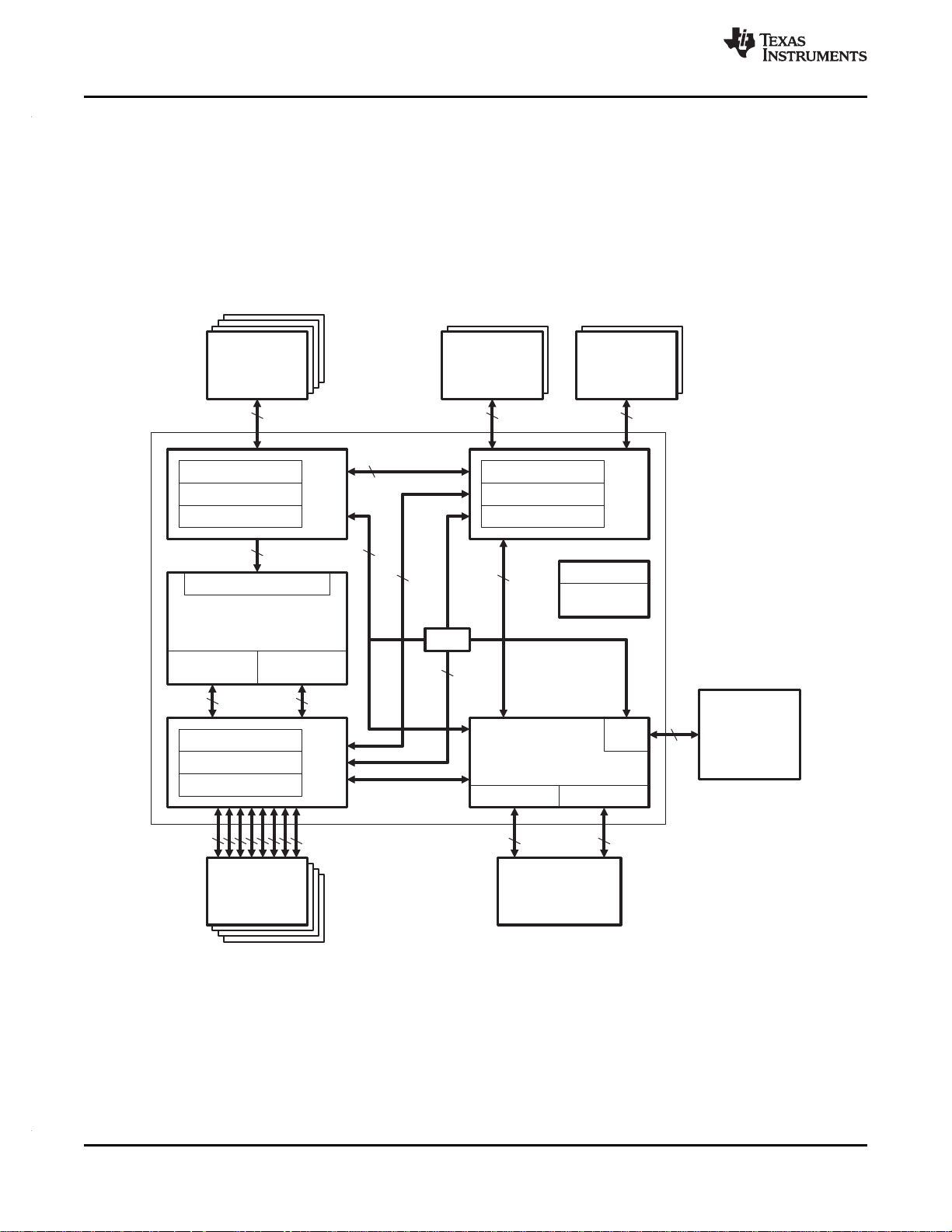

DSP Subsystem

C674x

TM

DSP CPU

32KB

L1 Pgm

32 KB

L1 Data

256 KB L2 Cache

Video Processing

Subsystem

Video Capture

Display Processing

HD OSD SD OSD

HD VENC SD VENC

HDMI Xmt

SD DACs

AET

ICE Crusher

DSP/EDMA MMU

McASP

(6)

McBSP

(m)DDR2/3

32-bit

(2)

GPMC

+

ELM

EDMA

EMAC

(R)(G)MII

(2)

MDIO

USB 2.0

Ctlr/PHY

(2)

PCIe 2.0

(One x1

Port)

UART

(6)

SPI

(4)

I

2

C

(4)

System Control

Serial Interfaces

Program/Data Storage

Connectivity

Peripherals

System Interconnect

GP Timer

(8)

Watchdog

Timer

Real-Time

Clock

PRCM

JTAG

128 KB On-Chip RAM

High Definition Video Image

Coprocessor (HDVICP)

Media Controller

Imaging

Subsystem

Parallel Cam Input

CSI2 Serial Input

IPIPE

Resizer

H3A

MMC/SD/

SDIO

(3)

DCAN

(2)

ARM Subsystem

Cortex

TM

-A8

CPU

32 KB

I-Cache

32 KB

D-Cache

256 KB L2 Cache

Boot ROM

48 KB

RAM

64 KB

NEON

FPU

Spin Lock

Mailbox

Face Detect (FD)

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

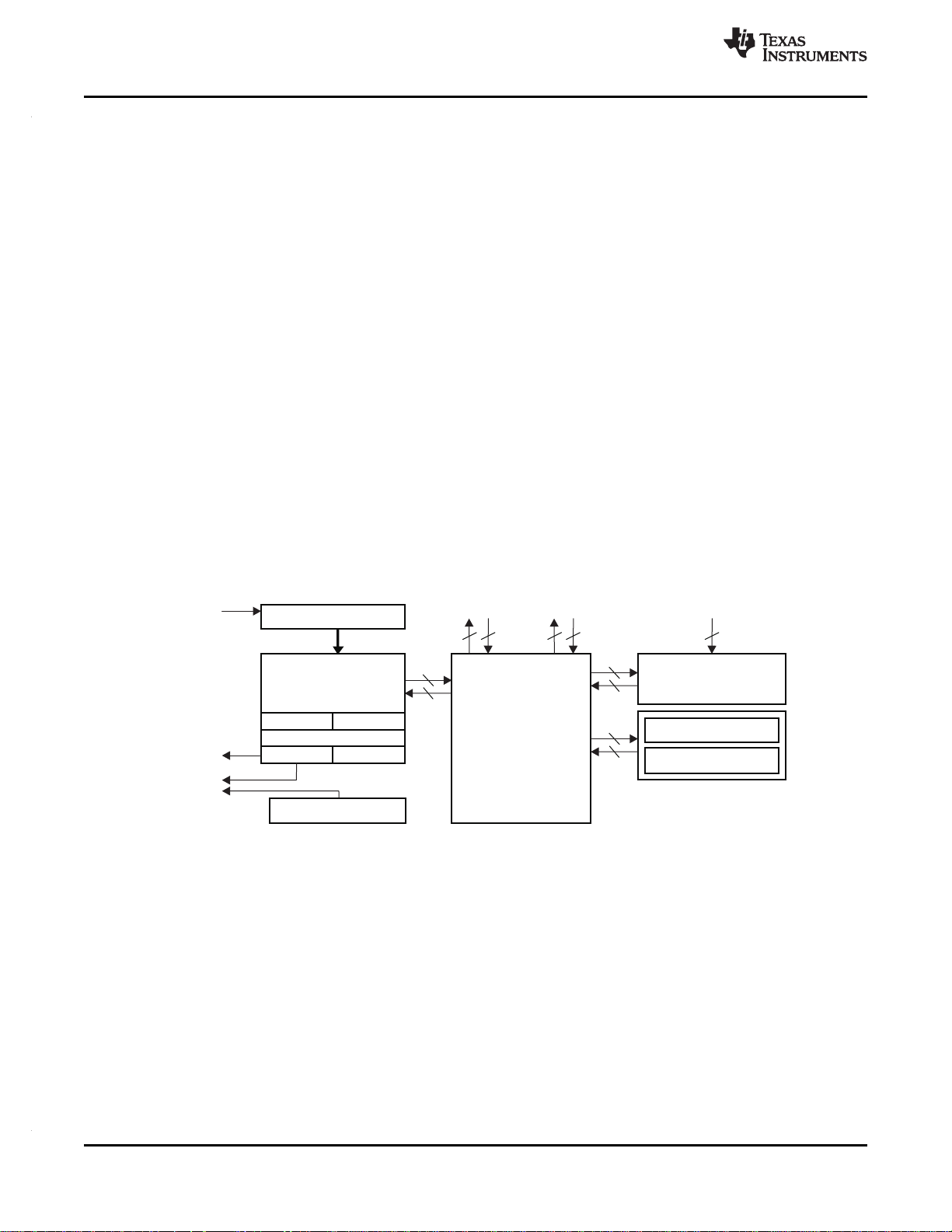

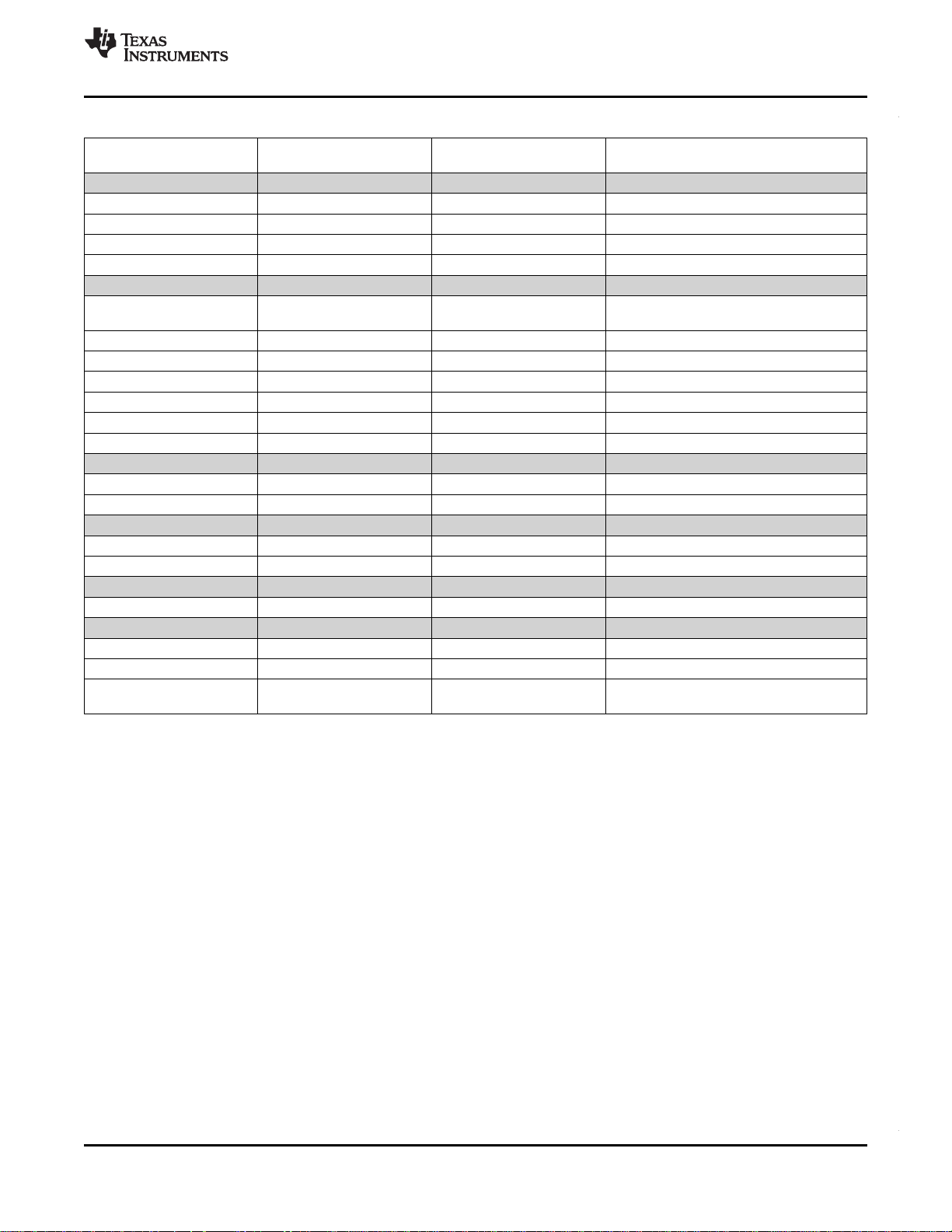

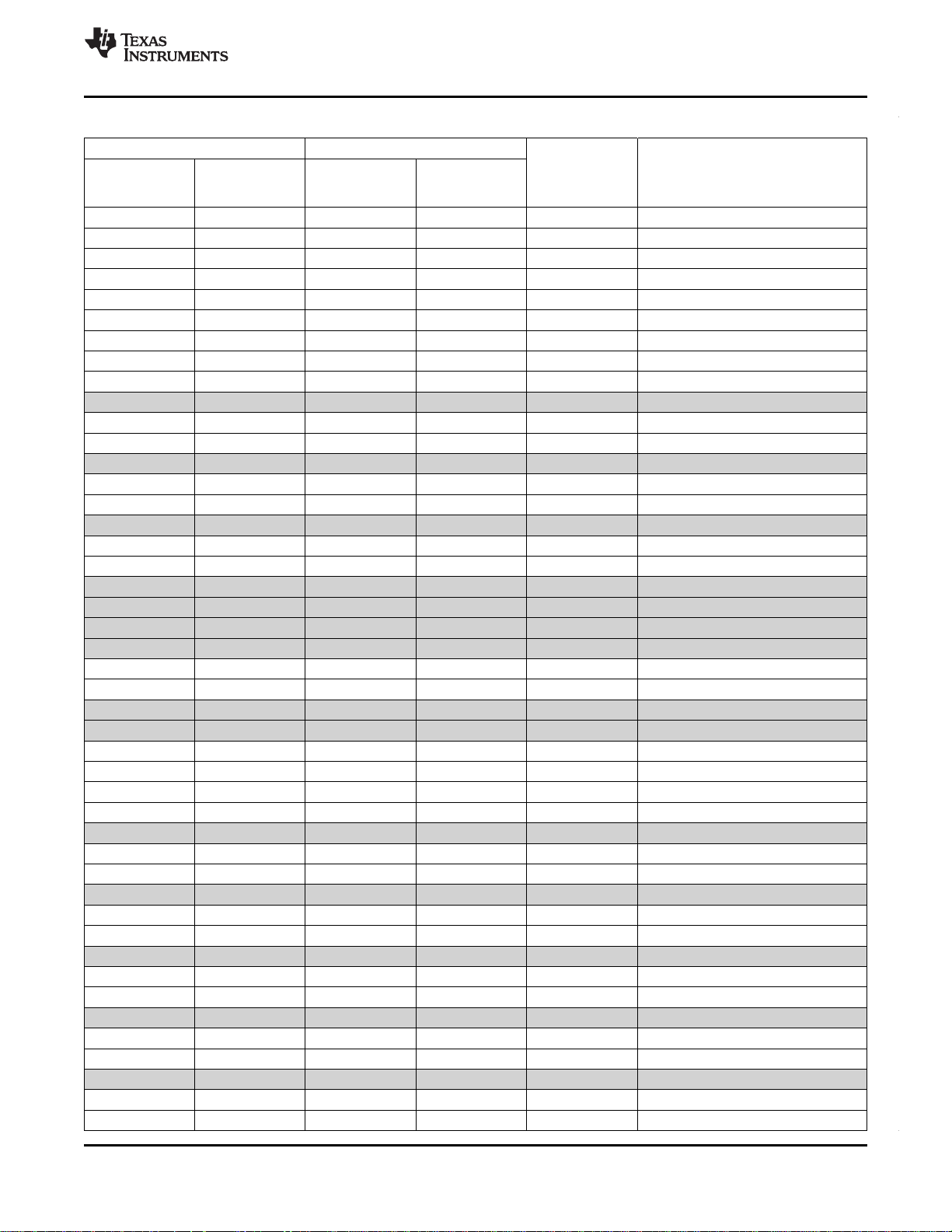

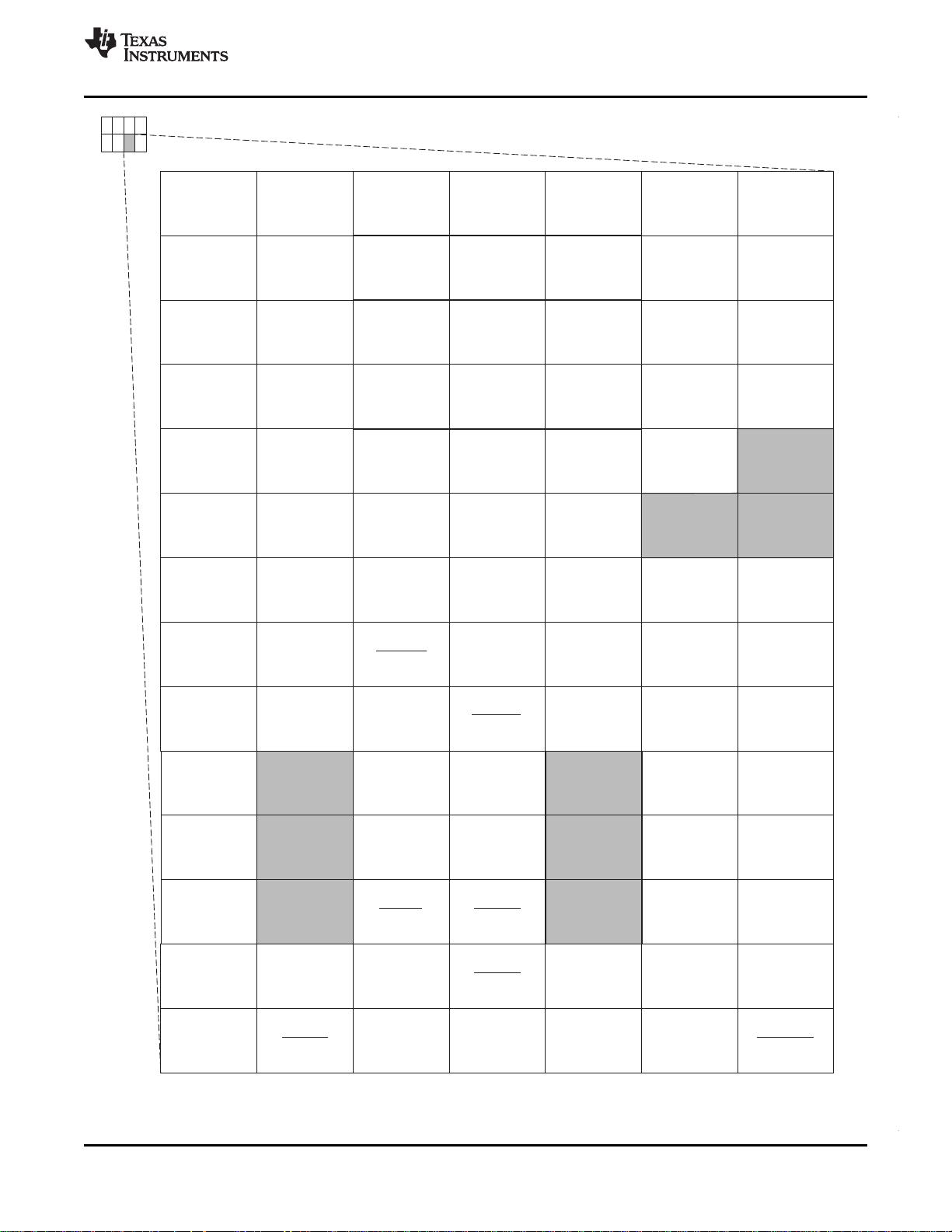

1.3 功能框图

图 1-1 shows the functional block diagram of the device.

www.ti.com.cn

图 1-1. TMS320DM814x DaVinci™ Digital Media Processors Functional Block Diagram

4 高性能片上系统 (SoC) 版权 © 2011, Texas Instruments Incorporated

Page 5

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

1 高性能片上系统 (SoC) ................................... 1

1.1 特性 .................................................. 1 7.2 Power .............................................. 166

1.2 说明 .................................................. 3

1.3 功能框图 ............................................. 4

2 Device Overview ........................................ 6

2.1 Device Comparison .................................. 6

2.2 Device Characteristics ............................... 6

2.3 Device Compatibility ................................. 8

2.4 ARM® Cortex™-A8 Microprocessor Unit (MPU)

Subsystem Overview ................................ 8

2.5 C674x™ DSP Overview ............................ 10

2.6 DSP/EDMA Memory Management Unit (MMU) .... 14

2.7 Media Controller Overview ......................... 15

2.8 HDVICP2 Overview ................................. 15

2.9 SGX530 Overview .................................. 16

2.10 Spinlock Module Overview ......................... 16

2.11 Mailbox Module Overview .......................... 17

2.12 Memory Map Summary ............................. 18

3 Device Pins ............................................. 26

3.1 Pin Maps ............................................ 26

3.2 Terminal Functions ................................. 35

4 Device Configurations .............................. 144

4.1 Control Module Registers ......................... 144

4.2 Boot Modes ....................................... 144 8.17 Peripheral Component Interconnect Express (PCIe)

4.3 Pin Multiplexing Control ........................... 145

4.4 Handling Unused Pins ............................ 155

4.5 DeBugging Considerations ........................ 155

5 System Interconnect ................................ 157

6 Device Operating Conditions ...................... 161

6.1 Absolute Maximum Ratings Over Operating Case

Temperature Range

(Unless Otherwise Noted) ......................... 161

6.2 Recommended Operating Conditions ............. 162

6.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating

Temperature (Unless Otherwise Noted) .......... 164

7 Power, Reset, Clocking, and Interrupts ......... 166

7.1 Power, Reset and Clock Management (PRCM)

ZHCS057–MARCH 2011

Module ............................................ 166

7.3 Reset .............................................. 173

7.4 Clocking ........................................... 181

7.5 Interrupts .......................................... 196

8 Peripheral Information and Timings ............. 203

8.1 Parameter Information ............................ 203

8.2 Recommended Clock and Control Signal Transition

Behavior ........................................... 204

8.3 Controller Area Network Interface (DCAN) ....... 204

8.4 EDMA ............................................. 206

8.5 Emulation Features and Capability ............... 209

8.6 Ethernet MAC Switch (EMAC SW) ................ 213

8.7 General-Purpose Input/Output (GPIO) ............ 225

8.8 General-Purpose Memory Controller (GPMC) and

Error Location Module (ELM) ..................... 228

8.9 High-Definition Multimedia Interface (HDMI) ...... 245

8.10 High-Definition Video Processing Subsystem

(HDVPSS) ......................................... 248

8.11 Inter-Integrated Circuit (I2C) ...................... 254

8.12 Imaging Subsystem (ISS) ......................... 258

8.13 LPDDR/DDR2/DDR3 Memory Controller ......... 261

8.14 Multichannel Audio Serial Port (McASP) .......... 294

8.15 Multichannel Buffered Serial Port (McBSP) ....... 302

8.16 MultiMedia Card/Secure Digital/Secure Digital Input

Output (MMC/SD/SDIO) ........................... 307

..................................................... 310

8.18 Serial ATA Controller (SATA) ..................... 315

8.19 Serial Peripheral Interface (SPI) .................. 319

8.20 Timers ............................................. 326

8.21 Universal Asynchronous Receiver/Transmitter

(UART) ............................................ 328

8.22 Universal Serial Bus (USB2.0) .................... 330

9 Device and Documentation Support ............. 338

9.1 Device Support .................................... 338

9.2 Documentation Support ........................... 339

9.3 Community Resources ............................ 339

10 Mechanical ............................................ 340

10.1 Thermal Data for CYE ............................. 340

10.2 Packaging Information ............................ 340

Copyright © 2011, Texas Instruments Incorporated 内容 5

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 6

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2 Device Overview

2.1 Device Comparison

Table 2-1 shows a comparison between devices, highlighting the differences.

FEATURES

SGX530 YES (1) NONE

2.2 Device Characteristics

Table 2-2 provides an overview of the TMS320DM814x DaVinci™ Digital Media Processors, which

includes significant features of the device, including the capacity of on-chip RAM, peripherals, and the

package type with pin count.

HARDWARE FEATURES DM841x

Peripherals

Not all peripherals pins

are available at the same

time (for more details, see

the Device Configurations

section).

HD Video Processing Subsystem (HDVPSS) and

Imaging Subsystem (ISS)

LPDDR/DDR2/3 Memory Controller 2 (32-bit Bus Widths)

GPMC + ELM

EDMA

10/100/1000 Ethernet MAC Switch with Management

Data Input/Output (MDIO)

USB 2.0

PCI Express 2.0 1 Port (1 5.0GT/s lane)

Timers and

UART control)

SPI 4 (Supports 4 slave devices)

MMC/SD/SDIO

I2C 4 (Master/Slave)

Media Controller Controls HDVPSS, HDVICP2, and ISS

www.ti.com.cn

Table 2-1. DM814x Device Comparison

DEVICES

TMS320DM8148 TMS320DM8147

Table 2-2. Characteristics of the Processor

1 16-/24-bit HD Capture Port or

2 8-bit SD Capture Ports

and

1 8/16/24-bit HD Capture Port

and

1 8-bit SD Capture Port

1 16-/24-/30-bit HD Display Port or

1 HDMI 1.3 Transmitter

and

1 16-/24-bit HD Display Port

and

2 SD Video DACs

1 Parallel Camera Input for Raw (up to 16-bit)

and BT.656/BT.1120 (8/16-bit)

Asynchronous (8-/16-bit bus width)

RAM, NOR, NAND

64 Independent Channels

8 QDMA Channels

1 (with 2 MII/RMII/GMII/RGMII Interfaces)

2 (Supports High- and Full-Speed as a Device and

High-, Full-, and Low-Speed as a Host, or OTG)

8 (32-bit General purpose)

1 (System Watchdog)

6 (with SIR, MIR, FIR, CIR support and RTS/CTS flow

(UART0 Supports Modem Interface)

1 (1-bit or 4-bit or 8-bit modes)

and

1 (8-bit mode) or

2 (1-bit or 4-bit modes)

6 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 7

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

Table 2-2. Characteristics of the Processor (continued)

HARDWARE FEATURES DM841x

McASP

McBSP 1 (2 Data Pins, Transmit/Receive)

Controller Area Network (DCAN) 2

Serial ATA (SATA) 3.0 Gbps 1 (Supports 1 Hard Disk Drive)

RTC 1

GPIO Up to 128 pins

Parallel Camera Interface (CAM) 1

Spin Lock Module 1 (up to 128 H/W Semaphores)

Mailbox Module 1 (with 12 Mailboxes)

Size (Bytes) 1120KB RAM, 48KB ROM

On-Chip Memory Organization 48KB Boot ROM

CPU ID + CPU Rev ID Control Status Register (CSR.[31:16]) 0x1401

C674x Megamodule

Revision

JTAG BSDL ID DEVICE_ID Register (address location: 0x4814_0600)

CPU Frequency MHz

Cycle Time ns

Voltage

Package 23 x 23 mm 684-Pin BGA (CYE) [with Via Channel™ Technology]

Process Technology μm 0.045 μm

Product Status

(1)

(1) PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

Revision ID Register (MM_REVID[15:0]) 0x0000

Core Logic (V) 0.83V – 1.2V

I/O (V) 1.5 V, 1.8 V, 3.3 V

Product Preview (PP),

Advance Information (AI), PP

or Production Data (PD)

ZHCS057–MARCH 2011

6 (10/10/4/4/4/4 Serializers, Each with

Transmit/Receive and DIT capability)

ARM

32KB I-cache

32KB D-cache

512KB L2 Cache

DSP

32KB L1 Program (L1P)/Cache (up to 32KB) with EDC

32KB L1 Data (L1D)/Cache (up to 32KB)

256KB Unified Mapped RAM/Cache (L2) with ECC

ADDITIONAL SHARED MEMORY

128KB On-chip RAM

see Section 8.5.3.1, JTAG ID (JTAGID) Register

Description

ARM® Cortex™-A8 720 MHZ

DSP 600 MHz

ARM® Cortex™ -A8 1.39 ns

DSP 1.66 ns

Copyright © 2011, Texas Instruments Incorporated Device Overview 7

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 8

PRODUCTPREVIEW

Arbiter

128

ICECrusher

Trace

Debug

48KB ROM

64KB RAM

ARM Cortex-A8

Interrupt Controller

(AINTC)

L3

DMM

128

64

64

128 128

128

PLL_ARM

128

System Events

32

32

128

ARM Cortex-A8

NEONETM

512KB L2$

32KB L1I$ 32KB L1D$

DEVOSC

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.3 Device Compatibility

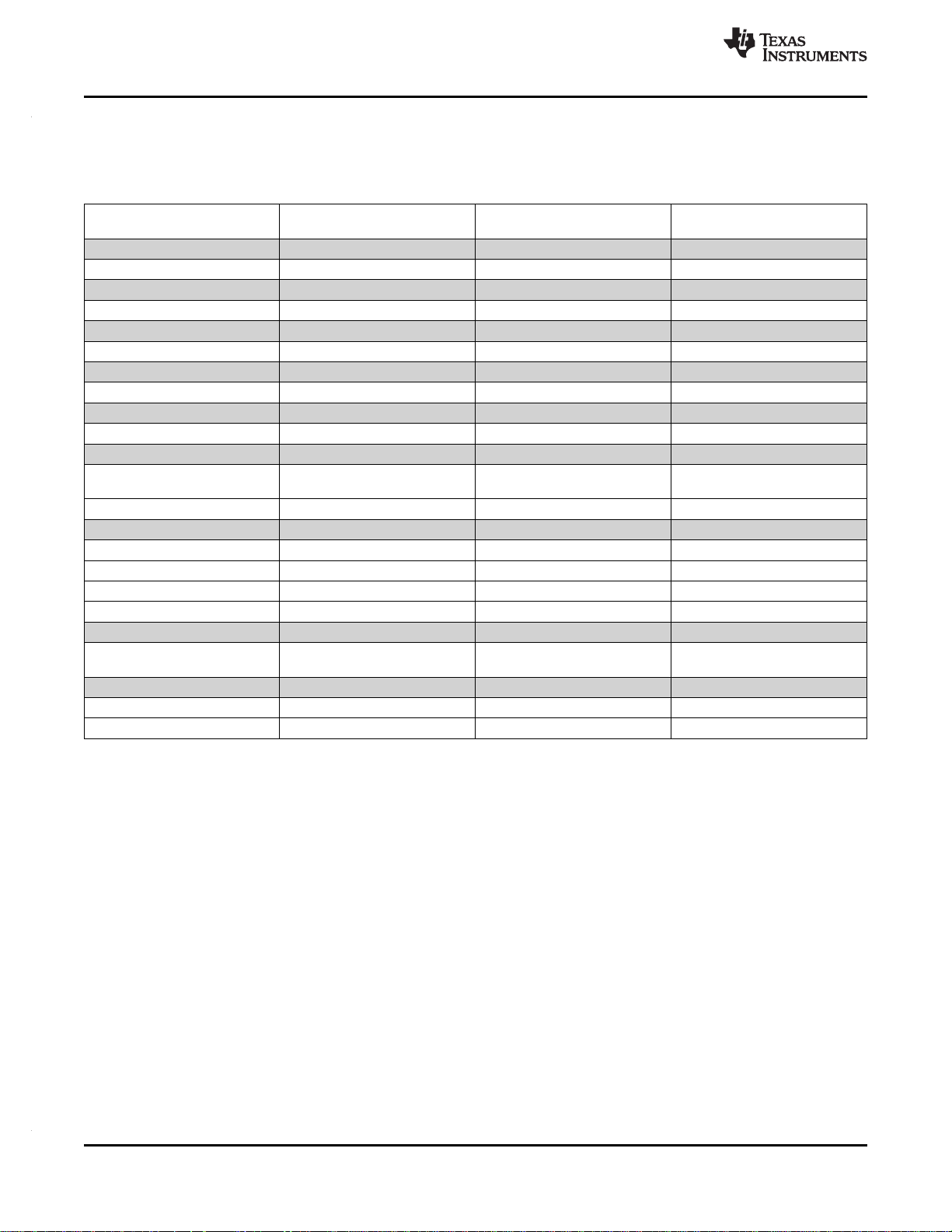

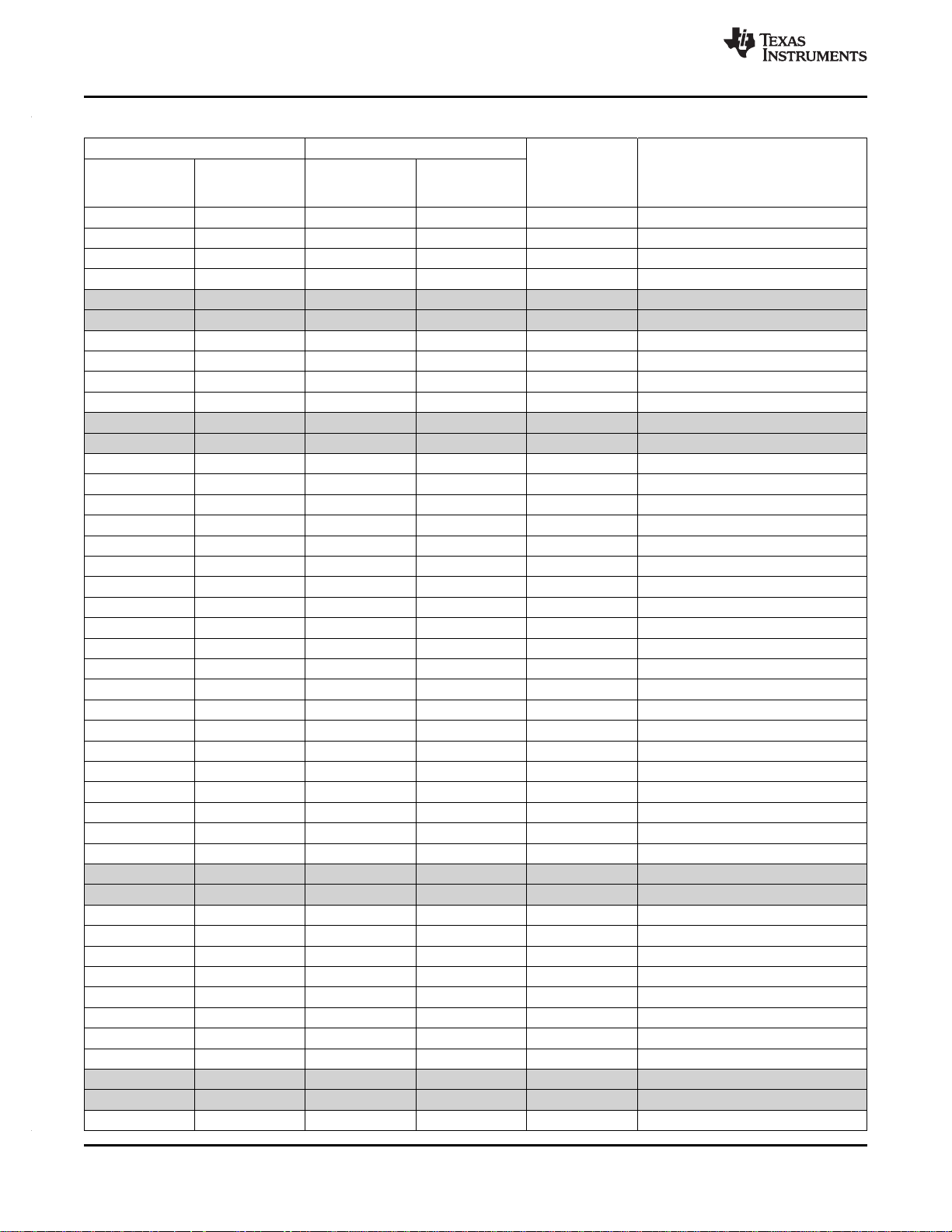

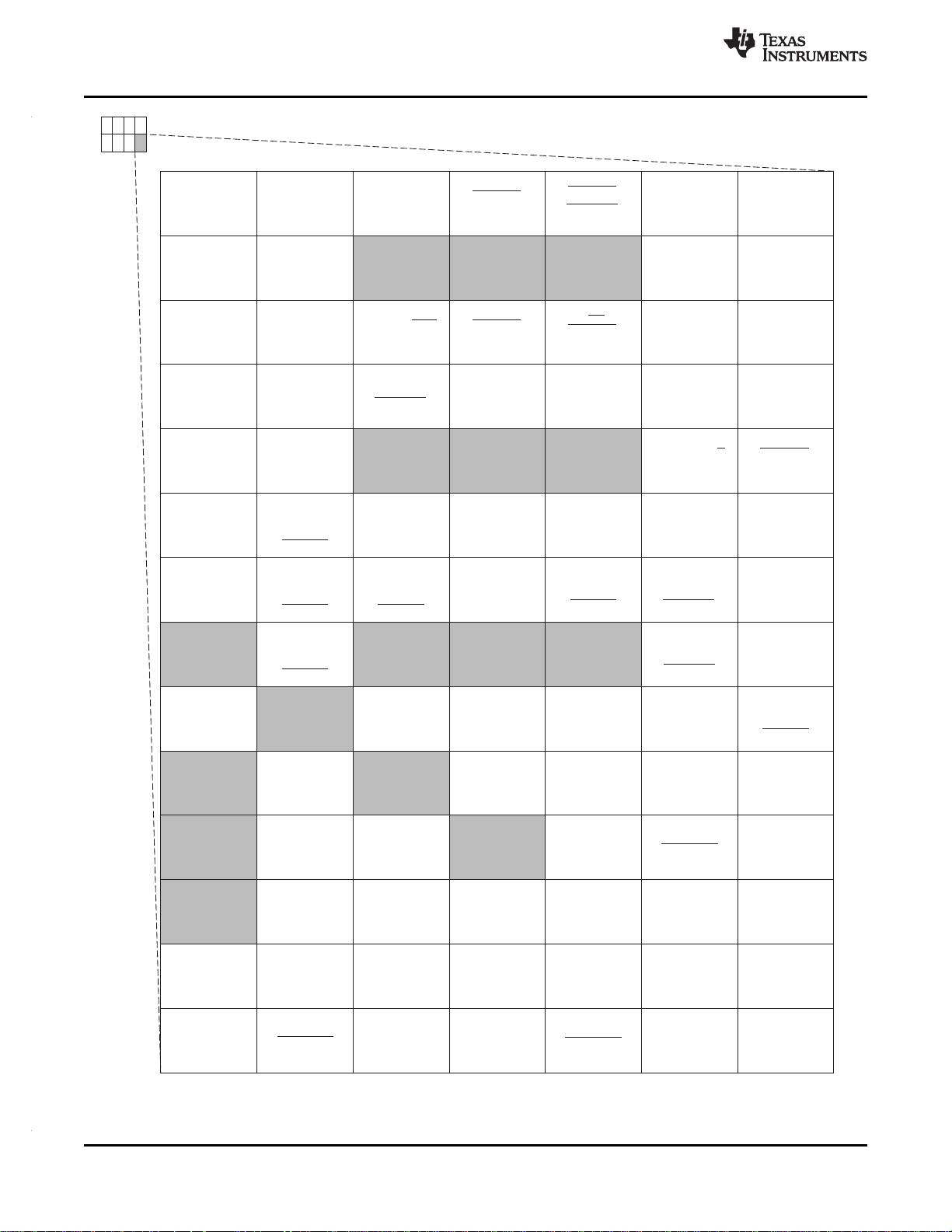

2.4 ARM® Cortex™-A8 Microprocessor Unit (MPU) Subsystem Overview

The ARM® Cortex™-A8 Subsystem is designed to give the ARM Cortex-A8 Master control of the device.

In general, the ARM Cortex-A8 is responsible for configuration and control of the various subsystems,

peripherals, and external memories.

The ARM Cortex-A8 Subsystem includes the following features:

• ARM Cortex-A8 RISC processor:

– ARMv7 ISA plus Thumb2™, JazelleX™, and Media Extensions

– Neon™ Floating-Point Unit

– Enhanced Memory Management Unit (MMU)

– Little Endian

– 32KB L1 Instruction Cache

– 32KB L1 Data Cache

– 512KB L2 Cache

• CoreSight Embedded Trace Module (ETM)

• ARM Cortex-A8 Interrupt Controller (AINTC)

• Embedded PLL Controller (PLL_ARM)

• 64KB Internal RAM

• 48KB Internal Public ROM

www.ti.com.cn

Figure 2-1 shows the ARM Cortex-A8 Subsystem for the device.

For more detailed information on the ARM Cortex-A8 Subsystem, see the ARM Cortex-A8 Subsystem

User's Guide (Literature Number: TBD).

2.4.1 ARM Cortex-A8 RISC Processor

The ARM Cortex-A8 Subsystem integrates the ARM Cortex-A8 processor. The ARM Cortex-A8 processor

is a member of ARM Cortex family of general-purpose microprocessors. This processor is targeted at

multi-tasking applications where full memory management, high performance, low die size, and low power

are all important. The ARM Cortex-A8 processor supports the ARM debug architecture and includes logic

to assist in both hardware and software debug. The ARM Cortex-A8 processor has a Harvard architecture

and provides a complete high-performance subsystem, including:

• ARM Cortex-A8 Integer Core

• Superscalar ARMv7 Instruction Set

• Thumb-2 Instruction Set

8 Device Overview Copyright © 2011, Texas Instruments Incorporated

Figure 2-1. ARM Cortex-A8 Subsystem

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 9

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

• Jazelle RCT Acceleration

• CP14 Debug Coprocessor

• CP15 System Control Coprocessor

• NEON™ 64-/128-bit Hybrid SIMD Engine for Multimedia

• Enhanced VFPv3 Floating-Point Coprocessor

• Enhanced Memory Management Unit (MMU)

• Separate Level-1 Instruction and Data Caches

• Integrated Level-2 Cache

• 128-bit Interconnector-to-System Memories and Peripherals

• Embedded Trace Module (ETM).

2.4.2 Embedded Trace Module (ETM)

To support real-time trace, the ARM Cortex-A8 processor provides an interface to enable connection of an

embedded trace module (ETM). The ETM consists of two parts:

• The Trace port which provides real-time trace capability for the ARM Cortex-A8.

• Triggering facilities that provide trigger resources, which include address and data comparators,

counter, and sequencers.

The ARM Cortex-A8 trace port is not pinned out and is, instead, only connected to the system-level

Embedded Trace Buffer (ETB). The ETB has a 32KB buffer memory. ETB enabled debug tools are

required to read/interpret the captured trace data.

ZHCS057–MARCH 2011

For more details on the ETM, see Section 8.5.2, Trace.

2.4.3 ARM Cortex-A8 Interrupt Controller (AINTC)

The ARM Cortex-A8 subsystem contains an interrupt controller (AINTC) that prioritizes all service requests

from the system peripherals and generates either IRQ or FIQ to the ARM Cortex-A8 processor. For more

details on the AINTC, see Section 7.5.1, ARM Cortex-A8 Interrupts.

2.4.4 ARM Cortex-A8 PLL (PLL_ARM)

The ARM Cortex-A8 subsystem contains an embedded PLL Controller (PLL_ARM) for generating the

subsystem’s clocks from the DEV Clock input. For more details on the PLL_ARM, see Section 7.4,

Clocking.

2.4.5 ARM MPU Interconnect

The ARM Cortex-A8 processor is connected through the arbiter to both an L3 interconnect port and a

DMM port. The DMM port is 128-bits wide and provides the ARM Cortex-A8 direct access to the DDR

memories, while the L3 interconnect port is 64-bits wide and provides access to the remaining device

modules.

Copyright © 2011, Texas Instruments Incorporated Device Overview 9

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 10

PRODUCTPREVIEW

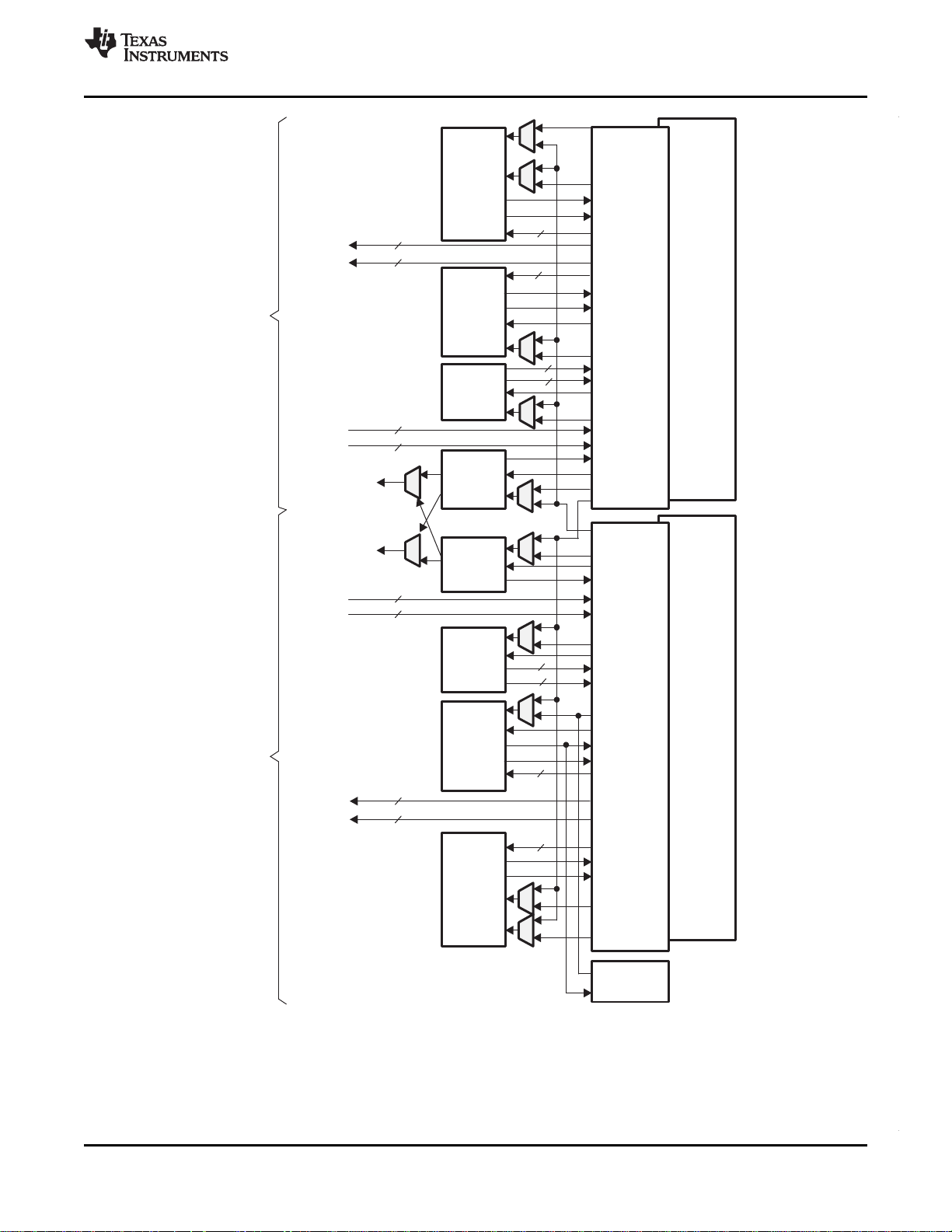

Instruction Fetch

C674x

Fixed/Floating Point CPU

Register

File A

Register

File B

Cache Control

Memory Protect

Bandwidth Mgmt

L1P

256

Cache Control

Memory Protect

Bandwidth Mgmt

L1D

64 64

8 x 32

32K Bytes

L1D RAM/

Cache

32K Bytes

L1P RAM/

Cache

w/EDC

256

Cache Control

Memory Protect

Bandwidth Mgmt

L2

256K Bytes

L2 RAM

w/ ECC

256

HDVICP2 Host

SL2 Port

256

CFG

MDMA SDMA

EMC

Power Down

Interrupt

Controller

IDMA

256

256

256

256

256

128

L3 (Fast)

Interconnect

128

32

L3 (Fast)

Interconnect

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

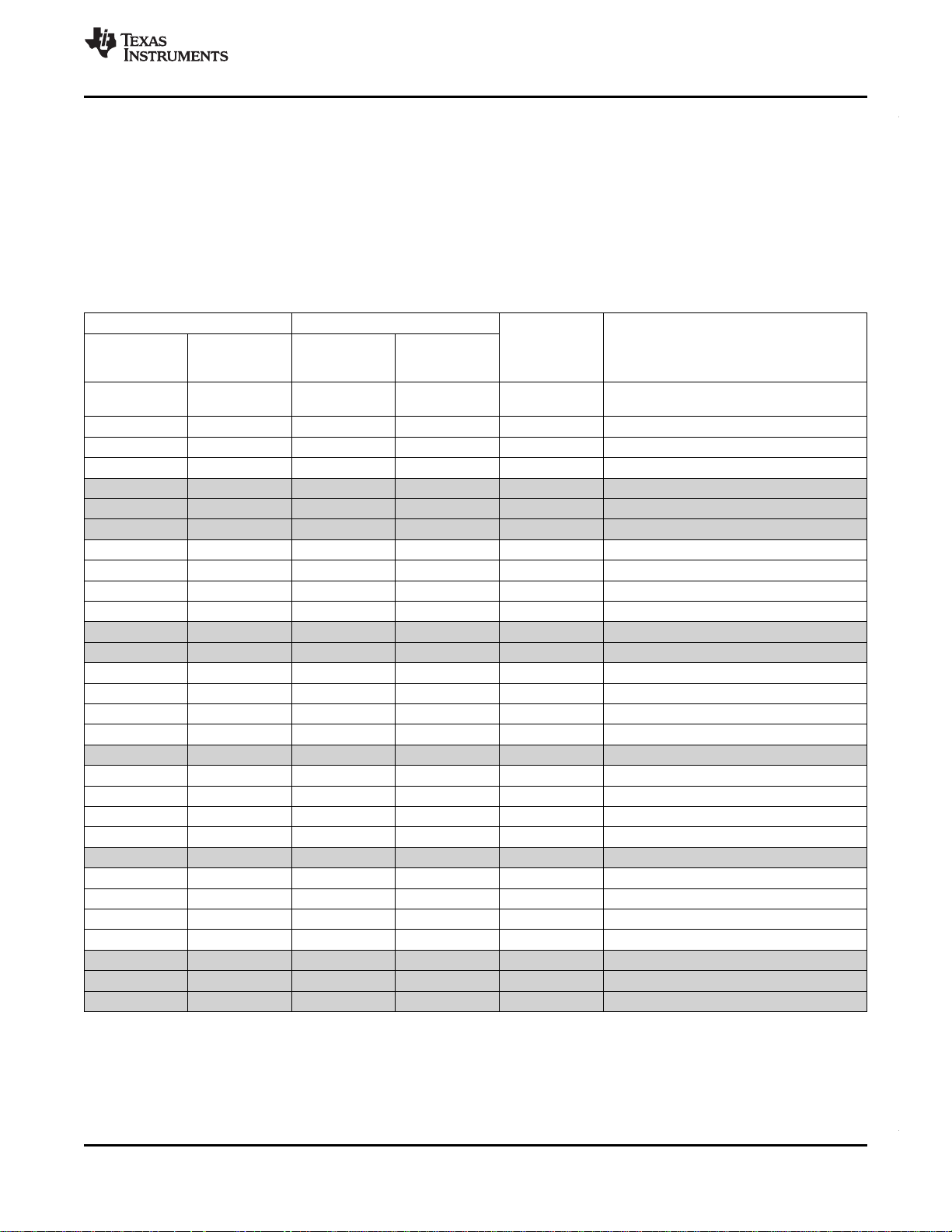

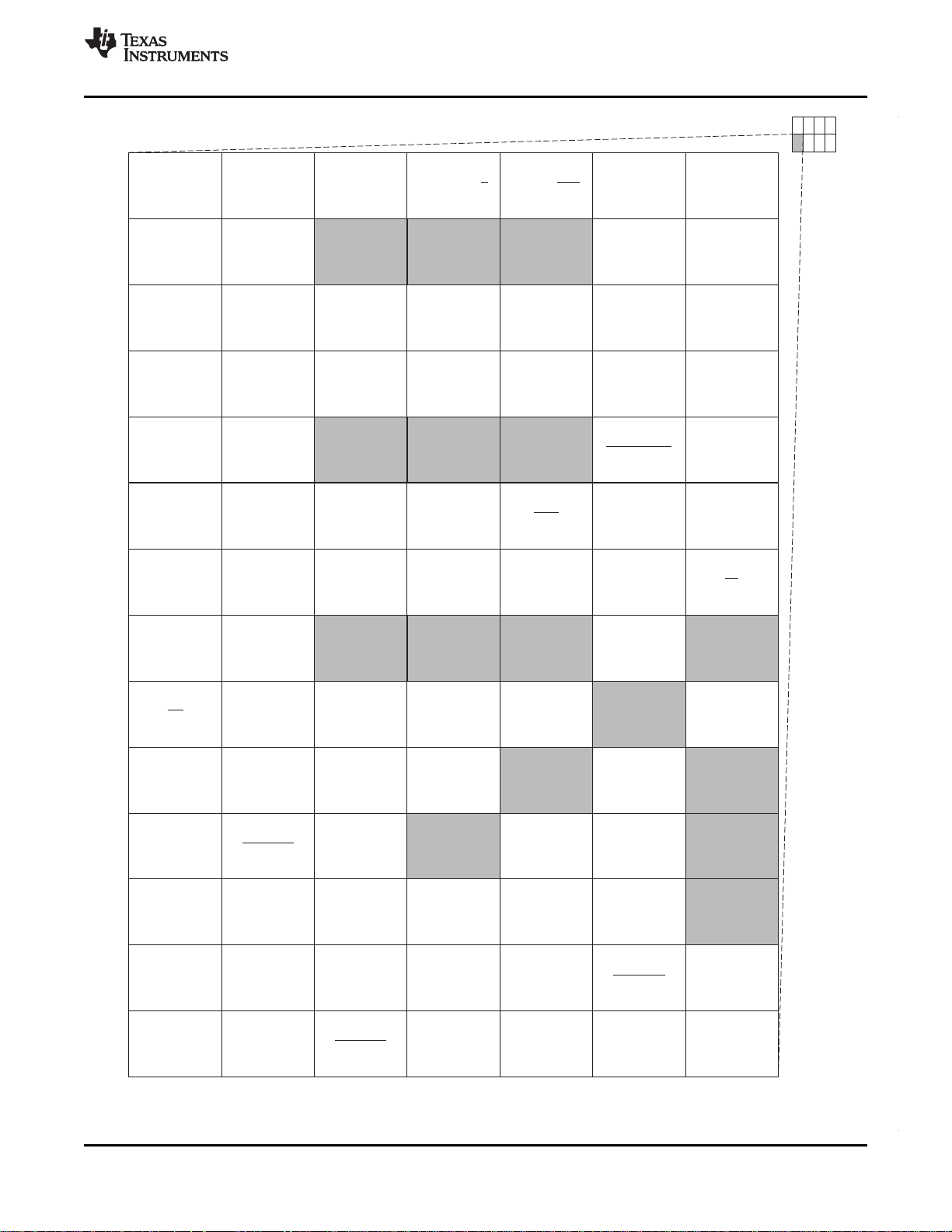

2.5 C674x™ DSP Overview

The DSP Subsystem includes the following features:

• C674x DSP CPU

• 32KB L1 Program (L1P)/Cache (up to 32KB) with Error Detection Circuitry (EDC)

• 32KB L1 Data (L1D)/Cache (up to 32KB)

• 256KB Unified Mapped RAM/Cache (L2) with Error Correction Circuitry (ECC)

• Direct Connection to the HDVICP2 Host SL2 Port

• Little Endian

www.ti.com.cn

For more details on the C674x DSP, see the C674x DSP Subsystem User's Guide (Literature Number:

TBD).

Figure 2-2. C674x Megamodule Block Diagram

10 Device Overview Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 11

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

2.5.1 C674x DSP CPU Description

The C674x central processing unit (CPU) consists of eight functional units, two register files, and two data

paths as shown in Figure 2-2. The two general-purpose register files (A and B) each contain 32 32-bit

registers for a total of 64 registers. The general-purpose registers can be used for data or can be data

address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit data,

40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored

in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in

the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

The C674x CPU combines the performance of the C64x+ core with the floating-point capabilities of the

C67x+ core.

Each C674x .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four 16

x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for high-precision algorithms on

a variety of signed and unsigned 32-bit data types.

ZHCS057–MARCH 2011

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C674x core enhances the .S unit in several ways. On the previous cores, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C674x core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C674x

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C674x CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

Copyright © 2011, Texas Instruments Incorporated Device Overview 11

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 12

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

•

Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C674x CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C674x DSP CPU and Instruction Set User's Guide (literature number SPRUFE8)

• TMS320C674x DSP Megamodule Reference Guide (literature number SPRUFK5)

www.ti.com.cn

12 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 13

PRODUCTPREVIEW

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

8

8

8

8

32

32

32

32

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

A. .M unit, is 32 MSB.

B On .M unit, is 32 LSB.

C. On C64x CPU .M unit, is 32 bits; on C64x+ CPU .M unit, is 64 bits.

D. On .L and .S units, connects to odd register files and even connects to even register files

dst2

dst1

src2 src2

odd dst dst

(D)

(A)

(B)

(C)

(C)

(B)

(A)

(D)

(D)

TMS320DM8148, TMS320DM8147

www.ti.com.cn

ZHCS057–MARCH 2011

Figure 2-3. TMS320C674x CPU (DSP Core) Data Paths

Copyright © 2011, Texas Instruments Incorporated Device Overview 13

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 14

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.6 DSP/EDMA Memory Management Unit (MMU)

All C674x accesses through its MDMA port will be directed through the DSP/EDMA MMU module where

they are remapped to physical system addresses. This protects the ARM Cortex-A8 memory regions from

accidental corruption by C674x code and allows for direct allocation of buffers in user space without the

need for translation between ARM and DSP applications.

In addition, accesses by the EDMA TC0 and TC1 may optionally be routed through the DSP/EDMA MMU.

This allows EDMA Channels 0 and 1 to be used by the DSP to perform transfers using only the known

virtual addresses of the associated buffers. The MMU_CFG register in the Control Module is used to

enable/disable use of the DSP/EDMA MMU by the EDMA TCs.

For more details on the DSP/EDMA MMU features, see the TBD Memory Management Unit (MMU) User's

Guide (Literature Number: TBD).

www.ti.com.cn

14 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 15

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

2.7 Media Controller Overview

The Media Controller has the responsibility of managing the HDVPSS, HDVICP2, and ISS modules.

For more details on the Media Controller, see the TBD Subsystem User's Guide (Literature Number:

TBD).

2.8 HDVICP2 Overview

The HDVICP2 is a Video Encoder/Decoder hardware accelerator supporting a range of encode, decode,

and transcode operations for most major video codec standards. The main video Codec standards

supported in hardware are MPEG1/2/4 ASP/SP, H.264 BL/MP/HP, VC-1 SP/MP/AP, RV9/10, AVS-1.0,

and ON2 VP6.2/VP7.

The HDVICP2 hardware accelerator is composed of the following elements:

• Motion estimation acceleration engine

• Loop filter acceleration engine

• Sequencer, including its memories and an interrupt controller

• Intra-prediction estimation engine

• Calculation engine

• Motion compensation engine

• Entropy coder/decoder

• Video Direct Memory Access (DMA)

• Synchronization boxes

• Shared L2 controller

• Local interconnect

ZHCS057–MARCH 2011

For more details on the HDVICP2 see the HDVICP2 User's Guide (Literature Number: TBD).

Copyright © 2011, Texas Instruments Incorporated Device Overview 15

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 16

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.9 SGX530 Overview

The SGX530 is a vector/3D graphics accelerator for vector and 3-dimensional (3D) graphics applications.

The SGX530 graphics accelerator efficiently processes a number of various multimedia data types

concurrently:

• Pixel data

• Vertex data

• Video data

This is achieved using a multi-threaded architecture using two levels of scheduling and data partitioning

enabling zero overhead task switching.

The SGX530 has the following major features:

• Vector graphics and 3D graphics

• Tile-based architecture

• Universal Scalable Shader Engine (USSE™) - multi-threaded engine incorporating pixel and vertex

shader functionality

• Advanced shader feature set - in excess of Microsoft VS3.0, PS3.0, and OpenGL2.0

• Industry standard API support - OpenGL ES 1.1 and 2.0, OpenVG v1.1

• Fine-grained task switching, load balancing, and power management

• Advanced geometry DMA driven operation for minimum CPU interaction

• Programmable high-quality image anti-aliasing

• POWERVR SGX core MMU for address translation from the core virtual address to the external

physical address (up to 4GB address range)

• Fully-virtualized memory addressing for OS operation in a unified memory architecture

• Advanced and standard 2D operations [e.g., vector graphics, block level transfers (BLTs), raster

operations (ROPs)]

www.ti.com.cn

For more details on the SSM, see the ARM Cortex-A8 Subsystem User's Guide (Literature Number: TBD).

2.10 Spinlock Module Overview

The Spinlock module provides hardware assistance for synchronizing the processes running on multiple

processors in the device:

• ARM Cortex-A8 processor

• C674x DSP

• Media Controller .

The Spinlock module implements 128 spinlocks (or hardware semaphores) that provide an efficient way to

perform a lock operation of a device resource using a single read-access, avoiding the need for a

read-modify-write bus transfer of which the programmable cores are not capable.

For more detailed information on the Spinlock Module, see the TBD User's Guide (Literature Number:

TBD).

16 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 17

PRODUCTPREVIEW

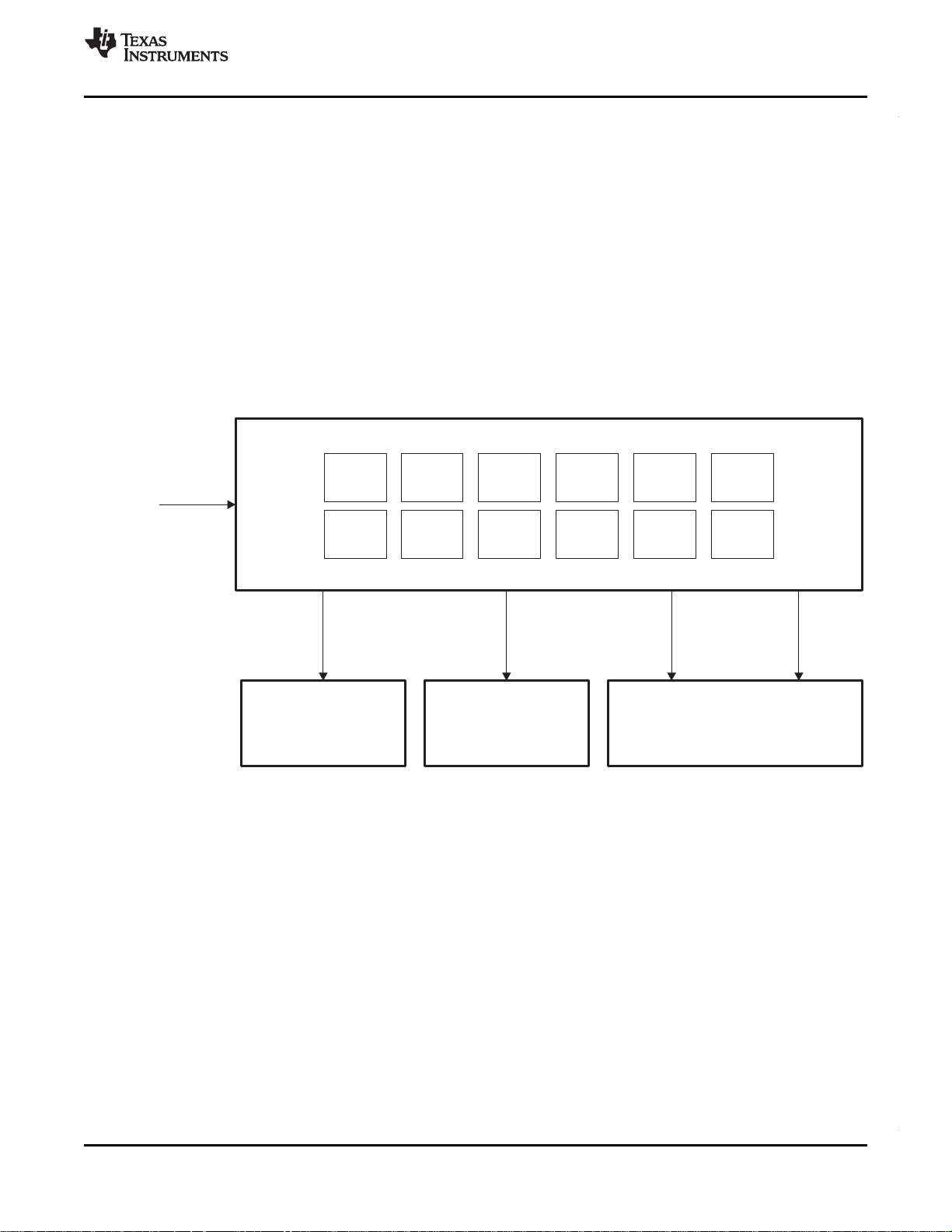

Mailbox Mailbox Mailbox Mailbox Mailbox Mailbox

Mailbox Mailbox Mailbox Mailbox Mailbox Mailbox

L4

Interconnect

Interrupt Interrupt Interrupt Interrupt

Mailbox Module

ARM Cortex-A8 C674x+ DSP Media Controller

TMS320DM8148, TMS320DM8147

www.ti.com.cn

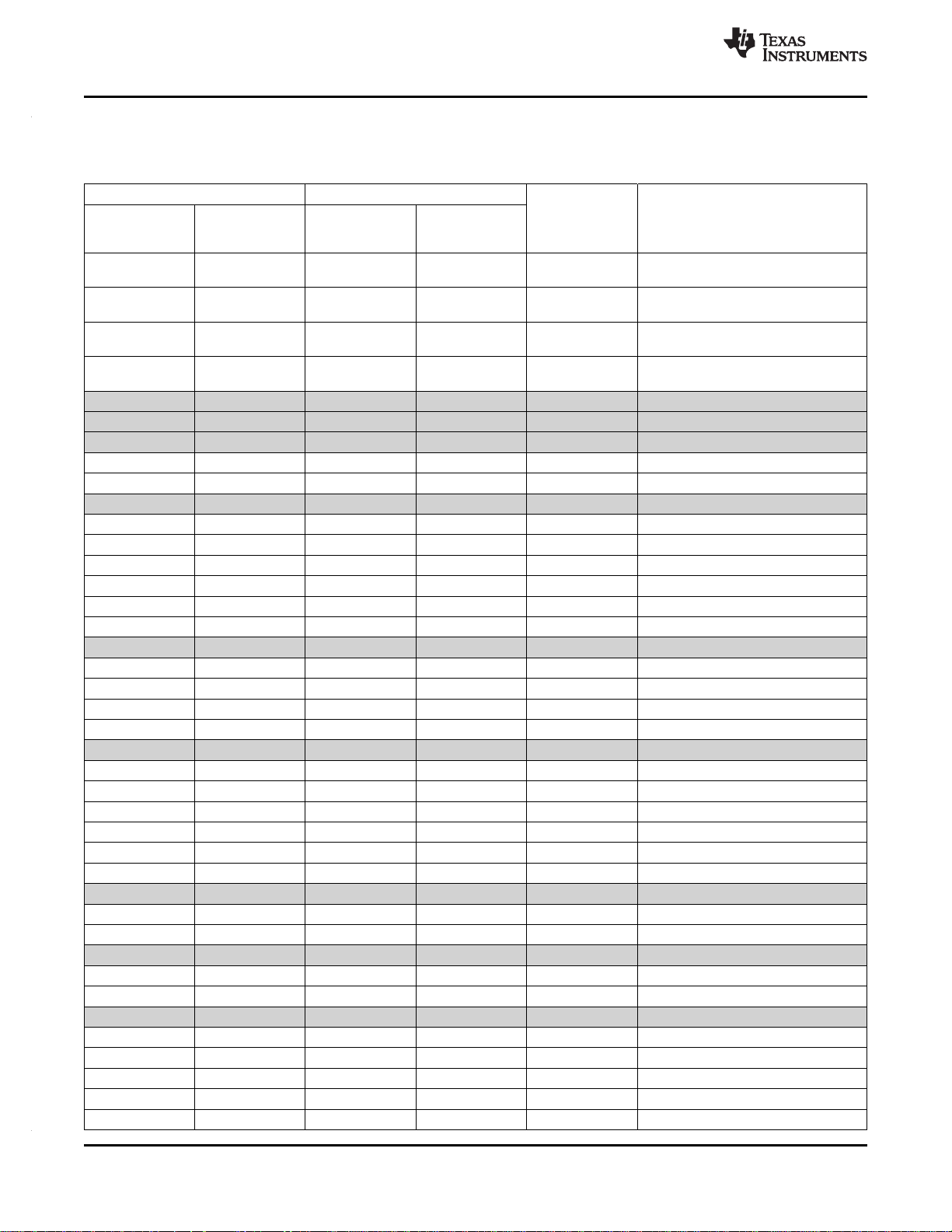

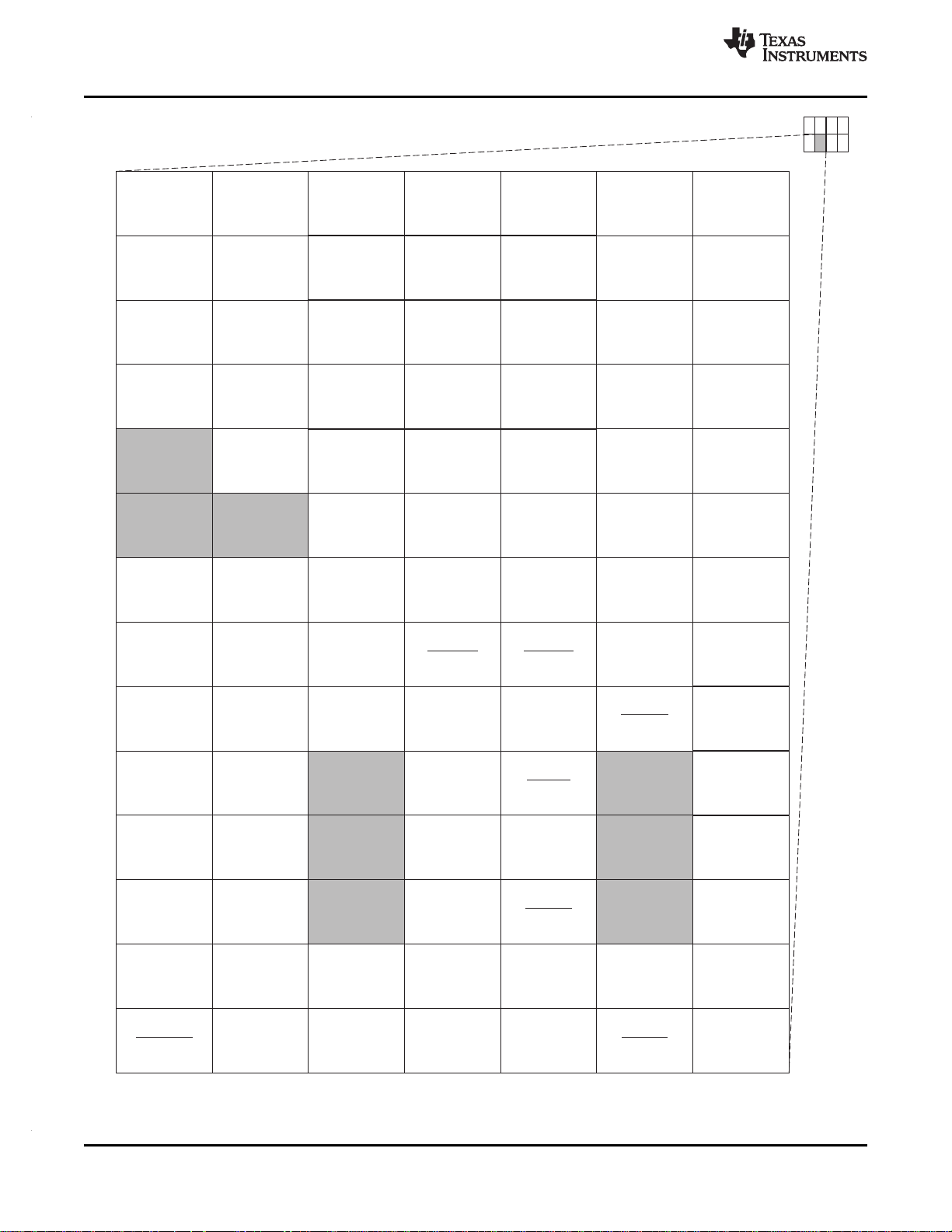

2.11 Mailbox Module Overview

The device Mailbox module facilitates communication between the ARM Cortex-A8, C674x DSP, and the

Media Controller. It consists of twelve mailboxes, each supporting a 1-way communication between two of

the above processors. The sender sends information to the receiver by writing a message to the mailbox

registers. Interrupt signaling is used to notify the receiver that a message has been queued or to notify the

sender about an overflow situation.

The Mailbox module supports the following features (see Figure 2-4):

• 12 mailboxes

• Flexible mailbox-to-processor assignment scheme

• Four-message FIFO depth for each message queue

• 32-bit message width

• Message reception and queue-not-full notification using interrupts

• Four interrupts (one to ARM Cortex-A8, one to C674x, and two to Media Controller)

ZHCS057–MARCH 2011

For more detailed information on the Mailbox Module, see the TBD User's Guide (Literature Number:

TBD).

Copyright © 2011, Texas Instruments Incorporated Device Overview 17

Figure 2-4. Mailbox Module Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 18

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.12 Memory Map Summary

The device has multiple on-chip memories associated with its two processors and various subsystems. To

help simplify software development a unified memory map is used where possible to maintain a consistent

view of device resources across all bus masters.

2.12.1 L3 Memory Map

Table 2-3 shows the L3 memory map for all system masters (including Cortex-A8), except for the C674x

DSP. Table 2-4 shows the memory map for the C674x DSP.

For more details on the interconnect topology and connectivity across the L3 and L4 interconnects, see

Section 5, System Interconnect.

START ADDRESS END ADDRESS

(HEX) (HEX)

0x0000_0000 0x1FFF_FFFF 512MB GPMC

0x2000_0000 0x2FFF_FFFF 256MB PCIe

0x3000_0000 0x3FFF_FFFF 256MB Reserved

0x4000_0000 0x4001_FFFF 128KB Reserved

0x4002_0000 0x4002_BFFF 48K

0x4002_C000 0x402E_FFFF 2832K Reserved

0x402F_0000 0x402F_FFFF 64KB

0x4030_0000 0x4031_FFFF 128KB OCMC SRAM

0x4032_0000 0x407F_FFFF 4992KB Reserved

0x4080_0000 0x4083_FFFF 256KB C674x™ L2 RAM

0x4084_0000 0x40DF_FFFF 5888KB Reserved

0x40E0_0000 0x40E0_7FFF 32KB C674x L1P Cache/RAM

0x40E0_8000 0x40EF_FFFF 992KB Reserved

0x40F0_0000 0x40F0_7FFF 32KB C674x L1D Cache/RAM

0x40F0_8000 0x40FF_FFFF 992KB Reserved

0x4100_0000 0x41FF_FFFF 16MB Reserved

0x4200_0000 0x43FF_FFFF 32MB Reserved

0x4400_0000 0x443F_FFFF 4MB L3 Fast configuration registers

0x4440_0000 0x447F_FFFF 4MB L3 Mid configuration registers

0x4480_0000 0x44BF_FFFF 4MB L3 Slow configuration registers

0x44C0_0000 0x45FF_FFFF 20MB Reserved

0x4600_0000 0x463F_FFFF 4MB McASP0 Data Peripheral Registers

0x4640_0000 0x467F_FFFF 4MB McASP1 Data Peripheral Registers

0x4680_0000 0x46BF_FFFF 4MB McASP2 Data Peripheral Registers

0x46C0_0000 0x46FF_FFFF 4MB HDMI

0x4700_0000 0x473F_FFFF 4MB McBSP

0x4740_0000 0x477F_FFFF 4MB USB

0x4780_0000 0x4780_FFFF 64KB Reserved

0x4781_0000 0x4781_1FFF 8KB MMCSD2

0x4781_2000 0x47BF_FFFF 4MB - 72KB Reserved

0x47C0_0000 0x47FF FFFF 4MB Reserved

0x4800_0000 0x48FF_FFFF 16MB L4 Slow Peripheral Domain

0x4900_0000 0x490F_FFFF 1MB EDMA TPCC Registers

www.ti.com.cn

Table 2-3. L3 Memory Map

SIZE DESCRIPTION

ARM Cortex-A8 ROM

(Accessible by ARM Cortex-A8 only)

ARM Cortex-A8 RAM

(Accessible by ARM Cortex-A8 only)

(see Table 2-6)

18 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 19

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

Table 2-3. L3 Memory Map (continued)

START ADDRESS END ADDRESS

(HEX) (HEX)

0x4910_0000 0x497F_FFFF 7MB Reserved

0x4980_0000 0x498F_FFFF 1MB EDMA TPTC0 Registers

0x4990_0000 0x499F_FFFF 1MB EDMA TPTC1 Registers

0x49A0_0000 0x49AF_FFFF 1MB EDMA TPTC2 Registers

0x49B0_0000 0x49BF_FFFF 1MB EDMA TPTC3 Registers

0x49C0_0000 0x49FF_FFFF 4MB Reserved

0x4A00_0000 0x4AFF_FFFF 16MB L4 Fast Peripheral Domain

0x4B00_0000 0x4BFF_FFFF 16MB Emulation Subsystem

0x4C00_0000 0x4CFF_FFFF 16MB DDR0 Registers

0x4D00_0000 0x4DFF_FFFF 16MB DDR1 Registers

0x4E00_0000 0x4FFF_FFFF 32MB DDR DMM Registers

0x5000_0000 0x50FF_FFFF 16MB GPMC Registers

0x5100_0000 0x51FF_FFFF 16MB PCIE Registers

0x5200_0000 0x54FF_FFFF 48MB Reserved

0x5500_0000 0x55FF_FFFF 16MB Media Controller

0x5600_0000 0x56FF_FFFF 16MB SGX530

0x5700_0000 0x57FF_FFFF 16MB Reserved

0x5800_0000 0x58FF_FFFF 16MB HDVICP2 Configuration

0x5900_0000 0x59FF_FFFF 16MB HDVICP SL2

0x5A00_0000 0x5BFF_FFFF 32MB Reserved

0x5C00_0000 0x5DFF_FFFF 32MB ISS

0x5E00_0000 0x5FFF_FFFF 32MB Reserved

0x6000_0000 0x7FFF_FFFF 512MB DDR DMM Tiler Window (see Table 2-7)

0x8000_0000 0xFFFF_FFFF 2GB DDR

0x1 0000 0000 0x1 FFFF FFFF 4GB DDR DMM Tiler Extended Address Map

SIZE DESCRIPTION

(see Table 2-5)

(ISS and HDVPSS only) [see Table 2-7]

ZHCS057–MARCH 2011

Copyright © 2011, Texas Instruments Incorporated Device Overview 19

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 20

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.12.2 C674x Memory Map

Table 2-4 shows the memory map for the C674x DSP.

START ADDRESS END ADDRESS

(HEX) (HEX)

0x0000_0000 0x003F_FFFF 4MB Reserved

0x0040_0000 0x0043_FFFF 256KB HDVICP SL2

0x0044_0000 0x007F_FFFF 3840KB Reserved

0x0080_0000 0x0083_FFFF 256KB C674x™ L2 RAM

0x0084_0000 0x00DF_FFFF 5888KB Reserved

0x00E0_0000 0x00E0_7FFF 32KB C674x L1P Cache/RAM

0x00E0_8000 0x00EF_FFFF 992KB Reserved

0x00F0_0000 0x00F0_7FFF 32KB C674x L1D Cache/RAM

0x00F0_8000 0x017F_FFFF 9184KB Reserved

0x0180_0000 0x01BF_FFFF 4MB C674x Internal CFG registers

0x01C0_0000 0x07FF_FFFF 100MB Reserved

0x0800_0000 0x08FF_FFFF 16MB L4 Slow Peripheral Domain

0x0900_0000 0x090F_FFFF 1MB EDMA TPCC Registers

0x0910_0000 0x097F_FFFF 7MB Reserved

0x0980_0000 0x098F_FFFF 1MB EDMA TPTC0 Registers

(1) Addresses 0x1000_0000 to 0x10FF_FFFF are mapped to C674x internal addresses 0x0000_0000 to 0x00FF_FFFF.

(2) For more details on the DSP/EDMA MMU, see the TMS320DM814x DMSoC Memory Management Units (MMU) User's Guide

0x0990_0000 0x099F_FFFF 1MB EDMA TPTC1 Registers

0x09A0_0000 0x09AF_FFFF 1MB EDMA TPTC2 Registers

0x09B0_0000 0x09BF_FFFF 1MB EDMA TPTC3 Registers

0x09C0_0000 0x09FF_FFFF 4MB Reserved

0x0A00_0000 0x0AFF_FFFF 16MB L4 Fast Peripheral Domain

0x0B00_0000 0x0FFF_FFFF 80MB Reserved

0x1000_0000 0x10FF_FFFF 16MB C674x Internal Global Address

0x1100_0000 0xFFFF_FFFF 3824MB DEMMU Mapped L3 Regions

(Literature Number: TBD).

www.ti.com.cn

Table 2-4. C674x Memory Map

SIZE DESCRIPTION

(see Table 2-6)

(see Table 2-5)

(1)

(2)

20 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 21

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

2.12.3 L4 Memory Map

The L4 Fast Peripheral Domain, L4 Slow Peripheral Domain regions of the memory maps above are

broken out into Table 2-5 and Table 2-6.

For more details on the interconnect topology and connectivity across the L3 and L4 interconnects, see

Section 5, System Interconnect.

2.12.3.1 L4 Fast Peripheral Memory Map

Cortex-A8 and L3 Masters C674x DSP

START START

ADDRESS ADDRESS

(HEX) (HEX)

0x4A00_0000 0x4A00_07FF 0x0A00_0000 0x0A00_07FF 2KB L4 Fast Configuration - Address/Protection

0x4A00_0800 0x4A00_0FFF 0x0A00_0800 0x0A00_0FFF 2KB L4 Fast Configuration - Link Agent (LA)

0x4A00_1000 0x4A00_13FF 0x0A00_1000 0x0A00_13FF 1KB L4 Fast Configuration - Initiator Port (IP0)

0x4A00_1400 0x4A00_17FF 0x0A00_1400 0x0A00_17FF 1KB L4 Fast Configuration - Initiator Port (IP1)

0x4A00_1800 0x4A00_1FFF 0x0A00_1800 0x0A00_1FFF 2KB Reserved

0x4A00_2000 0x4A07_FFFF 0x0A00_2000 0x0A07_FFFF 504KB Reserved

0x4A08_0000 0x4A0F_FFFF 0x0A08_0000 0x0A0F_FFFF 512KB Reserved

0x4A10_0000 0x4A10_7FFF 0x0A10_0000 0x0A10_7FFF 32KB EMAC SW Peripheral Registers

0x4A10_8000 0x4A10_8FFF 0x0A10_8000 0x0A10_8FFF 4KB EMAC SW Support Registers

0x4A14_0000 0x4A14_FFFF 0x0A14_0000 0x0A14_FFFF 64KB SATA Peripheral Registers

0x4A15_0000 0x4A15_0FFF 0x0A15_0000 0x0A15_0FFF 4KB SATA Support Registers

0x4A15_1000 0x4A17_FFFF 0x0A15_1000 0x0A17_FFFF 188KB Reserved

0x4A18_0000 0x4A1A_1FFF 0x0A18_0000 0x0A1A_1FFF 136KB Reserved

0x4A1A_2000 0x4A1A_3FFF 0x0A1A_2000 0x0A1A_3FFF 8KB McASP3 Configuration Peripheral Registers

0x4A1A_4000 0x4A1A_4FFF 0x0A1A_4000 0x0A1A_4FFF 4KB McASP3 Configuration Support Registers

0x4A1A_5000 0x4A1A_5FFF 0x0A1A_5000 0x0A1A_5FFF 4KB McASP3 Data Peripheral Registers

0x4A1A_6000 0x4A1A_6FFF 0x0A1A_6000 0x0A1A_6FFF 4KB McASP3 Data Support Registers

0x4A1A7000 0x4A1A7FFF 0x0A1A_7000 0x0A1A_7FFF 4KB Reserved

0x4A1A_8000 0x4A1A_9FFF 0x0A1A_8000 0x0A1A_9FFF 8KB McASP4 Configuration Peripheral Registers

0x4A1A_A000 0x4A1A_AFFF 0x0A1A_A000 0x0A1A_AFFF 4KB McASP4 Configuration Support Registers

0x4A1A_B000 0x4A1A_BFFF 0x0A1A_B000 0x0A1A_BFFF 4KB McASP4 Data Peripheral Registers

0x4A1A_C000 0x4A1A_CFFF 0x0A1A_C000 0x0A1A_CFFF 4KB McASP4 Data Support Registers

0x4A1A_D000 0x4A1A_DFFF 0x0A1A_D000 0x0A1A_DFFF 4KB Reserved

0x4A1A_E000 0x4A1A_FFFF 0x0A1A_E000 0x0A1A_FFFF 8KB McASP5 Configuration Peripheral Registers

0x4A1B_0000 0x4A1B_0FFF 0x0A1B_0000 0x0A1B_0FFF 4KB McASP5 Configuration Support Registers

0x4A1B_1000 0x4A1B_1FFF 0x0A1B_1000 0x0A1B_1FFF 4KB McASP5 Data Peripheral Registers

0x4A1B_2000 0x4A1B_2FFF 0x0A1B_2000 0x0A1B_2FFF 4KB McASP5 Data Support Registers

0x4A1B_3000 0x4A1B_5FFF 0x0A1B_3000 0x0A1B_5FFF 12KB Reserved

0x4A1B_6000 0x4A1B_6FFF 0x0A1B_6000 0x0A1B_6FFF 4KB Reserved

0x4A1B_4000 0x4AFF_FFFF 0x0A1B_4000 0x0AFF_FFFF 14632KB Reserved

END ADDRESS END ADDRESS

(HEX) (HEX)

ZHCS057–MARCH 2011

Table 2-5. L4 Fast Peripheral Memory Map

SIZE DEVICE NAME

(AP)

Copyright © 2011, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 22

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

2.12.3.2 L4 Slow Peripheral Memory Map

Cortex-A8 and L3 Masters C674x DSP

START

ADDRESS

(HEX)

0x4800_0000 0x4800_07FF 0x0800_0000 0x0800_07FF 2KB L4 Slow Configuration –

0x4800_0800 0x4800_0FFF 0x0800_0800 0x0800_0FFF 2KB L4 Slow Configuration – Link Agent

0x4800_1000 0x4800_13FF 0x0800_1000 0x0800_13FF 1KB L4 Slow Configuration – Initiator Port

0x4800_1400 0x4800_17FF 0x0800_1400 0x0800_17FF 1KB L4 Slow Configuration – Initiator Port

0x4800_1800 0x4800_1FFF 0x0800_1800 0x0800_1FFF 2KB Reserved

0x4800_2000 0x4800_7FFF 0x0800_2000 0x0800_7FFF 24KB Reserved

0x4800_8000 0x4800_8FFF 0x0800_8000 0x0800_8FFF 32KB Reserved

0x4801_0000 0x4801_0FFF 0x0801_0000 0x0801_0FFF 4KB DEMMU Peripheral Registers

0x4801_1000 0x4801_1FFF 0x0801_1000 0x0801_1FFF 4KB DEMMU Support Registers

0x4801_2000 0x4801_FFFF 0x0801_2000 0x0801_FFFF 56KB Reserved

0x4802_0000 0x4802_0FFF 0x0802_0000 0x0802_0FFF 4KB UART0 Peripheral Registers

0x4802_1000 0x4802_1FFF 0x0802_1000 0x0802_1FFF 4KB UART0 Support Registers

0x4802_2000 0x4802_2FFF 0x0802_2000 0x0802_2FFF 4KB UART1 Peripheral Registers

0x4802_3000 0x4802_3FFF 0x0802_3000 0x0802_3FFF 4KB UART1 Support Registers

0x4802_4000 0x4802_4FFF 0x0802_4000 0x0802_4FFF 4KB UART2 Peripheral Registers

0x4802_5000 0x4802_5FFF 0x0802_5000 0x0802_5FFF 4KB UART2 Support Registers

0x4802_6000 0x4802_7FFF 0x0802_6000 0x0802_7FFF 8KB Reserved

0x4802_8000 0x4802_8FFF 0x0802_8000 0x0802_8FFF 4KB I2C0 Peripheral Registers

0x4802_9000 0x4802_9FFF 0x0802_9000 0x0802_9FFF 4KB I2C0 Support Registers

0x4802_A000 0x4802_AFFF 0x0802_A000 0x0802_AFFF 4KB I2C1 Peripheral Registers

0x4802_B000 0x4802_BFFF 0x0802_B000 0x0802_BFFF 4KB I2C1 Support Registers

0x4802_C000 0x4802_DFFF 0x0802_C000 0x0802_DFFF 8KB Reserved

0x4802_E000 0x4802_EFFF 0x0802_E000 0x0802_EFFF 4KB TIMER1 Peripheral Registers

0x4802_F000 0x4802_FFFF 0x0802_F000 0x0802_FFFF 4KB TIMER1 Support Registers

0x4803_0000 0x4803_0FFF 0x0803_0000 0x0803_0FFF 4KB SPI0 Peripheral Registers

0x4803_1000 0x4803_1FFF 0x0803_1000 0x0803_1FFF 4KB SPI0 Support Registers

0x4803_2000 0x4803_2FFF 0x0803_2000 0x0803_2FFF 4KB GPIO0 Peripheral Registers

0x4803_3000 0x4803_3FFF 0x0803_3000 0x0803_3FFF 4KB GPIO0 Support Registers

0x4803_4000 0x4803_7FFF 0x0803_4000 0x0803_7FFF 16KB Reserved

0x4803_8000 0x4803_9FFF 0x0803_8000 0x0803_9FFF 8KB McASP0 CFG Peripheral Registers

0x4803_A000 0x4803_AFFF 0x0803_A000 0x0803_AFFF 4KB McASP0 CFG Support Registers

0x4803_B000 0x4803_BFFF 0x0803_B000 0x0803_BFFF 4KB Reserved

0x4803_C000 0x4803_DFFF 0x0803_C000 0x0803_DFFF 8KB McASP1 CFG Peripheral Registers

0x4803_E000 0x4803_EFFF 0x0803_E000 0x0803_EFFF 4KB McASP1 CFG Support Registers

0x4803_F000 0x4803_FFFF 0x0803_F000 0x0803_FFFF 4KB Reserved

0x4804_0000 0x4804_0FFF 0x0804_0000 0x0804_0FFF 4KB TIMER2 Peripheral Registers

0x4804_1000 0x4804_1FFF 0x0804_1000 0x0804_1FFF 4KB TIMER2 Support Registers

0x4804_2000 0x4804_2FFF 0x0804_2000 0x0804_2FFF 4KB TIMER3 Peripheral Registers

0x4804_3000 0x4804_3FFF 0x0804_3000 0x0804_3FFF 4KB TIMER3 Support Registers

0x4804_4000 0x4804_4FFF 0x0804_4000 0x0804_4FFF 4KB TIMER4 Peripheral Registers

END ADDRESS START END ADDRESS

(HEX) ADDRESS (HEX) (HEX)

www.ti.com.cn

Table 2-6. L4 Slow Peripheral Memory Map

SIZE DEVICE NAME

Address/Protection (AP)

(LA)

(IP0)

(IP1)

22 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 23

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

Table 2-6. L4 Slow Peripheral Memory Map (continued)

Cortex-A8 and L3 Masters C674x DSP

START

ADDRESS

(HEX)

0x4804_5000 0x4804_5FFF 0x0804_5000 0x0804_5FFF 4KB TIMER4 Support Registers

0x4804_6000 0x4804_6FFF 0x0804_6000 0x0804_6FFF 4KB TIMER5 Peripheral Registers

0x4804_7000 0x4804_7FFF 0x0804_7000 0x0804_7FFF 4KB TIMER5 Support Registers

0x4804_8000 0x4804_8FFF 0x0804_8000 0x0804_8FFF 4KB TIMER6 Peripheral Registers

0x4804_9000 0x4804_9FFF 0x0804_9000 0x0804_9FFF 4KB TIMER6 Support Registers

0x4804_A000 0x4804_AFFF 0x0804_A000 0x0804_AFFF 4KB TIMER7 Peripheral Registers

0x4804_B000 0x4804_BFFF 0x0804_B000 0x0804_BFFF 4KB TIMER7 Support Registers

0x4804_C000 0x4804_CFFF 0x0804_C000 0x0804_CFFF 4KB GPIO1 Peripheral Registers

0x4804_D000 0x4804_DFFF 0x0804_D000 0x0804_DFFF 4KB GPIO1 Support Registers

0x4804_E000 0x4804_FFFF 0x0804_E000 0x0804_FFFF 8KB Reserved

0x4805_0000 0x4805_1FFF 0x0805_0000 0x0805_1FFF 8KB McASP2 CFG Peripheral Registers

0x4805_2000 0x4805_2FFF 0x0805_2000 0x0805_2FFF 4KB McASP2 CFG Support Registers

0x4805_3000 0x4805_FFFF 0x0805_3000 0x0805_FFFF 52KB Reserved

0x4806_0000 0x4806_FFFF 0x0806_0000 0x0806_FFFF 64KB MMC/SD/SDIO Peripheral Registers

0x4807_0000 0x4807_0FFF 0x0807_0000 0x0807_0FFF 4KB MMC/SD/SDIO Support Registers

0x4807_1000 0x4807_FFFF 0x0807_1000 0x0807_FFFF 60KB Reserved

0x4808_0000 0x4808_FFFF 0x0808_0000 0x0808_FFFF 64KB ELM Peripheral Registers

0x4809_0000 0x4809_0FFF 0x0809_0000 0x0809_0FFF 4KB ELM Support Registers

0x4809_1000 0x4809_FFFF 0x0809_1000 0x0809_FFFF 60KB Reserved

0x480A_0000 0x480A_FFFF 0x080A_0000 0x080A_FFFF 64KB Reserved

0x480B_0000 0x480B_0FFF 0x080B_0000 0x080B_0FFF 4KB Reserved

0x480B_1000 0x480B_FFFF 0x080B_1000 0x080B_FFFF 60KB Reserved

0x480C_0000 0x480C_0FFF 0x080C_0000 0x080C_0FFF 4KB RTC Peripheral Registers

0x480C_1000 0x480C_1FFF 0x080C_1000 0x080C_1FFF 4KB RTC Support Registers

0x480C_2000 0x480C_3FFF 0x080C_2000 0x080C_3FFF 8KB Reserved

0x480C_4000 0x480C_7FFF 0x080C_4000 0x080C_7FFF 16KB Reserved

0x480C_8000 0x480C_8FFF 0x080C_8000 0x080C_8FFF 4KB Mailbox Peripheral Registers

0x480C_9000 0x480C_9FFF 0x080C_9000 0x080C_9FFF 4KB Mailbox Support Registers

0x480C_A000 0x480C_AFFF 0x080C_A000 0x080C_AFFF 4KB Spinlock Peripheral Registers

0x480C_B000 0x480C_BFFF 0x080C_B000 0x080C_BFFF 4KB Spinlock Support Registers

0x480C_C000 0x480F_FFFF 0x080C_C000 0x080F_FFFF 208KB Reserved

0x4810_0000 0x4811_FFFF 0x0810_0000 0x0811_FFFF 128KB HDVPSS Peripheral Registers

0x4812_0000 0x4812_0FFF 0x0812_0000 0x0812_0FFF 4KB HDVPSS Support Registers

0x4812_1000 0x4812_1FFF 0x0812_1000 0x0812_1FFF 4KB Reserved

0x4812_2000 0x4812_2FFF 0x0812_2000 0x0812_2FFF 4KB HDMI Peripheral Registers

0x4812_3000 0x4812_3FFF 0x0812_3000 0x0812_3FFF 4KB HDMI Support Registers

0x4812_4000 0x4813_FFFF 0x0812_4000 0x0813_FFFF 112KB Reserved

0x4814_0000 0x4815_FFFF 0x0814_0000 0x0815_FFFF 128KB Control Module Peripheral Registers

0x4816_0000 0x4816_0FFF 0x0816_0000 0x0816_0FFF 4KB Control Module Support Registers

0x4816_1000 0x4817_FFFF 0x0816_1000 0x0817_FFFF 124KB Reserved

0x4818_0000 0x4818_2FFF 0x0818_0000 0x0818_2FFF 12KB PRCM Peripheral Registers

0x4818_3000 0x4818_3FFF 0x0818_3000 0x0818_3FFF 4KB PRCM Support Registers

0x4818_4000 0x4818_7FFF 0x0818_4000 0x0818_7FFF 16KB Reserved

0x4818_8000 0x4818_8FFF 0x0818_8000 0x0818_8FFF 4KB SmartReflex0 Peripheral Registers

0x4818_9000 0x4818_9FFF 0x0818_9000 0x0818_9FFF 4KB SmartReflex0 Support Registers

END ADDRESS START END ADDRESS

(HEX) ADDRESS (HEX) (HEX)

ZHCS057–MARCH 2011

SIZE DEVICE NAME

Copyright © 2011, Texas Instruments Incorporated Device Overview 23

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 24

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

Cortex-A8 and L3 Masters C674x DSP

START

ADDRESS

(HEX)

0x4818_A000 0x4818_AFFF 0x0818_A000 0x0818_AFFF 4KB SmartReflex1 Peripheral Registers

0x4818_B000 0x4818_BFFF 0x0818_B000 0x0818_BFFF 4KB SmartReflex1 Support Registers

0x4818_C000 0x4818_CFFF 0x0818_C000 0x0818_CFFF 4KB OCP Watchpoint Peripheral Registers

0x4818_D000 0x4818_DFFF 0x0818_D000 0x0818_DFFF 4KB OCP Watchpoint Support Registers

0x4818_E000 0x4818_EFFF 0x0818_E000 0x0818_EFFF 4KB Reserved

0x4818_F000 0x4818_FFFF 0x0818_F000 0x0818_FFFF 4KB Reserved

0x4819_0000 0x4819_0FFF 0x0819_0000 0x0819_0FFF 4KB SmartReflex2 Peripheral Registers

0x4819_1000 0x4819_1FFF 0x0819_1000 0x0819_1FFF 4KB SmartReflex2 Support Registers

0x4819_2000 0x4819_2FFF 0x0819_2000 0x0819_2FFF 4KB SmartReflex3 Peripheral Registers

0x4819_3000 0x4819_3FFF 0x0819_3000 0x0819_3FFF 4KB SmartReflex3 Support Registers

0x4819_4000 0x4819_BFFF 0x0819_4000 0x0819_BFFF 32KB Reserved

0x4819_C000 0x481F_FFFF 0x0819_C000 0x081F_FFFF 400KB Reserved

0x4819_C000 0x4819_CFFF 0x0819_C000 0x0819_CFFF 4KB I2C2 Peripheral Registers

0x4819_D000 0x4819_DFFF 0x0819_D000 0x0819_DFFF 4KB I2C2 Support Registers

0x4819_E000 0x4819_EFFF 0x0819_E000 0x0819_EFFF 4KB I2C3 Peripheral Registers

0x4819_F000 0x4819_FFFF 0x0819_F000 0x0819_FFFF 4KB I2C3 Support Registers

0x481A_0000 0x481A_0FFF 0x081A_0000 0x081A_0FFF 4KB SPI1 Peripheral Registers

0x481A_1000 0x481A_1FFF 0x081A_1000 0x081A_1FFF 4KB SPI1 Support Registers

0x481A_2000 0x481A_2FFF 0x081A_2000 0x081A_2FFF 4KB SPI2 Peripheral Registers

0x481A_3000 0x481A_3FFF 0x081A_3000 0x081A_3FFF 4KB SPI2 Support Registers

0x481A_4000 0x481A_4FFF 0x081A_4000 0x081A_4FFF 4KB SPI3 Peripheral Registers

0x481A_5000 0x481A_5FFF 0x081A_5000 0x081A_5FFF 4KB SPI3 Support Registers

0x481A_6000 0x481A_6FFF 0x081A_6000 0x081A_6FFF 4KB UART3 Peripheral Registers

0x481A_7000 0x481A_7FFF 0x081A_7000 0x081A_7FFF 4KB UART3 Support Registers

0x481A_8000 0x481A_8FFF 0x081A_8000 0x081A_8FFF 4KB UART4 Peripheral Registers

0x481A_9000 0x481A_9FFF 0x081A_9000 0x081A_9FFF 4KB UART4 Support Registers

0x481A_A000 0x481A_AFFF 0x081A_A000 0x081A_AFFF 4KB UART5 Peripheral Registers

0x481A_B000 0x481A_BFFF 0x081A_B000 0x081A_BFFF 4KB UART5 Support Registers

0x481A_C000 0x481A_CFFF 0x081A_C000 0x081A_CFFF 4KB GPIO2 Peripheral Registers

0x481A_D000 0x481A_DFFF 0x081A_D000 0x081A_DFFF 4KB GPIO2 Support Registers

0x481A_E000 0x481A_EFFF 0x081A_E000 0x081A_EFFF 4KB GPIO3 Peripheral Registers

0x481A_F000 0x481A_FFFF 0x081A_F000 0x081A_FFFF 4KB GPIO3 Support Registers

0x481B_0000 0x481B_FFFF 0x081B_0000 0x081B_FFFF 64KB Reserved

0x481C_0000 0x481C_0FFF 0x081C_0000 0x081C_0FFF 4KB Reserved

0x481C_1000 0x481C_1FFF 0x081C_1000 0x081C_1FFF 4KB TIMER8 Peripheral Registers

0x481C_2000 0x481C_2FFF 0x081C_2000 0x081C_2FFF 4KB TIMER8 Support Registers

0x481C_3000 0x481C_3FFF 0x081C_3000 0x081C_3FFF 4KB SYNCTIMER32K Peripheral Registers

0x481C_4000 0x481C_4FFF 0x081C_4000 0x081C_4FFF 4KB SYNCTIMER32K Support Registers

0x481C_5000 0x481C_5FFF 0x081C_5000 0x081C_5FFF 4KB PLLSS Peripheral Registers

0x481C_6000 0x481C_6FFF 0x081C_6000 0x081C_6FFF 4KB PLLSS

0x481C_7000 0x481C_7FFF 0x081C_7000 0x081C_7FFF 4KB WDT0 Peripheral Registers

0x481C_8000 0x481C_8FFF 0x081C_8000 0x081C_8FFF 4KB WDT0 Support Registers

0x481C_9000 0x481C_9FFF 0x081C_9000 0x081C_9FFF 8KB Reserved

0x481C_A000 0x481C_BFFF 0x081C_A000 0x081C_BFFF 8KB Reserved

0x481C_C000 0x481C_DFFF 0x081C_C000 0x081C_DFFF 8KB DCAN0 Peripheral Registers

END ADDRESS START END ADDRESS

(HEX) ADDRESS (HEX) (HEX)

www.ti.com.cn

Table 2-6. L4 Slow Peripheral Memory Map (continued)

SIZE DEVICE NAME

24 Device Overview Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 25

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

www.ti.com.cn

ZHCS057–MARCH 2011

Table 2-6. L4 Slow Peripheral Memory Map (continued)

Cortex-A8 and L3 Masters C674x DSP

START

ADDRESS

(HEX)

0x481C_E000 0x481C_FFFF 0x081C_E000 0x081C_FFFF 8KB DCAN0 Support Registers

0x481D_0000 0x481D_1FFF 0x081D_0000 0x081D_1FFF 8KB DCAN1 Peripheral Registers

0x481D_2000 0x481D_3FFF 0x081D_2000 0x081D_3FFF 8KB DCAN1 Support Registers

0x481D_4000 0x481D_5FFF 0x081D_4000 0x081D_5FFF 8KB Reserved

0x481D_6000 0x481D_6FFF 0x081D_6000 0x081D_6FFF 4KB Reserved

0x481D_7000 0x481D_7FFF 0x081D_7000 0x081D_7FFF 4KB Reserved

0x481D_8000 0x481E_7FFF 0x081D_8000 0x081E_7FFF 64KB MMC/SD/SDIO1 Peripheral Registers

0x481E_8000 0x481E_8FFF 0x081E_8000 0x081E_8FFF 4KB MMC/SD/SDIO1 Support Registers

0x481E_9000 0x481F_FFFF 0x081E_9000 0x081F_FFFF 52KB Reserved

0x4820_0000 0x4820_0FFF 0x0820_0000 0x0820_0FFF 4KB Interrupt controller

0x4820_1000 0x4823_FFFF 0x0820_1000 0x0823_FFFF 252KB Reserved

0x4824_0000 0x4824_0FFF 0x0824_0000 0x0824_0FFF 4KB MPUSS config register

0x4824_1000 0x4827_FFFF 0x0824_1000 0x0827_FFFF 252KB Reserved

0x4828_0000 0x4828_0FFF 0x0828_0000 0x0828_0FFF 4KB SSM

0x4828_1000 0x482F_FFFF 0x0828_1000 0x082F_FFFF 508KB Reserved

0x4830_0000 0x48FF_FFFF 0x0830_0000 0x08FF_FFFF 13MB Reserved

(1) These regions decoded internally by the Cortex™-A8 Subsystem and are not physically part of the L4 Slow. They are included here only

for reference when considering the Cortex™-A8 Memory Map. For Masters other than the Cortex-A8 these regions are reserved.

(2) These regions decoded internally by the Cortex™-A8 Subsystem and are not physically part of the L4 Slow. They are included here only

for reference when considering the Cortex™-A8 Memory Map. For Masters other than the Cortex-A8 these regions are reserved.

END ADDRESS START END ADDRESS

(HEX) ADDRESS (HEX) (HEX)

SIZE DEVICE NAME

(1)

(1)

(1)

(1)

(1)

(2)

2.12.4 DDR DMM TILER Extended Addressing Map

The Tiler includes an additional 4-GBytes of addressing range, enabled by a 33rd address bit, to access

the frame buffer in rotated and mirrored views. shows the details of the Tiler Extended Address Mapping.

This entirety of this additional range is only accessible to the HDVPSS and ISS subsystems. However,

other masters can access any one single view through the 512-MB Tiler region in the base 4GByte

address memory map.

Table 2-7. DDR DMM TILER Extended Address Mapping

BLOCK NAME SIZE DESCRIPTION

Tiler View 0 0x1 0000_0000 0x1 1FFF_FFFF 512MB Natural 0° View

Tiler View 1 0x1 2000_0000 0x1 3FFF_FFFF 512MB 0° with Vertical Mirror

Tiler View 2 0x1 4000_0000 0x1 5FFF_FFFF 512MB 0° with Horizontal Mirror

Tiler View 3 0x1 6000_0000 0x1 7FFF_FFFF 512MB 180° View

Tiler View 4 0x1 8000_0000 0x1 9FFF_FFFF 512MB 90° with Vertical Mirror

Tiler View 5 0x1 A000_0000 0x1 BFFF_FFFF 512MB 270° View

Tiler View 6 0x1 C000_0000 0x1 DFFF_FFFF 512MB 90° View

Tiler View 7 0x1 E000_0000 0x1 FFFF_FFFF 512MB 90° with Horizontal Mirror

START ADDRESS END ADDRESS

(HEX) (HEX)

View

View

View

View

Copyright © 2011, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 26

PRODUCTPREVIEW

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

3 Device Pins

3.1 Pin Maps

Figure 3-1 through Figure 3-8 show the bottom view of the package pin assignments in eight pin maps (A,

B, C, D, E, F, G, and H).

www.ti.com.cn

26 Device Pins Copyright © 2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Page 27

PRODUCTPREVIEW

VDDA_1P8

P

N

M

A

B

C

D

E

F

G

H

J

K

L

1 2

3

4

5

6

7

MCA[3]_AXR[0]/

TIM4_IO/

GP0[18]

MCA[3]_AXR[1]/

TIM5_IO/

GP0[19]

AUD_CLKIN2/

MCA[0]_AXR[9]/

MCA[2]_AHCLKX/

MCA[5]_ACHCLKX/

EDMA_EVT2/

TIM3_IO/

GP0[9]

AUD_CLKIN0/

MCA[0]_AXR[7]/

MCA[0]_AHCLKX/

MCA[3]_AHCLKX]/

USB1_DRVVBUS

MCA[0]_AXR[1]/

I2C[3]_SCL

MCA[0]_AXR[3]

MCA[0]_AFSR/

MCA[5]_AXR[3]

MCA[0]_AXR[7]/

MCB_DX

MCA[0]_AFSX

MCA[1]_AFSR/

MCA[1]_AXR[5]

MCA[0]_AXR[5]/

MCA[1]_AXR[9]

SD0_CMD/

SD1_CMD/

GP0[2]

MCA[2]_AXR[0]/

SD0_DAT[6]/

UART5_RXD

GP0[12]

SD1_CMD/

GP0[0]

SD1_DAT[2]_SDRW

SD1_CLK SD1_DAT[1]_SDIRQ

SD1_DAT[3] DVDD_SD

MCA[1]_AXR[3]/

MCB_CLKR

DVDD

MCA[0]_AXR[9]/

MCB_CLKX/

MCB_CLKR

CLKIN32/

CLKOUT0/

TIM3_IO/

GP3[31]

NMI

MCA[5]_AXR[0]/

MCA[4]_AXR[2]/

GP0[27]

MCA[4]_ACLKX/

GP0[21]

MCA[0]_AXR[6]/

MCB_DR

MCA[1]_ACLKR/

MCA[1]_AXR[4]

SD1_DAT[0]

MCA[0]_ACLKR/

MCA[5]_AXR[2]

MCA[0]_AXR[8]/

MCB_FSX/

MCB_FSR

MCA[5]_ACLKX/

GP0[25]

MCA[5]_AXR[1]/

MCA[4]_AXR[3]/

TIM7_IO/

GP0[28]

RSTOUT_WD_OUT

MCA[4]_AFSX/

GP0[22]

MCA[4]_AXR[1]/

TIM6_IO/

GP0[24]

MCA[3]_AFSX/

GP0[17]

RESET

MCA[2]_AXR[3]/

MCA[1]_AXR[7]/

TIM3_IO/

GP0[15]

MCA[3]_AXR[3]/

MCA[1]_AXR[9]

MCA[4]_AXR[0]/

GP0[23]

MCA[3]_AXR[2]/

MCA[1]_AXR[8]/

GP0[20]

POR

DDR[1]_D[2]DDR[1]_D[3]

DDR[1]_DQS[0]

DDR[1]_DQS[0]

DDR[1]_D[8]

DDR[1]_D[7]

DDR[1]_DQM[1]

DDR[1]_VTP

DDR[1]_D[11]VSS

DDR[1]_DQM[0]

DDR[1]_D[1]

DDR[1]_D[5]DDR[1]_D[0]

DDR[1]_D[13]DDR[1]_D[10]

DDR[1]_D[12]DDR[1]_DQS[1]

DDR[1]_D[14]

DDR[1]_DQS[1]

DDR[1]_D[22]DDR[1]_D[9]

DDR[1]_D[20]DDR[1]_D[18]

DDR[1]_DQS[2]

DDR[1]_D[19]

DDR[1]_DQS[2]DDR[1]_D[15]

DDR[1]_D[6]

MCA[3]_ACLKX/

GP0[16]

DDR[1]_D[4]

DDR[1]_D[17]

DDR[1]_D[21]

DDR[1]_D[23]

DDR[1]_D[27]

MCA[5]_AFSX/

GP0[26]

MCA[0]_AXR[0]

MCA[0]_AXR[2]/

I2C[3]_SDA

A B C D

E F G H

TMS320DM8148, TMS320DM8147

www.ti.com.cn

ZHCS057–MARCH 2011

Figure 3-1. Pin Map A

Copyright © 2011, Texas Instruments Incorporated Device Pins 27

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 28

PRODUCTPREVIEW

P

N

M

A

B

C

D

E

F

G

H

J

K

L

8

9

10

11

12

13 14

DDR[1]_DQM[2] DDR[1]_DQM[3]

DDR[1]_D[16]

CVDD

VSS CVDD_DSP

DVDD VSS

VSS

CVDD_DSP

DVDD DVDD_SD LDOCAP_DSP VDDA_DSPPLL_1P8 CVDD VSS CVDD

CVDD_HDVICP CVDD_HDVICP

CVDD_HDVICP CVDD_HDVICP

VSS

DVDD_DDR[1]

CVDD_HDVICP

VSS

CVDD_DSP

CVDD_DSP

LDOCAP_DSPRAM

CVDD_DSP

CVDD_DSP

CVDD_DSP VSS

VSS

DVDD_DDR[1]

DDR[1]_ODT[0]

DVDD_DDR[1]

DDR[1]_CKE

VSS

DVDD_DDR[1]

DVDD_DDR[1]

DVDD_DDR[1]DDR[1]_D[25]

DDR[1]_D[24]DDR[1]_D[26]

DVDD_DDR[1]DVDD_DDR[1]

VSSDDR[1]_D[29]

DDR[1]_D[28]DDR[1]_D[30]

DDR[1]_D[31]DDR[1]_DQS[3]

DDR[1]_A[7]

DDR[1]_DQS[3]

DDR[1]_ODT[1]DDR[1]_A[1]

DDR[1]_A[13]

DDR[1]_A[2]

DDR[1]_A[0]DDR[1]_A[12]

DDR[1]_A[11]

DDR[1]_BA[1]

DDR[1]_A[6]

DDR[1]_BA[2]

DDR[1]_A[9]

DDR[1]_RAS

DDR[1]_CLKDDR[1]_A[5]

DDR[1]_CLKVSS

DVDD_DDR[1]

DDR[1]_A[10] DDR[1]_BA[0]

DDR[1]_A[8]

DDR[1]_A[4]

DDR[1]_A[3]

CVDD_DSP VSS CVDD

LDOCAP_HDVICP LDOCAP_HDVICPRAM VSS

DDR[1]_A[14]

VREFSSTL_DDR[1]

DDR[1]_RST DDR[1]_CS[1]

DDR[1]_CS[0]

DDR[1]_WE

DDR[1]_CAS

A B C D

E F G H

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

www.ti.com.cn

Figure 3-2. Pin Map B

28 Device Pins Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 29

PRODUCTPREVIEW

15

16

17

18

19

20 21

VREFSSTL_DDR[0] DVDD_DDR[0]

VDDA_DDRPLL_1P8

DVDD_DDR[0] DVDD_DDR[0]

VSS VSS

CVDD VSS

VSS CVDD

VSS

VSS

VSS CVDD VSS LDOCAP_RAM0 VSS DVDD_GPMC VSS

VSS VSS

DVDD_GPMC VSS

DDR[0]_D[18]

DVDD_GPMC

VSS

CVDD

CVDD

LDOCAP_RAM2

VSS

CVDD VDDA_1P8

DVDD_GPMC

DVDD_DDR[0]

DVDD_DDR[0]

DVDD_DDR[0]

DDR[0]_CKE

VSS

DDR[0]_ODT[1] DDR[0]_D[24]DVDD_DDR[0]

DDR[0]_A[14]DDR[0]_BA[0]

DDR[0]_A[12]DDR[0]_A[3]

DDR[0]_A[11]DDR[0]_A[4]

DDR[0]_WE

DDR[0]_A[9]

DDR[0]_CLK

DDR[0]_A[8]

DDR[0]_CLK

DDR[0]_A[6]

DDR[0]_CS[0]

DDR[0]_A[13]

DDR[0]_A[7]

DDR[0]_CAS

DDR[0]_RASDDR[0]_A[5]

DDR[0]_BA[2]VSS

DDR[0]_D[30]

DDR[0]_D[29]

DDR[0]_D[31]DDR[0]_A[0]

DDR[0]_BA[1]DDR[0]_A[10]

DDR[0]_D[26]

DDR[0]_A[1] DDR[0]_D[25]

DVDD_DDR[0]

DDR[0]_DQS[3]

DDR[0]_DQS[3]

VSS CVDD VSS

CVDD VDDA_L3PLL_1P8 CVDD

DDR[0]_A[2]

DDR[0]_D[19]DDR[0]_CS[1]

DDR[0]_ODT[0]

DDR[0]_RST

P

N

M

A

B

C

D

E

F

G

H

J

K

L

VSS

DDR[0]_D[28]

DDR[0]_DQM[3]

DVDD_DDR[0]

A B C D

E F G H

TMS320DM8148, TMS320DM8147

www.ti.com.cn

ZHCS057–MARCH 2011

Figure 3-3. Pin Map C

Copyright © 2011, Texas Instruments Incorporated Device Pins 29

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 30

PRODUCTPREVIEW

P

N

M

A

B

C

D

E

F

G

H

J

K

L

22

23

24

25

26

27

28

EMAC[0]_MRXD[0]/

VIN[1]B_D[5]/

EMAC[0]_RMTXD[0]/

GP3[28]

EMAC[0]_RGTXD[0]/

EMAC[0]_MTXD[4]/

EMAC[1]_RMRXER/

GPMC_A[11]/

EMAC[1]_RGTXD[2]/

UART4_RTS

EMAC[0]_MTXD[2]/

EMAC[1]_RMRXD[0]/

GPMC_A[9]/

UART4_TXD

EMAC[1]_RGTXCTL/

EMAC[0]_MTXD[6]/

EMAC[1]_RMTXD[0]/

GPMC_A[13]/

UART1_TXD

EMAC[1]_RGRXD[0]/

EMAC[0]_MTXEN/

EMAC[1]_RMTXEN/

GPMC_A[15]/

EMAC[1]_RGRXD[2]/

UART1_RTS

EMAC[0]_MRXDV/

GPMC_A[5]/

SPI[2]_SCLK

EMAC[1]_RGRXD[1]/

EMAC[0]_GMTCLK/

GPMC_A[6]/

SPI[2]_D[1]

EMAC[1]_RGRXC/

VSS

EMAC[0]_MCOL/

VIN[1]B_D[1]/

EMAC[0]_RMRXD[0]/

GP3[24]

EMAC[0]_RGRXCTL/

VDDA_1P8

SD2_SCLK/

GP1[15]

VSS

SD2_DAT[6]/

GPMC_A[25]/

GPMC_A[21]/

UART2_TXD/

GP1[20]

SD2_DAT[5]/

GPMC_A[26]/

GPMC_A[22]/

TIM6_IO/

GP1[21]

EMAC[0]_MRXD[1]/

VIN[1]B_D[6]/

EMAC[0]_RMTXD[1]/

GP3[29]

EMAC[0]_RGRXD[0]/

MDIO/

GP1[12]

GPMC_CS[4]/

SD2_CMD/

GP1[8]

GPMC_CS[3]

SPI[2]_SCS[0]

/

VIN[1]B_CLK/

/

GP1[26]

RSV13 RSV12

RSV11 RSV10

RSV8 RSV9

SD2_DAT[3]/

GPMC_A[1]/

GP2[5]

MDCLK/

GP1[11]

RSV7

GPMC_CS[1]/

GPMC_A[25]/

GP1[24]

SD2_DAT[1]_ /

GPMC_A[3]/

GP1[13]

SDIRQ

EMAC[0]_MTCLK/

VIN[1]B_D[0]/

/

I2C[2]_SDA/

GP3[23]

EMAC[0]_RGRXC/

SPI[3]_SCS[3]

GPMC_CS[2]/

GPMC_A[24]/

GP1[25]

SD2_DAT[7]/

GPMC_A[24]/

GPMC_A[20]/

UART2_RXD/

GP1[19]

GPMC_ _ALE/

/

TIM5_IO/

GP1[28]

ADV

GPMC_CS[6]

SD2_DAT[0]/

GPMC_A[4]/

GP1[14]

RSV6

SD2_DAT[2]_SDR /

GPMC_A[2]/

GP2[6]

W

EMAC[0]_MTXD[0]/

GPMC_A[7]/

SPI[2]_D[0]

EMAC[1]_RGRXD[3]/

EMAC[0]_MTXD[7]/

EMAC[1]_RMTXD[0]/

GPMC_A[14]/

EMAC[1]_RGTXD[3]/

UART1_CTS

EMAC[0]_MRXD[3]/

GPMC_A[27]/

GPMC_A[26]/

GPMC_A[0]/

UART5_RXD

EMAC[1]_RGRXCTL/

EMAC[0]_MTXD[1]/

GPMC_A[8]/

UART4_RXD

EMAC[1]_RGTXD[1]/

EMAC[0]_MRXER/

VIN[1]B_D[3]/

EMAC[0]_RMRXER/

GP3[26]

EMAC[0]_RGTXCTL/

EMAC[0]_MRXD[5]/

GPMC_A[2]/

EMAC[0]_RGTXD[3]/

UART5_CTS

EMAC_RMREFCLK/

TIM2_IO/

GP1[10]

EMAC[0]_MRCLK/

VIN[1]B_D[4]/

EMAC[0]_RMCRSDV/

/

GP3[27]

EMAC[0]_RGTXC/

SPI[3]_SCS[2]

EMAC[0]_MTXD[3]/

EMAC[1]_RMRXD[1]/

GPMC_A[10]/

EMAC[1]_RGTXD[0]/

UART4_CTS

EMAC[0]_MTXD[5]/

EMAC[1]_RMCRSDV/

GPMC_A[12]/

UART1_RXD

EMAC[1]_RGTXC/

DDR[0]_D[17]

DDR[0]_D[21] DDR[0]_DQM[0]

DDR[0]_D[20]

DDR[0]_DQS[0]

DDR[0]_D[22]

DDR[0]_D[7]

DDR[0]_DQS[2]

DDR[0]_D[23]

DDR[0]_DQS[2]

DDR[0]_D[27]

DDR[0]_D[3]DDR[0]_D[4]

DDR[0]_D[5] DDR[0]_D[2]

DDR[0]_D[9]DDR[0]_DQM[2]

DDR[0]_D[12]DDR[0]_D[16]

DDR[0]_D[14]DDR[0]_D[15]

DDR[0]_DQS[0]

DDR[0]_D[6]

DDR[0]_D[8]DDR[0]_D[10]

DDR[0]_VTPDDR[0]_DQS[1]

DDR[0]_D[11]DDR[0]_DQS[1]

DDR[0]_D[13]

EMAC[0]_MRXD[7]/

GPMC_A[4]/

EMAC[0]_RGTXD[1]/

SPI[2]_SCS[3]

DDR[0]_D[1]

EMAC[0]_MRXD[6]/

GPMC_A[3]/

EMAC[0]_RGTXD[2]/

UART5_RTS

DDR[0]_D[0]

DDR[0]_DQM[1]

VSS

A B C D

E F G H

TMS320DM8148, TMS320DM8147

ZHCS057–MARCH 2011

www.ti.com.cn

Figure 3-4. Pin Map D

30 Device Pins Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s): TMS320DM8148 TMS320DM8147

Submit Documentation Feedback

Page 31

PRODUCTPREVIEW

AH

AG

AF

R

T

U

V

W

Y

AA

AB

AC

AD

AE

1 2

3

4

5

6 7

SATA_RXP0

SATA_RXN0

SATA_TXN0

PCIE_RXN0 PCIE_RXP0

PCIE_TXN0 PCIE_TXP0

VSS VSS

SERDES_CLKP

SERDES_CLKN

VSS

UART0_DTR

UART3_CTS//

UART1_TXD/

GP1[4]

VSS

DEVOSC_MXO

UART0_DCD

SPI[0]_SCS[3]

/

UART3_RXD/

/

I2C[2]_SCL/

SD1_POW/

GP1[2]

UART0_RXD

DCAN0_TX/

UART2_TXD/

I2C[3]_SDA/

GP1[0]