Page 1

TMS320C3x

User’s Guide

Literature Number: SPRU031E

2558539-9761 revision L

July 1997

Printed on Recycled Paper

Page 2

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1997, Texas Instruments Incorporated

Page 3

About This Manual

Preface

Read This First

This user’s guide serves as an applications reference book for the TMS320C3x

generation of digital signal processors (DSPs). These include the TMS320C30,

TMS320C31, TMS320LC31, and TMS320C32. Throughout the book, all references to ’C3x refer collectively to the ’C30, ’C31, ’LC31 and ’C32.

This book provides information to assist managers and hardware/software

engineers in application development. It includes example code and hardware connections for various applications.

The guide shows how to use the instructions set, the architecture, and the ’C3x

interface. It presents examples for frequently used applications and discusses

more involved examples and applications. It also defines the principles involved

in many applications and gives the corresponding assembly language code for

instructional purposes and for immediate use. Whenever the detailed explanation

of the underlying theory is too extensive to be included in this manual, appropriate

references are given for further information.

Notational Conventions

This document uses the following conventions.

-

Program listings, program examples, and interactive displays are shown in

a special typeface. Examples use a bold version of the special

typeface for emphasis; interactive displays use a bold version of the

special typeface to distinguish commands that you enter from items that the

system displays (such as prompts, command output, error messages, etc.).

Here is a sample program listing:

0011 0005 0001 .field 1, 2

0012 0005 0003 .field 3, 4

0013 0005 0006 .field 6, 3

0014 0006 .even

Here is an example of a system prompt and a command that you might

enter:

C: csr –a /user/ti/simuboard/utilities

iii

Page 4

Notational Conventions

-

In syntax descriptions, the instruction, command, or directive is in bold

typeface and parameters are in an

italic typeface

. Portions of a syntax that

are in bold must be entered as shown; portions of a syntax that are in

describe the type of information that must be entered. Here is an example

of a directive syntax:

italics

.asect ”

The directive .asect has two parameters, indicated by

address

section name

”,

address

section name

. When you use .asect, the first parameter is an actual section

name, enclosed in double quotes; the second parameter is an address.

-

Square brackets ( [ and ] ) identify an optional parameter. If you use an

optional parameter, you specify the information within the brackets; you

do not enter the brackets themselves. Here is an example of an instruction

that has an optional parameter:

LALK

16-bit constant [, shift]

The LALK instruction has two parameters. The first parameter,

constant

, is required. The second parameter,

shift

, is optional. As this syntax

shows, if you use the optional second parameter, you must precede it with a

comma.

Square brackets are also used as part of the pathname specification for

VMS pathnames; in this case, the brackets are actually part of the pathname (they are not optional).

-

Braces ( { and } ) indicate a list. The symbol | (read as or) separates items

within the list. Here is an example of a list:

and

16-bit

{ * | *+ | *– }

This provides three choices: *, *+, or *–.

Unless the list is enclosed in square brackets, you must choose one item

from the list.

-

Some directives can have a varying number of parameters. For example,

the .byte directive can have up to 100 parameters. The syntax for this directive is:

.byte

value1 [, ... , valuen]

This syntax shows that .byte has at least one value parameter, but you

may supply additional value parameters, separated by commas.

iv

Page 5

Information About Cautions / Related Documentation from Texas Instruments

Information About Cautions

This book contains cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially

damage your software or equipment.

The information in a caution is provided for your protection. Please read each

caution carefully.

Related Documentation From Texas Instruments

The following books describe the TMS320 floating-point devices and related

support tools. To obtain a copy of any of these TI documents, call the Texas

Instruments Literature Response Center as indicated in the section

Need Assistance

title and literature number.

TMS320C3x General Purpose Applications User’s Guide

SPRU194) provides information to assist you in application development

for the TMS320C3x generation of digital signal processors (DSPs). It

includes example code and hardware connections for various appliances.

It also defines the principles involved in many applications and gives the

corresponding assembly language code for instructional purposes and for

immediate use.

…on page vi. When ordering, please identify the book by its

(literature number

TMS320C3x/C4x Assembly Language Tools User’s Guide

number SPRU035) describes the assembly language tools (assembler,

linker, and other tools used to develop assembly language code),

assembler directives, macros, common object file format, and symbolic

debugging directives for the ’C3x and ’C4x generations of devices.

TMS320C3x/C4x Optimizing C Compiler User’s Guide

SPRU034) describes the TMS320 floating-point C compiler. This C compiler

accepts ANSI standard C source code and produces TMS320 assembly

language source code for the ’C3x and ’C4x generations of devices.

(literature number

If You

(literature

Read This First

v

Page 6

Related Documentation from Texas Instruments / References

References

TMS320C3x C Source Debugger User’s Guide

(literature number

SPRU053) tells you how to invoke the ’C3x emulator , evaluation module,

and simulator versions of the C source debugger interface. This book

discusses various aspects of the debugger interface, including window

management, command entry , code execution, data management, and

breakpoints. It also includes a tutorial that introduces basic debugger

functionality.

TMS320 DSP Development Support Reference Guide

(literature number

SPRU011) describes the TMS320 family of digital signal processors and

the tools that support these devices. Included are code-generation tools

(compilers, assemblers, linkers, etc.) and system integration and debug

tools (simulators, emulators, evaluation modules, etc.). Also covered are

available documentation, seminars, the university program, and factory

repair and exchange.

TMS320 Third-Party Support Reference Guide

(literature number

SPRU052) alphabetically lists over 100 third parties that provide various

products that serve the family of TMS320 digital signal processors. A

myriad of products and applications are offered—software and hardware

development tools, speech recognition, image processing, noise cancellation, modems, etc.

The publications in the following reference list contain useful information

regarding functions, operations, and applications of digital signal processing

(DSP). These books also provide other references to many useful technical

papers. The reference list is organized into categories of general DSP , speech,

image processing, and digital control theory and is alphabetized by author.

-

General Digital Signal Processing

Antoniou, Andreas,

Digital Filters: Analysis and Design

. New York, NY:

McGraw-Hill Company, Inc., 1979.

Bateman, A., and Y ates, W.,

Digital Signal Processing Design

. Salt Lake

City, Utah: W. H. Freeman and Company, 1990.

Brigham, E. Oran,

The Fast Fourier Transform.

Englewood Cliffs, NJ:

Prentice-Hall, Inc., 1974.

Burrus, C.S., and Parks, T .W .,

DFT/FFT and Convolution Algorithms.

New

York, NY: John Wiley and Sons, Inc., 1984.

Chassaing, R., and Horning, D.,

TMS320C25.

New York, NY: John Wiley and Sons, Inc., 1990.

Digital Signal Processing Applications with the TMS320 Family , Vol. I.

Digital Signal Processing with the

Tex-

as Instruments, 1986; Prentice-Hall, Inc., 1987.

vi

Page 7

References

Digital Signal Processing Applications with the TMS320 Family, Vol. III.

Texas Instruments, 1990; Prentice-Hall, Inc., 1990.

Gold, Bernard, and Rader, C.M.

NY: McGraw-Hill Company, Inc., 1969.

Hamming, R.W.,

1977.

Hutchins, B., and Parks, T.,

the TMS320C25

IEEE ASSP DSP Committee (Editor),

New York, NY: IEEE Press, 1979.

Jackson, Leland B.,

Kluwer Academic Publishers, 1986.

Jones, D.L., and Parks, T.W .,

the TMS32010.

Lim, Jae, and Oppenheim, Alan V. (Editors),

Processing

Morris, L. Robert,

Carleton University, 1983.

Oppenheim, Alan V. (Editor),

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

Oppenheim, Alan V ., and Schafer, R.W .,

wood Cliffs, NJ: Prentice-Hall, Inc., 1975.

Oppenheim, Alan V ., and Schafer, R.W .,

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1989.

Oppenheim, Alan V., and Willsky, A.N., with Young, I.T.,

Systems.

Parks, T .W., and Burrus, C.S.,

and Sons, Inc., 1987.

Rabiner, Lawrence R., and Gold, Bernard,

Signal Processing

Treichler , J.R., Johnson, Jr., C.R., and Larimore, M.G.,

of Adaptive Filters

Digital Filters

. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1990.

Digital Filters and Signal Processing.

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1988.

Digital Signal Processing Software.

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

. New York, NY: John Wiley and Sons, Inc., 1987.

, Digital Processing of Signals.

. Englewood Cliffs, NJ: Prentice-Hall, Inc.,

New Y ork,

A Digital Signal Processing Laboratory Using

Programs for Digital Signal Processing.

Hingham, MA:

A Digital Signal Processing Laboratory Using

Advanced Topics in Signal

Ottawa, Canada:

Applications of Digital Signal Processing.

Digital Signal Processing.

Engle-

Discrete-Time Signal Processing.

Signals and

Digital Filter Design.

New Y or k, NY : John Wi ley

Theory and Application of Digital

Theory and Design

-

Speech

Gray , A.H., and Markel, J.D.,

Springer-Verlag, 1976.

Jayant, N.S., and Noll, Peter,

Cliffs, NJ: Prentice-Hall, Inc., 1984.

Papamichalis, Panos,

wood Cliffs, NJ: Prentice-Hall, Inc., 1987.

Linear Prediction of Speech

Digital Coding of Waveforms

Practical Approaches to Speech Coding.

. New Y ork, NY :

Read This First

. Englewood

Engle-

vii

Page 8

References

Parsons, Thomas.,

Voice and Speech Processing.

McGraw Hill Company, Inc., 1987.

Rabiner, Lawrence R., and Schafer, R.W.,

Signals.

Shaughnessy , Douglas.,

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

Speech Communication.

Digital Processing of Speech

Wesley, 1987.

-

Image Processing

Andrews, H.C., and Hunt, B.R.,

Digital Image Restoration

Cliffs, NJ: Prentice-Hall, Inc., 1977.

Gonzales, Rafael C., and Wintz, Paul,

Digital Image Processing.

MA: Addison-Wesley Publishing Company, Inc., 1977.

Pratt, William K.,

Digital Image Processing

. New Y ork, NY: John Wiley and

Sons, 1978.

-

Multirate DSP

Crochiere, R.E., and Rabiner, L.R.,

Multirate Digital Signal Processing

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

V aidyanathan, P .P .,

Multirate Systems and Filter Banks

NJ: Prentice-Hall, Inc.

-

Digital Control Theory

New York, NY:

Reading, MA: Addison-

. Englewood

Reading,

.

. Englewood Cliffs,

viii

Dote, Y .,

Servo Motor and Motion Control Using Digital Signal Processors

.

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1990.

Jacquot, R.,

Modern Digital Control Systems.

New Y ork, NY: Marcel Dekker,

Inc., 1981.

Katz, P.,

Digital Control Using Microprocessors

. Englewood Cliffs, NJ:

Prentice-Hall, Inc., 1981.

Kuo, B.C.,

Digital Control Systems.

New York, NY: Holt, Reinholt and

Winston, Inc., 1980.

Moroney , P .,

tors.

Cambridge, MA: The MIT Press, 1983.

Phillips, C., and Nagle, H.,

Issues in the Implementation of Digital Feedback Compensa-

Digital Control System Analysis and Design.

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

-

Adaptive Signal Processing

Haykin, S.,

Adaptive Filter Theory.

Englewood Cliffs, NJ: Prentice-Hall,

Inc., 1991.

Widrow, B., and Stearns, S.D.

Adaptive Signal Processing.

Englewood

Cliffs, NJ: Prentice-Hall, Inc., 1985.

Page 9

-

Array Signal Processing

References

Haykin, S., Justice, J.H., Owsley, N.L., Y en, J.L., and Kak, A.C.

Processing.

Hudson, J.E.

Englewood Cliffs, NJ: Prentice-Hall, Inc., 1985.

Adaptive Array Principles.

New York, NY: John Wiley and

Sons, 1981.

Monzingo, R.A., and Miller, J.W.

Introduction to Adaptive Arrays.

NY: John Wiley and Sons, 1980.

Array Signal

New Y or k,

Read This First

ix

Page 10

If You Need Assistance

If You Need Assistance . . .

-

World-Wide Web Sites

TI Online http://www.ti.com

Semiconductor Product Information Center (PIC) http://www.ti.com/sc/docs/pic/home.htm

DSP Solutions http://www.ti.com/dsps

320 Hotline On-line

Microcontroller Home Page http://www.ti.com/sc/micro

Networking Home Page http://www.ti.com/sc/docs/network/nbuhomex.htm

-

North America, South America, Central America

Product Information Center (PIC) (972) 644-5580

TI Literature Response Center U.S.A. (800) 477-8924

Software Registration/Upgrades (214) 638-0333 Fax: (214) 638-7742

U.S.A. Factory Repair/Hardware Upgrades (281) 274-2285

U.S. Technical Training Organization (972) 644-5580

Microcontroller Hotline (281) 274-2370 Fax: (281) 274-4203 Email: mi cro @ti.com

Microcontroller Modem BBS (281) 274-3700 8-N-1

DSP Hotline (281) 274-2320 Fax: (281) 274-2324 Email: dsph@ti.com

DSP Modem BBS (281) 274-2323

DSP Internet BBS via anonymous ftp to ftp://ftp.ti.com/pub/tms320bbs

Networking Hotline Fax: (281) 274-4027

-

Europe, Middle East, Africa

European Product Information Center (EPIC) Hotlines:

Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32 Email: epic@ti.com

Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68

English +33 1 30 70 11 65

Francais +33 1 30 70 11 64

Italiano +33 1 30 70 11 67

EPIC Modem BBS +33 1 30 70 11 99

European Factory Repair +33 4 93 22 25 40

Europe Customer Training Helpline Fax: +49 81 61 80 40 10

-

Asia-Pacific

Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200

Hong Kong DSP Hotline +852 2 956 7268 Fax: +852 2 956 1002

Korea DSP Hotline +82 2 551 2804 Fax: +82 2 551 2828

Korea DSP Modem BBS +82 2 551 2914

Singapore DSP Hotline Fax: +65 390 7179

Taiwan DSP Hotline +886 2 377 1450 Fax: +886 2 377 2718

Taiwan DSP Modem BBS +886 2 376 2592

Taiwan DSP Internet BBS via anonymous ftp to ftp://dsp.ee.tit.edu.tw/pub/TI/

-

Japan

Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)

DSP Hotline +03-3769-8735 or (INTL) 813-3769-8735 Fax: +03-3457-7071 or (INTL) 813-3457-7071

DSP BBS via Nifty-Serve Type “Go TIASP”

t

+03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813-3457-1259

http://www.ti.com/sc/docs/dsps/support.htm

Email: TLANHOT@micro.ti.com

x

Page 11

If You Need Assistance / Trademarks

-

Documentation

When making suggestions or reporting errors in documentation, please include the following information that is on the title

page: the full title of the book, the publication date, and the literature number.

Mail: Texas Instruments Incorporated Email: comments@books.sc.ti.com

Technical Documentation Services, MS 702

P.O. Box 1443

Houston, Texas 77251-1443

Note: When calling a Literature Response Center to order documentation, please specify the literature number of the

book.

Trademarks

ABEL is a trademark of DATA I/O.

CodeView, MS, MS-DOS, MS-Windows, and Presentation Manager are registered trademarks of

Microsoft Corporation.

DEC, Digital DX, Ultrix, VAX, and VMS are trademarks of Digital Equipment Corporation.

HPGL is registered trademark of Hewlett Packard Company.

Macintosh and MPW are trademarks of Apple Computer Corp.

Micro Channel, OS/2, PC-DOS, and PGA are trademarks of International Business Machines Corporation.

SP ARC, Sun 3, Sun 4, Sun Workstation, SunView, and SunWindows are trademark of SP ARC International,

Inc., but licensed exclusively to Sun Microsystems, Inc.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through

X/Open Company Limited.

Read This First

xi

Page 12

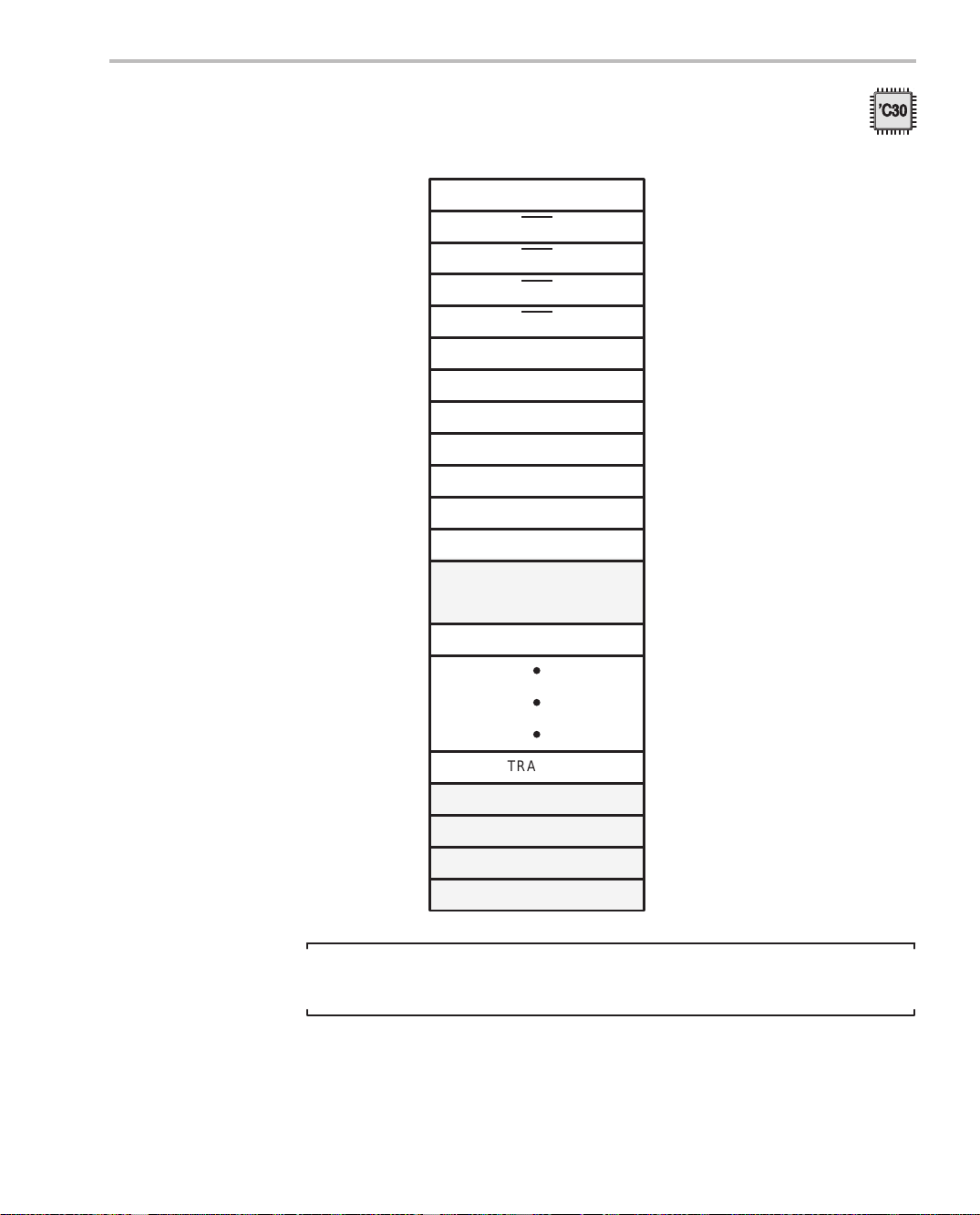

Contents

Contents

1 Introduction 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A general description of the TMS320C30, TMS320C31, and TMS320C32, their key features,

and typical applications.

1.1 TMS320C3x Devices 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 TMS320C3x Key Specifications 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 TMS320C30 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.3 TMS320C31 and TMS320LC31 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.4 TMS320C32 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Typical Applications 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architectural Overview 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional block diagram, ’C3x design description, hardware components, device operation,

and instruction set summary.

2.1 Overview 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Central Processing Unit (CPU) 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Floating-Point/Integer Multiplier 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Arithmetic Logic Unit (ALU) and Internal Buses 2-8. . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 Auxiliary Register Arithmetic Units (ARAUs) 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 CPU Primary Register File 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Other Registers 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Memory Organization 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 RAM, ROM, and Cache 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2 Memory Addressing Modes 2-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Internal Bus Operation 2-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 External Memory Interface 2-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 TMS320C32 16- and 32-Bit Program Memory 2-19. . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.2 TMS320C32 8-, 16-, and 32-Bit Data Memory 2-20. . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Interrupts 2-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 Peripherals 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.1 Timers 2-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9.2 Serial Ports 2-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10 Direct Memory Access (DMA) 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11 TMS320C30, TMS320C31, and TMS320C32 Differences 2-26. . . . . . . . . . . . . . . . . . . . . . .

xiii

Page 13

Contents

3 CPU Registers 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of the registers in the CPU register file.

3.1 CPU Multiport Register File 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Extended-Precision Registers (R7–R0) 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Auxiliary Registers (AR7–AR0) 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 Data-Page Pointer (DP) 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 Index Registers (IR0, IR1) 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.5 Block Size (BK) Register 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.6 System-Stack Pointer (SP) 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.7 Status (ST) Register 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.8 CPU/DMA Interrupt-Enable (IE) Register 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.9 CPU Interrupt Flag (IF) Register 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.10 I/O Flag (IOF) Register 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.11 Repeat-Counter (RC) and Block-Repeat (RS, RE) Registers 3-17. . . . . . . . . . . . .

3.2 Other Registers 3-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Program-Counter (PC) Register 3-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Instruction Register (IR) 3-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Reserved Bits and Compatibility 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Memory and the Instruction Cache 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of memory maps with explanation of instruction cache architecture, algorithm,

and control bits.

4.1 Memory 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 Memory Maps 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 Peripheral Bus Memory Map 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Reset/Interrupt/Trap Vector Map 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Instruction Cache 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Instruction-Cache Architecture 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Instruction-Cache Algorithm 4-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Cache Control Bits 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Data Formats and Floating-Point Operation 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of signed and unsigned integer and floating-point formats. Discussion of floatingpoint multiplication, addition, subtraction, normalization, rounding, and conversions.

5.1 Integer Formats 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Short-Integer Format 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Single-Precision Integer Format 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Unsigned-Integer Formats 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Short Unsigned-Integer Format 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 Single-Precision Unsigned-Integer Format 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Floating-Point Formats 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Short Floating-Point Format 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 TMS320C32 Short Floating-Point Format for External 16-Bit Data 5-6. . . . . . . . .

xiv

Page 14

Contents

5.3.3 Single-Precision Floating-Point Format 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.4 Extended-Precision Floating-Point Format 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.5 Determining the Decimal Equivalent of a TMS320C3x

Floating-Point Format 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.6 Conversion Between Floating-Point Formats 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Floating-Point Conversion (IEEE Std. 754) 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1 Converting IEEE Format to 2s-Complement TMS320C3x

Floating-Point Format 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.2 Converting 2s-Complement TMS320C3x Floating-Point Format

to IEEE Format 5-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Floating-Point Multiplication 5-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Floating-Point Addition and Subtraction 5-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Normalization Using the NORM Instruction 5-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Rounding (RND Instruction) 5-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 Floating-Point to Integer Conversion (FIX Instruction) 5-41. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 Integer to Floating-Point Conversion (FLOAT Instruction) 5-43. . . . . . . . . . . . . . . . . . . . . . .

5.11 Fast Logarithms on a Floating-Point Device 5-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11.1 Example of Fast Logarithm on a Floating-Point Device 5-45. . . . . . . . . . . . . . . . . .

5.11.2 Points to Consider 5-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Addressing Modes 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation, encoding, and implementation of addressing modes; format descriptions;

system stack management.

6.1 Addressing Types 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Register Addressing 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Direct Addressing 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Indirect Addressing 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Immediate Addressing 6-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6 PC-Relative Addressing 6-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.7 Circular Addressing 6-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 Bit-Reversed Addressing 6-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.9 Aligning Buffers With the TMS320 Floating-Point DSP Assembly Language Tools 6-28. . . .

6.10 System and User Stack Management 6-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.10.1 System-Stack Pointer 6-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.10.2 Stacks 6-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.10.3 Queues 6-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Program Flow Control 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Software control of program flow with repeat modes and branching; interlocked operations;

reset and interrupts.

7.1 Repeat Modes 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1 Repeat-Mode Control Bits 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.2 Repeat-Mode Operation 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.3 RPTB Instruction 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xv

Page 15

Contents

7.1.4 RPTS Instruction 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.5 Repeat-Mode Restrictions 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.6 RC Register Value After Repeat Mode Completes 7-7. . . . . . . . . . . . . . . . . . . . . . .

7.1.7 Nested Block Repeats 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Delayed Branches 7-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Calls, Traps, and Returns 7-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Interlocked Operations 7-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 Interrupting Interlocked Operations 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.2 Using Interlocked Operations 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.3 Pipeline Effects of Interlocked Instructions 7-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 Reset Operation 7-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 Interrupts 7-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.1 TMS320C30 and TMS320C31 Interrupt Vector Table 7-26. . . . . . . . . . . . . . . . . . . .

7.6.2 TMS320C32 Interrupt Vector Table 7-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.3 Interrupt Prioritization 7-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.4 CPU Interrupt Control Bits 7-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.5 Interrupt Flag Register Behavior 7-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.6 Interrupt Processing 7-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.7 CPU Interrupt Latency 7-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.8 External Interrupts 7-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7 DMA Interrupts 7-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7.1 DMA Interrupt Control Bits 7-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7.2 DMA Interrupt Processing 7-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7.3 CPU/DMA Interaction 7-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7.4 TMS320C3x Interrupt Considerations 7-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.7.5 TMS320C30 Interrupt Considerations 7-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.8 Traps 7-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.8.1 Initialization of Traps and Interrupts 7-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.8.2 Operation of Traps 7-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.9 Power Management Modes 7-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.9.1 IDLE2 Power-Down Mode 7-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.9.2 LOPOWER 7-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Pipeline Operation 8-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Discussion of the pipeline of operations on the TMS320C3x

8.1 Pipeline Structure 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Pipeline Conflicts 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1 Branch Conflicts 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.2 Register Conflicts 8-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.3 Memory Conflicts 8-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 Resolving Register Conflicts 8-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4 Memory Access for Maximum Performance 8-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5 Clocking Memory Accesses 8-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5.1 Program Fetches 8-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5.2 Data Loads and Stores 8-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

Page 16

Contents

9 TMS320C30 and TMS320C31 External-Memory Interface 9-1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of primary and expansion interfaces for the ’C30 and ’C31; external interface timing

diagrams; programmable wait-states and bank switching.

9.1 Overview 9-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 Memory Interface Signals 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.1 TMS320C30 Memory Interface Signals 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.2 TMS320C31 Memory Interface Signals 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 Memory Interface Control Registers 9-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.1 Primary-Bus Control Register 9-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.2 Expansion-Bus Control Register 9-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4 Programmable Wait States 9-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5 Programmable Bank Switching 9-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6 External Memory Interface Timing 9-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.1 Primary-Bus Cycles 9-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.2 Expansion-Bus I/O Cycles 9-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.3 Hold Cycles 9-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 TMS320C32 Enhanced External Memory Interface 10-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of primary and expansion interfaces for the ’C32; external interface timing

diagrams; programmable wait-states and bank switching.

10.1 TMS320C32 Memory Features 10-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 TMS320C32 Memory Overview 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.1 External Memory Interface Overview 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

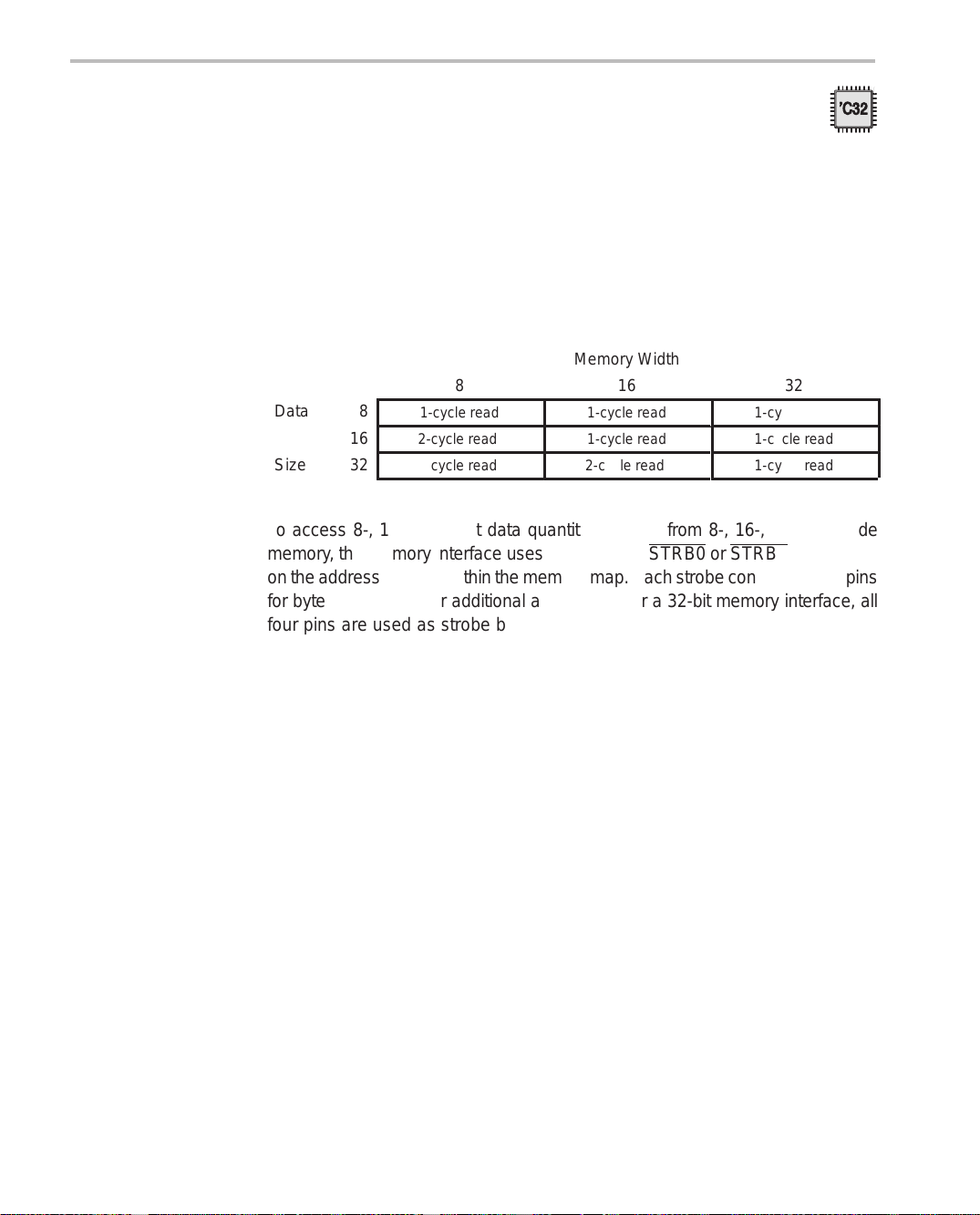

10.2.2 Program Memory Access 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.3 Data Memory Access 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Configuration 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1 External Interface Control Registers 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.2 Using Physical Memory Width and Data-Type Size Fields 10-13. . . . . . . . . . . . .

10.4 Programmable Wait States 10-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5 Programmable Bank Switching 10-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6 32-Bit-Wide Memory Interface 10-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.7 16-Bit-Wide Memory Interface 10-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.8 8-Bit-Wide Memory Interface 10-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.9 External Ready Timing Improvement 10-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.10 Bus Timing 10-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.10.1 STRB0

10.10.2 IOSTRB

and STRB1 Bus Cycles 10-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus Cycles 10-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.10.3 Inactive Bus States 10-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11 Using the TMS320C31 and TMS320C32 Boot Loaders 11-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of the boot loader operations for the ’C31 and ’C32.

11.1 TMS320C31 Boot Loader 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.1 TMS320C31 Boot-Loader Description 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.2 TMS320C31 Boot-Loader Mode Selection 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xvii

Page 17

Contents

11.1.3 TMS320C31 Boot-Loading Sequence 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.4 TMS320C31 Boot Data Stream Structure 11-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.5 Interrupt and Trap-Vector Mapping 11-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.6 TMS320C31 Boot-Loader Precautions 11-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 TMS320C32 Boot Loader 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1 TMS320C32 Boot-Loader Description 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.2 TMS320C32 Boot-Loader Mode Selection 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.3 TMS320C32 Boot-Loading Sequence 11-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.4 TMS320C32 Boot Data Stream Structure 11-20. . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.5 Boot-Loader Hardware Interface 11-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.6 TMS320C32 Boot-Loader Precautions 11-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 Peripherals 12-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description of the DMA controller, timers, and serial ports.

12.1 Timers 12-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.1 Timer Pins 12-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.2 Timer Control Registers 12-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.3 Timer Global-Control Register 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.4 Timer-Period and Counter Registers 12-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.5 Timer Pulse Generation 12-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.6 Timer Operation Modes 12-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.7 Using TCLKx as General-Purpose I/O Pins 12-12. . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.8 Timer Interrupts 12-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1.9 Timer Initialization/Reconfiguration 12-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Serial Ports 12-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.1 Serial-Port Global-Control Register 12-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.2 FSX/DX/CLKX Port-Control Register 12-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.3 FSR/DR/CLKR Port-Control Register 12-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.4 Receive/Transmit Timer-Control Register 12-25. . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.5 Receive/Transmit Timer-Counter Register 12-27. . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.6 Receive/Transmit Timer-Period Register 12-28. . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.7 Data-Transmit Register 12-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.8 Data-Receive Register 12-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.9 Serial-Port Operation Configurations 12-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.10 Serial-Port Timing 12-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.11 Serial-Port Interrupt Sources 12-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.12 Serial-Port Functional Operation 12-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.13 Serial-Port Initialization/Reconfiguration 12-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.14 TMS320C3x Serial-Port Interface Examples 12-41. . . . . . . . . . . . . . . . . . . . . . . . .

12.3 DMA Controller 12-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.1 DMA Functional Description 12-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.2 DMA Basic Operation 12-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.3 DMA Registers 12-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.4 CPU/DMA Interrupt-Enable Register 12-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xviii

Page 18

Contents

12.3.5 TMS320C32 DMA Internal Priority Schemes 12-62. . . . . . . . . . . . . . . . . . . . . . . . .

12.3.6 CPU and DMA Controller Arbitration 12-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.7 DMA and Interrupts 12-64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.8 DMA Memory Transfer Timing 12-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.9 DMA Initialization/Reconfiguration 12-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.10 Hints for DMA Programming 12-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3.11 DMA Programming Examples 12-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 Assembly Language Instructions 13-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional listing of instructions. Condition codes defined. Alphabetized individual instruction

set with examples.

13.1 Instruction Set 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.1 Load and Store Instructions 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.2 2-Operand Instructions 13-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.3 3-Operand Instructions 13-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.4 Program-Control Instructions 13-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.5 Low-Power Control Instructions 13-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.6 Interlocked-Operations Instructions 13-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.7 Parallel-Operations Instructions 13-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.8 Illegal Instructions 13-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2 Instruction Set Summary 13-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3 Parallel Instruction Set Summary 13-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4 Group Addressing Mode Instruction Encoding 13-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.1 General Addressing Modes 13-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2 3-Operand Addressing Modes 13-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.3 Parallel Addressing Modes 13-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.4 Conditional-Branch Addressing Modes 13-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.5 Condition Codes and Flags 13-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.6 Individual Instructions 13-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.6.1 Symbols and Abbreviations 13-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.6.2 Optional Assembler Syntax 13-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.6.3 Individual Instruction Descriptions 13-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Instruction Opcodes A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of the opcode fields for the TMS320C3x instructions.

B TMS320C31 Boot Loader Source Code B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C TMS320C32 Boot Loader Source Code C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.1 Boot-Loader Source Code Description C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2 Boot-Loader Source Code Listing C-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D Glossary D-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xix

Page 19

Figures

Figures

1–1 TMS320C3x Devices Block Diagram 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

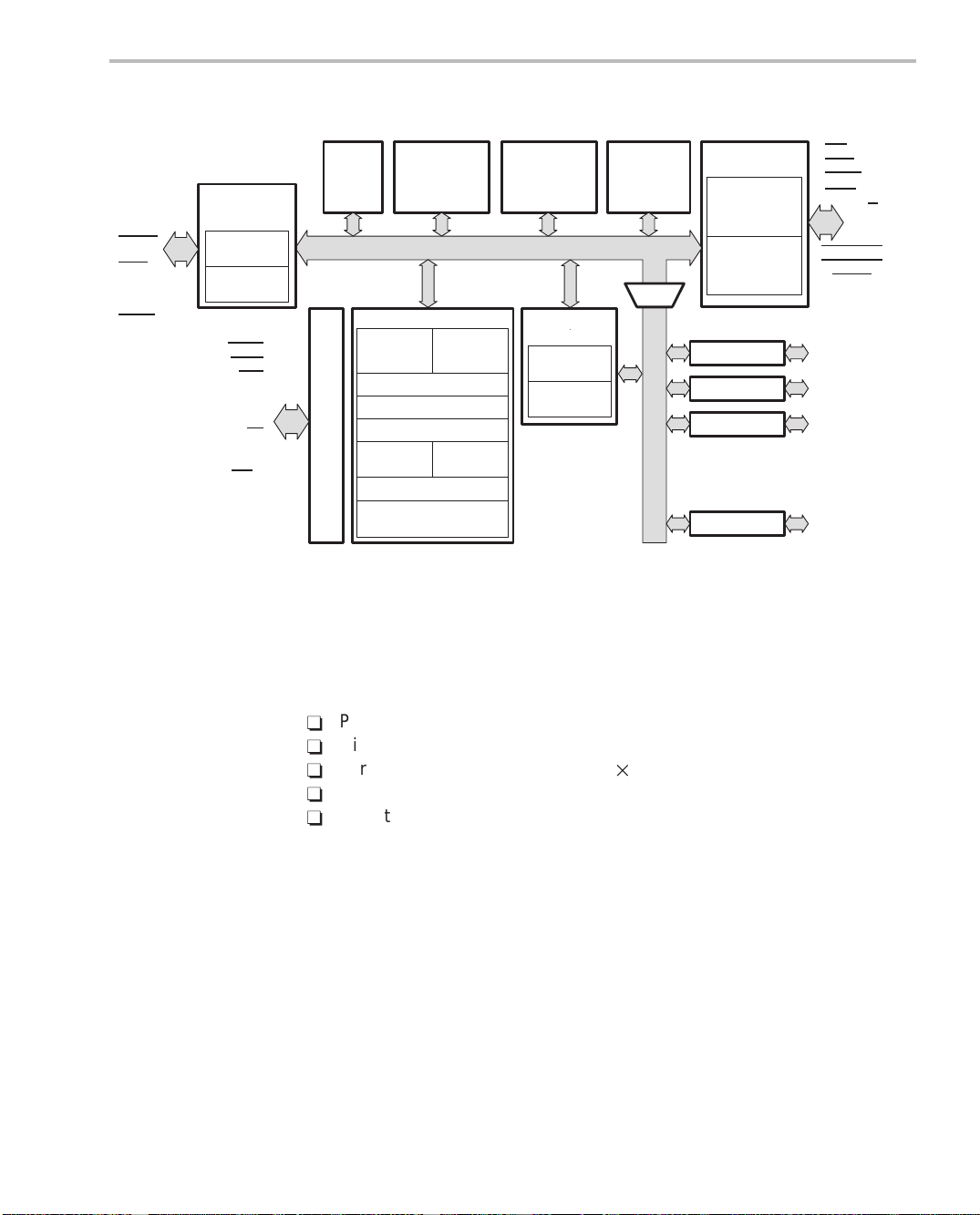

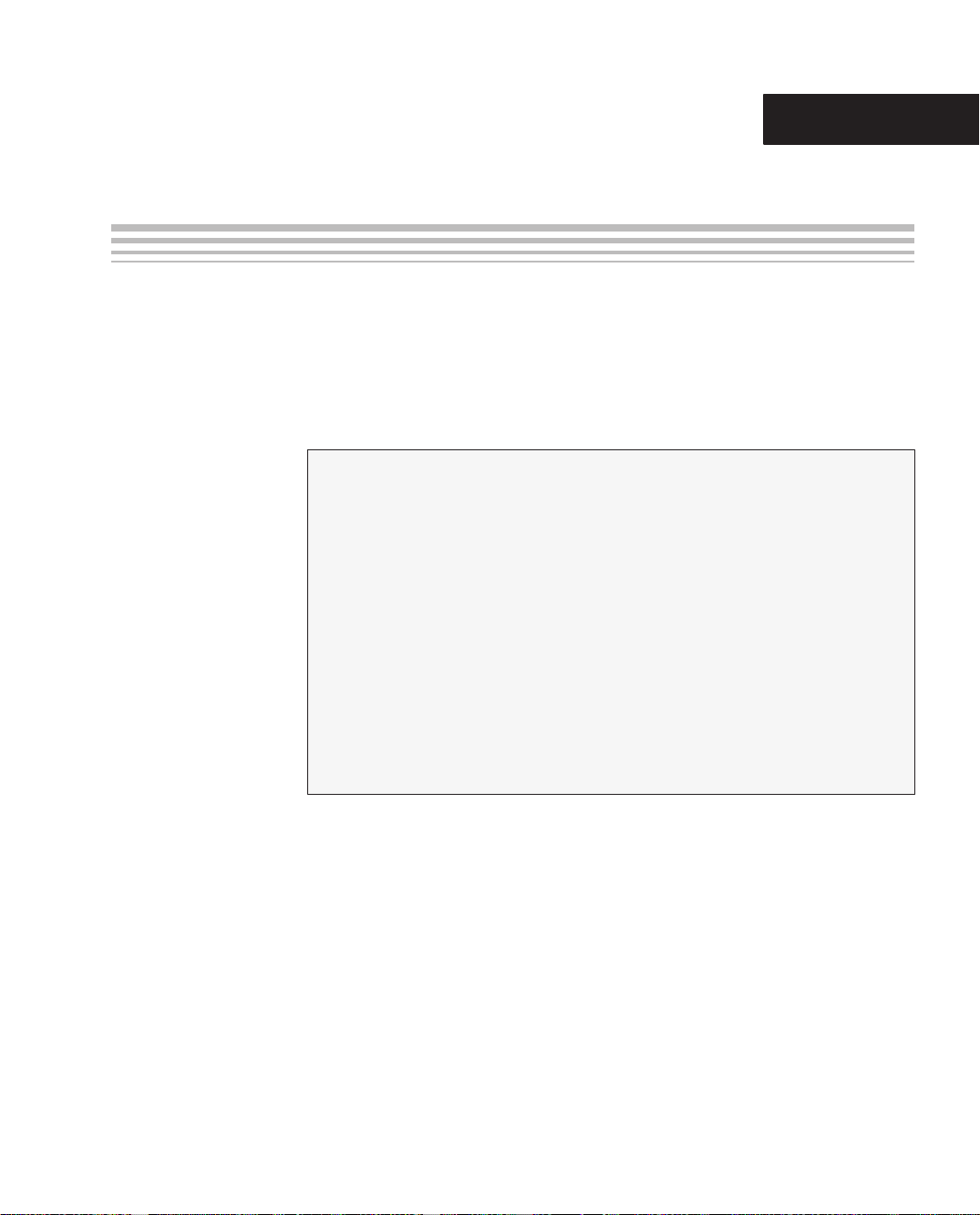

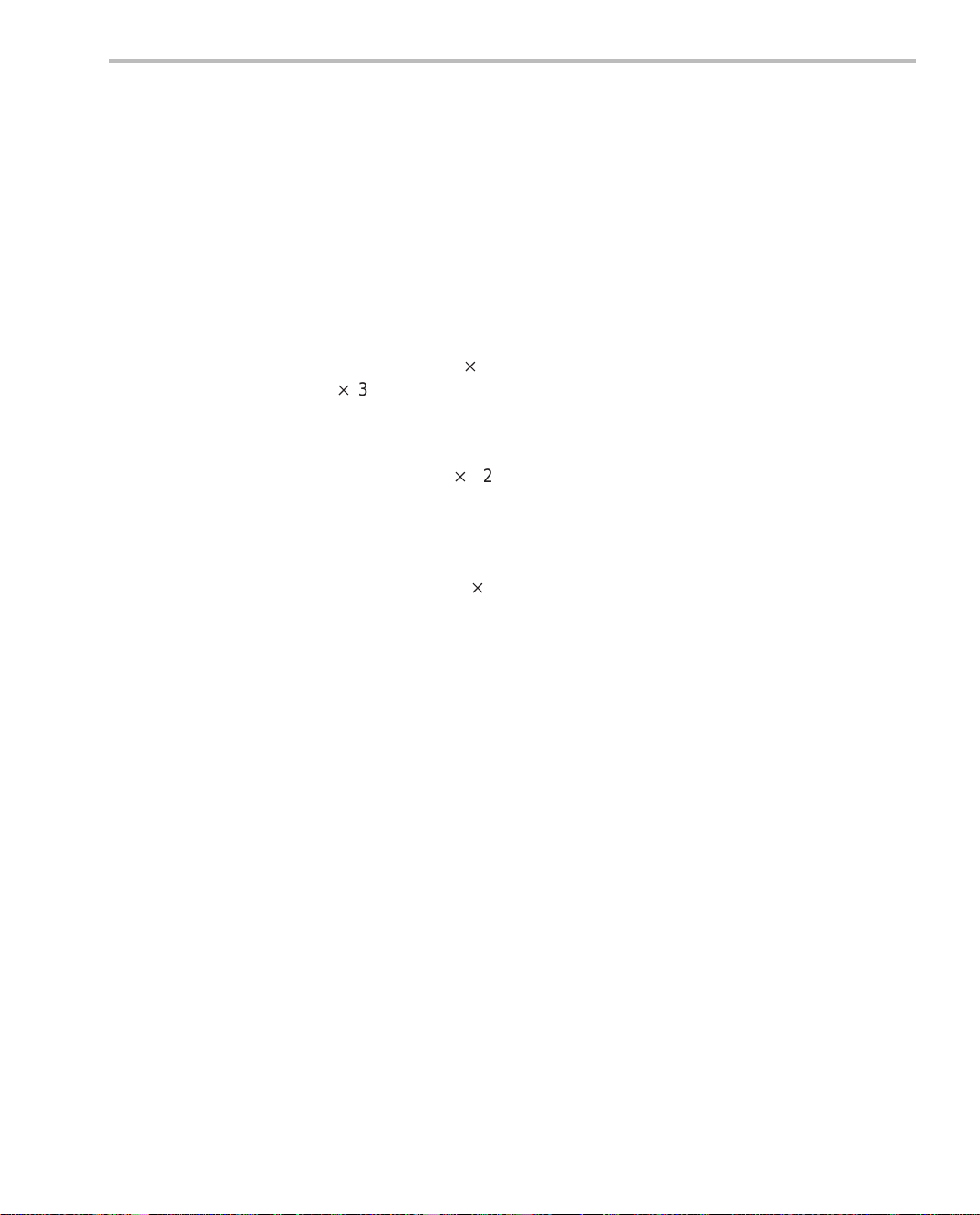

2–1 TMS320C30 Block Diagram 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

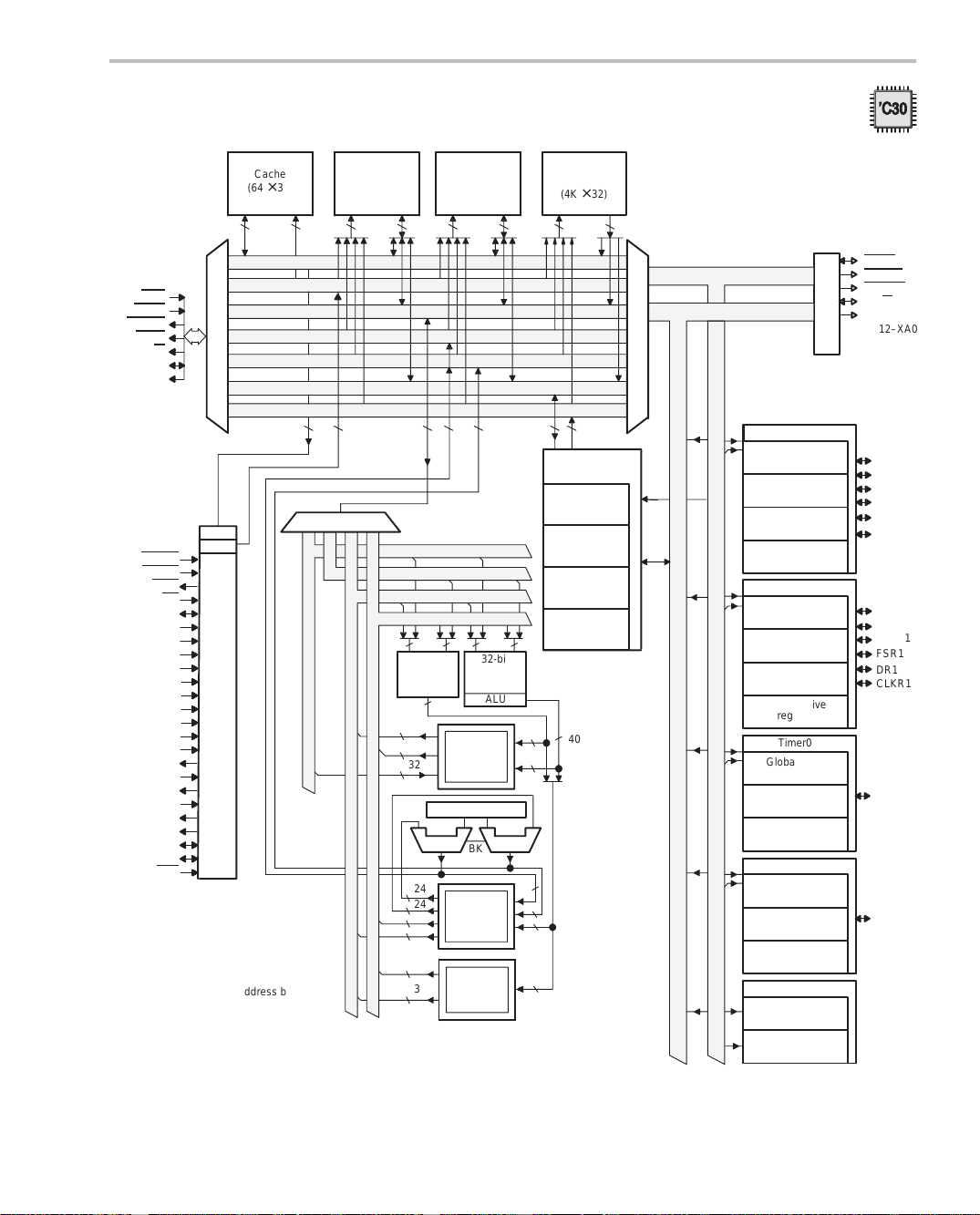

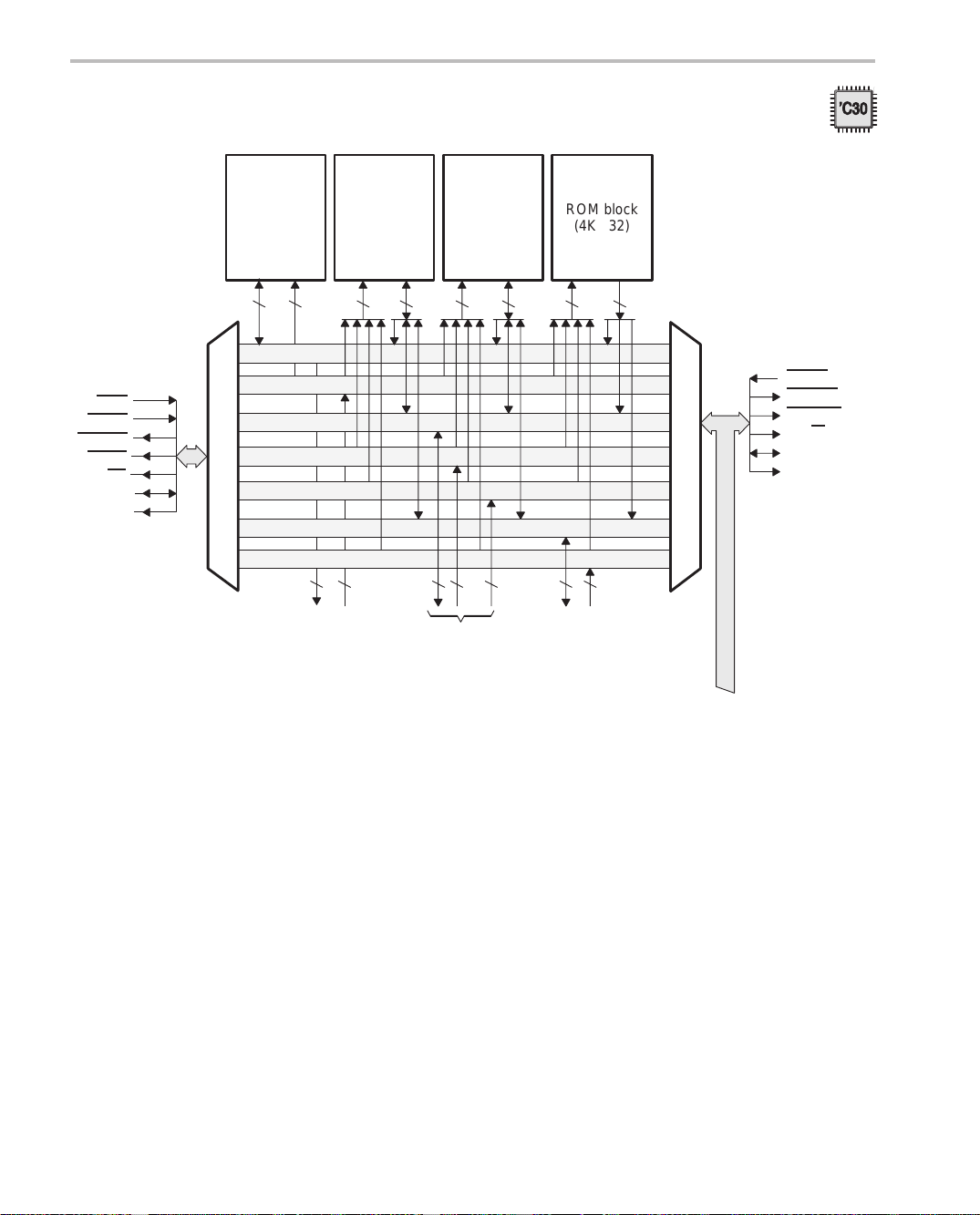

2–2 TMS320C31 Block Diagram 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

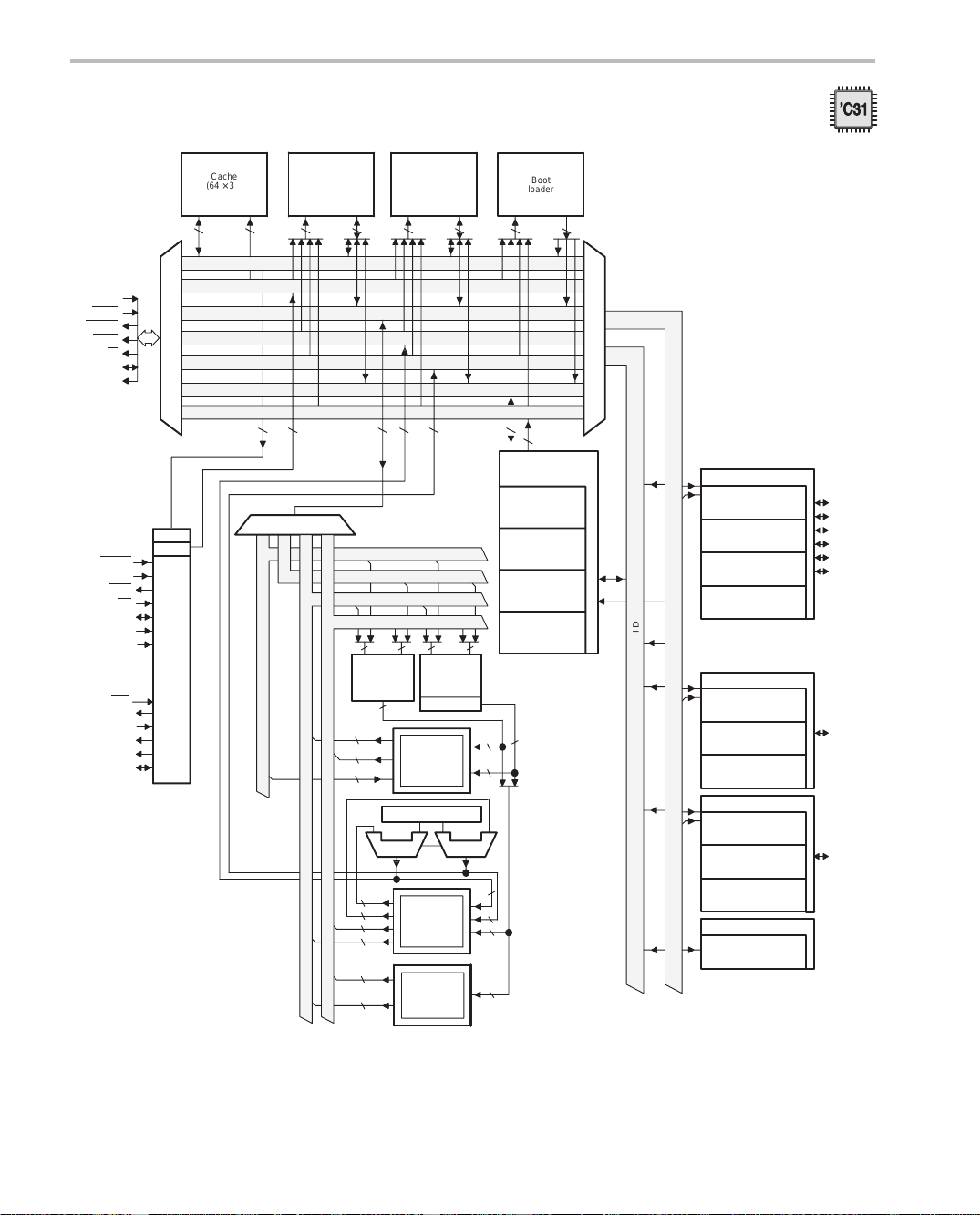

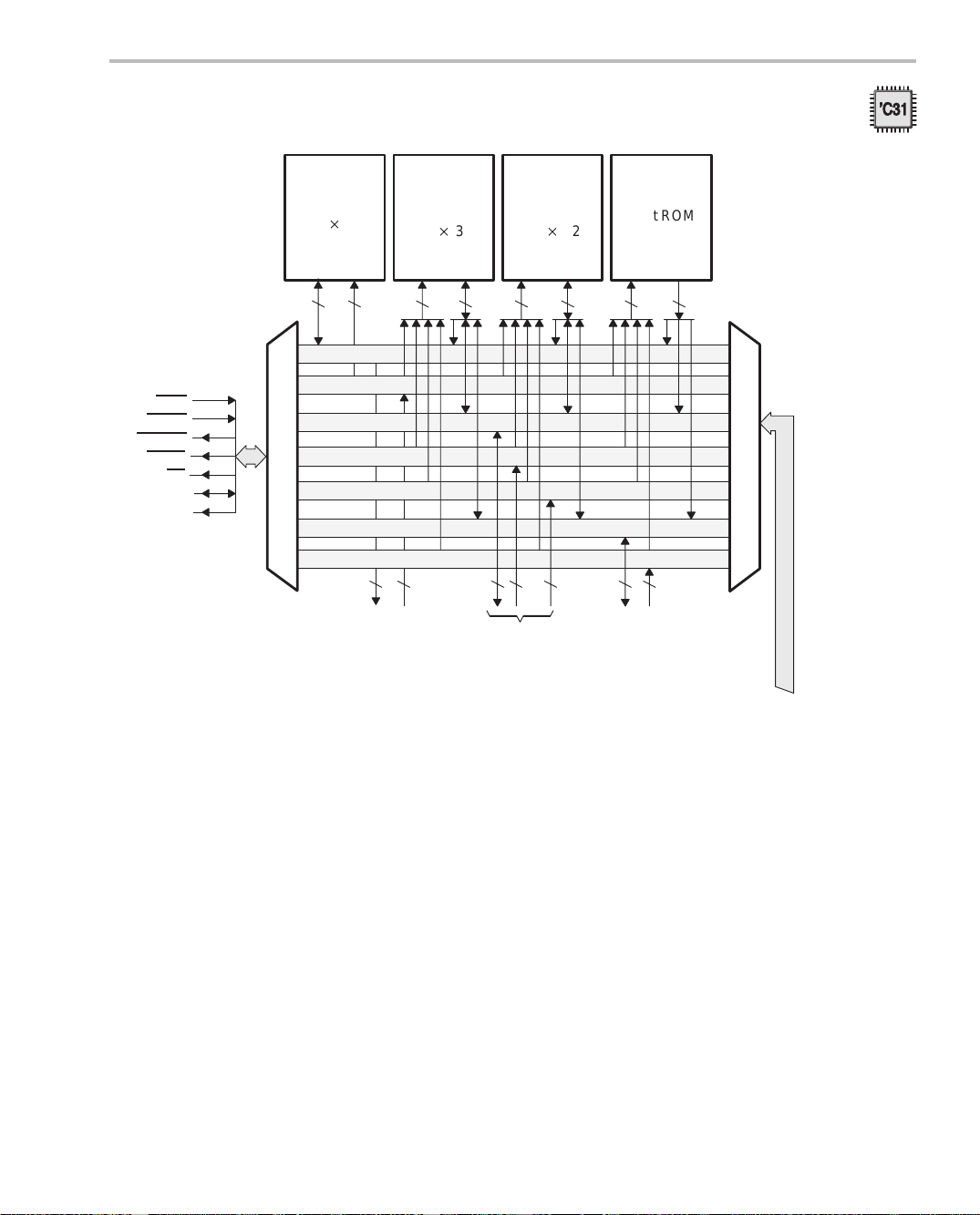

2–3 TMS320C32 Block Diagram 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Central Processing Unit (CPU) 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Memory Organization of the TMS320C30 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Memory Organization of the TMS320C31 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Memory Organization of the TMS320C32 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

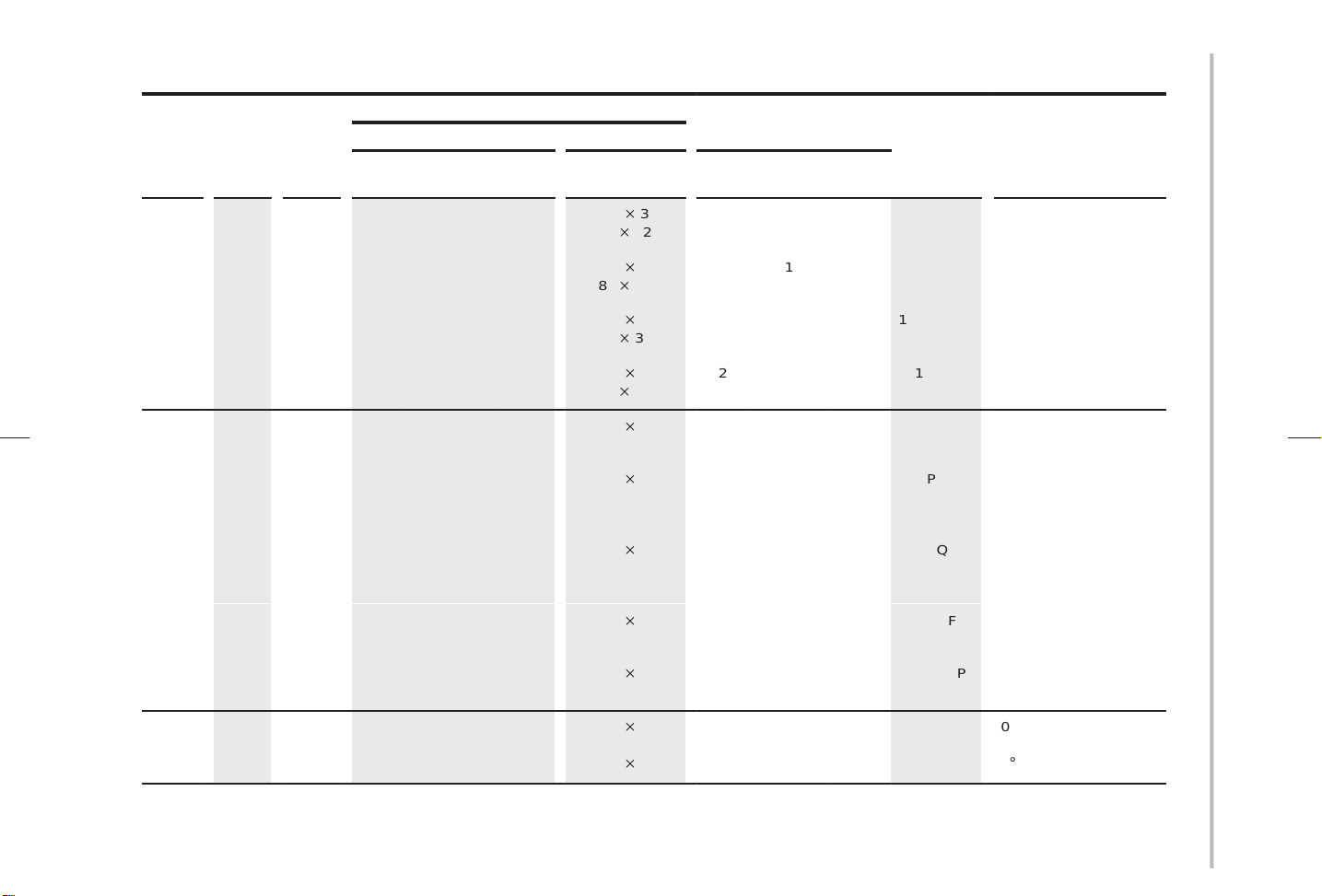

2–8 TMS320C32-Supported Data Types and Sizes and External Memory Widths 2-20. . . . . . . .

2–9 Peripheral Modules 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 DMA Controller 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Extended-Precision Register Floating-Point Format 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Extended-Precision Register Integer Format 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Status Register (TMS320C30 andTMS320C31) 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Status Register (TMS320C32 Only) 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 CPU/DMA Interrupt-Enable (IE) Register (TMS320C30 and TMS320C31) 3-9. . . . . . . . . . .

3–6 CPU/DMA Interrupt-Enable (IE) Register (TMS320C32) 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 TMS320C30 CPU Interrupt Flag (IF) Register 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 TMS320C31 CPU Interrupt Flag (IF) Register 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 TMS320C32 CPU Interrupt Flag (IF) Register 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Effective Base Address of the Interrupt-Trap Vector Table 3-14. . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Interrupt and Trap Vector Locations 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 I/O Flag (IOF) Register 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 TMS320C30 Memory Maps 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 TMS320C31 Memory Maps 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 TMS320C32 Memory Maps 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 TMS320C30 Peripheral Bus Memory-Mapped Registers 4-10. . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 TMS320C31 Peripheral Bus Memory-Mapped Registers 4-11. . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 TMS320C32 Peripheral Bus Memory-Mapped Registers 4-13. . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 Reset, Interrupt, and Trap Vector Locations for the TMS320C30

4–8 Reset, Interrupt, and Trap Vector Locations for theTMS320C31

4–9 Interrupt and Trap Branch Instructions for the TMS320C31 Microcomputer Mode 4-17. . . . .

4–10 Interrupt and Trap Vector Locations for TMS320C32 4-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 Address Partitioning for Cache Control Algorithm 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Instruction-Cache Architecture 4-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Microprocessor Mode 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Microprocessor Mode 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xx

Page 20

Figures

5–1 Short-Integer Format and Sign-Extension of Short Integers 5-2. . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Single-Precision Integer Format 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Short Unsigned-Integer Format and Zero Fill 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Single-Precision Unsigned-Integer Format 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 General Floating-Point Format 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Short Floating-Point Format 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 TMS320C32 Short Floating-Point Format for External 16-Bit Data 5-6. . . . . . . . . . . . . . . . . . .

5–8 Single-Precision Floating-Point Format 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Extended-Precision Floating-Point Format 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Converting from Short Floating-Point Format to Single-Precision

Floating-Point Format 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Converting from Short Floating-Point Format to Extended-Precision

Floating-Point Format 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Converting from Single-Precision Floating-Point Format to Extended-Precision

Floating-Point Format 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 Converting from Extended-Precision Floating-Point Format to Single-Precision

Floating-Point Format 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–14 IEEE Single-Precision Std. 754 Floating-Point Format 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–15 TMS320C3x Single-Precision 2s-Complement Floating-Point Format 5-15. . . . . . . . . . . . . . .

5–16 Flowchart for Floating-Point Multiplication 5-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–17 Flowchart for Floating-Point Addition 5-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–18 Flowchart for NORM Instruction Operation 5-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–19 Flowchart for Floating-Point Rounding by the RND Instruction 5-40. . . . . . . . . . . . . . . . . . . . .

5–20 Flowchart for Floating-Point to Integer Conversion by FIX Instruction 5-42. . . . . . . . . . . . . . .

5–21 Flowchart for Integer to Floating-Point Conversion by FLOAT Instruction 5-43. . . . . . . . . . . .

5–22 Tabulated Values for Mantissa 5-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–23 Fast Logarithm for FFT Displays 5-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Direct Addressing 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Indirect Addressing Operand Encoding 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Encoding for 24-Bit PC-Relative Addressing Mode 6-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Logical and Physical Representation of Circular Buffer 6-21. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Logical and Physical Representation of Circular Buffer after Writing Three Values 6-21. . . .

6–6 Logical and Physical Representation of Circular Buffer after Writing Eight Values 6-22. . . . .

6–7 Circular Buffer Implementation 6-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 Data Structure for FIR Filters 6-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 System Stack Configuration 6-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Implementations of High-to-Low Memory Stacks 6-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 Implementations of Low-to-High Memory Stacks 6-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 CALL Response Timing 7-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Multiple TMS320C3xs Sharing Global Memory 7-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Zero-Logic Interconnect of TMS320C3x Devices 7-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Effective Base Address of the Interrupt-Trap-Vector Table 7-29. . . . . . . . . . . . . . . . . . . . . . . . .

7–5 IF Register Modification 7-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 CPU Interrupt Processing 7-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–7 Interrupt Logic Functional Diagram 7-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xxi

Page 21

Figures

7–8 DMA Interrupt Processing 7-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 Parallel CPU and DMA Interrupt Processing 7-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–10 Flow of Traps 7-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–11 IDLE2 Timing 7-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–12 Interrupt Response Timing After IDLE2 Operation 7-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–13 LOPOWER Timing 7-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–14 MAXSPEED Timing 7-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–1 TMS320C3x Pipeline Structure 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–2 Minor Clock Periods 8-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–3 2-Operand Instruction Word 8-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–4 3-Operand Instruction Word 8-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–5 Multiply or CPU Operation With a Parallel Store 8-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–6 Two Parallel Stores 8-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–7 Parallel Multiplies and Adds 8-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–1 Memory-Mapped External Interface Control Registers 9-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–2 Primary-Bus Control Register 9-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–3 Expansion-Bus Control Register 9-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–4 BNKCMP Example 9-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–5 Bank-Switching Example 9-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–6 Read-Read-Write for (M)STRB

= 0 9-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–7 Write-Write-Read for (M)STRB = 0 9-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–8 Use of Wait States for Read for (M)STRB = 0 9-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–9 Use of Wait States for Write for (M)STRB = 0 9-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–10 Read and Write for IOSTRB

= 0 9-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–11 Read With One Wait State for IOSTRB = 0 9-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–12 Write With One Wait State for IOSTRB = 0 9-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–13 Memory Read and I/O Write for Expansion Bus 9-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–14 Memory Read and I/O Read for Expansion Bus 9-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–15 Memory Write and I/O Write for Expansion Bus 9-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–16 Memory Write and I/O Read for Expansion Bus 9-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–17 I/O Write and Memory Write for Expansion Bus 9-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–18 I/O Write and Memory Read for Expansion Bus 9-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–19 I/O Read and Memory Write for Expansion Bus 9-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–20 I/O Read and Memory Read for Expansion Bus 9-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–21 I/O Write and I/O Read for Expansion Bus 9-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–22 I/O Write and I/O Write for Expansion Bus 9-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–23 I/O Read and I/O Read for Expansion Bus 9-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–24 Inactive Bus States for IOSTRB

9–25 Inactive Bus States for STRB

and MSTRB 9-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–26 HOLD and HOLDA Timing 9-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–1 Memory Address Spaces 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–2 Status Register 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–3 Memory-Mapped External Interface Control Registers 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–4 STRB0

Control Register 10-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xxii

Page 22

Figures

10–5 STRB1 Control Register 10-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–6 IOSTRB

Control Register 10-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

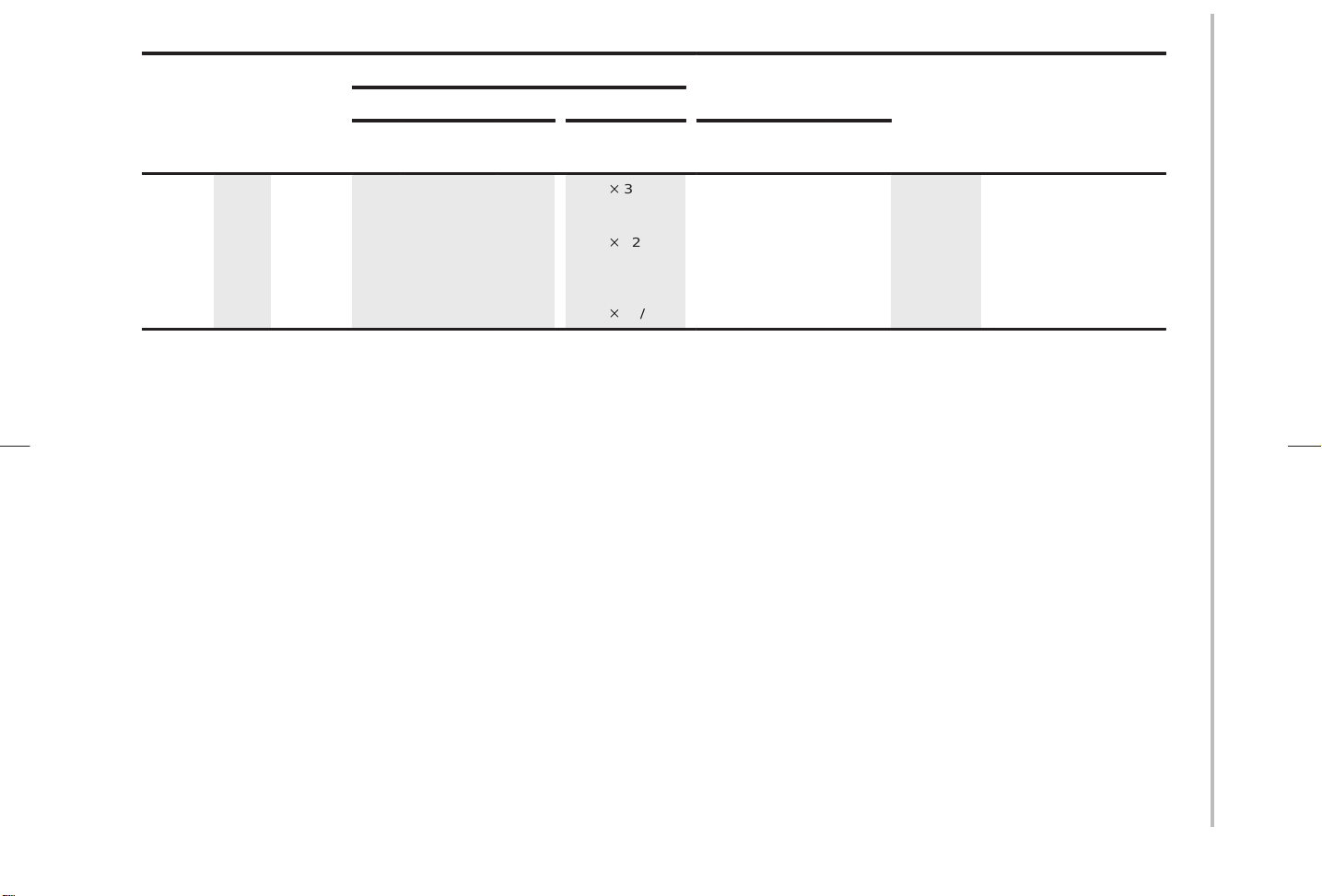

10–7 STRB Configuration 10-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–8 BNKCMP Example 10-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–9 Bank-Switching Example 10-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–10 TMS320C32 External Memory Interface for 32-Bit SRAMs 10-20. . . . . . . . . . . . . . . . . . . . . . .

10–1 1 Functional Diagram for 8-Bit Data-Type Size and 32-Bit External-Memory . . . . . . . . . . . . . . . .

Width 10-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–12 Functional Diagram for 16-Bit Data-Type Size and 32-Bit External-Memory . . . . . . . . . . . . .

Width 10-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–13 Functional Diagram for 32-Bit Data Size and 32-Bit External-Memory Width 10-24. . . . . . . .

10–14 External-Memory Interface for 16-Bit SRAMs 10-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–15 Functional Diagram for 8-Bit Data-Type Size and 16-Bit External-Memory Width 10-27. . . .

10–16 Functi onal Diagram for 16-Bit Data-Type Size and 16-Bit External-Memory Width 10-29. . . . .

10–17 Functi onal Diagram for 32-Bit Data-Type Size and 16-Bit External-Memory Width 10-30. . . . .

10–18 External Memory Interface for 8-Bit SRAMs 10-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–19 Functional Diagram for 8-Bit Data-Type Size and 8-Bit External-Memory Width 10-33. . . . . .

10–20 Functional Diagram for 16-Bit Data-Type Size and 8-Bit External-Memory Width 10-34. . . .

10–21 Functional Diagram for 32-Bit Data-Type Size and 8-Bit External-Memory Width 10-36. . . .

10–22 RDY

Timing for Memory Read 10-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–23 Read-Read-Write Sequence for STRBx Active 10-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–24 Write-Write-Read Sequence for STRBx Active 10-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–25 One Wait-State Read Sequence for STRBx

Active 10-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–26 One Wait-State Write Sequence for STRBx Active 10-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–27 Zero Wait-State Read and Write Sequence for IOSTRB

Active 10-43. . . . . . . . . . . . . . . . . . . .

10–28 One Wait-State Read Sequence for IOSTRB Active 10-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–29 One Wait-State Write Sequence for IOSTRB Active 10-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–30 STRBx Read and IOSTRB Write 10-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–31 STRBx

Read and IOSTRB Read 10-45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–32 STRBx Write and IOSTRB Write 10-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–33 STRBx

Write and IOSTRB Read 10-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–34 IOSTRB Write and STRBx Write 10-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–35 IOSTRB

Write and STRBx Read 10-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–36 IOSTRB Read and STRBx Write 10-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–37 IOSTRB Read and STRBx Read 10-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–38 IOSTRB

Write and Read 10-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–39 IOSTRB Write and Write 10-50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–40 IOSTRB

Read and Read 10-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–41 Inactive Bus States Following IOSTRB Bus Cycle 10-51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–42 Inactive Bus States Following STRBx Bus Cycle 10-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–1 TMS320C31 Boot-Loader Mode-Selection Flowchart 11-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–2 Boot-Loader Memory-Load Flowchart 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–3 Boot-Loader Serial-Port Load-Mode Flowchart 11-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–4 TMS320C32 Boot-Loader Mode-Selection Flowchart 11-17. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xxiii

Page 23

Figures

11–5 Boot-Loader Serial-Port Load Flowchart 11-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–6 Boot-Loader Memory-Load Flowchart 11-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–7 Handshake Data-Transfer Operation 11-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–8 External Memory Interface for Source Data Stream Memory Boot Load 11-23. . . . . . . . . . . .

12–1 Timer Block Diagram 12-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–2 Memory-Mapped Timer Locations 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–3 Timer Global-Control Register 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–4 Timer Timing 12-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .