Page 1

TLK3134

4-Channel Multi-Rate Transceiver

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SLLS838F

May 2007–Revised December 2009

Page 2

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

Contents

1 Introduction ...................................................................................................................... 11

1.1 Features .................................................................................................................... 11

1.2 Applications ................................................................................................................ 11

1.3 Pin Out ...................................................................................................................... 12

1.4 Description ................................................................................................................. 12

2 Detailed Description .......................................................................................................... 14

2.1 Clocking Modes ............................................................................................................ 14

2.2 Operating Frequency Range ............................................................................................. 15

2.3 CPRI Latency Support .................................................................................................... 15

2.4 Powerdown Mode ......................................................................................................... 15

2.5 Application Examples ..................................................................................................... 15

2.6 Device Operation Modes ................................................................................................. 20

2.7 Parallel Interface Modes - Detailed Description ....................................................................... 21

2.7.1 XAUI/10GFC Mode ............................................................................................. 21

2.7.2 RGMII Mode (Reduced Gigabit Media Independent Interface) ........................................... 22

2.7.3 RTBI Mode (Reduced Ten Bit Interface) .................................................................... 23

2.7.4 TBI Mode (Ten Bit Interface) .................................................................................. 24

2.7.5 GMII Mode (Gigabit Media Independent Interface) ........................................................ 25

2.7.6 EBI Mode (Eight Bit Interface) ................................................................................ 26

2.7.7 REBI Mode (Reduced Eight Bit Interface) ................................................................... 27

2.7.8 NBI Mode (Nine Bit Interface Mode) ......................................................................... 28

2.7.9 RNBI Mode (Reduced Nine Bit Interface) ................................................................... 29

2.7.10 TBID Mode (Ten Bit Interface DDR) ......................................................................... 30

2.7.11 NBID Mode (Nine Bit Interface DDR) ........................................................................ 31

2.7.12 Parallel Interface Clocking Modes ............................................................................ 32

2.7.13 Parallel Interface Data ......................................................................................... 33

2.7.14 Transmission Latency .......................................................................................... 33

2.7.15 Channel Clock to Serial Transmit Clock Synchronization ................................................. 34

2.7.16 Data Reception Latency ....................................................................................... 34

2.7.17 8B/10B Encoder ................................................................................................ 34

2.7.18 Comma Detect and 8B/10B Decoding ....................................................................... 36

2.7.19 Channel Initialization and Synchronization .................................................................. 36

2.7.20 Channel State Descriptions: ................................................................................... 37

2.7.21 End of Packet Error Detection ................................................................................ 38

2.7.22 Fault Detection and Reporting ................................................................................ 38

2.7.23 Receive Synchronization and Skew Compensation ....................................................... 39

2.7.24 Column State Descriptions: ................................................................................... 40

2.7.25 Inter-Packet Gap Management ............................................................................... 41

2.7.26 Clock Tolerance Compensation (CTC) ...................................................................... 44

2.7.27 Parallel to Serial ................................................................................................ 45

2.7.28 Serial to Parallel ................................................................................................ 45

2.7.29 High Speed CML Output ....................................................................................... 45

2.7.30 High Speed Receiver .......................................................................................... 47

2.7.31 Loopback ........................................................................................................ 47

2 Contents Copyright © 2007–2009, Texas Instruments Incorporated

Page 3

TLK3134

www.ti.com

2.7.32 Link Test Functions ............................................................................................. 47

2.7.33 MDIO Management Interface ................................................................................. 47

2.7.34 MDIO Protocol Timing ......................................................................................... 48

2.7.35 Clause 22 Indirect Addressing ................................................................................ 49

2.8 Programmers Reference ................................................................................................. 51

2.8.1 10G XAUI Programmers Reference (ST = 0) ............................................................... 51

2.9 1G Programmers Reference ............................................................................................. 62

2.10 Top Level Programmers Reference ..................................................................................... 68

SLLS838F–MAY 2007–REVISED DECEMBER 2009

3 Device Reset Requirements/Procedure ................................................................................ 91

3.1 XAUI MODE (XGMII) ...................................................................................................... 91

3.2 Gigabit Ethernet Mode (RGMII) ......................................................................................... 94

3.3 Jitter Test Pattern Generation and Verification Procedures ......................................................... 97

3.4 PRBS Test Generation and Verification Procedures ................................................................ 101

3.5 Signal Pin Description ................................................................................................... 104

4 Electrical Specifications ................................................................................................... 112

4.1 ABSOLUTE MAXIMUM RATINGS .................................................................................... 112

4.2 RECOMMENDED OPERATING CONDITIONS ..................................................................... 112

4.3 REFERENCE CLOCK TIMING REQUIREMENTS (REFCLKP/N) ................................................ 113

4.4 REFERENCE CLOCK ELECTRICAL CHARACTERISTICS (REFCLKP/N) ..................................... 113

4.5 SINGLE ENDED REFERENCE CLOCK ELECTRICAL CHARACTERISTICS (REFCLK) ..................... 113

4.6 JITTER CLEANER TIMING PARAMETERS ......................................................................... 113

4.7 LVCMOS ELECTRICAL CHARACTERISTICS ...................................................................... 114

4.8 MDIO ELECTRICAL CHARACTERISTICS ........................................................................... 114

4.9 HSTL SIGNALS (VDDQ = 1.5/1.8 V) ELECTRICAL CHARACTERISTICS ...................................... 114

4.10 SERIAL TRANSMITTER/RECEIVER CHARACTERISTICS ....................................................... 115

4.11 Parameter Measurement ................................................................................................ 116

4.12 HSTL Output Switching Characteristics (DDR Timing Mode Only) ............................................... 120

4.13 HSTL Output Switching Characteristics (SDR Timing Mode Only) ................................................ 121

4.14 HSTL (DDR Timing Mode Only) Input Timing Requirements ...................................................... 122

4.15 HSTL (SDR Timing Mode Only) Input Timing Requirements ...................................................... 123

4.16 MDIO Timing Requirements Over Recommended Operating Conditions ........................................ 124

4.17 JTAG Timing Requirements Over Recommended Operating Conditions ........................................ 125

4.18 Package Dissipation Rating ............................................................................................ 127

A APPENDIX A – Frequency Ranges Supported ..................................................................... 129

A.1 Recovered Byte Clock Jitter Cleaner Mode: ......................................................................... 144

B APPENDIX B – Jitter Cleaner PLL External Loop Filter ......................................................... 146

C APPENDIX C – Device Test Mode ....................................................................................... 147

Copyright © 2007–2009, Texas Instruments Incorporated Contents 3

Page 4

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

List of Figures

1-1 System Block Diagram – XAUI................................................................................................. 13

1-2 System Block Diagram – XAUI Backplane.................................................................................... 14

1-3 Block Diagram – TLK3134 Clocking Architecture............................................................................ 14

2-1 Quad 10-Bit SERDES Application ............................................................................................. 16

2-2 XAUI Mode – XAUI (Serial) Loopback Application........................................................................... 16

2-3 XAUI Mode - XGMII (Parallel ) Loopback Application....................................................................... 16

2-4 Custom Independent Configuration Application.............................................................................. 17

2-5 TLK3134 Block Diagram ........................................................................................................ 18

2-6 Detailed XAUI/1000Base-X Core Block Diagram ............................................................................ 19

2-7 Block Diagram of SERDES Core............................................................................................... 19

2-8 RGMII – Individual Channel Byte Ordering – Channel 0 Example ........................................................ 22

2-9 RTBI – Individual Channel Byte Ordering – Channel 0 Example.......................................................... 23

2-10 TBI – Individual Channel Byte Ordering – Channel 0 Example............................................................ 24

2-11 GMII – Individual Channel Byte Ordering – Channel 0 Example .......................................................... 25

2-12 EBI – Individual Channel Byte Ordering – Channel 0 Example............................................................ 26

2-13 REBI – Individual Channel Byte Ordering – Channel 0 Example.......................................................... 27

2-14 NBI – Individual Channel Byte Ordering – Channel 0 Example............................................................ 28

2-15 RNBI – Individual Channel Byte Ordering – Channel 0 Example.......................................................... 29

2-16 TBID – Individual Channel Byte Ordering – Channel 0 Example .......................................................... 30

2-17 NBID – Individual Channel Byte Ordering – Channel 0 Example.......................................................... 31

2-18 Receive Interface Timing – Source Centered/Aligned....................................................................... 32

2-19 Transmit Interface Timing....................................................................................................... 33

2-20 Transmission Latency ........................................................................................................... 34

2-21 Receiver Latency................................................................................................................. 34

2-22 Channel Synchronization State Machine...................................................................................... 37

2-23 End of Packet Error Detection.................................................................................................. 38

2-24 Column De-Skew State Machine............................................................................................... 39

2-25 Channel Deskew Using Alignment Code...................................................................................... 41

2-26 Inter-Packet Gap Management................................................................................................. 42

2-27 IPG Management State Machine .............................................................................................. 43

2-28 Clock Tolerance Compensation: Add.......................................................................................... 44

2-29 Clock Tolerance Compensation: Drop......................................................................................... 45

2-30 Example High Speed I/O AC Coupled Mode................................................................................. 46

2-31 Output differential voltage with 1-tap FIR de-emphasis..................................................................... 47

2-32 CL45 - Management Interface Extended Space Address Timing.......................................................... 48

2-33 CL45 – Management Interface Extended Space Write Timing............................................................. 48

2-34 CL45 – Management Interface Extended Space Read Timing ............................................................ 49

2-35 CL45 – Management Interface Extended Space Read And Increment Timing.......................................... 49

2-36 CL22 – Management Interface Read Timing................................................................................. 49

2-37 CL22 - Management Interface Write Timing.................................................................................. 49

2-38 CL22 – Indirect Address Method – Address Write........................................................................... 50

2-39 CL22 – Indirect Address Method – Data Write............................................................................... 50

2-40 CL22 – Indirect Address Method – Address Write........................................................................... 50

2-41 CL22 – Indirect Address Method – Data Read............................................................................... 50

3-1 Device Pinout Diagram – Part 1 (Top View) ................................................................................ 111

3-2 Device Pinout Diagram – Part 2 (Top View) ................................................................................ 111

4 List of Figures Copyright © 2007–2009, Texas Instruments Incorporated

Page 5

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

4-1 Transmit Output Waveform Parameter Definitions......................................................................... 116

4-2 Transmit Template.............................................................................................................. 117

4-3 Receive Template .............................................................................................................. 117

4-4 Input Jitter........................................................................................................................ 117

4-5 HSTL (DDR Timing Mode Only) Source Centered Output Timing Requirements ..................................... 120

4-6 HSTL (DDR Timing Mode Only) Source Aligned Output Timing Requirements........................................ 120

4-7 HSTL (SDR Timing Mode Only) Rising Edge Aligned Output Timing Requirements.................................. 121

4-8 HSTL (SDR Timing Mode Only) Falling Edge Aligned Output Timing Requirements ................................. 121

4-9 HSTL (DDR Timing Mode Only) Source Centered Data Input Timing Requirements................................. 122

4-10 HSTL (DDR Timing Mode Only) Source Aligned Data Input Timing Requirements ................................... 122

4-11 HSTL (SDR Timing Mode Only) Falling Edge Aligned (Rising Edge Sampled) Data Input Timing

Requirements ................................................................................................................... 123

4-12 HSTL (SDR Timing Mode Only) Rising Edge Aligned (Falling Edge Sampled) Data Input Timing

Requirements ................................................................................................................... 123

4-13 MDIO Read/Write Timing...................................................................................................... 124

4-14 HSTL I/O Schematic............................................................................................................ 124

4-15 JTAG Timing .................................................................................................................... 126

4-16 TLK3134 Application Mode vs Interface Timing Mode Support .......................................................... 127

4-17 PACKAGE Information (Package Designator = ZEL)...................................................................... 127

4-18 Worst Case Device Power Dissipation....................................................................................... 128

A-1 Reference Clock Selection – XAUI – 10 GbE Mode....................................................................... 130

A-2 Reference Clock Selection – 10 Gigabit Fibre Channel Mode............................................................ 130

A-3 Reference Clock Selection – Gigabit Ethernet Mode ...................................................................... 131

A-4 Reference Clock Selection – 1X/2X Fibre Channel Mode................................................................. 131

A-5 Reference Clock Selection – OBSAI Mode ................................................................................. 132

A-6 Reference Clock Selection – CPRI Mode ................................................................................... 132

A-7 Reference Clock Selection – 9/10 Bit SERDES Mode – Full Rate (SPEED[1:0] == 00).............................. 133

A-8 Reference Clock Selection – 9/10 Bit SERDES Mode – Half Rate (SPEED[1:0] == 01) ............................. 133

A-9 Reference Clock Selection –9/10 Bit SERDES Mode – Quarter Rate (SPEED[1:0] == 10).......................... 134

A-10 Reference Clock Selection – 8 Bit SERDES Mode – Full Rate (SPEED[1:0] == 00).................................. 134

A-11 Reference Clock Selection – 8 Bit SERDES Mode – Half Rate (SPEED[1:0] == 01) ................................. 135

A-12 Reference Clock Selection – 8 Bit SERDES Mode – Quarter Rate (SPEED[1:0] == 10)............................. 136

A-13 Standard Based Jitter Cleaner/SERDES Provisioning..................................................................... 137

A-14 9/10 BIT SERDES Mode – Jitter Cleaner/SERDES (2x) Provisioning................................................... 138

A-15 9/10 BIT SERDES Mode – Jitter Cleaner/SERDES (1x) Provisioning................................................... 139

A-16 9/10 BIT SERDES Mode – Jitter Cleaner/SERDES (0.5x) Provisioning ................................................ 140

A-17 9/10 BIT SERDES Mode – Jitter Cleaner/SERDES (0.25x) Provisioning............................................... 141

A-18 8 BIT SERDES Mode – Jitter Cleaner/SERDES (2x) Provisioning ..................................................... 142

A-20 8 BIT SERDES Mode – Jitter Cleaner/SERDES (0.5x) Provisioning .................................................... 144

A-21 Recovered Byte Clock Jitter Cleaner Mode................................................................................. 145

B-1 Jitter Cleaner External Loop Filter............................................................................................ 146

Copyright © 2007–2009, Texas Instruments Incorporated List of Figures 5

Page 6

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

List of Tables

2-1 Supported Protocol Rates and REFCLK Values............................................................................. 15

2-2 Device Operation Modes ........................................................................................................ 20

2-3 XAUI – Lane To Functional Pin Mapping (XAUI_ORDER = 1) ............................................................ 21

2-4 10GFC – Lane To Functional Pin Mapping (XAUI_ORDER = 0) .......................................................... 21

2-5 RGMII – Lane To Functional Pin Mapping.................................................................................... 22

2-6 RTBI – Lane To Functional Pin Mapping ..................................................................................... 23

2-7 TBI – Lane To Functional Pin Mapping ....................................................................................... 24

2-8 GMII – Lane To Functional Pin Mapping...................................................................................... 25

2-9 EBI – Lane To Functional Pin Mapping ....................................................................................... 26

2-10 REBI – Lane To Functional Pin Mapping ..................................................................................... 27

2-11 NBI – Lane To Functional Pin Mapping....................................................................................... 28

2-12 RNBI – Lane To Functional Pin Mapping ..................................................................................... 29

2-13 TBID – Lane To Functional Pin Mapping ..................................................................................... 30

2-14 NBID – Lane To Functional Pin Mapping ..................................................................................... 31

2-15 Valid K-Codes .................................................................................................................... 35

2-16 Valid XGMII Channel Encodings ............................................................................................... 35

2-17 Receive Data Controls........................................................................................................... 36

2-18 IPG Management State Machine Notation.................................................................................... 43

2-19 XS_CONTROL_1 ................................................................................................................ 51

2-20 XS_STATUS_1................................................................................................................... 51

2-21 XS_DEVICE_IDENTIFIER_1 ................................................................................................... 51

2-22 XS_DEVICE_IDENTIFIER_2 ................................................................................................... 51

2-23 XS_SPEED_ABILITY............................................................................................................ 52

2-24 XS_DEVICES_IN_PACKAGE_1 ............................................................................................... 52

2-25 XS_DEVICES_IN_PACKAGE_2 ............................................................................................... 52

2-26 XS_STATUS_2................................................................................................................... 52

2-27 XS_PACKAGE_IDENTIFIER_1 ................................................................................................ 52

2-28 XS_PACKAGE_IDENTIFIER_2 ................................................................................................ 53

2-29 XS_LANE_STATUS.............................................................................................................. 53

2-30 XS_TEST_CONTROL ........................................................................................................... 53

2-31 TEST_CONFIG................................................................................................................... 53

2-32 TEST_VERIFICATION_CONTROL............................................................................................ 53

2-33 TX_FIFO_STATUS............................................................................................................... 54

2-34 TX_FIFO_DROP_COUNT ...................................................................................................... 54

2-35 TX_FIFO_INSERT_COUNT .................................................................................................... 54

2-36 TX_CODEGEN_STATUS....................................................................................................... 54

2-37 LANE_0_TEST_ERROR_COUNT............................................................................................. 54

2-38 LANE_1_ TEST_ERROR_COUNT ............................................................................................ 55

2-39 LANE_2_ TEST_ERROR_COUNT ............................................................................................ 55

2-40 LANE_3_ TEST_ERROR_COUNT ............................................................................................ 55

2-41 10GFCCJPAT_CRPAT_CJPAT_TEST_ERROR_COUNT_1 ............................................................. 55

2-42 10GFCCJPAT_CRPAT_CJPAT_TEST_ERROR_COUNT_2 ............................................................. 55

2-43 LANE_0_EOP_ERROR_COUNT ............................................................................................. 55

2-44 LANE_1_EOP_ERROR_COUNT ............................................................................................. 56

2-45 LANE_2_EOP_ERROR_COUNT ............................................................................................. 56

2-46 LANE_3_EOP_ERROR_COUNT ............................................................................................. 56

6 List of Tables Copyright © 2007–2009, Texas Instruments Incorporated

Page 7

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2-47 LANE_0_CODE_ERROR_COUNT ........................................................................................... 56

2-48 LANE_1_CODE_ERROR_COUNT ........................................................................................... 56

2-49 LANE_2_CODE_ERROR_COUNT ........................................................................................... 57

2-50 LANE_3_CODE_ERROR_COUNT ........................................................................................... 57

2-51 RX_CHANNEL_SYNC_STATE ................................................................................................ 57

2-52 RX_LANE_ALIGN_STATUS.................................................................................................... 57

2-53 RX_CHANNEL_SYNC_STATUS............................................................................................... 57

2-54 BIT_ORDER ...................................................................................................................... 57

2-55 LOOPBACK_CONTROL ....................................................................................................... 58

2-56 TX_MODE_CONTROL.......................................................................................................... 58

2-57 RX_CTC_STATUS............................................................................................................... 58

2-58 RX_CTC_INSERT_COUNT..................................................................................................... 58

2-59 RX_CTC_DELETE_COUNT.................................................................................................... 59

2-60 DATA_DOWN..................................................................................................................... 59

2-61 RX_MODE_CONTROL.......................................................................................................... 59

2-62 CLOCK_DOWN_STATUS ...................................................................................................... 59

2-63 DATAPATH_RESET_CONTROL .............................................................................................. 59

2-64 TEST_PATTERN_STATUS..................................................................................................... 60

2-65 LANE_0_ERROR_CODE ....................................................................................................... 60

2-66 LANE_1_ERROR_CODE ....................................................................................................... 60

2-67 LANE_2_ERROR_CODE ....................................................................................................... 60

2-68 LANE_3_ERROR_CODE ....................................................................................................... 60

2-69 RX_PHASE_SHIFT_CONTROL ............................................................................................... 60

2-70 CHANNEL_SYNC_CONTROL ................................................................................................. 61

2-71 XGMII_IO_MODE_CONTROL.................................................................................................. 61

2-72 10G_MODE_CONTROL ........................................................................................................ 61

2-73 RX_CLK_OUTPUT_CONTROL................................................................................................ 61

2-74 PHY_CONTROL_1............................................................................................................... 62

2-75 PHY_STATUS_1 ................................................................................................................. 63

2-76 PHY_IDENTIFIER_1............................................................................................................. 63

2-77 PHY_IDENTIFIER_2............................................................................................................. 63

2-78 PHY_EXT_STATUS ............................................................................................................. 63

2-79 PHY_CH_CONTROL_1 ......................................................................................................... 64

2-80 PHY_CH_CONTROL_2 ......................................................................................................... 64

2-81 PHY_RX_CTC_FIFO_STATUS ................................................................................................ 66

2-82 PHY_TX_CTC_FIFO_STATUS ................................................................................................ 66

2-83 PHY_TX_WIDE_FIFO _STATUS.............................................................................................. 66

2-84 PHY_TEST_PATTERN_SYNC_STATUS..................................................................................... 66

2-85 PHY_TEST_PATTERN_COUNTER........................................................................................... 66

2-86 PHY_CRPAT_PATTERN_COUNTER_1 ..................................................................................... 66

2-87 PHY_CRPAT_PATTERN_COUNTER_2 ..................................................................................... 67

2-88 PHY_TEST_MODE_CONTROL................................................................................................ 67

2-89 PHY_CHANNEL_STATUS...................................................................................................... 67

2-90 PHY_PRBS_HIGH_SPEED_TEST_COUNTER ............................................................................. 67

2-91 PHY_EXT_ADDRESS_CONTROL ........................................................................................... 67

2-92 PHY_EXT_ADDRESS_DATA ................................................................................................. 67

2-93 SERDES_PLL_CONFIG ........................................................................................................ 68

2-94 PLL Multiplier Control............................................................................................................ 68

Copyright © 2007–2009, Texas Instruments Incorporated List of Tables 7

Page 8

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

2-95 SERDES_RATE_CONFIG_TX_RX ........................................................................................... 68

2-96 SERDES_RX0_CONFIG ....................................................................................................... 70

2-97 SERDES_RX1_CONFIG ....................................................................................................... 70

2-98 SERDES_RX2_CONFIG ....................................................................................................... 71

2-99 SERDES_RX3_CONFIG ....................................................................................................... 71

2-100 SERDES_TX0_CONFIG ....................................................................................................... 72

2-101 SERDES_TX1_CONFIG ....................................................................................................... 72

2-102 SERDES_TX2_CONFIG ....................................................................................................... 73

2-103 SERDES_TX3_CONFIG ....................................................................................................... 73

2-104 Transmit De-emphasis Control................................................................................................. 74

2-105 Output Swing Control............................................................................................................ 74

2-106 SERDES_TEST_CONFIG_TX ................................................................................................. 74

2-107 SERDES_TEST_CONFIG_RX ................................................................................................ 76

2-108 SERDES_RX0_STATUS ....................................................................................................... 76

2-109 SERDES_RX1_STATUS ....................................................................................................... 76

2-110 SERDES_RX2_STATUS ....................................................................................................... 77

2-111 SERDES_RX3_STATUS ....................................................................................................... 77

2-112 SERDES_TX0_STATUS ....................................................................................................... 77

2-113 SERDES_TX1_STATUS ....................................................................................................... 77

2-114 SERDES_TX2_STATUS ....................................................................................................... 77

2-115 SERDES_TX3_STATUS ....................................................................................................... 78

2-116 SERDES_PLL_STATUS ........................................................................................................ 78

2-117 JC_CLOCK_MUX_CONTROL.................................................................................................. 78

2-118 JC_VTP_CLK_DIV_CONTROL ................................................................................................ 79

2-119 JC_DELAY_STOPWATCH_CLK_DIV_CONTROL.......................................................................... 79

2-120 JC_DELAY_STOPWATCH_COUNTER....................................................................................... 79

2-121 JC_REFCLK_FB_DIV_CONTROL............................................................................................. 79

2-122 JC_RXB_OUTPUT_CLK_DIV_CONTROL ................................................................................... 80

2-123 JC_CHARGE_PUMP_ CONTROL ............................................................................................ 80

2-124 Charge Pump Control Setting (CP_CTRL) ................................................................................... 80

2-125 JC_PLL_CONTROL.............................................................................................................. 81

2-126 JC_TEST_CONTROL_1 ........................................................................................................ 81

2-127 JC_TEST_CONTROL_2 ........................................................................................................ 81

2-128 JC_TI_TEST_CONTROL_1..................................................................................................... 81

2-129 JC_TI_TEST_CONTROL_2..................................................................................................... 82

2-130 JC_TRIM_STATUS .............................................................................................................. 82

2-131 DIE_ID_7.......................................................................................................................... 82

2-132 DIE_ID_6.......................................................................................................................... 82

2-133 DIE_ID_5.......................................................................................................................... 82

2-134 DIE_ID_4.......................................................................................................................... 82

2-135 DIE_ID_3.......................................................................................................................... 82

2-136 DIE_ID_2.......................................................................................................................... 82

2-137 DIE_ID_1.......................................................................................................................... 83

2-138 DIE_ID_0.......................................................................................................................... 83

2-139 EFUSE_STATUS................................................................................................................. 83

2-140 EFUSE_CONTROL .............................................................................................................. 83

2-141 HSTL_INPUT_TERMINATION_CONTROL................................................................................... 83

2-142 HSTL_OUTPUT_SLEWRATE_CONTROL ................................................................................... 84

8 List of Tables Copyright © 2007–2009, Texas Instruments Incorporated

Page 9

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2-143 HSTL_INPUT_VTP_CONTROL................................................................................................ 84

2-144 HSTL_OUTPUT_VTP_CONTROL............................................................................................. 85

2-145 HSTL_GLOBAL_CONTROL.................................................................................................... 85

2-146 TX0_DLL_CONTROL............................................................................................................ 86

2-147 TX1_DLL_CONTROL............................................................................................................ 86

2-148 TX2_DLL_CONTROL............................................................................................................ 86

2-149 TX3_DLL_CONTROL............................................................................................................ 86

2-150 RX0_DLL_CONTROL ........................................................................................................... 87

2-151 RX1_DLL_CONTROL ........................................................................................................... 87

2-152 RX2_DLL_CONTROL ........................................................................................................... 87

2-153 RX3_DLL_CONTROL ........................................................................................................... 87

2-154 DLL Offset Control ............................................................................................................... 87

2-155 TX0_DLL_STATUS .............................................................................................................. 88

2-156 TX1_DLL_STATUS .............................................................................................................. 88

2-157 TX2_DLL_STATUS .............................................................................................................. 88

2-158 TX3_DLL_STATUS .............................................................................................................. 88

2-159 RX0_DLL_STATUS.............................................................................................................. 88

2-160 RX1_DLL_STATUS.............................................................................................................. 88

2-161 RX2_DLL_STATUS.............................................................................................................. 88

2-162 RX3_DLL_STATUS.............................................................................................................. 89

2-163 CH0_TESTFAIL_ERR_COUNTER ............................................................................................ 89

2-164 CH1_TESTFAIL_ERR_COUNTER ............................................................................................ 89

2-165 CH2_TESTFAIL_ERR_COUNTER ............................................................................................ 89

2-166 CH3_TESTFAIL_ERR_COUNTER ............................................................................................ 89

2-167 STCI_CONTROL_STATUS..................................................................................................... 89

2-168 TESTCLK_CONTROL........................................................................................................... 90

2-169 BIDI_CMOS_CONTROL ........................................................................................................ 90

2-170 DEBUG_CONTROL.............................................................................................................. 90

2-171 DUTY_CYCLE_CONTROL ..................................................................................................... 90

3-1 Global Signals................................................................................................................... 104

3-2 JTAG Signals.................................................................................................................... 105

3-3 MDIO Related Signals ......................................................................................................... 105

3-4 Parallel Data Pins............................................................................................................... 106

3-5 Serial Side Data/Clock Pins ................................................................................................... 108

3-6 Miscellaneous Pins ............................................................................................................. 108

3-7 Voltage Supply and Reference Pins ......................................................................................... 109

3-8 Jitter Cleaner Related Pins.................................................................................................... 110

4-1 XAUI Driver Template Parameters ........................................................................................... 116

4-2 Parallel Interface – Valid Signal Operational Mode Definitions........................................................... 118

C-1 Device Mode Configuration.................................................................................................... 147

C-2 Device Test Mode Pin Configuration......................................................................................... 147

Copyright © 2007–2009, Texas Instruments Incorporated List of Tables 9

Page 10

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

10 List of Tables Copyright © 2007–2009, Texas Instruments Incorporated

Page 11

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

4-Channel Multi-Rate Transceiver

Check for Samples: TLK3134

1 Introduction

1.1 Features

1

• Four-Channel 600Mbps to 3.75Gbps Multi-Rate • XGMII/GMII/RGMII: Source And Data Centered

Transceiver I/O Timing Modes

• Supports 10GbE (XAUI), 1X/2X/10X Fibre • Supports Jumbo Packet (9600 byte maximum)

Channel (FC), CPRI (x1/x2/x4), OBSAI Operation.

(x1/x2/x4), and 1GbE (1000Base-X) Data Rates

• Complete IEEE Compliant 10 GbE XGXS (XAUI) Times at Chip Pins

Compliant Core and 1000Base-X PCS Support

• Supports Independent Channel SERDES Compliant Management Data Input / Output

Operation Modes in 8/10 Bit Data Modes (TBI Interface Modes (Either 1.2 V or 2.5 V MDIO I/O)

and 8 Bit + Control)

• Serial Side Transmit De-Emphasis and Receive V LVCMOS I/O Supply

Adaptive Equalization to Allow Extended

Backplane Reach

• Low Jitter LC Oscillator Jitter-Cleaner Allows

use of Poor Quality REFCLK

• Full Datapath Loopback Capability

(Serial/Parallel Side)

• Support PRBS 27-1 and 223- 1 Gen/Verify.

Support standard defined CJPAT, CRPAT, High

and Low Frequency, and Mixed Freq Testing.

• XGMII/GMII/RGMII: HSTL Class 1 I/O With

On-Chip 50Ω Termination on Inputs/Outputs

(1.5/1.8 V Power Supply)

• XAUI Align Character Skew Support of 30 Bit

• MDIO: IEEE 802.3ae Clause 22 and Clause 45

• 1.2 V Core, 1.5 V/1.8 V HSTL I/O Supply, and 2.5

• JTAG: IEEE 1149.1/1149.6 Test Interface

• ±200 ppm Clock Tolerance in XAUI TX and

1000Base-X/XAUI RX Datapaths

• 90 nm Advanced CMOS Technology

• Package: PBGA, 19×19mm, 289 Ball, 1mm Pitch

• 1.3W Maximum Power Dissipation (1.5 V HSTL

XAUI Mode, Input HSTL Termination Disabled)

• Asymmetric RX/TX Rates Supported in

Independent Channel Modes

• Industrial Ambient Operating Temperature

(–40°C to 85°C) at Full Rate

1.2 Applications

• Gigabit Ethernet links

• CPRI/OBSAI Links

• Point-to-Point High-Speed Backplane Links

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2007–2009, Texas Instruments Incorporated

Page 12

TLK3134

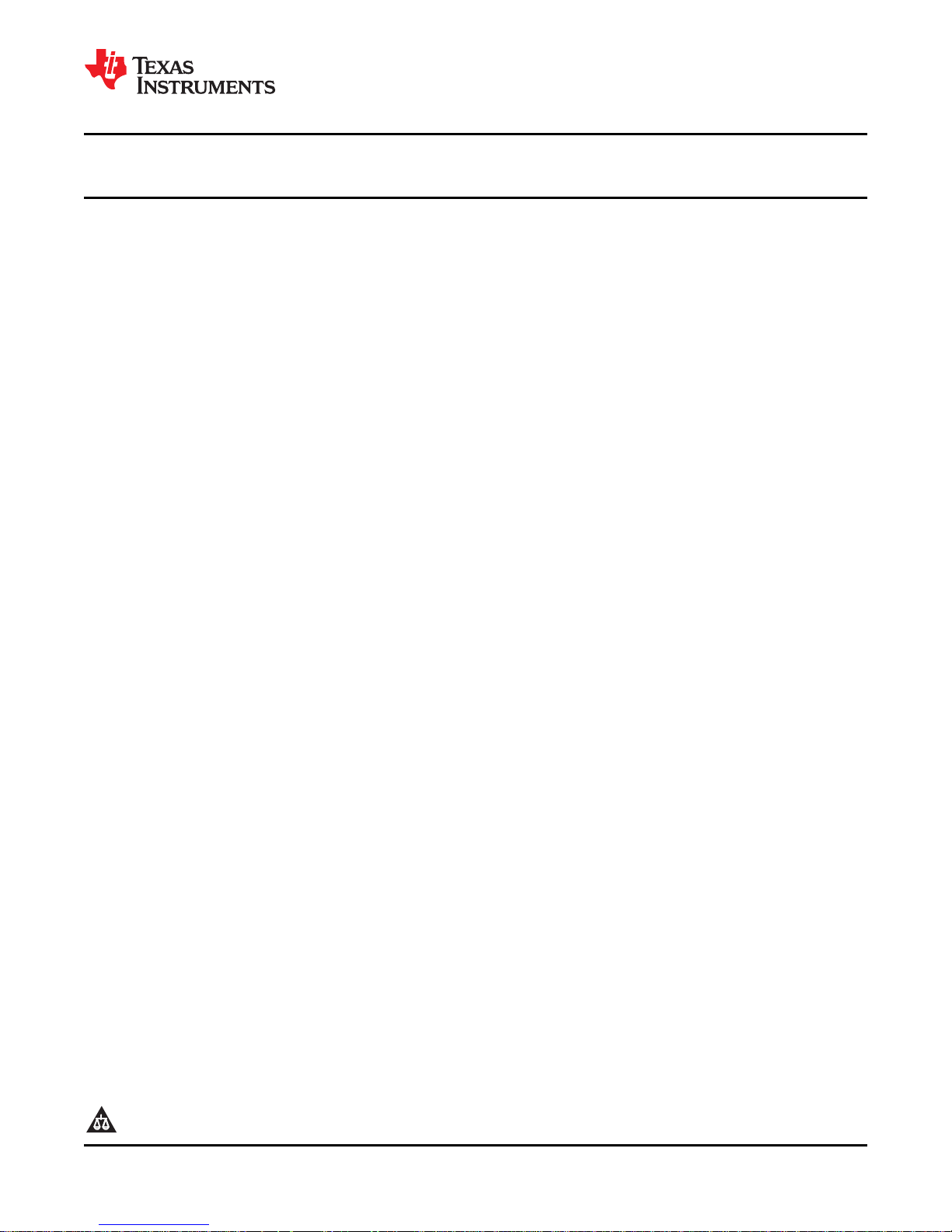

4

4

TDP/N[3:0]

RDP/N[3:0]

TD(31..0)

TCLK(3:0)

TC(7..0)

RCLK(3:0)

RD(31..0)

RC(7..0)

(R)GMII/XGMII

XAUI/SerialI/F

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

1.3 Pin Out

1.4 Description

The TLK3134 is a flexible four-channel independently configurable serial transceiver. It can be configured

to be compliant with the 10Gbps Ethernet XAUI specification. It can also be configured to be compliant

with the 1000Base-X 1Gbps Ethernet Specification (Auto-Negotiation not supported). The TLK3134

provides high-speed bidirectional point-to-point data transmissions with up to 30 Gbps of raw data

transmission capacity. The primary application of this device is in backplanes and front panel connections

requiring 10Gbps connections over controlled impedance media of approximately 50Ω. The transmission

media can be printed circuit board (PCB) traces, copper cables or fiber-optical media. The ultimate rate

and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise

coupling into the lines.

www.ti.com

The TLK3134 performs the parallel-to-serial, serial-to-parallel conversion, and clock extraction functions

for a physical layer interface. The TLK3134 provides a complete XGXS/PCS function defined in Clause

47/48 of the IEEE 802.3ae 10Gbps Ethernet standard. The TLK3134 also provides 1000Base-X (PCS)

layer functionality described in Clause 36 of 802.3-2002. The serial transmitter is implemented using

differential Current Mode Logic (CML) with integrated termination resistors.

The TLK3134 can be optionally configured as a XAUI or 10GFC transceiver. TLK3134 supports a 32-bit

data path, 4-bit control, 10 Gigabit Media Independent Interface (XGMII) to the protocol device. Figure 1-1

shows an example system block diagram for TLK3134 used to provide the 10Gbps Ethernet Physical

Coding Sublayer to Coarse Wave-length Division Multiplexed optical transceiver or parallel optics.

Many common applications may be enabled by way of externally available control pins. Detailed control of

the TLK3134 on a per channel basis is available by way of accessing a register space of control bits

available through a two-wire access port called the Management Data Input/Output (MDIO) interface.

The PCS (Physical Coding Sublayer) functions such as the CTC FIFO are designed to be compliant for an

IEEE 802.3 XAUI or 1000Base-X PCS link. However, each of the PCS functions may be disabled or

bypassed until the TLK3134 is operating at its most basic state, that of a simple four channel 10-bit

SERDES suitable for a wide range of applications such as CPRI or OBSAI wireless infrastructure links.

The differential output swing for the TLK3134 is suitable for compliance with IEEE 802.3 XAUI links, which

is also suitable for CPRI LV serial links. The TLK3134 provides for setting larger output signal swing

suitable for CPRI HV links by setting an appropriate register bit available though MDIO.

12 Introduction Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 13

TLK3134TLK3134

TD(31:0)

TCLK

RCLK

RD(31:0)

LineCard

4

4

4

4

TC(3:0)

RC(3:0)

XAUIBackplane

XAUI

XGMIRX

A

XGMITX

A

MAC/

Packet

Processor

XAUI

CWDMor

Parallel

Optics

LineCard

4

4

4

4

TLK3134

TD(31:0)

RD(31:0)

TCLK

RCLK

RDP/N[3:0]

TDP/N[3:0]

TC(3:0)

TLK3134

TD(31:0)

RD(31:0)

TCLK

RCLK

RDP/N[3:0]

TDP/N[3:0]

TC(3:0)

RC(3:0)

RC(3:0)

MAC/

PACKET

PROCESSOR

FRAMER/

PCS

PHY/

OPTICS

SystemBackplane

SWITCH

FABRIC

TLK3134

www.ti.com

Figure 1-2 shows an example system block diagram for TLK3134 used to provide the system backplane

interconnect.

SLLS838F–MAY 2007–REVISED DECEMBER 2009

Figure 1-1. System Block Diagram – XAUI

Copyright © 2007–2009, Texas Instruments Incorporated Introduction 13

Figure 1-2. System Block Diagram – XAUI Backplane

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 14

REFCLK_P

REFCLK_N

REFCLK

RXBCLK[0]

REF_SEL[1:0]

REFCLK

Divider

REF_DIV[6:0]

PLL

Feedback

Divider

FB_DIV[6:0]

FirstPLL Output

Divider

RXTX_DIV[6:0]

JitterCleaner

PLL Core

SecondPLL

Output

Divider

RXB_DIV[6:0]

TX_SEL[1:0]

RX_SEL[1:0]

REFCLK_TX

REFCLK_RX

ThirdPLL

Output

Divider

DEL_DIV[6:0]

DELAY_CLK

DEL_SEL[1:0]

RXB_SEL[1:0]

RXBYTE_CLK

00

01

1X

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

(2.875GhzMin.,3GhzTyp.,3.125GhzMax.)

FourthPLL

Output

Divider

HSTL_DIV1[6:0]

HSTL_2X_CLK

HSTL_SEL[1:0]

00

01

10

11

SERDESTX

SERDESRX

TX3P/N

TX2P/N

TX1P/N

TX0P/N

RX3P/N

RX2P/N

RX1P/N

RX0P/N

PLL

P2S

P2S

P2S

P2S

PLL

S2P

S2P

S2P

S2P

Note:DefaultMuxSelects AreUnderlined.

HSTL Output

Divider

HSTL_DIV2[6:0]

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

Figure 1-3. Block Diagram – TLK3134 Clocking Architecture

2 Detailed Description

2.1 Clocking Modes

The TLK3134 contains an internal low-bandwidth, low-jitter high quality LC oscillator that may be

configured as a jitter cleaner. The jitter cleaner oscillator has a high frequency narrow band of operation

that may be used to generate all common reference clock frequencies by way of programmable pre-scaler

and post-scaler registers. In this manner a poor quality input reference clock can be input to the jitter

cleaner which will lock to the reference clock and provide a clean reference to the internal SERDES PLLs.

Appendix A defines in detail the clocking possibilities, and device settings.

Alternatively, the jitter cleaner may be used to lock to a recovered byte clock from RX channel 0 and

remove jitter that may have transferred through the clock/data recovery circuit from the serial data stream

to the recovered byte clock (including parallel output data timing). In this way the recovered byte clock

may be extracted from the serial data stream yet be suitable for use in applications that require a clean

clock source derived from the serial data stream. The TLK3134 jitter cleaner may only be used on the

recovered byte clock from Channel 0. If the jitter cleaner is used to clean the recovered byte clock, it may

not be used to clean the input reference clock, and the PLL at the center of the deserializer core must

have a clean low-jitter reference clock from an external clock source, preferably a low-jitter crystal based

oscillator. Note that the Transmit SERDES macro can run from the cleaned recovered RX channel 0 byte

clock which allows for the outgoing TX serial data rate for all channels to exactly match the incoming data

rate of RX Channel 0.

The TLK3134 clocking architecture allows for bypass of the Jitter cleaner PLL in cases where power or

application board area is critical.

See Figure 1-3 Clocking Architecture for a representation of the use of the jitter cleaner in the TLK3134.

14 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 15

TLK3134

www.ti.com

2.2 Operating Frequency Range

The TLK3134 is optimized for operation at a serial data rate of 600 Mbit/s through 3.75 Gbit/s. The

external differential (optionally single-ended) reference clock has a large operating frequency range

allowing support for many different applications. The reference clock frequency must be within ±200 PPM

of the incoming serial data rate, and have less than 40ps of jitter. Table 2-1 shows a summary of

frequency ranges supported. For more details, see Appendix A. In all applications except XAUI/10GFC,

the transmit parallel clock must be frequency locked (0 ppm) to the supplied REFCLK frequency

(XAUI/10GFC allows ±200 ppm).

Table 2-1. Supported Protocol Rates and REFCLK Values

PROTOCOL Refclk (MHz) LINE RATE (Gbps)

XAUI – 10G Ethernet 78.125/156.25/312.5 3.125

10 Gigabit Fibre Channel 79.6875/159.375/ 318.75 3.1875

1G Ethernet 62.5/125/250 1.25

1X/2X Fibre Channel 53.125/106.25/212.5

OBSAI 76.8/153.6/307.2 1.536

CPRI 61.44/122.88/245.76 1.2288

Generic TBI 50 → 375 MHz 0.600 → 3.75

Generic RTBI 50 → 375 MHz 0.600 → 1.6

Generic NBID/TBID 50 → 375 MHz 0.600 → 3.2

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2.125

1.0625

3.072

0.768

2.4576

0.6144

2.3 CPRI Latency Support

The TLK3134 has a round trip latency measurement capability to support its use in CPRI applications.

When enabled, the TLK3134 will measure the elapsed time from the transmission of a K28.5 code in a

CPRI frame until the reception of a K28.5 code in the receive path. This measurement result may be read

through an MDIO readable register. The measurement has an accuracy of ±4 ns with the Jitter Cleaner

PLL enabled, and an accuracy of ±2 parallel byte clock periods if the Jitter Cleaner PLL is disabled.

2.4 Powerdown Mode

The TLK3134 (through the ENABLE pin and through register control) is capable of going into a low power

quiescent state. In this state, all analog and digital circuitry is disabled.

2.5 Application Examples

TLK3134 supports many different application modes. Detailed register settings per application mode are

shown in Table 2-2. The following application diagrams do not show all possible applications, and are

intended only to illustrate the flexibility of the device.

Figure 2-1 shows the TLK3134 in a Quad independent channel SERDES Application. The 1000Base-X

PCS layer can be enabled or disabled. Note that in independent channel mode, the 8B/10B

encoder/decoder functions can either be turned on or turned off. When turned off, either 5 or 10 bits

(DDR/SDR) of data is accepted from and presented to the parallel side. When the 8B/10B

encoder/decoder functions are enabled, 1 bit of control and 8 bits of data are accepted from and

presented to the parallel side using the standardized (R)GMII control characters.

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 15

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 16

XGMII

10

1

10

1

10

1

10

1

10

1

10

1

10

1

10

1

XAUI

TLK3134

TLK3134

XGXSCORE

36

4

4

XGMII

XAUI

TLK3134

XGXSCORE A

36

4

XGMII

XAUI

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

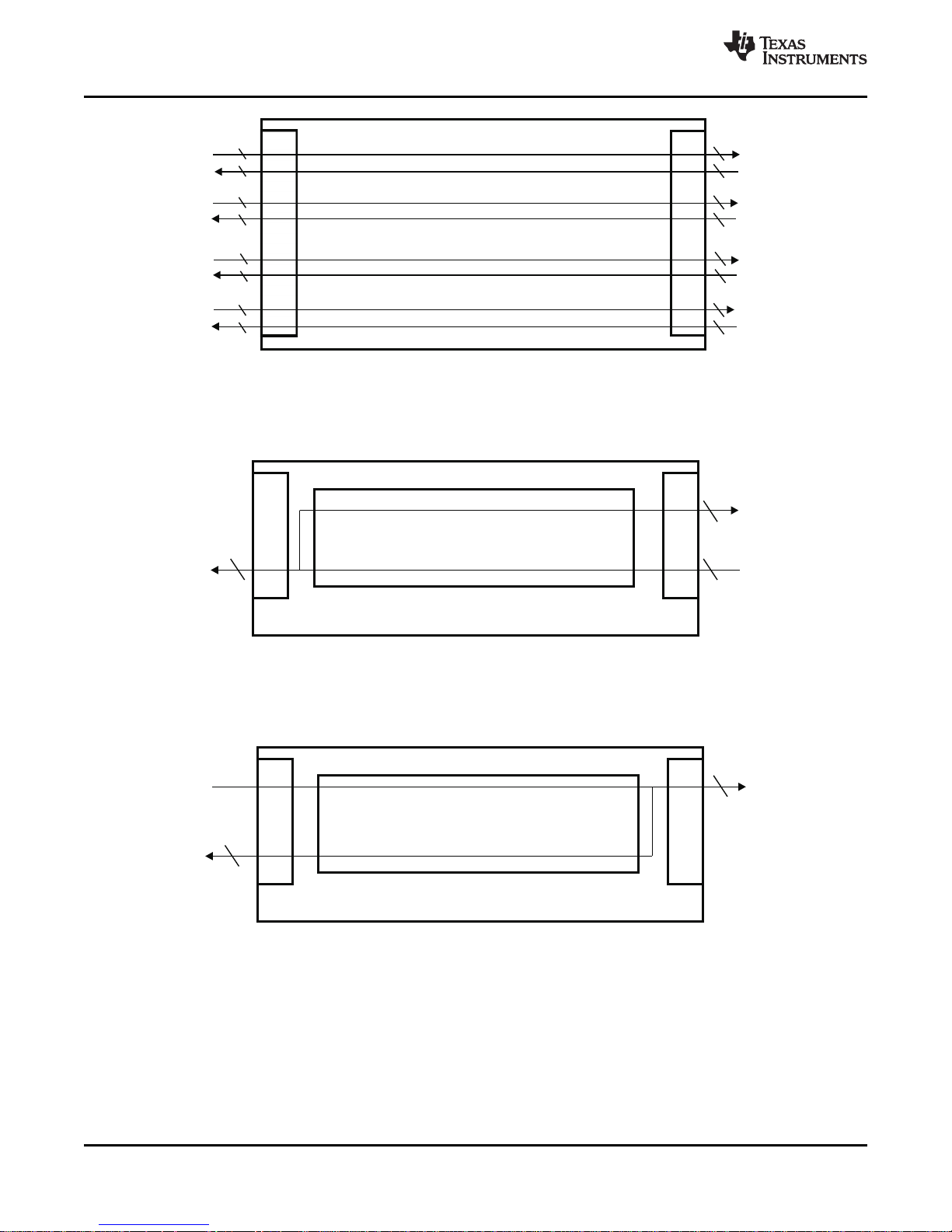

Figure 2-1. Quad 10-Bit SERDES Application

Figure 2-2 shows the TLK3134 in a XAUI Loopback Application. It is possible to configure XAUI side

loopback in SERDES mode for all 4 channels on an individual basis.

www.ti.com

Figure 2-2. XAUI Mode – XAUI (Serial) Loopback Application

Figure 2-3 shows the TLK3134 in a XGMII Loopback Application. It is possible to configure XGMII side

loopback in SERDES mode for all 4 channels on an individual basis.

Figure 2-3. XAUI Mode - XGMII (Parallel ) Loopback Application

Figure 2-4 shows the TLK3134 in a custom application example with mixed modes per Channel.

• Channel 1 in Parallel independent loopback mode

• Channel 3 in Serial independent loopback mode

• Channel 0 & 2 in independent channel transceiver mode

16 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 17

PARALLEL

XGXSCORE

LANE0

LANE1

LANE2

LANE3

SERIAL

TLK3134

TLK3134

www.ti.com

The TLK3134 supports the IEEE 802.3 defined Management Data Input/Output (MDIO) Interface to allow

ease in configuration and status monitoring of the link. The bi-directional data pin (MDIO) must be

externally pulled up to 1.2 V or 2.5 V (VDDM) per the standard for MDIO.

The TLK3134 supports the IEEE 1149.1/1149.6 defined JTAG test port for ease in board manufacturing

test. It also supports a comprehensive series of built-in tests for self-test purposes including PRBS

generation and verification, CRPAT, CJPAT, Mixed/High/Low Frequency testing.

SLLS838F–MAY 2007–REVISED DECEMBER 2009

Figure 2-4. Custom Independent Configuration Application

The TLK3134 operates with a 1.2 V core voltage supply, a 1.5/1.8 V HSTL I/O voltage supply and a 2.5 V

LVCMOS/bias supply.

The TLK3134 is packaged in a 19×19mm, 289-ball, 1mm ball pitch Plastic Ball Grid Array (PBGA)

package and is characterized for operation from –40°C to 85°C Ambient, 105°C Junction, and 5% power

supply variation at the balls of the device unless noted otherwise.

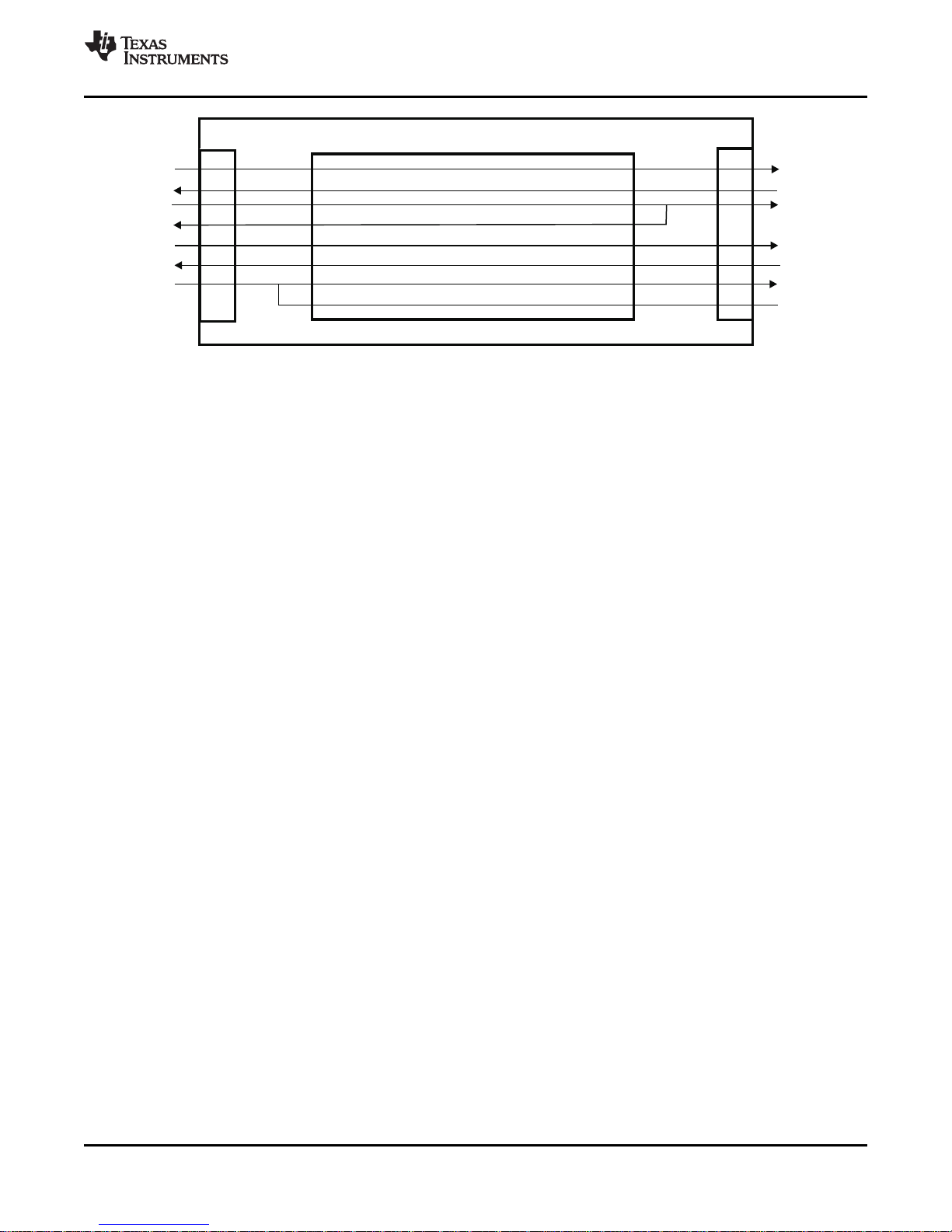

The following block diagram provides a high level description of the TLK3134.

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 17

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 18

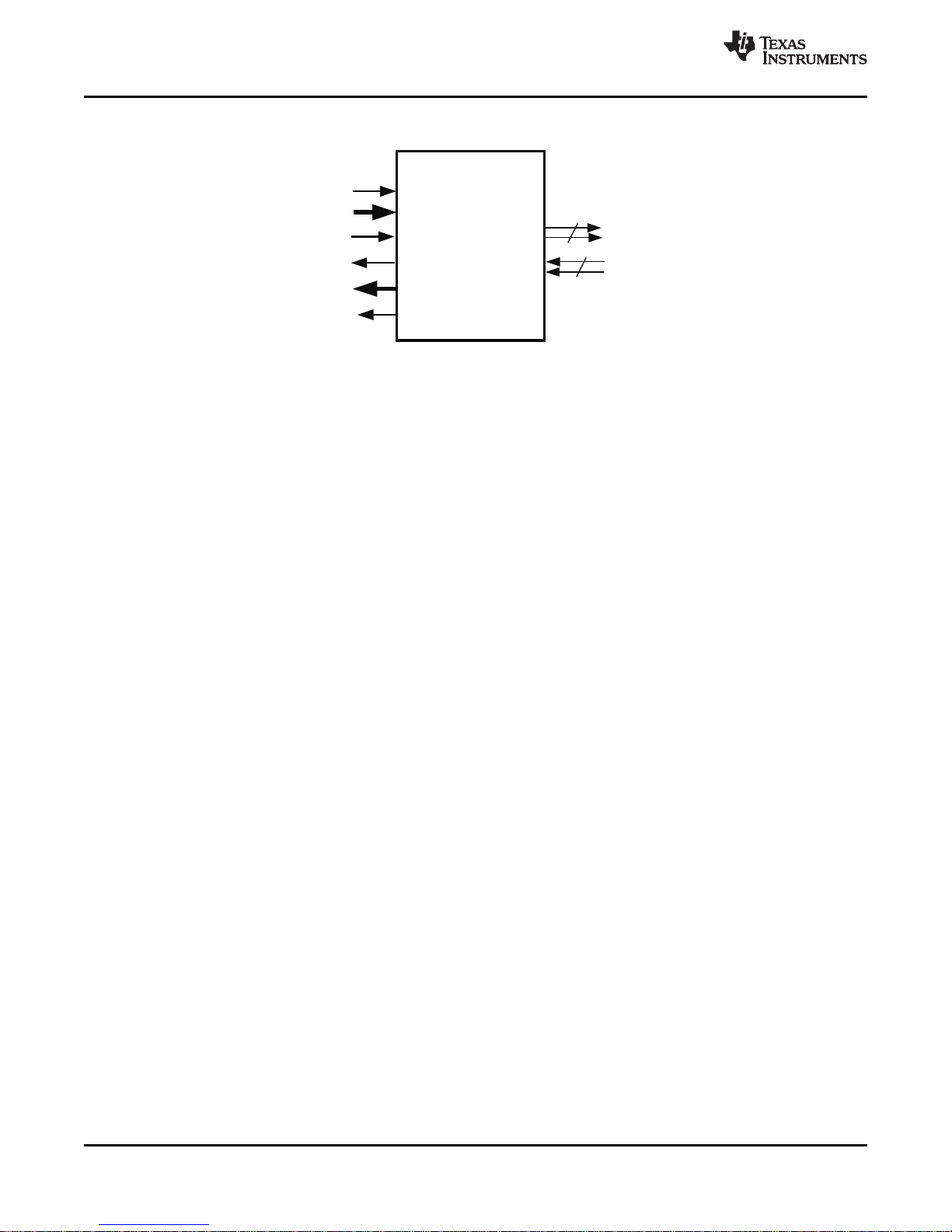

XGMII/

GMII/

RGMII/

TBI/

RTBI

TX

TXD(31:0)

XGMII/

GMII/

RGMII/

TBI/

RTBI

RX

RXD(31:0)

Serial

I/F

Core

MDIO

PRTAD[4:0]

MDIO

MDC

JTAG

TCK

TDI

TMS

TRSTN

TDO

TDP[3:0]

TDN[3:0]

4

TCLK(3:0)

RCLK(3:0)

4

TXC(7:0)

RXC(7:0)

XAUICore+

1000Base-XPCS

RDN[3:0]

RDP[3:0]

Jitter

Cleaner

PLL

TDP3/TDN3

RDP3/RDN3

CHANNEL 3

Test

mode

TDP2/TDN2

RDP2/RDN2

CHANNEL 2

Test

mode

TDP1/TDN1

RDP1/RDN1

CHANNEL 1

Test

mode

Self

Test

SERDES

Core

TCLK

TXD[7:0]

8Bit

10Bit

RCLK

REFCLKP

REFCLKN

8b/10b

Decoding

And

SelfTest

Verification/

Reporting

RX

FIFO

/

CTC

RCLK

RXD(7:0)

TDP0

TDN0

RDP0

RDN0

RCLK

CHANNEL 0

10Bit

Test

mode

8Bit

8b/

10b

enc

TX

FIFO

/

CTC

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

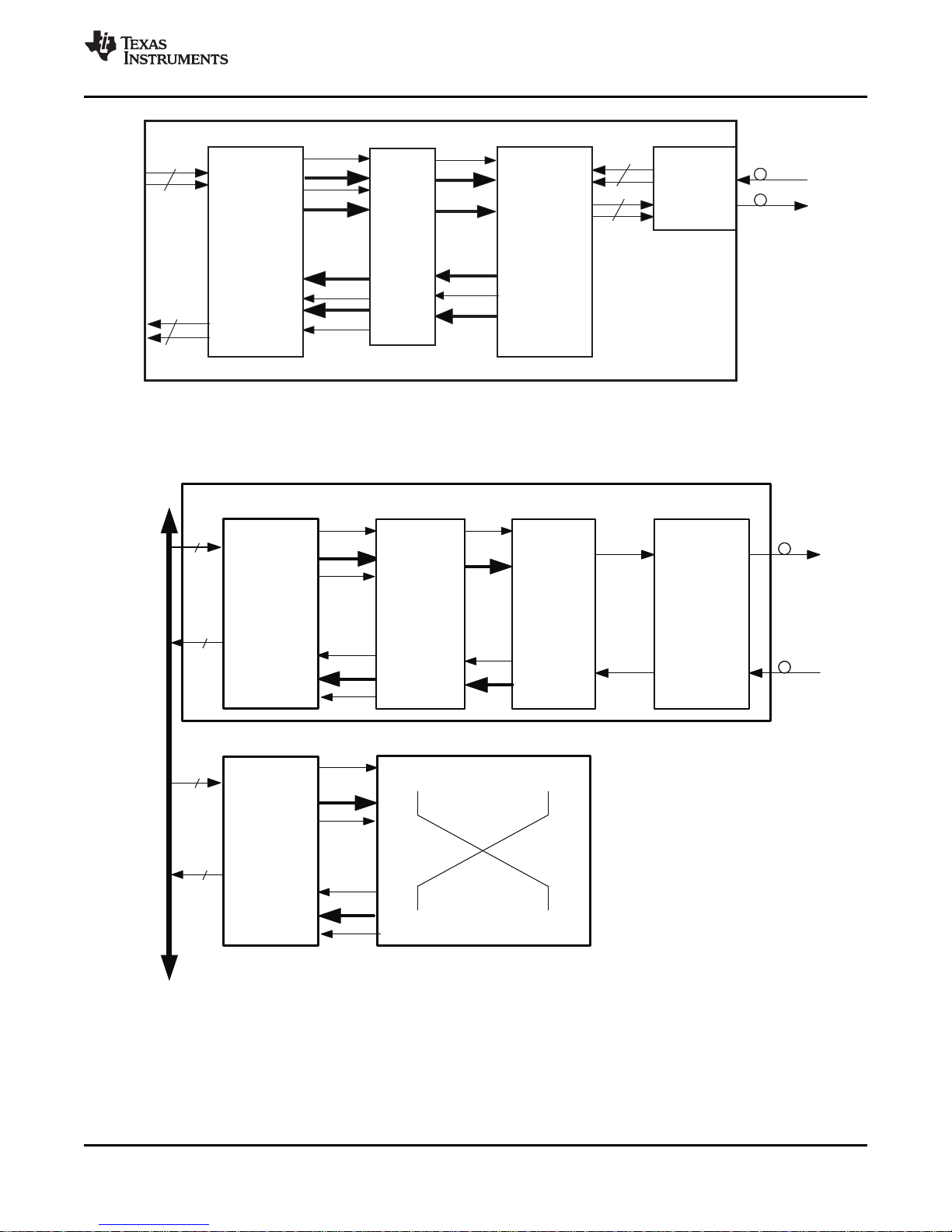

Following is a more detailed block diagram description of the XAUI core.

18 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Figure 2-6. Detailed XAUI/1000Base-X Core Block Diagram

Figure 2-5. TLK3134 Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 19

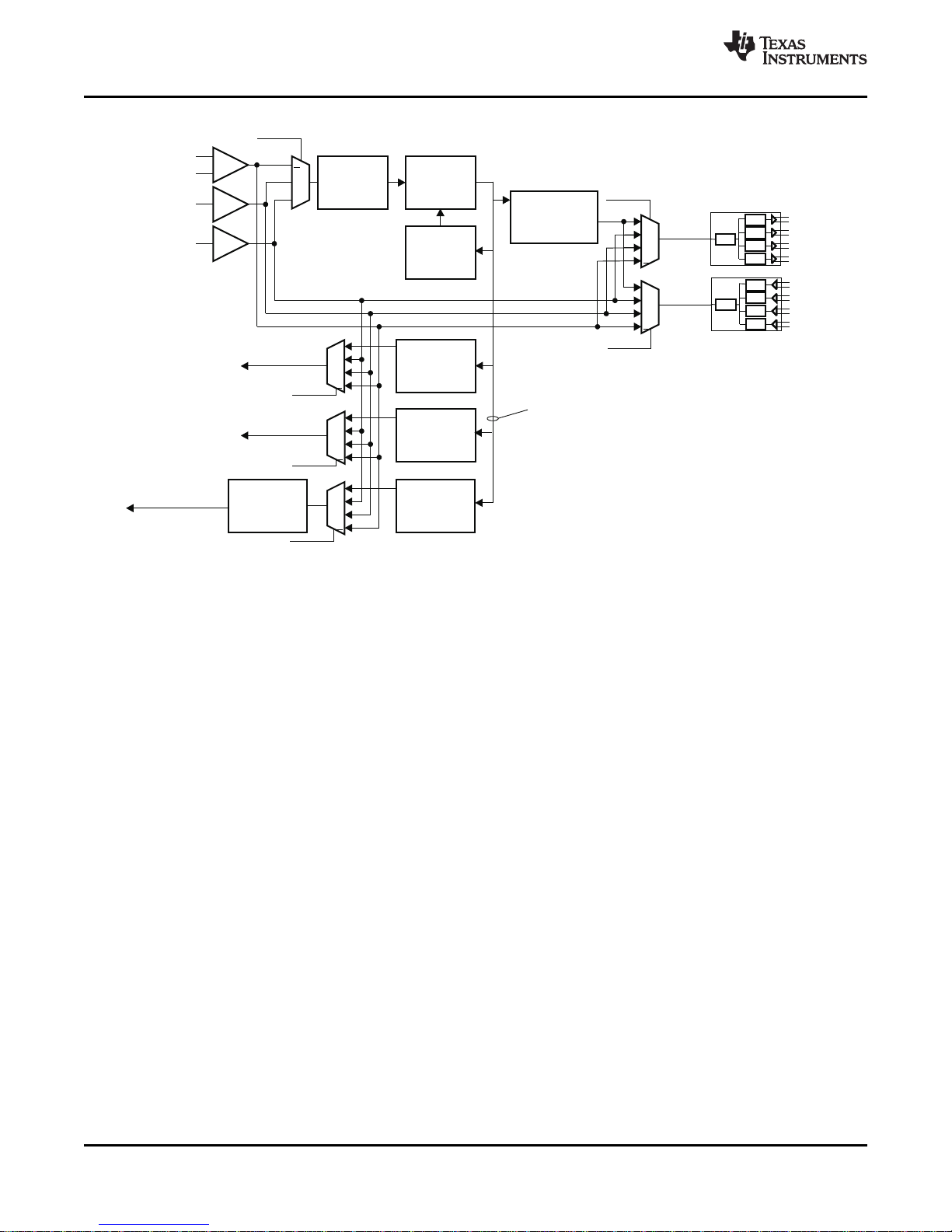

Parallel

toSerial

REFCLKP

/

N

Baud

Clock

D Q

Serialto

Parallel

and

Comma

Detect

Interpolator

andClock

Recovery

Multiplying

Clock

Synthesizer

RCLK

Recovered

Clock

TDP

TDN

RDP

RDN

ParallelDataIn

ParallelDataOut

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 19

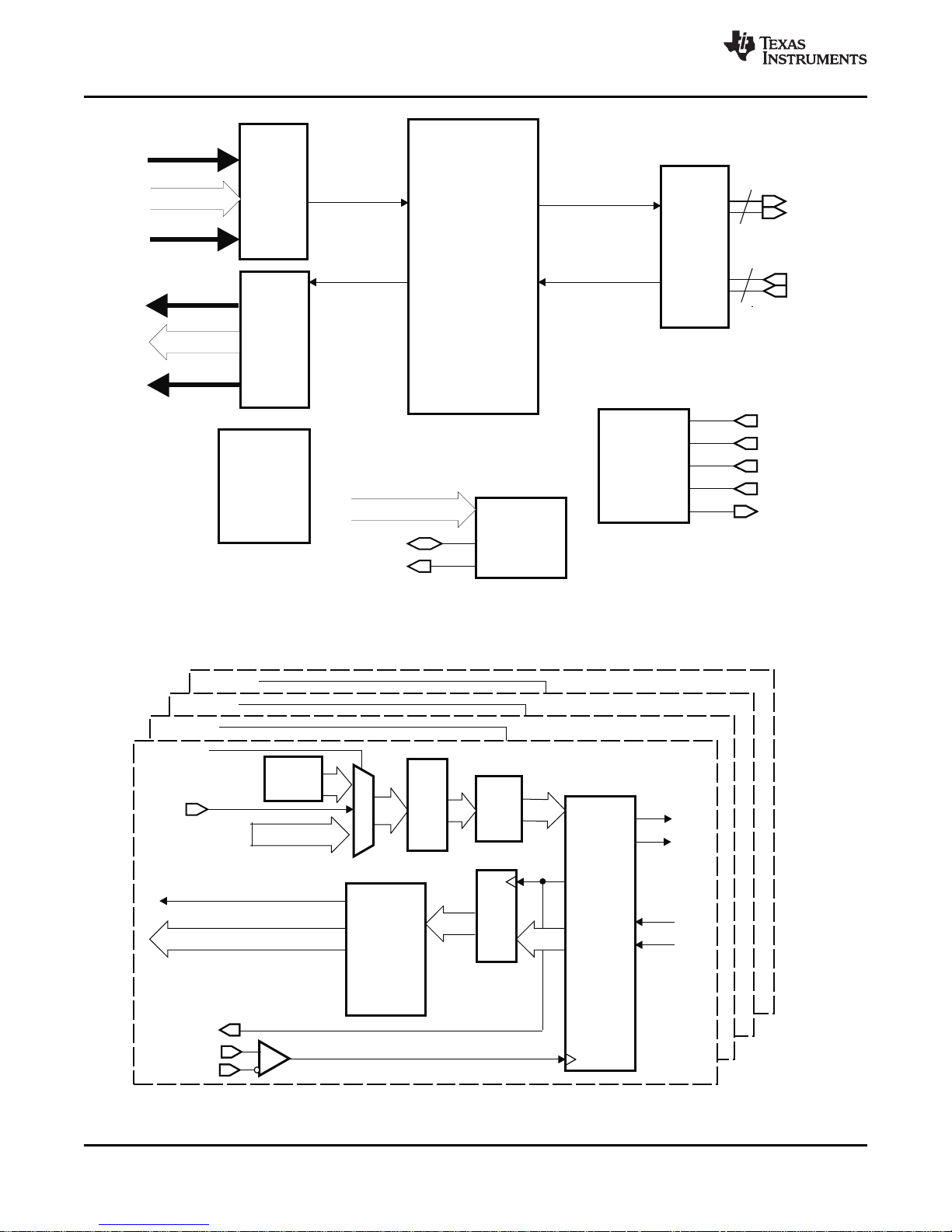

Figure 2-7. Block Diagram of SERDES Core

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 20

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

2.6 Device Operation Modes

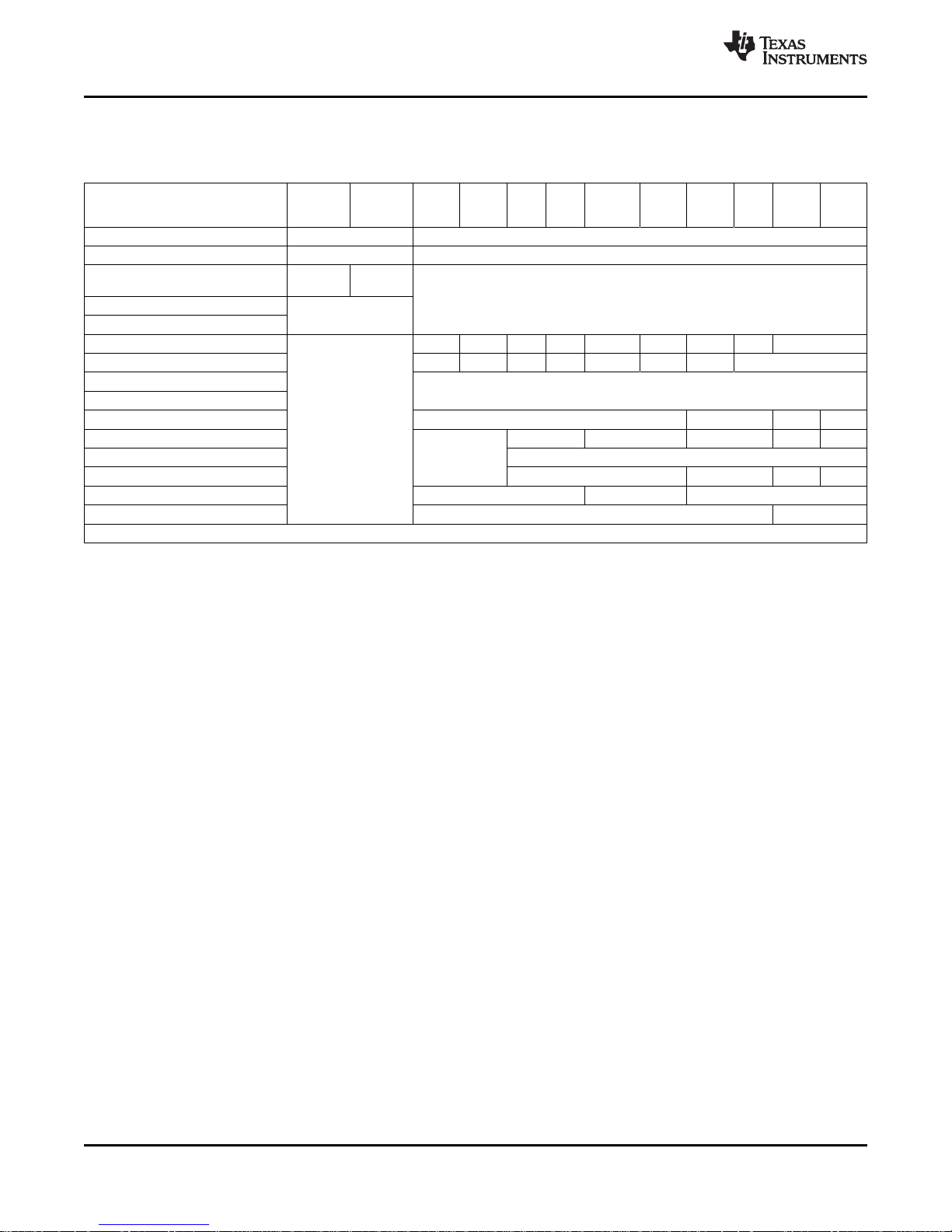

Table 2-2. Device Operation Modes

(1)

DEVICE MODE (DDR (SDR (SDR

ST Primary Chip Input 0 1

MDIO Access Method Clause 45 Clause 22

XAUI_ORDER 32809.15

Logical Or w/CODE pin

XAUI_TX_EDGE_ALIGN 32808.15

XAUI_RX_EDGE_ALIGN 32808.11

DDR_SDR 17.5 1 0 1 0 1 0 1 0 X

NIBBLE_ORDER 17.4 0/1 X 0/1 X 0/1 X 0/1 X

TX_EDGE_MODE 17.1

RX_EDGE_MODE 17.0

FC_ENC_MODE 17.6 0 0/1 0 0/1

COMMA_DET_EN 17.7 0/1 0 1 0/1 1

PCS_EN 17.3 Logical OR w/CODE pin 1 0

ENC_DEC_EN 17.2 0 1 0 1

BUSWIDTH 36864.7 0 1 0

FULL_DDR 17.9 0 1

Legend : (X = Don’t Care) — (0 = Must Be Zero) — (1 = Must Be One) — (0/1 = Can Be Either Zero-or-One)

XAUI

(DDR) (DDR) (DDR) (SDR) (DDR) (SDR) (DDR) (DDR) (DDR)

1 0

0/1

X

10GFC

(2)

RGMII GMII REBI EBI RNBI TBID NBID

(1) Default Mode if ST Primary Chip Input Pin “0”, CODE Primary Chip Input Pin “1”.

(2) Default Mode if ST Primary Chip Input Pin “0”, CODE Primary Chip Input Pin “0”.

(3) All Clause 22 Registers are Per Device Channel.

RTBI TBI NBI

) ) )

(3)

X

0/1

20 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 21

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2.7 Parallel Interface Modes - Detailed Description

The TLK3134 has several parallel interface modes. The major parallel interface modes of operation are

presented below:

2.7.1 XAUI/10GFC Mode

Table 2-3. XAUI – Lane To Functional Pin Mapping (XAUI_ORDER = 1)

XAUI LANE CONTROL BIT DATA BYTE CONTROL BIT CONTROL BYTE CLOCK CLOCK

Lane 3 TXC_[3] TXD_[31:24] RXC_[3] RXD_[31:24] TXCLK_[1] RXCLK_[1]

Lane 2 TXC_[2] TXD_[23:16] RXC_[2] RXD_[23:16] TXCLK_[1] RXCLK_[1]

Lane 1 TXC_[1] TXD_[15:8] RXC_[1] RXD_[15:8] TXCLK_[1] RXCLK_[1]

Lane 0 TXC_[0] TXD_[7:0] RXC_[0] RXD_[7:0] TXCLK_[1] RXCLK_[1]

10GFC LANE CONTROL BIT DATA BYTE CONTROL BIT CONTROL BYTE CLOCK CLOCK

Lane 0 TXC_[3] TXD_[31:24] RXC_[3] RXD_[31:24] TXCLK_[1] RXCLK_[1]

Lane 1 TXC_[2] TXD_[23:16] RXC_[2] RXD_[23:16] TXCLK_[1] RXCLK_[1]

Lane 2 TXC_[1] TXD_[15:8] RXC_[1] RXD_[15:8] TXCLK_[1] RXCLK_[1]

Lane 3 TXC_[0] TXD_[7:0] RXC_[0] RXD_[7:0] TXCLK_[1] RXCLK_[1]

TRANSMIT TRANSMIT RECEIVE RECEIVE TRANSMIT RECEIVE

(INPUT) (INPUT) (OUTPUT) (OUTPUT) (INPUT) (OUTPUT)

Table 2-4. 10GFC – Lane To Functional Pin Mapping (XAUI_ORDER = 0)

TRANSMIT TRANSMIT RECEIVE RECEIVE TRANSMIT RECEIVE

(INPUT) (INPUT) (OUTPUT) (OUTPUT) (INPUT) (OUTPUT)

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 21

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 22

TXCLK_[0]

{TX_EN,Data0[3:0]}

{TX_EN^TX_ER,

Data0[7:4]}

{TX_EN,Data1[3:0]}

{TX_EN^TX_ER,

Data1[7:4]}

TXD_[4:0]

RXCLK_[0]

{RX_DV,Data0[3:0]}

{RX_DV^RX_ER,

Data0[7:4]}

{RX_DV,Data1[3:0]}

{RX_DV^RX_ER,

Data1[7:4]}

RXD_[4:0]

DDRSourceCenteredTiming

NibbleOrder=1(Default)

TXCLK_[0]

{TX_EN,Data0[3:0]}

{TX_EN^TX_ER,

Data0[7:4]}

{TX_EN,Data1[3:0]}

{TX_EN^TX_ER,

Data1[7:4]}

TXD_[4:0]

RXCLK_[0]

{RX_DV,Data0[3:0]}

{RX_DV^RX_ER,

Data0[7:4]}

{RX_DV,Data1[3:0]}

{RX_DV^RX_ER,

Data1[7:4]}

RXD_[4:0]

DDRSource AlignedTiming

NibbleOrder=1(Default)

Note:IfNibbleOrder=0,thepictureis

thesameexceptthat

{TX_EN,DataN[3:0]}and

{TX_EN^TX_ER,DataN[7:4]}swap

locations.

Note:IfNibbleOrder=0,thepictureis

thesameexceptthat

{RX_DV,DataN[3:0]}and

{RX_DV^RX_ER,DataN[7:4]}swap

locations.

Note:IfNibbleOrder=0,thepictureis

thesameexceptthat

{TX_EN,DataN[3:0]}and

{TX_EN^TX_ER,DataN[7:4]}swap

locations.

Note:IfNibbleOrder=0,thepictureis

thesameexceptthat

{RX_DV,DataN[3:0]}and

{RX_DV^RX_ER,DataN[7:4]}swap

locations.

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

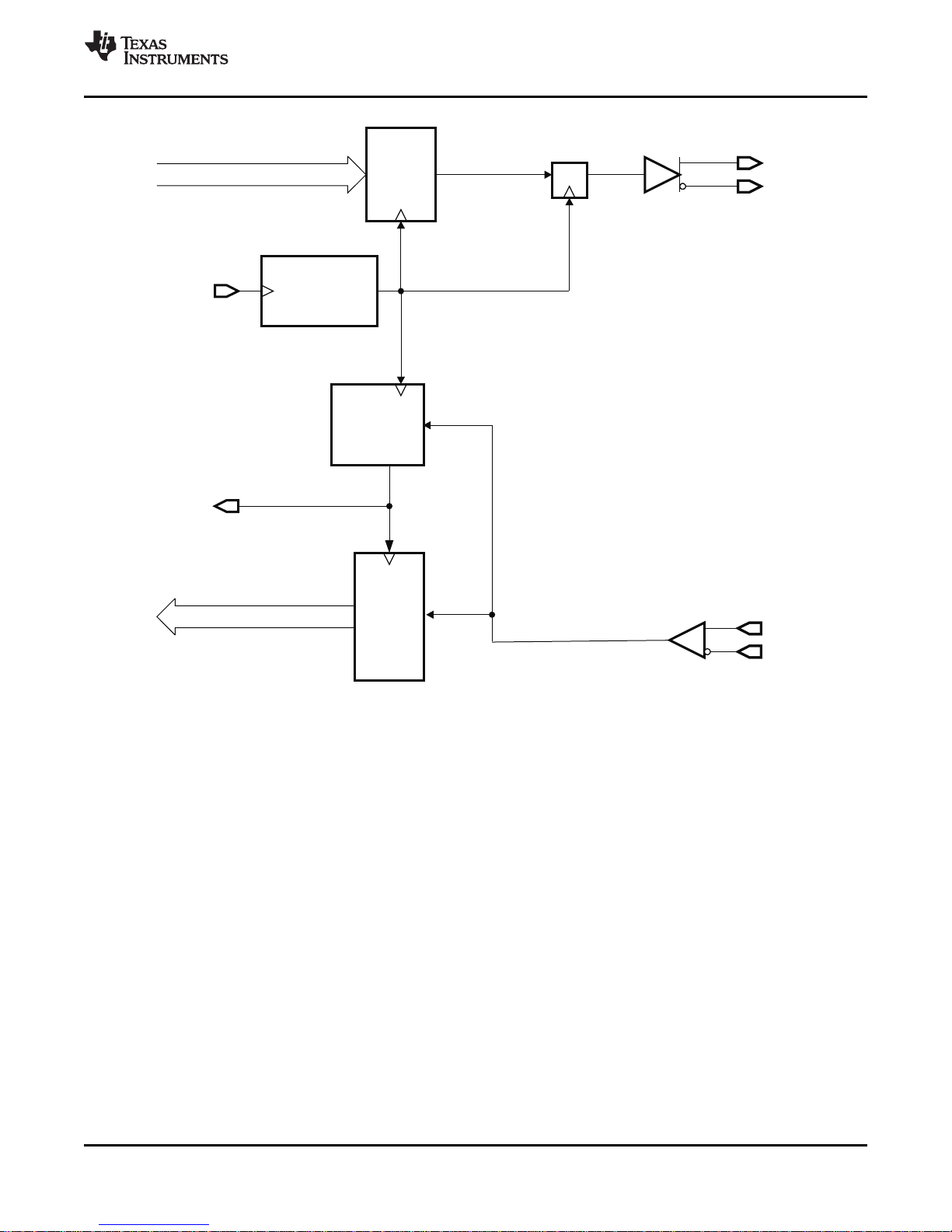

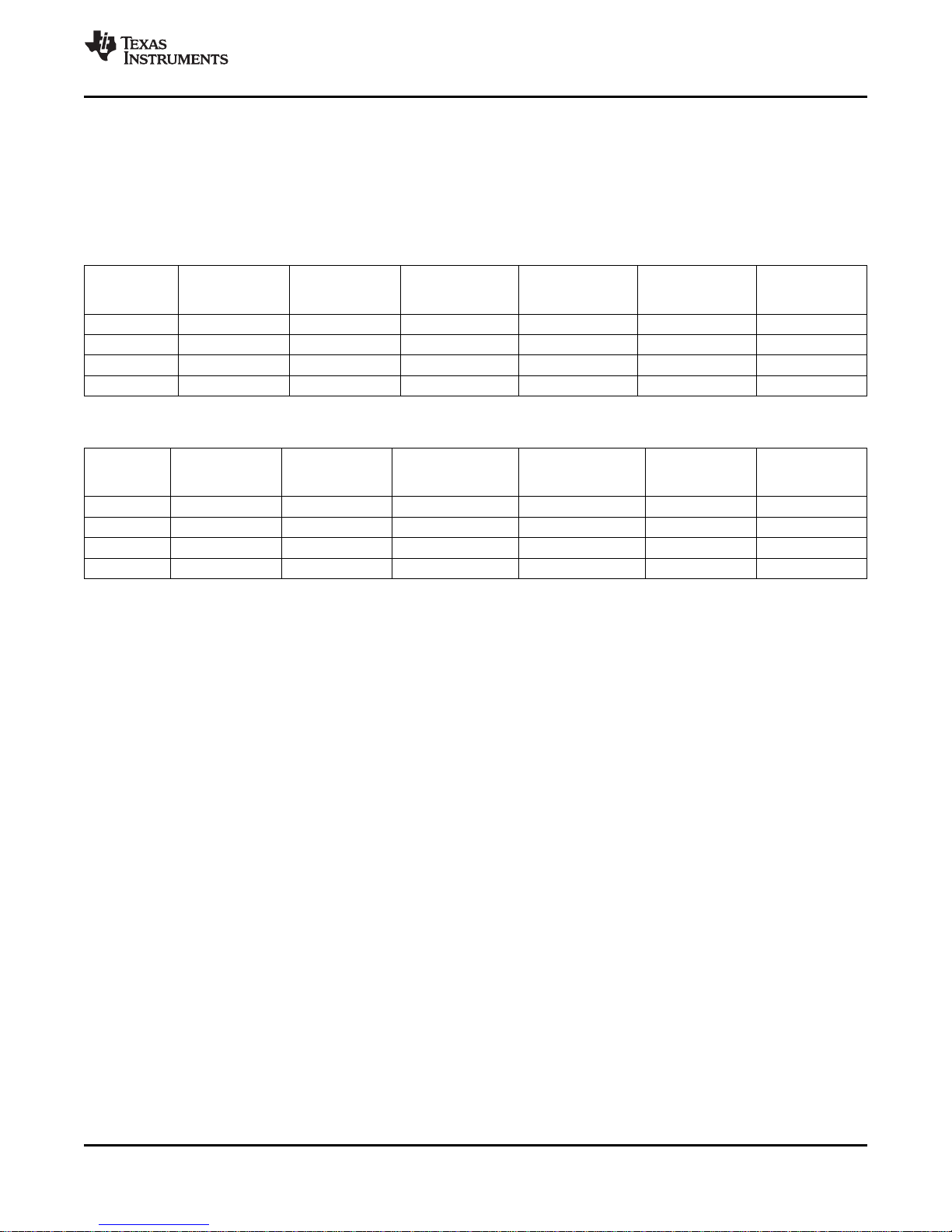

2.7.2 RGMII Mode (Reduced Gigabit Media Independent Interface)

Table 2-5. RGMII – Lane To Functional Pin Mapping

DATA TX_EN/TX_ER TRANSMIT RX_DV/RX_ER TRANSMIT RECEIVE

CHANNEL CONTROL BIT DATA NIBBLE CONTROL BIT CLOCK CLOCK

NUMBER (INPUT) (INPUT) (OUTPUT) (INPUT) (OUTPUT)

Channel 0 TXD_[4] TXD_[3:0] RXD_[4] RXD_[3:0] TXCLK_[0] RXCLK_[0]

Channel 1 TXD_[12] TXD_[11:8] RXD_[12] RXD_[11:8] TXCLK_[1] RXCLK_[1]

Channel 2 TXD_[20] TXD_[19:16] RXD_[20] RXD_[19:16] TXCLK_[2] RXCLK_[2]

Channel 3 TXD_[28] TXD_[27:24] RXD_[28] RXD_[27:24] TXCLK_[3] RXCLK_[3]

RECEIVE

CONTROL

NIBBLE

(OUTPUT)

www.ti.com

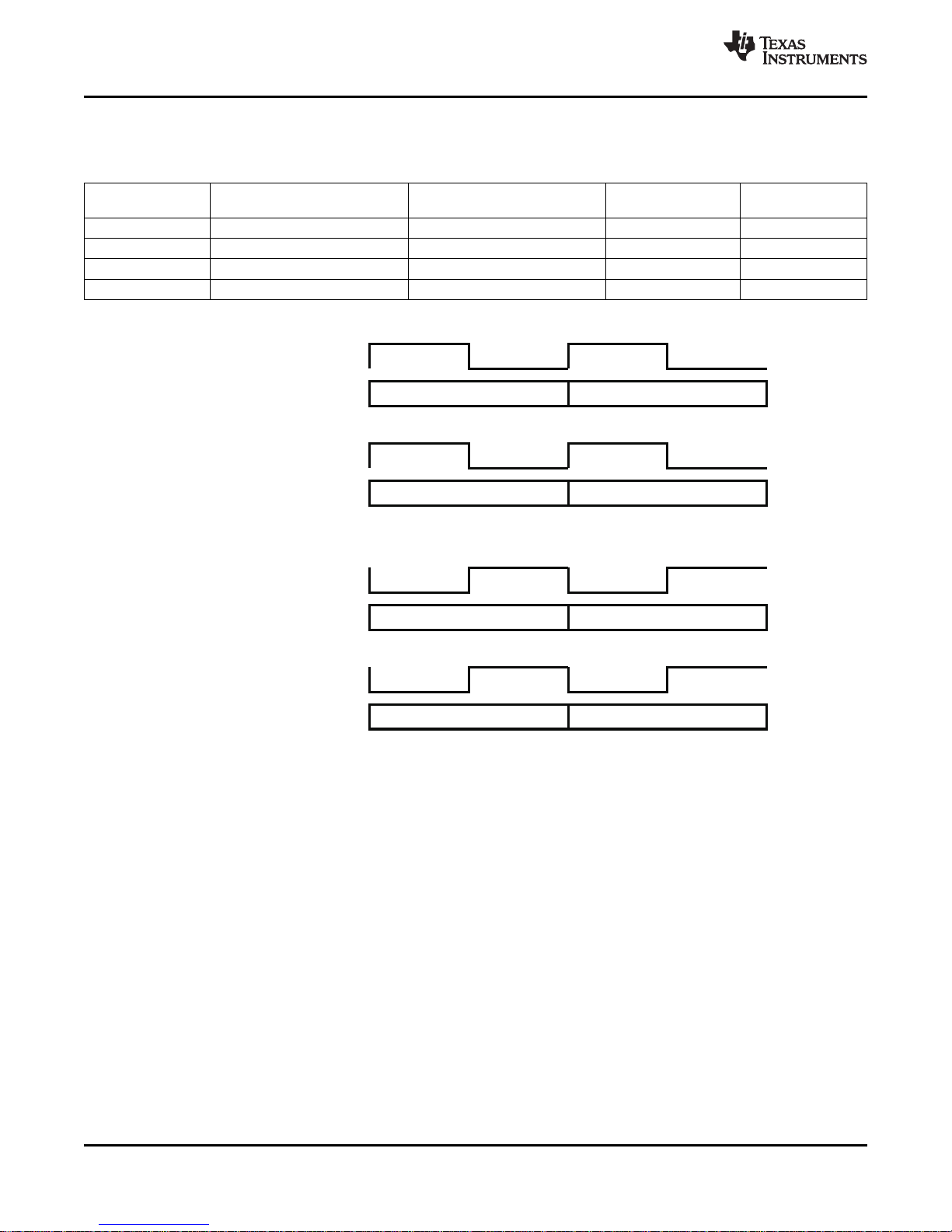

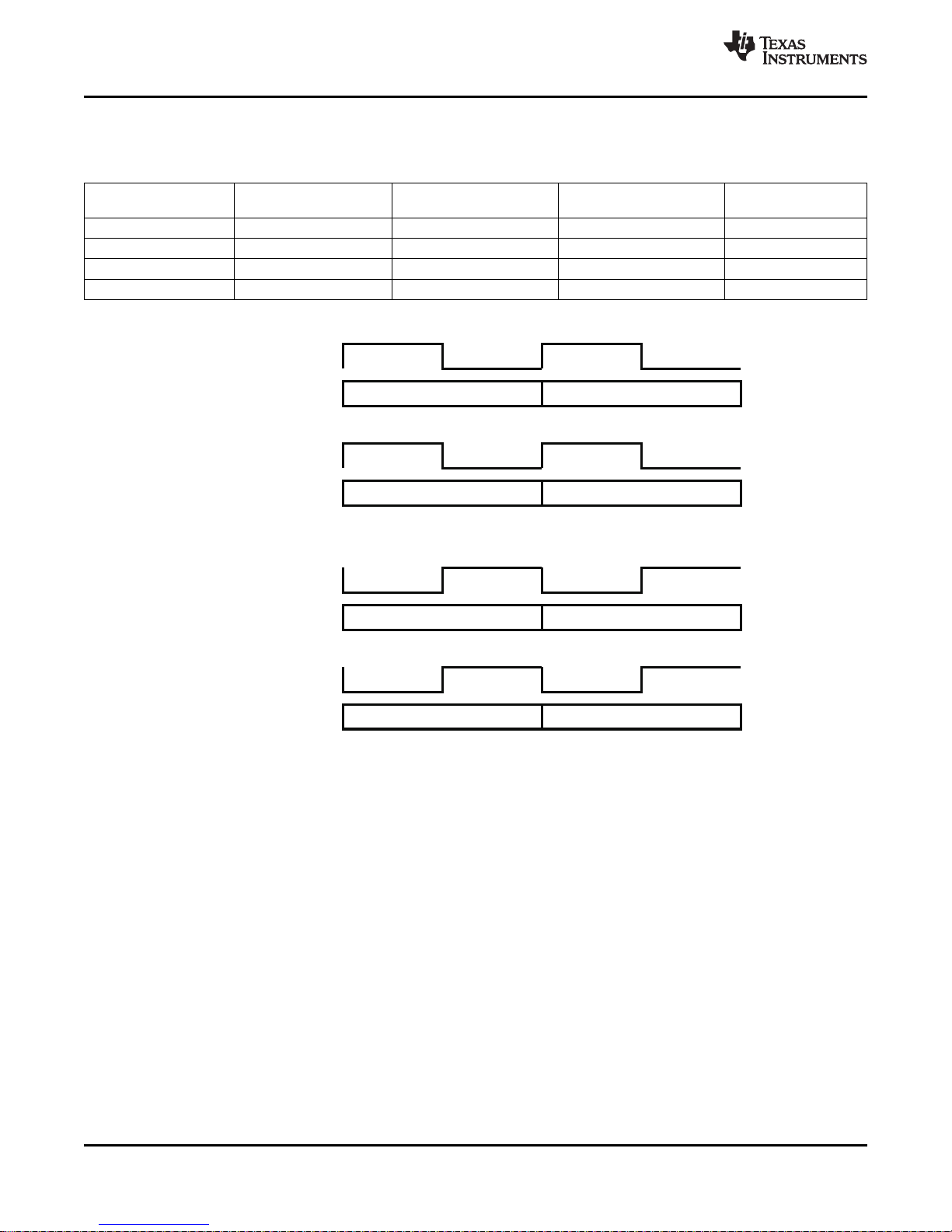

Figure 2-8. RGMII – Individual Channel Byte Ordering – Channel 0 Example

22 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 23

TXCLK_[0]

Data0[4:0] Data0[9:5]

TXD_[4:0]

RXCLK_[0]

Data0[4:0] Data0[9:5]

RXD_[4:0]

DDRSourceCenteredTiming

(NibbleOrder=1Default)

TXCLK_[0]

TXD_[4:0]

RXCLK_[0]

RXD_[4:0]

DDRSource AlignedTiming

(NibbleOrder=1Default)

Data0[4:0] Data0[9:5]

Data0[4:0] Data0[9:5]

TXCLK_[0]

Data0[4:0]Data0[9:5]

TXD_[4:0]

RXCLK_[0]

Data0[4:0]Data0[9:5]

RXD_[4:0]

DDRSourceCenteredTiming

(NibbleOrder=0)

TXCLK_[0]

TXD_[4:0]

RXCLK_[0]

RXD_[4:0]

DDRSource AlignedTiming

(NibbleOrder=0)

Data0[4:0]Data0[9:5]

Data0[4:0]Data0[9:5]

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2.7.3 RTBI Mode (Reduced Ten Bit Interface)

Table 2-6. RTBI – Lane To Functional Pin Mapping

DATA CHANNEL TRANSMIT DATA 5 BITS RECEIVE DATA 5 BITS TRANSMIT CLOCK RECEIVE CLOCK

NUMBER (INPUT) (OUTPUT) (INPUT) (OUTPUT)

Channel 0 TXD_[4:0] RXD_[4:0] TXCLK_[0] RXCLK_[0]

Channel 1 TXD_[12:8] RXD_[12:8] TXCLK_[1] RXCLK_[1]

Channel 2 TXD_[20:16] RXD_[20:16] TXCLK_[2] RXCLK_[2]

Channel 3 TXD_[28:24] RXD_[28:24] TXCLK_[3] RXCLK_[3]

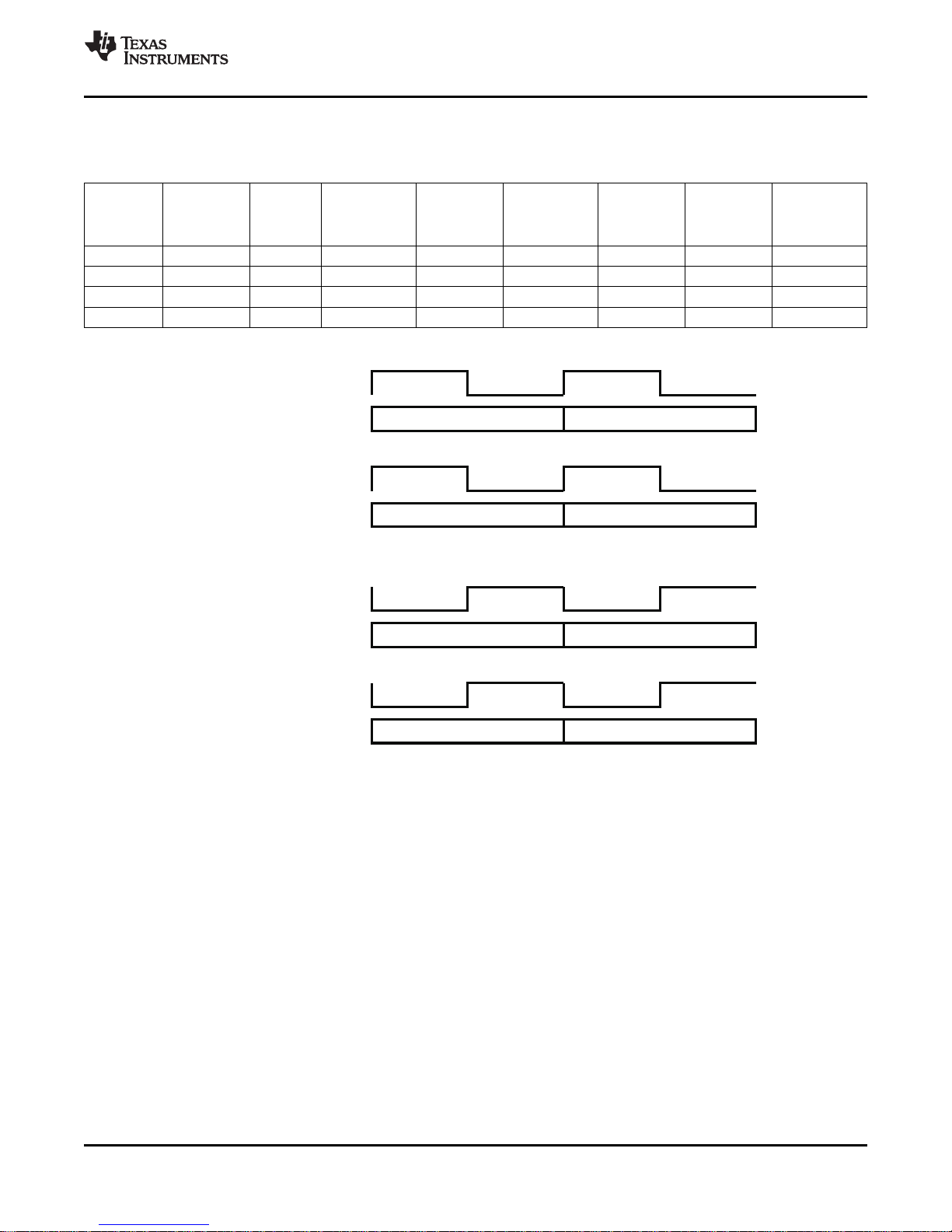

Figure 2-9. RTBI – Individual Channel Byte Ordering – Channel 0 Example

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 23

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 24

TXCLK_[0]

TXC_[4],TXC_[0],TXD_[7:0]

RXCLK_[0]

RXC_[4],RXC_[0],RXD_[7:0]

SDRRisingEdge AlignedTiming

TXCLK_[0]

TXC_[4],TXC_[0],TXD_[7:0]

RXCLK_[0]

RXC_[4],RXC_[0],RXD_[7:0]

SDRFallingEdge AlignedTiming

Data0[9:0] Data1[9:0]

Data0[9:0] Data1[9:0]

Data0[9:0] Data1[9:0]

Data0[9:0] Data1[9:0]

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

www.ti.com

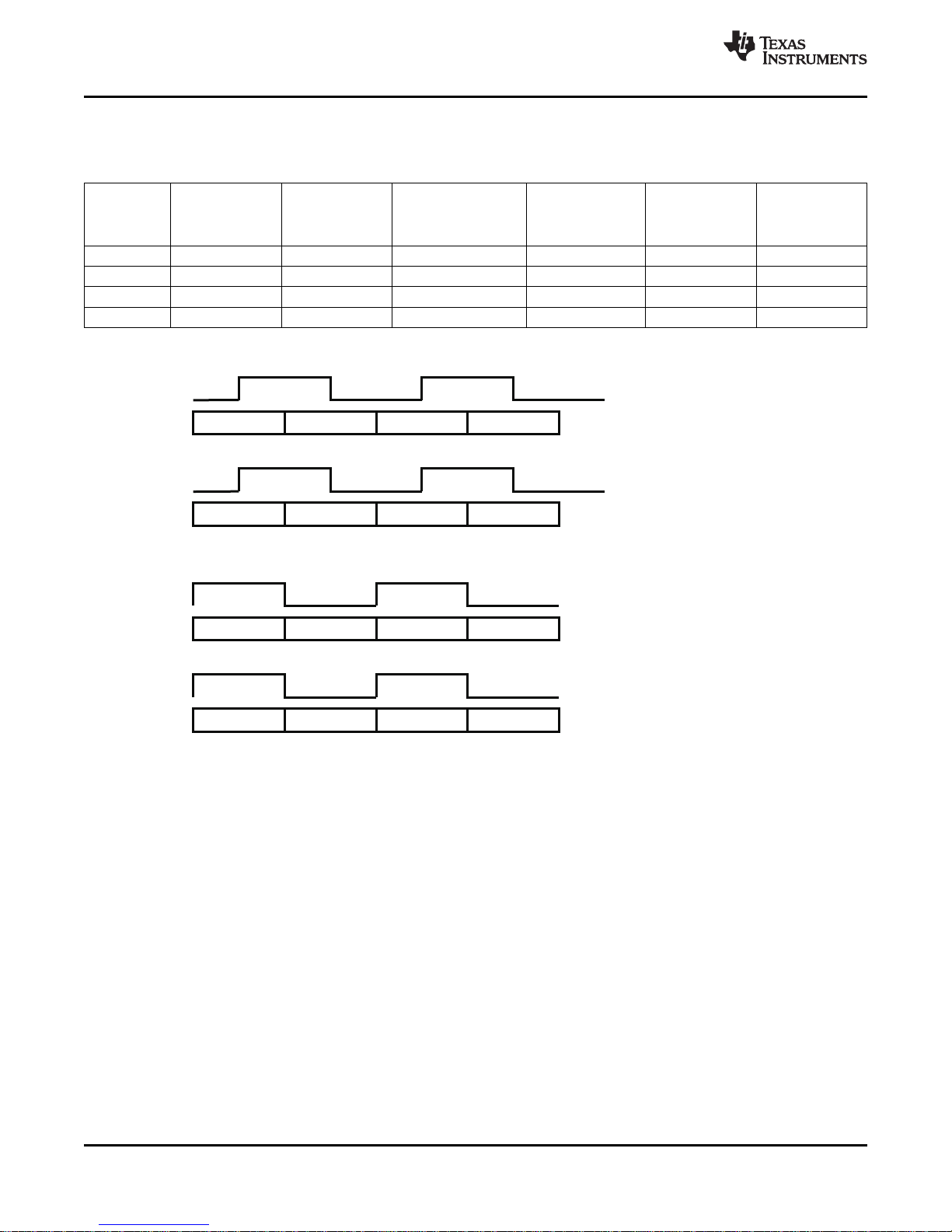

2.7.4 TBI Mode (Ten Bit Interface)

Table 2-7. TBI – Lane To Functional Pin Mapping

DATA CHANNEL TRANSMIT DATA 10 BITS RECEIVE DATA 10 BITS TRANSMIT CLOCK RECEIVE CLOCK

NUMBER (INPUT) (OUTPUT) (INPUT) (OUTPUT)

Channel 0 {TXC_[4], TXC_[0],TXD_[7:0]} {RXC_[4], RXC_[0],RXD_[7:0]} TXCLK_[0] RXCLK_ [0]

Channel 1 {TXC_[5],TXC_[1],TXD_[15:8]} {RXC_[5], RXC_[1],RXD_[15:8]} TXCLK_[1] RXCLK_ [1]

Channel 2 {TXC_[6],TXC_[2],TXD_[23:16]} {RXC_[6],RXC_[2],RXD_[23:16]} TXCLK_[2] RXCLK_ [2]

Channel 3 {TXC_[7],TXC_[3],TXD_[31:24]} {RXC_[7],RXC_[3],RXD_[31:24]} TXCLK_[3] RXCLK_ [3]

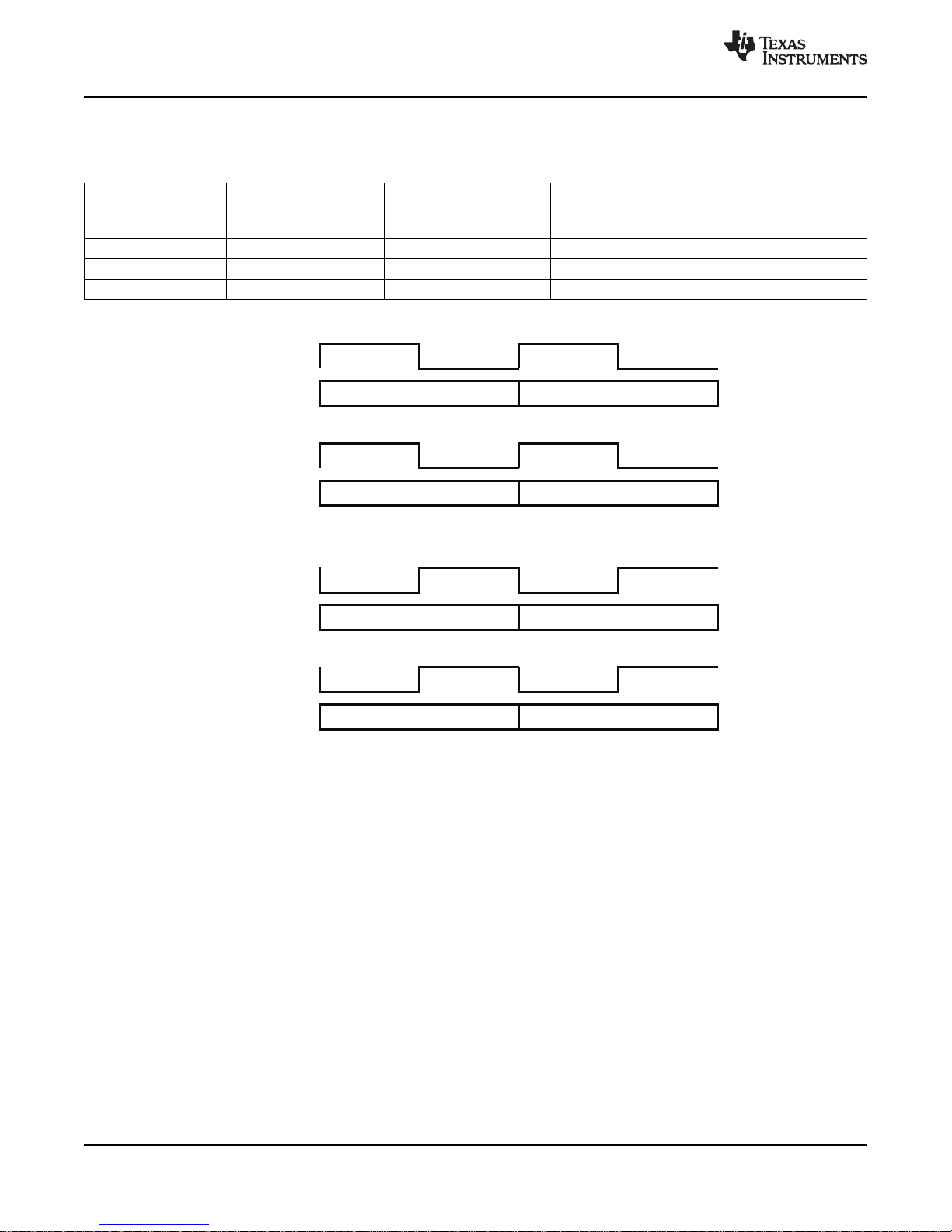

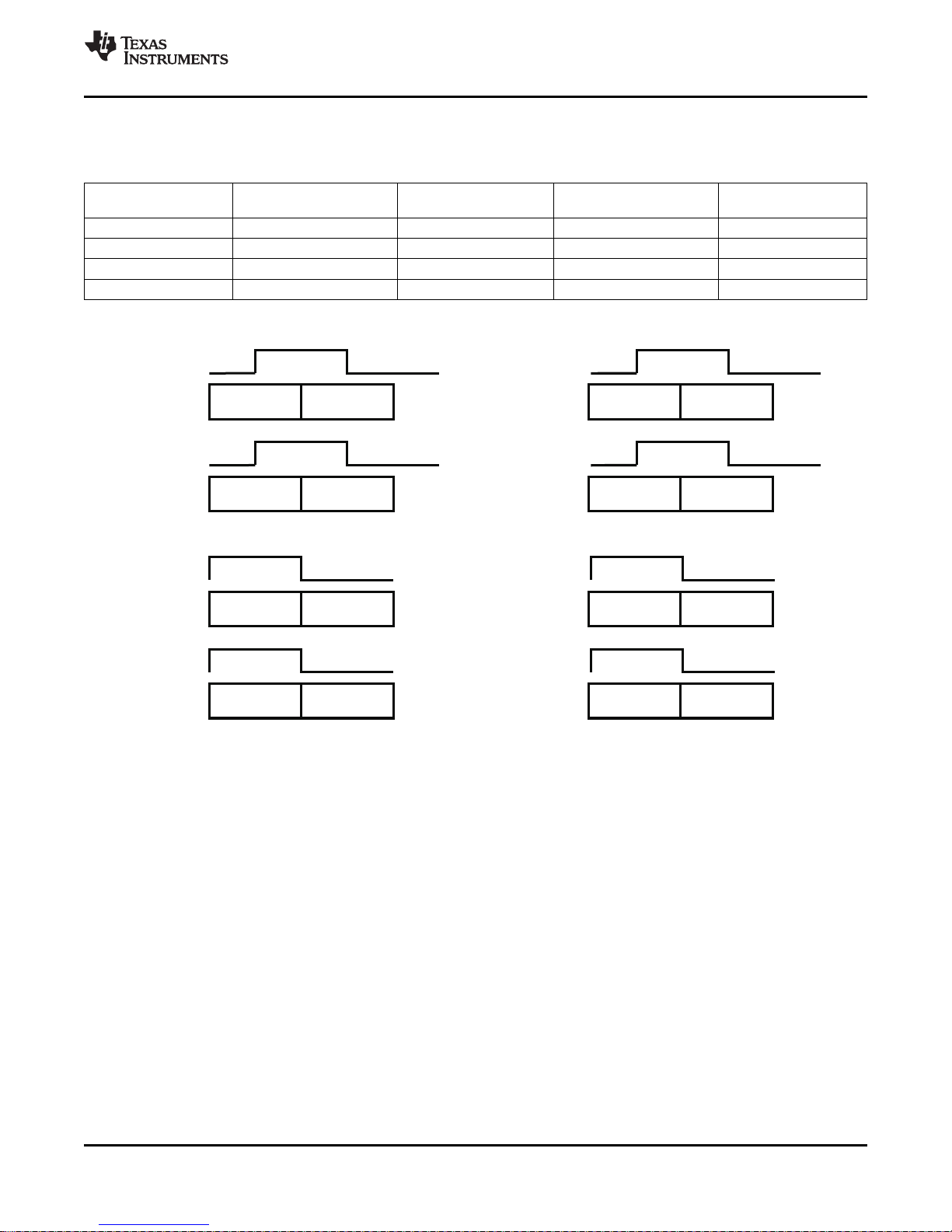

Figure 2-10. TBI – Individual Channel Byte Ordering – Channel 0 Example

24 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 25

TXCLK_[0]

TXC_[0],TXC_[4],TXD_[7:0]

RXCLK_[0]

RXC_[0],RXC_[4],RXD_[7:0]

TXCLK_[0]

TXC_[0],TXC_[4],TXD_[7:0]

RXCLK_[0]

RXC_[0],RXC_[4],RXD_[7:0]

SDRRisingEdge AlignedTiming

SDRFallingEdge AlignedTiming

{TX_EN,TX_ER,Data0[7:0]} {TX_EN,TX_ER,Data1[7:0]}

{RX_DV,RX_ER,Data0[7:0]} {RX_DV,RX_ER,Data1[7:0]}

{TX_EN,TX_ER,Data0[7:0]} {TX_EN,TX_ER,Data1[7:0]}

{RX_DV,RX_ER,Data0[7:0]} {RX_DV,RX_ER,Data1[7:0]}

TLK3134

www.ti.com

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2.7.5 GMII Mode (Gigabit Media Independent Interface)

Table 2-8. GMII – Lane To Functional Pin Mapping

DATA TRANSMIT RX_ER RECEIVE TRANSMIT RECEIVE

CHANNEL DATA BYTE CONTROL BIT DATA BYTE CLOCK CLOCK

NUMBER (INPUT) (OUTPUT) (OUTPUT) (INPUT) (OUTPUT)

Channel 0 TXC_[0] TXC_[4] TXD_[7:0] RXC_[0] RXC_[4] RXD_[7:0] TXCLK_[0] RXCLK_[0]

Channel 1 TXC_[1] TXC_[5] TXD_[15:8] RXC_[1] RXC_[5] RXD_[15:8] TXCLK_[1] RXCLK_[1]

Channel 2 TXC_[2] TXC_[6] TXD_[23:16] RXC_[2] RXC_[6] RXD_[23:16] TXCLK_[2] RXCLK_[2]

Channel 3 TXC_[3] TXC_[7] TXD_[31:24] RXC_[3] RXC_[7] RXD_[31:24] TXCLK_[3] RXCLK_[3]

TX_EN TX_ER RX_DV

CONTROL CONTROL CONTROL

BIT BIT BIT

(INPUT) (INPUT) (OUTPUT)

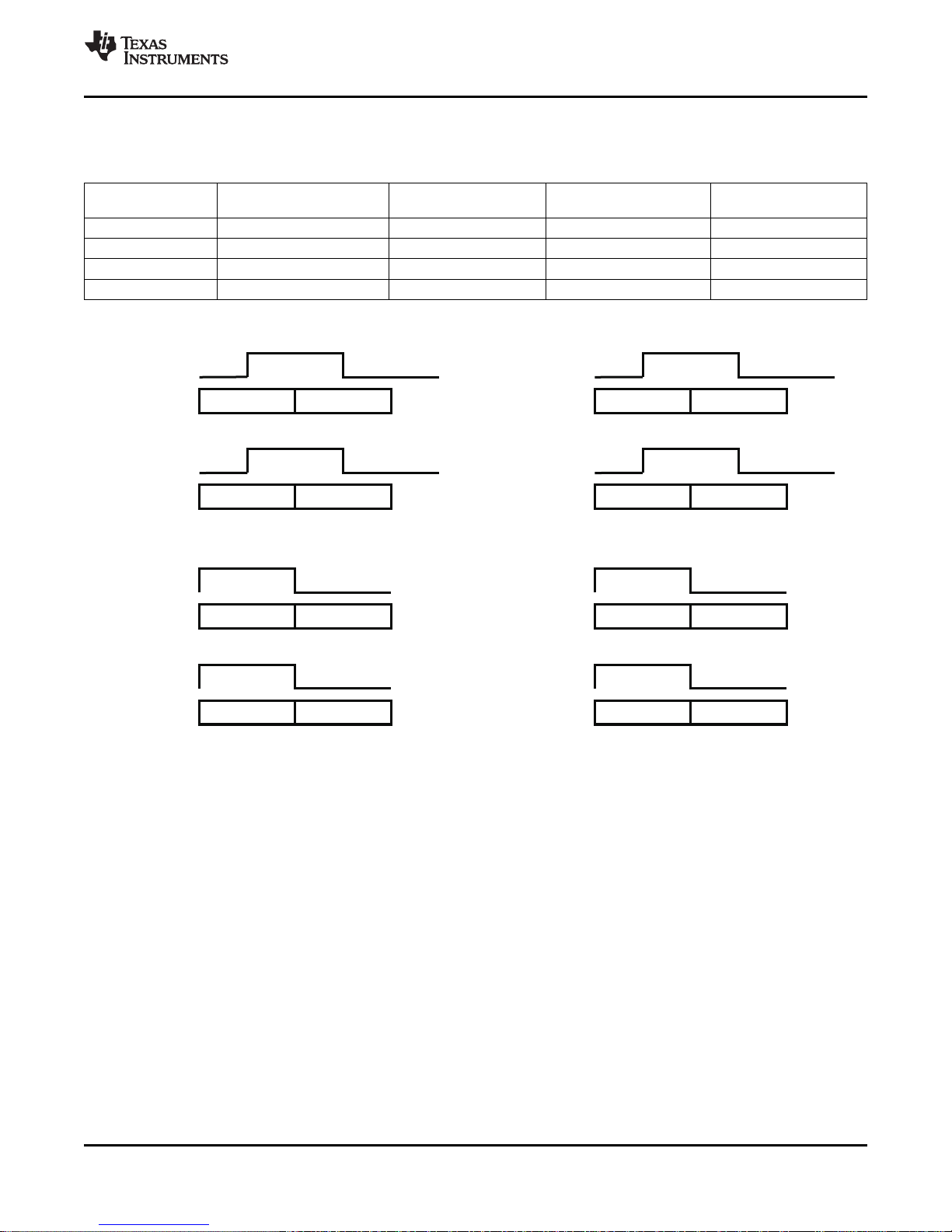

Figure 2-11. GMII – Individual Channel Byte Ordering – Channel 0 Example

Copyright © 2007–2009, Texas Instruments Incorporated Detailed Description 25

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 26

TXCLK_[0]

Data0[7:0]

TXD_[7:0]

RXCLK_[0]

RXD_[7:0]

SDRRisingEdge AlignedTiming

TXCLK_[0]

TXD_[7:0]

RXCLK_[0]

RXD_[7:0]

SDRFallingEdge AlignedTiming

Data1[7:0]

Data0[7:0] Data1[7:0]

Data0[7:0] Data1[7:0]

Data0[7:0] Data1[7:0]

TLK3134

SLLS838F–MAY 2007–REVISED DECEMBER 2009

2.7.6 EBI Mode (Eight Bit Interface)

Table 2-9. EBI – Lane To Functional Pin Mapping

DATA CHANNEL TRANSMIT DATA 8 BITS RECEIVE DATA 8 BITS TRANSMIT CLOCK RECEIVE CLOCK

NUMBER (INPUT) (OUTPUT) (INPUT) (OUTPUT)

Channel 0 TXD_[7:0] RXD_[7:0] TXCLK_[0] RXCLK_[0]

Channel 1 TXD_[15:8] RXD_[15:8] TXCLK_[1] RXCLK_[1]

Channel 2 TXD_[23:16] RXD_[23:16] TXCLK_[2] RXCLK_[2]

Channel 3 TXD_[31:24] RXD_[31:24] TXCLK_[3] RXCLK_[3]

www.ti.com

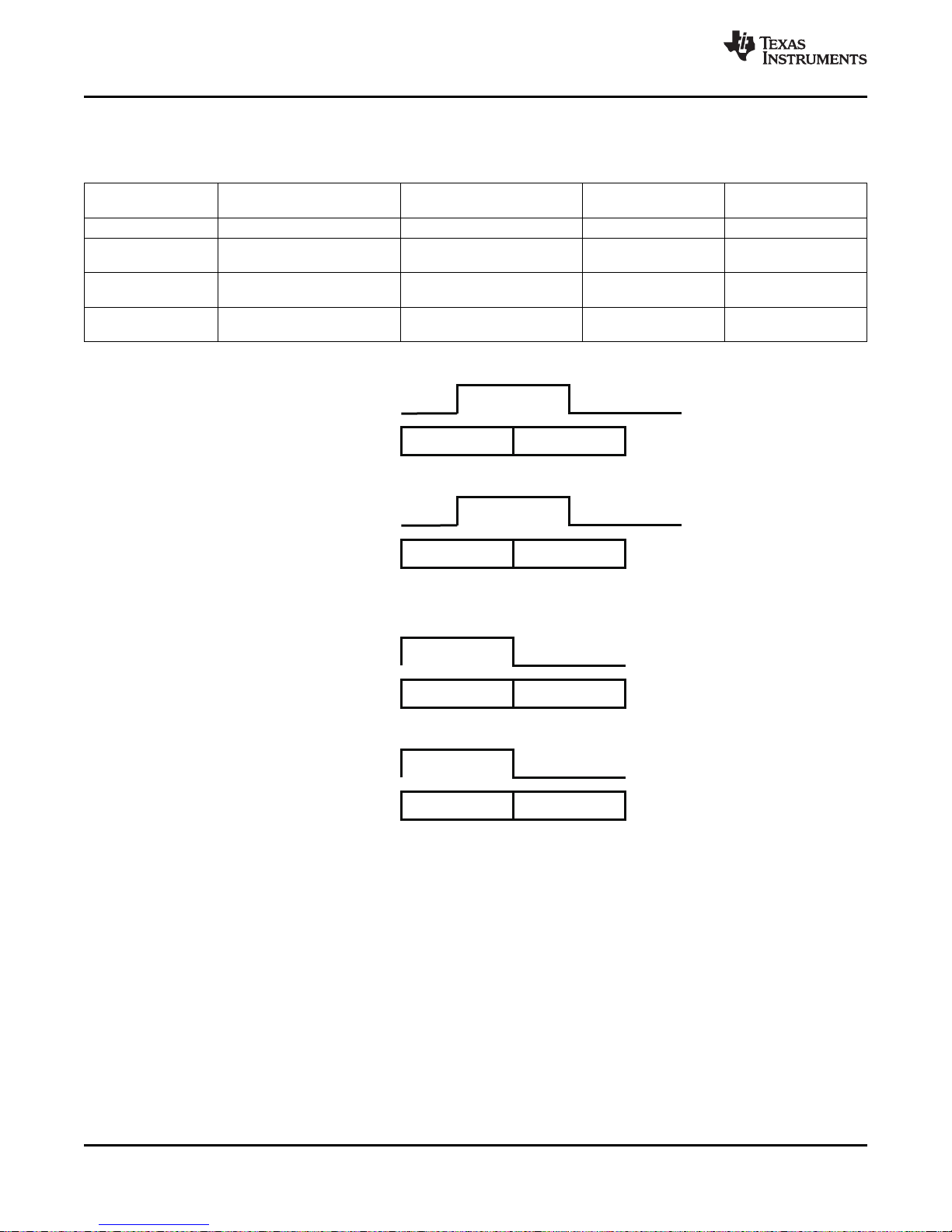

Figure 2-12. EBI – Individual Channel Byte Ordering – Channel 0 Example

26 Detailed Description Copyright © 2007–2009, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TLK3134

Page 27

TXCLK_[0]

Data0[3:0] Data0[7:4]

TXD_[3:0]

RXCLK_[0]

Data0[3:0] Data0[7:4]

RXD_[3:0]

DDRSourceCenteredTiming

(NibbleOrder=1Default)

TXCLK_[0]

TXD_[3:0]

RXCLK_[0]

RXD_[3:0]

DDRSource AlignedTiming

(NibbleOrder=1Default)

Data0[3:0] Data0[7:4]

Data0[3:0] Data0[7:4]

TXCLK_[0]

TXD_[3:0]

RXCLK_[0]

RXD_[3:0]

DDRSourceCenteredTiming

(NibbleOrder=0)

TXCLK_[0]

TXD_[3:0]

RXCLK_[0]

RXD_[3:0]

DDRSource AlignedTiming

(NibbleOrder=0)

Data0[3:0]Data0[7:4]

Data0[3:0]Data0[7:4]

Data0[3:0]Data0[7:4]

Data0[3:0]Data0[7:4]

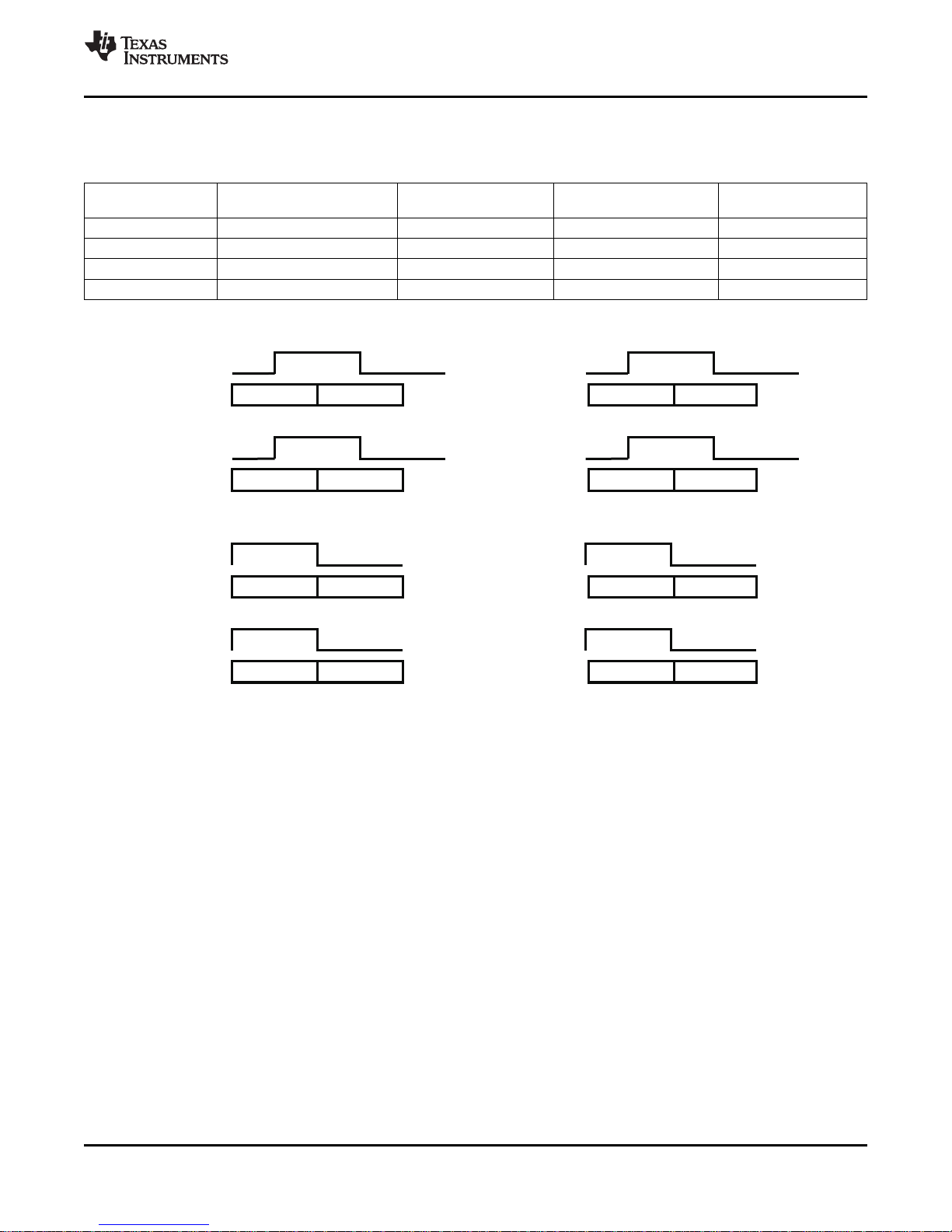

TLK3134

www.ti.com