TLC320AD57C

Data Manual

Sigma-Delta Stereo Analog-to-Digital Converter

SLAS086A

January 1995

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1995, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Functional Block Diagram 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Terminal Assignments 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Terminal Functions 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Detailed Description 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Power-Down and Reset Functions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Power Down 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Reset Function 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Differential Input 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Sigma-Delta Modulator 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Decimation Filter 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 High-Pass Filter 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Master-Clock Circuit 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 T est 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Serial Interface 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8.1 Master Mode 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8.2 Slave Mode 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Specifications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range 3–1. . . . .

3.2 Recommended Operating Conditions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Electrical Characteristics 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Digital Interface, T

3.3.2 Analog Interface 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Channel Characteristics, T

f

= 48 kHz 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Switching Characteristics 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

s

= 25°C, AVDD = DVDD = 5 V 3–2. . . . . . . . . . . . . . . . . . . .

A

= 25°C, AVDD = DVDD = 5 V,

A

4 Parameter Measurement Information 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

List of Illustrations

Figure Title Page

2–1 Power-Down Timing Relationships 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Differential Analog Input Configuration 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Serial Master Transfer Modes 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Serial Slave Transfer Modes 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 SCLK to Fsync and DOUT – Master Mode 3 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 SCLK to Fsync, DOUT and LRClk – Master Modes 4 and 6 4–1. . . . . . . . . . . . . . . . . . . .

4–3 SCLK to Fsync, DOUT, and LRClk – Master Mode 5 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 SCLK to Fsync, DOUT, and LRClk – Master Mode 7 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 SCLK to LRClk and DOUT – Slave Mode 0, Fsync High 4–2. . . . . . . . . . . . . . . . . . . . . . .

4–6 SCLK to Fsync, LRClk, and DOUT – Slave Mode 2, Fsync Controlled 4–2. . . . . . . . . . .

List of Tables

Table Title Page

2–1 Master-Clock to Sample-Rate Comparison 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

1 Introduction

The TLC320AD57C provides high-resolution signal conversion from analog to digital using oversampling

sigma-delta technology. This device consists of two synchronous conversion paths. Also included is a

decimation filter after the modulator as shown in the functional block diagram. Other functions provide

analog filtering and on-chip timing and control.

A functional block diagram of the TLC320AD57C is included in section 1.2. Each block is described in the

Detailed Description section.

1.1 Features

• Single 5-V Power Supply

• Sample Rates (f

• 18-Bit Resolution

• Signal-to-Noise (EIAJ) of 97 dB

• Dynamic Range of 95 dB

• Total Signal-to-Noise+Distortion of 91 dB

• Internal Reference Voltage (V

• Serial Port Interface

• Differential Architecture

• Power Dissipation of 200 mW. Power-Down Mode for Low-Power Applications

• One Micron Advanced LinEPIC1Z Process

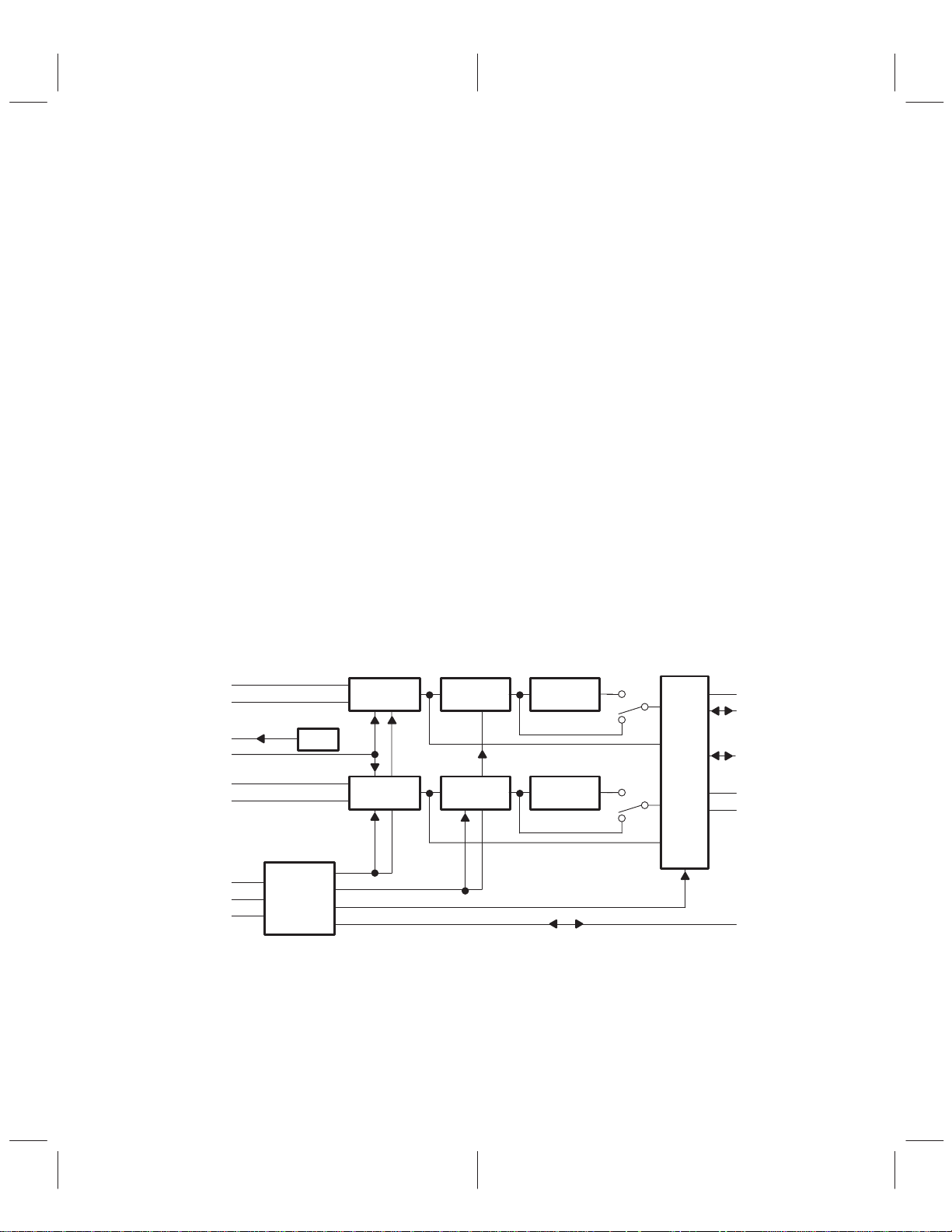

1.2 Functional Block Diagram

) up to 48 kHz

s

ref

)

INLP

INLM

REFO

REFI

INRP

INRM

MCLK

CMODE

MODE0–MODE2

Control

VREF

Sigma-Delta

Modulator

Sigma-Delta

Modulator

LinEPIC1Z is a trademark of Texas Instruments Incorporated.

Decimation

Filter

Decimation

Filter

High-Pass

Filter

High-Pass

Filter

I

S

n

e

t

r

e

i

r

a

f

l

a

c

e

DOUT

Fsync

LRClk

OSFR

OSFL

SCLK

1–1

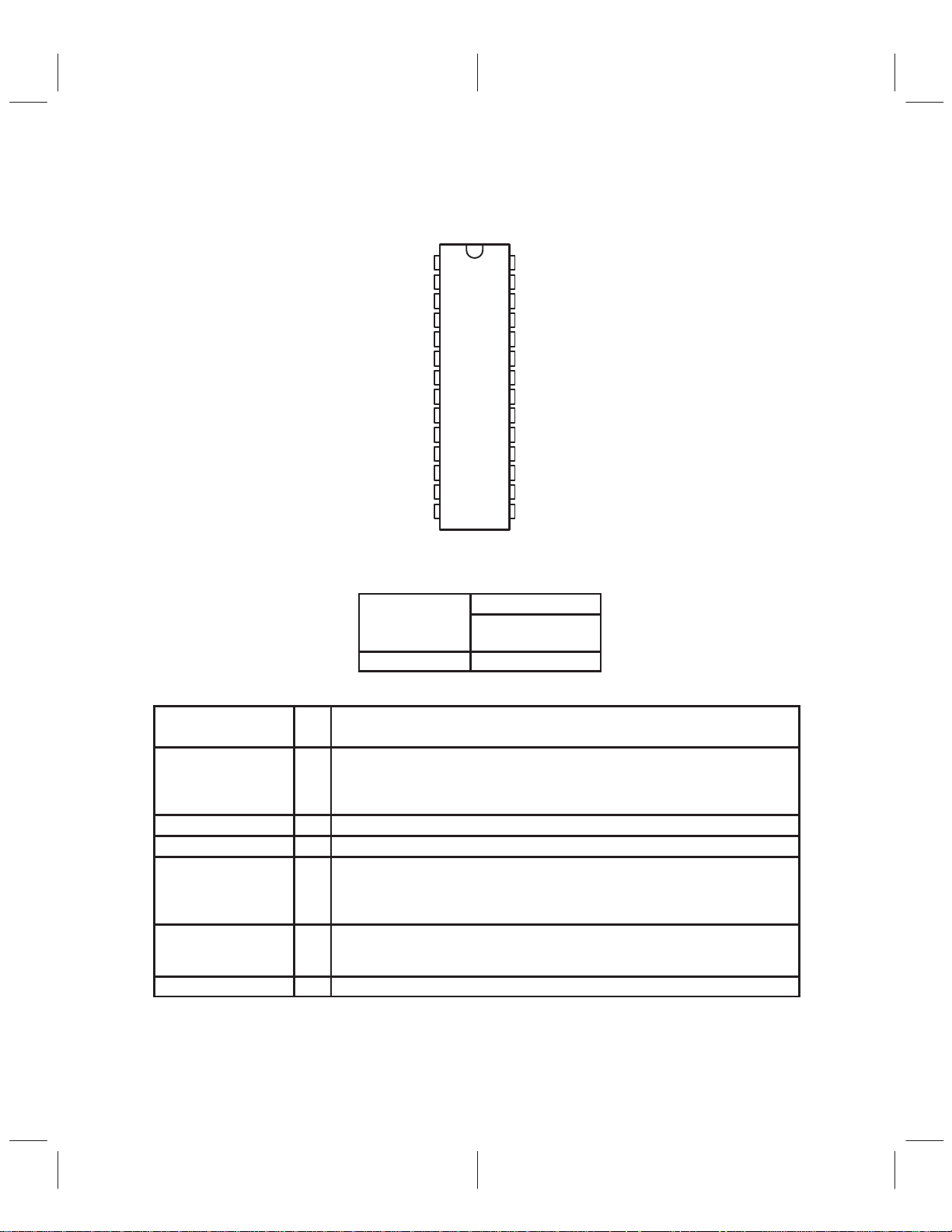

1.3 Terminal Assignments

I/O

DESCRIPTION

DW PACKAGE

(TOP VIEW)

INLP

INLM

REFI

AV

AV

AnaPD

HPByp

MODE2

OSFL

DigPD

TEST

CMODE

MODE0

LRClk

NC – No internal connection

DD

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

INRP

INRM

REFO

LGND

Vlogic

NC

MODE1

OSFR

MCLK

DV

SS

DV

DD

Fsync

DOUT

SCLK

1.4 Ordering Information

PACKAGE

T

A

0°C to 70°C TLC320AD57CDW

SMALL OUTLINE

(DW)

1.5 Terminal Functions

TERMINAL

NAME NO.

AnaPD 6 I Analog power-down mode. The analog power-down mode disables the analog

AV

DD

AV

SS

CMODE 12 I Clock mode. CMODE selects between two methods of determining the master clock

DOUT 16 O Data output. DOUT transmits the sigma-delta audio analog-to-digital converter (ADC)

DV

DD

4 I Analog supply voltage

5 I Analog ground

18 I Digital supply voltage

modulators. The single-bit modulator outputs become invalid, which renders the

outputs of the digital filters invalid. When AnaPD is pulled low, normal operation of the

device resumes.

frequency. When CMODE is high, the master clock input is 384× the conversion

frequency. When CMODE is low, the master clock input is 256× the conversion

frequency.

output data to a digital signal processor (DSP) serial port or other compatible serial

interface and is synchronized to SCLK. DOUT is low when DigPD is high.

1–2

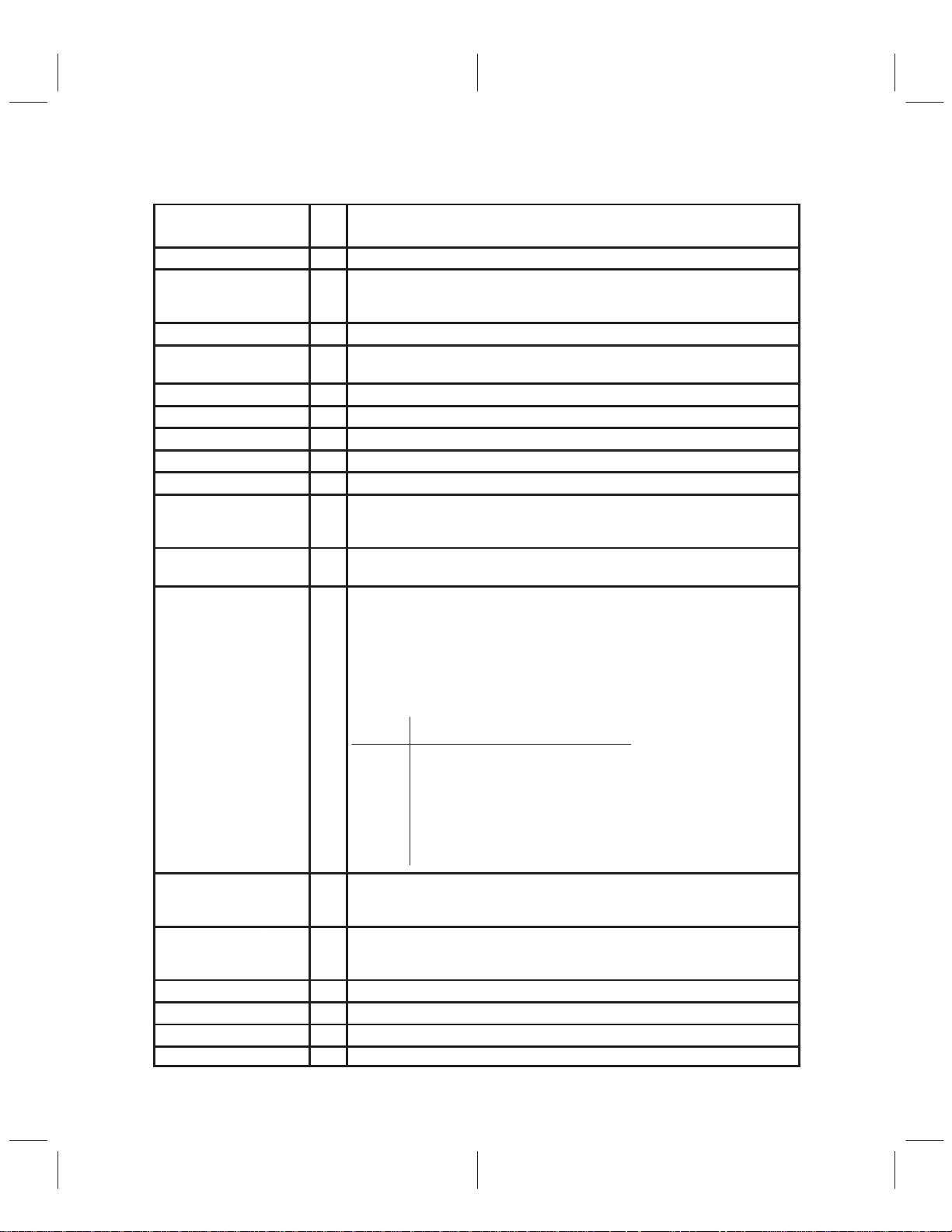

1.5 Terminal Functions (Continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

DV

SS

DigPD 10 I Digital power-down mode. The digital power-down mode shuts down the digital

Fsync 17 I/O Frame synchronization. Fsync designates valid data from the ADC.

HPByp 7 I High-pass filter bypass. When HPByp is high, the high-pass filter is bypassed. This

INLM 2 I Inverting input to left analog input amplifier

INLP 1 I Noninverting input to left analog input amplifier

INRM 27 I Inverting input to right analog input amplifier

INRP 28 I Noninverting input to right analog input amplifier

LGND 25 I Logic-power-supply ground for analog modulator

LRClk 14 I/O Left/right clock. LRClk signifies whether the serial data is associated with the left

MCLK 20 I Master clock. MCLK derives all of the key logic signals of the sigma-delta audio

MODE0–MODE2 8, 13,22I Serial modes. MODE0–MODE2 configure this device for many different modes of

OSFL, OSFR 9, 21 O Over scale flag left/right. If the left/right channel analog input exceeds the full scale

SCLK 15 I/O Shift clock. If SCLK is confirgured as an input, SCLK clocks serial data out of the

TEST 11 I Test mode. TEST should be low for normal operation.

REFI 3 I Input voltage for modulator reference (normally connected to REFO, terminal 26).

REFO 26 I Internal voltage reference

Vlogic 24 I Logic power supply (5 V) for analog modulator

19 I Digital ground

filters and clock generators. All digital outputs are brought to unasserted levels.

When DigPD is pulled low, normal operation of the device resumes.

allows dc analog signal conversion.

channel ADC (when high) or the right channel ADC (when low). LRClk is low when

DigPD is high.

ADC. The nominal input frequency range is 18.432 MHz to 256 kHz.

operation. The different configurations are:

Master versus slave

16 bit versus 18 bit

MSB first versus LSB first

Slave: Fsync controlled versus Fsync high

Each of these modes is described in the Serial Interface section with timing

diagrams.

MODE MASTER/ MSB/LSB

0 1 2 SLAVE BITS FIRST

0 0 0 slave up to 18 MSB

0 0 1 slave 18 LSB

0 1 0 slave up to 18 MSB

0 1 1 master 16 MSB

1 0 0 master 18 MSB

1 0 1 master 18 LSB

1 1 0 master 16 MSB

1 1 1 master 16 LSB

input range for two consecutive conversions, OSFL and OSFR are set high for 4096

LRClk periods. OSFL and OSFR are low when DigPD is high.

sigma-delta audio ADC. If SCLK is configured as an output, SCLK stops clocking

when DigPD is high.

1–3

1–4

2 Detailed Description

The following sections contain a detailed description of the TLC320AD57C.

2.1 Power-Down and Reset Functions

The following sections contain descriptions of the power-down and reset functions of the TLC320AD57C.

2.1.1 Power Down

The power-down state is comprised of a separate digital and analog power down. The power consumption

of each is detailed in Section 3.3, Electrical Characteristics.

The digital power-down mode shuts down the digital filters and clock generators. All digital outputs are set

to an unasserted level. When the digital power-down terminal (DigPD) is pulled low, normal operation of the

device is initiated.

In slave mode, the conversion process must synchronize to an input on the LRClk terminal and the SCLK

terminal. Therefore, the conversion process is not initiated until the first rising edges on both SCLK and

LRClk are detected after DigPD is pulled low. This synchronizes the conversion cycle. All conversions are

performed at a fixed LRClk rate [MCLK /256 (CMODE low) or MCLK/384 (CMODE high)] after the initial

synchronization. After the digital power-down terminal is brought low, the output of the digital filters remains

invalid for 50 LRClk cycles [see Figures 2–1(a) and 2–1(b)].

In master mode, LRClk is an output; therefore, the conversion process initiates based on internal timing.

The first valid data out occurs as shown in Figure 2–1(c).

The analog power-down mode disables the analog modulators. The single-bit modulator outputs become

invalid, which renders the outputs of the digital filters invalid. When the analog power-down terminal is

brought low, the modulators are brought back online; however, the outputs of the digital filters require 50

LRClk cycles for valid results.

2–1

2.1.2 Reset Function

The conversion process is not initiated until the first rising edges on both SCLK and LRClk are detected after

DigPD is pulled low. This synchronizes the conversion cycle. All conversions are performed at a fixed LRClk

rate [MCLK/256 (CMODE low) or MCLK/384 (CMODE high)] after the initial synchronization.

t

su1

Slave Mode Digital Power Down

DigPD

LRClk

DOUT

DigPD

LRClk

DOUT

AnaPD

DOUT

Data Valid

(a)

t

su2

t

d1

Master Mode Digital Power Down

Data Valid

(b)

Analog Power Down

2–2

(c)

Figure 2–1. Power-Down Timing Relationships

2.2 Differential Input

The input is differential in order to provide common-mode noise rejection and increase the input dynamic

range. Figure 2–2 shows the analog input signals used in a differential configuration to achieve

6.4-V peak-to-peak differential swing with a 3.2-V peak-to-peak

4.1 V

swing per input line.

TLC320AD57

2.5 V

0.9 V

4.1 V

2.5 V

0.9 V

INLP, INRP

INLM, INRM

Figure 2–2. Differential Analog Input Configuration

2.3 Sigma-Delta Modulator

The modulator is a fourth order sigma-delta modulator with 64 times oversampling. The ADC provides

high-resolution, low-noise performance from a one-bit converter using oversampling techniques.

2.4 Decimation Filter

The decimation filter used after the sigma-delta modulator reduces the digital data rate to the sampling rate

of LRClk. This is accomplished by decimating with a ratio of 1:64. The output of this filter is a 2s complement

data word of up to 18 bits serially clocked out.

If the input value exceeds the full range of the converter, the output of the decimator is held at the appropriate

extreme until the input returns to within the dynamic range of the device.

2.5 High-Pass Filter

The high-pass filter removes dc from the input. With this filtering, offset calibration is not needed. The

high-pass filter can be circumvented by asserting the HPByp terminal to pass dc signals through the

converter. However, an offset due to the converter can be present when bypassing the high-pass filter.

2.6 Master-Clock Circuit

The master-clock circuit generates and distributes necessary clocks throughout the device. MCLK is the

external master-clock input. CMODE selects the relationship of MCLK to the sample rate, LRClk. When

CMODE is low, the sample rate of the data paths is set to LRClk = MCLK/256. When CMODE is high, the

sample rate is set to LRClk = MCLK/384. With a fixed oversampling ratio of 64× , the effect of changing MCLK

is shown in Table 2–1.

When the device is in master mode, SCLK is derived from MCLK in order to provide clocking of the serial

communications between the sigma-delta audio ADC and a digital signal processor (DSP) or control logic.

This is equivalent to a clock running at 64 × LRClk.

When the device is in slave mode, SCLK is externally derived.

2–3

T able 2–1. Master-Clock to Sample-Rate Comparison

3.0720

48

2.8224

44.1

2.0480

32

0.0640

1

(modes 1, 3, 4, 5)

MCLK

(MHz)

12.2880 Low

18.4320 High

11.2896 Low

16.9344 High

8.1920 Low

12.2880 High

0.2560 Low

0.3840 High

CMODE

SCLK

(MHz)

LRClk

(kHz)

2.7 Test

When the TEST input is high, the test mode is selected, which routes the high speed one-bit modulator result

to the serial port output. When in the test mode, the SCLK output frequency is equal to the data output rate.

LRClk is an input when the test mode is selected. This allows for the selection of the left or right modulator

output to be routed to the serial port (high = left and low = right).

2.8 Serial Interface

Although the serial data is shifted out in two seperate time packets that represent the left and right channels,

the inputs are sampled and converted simultaneously .

The serial interface protocol has master and slave modes each with different read-out modes. The master

mode sources the control signals for conversion synchronization while the slave mode allows an external

controller to provide conversion synchronization signals.

The five master modes are shown in Figures 2–3(a) through 2–3(e) and the three slave modes are shown

in Figures 2–4(a) through 2–4(c). For a 16-bit word, D15 is the most significant bit and D0 is the least

significant bit. Unless otherwise specified, all values are in 2s complement format.

In the master mode, SCLK is generated internally and is sourced as an output. The relationship of SCLK

to LRClk is 64× (modes 1, 3, 4, 5) or 32× (modes 6, 7). In the slave mode, SCLK is an input. SCLK timing

must meet the timing specifications listed in the Recommended Operating Conditions section.

2.8.1 Master Mode

As the master, the TLC320AD57C generates LRClk, Fsync, and SCLK from MCLK. These signals are

provided for synchronizing the serial port of a DSP or other control devices.

Fsync designates valid data from the ADC, and accomplishes this in the master modes by one of two

methods. The first method is to place a single pulse on Fsync prior to valid data. This indicates the starting

point for the data. The second method of frame synchronization is to hold Fsync high during the entire valid

data cycle which provides boundaries for the data.

LRClk is generated internally from MCLK. The frequency of this signal is fixed at the sampling frequency

f

[MCLK/256 (CMODE low) or MCLK/384 (CMODE high)]. During the high period of this signal, the left

s

channel data is serially shifted to the output; during the low period, the right channel data is shifted to the

output. The conversion cycle synchronizes with the rising edge of LRClk.

Five modes are available when the device is configured as a master. Two modes are for 18-bit

communications. These modes differ from each other in that the MSB is transferred first in one mode while

the LSB is transferred first in the second mode [see Figures 2–3(b) and 2–3(c)]. When the LSB is transferred

first, the data is right justified to the LRClk [see Figures 2–3(a) through 2–3(e)]. The three other modes

2–4

available as a master are 16-bit modes. Two of the modes differ as MSB first versus LSB first. These two

modes set SCLK = LRClk × 32. This is one half the frequency used in the other transfer modes [see Figures

2–3(d) and 2–3(e)]. The third 16-bit mode provides the data MSB first with one clock delay after LRClk [see

Figure 2–3(a)].

Mode 011

SCLK

Fsync

DOUT

LRClk

Mode 100

SCLK

Fsync

DOUT

LRClk

Mode 101

SCLK

Fsync

DOUT

LRClk

Mode 110

SCLK

Fsync

DOUT

LRClk

Left

17 16

Left

Left

Left

(a) MASTER MODE (Fsync bound)

15 14

. . .

1 0 15 14

(b) 18-BIT MASTER MODE

. . .

1 0 17 16

(c) 18-BIT MASTER MODE

. . .

01

(d) DSP CONTINUOUS MODE

. . .

14

1015 14

64 SCLKs

64 SCLKs

16 17 0 1

64 SCLKs

32 SCLKs

Right

Right

Right

Right

. . .

10

. . .

. . .

10

. . .

16 17

1015

17

15

Mode 11 1

SCLK

Fsync

DOUT

LRClk

(e) DSP CONTINUOUS MODE

. . .

1

Left

14 1501

32 SCLKs

Figure 2–3. Serial Master Transfer Modes

Right

. . .

14 150

0

2–5

2.8.2 Slave Mode

As a slave, the TLC320AD57C receives LRClk, Fsync, and SCLK as inputs. The conversion cycle

synchronizes to the rising edge of LRClk, and the data synchronizes to the falling edge of SCLK. SCLK must

meet the setup time requirements specified in Section 3.2, Recommended Operating Conditions.

Synchronization of the slave modes is accomplished with the digital power-down control.

In slave mode, Fsync is an input. Three modes are provided as shown in Figures 2–4(a) through 2–4(c).

SCLK and LRClk are externally generated and sourced. The first rising edges of SCLK and LRClk after a

power-down cycle initiate the conversion cycle. Refer to Section 2.8.1, Master Mode for signal functions.

Several modes are available when the TLC320AD57C is configured as a slave. Using the Mode0, Mode1,

and Mode2 terminals, the TLC320AD57C can be set to shift out the MSB first or the LSB first [see Figures

2–4(a) and 2–4(b)]. The number of bits shifted out can be controlled by the number of valid SCLK cycles

provided within the left or right channel period. If only enough clocks are provided to shift out 16 data bits

before LRClk changes state, this is equivalent to a 16-bit mode.

Mode 000 (a) SLAVE MODE (Fsync high)

SCLK

Fsync

DOUT

LRClk

input

input

output

input

17 16

Left

. . .

10

17 16

32–128 SCLKs

Right

. . .

10

Mode 001

SCLK

Fsync

DOUT

LRClk

Mode 010

SCLK

Fsync(1)

DOUT(1)

Fsync(2)

DOUT(2)

LRClk

(b) SLAVE MODE (Fsync high)

. . .

16

17

64 SCLKs

Right

017

0

32–128 SCLKs

Right

Left

Left

01

(c) SLAVE MODE (Fsync controlled)

17

17

. . .

. . .

Figure 2–4. Serial Slave Transfer Modes

01

. . .

0

17 0

. . .

. . .

16

17

2–6

3 Specifications

3.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range

(Unless Otherwise Noted)

Analog supply voltage range, AV

Digital supply voltage range, DV

Digital output voltage range, (externally applied) –0.3 V to DV

Digital input voltage range, MODE0 – MODE2 –0.3 V to DV

Analog input voltage range, INLP, INLM, INRP, INRM –0.3 V to A V

Operating free-air temperature range, T

Storage temperature range, T

Case temperature for 10 seconds, T

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These

are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated

under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

NOTES: 1. Voltage values for maximum ratings are with respect to AVSS.

2. Voltage values for maximum ratings are with respect to DVSS.

†

(see Note 1) –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . .

DD

(see Note 2) –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . .

DD

A

stg

C

) 0.3 V. . . . . . . . . . .

DD

) 0.3 V. . . . . . . . . . . .

DD

) 0.3 V. . . . . .

DD

0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Recommended Operating Conditions

MIN NOM MAX UNIT

Analog supply voltage, A VDD (see Note 3) 4.75 5 5.25 V

Digital supply voltage, DV

Analog logic supply voltage, at Vlogic 4.75 5 5.25 V

Reference voltage, V

Setup time, DigPD↓ to LRClk↑, slave mode, t

Setup time, DigPD↓ to LRClk↑, master mode, t

Setup time, SCLK↑ to LRClk, slave mode, t

Setup time, LRClk to SCLK↑, slave mode, t

Setup time, SCLK↑ to Fsync, slave mode, t

Setup time, Fsync to SCLK↑, slave mode, t

Load resistance at DOUT, R

Operating free-air temperature, T

NOTE 3: Voltages at analog inputs and outputs and A VDD are with respect to the AVSS terminal.

ref

DD

(see Figure 2–1(a)) 30 ns

su1

(see Figure 2–1(b)) 30 ns

su2

(see Figures 4–5 and 4–6) 30 ns

su3

(see Figure 4–5) 30 ns

su4

(see Figure 4–6) 30 ns

su5

(see Figure 4–6) 30 ns

su6

L

A

4.75 5 5.25 V

3.2 V

10 kΩ

0 70 °C

3–1

3.3 Electrical Characteristics

1dB down from

3.3.1 Digital Interface, TA = 25°C, AVDD = DVDD = 5 V

PARAMETER TEST CONDITIONS MIN TYP MAX

V

V

V

V

I

I

C

C

3.3.2 Analog Interface

High-level input voltage 2 4.6 V

IH

Low-level input voltage 0.2 0.8 V

IL

High-level output voltage, DOUT IOH = 2 mA 2.4 4.6 V

OH

Low-level output voltage, DOUT IOL = 2 mA 0.2 0.4 V

OL

High-level input current, any digital input 1 µA

IH

Low-level input current, any digital input 1 µA

IL

Input capacitance 5 pF

i

Output capacitance 5 pF

o

UNIT

3.3.2.1 ADC Modulator, T

= 25°C, AVDD = DVDD = 5 V, fs = 48 kHz, Bandwidth = 24 kHz,

A

HPByp = 1, CMODE = 0, MODE0 – 2 = 101

PARAMETER

Resolution 18 Bits

DYNAMIC PERFORMANCE

Signal to noise (EIAJ)

Dynamic range

Signal to noise + distortion (THD + N)

Total harmonic distortion (THD)

Interchannel isolation 108 dB

DC ACCURACY

Gain error ±0.2 dB

Interchannel gain mismatch ±0.2 dB

Offset error (18-bit resolution) ±5 mV

Offset drift ±0.17 LSB/°C

TEST CONDITIONS

INLP = INRP = 2.5 V dc

INLM = INRM = 2.5 V dc

–

6-V differential input between

INRP (INLP) and INRM (INLM)

MIN TYP MAX

93 97 dB

91 95 dB

91 dB

0.001%

UNIT

3–2

3.3.2.2 Inputs/Supplies, TA = 25°C, AVDD = DVDD = 5 V, fs = 48 kHz, Bandwidth = 24 kHz,

Input voltage

V

Power-supply current

HPByp = 1

PARAMETER TEST CONDITIONS MIN TYP MAX

ANALOG INPUT

p

Input impedance 50 kΩ

POWER SUPPLIES

pp

Power dissipation 230 mW

Differential input 6.4

Single-ended input 3.2

IDD (analog), operating 22 30 mA

IDD (digital), operating 24 32 mA

IDD (analog), power down 100 µA

IDD (digital), power down 40 µA

UNIT

3.3.3 Channel Characteristics, TA = 25°C, AVDD=DVDD = 5 V, fs = 48 kHz, HPByp = 1

PARAMETER TEST CONDITIONS MIN TYP MAX

Passband (–3 dB) HPByp = 0 0.001 24 kHz

Passband ripple 30 Hz – 21.8 kHz ±0.01 dB

Stopband attenuation 26.2 kHz – 3046 kHz 80 dB

Group delay 25/F

s

UNIT

s

3.4 Switching Characteristics

t

d1

t

d(MFSD)

t

d(MDD)

t

d(MIRD)

t

d(SDD1)

t

d(SDD2)

PARAMETER MIN TYP MAX

Delay time, AnaPD↓ to DOUT valid (see Figure 2–1(c)) 30 ns

Delay time, SCLK↓ to Fsync, master mode

(see Figures 4–1, 4–2, 4–3, and 4–4)

Delay time, SCLK↓ to DOUT, master mode

(see Figures 4–1, 4–2, 4–3, and 4–4)

Delay time, SCLK↓ to LRClk, master mode

(see Figures 4–2 and 4–4)

Delay time, LRClk to DOUT, slave mode (see Figure 4–5) 50 ns

Delay time, SCLK↓ to DOUT, slave mode

(see Figures 4–5 and 4–6)

–20 20

0 50

–20 20

50

UNIT

ns

ns

ns

ns

3–3

3–4

4 Parameter Measurement Information

SCLK

t

d(MFSD)

Fsync

t

d(MDD)

DOUT

LRClk

Figure 4–1. SCLK to Fsync and DOUT – Master Mode 3

SCLK

t

d(MFSD)

Fsync

t

d(MDD)

DOUT

t

d(MIRD)

MSB MSB–1

MSB MSB–1

. . .

. . .

LRClk

SCLK

Fsync

DOUT

LRClk

Figure 4–2. SCLK to Fsync, DOUT, and LRClk – Master Modes 4 and 6

t

d(MFSD)

t

d(MDD)

LSB LSB–1

Figure 4–3. SCLK to Fsync, DOUT, and LRClk – Master Mode 5

. . .

4–1

SCLK

Fsync

DOUT

LRClk

t

d(MFSD)

t

d(MDD)

LSB LSB–1

t

d(MIRD)

Figure 4–4. SCLK to Fsync, DOUT, and LRClk – Master Mode 7

. . .

SCLK

LRClk

DOUT

SCLK

Fsync

DOUT

t

su3

t

d(SDD1)

17 16

t

su4

t

d(SDD2)

. . .

Figure 4–5. SCLK to LRClk and DOUT – Slave Mode 0, Fsync High

t

su3

t

su5

17

t

t

d(SDD2)

su6

. . .

1

4–2

LRClk

Figure 4–6. SCLK to Fsync, LRClk, and DOUT – Slave Mode 2, Fsync Controlled

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...