TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

Copyright 1991, Texas Instruments Incorporated

4-1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

• Solid-State Reliability

• Supports Both Color and Monochrome

Applications

• Three Independent Channels Available for

Use With RGB Monitors

• Y Signal Generated From Three

Independent Channels

• Clamp Pulse-Select Option

• White-Clip Function for Y Signal

• Gain Control for R, G, B, and Y

• Noise Suppression During Video-Blanking

Periods

description

The TL1051 is a bipolar monolithic integrated circuit designed for use in preprocessing three channels of TI CCD

image sensors. It receives video inputs from the TI TL1593 three-channel sample-and-hold circuit and outputs

three processed channel signals and a single multiplexed Y (luminance) signal. Processing functions of the

TL1051 include gain, automatic gain control, clamp, white balance, and white clip.

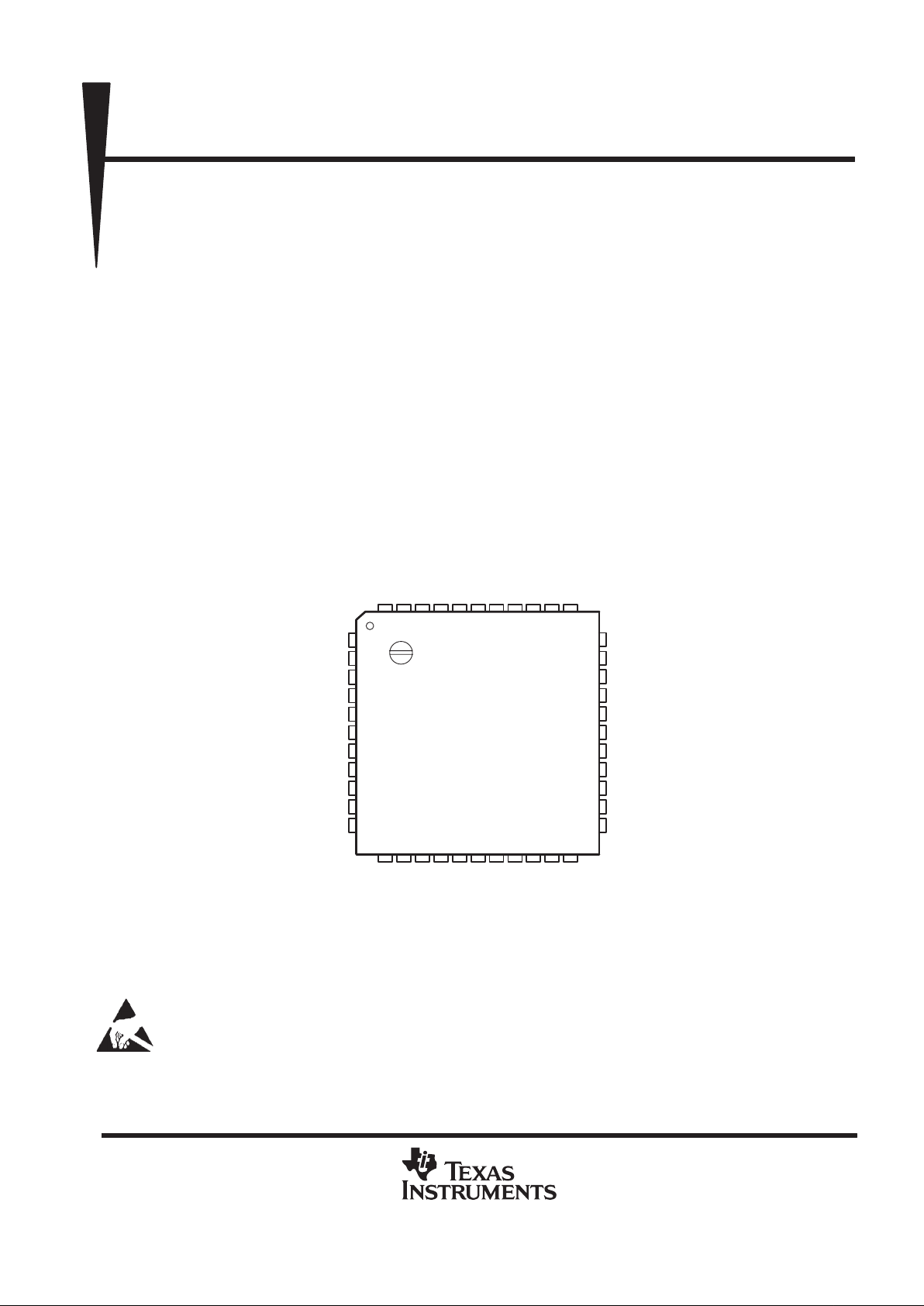

The TL1051 is supplied in a 44-pin surface-mount plastic package and is characterized for operation from –20°C

to 45°C.

AGCOUT

REF2V

AGCCONT

AGCLMT

BOUT

GOUT

ROUT

YOUT

YALC

WCPCONT

YCLAMP

12 13

1

2

3

4

5

6

7

8

9

10

11

NC

WB

CONTB

CONTA

V

CC

BIN

GIN

RIN

CLPLVLB

CLPLVLG

CLPLVLR

14 15 16 17

FR PACKAGE

(TOP VIEW)

GND

ALCREF

AGCSET

AGCDET

43 42 41 40 3944 38

RESET

ALCDRV

ALC–

ALC+

GATE

GATEOUT

GATEIN

HL

YSW

YAGCIN

GND

SWR

SWG

SWB

PCL1

PBL

PCL2

36 35 3437

18 19 20 21 22

YAGC

33

32

31

30

29

28

27

26

25

24

23

NC – No internal connection

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These

circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C,

Method 3015; however, precautions should be taken to avoid application of any voltage higher than maximum-rated voltages to these

high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in

conductive foam. In a circuit, unused inputs should always be connected to an appropriate logic voltage level, preferably either VCC or ground.

Specific guidelines for handling devices of this type are contained in the publication

Guidelines for Handling Electrostatic-Discharge-Sensitive

(ESDS) Devices and Assemblies

available from Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

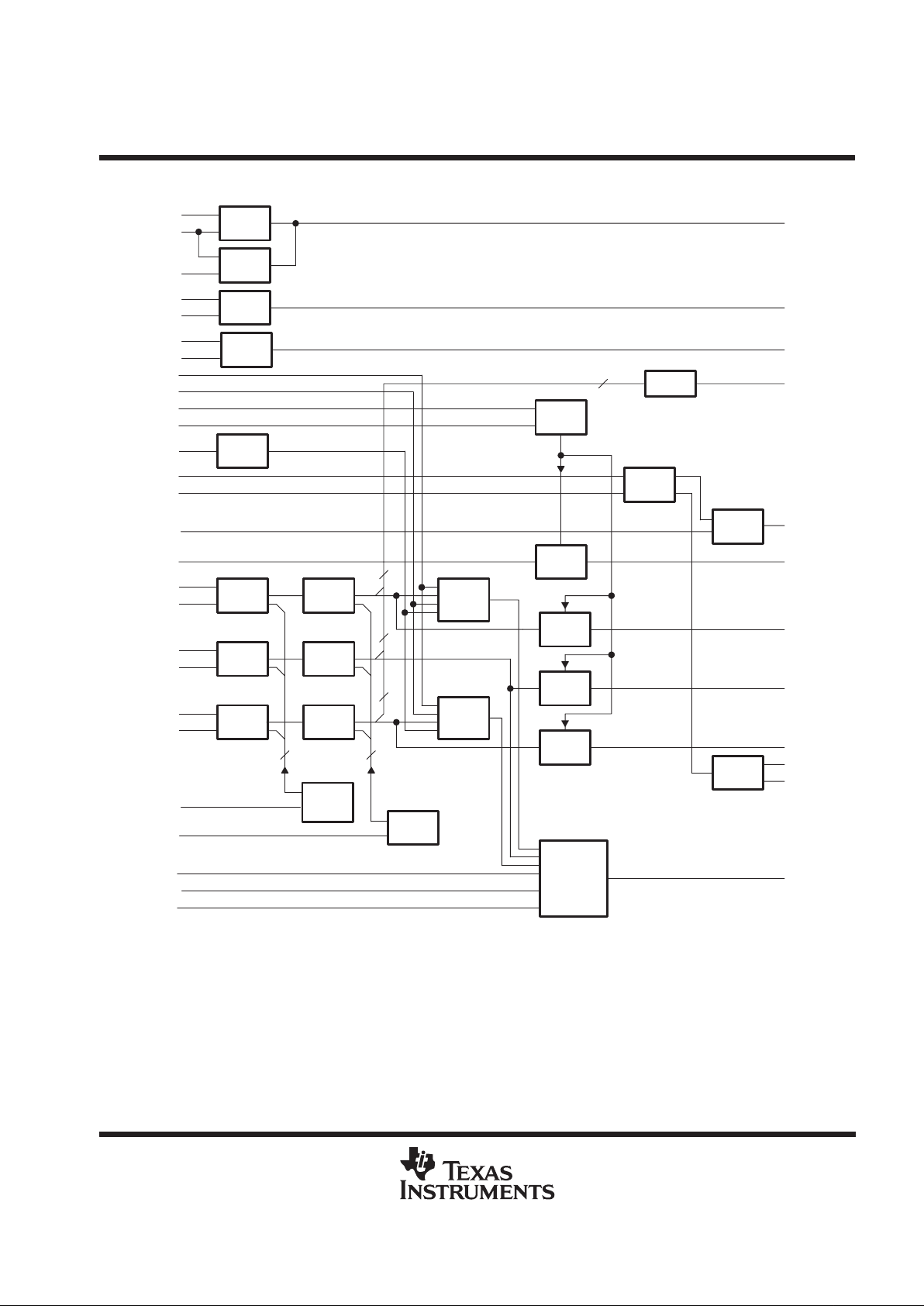

functional block diagram

3 3

1

2

3

A/D

ALC

AMP

Reset

Gate

AGC

AMP

Blue

Clamp

Green

Clamp

Red

Clamp

Blue

Blank

Green

Blank

Red

Blank

Clamp

Buffer

Blank

Buffer

White

Level

White

Level

AGC

CONT

YAGC

Blue

AGC

Green

AGC

Red

AGC

YSW

HLMIX

Y

Clamp

WCPCONT

ALC

REF

41

42

44

40

38

34

35

4

3

30

31

2

18

23

21

6

9

7

10

8

11

13

14

15

ALC

+

ALC –

RESET

GATE

GATE IN

AGCDET

AGCSET

CONTA

CONTB

AGCLMT

AGCCONT

WB

PCL2

YCLAMP

YAGCIN

BIN

CLPLVLB

GIN

CLPLVLG

RIN

CLPLVLR

SWR

SWG

SWB

43

39

33

19

22

26

29

28

27

25

36

20

ALCDRV

GATEOUT

AGCOUT

HL

YAGC

YOUT

WCPCONT

BOUT

GOUT

ROUT

YALC

ALCREF

YSW

3

17

16

PBL

PCL1

24

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

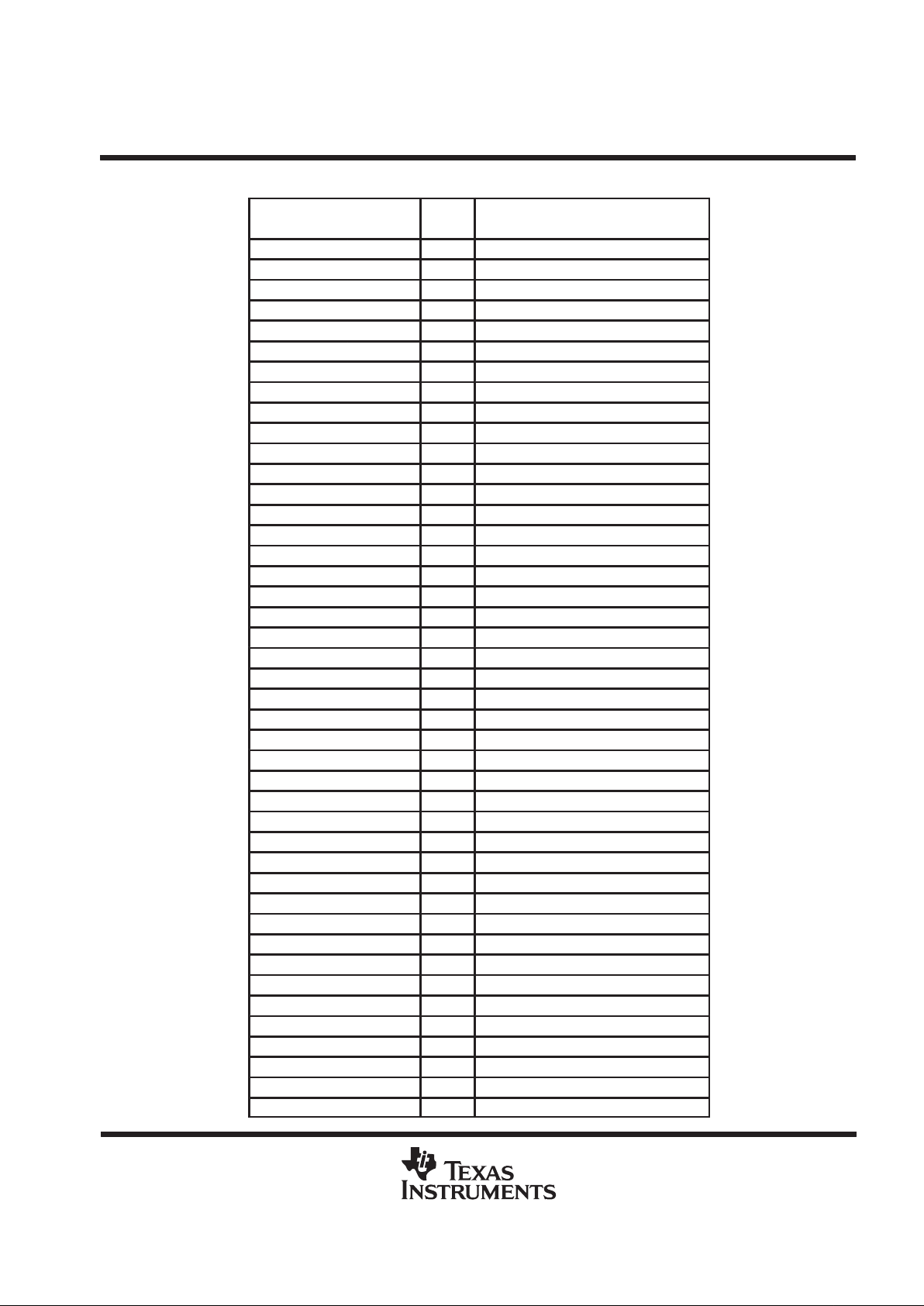

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

AGCCONT 31 I AGC control

AGCDET 34 I AGC detect

AGCLMT 30 I AGC limit

AGCOUT 33 O AGC out

AGCSET 35 I AGC set

ALCDRV 43 O ALC drive

ALCREF 36 O ALC reference

ALC+ 41 I ALC noninverting input

ALC– 42 I ALC inverting input

BIN 6 I Blue channel in

BOUT 29 O Blue channel out

CLPLVLB 9 I DC clamp level – blue

CLPLVLG 10 I DC clamp level – green

CLPLVLR 11 I DC clamp level – red

CONTA 4 I White balance digital control – A

CONTB 3 I White balance digital control – B

GATE 40 I Video gate control switch

GATEIN 38 I Video gate in

GATEOUT 39 O Video gate out

GIN 7 I Green channel in

GND 12, 37 Ground

GOUT 28 O Green channel out

HL 19 O Highlight suppression (not used)

NC 1 No internal connection

PBL 17 I Process blanking

PCL1 16 I Clamp signal 1

PCL2 18 I Clamp signal 2

REF2V 32 O 2-V reference

RESET 44 I Reset

RIN 8 I Red channel in

ROUT 27 O Red channel out

SWB 15 I Multiplex switch – blue

SWG 14 I Multiplex switch – green

SWR 13 I Multiplex switch – red

V

CC

5 Power supply voltage

WB 2 I White balance analog control

WCPCONT 24 I White clip control

YAGC 22 O YAGC out

YAGCIN 21 I Y AGC in

YALC 25 O Y automatic level control

YCLAMP 23 I Y clamp

YOUT 26 O Y signal out

YSW 20 O Multiplexed Y out

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

detailed description

white-balance control

White balance in the monochrome mode can be adjusted with either terminal 2 (white-balance analog control)

or with terminals 3 and 4 (white-balance digital controls B and A, respectively). If analog control is selected,

terminals 3 and 4 should be left open and terminal 2 adjusted appropriately (see Figure 1 and Figure 2 for control

characteristics). The white balance is controlled per the following table:

CONTB CONTA VOLTAGE LEVEL ON WB RED BLUE

L L 2.4 V –3 dB –4 dB

L H 2.7 V –1 dB –1.5 dB

H L 3 V 1 dB 1.5 dB

H H 3.5 V 3 dB 4 dB

analog inputs RIN, GIN, BIN

The TI TL1593 sample-and-hold circuit is normally the source for these inputs. The source signals should be

ac coupled into the TL1051. Gain control should be used on at least two of the three channels in order to obtain

an optimum balance.

clamp level

Input terminals 9, 10, and 11 (CLPLVLB, CLPLVLG, and CLPLVLR, respectively) should initially be set at

approximately 2 V dc. The levels should then be balanced so that clock feedthrough on terminal 20 (YSW) is

minimized under dark conditions.

multiplexed switching

Input terminals 13, 14, and 15 (SWR, SWG, and SWB, respectively) are the TTL-level signals used to multiplex

the three channels.

clamping and process blanking

Input terminals 16, 17, and 18 (PCL1, PBL, and PCL2) are used for TTL clamp and blank signals. The dark

references are clamped by the PCL1 signal. Unwanted noise in the video signal is eliminated by the PBL signal.

The Y signal can then be reclamped with the PCL2 signal.

Depending on the application, gain and automatic gain control (AGC) may or may not be selected. The following

descriptions cover both selections.

YSW

YSW output (terminal 20): Fast sampling of the video input signals with the TTL multiplex signals generates this

high-bandwidth output without adjustable gain or AGC.

gain and AGC selected

Y AGCIN input (terminal 21): If gain or AGC operation is selected, the YSW output (terminal 20) should be directly

connected to YAGCIN.

YAGC output (terminal 22): The multiplexed signal with controllable gain (controlled by the AGCCONT input)

is available at this terminal if terminals 20 (YSW) and 21 (Y AGCIN) are connected. If further signal processing

is desired, this terminal should be ac coupled to terminal 23 (YCLAMP).

YCLAMP input (terminal 23): The Y signal from Y AGC can be reclamped at this point by applying a wider clamp

pulse to terminal 18 (PCL2).

WCPCONT input (terminal 24): A dc voltage applied to this white clip control input causes the white clip function

to be performed on the Y signal. See Figure 4 for the clip control characteristics.

Y ALC output (terminal 25): If either AGC or automatic level control (ALC) is selected, the Y signal at this point

should be fed back to either the ALC or AGC block.

YOUT output (terminal 26): The white-clipped Y signal is available at this output.

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

analog output channels

T erminals 27, 28, and 29 (ROUT, GOUT, and BOUT) are the individual analog output signals used in RGB color

applications. Their gain can be affected by the control voltage applied to terminal 31 (AGCCONT).

AGC section

The AGC amplifier is a high-gain amplifier that requires an appropriate feedback network.

AGCLMT input (terminal 30): A dc voltage applied to this terminal limits the amount of gain for R, G, B, and Y.

AGCCONT input (terminal 31): A dc voltage applied to this terminal sets the gain (see Figure 3). It is also

possible to build a feedback network and obtain AGC action. In this case, the video signal is fed back through

AGCCONT.

REF2V output (terminal 32): This terminal provides a 2-V reference output.

AGCOUT output (terminal 33): This is the output from the AGC block.

AGCDET input (terminal 34): Video from terminal 26 (YOUT) can be applied to this node to obtain feedback

action.

AGCSET input (terminal 35): A dc voltage applied to this terminal sets the gain for AGC action.

gate section

GATEIN input (terminal 38): If a gating function is desired, video from the YOUT output (terminal 26) can be

applied to this terminal.

GA TEOUT output (terminal 39): Video is passed from GATEIN to GA TEOUT if GA TE (terminal 40) is low. If GA TE

is high, GATEOUT is in the high-impedance state.

GA TE input (terminal 40): A TTL signal can be applied to this input to control the active video (see the description

of the GATEOUT terminal above).

ALC section

An amplifier similar to that in the AGC section is available for use as an integrator. If used, a capacitor should

be connected from the ALC-input (terminal 42) to the ALCDRV output (terminal 43). A reset switch is available

at the RESET input (terminal 44). The ALC amplifier is a high-gain amplifier requiring an appropriate feedback

network.

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage, V

CC

(see Note 1) 8 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

8 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

–25°C to 75°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to the GND terminal.

recommended operating conditions

MIN NOM MAX UNIT

Supply voltage, V

CC

4.8 5 5.2 V

RIN, GIN, BIN 250 mV

WB 0 3.05 5

Input voltage, V

I

CLPLVLR, CLPLVLG, CLPLVLB 2

WCPCONT, AGCLMT, AGCCONT 0 3 5

V

AGCDET, AGCSET 3

High-level input voltage, V

IH

CONTA, CONTB, SWR, SWG, SWB, PCL1, 3.5 V

Low-level input voltage, V

IL

PCL2, PBL, RESET 0.4 V

Operating free-air temperature, T

A

–20 45 °C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

all sections

PARAMETER TEST CONDITIONS MIN TYP‡MAX UNIT

I

CC

Supply current VCC = 5 V 40 50 mA

Y-switch section

PARAMETER TEST CONDITIONS MIN TYP‡MAX UNIT

White-clip level (see Note 2) 400%

Gate-pulse impedance SWB, SWG, 5 kΩ

Gate-pulse capacitance SWR 10 pF

clamp section

PARAMETER TEST CONDITIONS MIN TYP‡MAX UNIT

Clamp-pulse current PCL1 –0.2 0.2 mA

Clamp resistance BIN, GIN, RIN PCL1 = 1 µs 30 Ω

Clamp-pulse input capacitance PCL1 30 pF

Noise rejection PCL1 to YSW 30 dB

‡

All typical values are at TA = 25° C.

NOTE 2: 250 mV = 100%.

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted) (continued)

blanking section

PARAMETER TEST CONDITIONS MIN MAX UNIT

Blanking-pulse current PBL –0.2 0.2 mA

Blanking-pulse input capacitance PBL 30 pF

Noise rejection PBL to YSW 30 dB

white-balance section

PARAMETER TEST CONDITIONS MIN MAX UNIT

Input current WB –10 10 µA

WB = 3.5 V 2.6 3.5

WB = 3 V 0.5 1.5

Red channel gain

RIN, WB to YSW

WB = 2.7 V –1.7 –0.6

dB

WB = 2.4 V –3.7 –2.7

WB = 3.5 V –4.4 –3.1

WB = 3 V –1.9 –0.8

Blue channel gain

BIN, WB to YSW

WB = 2.7 V 1 1.9

dB

WB = 2.4 V 3.5 4.5

AGC section

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

Gain delta between R, G, B channels –0.5 0 0.5 dB

AGCCONT = 1.5 V –1 0 1

Gain control

RIN, GIN, BIN to ROUT,

AGCCONT = 4.5 V 11.5 12.5 14.5

dB

AGC limit 1

,, ,

GOUT, BOUT, YAGC

AGCLMT = 0 0

AGC limit 2 AGCLMT = 5 V 12.5

dB

RIN, GIN, BIN to

AGCCONT = 2.5 V (AGC on) 2.9 3.6

,,

ROUT, GOUT, BOUT

AGCCONT = 0.5 V (AGC off) 3 5.1

RGB bandwidth

AGCCONT = 2.5 V (AGC on) 3.4 4.2

MH

z

RIN, GIN, BIN to YAGC

AGCCONT = 0.5 V (AGC off) 5 6.2

Output impedance ROUT, GOUT, BOUT 150 Ω

Y-clamp section

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

Clamp pulse current PCL2 –0.2 0.2 mA

Clamp pulse capacitance PCL2 50 pF

white-clip section

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

White-clip point See Note 3 400%

Knee point 1 WCPCONT open, See Note 3 118%

Knee point 2 YCL to YOUT WCPCONT = 3 V, See Note 3 176% 236%

Knee point 3 WCPCONT = 2 V, See Note 3 35% 59%

Knee compression ratio 13.5 15.5 17.5 dB

Output impedance YOUT 100 Ω

†

All typical values are at TA = 25° C.

NOTE 3: 340 mV = 100%.

Output voltageV

O

AGCDET, AGCSET,

AGCOUT

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted) (continued)

ALC-clip section

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

ALCREF VCC = 4.8 V to 5.2 V 2.6 2.8 3 V

YALC 340 mV

Clip level YALC 800 mV

Output impedance ALCREF, YALC 100 Ω

AGCDET section (see Note 4)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

Gain AGCDET, AGCOUT 60 dB

AGC setpoint 1 AGCSET = 3.5 V 41%

AGC setpoint 2 AGCSET = 1.5 V 12%

AGC setpoint 3 AGCSET open 24%

ALC-amplifier section

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

Maximum output voltage ALCDRV 3.5 V

Minimum output voltage ALCDRV 0.5 V

V

IO

Input offset voltage ALC+, ALC– –8 0 8 mV

I

IB

Input bias current ALC+, ALC– 200 nA

I

I

Input current RESET –0.5 0.5 mA

Gain ALC+, ALC–, ALCDRV 60 dB

†

All typical values are at TA = 25° C.

NOTE 4: The YAGC output is 100% when the YAGCIN input = 250 mV.

operating characteristics over recommended operating temperature range (unless otherwise

noted)

Y-switch section

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Switching frequency, RIN, GIN, BIN to YSW WB = 0 V to V

CC

8 10 MHz

RIN or BIN to YSW 20 30

t

pd

GIN to YSW 10 20 ns

SWR, SWG, or SWB to YSW 5

SWR, SWG, SWB acquisition time 20 ns

YSW output settling time 30 ns

clamp section

PARAMETER TEST CONDITIONS MIN MAX UNIT

t

pd

PCL1 to YSW 100 ns

blanking section

PARAMETER TEST CONDITIONS MIN MAX UNIT

t

pd

PBL to YSW 150 ns

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

operating characteristics over recommended operating temperature range (unless otherwise

noted) (continued)

Y-clamp section

PARAMETER TEST CONDITIONS MIN MAX UNIT

t

pd

PCL2 to YOUT 500 ns

white-clip section

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Switching frequency, YCL to YOUT WCPCONT open 6 8 MHz

ALC-clip section

PARAMETER TEST CONDITIONS MIN MAX UNIT

Switching frequency, YCL to YALC 2 MHz

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

0

–2

–4

0 2.5 2.6 2.7 2.8 2.9 3

Red-Channel Gain Change – dB

2

4

White-Balance Control Voltage – V

RED-CHANNEL GAIN CHANGE

vs

WHITE-BALANCE CONTROL VOLTAGE

3.1 3.2 5

0

–2

–4

0 2.5 2.6 2.7 2.8 2.9 3

Blue-Channel Gain Change – dB

2

4

White-Balance Control Voltage – V

BLUE-CHANNEL GAIN CHANGE

vs

WHITE-BALANCE CONTROL VOLTAGE

3.1 3.2 5

Figure 1 Figure 2

10

8

4

2

0

18

6

0123

AGC Gain Change – dB

14

12

16

AGC Control Voltage – V

AGC GAIN CHANGE

vs

AGC CONTROL VOLTAGE

45

Knee

YOUT Voltage – V

WCPCONT Voltage – V

Y-SIGNAL OUTPUT VOLTAGE

vs

WHITE-CLIP CONTROL INPUT VOLTAGE

Voltage

Figure 3 Figure 4

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

33

GT1

22

44

NC

YAGC

1

AGCOUT

RESET

43

ALCDRV

42

ALC–

41

ALC+

40

GATE

39

GATEOUT

38

GATEIN

37

GND

36

ALCREF

35

AGCSET

34

AGCDET

WB

2

CONTB

3

CONTA

4

5

BIN

6

GIN

7

RIN

8

CLPLVLB

9

CLPLVLG

10

CLPLVLR

11

12

GND13SWR14SWG15SWB16PCL117PBL18PCL219HL20YSW21YAGCIN

32

REF2V

31

AGCCONT

30

AGCLMT

29

BOUT

28

GOUT

27

ROUT

26

YOUT

25

YALC

24

WCPCONT

23

YCLAMP

V

CC

Q4

2N3904

C13

0.1 µF

YOUT

R14

1 kΩ

R10

100 Ω

5 V

Q1

2N3904

C10

0.1 µF

BOUT

R11

1 kΩ

R7

100 Ω

5 V

Q2

2N3904

C11

0.1 µF

GOUT

R12

1 kΩ

R8

100 Ω

5 V

Q3

2N390

4

C12

0.1 µF

ROUT

R13

1 kΩ

R9

100 Ω

5 V

R6

10 kΩ

C9

0.1 µF

5 V

C8

0.1 µF

GT2

GT3

BCP1

CP2

BCP2

From Timing

Generator

(see Note A)

5 V

C4

C5

C6

0.1 µF

0.1 µF

0.1 µF

5 V

C7

0.1 µF

R3

10 kΩR410 kΩR510 kΩ

5 V

5 V

C3

0.1 µF

R1

22 kΩ

R2

33 kΩ

C2

0.1 µF

C1

0.1 µF

TL1051

Video

Preprocessor

NOTE A: This application circuit shows TTL signals originating from the TI SN28835 1/2-Inch NTSC Timer. However, the TL1051 video

preprocessor interfaces equally well with a TI TMS3471C 2/3-Inch NTSC timer, a TI SN28837 1/2-Inch PAL timer, or a user-defined

timing generator.

Figure 5. Typical Application Circuit

TL1051

VIDEO PREPROCESSOR CIRCUIT

SOCS032B – NOVEMBER 1991

4-12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MECHANICAL DATA

FR/S-PDFP-G44 PLASTIC QUAD FLATP ACK

4040159/A–10/93

0,80

0,30

12,80

12,00

33 23

34

44

111

22

12

2,25 MAX

0,10

0,20

0,80 TYP

SQ

0,40

0,20

8,00 TYP

0°–10°

10,20

9,80

SQ

Seating Plane

0,10 MIN

0,10

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...