Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

TDA2Ex SoC for Advanced Driver Assistance Systems (ADAS)

23mm Package (ABC Package)

Silicon Revision 2.0 and 2.1

1 Device Overview

1.1 Features

1

• Architecture designed for ADAS applications

• Video, image, and graphics processing support

– Full-HD video (1920 × 1080p, 60 fps)

– Multiple video inputs and video outputs

• Arm®Cortex®-A15 microprocessor subsystem

• C66x floating-point VLIW DSP cores

– Fully object-code compatible with C67x and

C64x+

– Up to thirty-two 16 × 16-bit fixed-point multiplies

per cycle

• Up to 512KB of on-chip L3 RAM

• Level 3 (L3) and level 4 (L4) interconnects

• DDR3/DDR3L External Memory Interface (EMIF)

module

– Supports up to DDR3-1333 (667 MHz)

– Up to 2GB across single chip select

• Dual Arm®Cortex®-M4 Image Processing Units

(IPU)

• IVA-HD subsystem

• Display subsystem

– Display controller with DMA engine and up to

three pipelines

– HDMI™ encoder: HDMI 1.4a and DVI 1.0

compliant

• Single-core PowerVR®SGX544 3D GPU

• 2D-graphics accelerator (BB2D) subsystem

– Vivante®GC320 core

• Video Processing Engine (VPE)

• One Video Input Port (VIP) module

– Support for up to four multiplexed input ports

• General-Purpose Memory Controller (GPMC)

• Enhanced Direct Memory Access (EDMA)

controller

• 2-Port Gigabit Ethernet switch

– Up to two external ports, one internal

• Sixteen 32-bit general-purpose timers

• 32-bit MPU watchdog timer

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

• Six high speed Inter-Integrated Circuit ( I2C™)

ports

• Ten configurable UART/IrDA/CIR modules

• Four Multichannel Serial Peripheral Interfaces

(McSPI)

• Quad Serial Peripheral Interface ( QSPI™)

• SATA interface

• Eight Multichannel Audio Serial Port (McASP)

modules

• SuperSpeed USB 3.0 dual-role device

• High Speed USB 2.0 dual-role device

• High Speed USB 2.0 on-the-go

• Four MultiMedia Card/ Secure Digital®/Secure

Digital Input Output interfaces ( MMC™/

SD®/SDIO)

• PCI-Express®( PCIe®) revision 3.0 Port with

integrated PHY

– One 2-lane gen2-compliant port

– or Two 1-lane gen2-compliant ports

• Dual Controller Area Network (DCAN) modules

– CAN 2.0B protocol

• MIPI®Camera Serial Interface 2 (CSI-2)

• Up to 215 General-Purpose I/O (GPIO) pins

• Real-Time Clock subsystem (RTCSS)

• Device Security Features

– Hardware crypto accelerators and DMA

– Firewalls

– JTAG lock

– Secure keys

– Secure ROM and boot

– Customer programmable keys (Silicon Revision

2.1)

• Power, reset, and clock management

• On-chip debug with CTools technology

• 28-nm CMOS technology

• 23 mm × 23 mm, 0.8-mm Pitch, 760-Pin BGA

(ABC)

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

1.2 Applications

• Mono, Stereo or Tri-Optic Front Camera

– Object detection

– Pedestrian detection

– Traffic sign recognition

– Lane detection and departure warning

– Automatic emergency braking

– Adaptive cruise control

– Forward collision warning

– High beam assist

1.3 Description

TI’s new TDA2Ex System-on-Chip (SoC) is a highly optimized and scalable family of devices designed to

meet the requirements of leading Advanced Driver Assistance Systems (ADAS). The TDA2Ex family

enables broad ADAS applications in today’s automobile by integrating an optimal mix of performance, low

power, and ADAS vision analytics processing that aims to facilitate a more autonomous and collision-free

driving experience.

www.ti.com

• LVDS or ethernet surround view

– 2D surround view

– 3D surround view

– Rear object detection

– Parking assist

– Pedestrian detection

– Lane tracking

– Drive recording

• Sensor fusion – vision, radar, ultrasonic, lidar

sensors

– Object data fusion

– Raw data fusion

The TDA2Ex SoC enables sophisticated embedded vision technology in today’s automobile by enabling a

board range of ADAS applications including park assist, surround view and sensor fusion on a single

architecture.

The TDA2Ex SoC incorporates a heterogeneous, scalable architecture that includes a mix of TI’s fixed

and floating-point TMS320C66x digital signal processor (DSP) generation core, Arm®Cortex®-A15

MPCore™ and dual- Arm®Cortex®-M4 processors. The integration of a video accelerator for decoding

multiple video streams over an Ethernet AVB network, along with graphics accelerator for rendering virtual

views, enable a 3D viewing experience. The TDA2Ex SoC also integrates a host of peripherals including

multicamera interfaces (both parallel and serial, including CSI-2) to enable Ethernet or LVDS-based

surround view systems, displays and GigB Ethernet AVB.

Additionally, TI provides a complete set of development tools for the Arm®and DSP, including C

compilers, a DSP assembly optimizer to simplify programming and scheduling, and a debugging interface

for visibility into source code execution.

Cryptographic acceleration is available in all devices. All other supported security features, including

support for secure boot, debug security and support for trusted execution environment is available on

High-Security (HS) devices. For more information about HS devices, contact your TI representative.

The TDA2Ex ADAS processor is qualified according to the AEC-Q100 standard.

Device Information

PART NUMBER PACKAGE BODY SIZE

TDA2EGABC FCBGA (760) 23.0 mm × 23.0 mm

(1) For more information, see Section 10, Mechanical, Packaging, and Orderable Information.

(1)

2

Device Overview Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

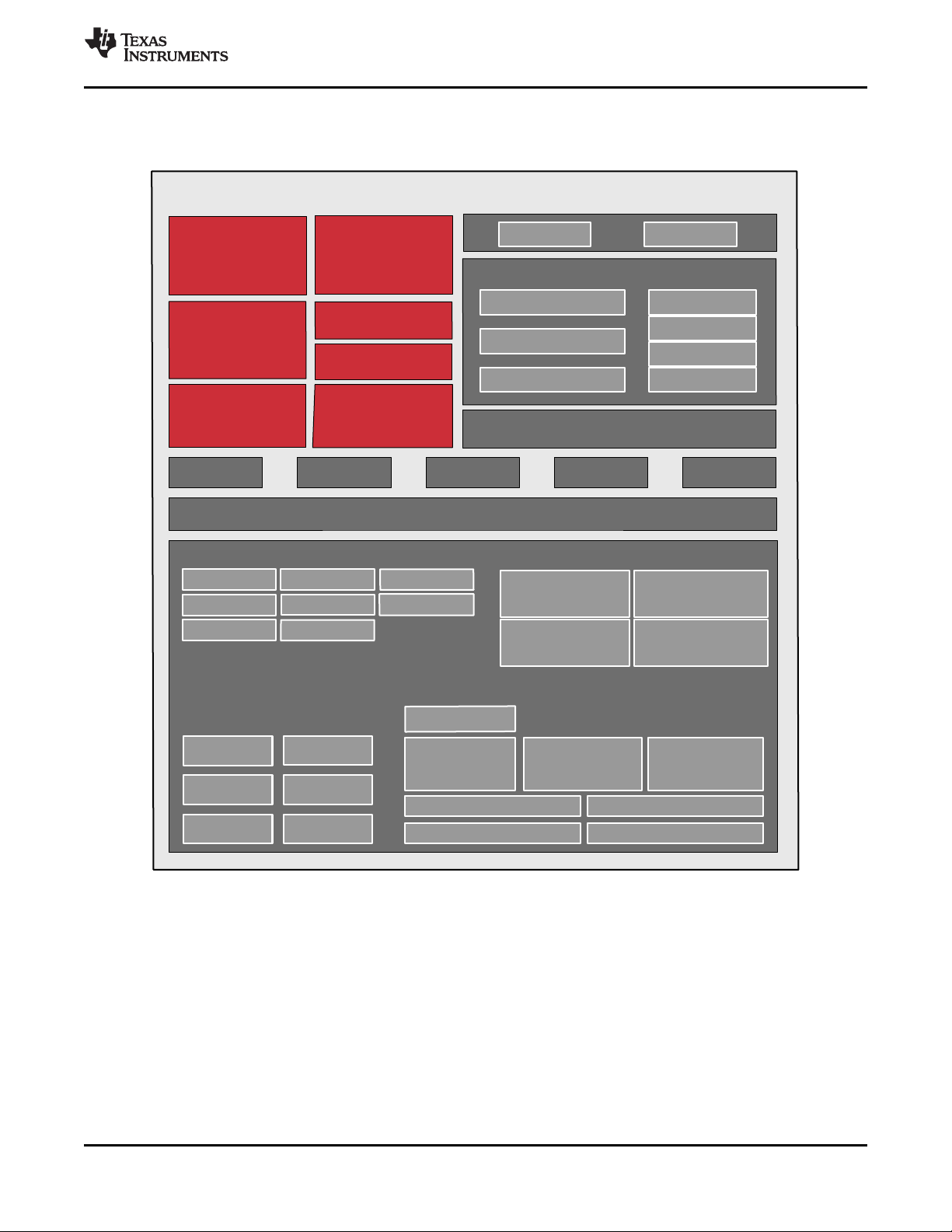

Mailbox x13

High Speed Interconnect

Program/Data Storage

Connectivity

System

(1x Arm

Cortex–A15)

IVA HD

1080p Video

Coprocessor

(C66x Coprocessor)

DSP

PCIe SS x2

(NAND/NOR/

Async)

(1x SGX544 3D)

intro-001

GPMC / ELM

256-KB ROM

OCMC

TDA2Ex

GPU

MPU

Serial Interfaces

I2C x6

UART x10

McSPI x4

DCAN x2

Spinlock

GPIO x8

Timers x16

WDT

QSPI

EMIF 32-bit

DDR3/3L W/ECC

McASP x8

CAL

CSI2 x2

Display Subsystem

LCD1

LCD2

LCD3

HDMI 1.4a

1x GFX Pipeline

3x Video Pipeline

Blend / Scale

GMAC AVB

1x USB 3.0

Dual Mode FS/HS/SS

w/ PHY

2x USB 2.0

Dual Mode FS/HS

1x PHY, 1x ULPI

512-KB

RAM

DMM

MMC / SD x4

EDMA

VIP x1

JTAG

VPE

MMU x2

(Dual Cortex–M4)

IPU 1

(Dual Cortex–M4)

IPU 2

BB2D

(GC320 2D)

RTC SS

PWM SS x3

SDMA

SATA

Secure Boot Debug

SecurityTEE (HS devices)

www.ti.com

1.4 Functional Block Diagram

Figure 1-1 is functional block diagram for the device.

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Figure 1-1. TDA2Ex Block Diagram

Submit Documentation Feedback

Product Folder Links: TDA2EG

Device OverviewCopyright © 2016–2019, Texas Instruments Incorporated

3

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

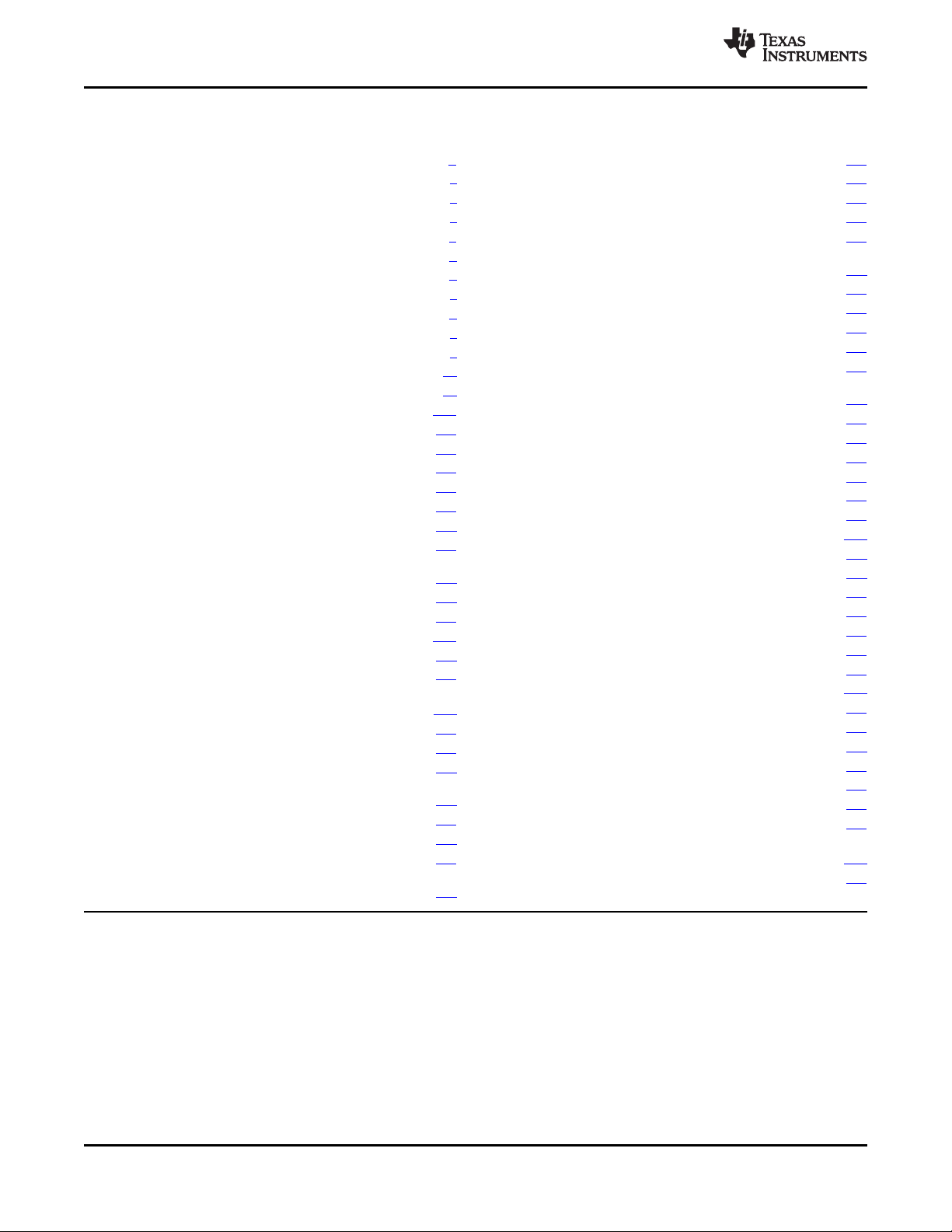

Table of Contents

1 Device Overview ......................................... 1

1.1 Features .............................................. 1

1.2 Applications........................................... 2

1.3 Description............................................ 2

1.4 Functional Block Diagram ........................... 3

2 Revision History ......................................... 5

3 Device Comparison ..................................... 6

3.1 Related Products ..................................... 7

4 Terminal Configuration and Functions.............. 8

4.1 Terminal Assignment ................................. 8

4.2 Ball Characteristics ................................... 9

4.3 Multiplexing Characteristics ......................... 69

4.4 Signal Descriptions.................................. 85

5 Specifications ......................................... 121

5.1 Absolute Maximum Ratings........................ 121

5.2 ESD Ratings ....................................... 123

5.3 Power-On-Hour (POH) Limits...................... 123

5.4 Recommended Operating Conditions ............. 123

5.5 Operating Performance Points..................... 127

5.6 Power Consumption Summary .................... 147

5.7 Electrical Characteristics........................... 147

5.8 VPP Specifications for One-Time Programmable

(OTP) eFuses...................................... 157

5.9 Thermal Characteristics............................ 158

5.10 Power Supply Sequences ......................... 159

6 Clock Specifications ................................. 168

6.1 Input Clock Specifications ......................... 169

6.2 DPLLs, DLLs Specifications ....................... 178

7 Timing Requirements and Switching

Characteristics ........................................ 182

7.1 Timing Test Conditions ............................ 182

7.2 Interface Clock Specifications ..................... 182

7.3 Timing Parameters and Information ............... 182

7.4 Recommended Clock and Control Signal Transition

Behavior............................................ 184

7.5 Virtual and Manual I/O Timing Modes ............. 184

7.6 Video Input Ports (VIP) ............................ 186

7.7 Display Subsystem - Video Output Ports.......... 205

7.8 Display Subsystem - High-Definition Multimedia

Interface (HDMI) ................................... 216

7.9 Camera Serial Interface 2 CAL bridge (CSI2) ..... 217

7.10 External Memory Interface (EMIF)................. 217

7.11 General-Purpose Memory Controller (GPMC)..... 217

7.12 Timers.............................................. 241

7.13 Inter-Integrated Circuit Interface (I2C)............. 241

7.14 Universal Asynchronous Receiver Transmitter

(UART)............................................. 244

7.15 Multichannel Serial Peripheral Interface (McSPI) . 246

7.16 Quad Serial Peripheral Interface (QSPI) .......... 252

7.17 Multichannel Audio Serial Port (McASP) .......... 256

7.18 Universal Serial Bus (USB) ........................ 276

7.19 Serial Advanced Technology Attachment (SATA). 277

7.20 Peripheral Component Interconnect Express

(PCIe) .............................................. 278

7.21 Controller Area Network Interface (DCAN) ........ 278

7.22 Ethernet Interface (GMAC_SW) ................... 279

7.23 eMMC/SD/SDIO ................................... 292

7.24 General-Purpose Interface (GPIO) ................ 315

7.25 System and Miscellaneous interfaces ............. 316

7.26 Test Interfaces ..................................... 316

8 Applications, Implementation, and Layout ...... 320

8.1 Introduction ........................................ 320

8.2 Power Optimizations............................... 321

8.3 Core Power Domains .............................. 332

8.4 Single-Ended Interfaces ........................... 343

8.5 Differential Interfaces .............................. 345

8.6 Clock Routing Guidelines.......................... 365

8.7 DDR3 Board Design and Layout Guidelines....... 366

9 Device and Documentation Support.............. 390

9.1 Device Nomenclature and Orderable Information . 390

9.2 Tools and Software ................................ 392

9.3 Documentation Support............................ 393

9.4 Support Resources ................................ 393

9.5 Trademarks ........................................ 393

9.6 Electrostatic Discharge Caution ................... 394

9.7 Glossary............................................ 394

10 Mechanical, Packaging, and Orderable

Information............................................. 395

10.1 Packaging Information ............................. 395

4

Table of Contents Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

TDA2EG

www.ti.com

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

2 Revision History

Changes from June 8, 2018 to February 15, 2019 (from F Revision (June 2018) to G Revision) Page

• Added Device Security Features for Silicon revision 2.1 in Section 1.1, Features........................................... 1

• Added clarification note regarding XDRA726 part number in Table 3-1, Device Comparison ............................. 6

• Added vpp details for Silicon revision 2.1 in Table 4-1, Unused Balls Specific Connection Requirements,

Table 4-2, Ball Characteristics and Table 4-31, Power Supply Signal Descriptions......................................... 9

• Updated porz, resetn and rstoutn signal descriptions in Table 4-26, PRCM Signal Descriptions ...................... 115

• Added clarification note regarding TSHUT feature in Table 5-4, Recommended Operating Conditions............... 127

• Updated OPP_HIGH power supply value in note (6) under Table 5-7, Voltage Domains Operating Performance

Points................................................................................................................................ 128

• Added missing RTC details in Table 5-8, Supported OPP vs Max Frequency and added Section 5.7.6, LVCMOS

OSC Buffers DC Electrical Characteristics..................................................................................... 128

• Updated SYS_32K to FUNC_32K_CLK in Table 5-9, Maximum Supported Frequency ................................ 129

• Added Section 5.8, VPP Specifications for One-Time Programmable (OTP) eFuses for Silicon revision 2.1 ........ 157

• Updated Section 5.10, Power Supply Sequences............................................................................. 159

• Updated system clock names in Section 6, Clock Specifications ........................................................... 168

• Added missing RTC details in Section 6, Clock Specifications.............................................................. 168

• Added Section 8.3.7, Loss of Input Power Event.............................................................................. 337

• Added Section 8.5.5, SATA Board Design and Layout Guidelines ........................................................ 359

• Added Section 8.6, Clock Routing Guidelines ................................................................................ 365

• Updated note for cosmetic marks on package................................................................................. 390

• Added Silicon revison 2.1 in support in Table 9-1, Nomenclature Description ............................................ 391

• Added clarification note regarding XDRA726 part number in Table 9-1, Nomenclature Description................... 391

Changes from February 16, 2019 to November 15, 2019 (from G Revision (February 2019) to H Revision) Page

• Updated note regarding XDRA726 part number in Table 3-1, Device Comparison ......................................... 7

• Added reminders to disable unused pulls and RX pads in Section 4.2, Ball Characteristics ............................. 10

• Removed uart2_rxd for Muxmode 0 .............................................................................................. 12

• Added clarification notes for EMU[1:0] connections in Table 4-22, GPIOs Signal Descriptions and Table 4-24,

Debug Signal Descriptions ....................................................................................................... 107

• Updated clock names in Table 5-9, Maximum Supported Frequency ...................................................... 129

• Updated EMIF_DLL_FCLK max rate in Table 6-15, DLL Characteristics.................................................. 181

• Updated GPMC timing table footnotes.......................................................................................... 218

• Updated timing specification values for GPMC and MMC ................................................................... 218

• Updated information about WD_TIMER1 in Section 7.12, Timers .......................................................... 241

• Updated parameter in Table 7-42, Timing Requirements for QSPI......................................................... 254

• Added MII_TXER timing to Section 7.22.1, GMAC MII Timings............................................................. 281

• Updated MDIO Timing Diagram and MDIO7 parameter values............................................................. 283

• Updated Delay time for MMC2 in Table 7-109, Switching Characteristics for MMC2 - JC64 High Speed DDR

Mode................................................................................................................................. 304

• Added note regarding DDR ECC solutions to Table 8-30, Supported DDR3 Device Combinations ................... 367

• Added clarifications about validated DDR topology ........................................................................... 376

• Updated note regarding XDRA726 part number in Table 9-1, Nomenclature Description............................... 392

Submit Documentation Feedback

Product Folder Links: TDA2EG

Revision HistoryCopyright © 2016–2019, Texas Instruments Incorporated

5

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

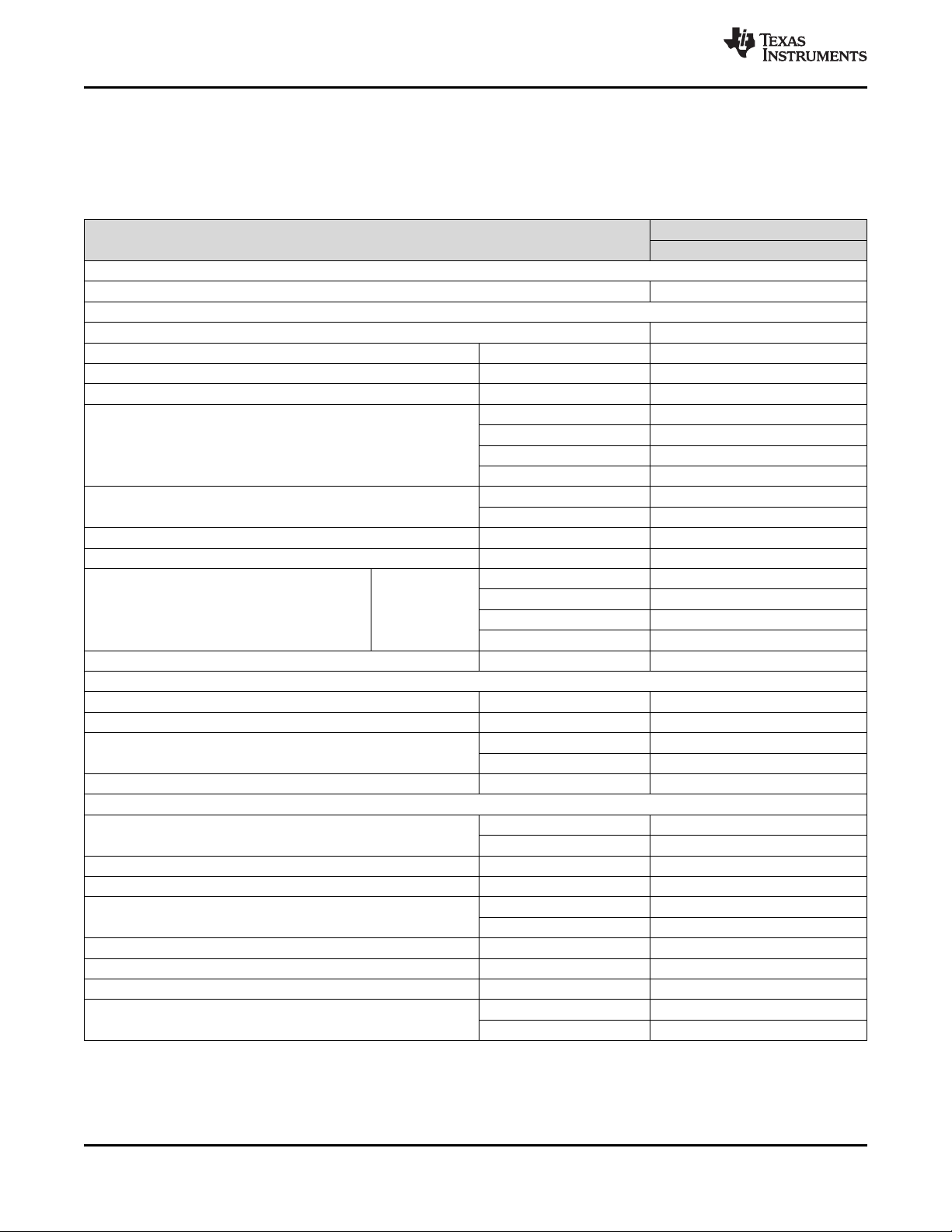

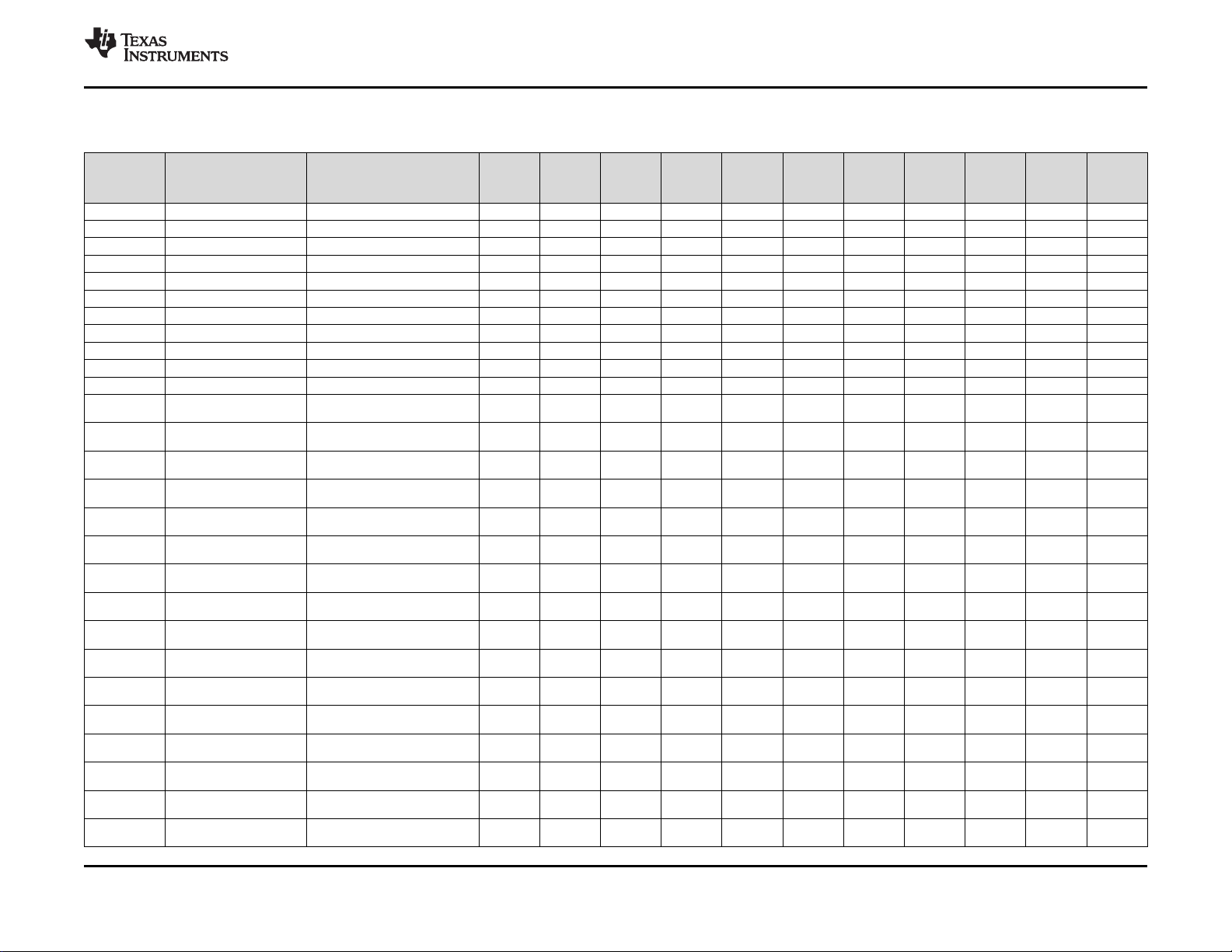

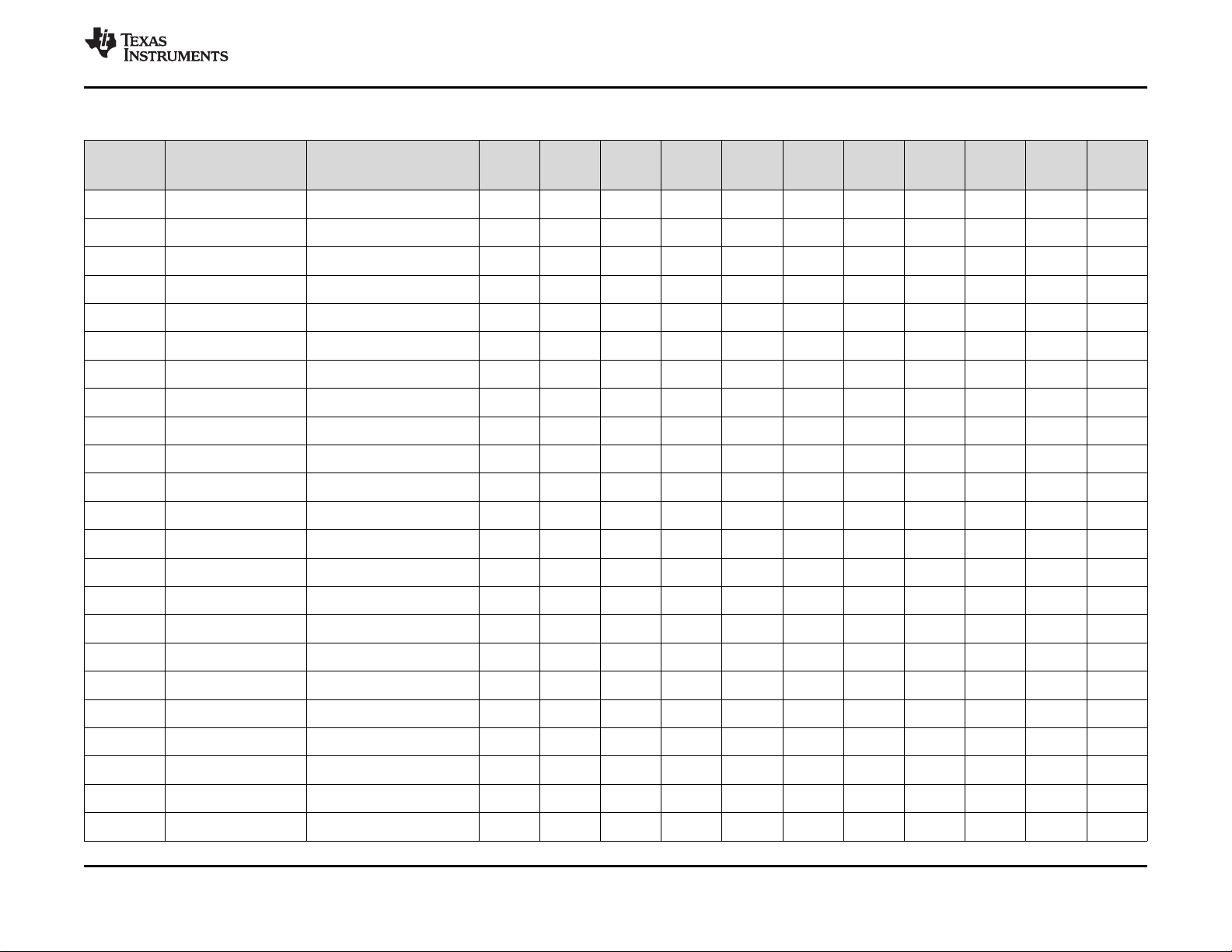

3 Device Comparison

Table 3-1 shows a comparison between devices, highlighting the differences.

www.ti.com

Table 3-1. Device Comparison

FEATURES

Features

CTRL_WKUP_STD_FUSE_DIE_ID_2[31:24] Base PN register bit field value

Processors/Accelerators

Speed Grades H, D

Arm Single Cortex-A15 Microprocessor (MPU) Subsystem MPU core 0 Yes

C66x VLIW DSP DSP1 Yes

BitBLT 2D Hardware Acceleration Engine (BB2D) BB2D Yes

Display Subsystem

Dual Arm Cortex-M4 Image Processing Unit (IPU)

Image Video Accelarator (IVA) IVA Yes

SGX544 Single-Core 3D Graphics Processing Unit (GPU) GPU Yes

Video Input Port (VIP) VIP1

Video Processing Engine (VPE) VPE Yes

Program/Data Storage

On-Chip Shared Memory (RAM) OCMC_RAM1 512KB

General-Purpose Memory Controller (GPMC) GPMC Yes

DDR3 Memory Controller

Dynamic Memory Manager (DMM) DMM Yes

Peripherals

Dual Controller Area Network (DCAN) Interface

Enhanced DMA (EDMA) EDMA Yes

System DMA (DMA_SYSTEM) DMA_SYSTEM Yes

Ethernet Subsystem (Ethernet SS)

General-Purpose I/O (GPIO) GPIO up to 215

Inter-Integrated Circuit (I2C) Interface I2C 6

System Mailbox Module MAILBOX 13

Camera Adaptation Layer (CAL) Camera Serial Interface 2 (CSI2)

(1)(2)

VOUT1 Yes

VOUT2 Yes

VOUT3 Yes

HDMI Yes

IPU1 Yes

IPU2 Yes

vin1a Yes

vin1b Yes

vin2a Yes

vin2b Yes

EMIF1 up to 2GB across single chip select

SECDED/ECC Yes

DCAN1 Yes

DCAN2 Yes

GMAC_SW[0] MII, RMII, or RGMII

GMAC_SW[1] MII, RMII, or RGMII

CSI2_0 1 CLK + 4 Data Line

CSI2_1 1 CLK + 2 Data Line

(2)

DEVICE

TDA2EG

TDA2EGx: 20 (0x14)

6

Device Comparison Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 3-1. Device Comparison

FEATURES

McASP1 16 serializers

McASP2 16 serializers

McASP3 4 serializers

Multichannel Audio Serial Port (McASP)

MultiMedia Card/Secure Digital/Secure Digital Input Output Interface

(MMC/SD/SDIO)

PCI-Express 3.0 Port with Integrated PHY

Serial Advanced Technology Attachment (SATA) SATA Yes

Real-Time Clock Subsystem (RTCSS) RTCSS Yes

Multichannel Serial Peripheral Interface (McSPI) McSPI 4

Quad SPI (QSPI) QSPI Yes

Spinlock Module SPINLOCK Yes

Timers, General-Purpose TIMERS GP 16

Timer, Watchdog WD TIMER Yes

Pulse-Width Modulation Subsystem (PWMSS)

Universal Asynchronous Receiver/Transmitter (UART) UART 10

Universal Serial Bus (USB3.0)

Universal Serial Bus (USB2.0)

(1) For more details about the CTRL_WKUP_STD_FUSE_DIE_ID_2 register and Base PN bit field, see the TDA2Ex Technical Reference

Manual.

(2) XDRA726 base part number with X speed grade indicator is the part number for the superset device. Software should constrain the

features and speed used to match the intended production device. The Base PN register bit field value is 0x4.

McASP4 4 serializers

McASP5 4 serializers

McASP6 4 serializers

McASP7 4 serializers

McASP8 4 serializers

MMC1 1x UHSI 4b

MMC2 1x eMMC™ 8b

MMC3 1x SDIO 8b

MMC4 1x SDIO 4b

PCIe_SS1 Yes

PCIe_SS2 Yes

PWMSS1 Yes

PWMSS2 Yes

PWMSS3 Yes

USB1 (SuperSpeed, DualRole-Device [DRD])

USB2 (High Speed, DualRole-Device [DRD], with

embedded HS PHY)

USB3 (High Speed, OTG2.0,

with ULPI)

USB4 (High Speed, OTG2.0,

with ULPI)

(2)

(continued)

DEVICE

TDA2EG

Yes

Yes

Yes

No

3.1 Related Products

Automotive Processors

TDAx ADAS SoCs TI's TDAx Driver Assistance System-on-Chip (SoC) family offers scalable and open

solutions and a common hardware and software architecture for Advanced Driver Assistance

Systems (ADAS) applications including camera-based front (mono and stereo), rear,

surround view and night vision systems, and mid- and long-range radar and sensor fusion

systems.

Companion Products for TDAx Review products that are frequently purchased or used in conjunction

with this product.

Submit Documentation Feedback

Product Folder Links: TDA2EG

Device ComparisonCopyright © 2016–2019, Texas Instruments Incorporated

7

SPRS906_BALL_01

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

4 Terminal Configuration and Functions

4.1 Terminal Assignment

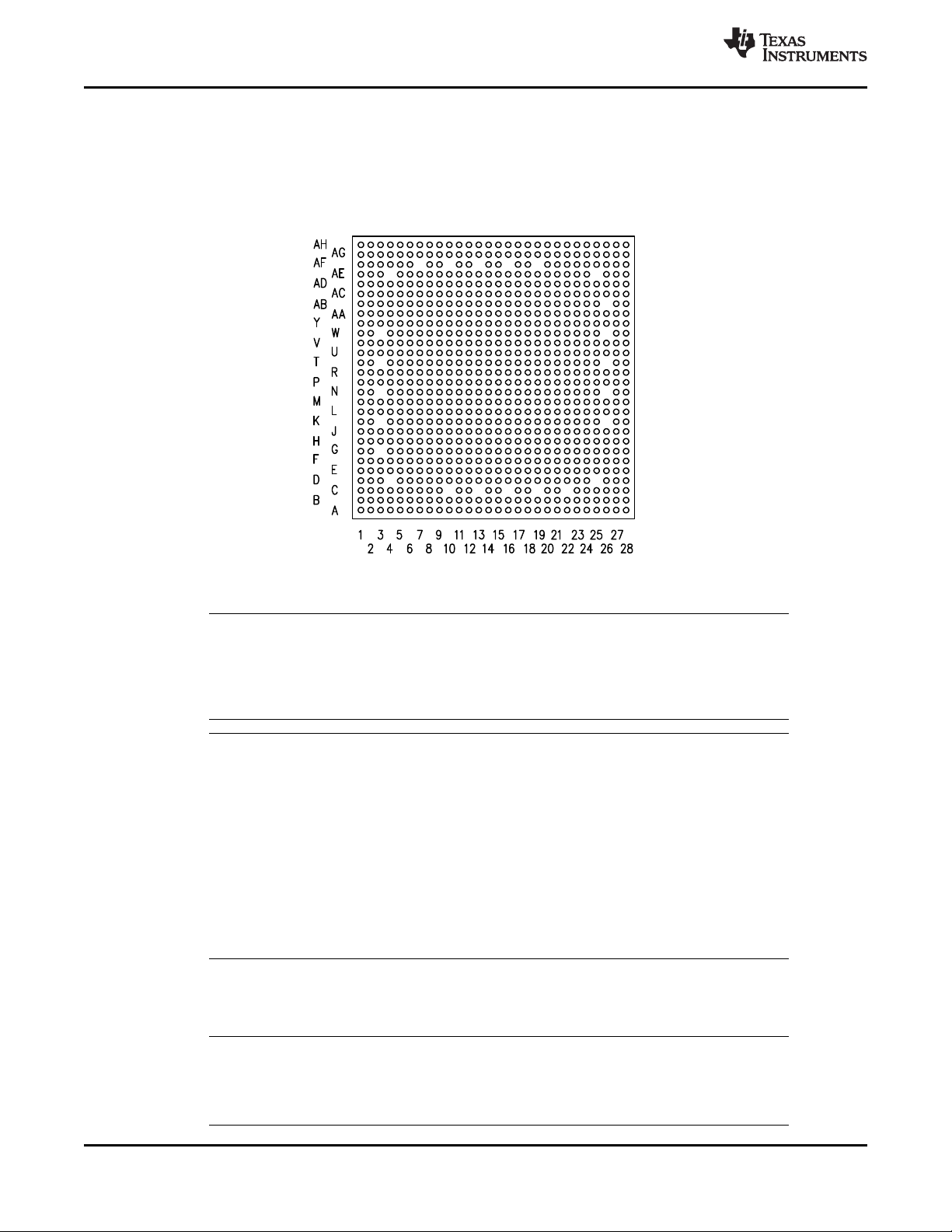

Figure 4-1 shows the ball locations for the 760 plastic ball grid array (PBGA) package and is used in

conjunction with Table 4-2 through Table 4-31 to locate signal names and ball grid numbers.

www.ti.com

Figure 4-1. ABC S-PBGA-N760 Package (Bottom View)

The following bottom balls are not pinned out: AF7, AF10, AF13, AF16, AF19, AE4, AE25,

AB26, W3, W26, T3, T26, N3, N26, K3, K26, G3, D4, D25, C10, C13, C16, C19, C22.

These balls do not exist on the package.

The following bottom balls are not connected: AH11, AH12, AG2, AG8, AG11, AG12, AF4,

AF6, AF8, AF9, AE3, AE5, AE6, AE8, AE9, AD3, AD8, AD9, Y15, Y16, V18, V19, U18, U19,

U22, U23, U24, U25, U26, U27, U28, T22, T23, T27, T28, R20, R22, R23, R24, R25, R26,

R27, R28, P19, P22, P23, P24, P25, P26, P27, N20, N22, N23, N27, N28, M20, M21, M22,

M23, M24, M25, M26, M27, M28, L20, L21, L22, L23, L24, L25, L26, L27, L28, K20, K21,

K22, K23, K27, K28, J20, J21, J22, J23, J24, J25, J26, J27, H20, H21, H22, H23, H24, H25,

H26, H27, H28, G22, G23, G24, G25, G26, G27, G28, F24, F25, F26, F27, F28, E24, E26,

E27, E28

These balls can be connected as desired, including to VSS. For users designing TDA2x

compatible PCB, please refer to TDA2x Data Manual for appropriate requirements.

4.1.1 Unused Balls Connection Requirements

This section describes the connection requirements of the unused and reserved balls.

NOTE

NOTE

NOTE

The following balls are reserved: A27, Y5, Y10, B28, AC1, AC2, AA1, AA2, AB1, AB2, AD14.

These balls must be left unconnected.

8

Terminal Configuration and Functions Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

All unused power supply balls must be supplied with the voltages specified in the

Section 5.4, Recommended Operating Conditions, unless alternative tie-off options are

included in Section 4.4, Signal Descriptions.

Table 4-1. Unused Balls Specific Connection Requirements

BALLS CONNECTION REQUIREMENTS

AE15, AC15, AE14, D20, AD17, AC16, V27, AH25, AE27, AD27,

Y28

E20, D21, E23, C20, C21, V28, F18, AG25, AE28, AD28, Y27, F17,

C25

K14 (vpp) This ball must be left unconnected if unused

AF14 (rtc_iso)

AB17 (rtc_porz)

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

NOTE

These balls must be connected to GND through an external pull

resistor if unused.

These balls must be connected to the corresponding power supply

through an external pull resistor if unused.

This ball should be connected to the corresponding power supply

through an external pull resistor if unused; or can be connected to

F22 (porz) when RTC unused (level translation may be needed)

This ball should be connected to VSS when RTC is unused; or can

be connected to F22 (porz) when RTC unused (level translation may

be needed)

All other unused signal balls with a Pad Configuration register can be left unconnected with

their internal pullup or pulldown resistor enabled.

All other unused signal balls without a Pad Configuration register can be left unconnected.

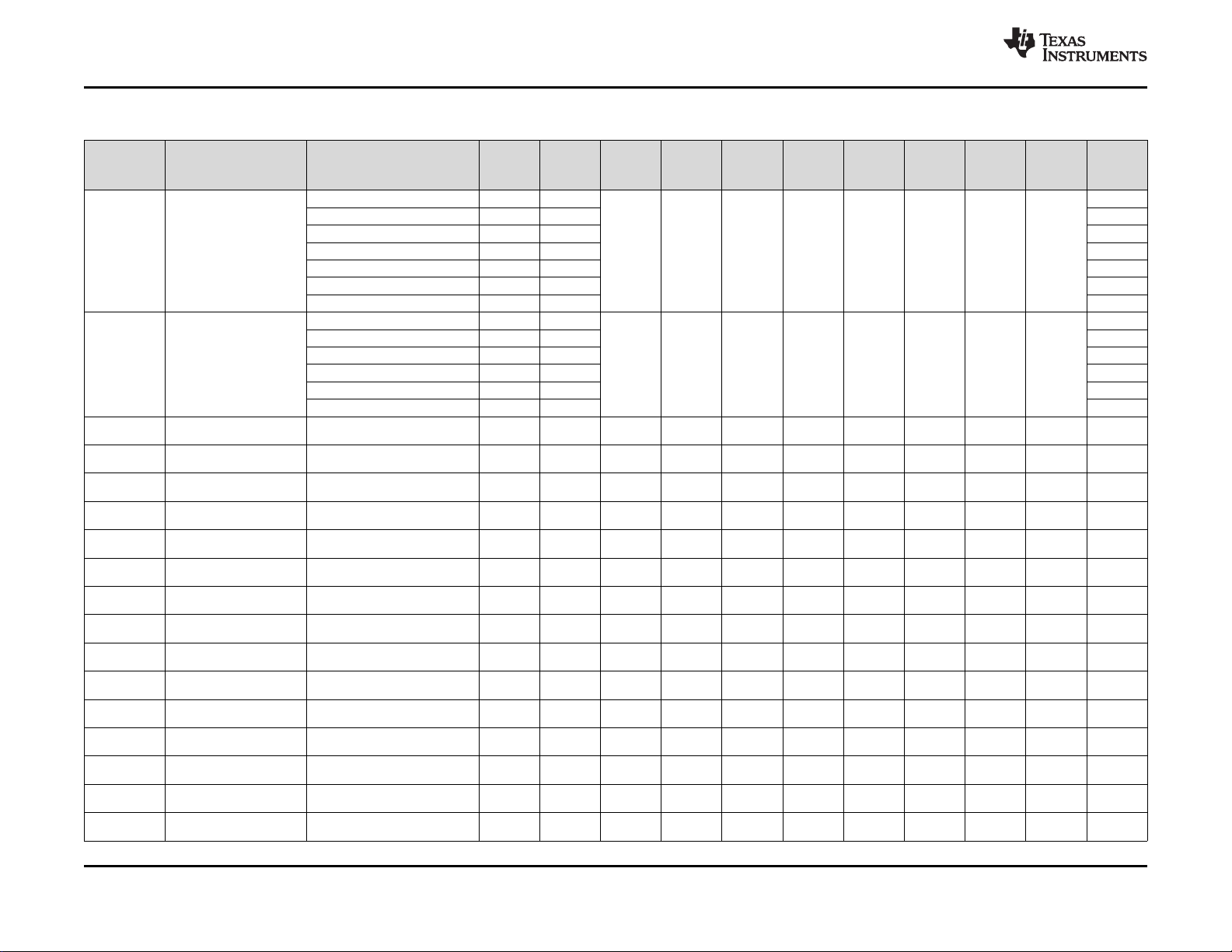

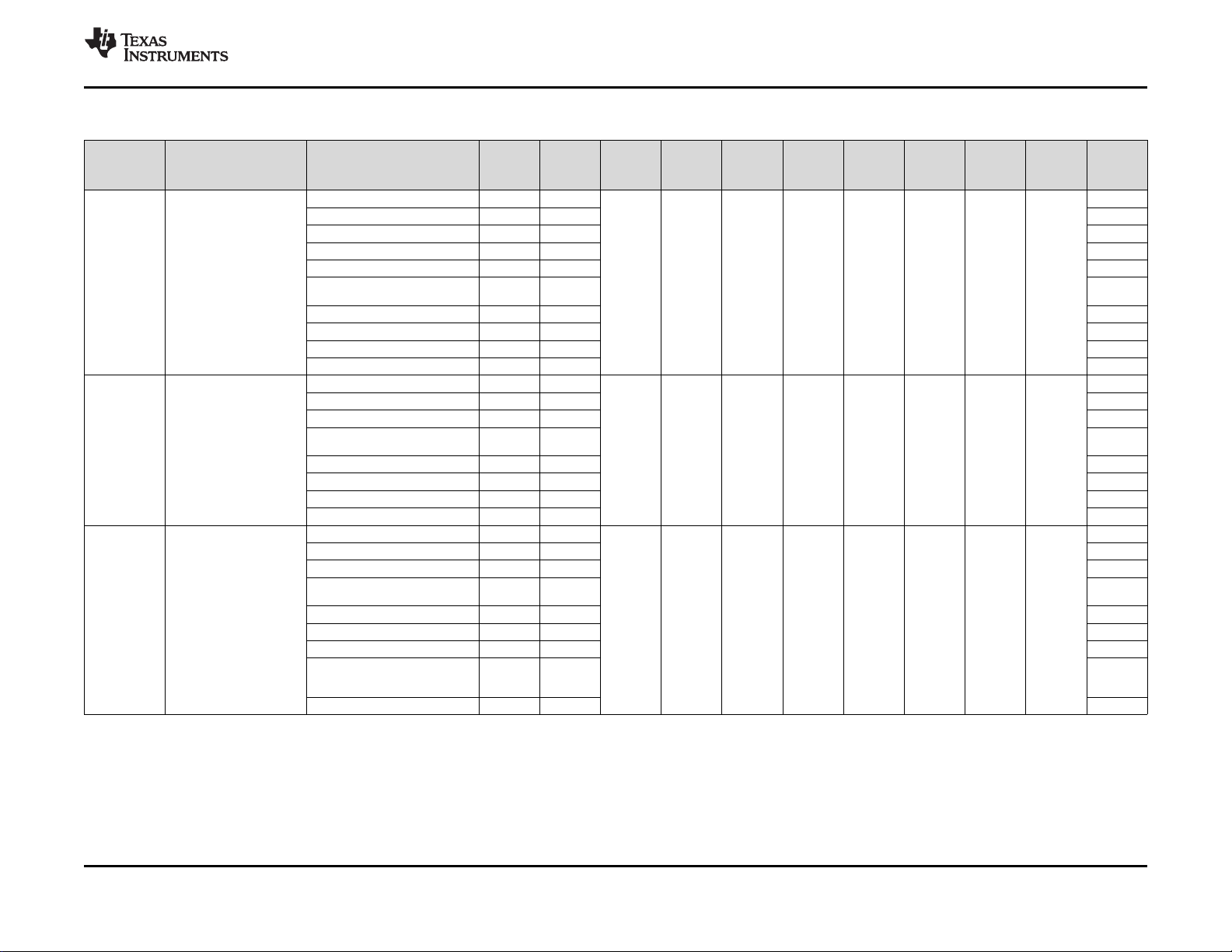

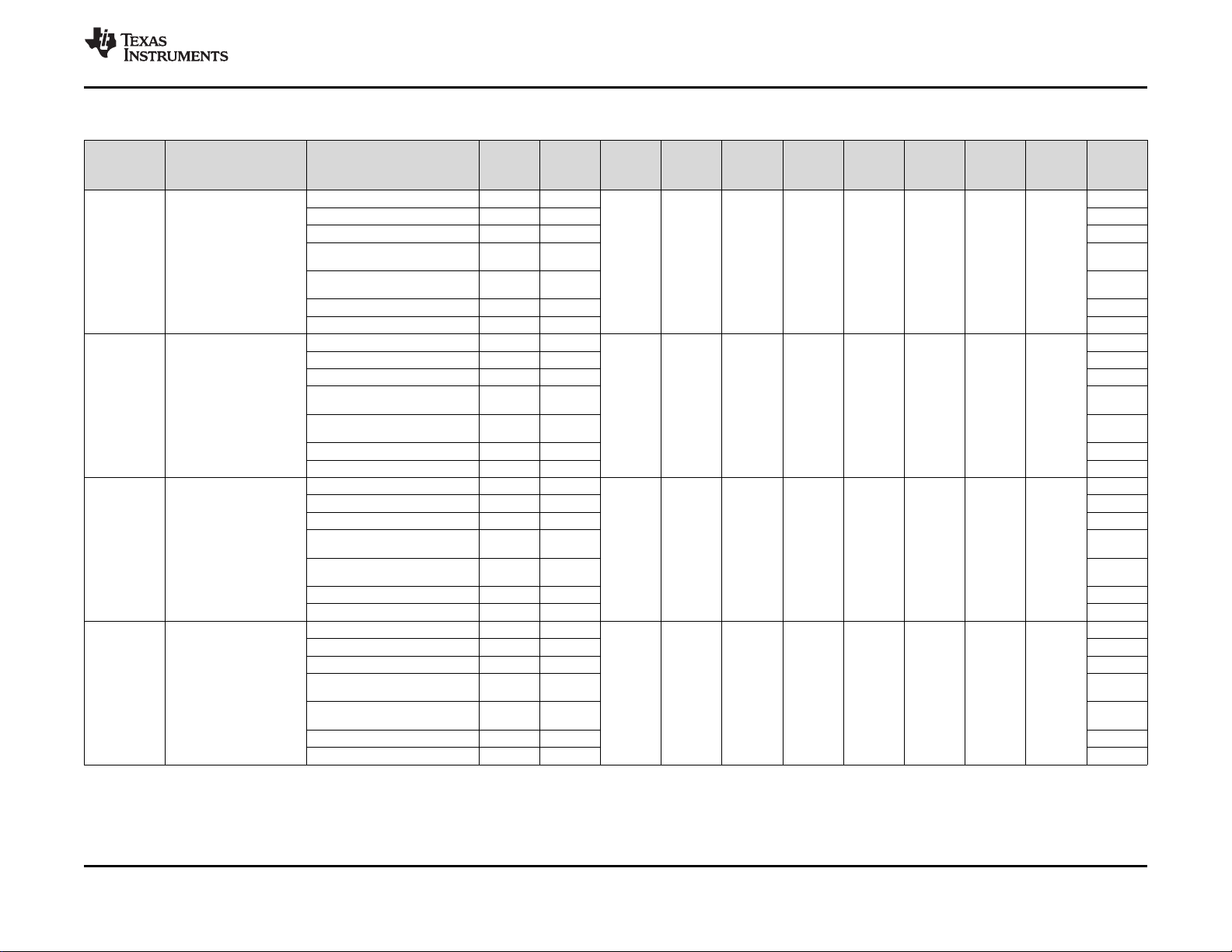

4.2 Ball Characteristics

Table 4-2 describes the terminal characteristics and the signals multiplexed on each ball. The following list

describes the table column headers:

1. BALL NUMBER:This column lists ball numbers on the bottom side associated with each signal on the

bottom.

2. BALL NAME: This column lists mechanical name from package device (name is taken from muxmode

0).

3. SIGNAL NAME:This column lists names of signals multiplexed on each ball (also notice that the name

of the ball is the signal name in muxmode 0).

Table 4-2 does not take into account the subsystem multiplexing signals. Subsystem

multiplexing signals are described in Section 4.4, Signal Descriptions.

NOTE

NOTE

NOTE

NOTE

In driver off mode, the buffer is configured in high-impedance.

Submit Documentation Feedback

Product Folder Links: TDA2EG

Terminal Configuration and FunctionsCopyright © 2016–2019, Texas Instruments Incorporated

9

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

In some cases Table 4-2 may present more than one signal name per muxmode for the

same ball. First signal in the list is the dominant function as selected via

CTRL_CORE_PAD_* register.

All other signals are virtual functions that present alternate multiplexing options. This virtual

functions are controlled via CTRL_CORE_ALT_SELECT_MUX or

CTRL_CORE_VIP_MUX_SELECT register. For more information on how to use these

options, see Pad Configuration Registers section, Control Module chapter in the device TRM.

4. MUXMODE: Multiplexing mode number:

a. MUXMODE 0 is the primary mode; this means that when MUXMODE=0 is set, the function

mapped on the pin corresponds to the name of the pin. The primary muxmode is not necessarily

the default muxmode.

The default mode is the mode at the release of the reset; also see the RESET REL.

MUXMODE column.

b. MUXMODE 1 through 15 are possible muxmodes for alternate functions. On each pin, some

muxmodes are effectively used for alternate functions, while some muxmodes are not used. Only

MUXMODE values which correspond to defined functions should be used.

c. An empty box means Not Applicable.

5. TYPE: Signal type and direction:

– I = Input

– O = Output

– IO = Input or Output

– D = Open drain

– DS = Differential Signaling

– A = Analog

– PWR = Power

– GND = Ground

– CAP = LDO Capacitor

www.ti.com

NOTE

NOTE

10

NOTE

The RX buffer within the pad logic should be disabled on all pins that are not being used as

an input. For more information, see the Control Module / Control Module Functional

Description / PAD Functional Multiplexing and Configuration section in the device TRM.

6. BALL RESET STATE: The state of the terminal at power-on reset:

– drive 0 (OFF): The buffer drives VOL(pulldown or pullup resistor not activated)

– drive 1 (OFF): The buffer drives VOH(pulldown or pullup resistor not activated)

– OFF: High-impedance

– PD: High-impedance with an active pulldown resistor

– PU: High-impedance with an active pullup resistor

– An empty box means Not Applicable

NOTE

Designs that contain pullup or pulldown resistors, either on the board or in attached devices

that oppose internal pullup or pulldown resistors, that are active while the device is held in

reset, must not remain in reset for long periods of time.

7. BALL RESET REL. STATE: The state of the terminal at the deactivation of the rstoutn signal (also

Terminal Configuration and Functions Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

8. BALL RESET REL. MUXMODE: This muxmode is automatically configured at the release of the

9. IO VOLTAGE VALUE: This column describes the IO voltage value (VDDS supply).

10. POWER: The voltage supply that powers the terminal IO buffers.

11. HYS: Indicates if the input buffer is with hysteresis:

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

mapped to the PRCM SYS_WARM_OUT_RST signal)

– drive 0 (OFF): The buffer drives VOL(pulldown or pullup resistor not activated)

– drive clk (OFF): The buffer drives a toggling clock (pulldown or pullup resistor not activated)

– drive 1 (OFF): The buffer drives VOH(pulldown or pullup resistor not activated)

– OFF: High-impedance

– PD: High-impedance with an active pulldown resistor

– PU: High-impedance with an active pullup resistor

– An empty box means Not Applicable

NOTE

For more information on the CORE_PWRON_RET_RST reset signal and its reset sources,

see Power, Reset, and Clock Management chapter in the device TRM.

rstoutn signal (also mapped to the PRCM SYS_WARM_OUT_RST signal).

An empty box means Not Applicable.

An empty box means Not Applicable.

An empty box means Not Applicable.

– Yes: With hysteresis

– No: Without hysteresis

– An empty box: Not Applicable

NOTE

For more information, see the hysteresis values in Section 5.7, Electrical Characteristics.

12. BUFFER TYPE: Drive strength of the associated output buffer.

An empty box means Not Applicable.

NOTE

For programmable buffer strength:

– The default value is given in Table 4-2.

– A note describes all possible values according to the selected muxmode.

13. PULLUP / PULLDOWN TYPE: Denotes the presence of an internal pullup or pulldown resistor.

Pullup and pulldown resistors can be enabled or disabled via software.

– PU: Internal pullup

– PD: Internal pulldown

– PU/PD: Internal pullup and pulldown

– PUx/PDy: Programmable internal pullup and pulldown

– PDy: Programmable internal pulldown

– An empty box means No pull

NOTE

Internal pullup or pulldown resistors must be disabled when opposed by an external pullup or

pulldown resistor on the board or within an attached device.

14. DSIS: The deselected input state (DSIS) indicates the state driven on the peripheral input (logic "0" or

logic "1") when the peripheral pin function is not selected by any of the PINCNTLx registers.

– 0: Logic 0 driven on the peripheral's input signal port.

Terminal Configuration and FunctionsCopyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

11

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

– 1: Logic 1 driven on the peripheral's input signal port.

– blank: Pin state driven on the peripheral's input signal port.

Configuring two pins to the same input signal is not supported as it can yield unexpected

results. This can be easily prevented with the proper software configuration (Hi-Z mode is not

an input signal).

When a pad is set into a multiplexing mode which is not defined by pin multiplexing, that

pad’s behavior is undefined. This should be avoided.

Some of the EMIF1 signals have an additional state change at the release of porz. The state

that the signals change to at the release of porz is as follows:

drive 0 (OFF) for: ddr1_csn0, ddr1_ck, ddr1_nck, ddr1_casn, ddr1_rasn, ddr1_wen,

ddr1_ba[2:0], ddr1_a[15:0].

OFF for: ddr1_ecc_d[7:0], ddr1_dqm[3:0], ddr1_dqm_ecc, ddr1_dqs[3:0], ddr1_dqsn[3:0],

ddr1_dqs_ecc, ddr1_dqsn_ecc, ddr1_d[31:0].

www.ti.com

NOTE

NOTE

NOTE

NOTE

Dual rank support is not available on this device, but signal names are retained for

consistency with the TDA2xx family of devices.

12

Terminal Configuration and Functions Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

BALL

(1)

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

CSI2

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

K9 cap_vbbldo_dsp cap_vbbldo_dsp CAP

Y14 cap_vbbldo_gpu cap_vbbldo_gpu CAP

J10 cap_vbbldo_iva cap_vbbldo_iva CAP

J16 cap_vbbldo_mpu cap_vbbldo_mpu CAP

T20 cap_vddram_core1 cap_vddram_core1 CAP

L9 cap_vddram_core3 cap_vddram_core3 CAP

J19 cap_vddram_core4 cap_vddram_core4 CAP

J9 cap_vddram_dsp cap_vddram_dsp CAP

Y13 cap_vddram_gpu cap_vddram_gpu CAP

K16 cap_vddram_iva cap_vddram_iva CAP

K19 cap_vddram_mpu cap_vddram_mpu CAP

AE1 csi2_0_dx0 csi2_0_dx0 0 I 1.8 vdda_csi Yes LVCMOS

AF1 csi2_0_dx1 csi2_0_dx1 0 I 1.8 vdda_csi Yes LVCMOS

AF2 csi2_0_dx2 csi2_0_dx2 0 I 1.8 vdda_csi Yes LVCMOS

AH4 csi2_0_dx3 csi2_0_dx3 0 I 1.8 vdda_csi Yes LVCMOS

AH3 csi2_0_dx4 csi2_0_dx4 0 I 1.8 vdda_csi Yes LVCMOS

AD2 csi2_0_dy0 csi2_0_dy0 0 I 1.8 vdda_csi Yes LVCMOS

AE2 csi2_0_dy1 csi2_0_dy1 0 I 1.8 vdda_csi Yes LVCMOS

AF3 csi2_0_dy2 csi2_0_dy2 0 I 1.8 vdda_csi Yes LVCMOS

AG4 csi2_0_dy3 csi2_0_dy3 0 I 1.8 vdda_csi Yes LVCMOS

AG3 csi2_0_dy4 csi2_0_dy4 0 I 1.8 vdda_csi Yes LVCMOS

AG5 csi2_1_dx0 csi2_1_dx0 0 I 1.8 vdda_csi Yes LVCMOS

AG6 csi2_1_dx1 csi2_1_dx1 0 I 1.8 vdda_csi Yes LVCMOS

AH7 csi2_1_dx2 csi2_1_dx2 0 I 1.8 vdda_csi Yes LVCMOS

AH5 csi2_1_dy0 csi2_1_dy0 0 I 1.8 vdda_csi Yes LVCMOS

AH6 csi2_1_dy1 csi2_1_dy1 0 I 1.8 vdda_csi Yes LVCMOS

AG7 csi2_1_dy2 csi2_1_dy2 0 I 1.8 vdda_csi Yes LVCMOS

BALL NAME [2] SIGNAL NAME [3]

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

RESET REL.

STATE [7]

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

13

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

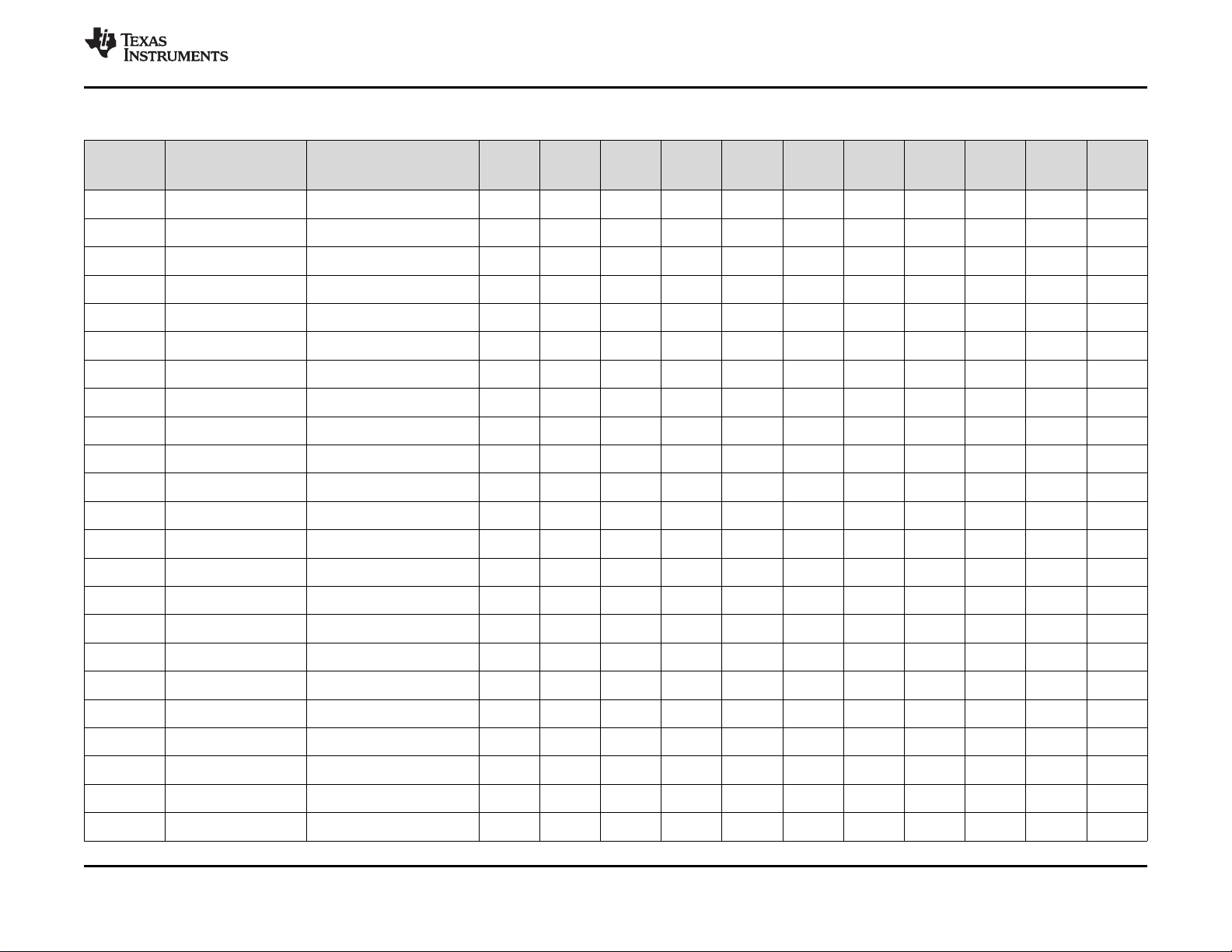

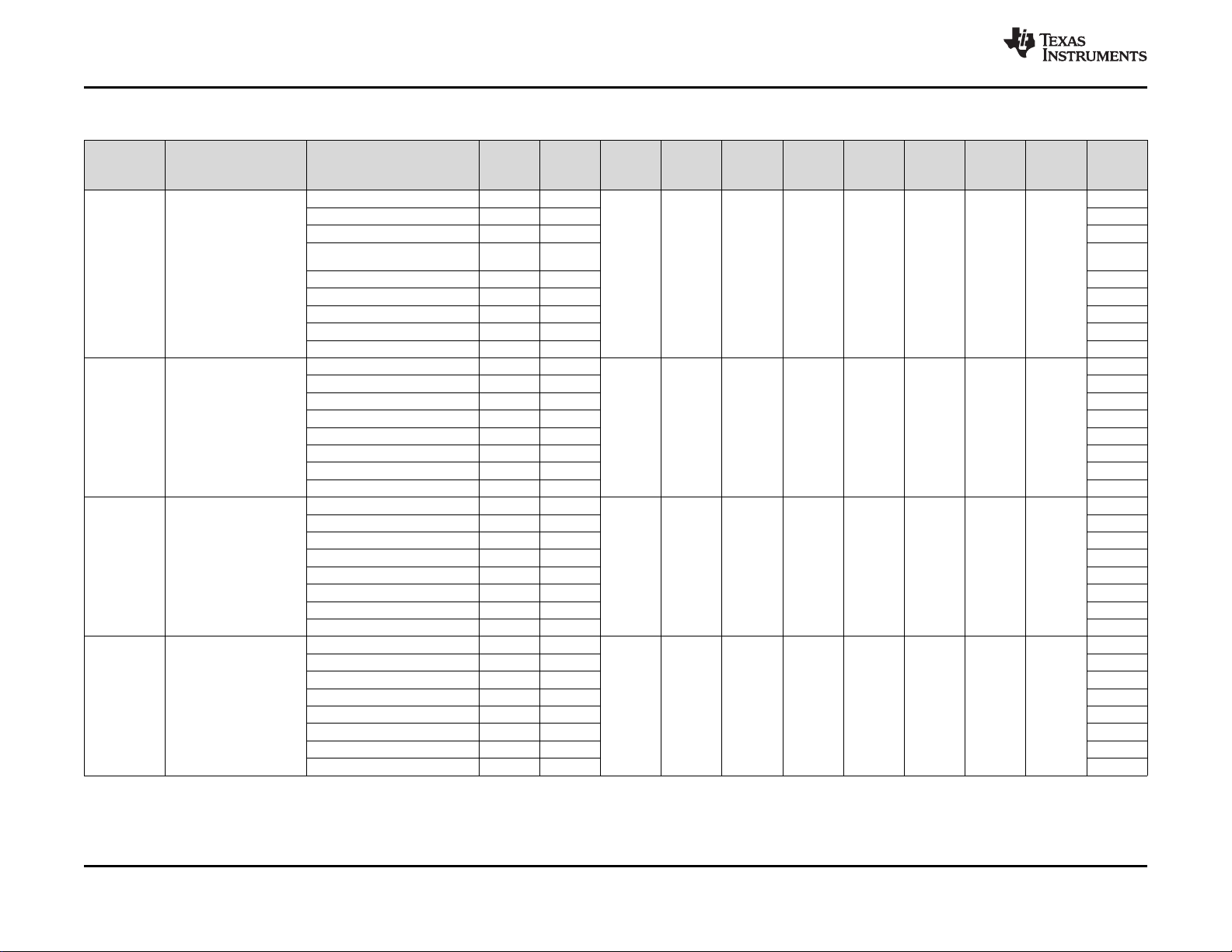

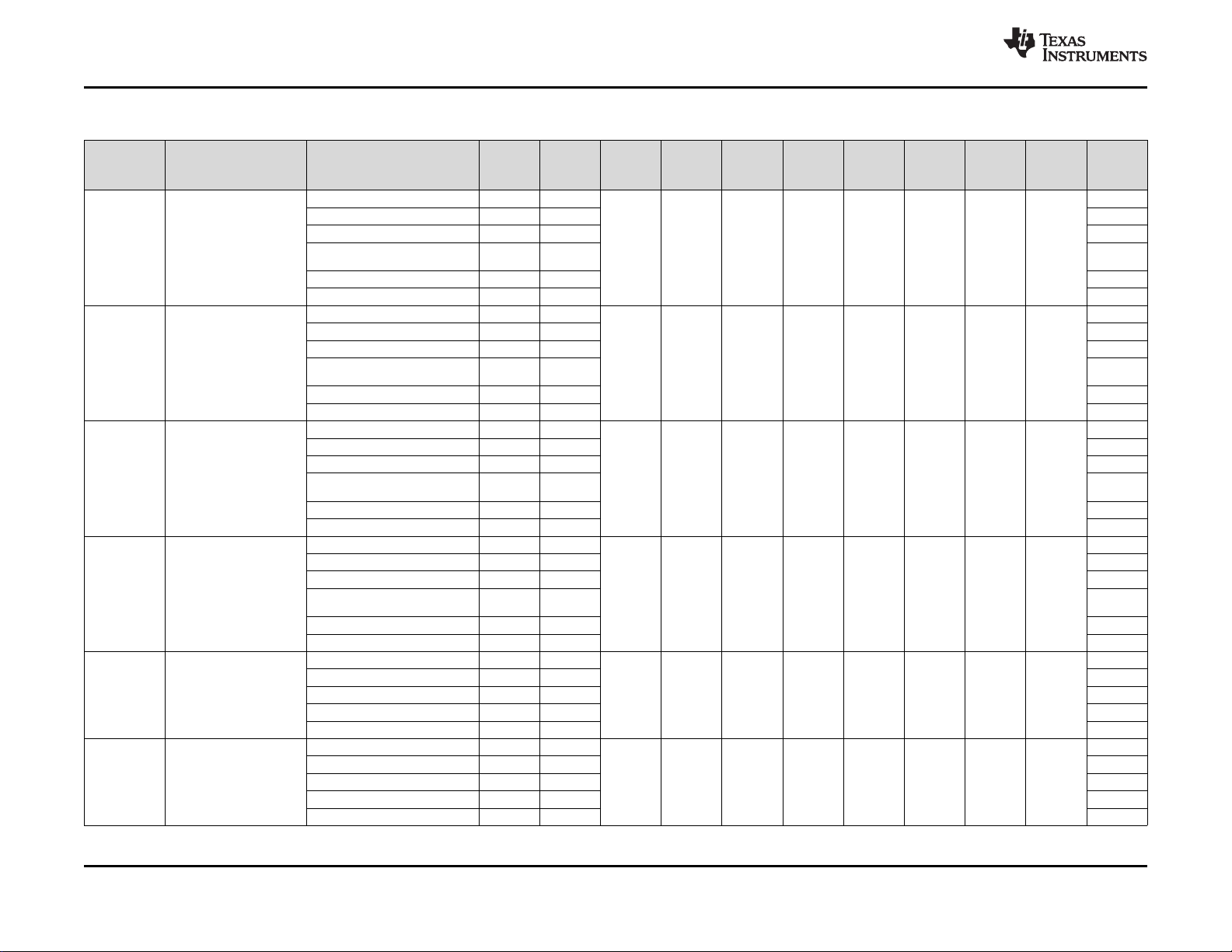

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

G19 dcan1_rx dcan1_rx 0 IO PU PU 15 1.8/3.3 vddshv3 Yes Dual Voltage

G20 dcan1_tx dcan1_tx 0 IO PU PU 15 1.8/3.3 vddshv3 Yes Dual Voltage

AD20 ddr1_a0 ddr1_a0 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC19 ddr1_a1 ddr1_a1 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC20 ddr1_a2 ddr1_a2 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AB19 ddr1_a3 ddr1_a3 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF21 ddr1_a4 ddr1_a4 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AH22 ddr1_a5 ddr1_a5 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AG23 ddr1_a6 ddr1_a6 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AE21 ddr1_a7 ddr1_a7 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF22 ddr1_a8 ddr1_a8 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AE22 ddr1_a9 ddr1_a9 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AD21 ddr1_a10 ddr1_a10 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AD22 ddr1_a11 ddr1_a11 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC21 ddr1_a12 ddr1_a12 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF18 ddr1_a13 ddr1_a13 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AE17 ddr1_a14 ddr1_a14 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

BALL NAME [2] SIGNAL NAME [3]

uart8_txd 2 O

mmc2_sdwp 3 I 0

sata1_led 4 O

hdmi1_cec 6 IO

gpio1_15 14 IO

Driver off 15 I

uart8_rxd 2 I 1

mmc2_sdcd 3 I 1

hdmi1_hpd 6 IO

gpio1_14 14 IO

Driver off 15 I

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

PULL

UP/DOWN

TYPE [13]

PU/PD 1

PU/PD 1

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

DSIS [14]

14

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

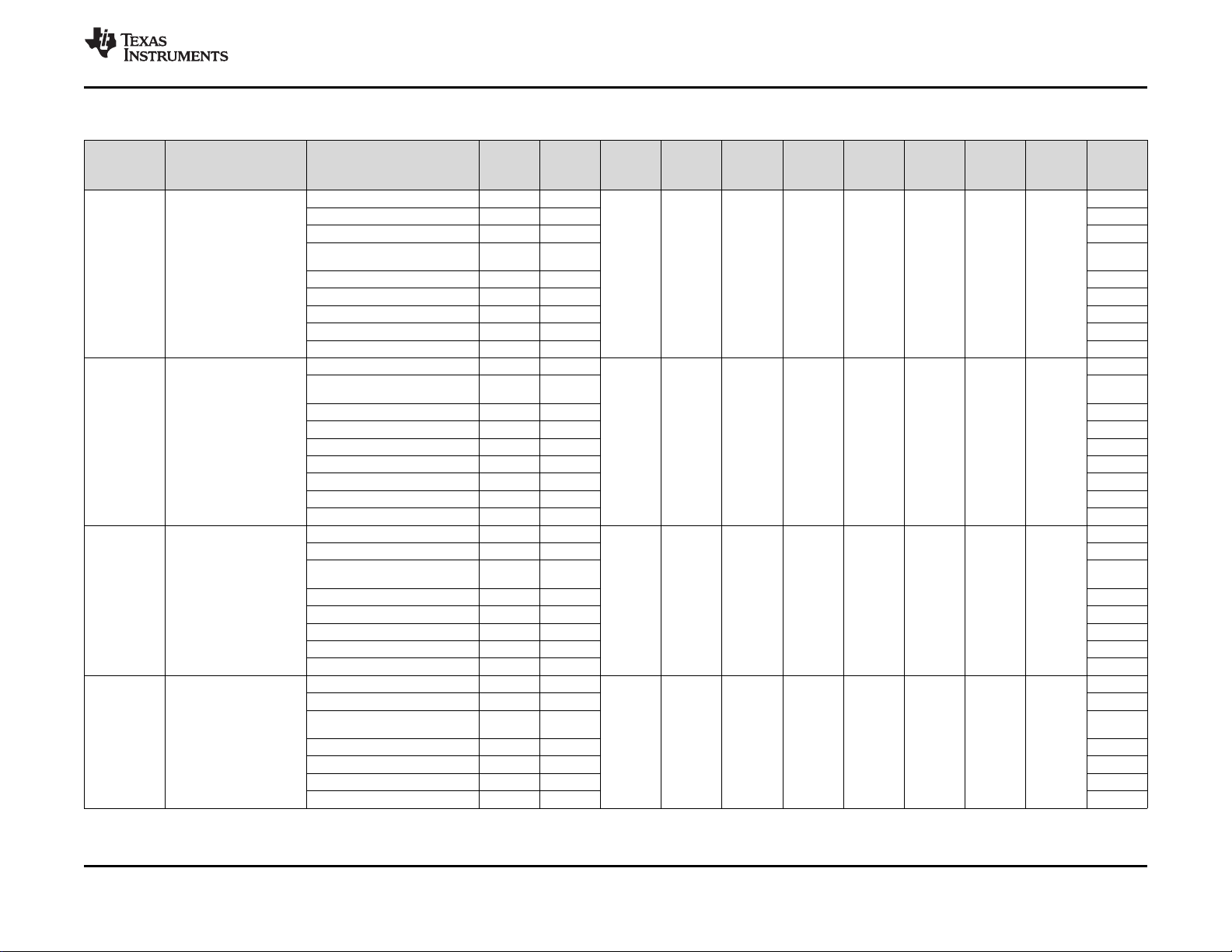

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

AD18 ddr1_a15 ddr1_a15 0 O PD drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF17 ddr1_ba0 ddr1_ba0 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AE18 ddr1_ba1 ddr1_ba1 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AB18 ddr1_ba2 ddr1_ba2 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC18 ddr1_casn ddr1_casn 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AG24 ddr1_ck ddr1_ck 0 O PD drive 0 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AG22 ddr1_cke ddr1_cke 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AH23 ddr1_csn0 ddr1_csn0 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AB16 ddr1_csn1 ddr1_csn1 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF25 ddr1_d0 ddr1_d0 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AF26 ddr1_d1 ddr1_d1 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AG26 ddr1_d2 ddr1_d2 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AH26 ddr1_d3 ddr1_d3 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AF24 ddr1_d4 ddr1_d4 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AE24 ddr1_d5 ddr1_d5 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AF23 ddr1_d6 ddr1_d6 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AE23 ddr1_d7 ddr1_d7 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AC23 ddr1_d8 ddr1_d8 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AF27 ddr1_d9 ddr1_d9 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AG27 ddr1_d10 ddr1_d10 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AF28 ddr1_d11 ddr1_d11 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AE26 ddr1_d12 ddr1_d12 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AC25 ddr1_d13 ddr1_d13 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

BALL NAME [2] SIGNAL NAME [3]

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

PULL

UP/DOWN

TYPE [13]

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

15

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

AC24 ddr1_d14 ddr1_d14 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AD25 ddr1_d15 ddr1_d15 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

V20 ddr1_d16 ddr1_d16 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

W20 ddr1_d17 ddr1_d17 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AB28 ddr1_d18 ddr1_d18 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AC28 ddr1_d19 ddr1_d19 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AC27 ddr1_d20 ddr1_d20 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y19 ddr1_d21 ddr1_d21 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AB27 ddr1_d22 ddr1_d22 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y20 ddr1_d23 ddr1_d23 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AA23 ddr1_d24 ddr1_d24 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y22 ddr1_d25 ddr1_d25 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y23 ddr1_d26 ddr1_d26 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AA24 ddr1_d27 ddr1_d27 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y24 ddr1_d28 ddr1_d28 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AA26 ddr1_d29 ddr1_d29 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AA25 ddr1_d30 ddr1_d30 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AA28 ddr1_d31 ddr1_d31 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AD23 ddr1_dqm0 ddr1_dqm0 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AB23 ddr1_dqm1 ddr1_dqm1 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC26 ddr1_dqm2 ddr1_dqm2 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AA27 ddr1_dqm3 ddr1_dqm3 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

V26 ddr1_dqm_ecc ddr1_dqm_ecc 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

BALL NAME [2] SIGNAL NAME [3]

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

PULL

UP/DOWN

TYPE [13]

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

DSIS [14]

16

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

AH25 ddr1_dqs0 ddr1_dqs0 0 IO PD PD 1.35/1.5 vdds_ddr1 LVCMOS

AE27 ddr1_dqs1 ddr1_dqs1 0 IO PD PD 1.35/1.5 vdds_ddr1 LVCMOS

AD27 ddr1_dqs2 ddr1_dqs2 0 IO PD PD 1.35/1.5 vdds_ddr1 LVCMOS

Y28 ddr1_dqs3 ddr1_dqs3 0 IO PD PD 1.35/1.5 vdds_ddr1 LVCMOS

AG25 ddr1_dqsn0 ddr1_dqsn0 0 IO PU PU 1.35/1.5 vdds_ddr1 LVCMOS

AE28 ddr1_dqsn1 ddr1_dqsn1 0 IO PU PU 1.35/1.5 vdds_ddr1 LVCMOS

AD28 ddr1_dqsn2 ddr1_dqsn2 0 IO PU PU 1.35/1.5 vdds_ddr1 LVCMOS

Y27 ddr1_dqsn3 ddr1_dqsn3 0 IO PU PU 1.35/1.5 vdds_ddr1 LVCMOS

V28 ddr1_dqsn_ecc ddr1_dqsn_ecc 0 IO PU PU 1.35/1.5 vdds_ddr1 LVCMOS

V27 ddr1_dqs_ecc ddr1_dqs_ecc 0 IO PD PD 1.35/1.5 vdds_ddr1 LVCMOS

W22 ddr1_ecc_d0 ddr1_ecc_d0 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

V23 ddr1_ecc_d1 ddr1_ecc_d1 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

W19 ddr1_ecc_d2 ddr1_ecc_d2 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

W23 ddr1_ecc_d3 ddr1_ecc_d3 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y25 ddr1_ecc_d4 ddr1_ecc_d4 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

V24 ddr1_ecc_d5 ddr1_ecc_d5 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

V25 ddr1_ecc_d6 ddr1_ecc_d6 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

Y26 ddr1_ecc_d7 ddr1_ecc_d7 0 IO PD PD 1.35/1.5 vdds_ddr1 No LVCMOS

AH24 ddr1_nck ddr1_nck 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AE20 ddr1_odt0 ddr1_odt0 0 O PD drive 0 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AC17 ddr1_odt1 ddr1_odt1 0 O PD drive 0 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AF20 ddr1_rasn ddr1_rasn 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AG21 ddr1_rst ddr1_rst 0 O PD drive 0 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

BALL NAME [2] SIGNAL NAME [3]

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

DDR

PULL

UP/DOWN

TYPE [13]

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

PUx/PDy

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

17

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

Y18 ddr1_vref0 ddr1_vref0 0 PWR OFF drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

AH21 ddr1_wen ddr1_wen 0 O PU drive 1 (OFF) 1.35/1.5 vdds_ddr1 No LVCMOS

G21 emu0 emu0 0 IO PU PU 0 1.8/3.3 vddshv3 Yes Dual Voltage

D24 emu1 emu1 0 IO PU PU 0 1.8/3.3 vddshv3 Yes Dual Voltage

AC5 gpio6_10 gpio6_10 0 IO PU PU 15 1.8/3.3 vddshv7 Yes Dual Voltage

AB4 gpio6_11 gpio6_11 0 IO PU PU 15 1.8/3.3 vddshv7 Yes Dual Voltage

E21 gpio6_14 gpio6_14 0 IO PU PU 15 1.8/3.3 vddshv3 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

gpio8_30 14 IO

gpio8_31 14 IO

mdio_mclk 1 O 1

i2c3_sda 2 IO 1

usb3_ulpi_d7 3 IO 0

vin2b_hsync1 4 I

vin1a_clk0 9 I 0

ehrpwm2A 10 O

gpio6_10 14 IO

Driver off 15 I

mdio_d 1 IO 1

i2c3_scl 2 IO 1

usb3_ulpi_d6 3 IO 0

vin2b_vsync1 4 I

vin1a_de0 9 I 0

ehrpwm2B 10 O

gpio6_11 14 IO

Driver off 15 I

mcasp1_axr8 1 IO 0

dcan2_tx 2 IO 1

uart10_rxd 3 I 1

vout2_hsync 6 O

vin2a_hsync0

vin1a_hsync0

i2c3_sda 9 IO 1

timer1 10 IO

gpio6_14 14 IO

Driver off 15 I

MUXMODE

[4]

8 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

DDR

DDR

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PUx/PDy

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

18

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

F20 gpio6_15 gpio6_15 0 IO PU PU 15 1.8/3.3 vddshv3 Yes Dual Voltage

F21 gpio6_16 gpio6_16 0 IO PU PU 15 1.8/3.3 vddshv3 Yes Dual Voltage

R6 gpmc_a0 gpmc_a0 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

mcasp1_axr9 1 IO 0

dcan2_rx 2 IO 1

uart10_txd 3 O

vout2_vsync 6 O

vin2a_vsync0

vin1a_vsync0

i2c3_scl 9 IO 1

timer2 10 IO

gpio6_15 14 IO

Driver off 15 I

mcasp1_axr10 1 IO 0

vout2_fld 6 O

vin2a_fld0

vin1a_fld0

clkout1 9 O

timer3 10 IO

gpio6_16 14 IO

Driver off 15 I

vin1a_d16 2 I 0

vout3_d16 3 O

vin2a_d0

vin1a_d0

vin1b_d0 6 I 0

i2c4_scl 7 IO 1

uart5_rxd 8 I 1

gpio7_3

gpmc_a26

gpmc_a16

Driver off 15 I

MUXMODE

[4]

8 I

8 I

4 I

14 IO

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

19

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

T9 gpmc_a1 gpmc_a1 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

T6 gpmc_a2 gpmc_a2 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

T7 gpmc_a3 gpmc_a3 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

vin1a_d17 2 I 0

vout3_d17 3 O

vin2a_d1

vin1a_d1

vin1b_d1 6 I 0

i2c4_sda 7 IO 1

uart5_txd 8 O

gpio7_4 14 IO

Driver off 15 I

vin1a_d18 2 I 0

vout3_d18 3 O

vin2a_d2

vin1a_d2

vin1b_d2 6 I 0

uart7_rxd 7 I 1

uart5_ctsn 8 I 1

gpio7_5 14 IO

Driver off 15 I

qspi1_cs2 1 O 1

vin1a_d19 2 I 0

vout3_d19 3 O

vin2a_d3

vin1a_d3

vin1b_d3 6 I 0

uart7_txd 7 O

uart5_rtsn 8 O

gpio7_6 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

4 I

4 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

DSIS [14]

20

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

P6 gpmc_a4 gpmc_a4 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

R9 gpmc_a5 gpmc_a5 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

R5 gpmc_a6 gpmc_a6 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

qspi1_cs3 1 O 1

vin1a_d20 2 I 0

vout3_d20 3 O

vin2a_d4

vin1a_d4

vin1b_d4 6 I 0

i2c5_scl 7 IO 1

uart6_rxd 8 I 1

gpio1_26 14 IO

Driver off 15 I

vin1a_d21 2 I 0

vout3_d21 3 O

vin2a_d5

vin1a_d5

vin1b_d5 6 I 0

i2c5_sda 7 IO 1

uart6_txd 8 O

gpio1_27 14 IO

Driver off 15 I

vin1a_d22 2 I 0

vout3_d22 3 O

vin2a_d6

vin1a_d6

vin1b_d6 6 I 0

uart8_rxd 7 I 1

uart6_ctsn 8 I 1

gpio1_28 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

4 I

4 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

21

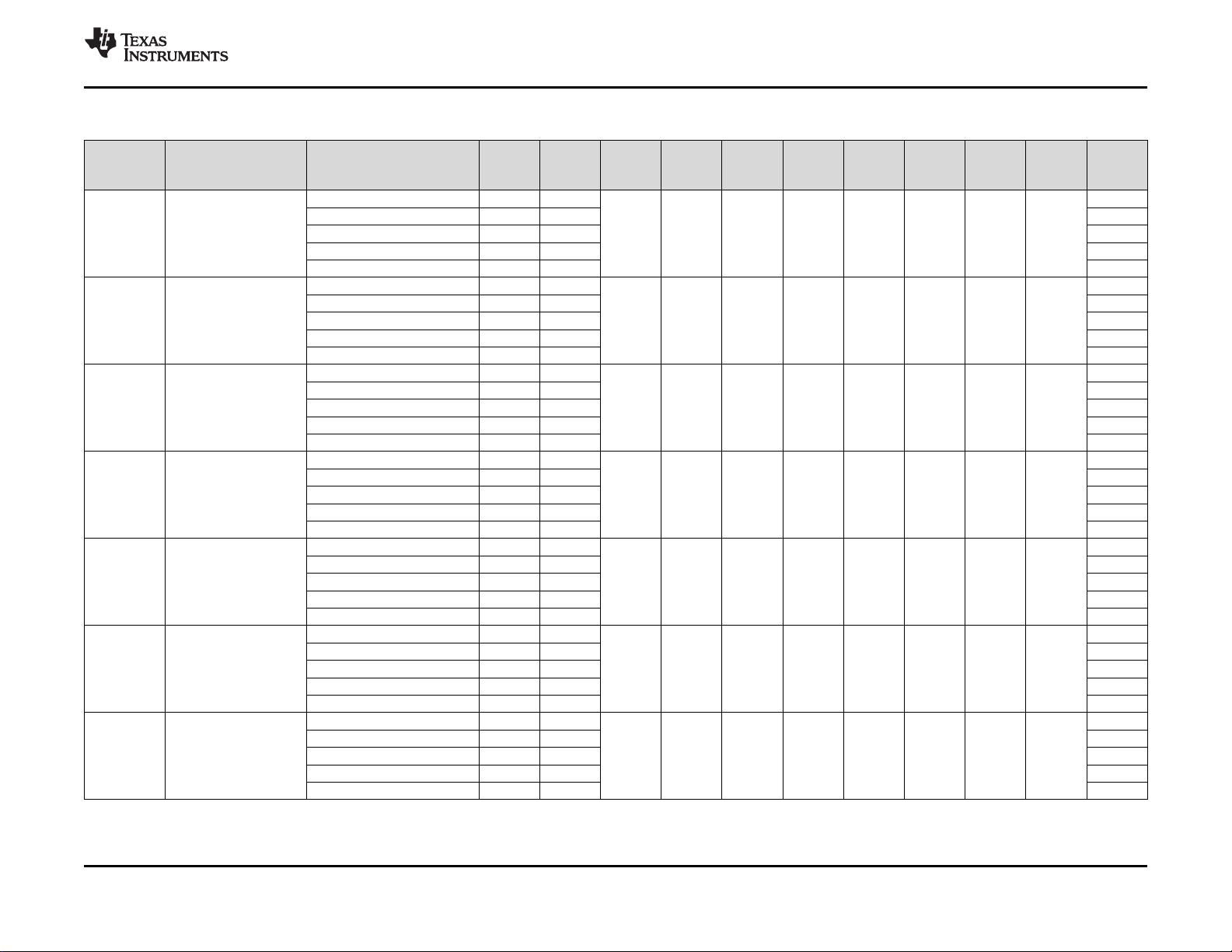

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

P5 gpmc_a7 gpmc_a7 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

N7 gpmc_a8 gpmc_a8 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

R4 gpmc_a9 gpmc_a9 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

N9 gpmc_a10 gpmc_a10 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

vin1a_d23 2 I 0

vout3_d23 3 O

vin2a_d7

vin1a_d7

vin1b_d7 6 I 0

uart8_txd 7 O

uart6_rtsn 8 O

gpio1_29 14 IO

Driver off 15 I

vin1a_hsync0 2 I 0

vout3_hsync 3 O

vin1b_hsync1 6 I 0

timer12 7 IO

spi4_sclk 8 IO 0

gpio1_30 14 IO

Driver off 15 I

vin1a_vsync0 2 I 0

vout3_vsync 3 O

vin1b_vsync1 6 I 0

timer11 7 IO

spi4_d1 8 IO 0

gpio1_31 14 IO

Driver off 15 I

vin1a_de0 2 I 0

vout3_de 3 O

vin1b_clk1 6 I 0

timer10 7 IO

spi4_d0 8 IO 0

gpio2_0 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

22

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

P9 gpmc_a11 gpmc_a11 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

P4 gpmc_a12 gpmc_a12 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

R3 gpmc_a13 gpmc_a13 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

T2 gpmc_a14 gpmc_a14 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

vin1a_fld0 2 I 0

vout3_fld 3 O

vin2a_fld0

vin1a_fld0

vin1b_de1 6 I 0

timer9 7 IO

spi4_cs0 8 IO 1

gpio2_1 14 IO

Driver off 15 I

vin2a_clk0

vin1a_clk0

gpmc_a0 5 O

vin1b_fld1 6 I 0

timer8 7 IO

spi4_cs1 8 IO 1

dma_evt1 9 I 0

gpio2_2 14 IO

Driver off 15 I

qspi1_rtclk 1 I 0

vin2a_hsync0

vin1a_hsync0

timer7 7 IO

spi4_cs2 8 IO 1

dma_evt2 9 I 0

gpio2_3 14 IO

Driver off 15 I

qspi1_d3 1 IO 0

vin2a_vsync0

vin1a_vsync0

timer6 7 IO

spi4_cs3 8 IO 1

gpio2_4 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

4 I

4 I

4 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

23

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

U2 gpmc_a15 gpmc_a15 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

U1 gpmc_a16 gpmc_a16 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

P3 gpmc_a17 gpmc_a17 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

R2 gpmc_a18 gpmc_a18 0 O PD PD 15 1.8/3.3 vddshv10 Yes Dual Voltage

(9)

K7

BALL NAME [2] SIGNAL NAME [3]

qspi1_d2 1 IO 0

vin2a_d8

vin1a_d8

timer5 7 IO

gpio2_5 14 IO

Driver off 15 I

qspi1_d0 1 IO 0

vin2a_d9

vin1a_d9

gpio2_6 14 IO

Driver off 15 I

qspi1_d1 1 IO 0

vin2a_d10

vin1a_d10

gpio2_7 14 IO

Driver off 15 I

qspi1_sclk 1 IO

vin2a_d11

vin1a_d11

gpio2_8 14 IO

Driver off 15 I

gpmc_a19 gpmc_a19 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat4 1 IO 1

gpmc_a13 2 O

vin2a_d12

vin1a_d12

vin2b_d0

vin1b_d0

gpio2_9 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

4 I

4 I

4 I

4 I

6 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

24

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

(9)

M7

(9)

J5

(9)

K6

J7 gpmc_a23 gpmc_a23 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

gpmc_a20 gpmc_a20 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat5 1 IO 1

gpmc_a14 2 O

vin2a_d13

vin1a_d13

vin2b_d1

vin1b_d1

gpio2_10 14 IO

Driver off 15 I

gpmc_a21 gpmc_a21 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat6 1 IO 1

gpmc_a15 2 O

vin2a_d14

vin1a_d14

vin2b_d2

vin1b_d2

gpio2_11 14 IO

Driver off 15 I

gpmc_a22 gpmc_a22 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat7 1 IO 1

gpmc_a16 2 O

vin2a_d15

vin1a_d15

vin2b_d3

vin1b_d3

gpio2_12 14 IO

Driver off 15 I

mmc2_clk 1 IO 1

gpmc_a17 2 O

vin2a_fld0

vin1a_fld0

vin2b_d4

vin1b_d4

gpio2_13 14 IO

Driver off 15 I

MUXMODE

[4]

4 I

6 I

4 I

6 I

4 I

6 I

4 I

6 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

25

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

(9)

J4

(9)

J6

(9)

H4

(9)

H5

M6 gpmc_ad0 gpmc_ad0 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

M2 gpmc_ad1 gpmc_ad1 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

gpmc_a24 gpmc_a24 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat0 1 IO 1

gpmc_a18 2 O

vin2b_d5

vin1b_d5

gpio2_14 14 IO

Driver off 15 I

gpmc_a25 gpmc_a25 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat1 1 IO 1

gpmc_a19 2 O

vin2b_d6

vin1b_d6

gpio2_15 14 IO

Driver off 15 I

gpmc_a26 gpmc_a26 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat2 1 IO 1

gpmc_a20 2 O

vin2b_d7

vin1b_d7

gpio2_16 14 IO

Driver off 15 I

gpmc_a27 gpmc_a27 0 O PD PD 15 1.8/3.3 vddshv11 Yes Dual Voltage

mmc2_dat3 1 IO 1

gpmc_a21 2 O

vin2b_hsync1

vin1b_hsync1

gpio2_17 14 IO

Driver off 15 I

vin1a_d0 2 I 0

vout3_d0 3 O

gpio1_6 14 IO

sysboot0 15 I

vin1a_d1 2 I 0

vout3_d1 3 O

gpio1_7 14 IO

sysboot1 15 I

MUXMODE

[4]

6 I

6 I

6 I

6 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

PU/PD

PU/PD 0

PU/PD 0

DSIS [14]

26

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

L5 gpmc_ad2 gpmc_ad2 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

M1 gpmc_ad3 gpmc_ad3 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

L6 gpmc_ad4 gpmc_ad4 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

L4 gpmc_ad5 gpmc_ad5 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

L3 gpmc_ad6 gpmc_ad6 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

L2 gpmc_ad7 gpmc_ad7 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

L1 gpmc_ad8 gpmc_ad8 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

vin1a_d2 2 I 0

vout3_d2 3 O

gpio1_8 14 IO

sysboot2 15 I

vin1a_d3 2 I 0

vout3_d3 3 O

gpio1_9 14 IO

sysboot3 15 I

vin1a_d4 2 I 0

vout3_d4 3 O

gpio1_10 14 IO

sysboot4 15 I

vin1a_d5 2 I 0

vout3_d5 3 O

gpio1_11 14 IO

sysboot5 15 I

vin1a_d6 2 I 0

vout3_d6 3 O

gpio1_12 14 IO

sysboot6 15 I

vin1a_d7 2 I 0

vout3_d7 3 O

gpio1_13 14 IO

sysboot7 15 I

vin1a_d8 2 I 0

vout3_d8 3 O

gpio7_18 14 IO

sysboot8 15 I

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

27

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

K2 gpmc_ad9 gpmc_ad9 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

J1 gpmc_ad10 gpmc_ad10 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

J2 gpmc_ad11 gpmc_ad11 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

H1 gpmc_ad12 gpmc_ad12 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

J3 gpmc_ad13 gpmc_ad13 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

H2 gpmc_ad14 gpmc_ad14 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

H3 gpmc_ad15 gpmc_ad15 0 IO OFF OFF 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

vin1a_d9 2 I 0

vout3_d9 3 O

gpio7_19 14 IO

sysboot9 15 I

vin1a_d10 2 I 0

vout3_d10 3 O

gpio7_28 14 IO

sysboot10 15 I

vin1a_d11 2 I 0

vout3_d11 3 O

gpio7_29 14 IO

sysboot11 15 I

vin1a_d12 2 I 0

vout3_d12 3 O

gpio1_18 14 IO

sysboot12 15 I

vin1a_d13 2 I 0

vout3_d13 3 O

gpio1_19 14 IO

sysboot13 15 I

vin1a_d14 2 I 0

vout3_d14 3 O

gpio1_20 14 IO

sysboot14 15 I

vin1a_d15 2 I 0

vout3_d15 3 O

gpio1_21 14 IO

sysboot15 15 I

MUXMODE

[4]

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

DSIS [14]

28

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

N1 gpmc_advn_ale gpmc_advn_ale 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

N6 gpmc_ben0 gpmc_ben0 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

M4 gpmc_ben1 gpmc_ben1 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

gpmc_cs6 1 O

clkout2 2 O

gpmc_wait1 3 I 1

vin2a_vsync0

vin1a_vsync0

gpmc_a2 5 O

gpmc_a23 6 O

timer3 7 IO

i2c3_sda 8 IO 1

dma_evt2 9 I 0

gpio2_23

gpmc_a19

Driver off 15 I

gpmc_cs4 1 O

vin2b_de1

vin1b_de1

timer2 7 IO

dma_evt3 9 I 0

gpio2_26

gpmc_a21

Driver off 15 I

gpmc_cs5 1 O

vin2b_clk1

vin1b_clk1

gpmc_a3 5 O

vin2b_fld1

vin1b_fld1

timer1 7 IO

dma_evt4 9 I 0

gpio2_27

gpmc_a22

Driver off 15 I

MUXMODE

[4]

4 I

14 IO

6 I

14 IO

4 I

6 I

14 IO

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD

PU/PD

PU/PD

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

29

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

P7 gpmc_clk gpmc_clk 0 IO PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

T1 gpmc_cs0 gpmc_cs0 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

H6 gpmc_cs1 gpmc_cs1 0 O PU PU 15 1.8/3.3 vddshv11 Yes Dual Voltage

P2 gpmc_cs2 gpmc_cs2 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

gpmc_cs7 1 O

clkout1 2 O

gpmc_wait1 3 I 1

vin2a_hsync0

vin1a_hsync0

vin2a_de0

vin1a_de0

vin2b_clk1

vin1b_clk1

timer4 7 IO

i2c3_scl 8 IO 1

dma_evt1 9 I 0

gpio2_22

gpmc_a20

Driver off 15 I

gpio2_19 14 IO

Driver off 15 I

mmc2_cmd 1 IO 1

gpmc_a22 2 O

vin2a_de0

vin1a_de0

vin2b_vsync1

vin1b_vsync1

gpio2_18 14 IO

Driver off 15 I

qspi1_cs0 1 IO 1

gpio2_20

gpmc_a23

gpmc_a13

Driver off 15 I

MUXMODE

[4]

4 I

5 I

6 I

14 IO

4 I

6 I

14 IO

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD 0

PU/PD

PU/PD

PU/PD

DSIS [14]

30

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

P1 gpmc_cs3 gpmc_cs3 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

M5 gpmc_oen_ren gpmc_oen_ren 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

N2 gpmc_wait0 gpmc_wait0 0 I PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

M3 gpmc_wen gpmc_wen 0 O PU PU 15 1.8/3.3 vddshv10 Yes Dual Voltage

AG16 hdmi1_clockx hdmi1_clockx 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AH16 hdmi1_clocky hdmi1_clocky 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AG17 hdmi1_data0x hdmi1_data0x 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AH17 hdmi1_data0y hdmi1_data0y 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AG18 hdmi1_data1x hdmi1_data1x 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AH18 hdmi1_data1y hdmi1_data1y 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AG19 hdmi1_data2x hdmi1_data2x 0 O 1.8 vdda_hdmi HDMIPHY Pdy

AH19 hdmi1_data2y hdmi1_data2y 0 O 1.8 vdda_hdmi HDMIPHY Pdy

C20 i2c1_scl i2c1_scl 0 IO 1.8/3.3 vddshv3 Yes Dual Voltage

C21 i2c1_sda i2c1_sda 0 IO 1.8/3.3 vddshv3 Yes Dual Voltage

F17 i2c2_scl i2c2_scl 0 IO 15 1.8/3.3 vddshv3 Yes Dual Voltage

C25 i2c2_sda i2c2_sda 0 IO 15 1.8/3.3 vddshv3 Yes Dual Voltage

AH15 ljcb_clkn ljcb_clkn 0 IO 1.8 vdda_pcie LJCB

BALL NAME [2] SIGNAL NAME [3]

qspi1_cs1 1 O 1

vin1a_clk0 2 I 0

vout3_clk 3 O

gpmc_a1 5 O

gpio2_21

gpmc_a24

gpmc_a14

Driver off 15 I

gpio2_24 14 IO

Driver off 15 I

gpio2_28

gpmc_a25

gpmc_a15

Driver off 15 I

gpio2_25 14 IO

Driver off 15 I

Driver off 15 I

Driver off 15 I

hdmi1_ddc_sda 1 IO

Driver off 15 I

hdmi1_ddc_scl 1 IO

Driver off 15 I

MUXMODE

[4]

14 IO

14 IO

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS I2C

LVCMOS I2C

LVCMOS I2C

LVCMOS I2C

PU/PD

PU/PD

PU/PD 1

PU/PD

PU/PD

PU/PD

PU/PD 1

PU/PD 1

PULL

UP/DOWN

TYPE [13]

DSIS [14]

Copyright © 2016–2019, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

31

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

www.ti.com

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

AG15 ljcb_clkp ljcb_clkp 0 IO 1.8 vdda_pcie LJCB

B14 mcasp1_aclkr mcasp1_aclkr 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

C14 mcasp1_aclkx mcasp1_aclkx 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

G12 mcasp1_axr0 mcasp1_axr0 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

F12 mcasp1_axr1 mcasp1_axr1 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

G13 mcasp1_axr2 mcasp1_axr2 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

mcasp7_axr2 1 IO 0

vout2_d0 6 O

vin2a_d0

vin1a_d0

i2c4_sda 10 IO 1

gpio5_0 14 IO

Driver off 15 I

vin1a_fld0 7 I 0

i2c3_sda 10 IO 1

gpio7_31 14 IO

Driver off 15 I

uart6_rxd 3 I 1

vin1a_vsync0 7 I 0

i2c5_sda 10 IO 1

gpio5_2 14 IO

Driver off 15 I

uart6_txd 3 O

vin1a_hsync0 7 I 0

i2c5_scl 10 IO 1

gpio5_3 14 IO

Driver off 15 I

mcasp6_axr2 1 IO 0

uart6_ctsn 3 I 1

vout2_d2 6 O

vin2a_d2

vin1a_d2

gpio5_4 14 IO

Driver off 15 I

MUXMODE

[4]

8 I

8 I

TYPE [5]

BALL

RESET

STATE [6]

(1)

(continued)

BALL

RESET REL.

STATE [7]

BALL

RESET REL.

MUXMODE

[8]

I/O

VOLTAGE

VALUE [9]

POWER [10] HYS [11]

BUFFER

TYPE [12]

LVCMOS

LVCMOS

LVCMOS

LVCMOS

LVCMOS

PULL

UP/DOWN

TYPE [13]

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

PU/PD 0

DSIS [14]

32

Copyright © 2016–2019, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: TDA2EG

www.ti.com

TDA2EG

SPRS958H –MARCH 2016–REVISED NOVEMBER 2019

Table 4-2. Ball Characteristics

BALL NUMBER

[1]

J11 mcasp1_axr3 mcasp1_axr3 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

E12 mcasp1_axr4 mcasp1_axr4 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

F13 mcasp1_axr5 mcasp1_axr5 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

C12 mcasp1_axr6 mcasp1_axr6 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

D12 mcasp1_axr7 mcasp1_axr7 0 IO PD PD 15 1.8/3.3 vddshv3 Yes Dual Voltage

BALL NAME [2] SIGNAL NAME [3]

mcasp6_axr3 1 IO 0

uart6_rtsn 3 O

vout2_d3 6 O

vin2a_d3

vin1a_d3

gpio5_5 14 IO

Driver off 15 I

mcasp4_axr2 1 IO 0

vout2_d4 6 O

vin2a_d4

vin1a_d4

gpio5_6 14 IO

Driver off 15 I

mcasp4_axr3 1 IO 0

vout2_d5 6 O

vin2a_d5

vin1a_d5

gpio5_7 14 IO

Driver off 15 I

mcasp5_axr2 1 IO 0

vout2_d6 6 O

vin2a_d6

vin1a_d6

gpio5_8 14 IO

Driver off 15 I

mcasp5_axr3 1 IO 0

vout2_d7 6 O

vin2a_d7

vin1a_d7

timer4 10 IO

gpio5_9 14 IO

Driver off 15 I

MUXMODE