Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

www.ti.com

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

TM

FEATURES

D 2×125 W at 10% THD+N Into 4-W BTL

D 2×98 W at 10% THD+N Into 6-W BTL

D 2×76 W at 10% THD+N Into 8-W BTL

D 4×45 W at 10% THD+N Into 3-W SE

D 4×35 W at 10% THD+N Into 4-W SE

D 1×192 W at 10% THD+N Into 3-W PBTL

D 1×240 W at 10% THD+N Into 2-W PBTL

D >100-dB SNR (A-Weighted)

D <0.1% THD+N at 1 W

D Thermally Enhanced Package Option:

− DKD (36-Pin PSOP3)

D High-Efficiency Power Stage (>90%) With

140-mW Output MOSFETs

D Power-On Reset for Protection on Power Up

Without Any Power-Supply Sequencing

D Integrated Self-Protection Circuits Including:

− Undervoltage

− Overtemperature

− Overload

− Short Circuit

D Error Reporting

D EMI Compliant When Used With

Recommended System Design

D Intelligent Gate Drive

APPLICATIONS

D Mini/Micro Audio System

D DVD Receiver

D Home Theater

DESCRIPTION

The TAS5152 is a third-generation, high-performance,

integrated stereo digital amplifier power stage with

improved protection system. The TAS5152 is capable

of driving a 4-Ω bridge-tied load (BTL) at up to 125 W

per channel with low integrated noise at the output, low

THD+N performance, and low idle power dissipation.

A low-cost, high-fidelity audio system can be built using

a TI chipset, comprised of a modulator (e.g., T AS5508)

and the TAS5152. This system only requires a simple

passive LC demodulation filter to deliver high-quality,

high-efficiency audio amplification with proven EMI

compliance. This device requires two power supplies,

12 V for GVDD and VDD, and 35 V for PVDD. The

TAS5152 does not require power-up sequencing due to

internal power-on reset. The efficiency of this digital

amplifier is g rea t e r t h a n 9 0 % i n t o 6 Ω, which enables the

use of smaller power supplies and heatsinks.

The TAS5152 has an innovative protection system

integrated on-chip, safeguarding the device against a

wide range of fault conditions that could damage the

system. These safeguards are short-circuit protection,

overcurrent protection, undervoltage protection, and

overtemperature protection. The TAS5152 has a new

proprietary current-limiting circuit that reduces the

possibility of device shutdown during high-level music

transients. A new programmable overcurrent detector

allows the use of lower-cost inductors in the

demodulation output filter.

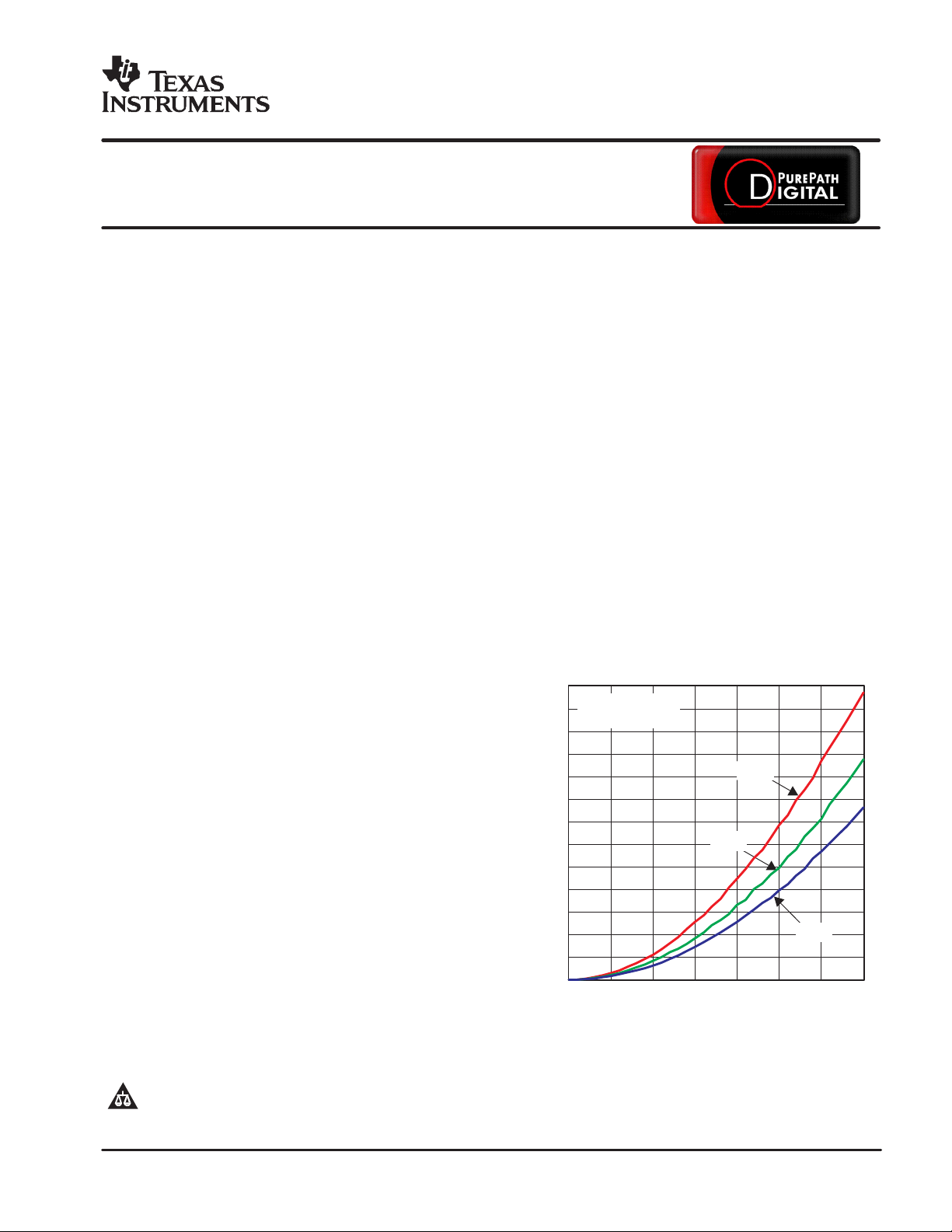

BTL OUTPUT POWER vs SUPPLY VOL TAGE

130

TC = 75°C

120

THD+N @ 10%

110

100

90

80

70

60

50

− Output Power − W

40

O

P

30

20

10

0

0 5 10 15 20 25 30 35

PVDD − Supply V oltage − V

4 Ω

6 Ω

8 Ω

semiconductor products and disclaimers thereto appears at the end of this data sheet.

PurePath Digital and PowerPAD are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

! "#$ %!& %

"! "! '! ! !( ! %% )*&

% "!+ %! !!$* $%! !+ $$ "!!&

Copyright 2005, Texas Instruments Incorporated

A

A

B

C

D

D

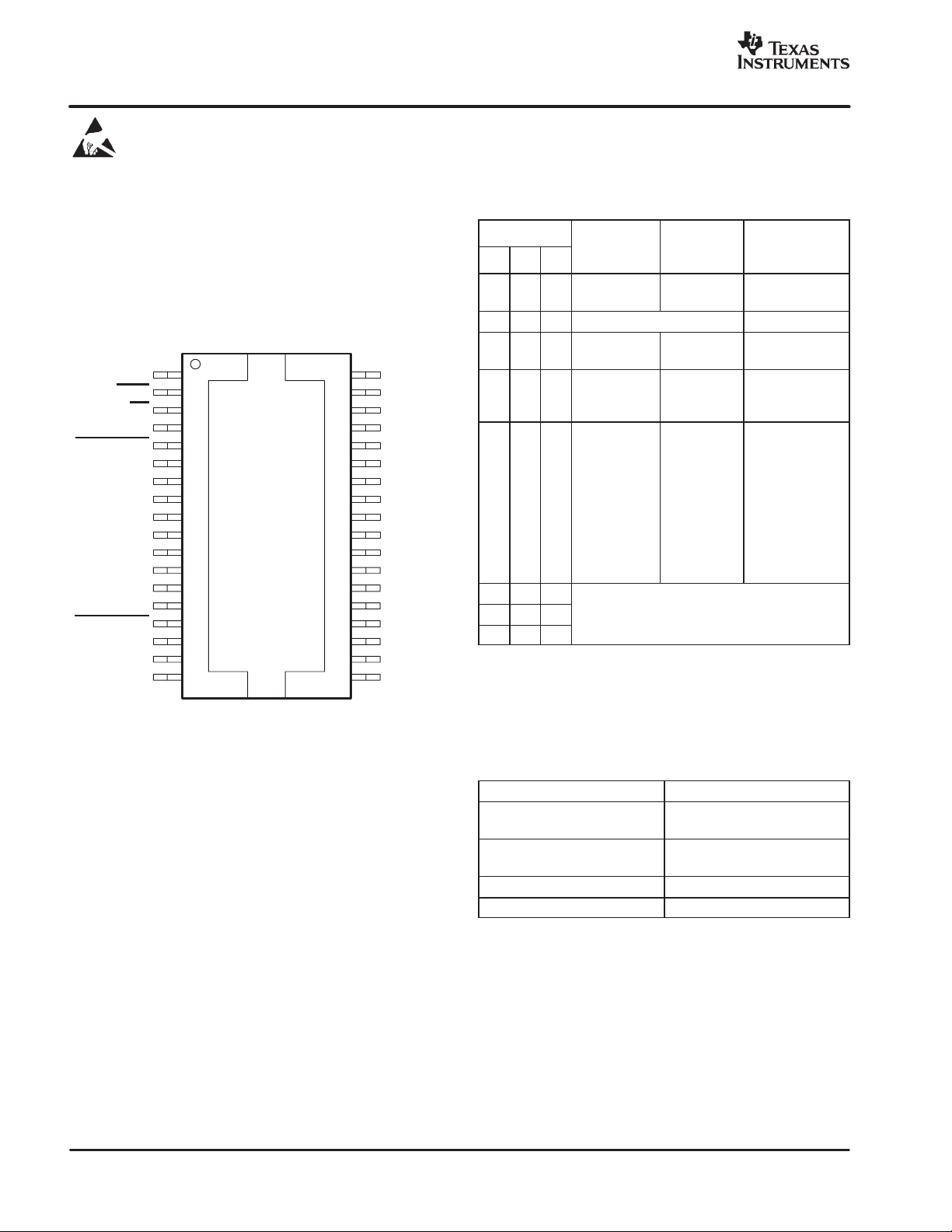

DKD PACKAGE

CONFIGU-

SCHEME

Reserved

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during

storage or handling to prevent electrostatic damage to the MOS gates.

GENERAL INFORMATION

The TAS5152 is available in a 36-pin PSOP3 (DKD)

thermally enhanced package. The package contains a

heat slug that is located on the top side of the device for

convenient thermal coupling to the heatsink.

(TOP VIEW)

GVDD_B

OTW

SD

PWM_A

RESET_AB

PWM_B

OC_ADJ

GND

AGND

VREG

M3

M2

M1

PWM_C

RESET_CD

PWM_D

VDD

GVDD_C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

GVDD_

BST_A

PVDD_

OUT_A

GND_A

GND_B

OUT_B

PVDD_

BST_B

BST_C

PVDD_

OUT_C

GND_C

GND_D

OUT_D

PVDD_

BST_D

GVDD_

www.ti.com

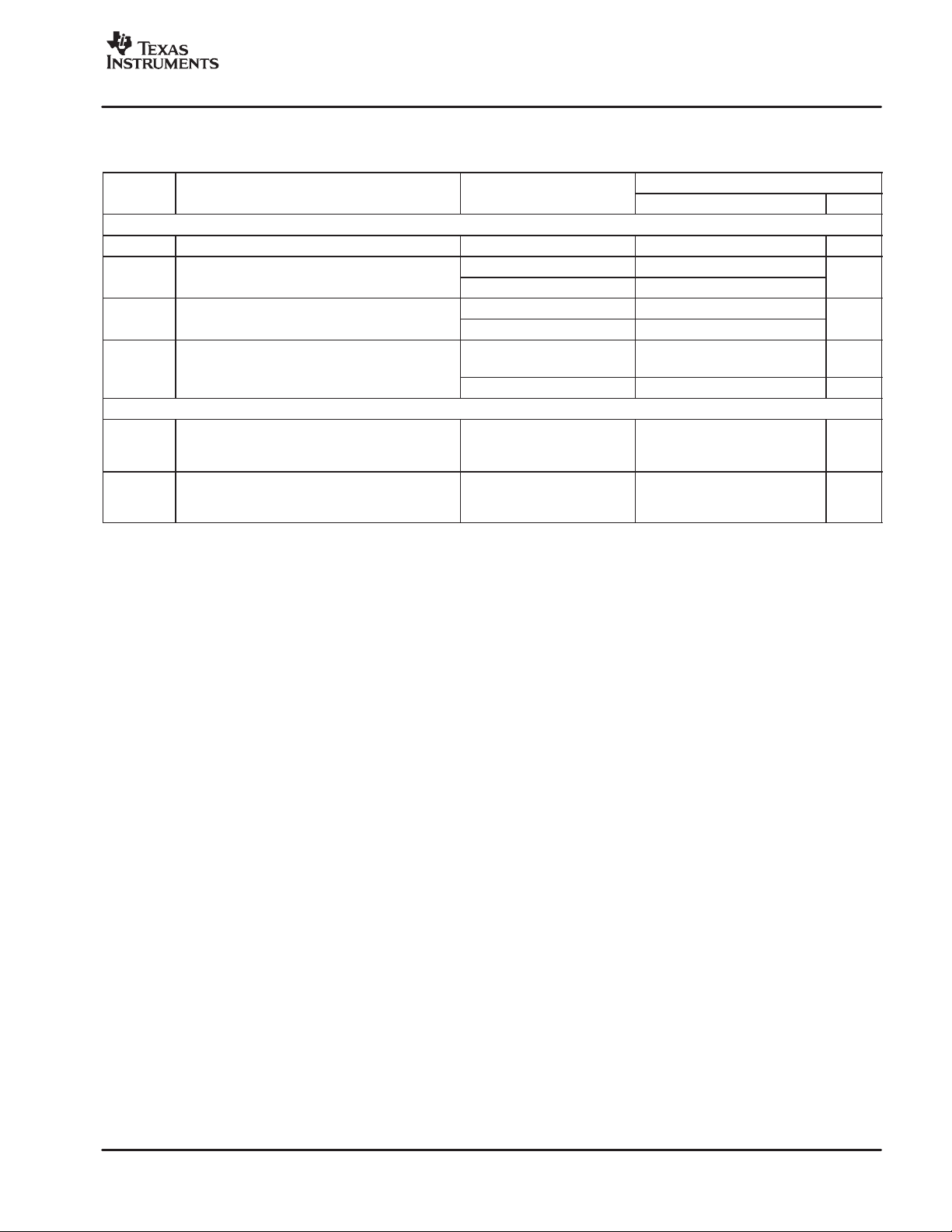

MODE Selection Pins

MODE PINS PWM INPUT OUTPUT

M3 M2 M1

(1)

2N

0 0 0

0 0 1 Reserved

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

(1)

The 1N and 2N naming convention is used to indicate the required

number of PWM lines to the power stage per channel in a specific

mode.

(2)

An overload protection (OLP) occurring on A or B causes both

channels to shut down. An OLP on C or D works similarly. Global

errors like overtemperature error (OTE), undervoltage protection

(UVP) and power-on reset (POR) affect all channels.

AD/BD

modulation

(1)

1N

AD

modulation

(1)

1N

AD

modulation

(1)

1N

AD

modulation

Reserved

RATION

2 channels

BTL output

2 channels

BTL output

1 channel

PBTL output

4 channels

SE output

Package Heat Dissipation Ratings

PARAMETER TAS5152DKD

R

(°C/W)—2 BTL or 4 SE

θJC

channels (8 transistors)

R

〈°C/W)—1 BTL or 2 SE

θJC

channel(s) (4 transistors)

R

(°C/W)—(1 transistor) 8.6

θJC

Pad area

(1)

JC is junction-to-case, CH is case-to-heatsink.

(2)

R

is an important consideration. Assume a 2-mil thickness of

θCH

typical thermal grease between the pad area and the heatsink. The

R

with this condition is 0.8°C/W for the DKD package and

θCH

1.8°C/W for the DDV package.

(2)

PROTECTION

BTL mode

BTL mode

PBTL mode.

Only PWM_A

input is used.

Protection works

similarly to BTL

(2)

mode

difference in SE

mode is that

OUT_x is Hi-Z

instead of a

pulldown through

internal pulldown

resistor.

(1)

1.28

2.56

2

80 mm

(2)

(2)

. Only

2

www.ti.com

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted

TAS5152

VDD to AGND –0.3 V to 13.2 V

GVDD_X to AGND –0.3 V to 13.2 V

(2)

(2)

(2)

J

–0.3 V to 50 V

–0.3 V to 50 V

–0.3 V to 63.2 V

–0.3 V to 4.2 V

9 mA

0°C to 125°C

260_C

PVDD_X to GND_X

OUT_X to GND_X

BST_X to GND_X

VREG to AGND –0.3 V to 4.2 V

GND_X to GND –0.3 V to 0.3 V

GND_X to AGND –0.3 V to 0.3 V

GND to AGND –0.3 V to 0.3 V

PWM_X, OC_ADJ, M1, M2, M3 to

AGND

RESET_X, SD, OTW to AGND –0.3 V to 7 V

Maximum continuous sink current (SD,

OTW)

Maximum operating junction

temperature range, T

Storage temperature –40_C to 125_C

Lead temperature, 1,6 mm (1/16 inch)

from case for 10 seconds

Minimum pulse width low 50 ns

(1)

Stresses beyond those listed under “absolute maximum ratings”

may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any

other conditions beyond those indicated under “recommended

operating conditions” is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device

reliability.

(2)

These voltages represent the dc voltage + peak ac waveform

measured at the terminal of the device in all conditions.

(1)

Ordering Information

T

A

0°C to 70°C TAS5152DKD 36-pin PSOP3

PACKAGE DESCRIPTION

For the most current specification and package

information, see the TI Web site at www.ti.com.

3

FUNCTION

(1)

DESCRIPTION

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

www.ti.com

Terminal Functions

TERMINAL

NAME NO.

AGND 9 P Analog ground

BST_A 35 P HS bootstrap supply (BST), external capacitor to OUT_A required

BST_B 28 P HS bootstrap supply (BST), external capacitor to OUT_B required

BST_C 27 P HS bootstrap supply (BST), external capacitor to OUT_C required

BST_D 20 P HS bootstrap supply (BST), external capacitor to OUT_D required

GND 8 P Ground

GND_A 32 P Power ground for half-bridge A

GND_B 31 P Power ground for half-bridge B

GND_C 24 P Power ground for half-bridge C

GND_D 23 P Power ground for half-bridge D

GVDD_A 36 P Gate-drive voltage supply requires 0.1-µF capacitor to AGND

GVDD_B 1 P Gate-drive voltage supply requires 0.1-µF capacitor to AGND

GVDD_C 18 P Gate-drive voltage supply requires 0.1-µF capacitor to AGND

GVDD_D 19 P Gate-drive voltage supply requires 0.1-µF capacitor to AGND

M1 13 I Mode selection pin

M2 12 I Mode selection pin

M3 11 I Mode selection pin

OC_ADJ 7 O Analog overcurrent programming pin requires resistor to ground

OTW 2 O Overtemperature warning signal, open drain, active-low

OUT_A 33 O Output, half-bridge A

OUT_B 30 O Output, half-bridge B

OUT_C 25 O Output, half-bridge C

OUT_D 22 O Output, half-bridge D

PVDD_A 34 P Power-supply input for half-bridge A requires close decoupling of 0.1-µF capacitor to

GND_A

PVDD_B 29 P Power-supply input for half-bridge B requires close decoupling of 0.1-µF capacitor to

GND_B

PVDD_C 26 P Power-supply input for half-bridge C requires close decoupling of 0.1-µF capacitor to

GND_C

PVDD_D 21 P Power-supply input for half-bridge D requires close decoupling of 0.1-µF capacitor to

GND_D

PWM_A 4 I Input signal for half-bridge A

PWM_B 6 I Input signal for half-bridge B

PWM_C 14 I Input signal for half-bridge C

PWM_D 16 I Input signal for half-bridge D

RESET_AB 5 I Reset signal for half-bridge A and half-bridge B, active-low

RESET_CD 15 I Reset signal for half-bridge C and half-bridge D, active-low

SD 3 O Shutdown signal, open drain, active-low

VDD 17 P Power supply for digital voltage regulator requires 0.1-µF capacitor to GND.

VREG 10 P Digital regulator supply filter pin requires 0.1-µF capacitor to AGND

(1)

I = input, O = Output, P = Power

4

www.ti.com

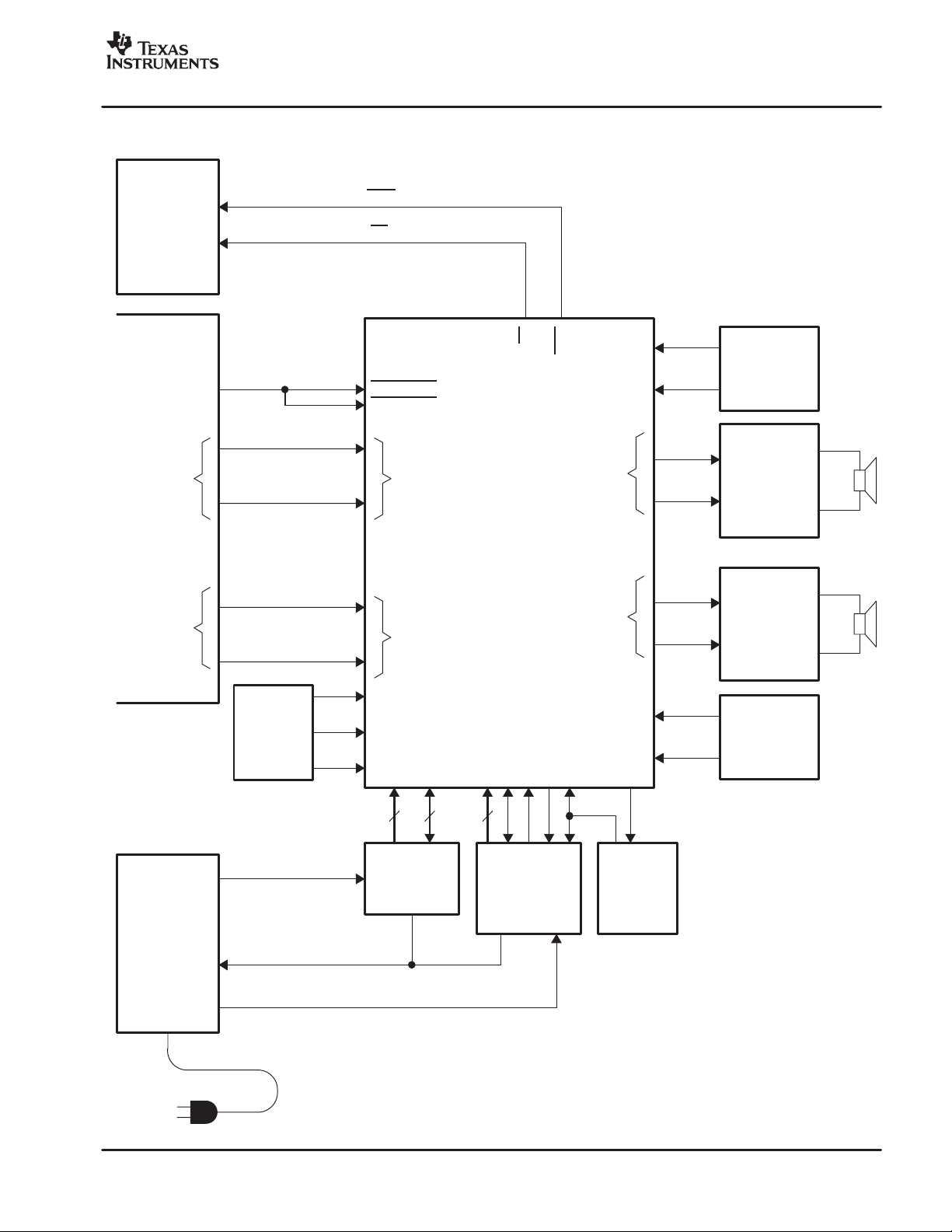

SYSTEM BLOCK DIAGRAM

System

Microcontroller

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

OTW

SD

TAS5508

Channel

Output

Right-

Channel

Output

Left-

VALID

Hardwire

Mode

Control

PWM_A

PWM_B

PWM_C

PWM_D

M1

M2

M3

RESET_AB

RESET_CD

Input

H-Bridge 1

Input

H-Bridge 2

PVDD_A, B, C, D

2-Channel

H-Bridge

BTL Mode

GND_A, B, C, D

GVDD_A, B, C, D

GND

SD

VDD

OTW

Output

H-Bridge 1

Output

H-Bridge 2

VREG

AGND

OUT_A

OUT_B

OUT_C

OUT_D

OC_ADJ

BST_A

BST_B

BST_C

BST_D

Bootstrap

Capacitors

2nd-Order L- C

Output Filter

for Each

Half-Bridge

2nd-Order L- C

Output Filter

for Each

Half-Bridge

Bootstrap

Capacitors

System

Power

Supply

VAC

35 V

GND

12 V

4

PVDD

Decoupling

GND

GVDD (12 V)/VDD (12 V)

44

PVDD

PowerSupply

GVDD

VDD

VREG

Power-Supply

Decoupling

Hardwire

OC Limit

5

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

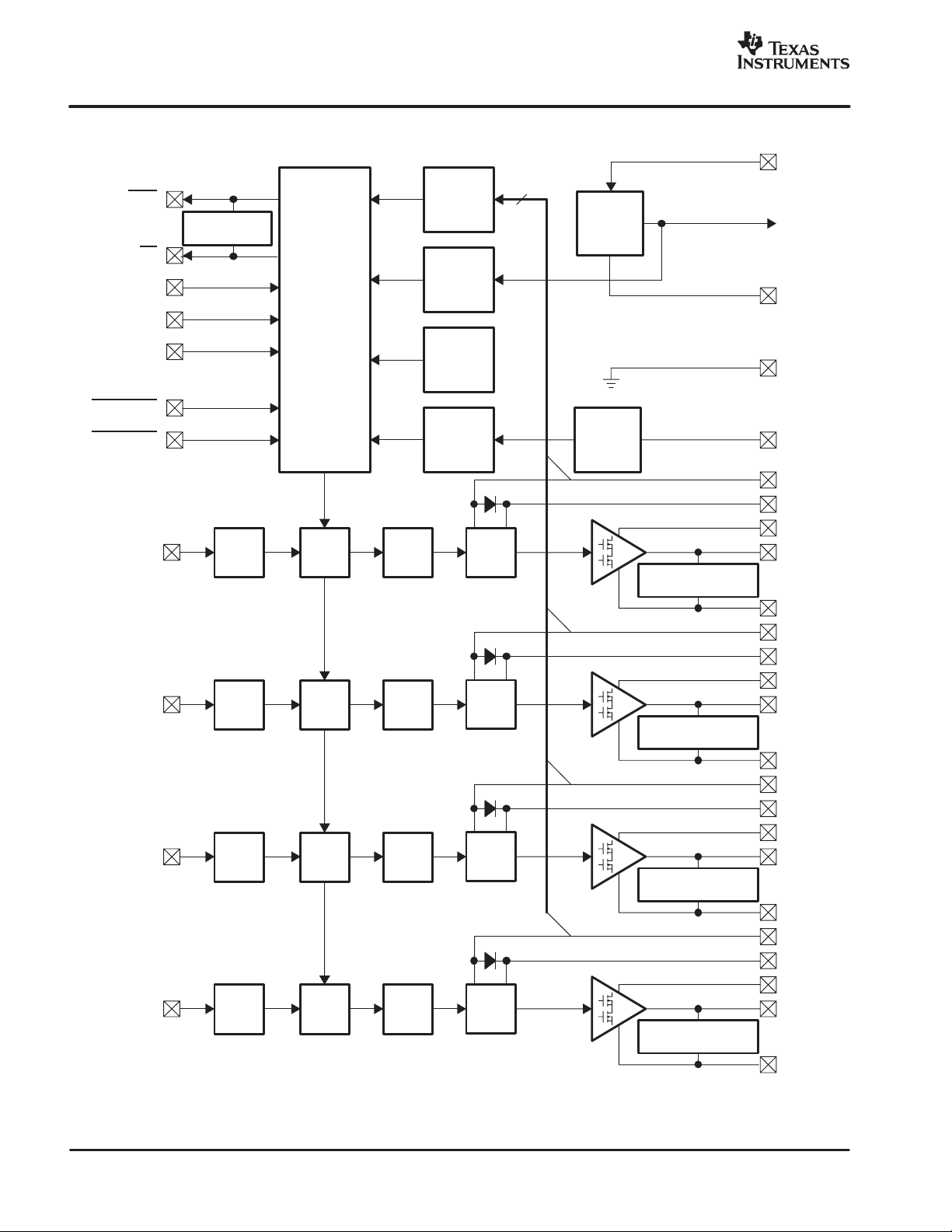

FUNCTIONAL BLOCK DIAGRAM

Under-

OTW

SD

M1

M2

Internal Pullup

Resistors to VREG

Protection

and

voltage

Protection

Power

On

Reset

I/O Logic

M3

Temp.

Sense

RESET_AB

RESET_CD

PWM_D OUT_D

PWM_C OUT_C

PWM_B OUT_B

PWM_A OUT_A

PWM

Rcv.

PWM

Rcv.

PWM

Rcv.

PWM

Rcv.

Ctrl.

Ctrl.

Ctrl.

Ctrl.

Overload

Protection

Timing

Timing

Timing

Timing

Gate

Drive

Gate

Drive

Gate

Drive

Gate

Drive

4

VREG VREG

Isense

BTL/PBTL−Configuration

Pulldown Resistor

BTL/PBTL−Configuration

Pulldown Resistor

BTL/PBTL−Configuration

Pulldown Resistor

BTL/PBTL−Configuration

Pulldown Resistor

www.ti.com

VDD

AGND

GND

OC_ADJ

GVDD_D

BST_D

PVDD_D

GND_D

GVDD_C

BST_C

PVDD_C

GND_C

GVDD_B

BST_B

PVDD_B

GND_B

GVDD_A

BST_A

PVDD_A

GND_A

6

www.ti.com

Output filter: L = 10 µH, C = 470 nF

Load impedance

Output AD modulation, switching

Ω

Output-filter inductance

short-circuit condition

µH

SYMBOL

PARAMETER

CONDITIONS

UNIT

PoPower output per channel

W

THD+N

Total harmonic distortion + noise

%

DNR

Dynamic range

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

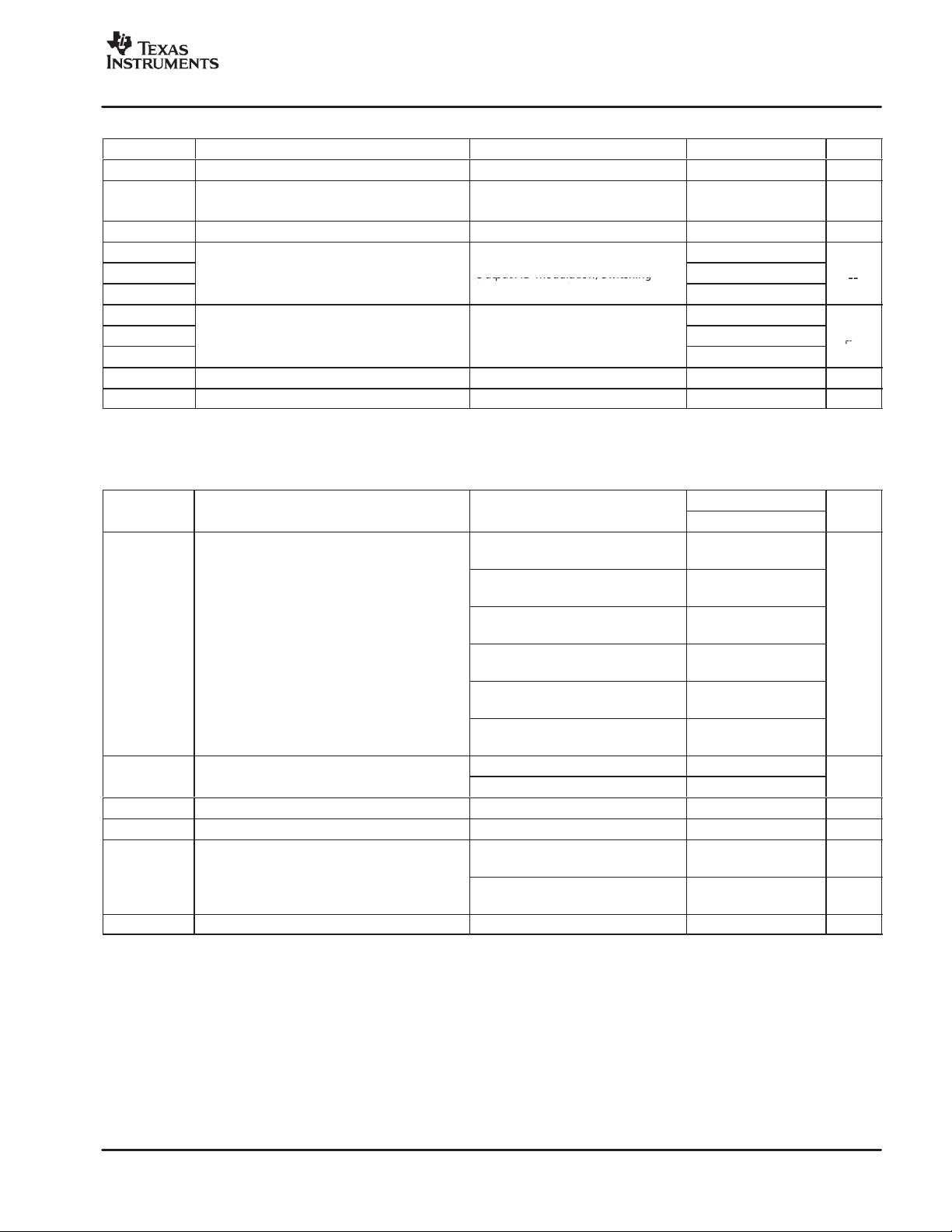

RECOMMENDED OPERATING CONDITIONS

CONDITIONS MIN NOM MAX UNIT

PVDD_x Half-bridge supply DC supply voltage 0 35 37 V

GVDD_x

VDD Digital regulator input DC supply voltage 10.8 12 13.2 V

RL (BTL)

RL (SE)

RL (PBTL)

L

(BTL)

Output

L

(SE)

Output

L

(PBTL)

Output

F

PWM

T

J

Supply for logic regulators and gate-drive

circuitry

Load impedance

Output-filter inductance

PWM frame rate 192 384 432 kHz

Junction temperature 0 125 _C

DC supply voltage 10.8 12 13.2 V

3 4

Output AD modulation, switching

frequency > 350 kHz

Minimum output inductance under

2 3

1.5 2

10

10

10

Ω

µH

AUDIO SPECIFICATIONS (BTL)

PVDD_X = 35 V, GVDD = VDD = 12 V , BTL mode, RL = 4 Ω, audio frequency = 1 kHz, AES17 filter, F

unless otherwise noted. Audio performance is recorded as a chipset, using TAS5508 PWM processor with an ef fective modulation in dex limit of

96.1%. All performance is in accordance with recommended operating conditions unless otherwise specified.

RL = 4 Ω,10% THD, clipped input

signal

RL = 6 Ω,10% THD, clipped input

signal

RL = 8 Ω,10% THD, clipped input

signal

RL = 4 Ω, 0 dBFS, unclipped input

signal

RL = 6 Ω, 0 dBFS, unclipped input

signal

RL = 8 Ω, 0 dBFS, unclipped input

signal

0 dBFS 0.1

1 W 0.02

V

n

SNR Signal-to-noise ratio

P

idle

(1)

SNR is calculated relative to 0-dBFS input level.

(2)

Actual system idle losses are affected by core losses of output inductors.

Output integrated noise A-weighted 145 µV

(1)

Power dissipation due to idle losses (IPVDDx) PO = 0 W, 2 channels switching

A-weighted 102 dB

A-weighted, input level = –60 dBFS

using TAS5508 modulator

A-weighted, input level = –60 dBFS

using TAS5518 modulator

= 384 kHz, case temperature = 75°C,

PWM

TAS5152

MIN TYP MAX

125

98

76

96

72

57

102 dB

110 dB

(2)

2 W

7

SYMBOL

PARAMETER

CONDITIONS

UNIT

PoPower output per channel

W

THD+N

Total harmonic distortion + noise

%

SYMBOL

PARAMETER

CONDITIONS

UNIT

PoPower output per channel

W

THD+N

Total harmonic distortion + noise

%

DNR

Dynamic range

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

www.ti.com

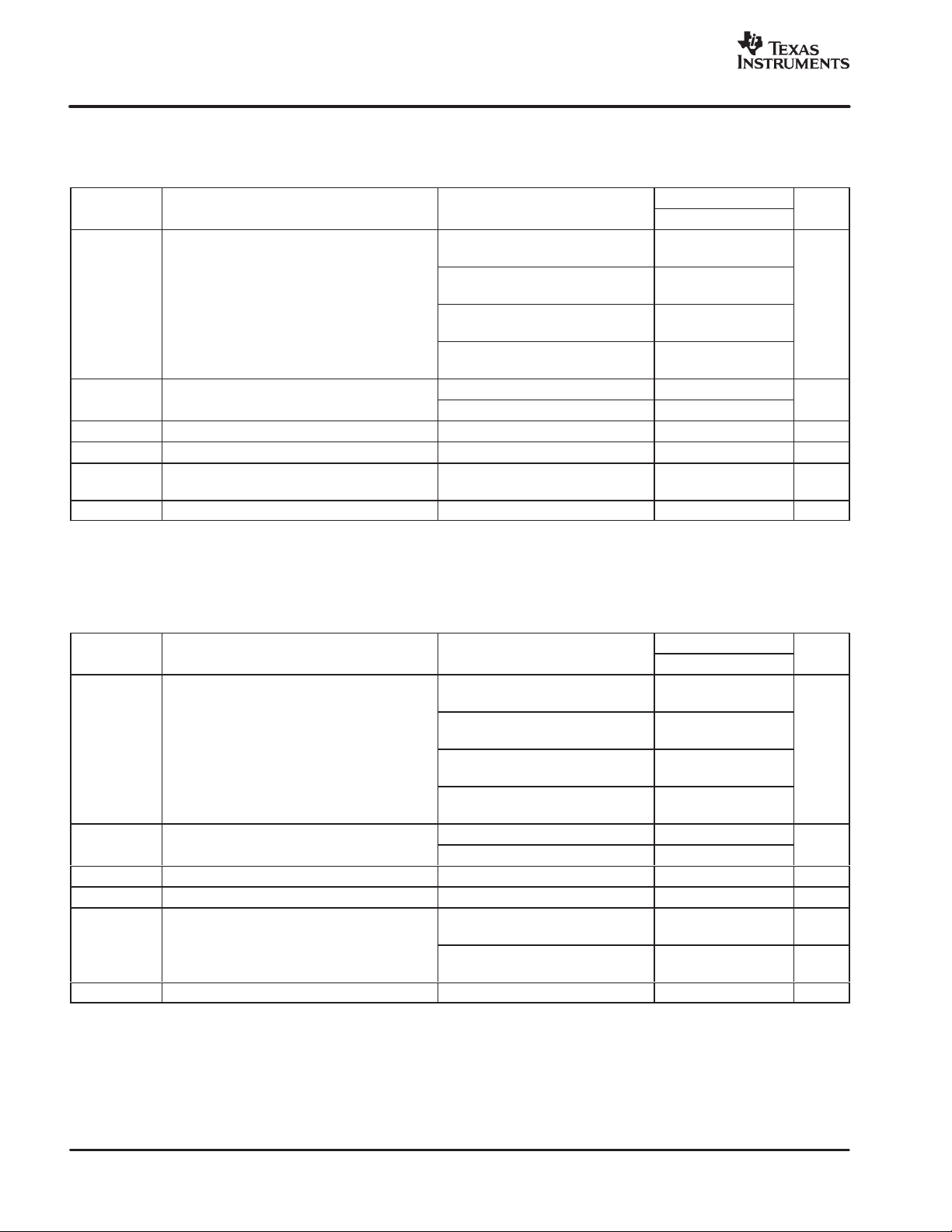

AUDIO SPECIFICATIONS (Single-Ended Output)

PVDD_X = 35 V, GVDD = VDD = 12 V , SE mode, RL = 4 Ω, audio frequency = 1 kHz, AES17 filter, F

unless otherwise noted. Audio performance is recorded as a chipset, using TAS5086 PWM processor with an ef fective modulation index limit of

96.1%. All performance is in accordance with recommended operating conditions unless otherwise specified.

RL = 3 Ω,10% THD, clipped input

signal

RL = 4 Ω,10% THD, clipped input

signal

RL = 3 Ω, 0 dBFS, unclipped input

signal

RL = 4 Ω, 0 dBFS, unclipped input

signal

0 dBFS 0.2

1 W 0.03

V

n

SNR Signal-to-noise ratio

DNR Dynamic range

P

idle

(1)

SNR is calculated relative to 0-dBFS input level.

(2)

Actual system idle losses are affected by core losses of output inductors.

Output integrated noise A-weighted 90 µV

(1)

Power dissipation due to idle losses (IPVDDx) PO = 0 W, 4 channels switching

A-weighted 100 dB

A-weighted, input level = –60 dBFS

using TAS5508 modulator

= 384 kHz, case temperature = 75°C,

PWM

TAS5152

MIN TYP MAX

45

35

35

25

100 dB

(2)

2 W

AUDIO SPECIFICATIONS (PBTL)

PVDD_X = 35 V, GVDD = VDD = 12 V , PBTL mode, RL = 3 Ω, audio frequency = 1 kHz, AES17 filter, F

75°C, unless otherwise noted. Audio performance is recorded as a chipset, using TAS5508 PWM processor with an effective modulation index

limit of 96.1%. All performance is in accordance with recommended operating conditions unless otherwise specified.

RL = 3 Ω,10% THD, clipped input

signal

RL = 2 Ω,10% THD, clipped input

signal

RL = 3 Ω, 0 dBFS, unclipped input

signal

RL = 2 Ω, 0 dBFS, unclipped input

signal

0 dBFS 0.2

1 W 0.02

V

n

SNR Signal-to-noise ratio

P

idle

(1)

SNR is calculated relative to 0-dBFS input level.

(2)

Actual system idle losses are affected by core losses of output inductors.

Output integrated noise A-weighted 160 µV

(1)

Power dissipation due to idle losses (IPVDDx) PO = 0 W, 1 channel switching

A-weighted 102 dB

A-weighted, input level = –60 dBFS

using TAS5508 modulator

A-weighted, input level = –60 dBFS

using TAS5518 modulator

= 384 kHz, case temperature =

PWM

TAS5152

MIN TYP MAX

192

240

145

190

102 dB

110 dB

(2)

2 W

8

www.ti.com

SYMBOL

PARAMETER

CONDITIONS

IVDD

VDD supply current

mA

IGVDD_x

Gate supply current per half-bridge

mA

Half-bridge idle current

IPVDD_x

Half-bridge idle current

SLES127A − FEBRUARY 2005 − REVISED NOVEMBER 2005

ELECTRICAL CHARACTERISTICS

RL= 4 Ω. F

specified.

Internal Voltage Regulator and Current Consumption

VREG Voltage regulator, only used as a reference node VDD = 12 V 3 3.3 3.6 V

IPVDD_x

Output Stage MOSFETs

R

DSon,LS

R

DSon,HS

= 384 kHz, unless otherwise noted. All performance is in accordance with recommended operating conditions unless otherwise

PWM

TAS5152

MIN TYP MAX UNITS

Operating, 50% duty cycle 7 17

Idle, reset mode 6 11

50% duty cycle 5 16

Reset mode 0.3 1

Drain-to-source resistance, LS

Drain-to-source resistance, HS

50% duty cycle, without

output filter or load

Reset mode, no switching 7 25 µA

T

25°C, includes

J

=

metallization resistance,

GVDD = 12 V

T

25°C, includes

J

=

metallization resistance,

GVDD = 12 V

15 25 mA

140 155 mΩ

140 155 mΩ

9

Loading...

Loading...