查询TAS5101IDAP供应商

TAS5101

SLES039 – JUNE 2002

TRUE DIGITAL STEREO AUDIO AMPLIFIER

WITH PWM STEREO POWER OUTPUT STAGE

FEATURES

2 × 15 W High-Quality Digital Amplifier Power

D

Stage

D Single-Ended Output

D >95-dB Dynamic Range (TDAA System)

D THD+N < 0.1% (1 kHz, 1 W to 15 W RMS

Into 4 Ω)

D Power Efficiency > 90% Into 4-Ω to 8-Ω Load

D Low Profile, SMD 32-Pin PowerPAD Package

Requires No Heat-Sink When Using

Recommended Layout

D 2 × 15-W RMS Continuous Power Into 4 Ω

D Self-Protecting Design

D 3.3-V Digital Interface

D EMI Compliant When Used With

Recommended System Design

APPLICATIONS

D Digital TV Audio Amplifier

D Car Audio Amplifiers and Head Units

D Internet Music Appliance

D Mini/Micro Component Systems

DESCRIPTION

The T AS5101 is a high-performance true digital stereo

audio amplifier (TDAA) Power Stage, designed to drive

2 × 15 watts per channel. The TAS5101 incorporates

TI’s equibitt technology and is used in conjunction with

a Digital Audio PWM processor (TAS50xx) to deliver

high-power, true digital audio amplification. The

efficiency of this digital amplifier can be greater than

90%, reducing the size of both the power supplies and

heat sinks needed. The TAS5101 accepts a stereo

PWM 3.3V input and controls the switching of an

internal CMOS H-bridge.

When used with the T AS50xx PWM Processor , system

performance of less than 0.09% THD is attainable.

Over-current protection, over-temperature, and

under-voltage protections are built into the TAS5101,

safeguarding the H-bridge and speakers against output

shorts, over-voltage conditions, and other fault

conditions that could damage the system.

TYPICAL TDAA STEREO AUDIO SYSTEM

Digital Audio

• TAS3001

• TAS3103

• DSP

• DIR1703

• 1394

• Volume

• EQ

• DRC

• Bass

• Treble

The T AS5000 in NOT recommended for use with the TAS5101

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD and Equibit are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

• Serial Audio Input Port

• Internal PLL

• PCM–PWM Modulator

TAS5010

NOTE:

www.ti.com

L-C

Filter

TAS5101

L-C

Filter

• 2 × 15 W Single-Ended

H-Bridge Power Devices

Copyright 2002, Texas Instruments Incorporated

1

TAS5101

SLES039 – JUNE 2002

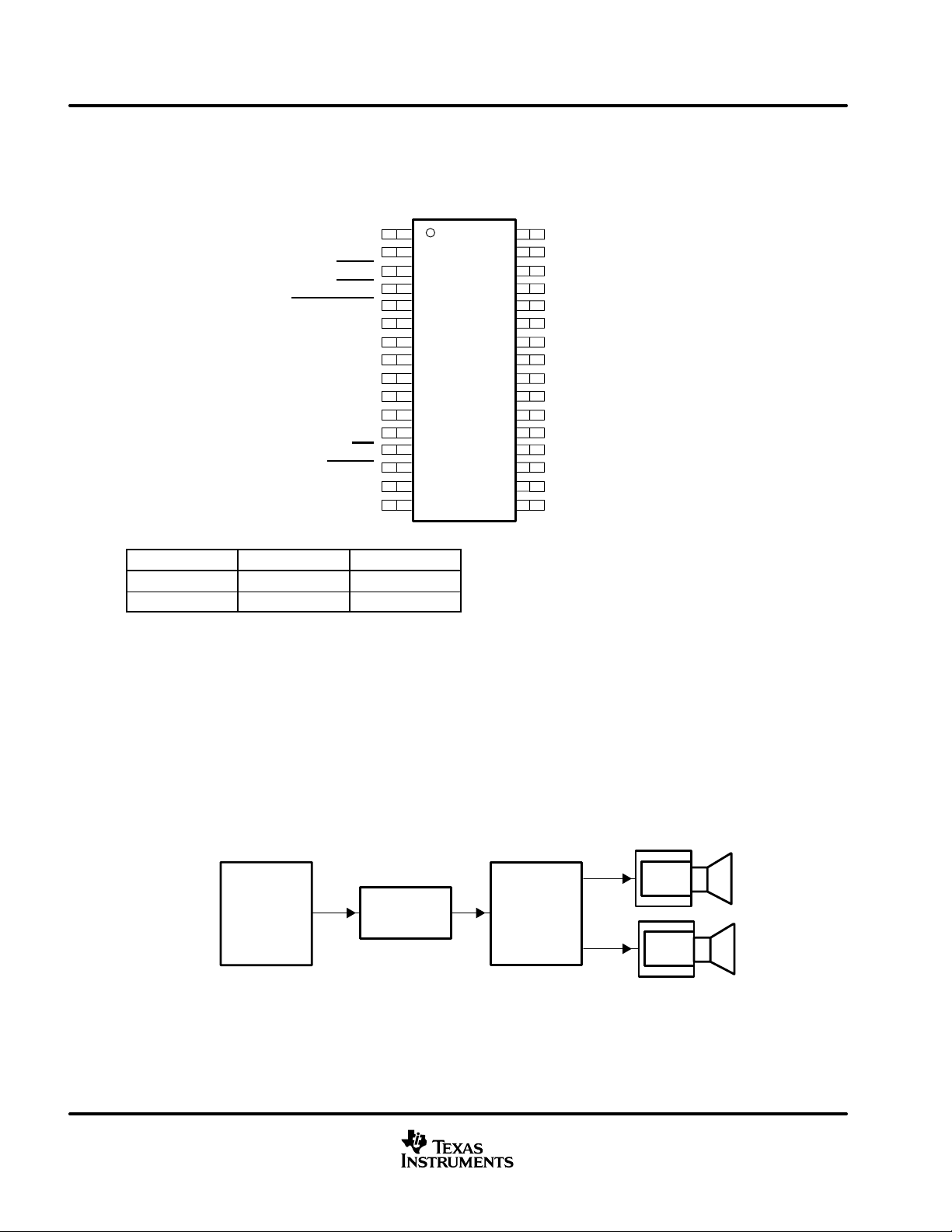

terminal assignments

The TAS5101 is offered in a thermally enhanced 32-pin HTSSOP surface-mount package (DAP).

DAP PACKAGE

(TOP VIEW)

PWM_AP

PWM_AM

ERR1

ERR0

SHUTDOWN

DVDD

DVSS

DVSS

DVSS

VRFILT

BIAS_A

BIAS_B

HiZ

RESET

PWM_BM

PWM_BP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

PVDDA2

LDROUTA

BOOTSTRAPA

PVDDA1

PVDDA1

OUTPUTA

OUTPUTA

PVSS

PVSS

OUTPUTB

OUTPUTB

PVDDB1

PVDDB1

BOOTSTRAPB

LDROUTB

PVDDB2

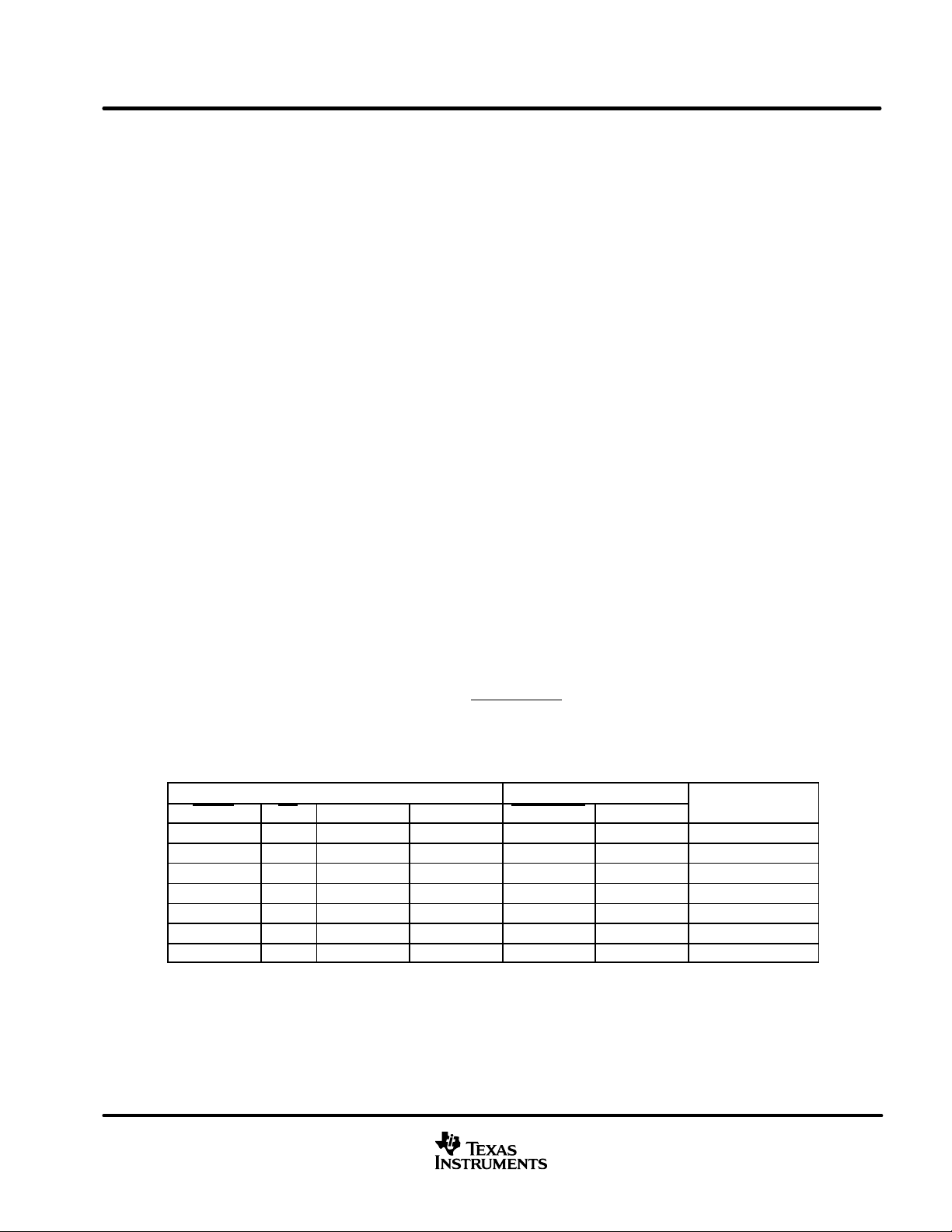

ordering information

T

A

0°C to 70°C TAS5101DAP TAS5101DAPR

–40°C to 85°C TAS5101IDAP TAS5101IDAPR

PACKAGE TAPE and Reel

references

TAS5010 Digital Audio PWM Processor Data Manual – TI Literature Number SLAS328

System Design Considerations for True Digital Audio Power Amplifiers – TI Literature Number SLAA117

Digital Audio Measurements – TI Literature Number SLAA114

PowerPAD Thermally Enhanced Package – TI Literature Number SLMA002

T AS5101_SE Application Report – TI Literature Number SLEA001

suggested system block diagrams

See application note SLAA117 for more details.

Digital Audio

• TAS3001

• TAS3103

• DSP

• DIR1703

• 1394

• Digital Parametric EQ

• Volume

TAS5010

• Serial Audio Input Port

• Internal PLL

TAS5101

• 2 × 1/2 H-Bridge

• DRC

• Bass

• Treble

Figure 1. System #1: Stereo Configuration With TAS3001 Digital Audio Processor

L-C

Filter

L-C

Filter

2

www.ti.com

A

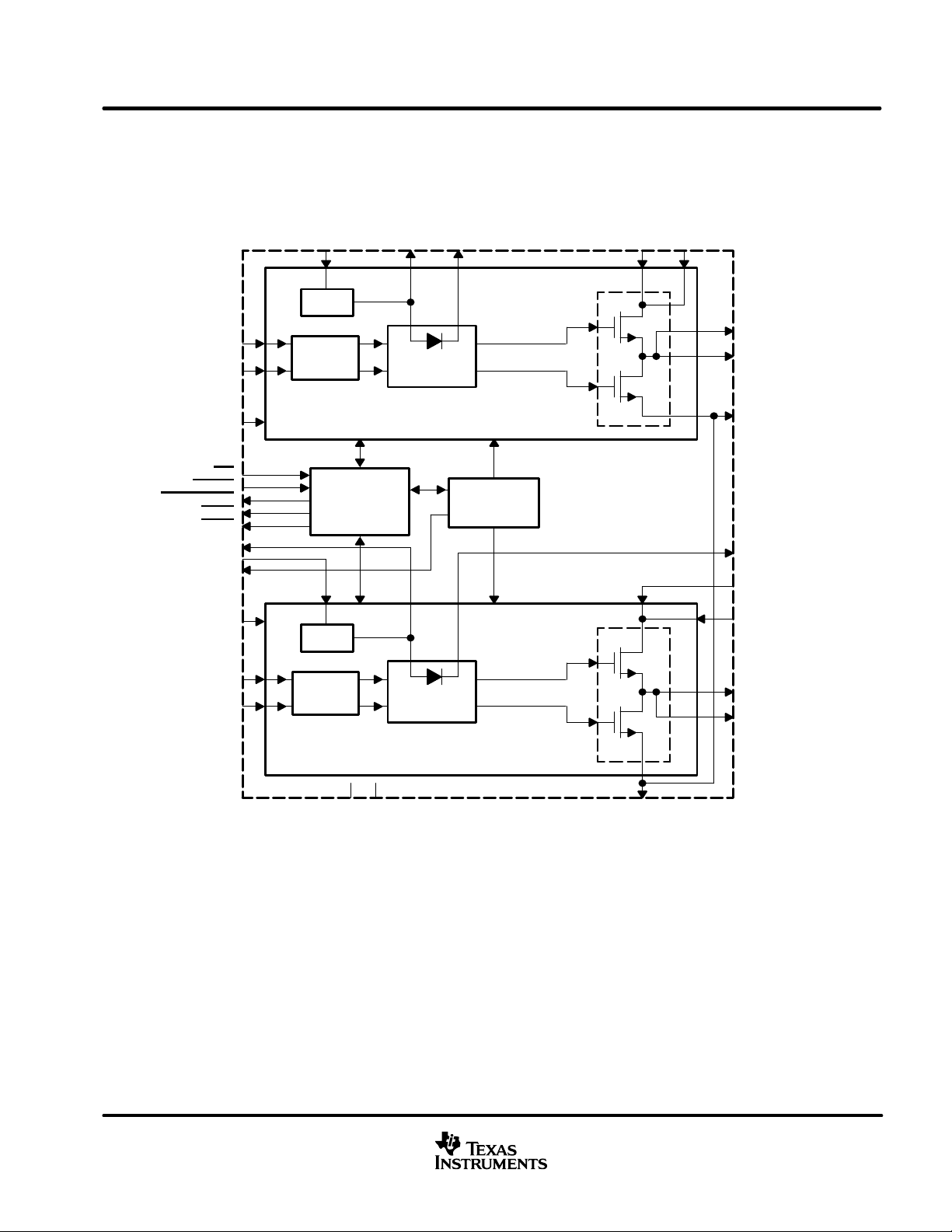

functional block diagram

TAS5101

SLES039 – JUNE 2002

PWM_AP

PWM_AM

BIAS_A

HiZ

RESET

SHUTDOWN

ERR1

ERR0

LDROUTB

PVDDB2

VRFILT

BIAS_B

PWM_BM

PWM_BP

PVDDA2

LDR

DIFF

RCVR

Control/Sense

Circuit

LDR

DIFF

RCVR

LDROUTA

Boot Strap

Gate Drive

Boot Strap

Gate Drive

BOOTSTRAP

1/2 H-Bridge

Bandgap

Reference

1/2 H-Bridge

PVDDA1

PVDDA1

OUTPUTA

OUTPUTA

PVSS

BOOTSTRAPB

PVDDB1

PVDDB1

OUTPUTB

OUTPUTB

DVDD

DVSS

www.ti.com

PVSS

3

TAS5101

SLES039 – JUNE 2002

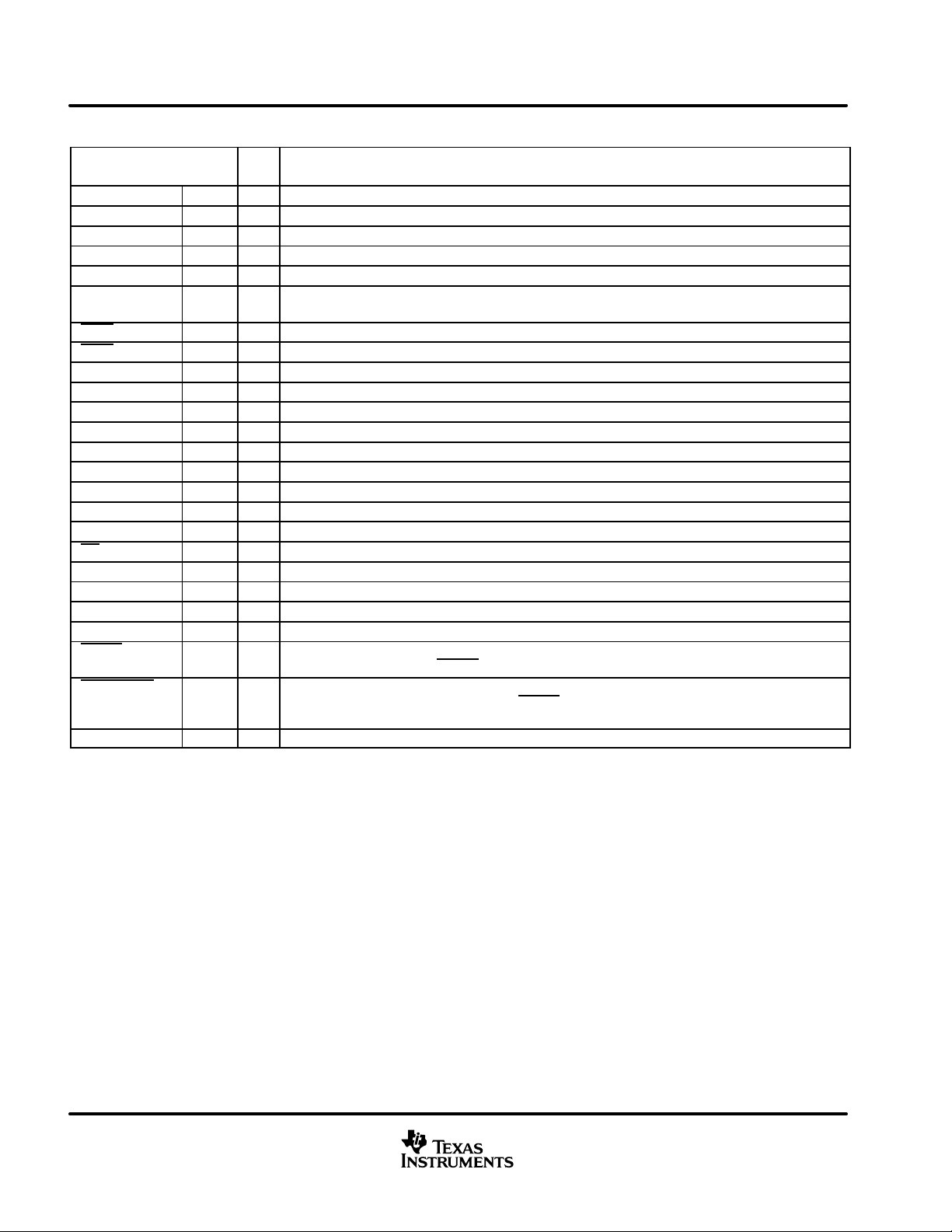

Terminal Functions

TERMINAL

NAME NO.

BIAS_A 11 I Connect external resistor to DVSS. See application note SLAA117

BIAS_B 12 I Connect external resistor to DVSS. See application note SLAA117

BOOTSTRAPA 30 O Bootstrap capacitor pin for H-bridge A

BOOTSTRAPB 19 O Bootstrap capacitor pin for H-bridge B

DVDD 6 I 3.3-V digital voltage supply for logic

DVSS 7, 8, 9 I Digital ground for logic is internally connected to PVSS. All three pins must be tied together but not

ERR1 3 O Error/warning report indicator. This output is open drain with internal pullup resistor.

ERR0 4 O Error/warning report indicator. This output is open drain with internal pullup resistor.

LDROUTA 31 O Low voltage drop-out regulator output A (not to be used to supply current to external circuitry)

LDROUTB 18 O Low voltage drop-out regulator output B (not to be used to supply current to external circuitry)

OUTPUTA 26, 27 O H-bridge output A

OUTPUTB 22, 23 O H-bridge output B

PVDDA1 28, 29 I High voltage power supply , H-bridge A

PVDDA2 32 I High voltage power supply for low-dropout voltage regulator A-side

PVDDB1 20, 21 I High voltage power supply , H-bridge B

PVDDB2 17 I High voltage power supply for low-dropout voltage regulator B-side

PVSS 24, 25 I High voltage power supply ground

HiZ 13 I HiZ = 0, when asserted, the H-bridge output is set to high-impedance mode

PWM_AP 1 I PWM input A(+)

PWM_AM 2 I PWM input A(–)

PWM_BP 16 I PWM input B(+)

PWM_BM 15 I PWM input B(–)

RESET 14 I Reset and mute mode = 0, normal mode = 1, when in reset mode, H-bridge MOSFETs are in low-low

SHUTDOWN 5 O Device is in shutdown due to fault condition, normal mode = 1, shutdown = 0. The shutdown

VRFILT 10 O A filter capacitor should be added between VRFIL T and DVSS pins.

NOTE: The four PWM inputs: PWM_AP , PWM_AM, PWM_BP, and PWM_BM must always be connected to the TAS5010 output pins, and never

left floating. Floating PWM input pins will cause an illegal PWM input state signal to be asserted.

I/O

connected externally to PVSS. See Figure 5.

output state. Asserting the RESET

condition can be cleared by asserting the RESET

pullup resistor.

DESCRIPTION

signal low causes all fault conditions to be cleared.

signal. This output is open drain with internal

Dual pins: OUTPUTA, OUTPUTB, PVDDA1 and PVDDB1 must have both pins connected externally to the same point on the circuit board,

respectively. Both PVSS pins must also be connected together externally. These multiple pins are for the high current DMOS output

devices. Failure to connect all the multiple pins to the same respective node will result in excessive current flow in the internal bond wires

and can cause the device to fail. All electrical characteristics are specified and measured with all of the multiple pins conne cted to the same

node, respectively .

4

www.ti.com

SLES039 – JUNE 2002

functional description

PWM H-bridge state control

The digital interface control signals consists of PWM_AP, PWM_AM, PWM_BP, and PWM_BM. These signals

are a complementary differential signal format for the A-side H-bridge and the B-side H-bridge.

bootstrapped gate drive

The TAS5101 includes 2 dedicated bootstrapped power supplies. A bootstrap capacitor is connected between

the individual bootstrap pin and the associated output as described in the application note SLAA117. For

example, a capacitor will be connected between the BOOTSTRAPA pin and OUTPUTA pin, and another

capacitor will be connected between the BOOTSTRAPB pin and the OUTPUTB pin. The bootstrap power

supply minimizes the number of high voltage power supply levels externally supplied to the system while

providing a low noise supply level for driving the high-side N-channel DMOS transistors. See application note

SLAA117 for details.

low-dropout voltage regulator

Two on-chip low-dropout voltage regulators (LDO) are provided to minimize the number of external power

supplies needed for the system. These voltage regulators are for internal circuits only and cannot be used for

external circuitry. Each LDO is dedicated to an H-bridge and its gate driver. An LDO output capacitor is

connected between the individual LDO output pin and the associated output return as described in the

application note SLAA1 17. For example, a capacitor will be connected between the LDROUTA pin and PVSS

pin, and another capacitor will be connected between the LDROUTB pin and PVSS pin. This capacitor is usually

0.1 µF.

TAS5101

high-current H-bridge output stage

The positive outputs of the H-bridge are the two OUTPUT A pins. The negative outputs of the H-bridge are the

two OUTPUTB pins. The logic for the input command to H-bridge outputs is described in the H-bridge output

mapping section below. When the TAS5101 is in the normal mode, as seen in the H-bridge output mapping

tables, the outputs are decoded from the inputs. However, the TAS5101 is immediately shut down if any of the

following error conditions occur: over-current, over-temperature, low regulator output voltage, or an illegal PWM

input state is applied. For these conditions, the outputs are set to the appropriate disabled state as specified

in the H-bridge output mapping section, and the SHUTDOWN

pin is set low.

H-bridge output mapping

The A-side and B-side H-bridge output is designed to the following truth table:

INPUTS OUTPUTS

RESET HiZ PWM_AP/BP PWM_AM/BM SHUTDOWN OUTPUTA/B

X X X X 0 0 or Hi-Z

X 0 X X 1 Hi-Z High Impedance

0 1 X X 1 0 Low

1 1 0 0 0 0 Low

1 1 0 1 1 0 Normal

1 1 1 0 1 1 Normal

1 1 1 1 0 0 Low

†

Output is 0 for low voltage, over temperature, and illegal input. Hi-Z is for over current.

†

DESCRIPTION

Shutdown

www.ti.com

5

TAS5101

SLES039 – JUNE 2002

control/sense circuitry

The control/sense circuitry consists of the following 3.3-V logic level pins: HiZ

SHUTDOWN

to the Hi-Z state. When the HiZ

so that their outputs can be pulled high. The active-low RESET

low-low state and resets the over-current shutdown latch. The HiZ

ERR1

, and SHUTDOWN outputs indicate the following conditions in the T AS5101 as shown in the table below.

. The active-low HiZ input pin powers down all internal circuitry and forces the H-bridge outputs

pin is low, the open drain ERR0, ERR1, and SHUTDOWN pins are also disabled

input pin forces the H-bridge outputs to the

pin overrides the RESET pin. The ERR0,

, RESET, ERR0, ERR1, and

These three outputs are open-drain connections with internal pullup resistors so that wire-ORed connections

can be made by the user with other external control devices. The short circuit protect error condition will latch

the T AS5101 in this shutdown state and force the H-bridge outputs to the Hi-Z state until the device is reset by

means of the RESET

pin. The illegal PWM input state, over-temperature, and low regulator voltage error

conditions will not latch the device in the shutdown condition. Instead the H-bridge outputs are forced to the

low-low state and the TAS5101 will return to normal operation as soon as the error condition ends. Loss of

clocking PWM signal is also considered an illegal PWM input state.

SHUTDOWN ERR1 ERR0 FUNCTION OUTPUTA OUTPUTB

0 0 0 Illegal PWM input state Low Low

0 0 1 Short circuit protect (latch) Hi-Z Hi-Z

0 1 0 Over temperature protect Low Low

0 1 1 Low regulator voltage protect Low Low

1 0 0 Reserved — —

1 0 1 Reserved — —

1 1 0 High temperature – warning Normal Normal

1 1 1 Normal operation Normal Normal

6

www.ti.com

SLES039 – JUNE 2002

device operation

power sequences

system power-up/power-down sequencing

The recommended power-up/power-down sequence is shown in Figure 3. For proper operation the RESET

signal should be kept LOW when both DVDD and output power (PVDDA1, PVDDA2, PVDDB1, and PVDDB2)

are being applied. The RESET

DVDD

PVDDA1

PVDDA2

PVDDB1

PVDDB2

> 100 ms

RESET/HiZ

signal should remain LOW for at least 1 ms after output power is applied.

> 1 ms

> 1 ms

TAS5101

NOTE: This power-up/power-down sequence will ensure that there are no device reliability issues. However, audio artifacts during power cycling

may occur (see TAS5101_SE Application Report (SLEA001) for more information).

Figure 2. Power-Up/Power-Down Sequence

RESET

function

The device is put into a reset condition when the (active low) RESET

signal is asserted. While in the reset state,

the input H-bridge control signals consisting of PWM_AP , PWM_AM, PWM_BP , and PWM_BM are ignored, and

the H-bridge MOSFETs are placed in a state where OUTPUTA and OUTPUTB are both low. Asserting the

RESET

signal low also causes the short circuit protection latch to be reset. The RESET and HiZ signals are

normally connected to the VALID signal from the TAS5010, when used in a single-ended configuration.

function

HiZ

The HiZ

placing pin 13 at logic low. This function is usually used in conjunction with the RESET

function places the output MOSFETs in a high-impedance state when this function is asserted by

function during power

on and off to reduce or eliminate “pops and clicks” associated with powering the amplifier.

reinitialization sequence

Proper initial conditions for this device include asserting the RESET

and HiZ signals until the reset operation

has completed (1 ms). Additionally, when using this device with the TAS5010 controller, this function can be

accomplished by asserting the reset pin on the TAS5010 during the reset sequence (see Figure 3).

audio application considerations

power supply decoupling

Power supply decoupling and layout optimization information should be obtained by following the detailed

information in the application note SLEA005.

optimal power transfer for H-bridge

The T AS5101 is a power H-bridge that is designed to deliver 2 × 15 W/rms into loads of 4 Ω in a single-ended

configuration. Rather than requiring the usual heatsink, the package is designed to deliver this wattage by

careful layout as described in the application note SLAA1 17. Careful attention must be given to the value of the

high-voltage power supply level for a given load resistance. See recommended operating conditions.

www.ti.com

7

TAS5101

SLES039 – JUNE 2002

audio application considerations (continued)

reconstruction output filter

An output reconstruction filter is required between the H-bridge outputs and the loudspeaker load. This second

order low-pass filter passes the audio information to the loudspeaker, while filtering out the high frequency

out-of-band information contained in the H-bridge output PWM pulses. The values of the L and C components

selected are dependent on the loudspeaker load impedance. See application note SLAA117.

fault indicator usage

The T AS5101 is a self-protecting device that provides device fault reporting, including over-temperature protect,

under-voltage lockout (low-regulator voltage), and short circuit protection. The short circuit protection protects

against short circuits that may occur at the loudspeaker load when configured according to the application note

SLAA117. The TAS5101 is not recommended for driving loads less than 4 Ω, since the internal current limit

protection might be activated.

An under-voltage lockout signal occurs when an insufficient voltage level is present on the LDROUTA or

LDROUTB pins. During this condition gate drive levels are not sufficient for driving the power MOSFET s. Normal

operation is resumed when the minimum proper LDROUT A or LDROUTB level is obtained, and the low regulator

voltage protect signal is de-asserted. See the control/sense circuitry section for error and warning conditions.

A high temperature warning signal is asserted on pin ERR0

when the device temperature exceeds 125°C

typical.

If the internal device temperature exceeds 150°C typical, the over temperature protect signal is asserted and

the TAS5101 is shut down. The device will re-enable once the temperature drops to 125°C typical. See the

control/sense circuitry section for error and warning conditions.

Detection of an illegal PWM input state or the loss of a clocking PWM input signal will cause an illegal PWM input

state signal to be asserted on the ERR1

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

and ERR0 pins and will set the SHUTDOWN pin to the low state.

†

DC supply voltage range: DVDD to DVSS –0.3 V to 5.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PWM_AP, PWM_AM, PWM_BP, PWM_BM –0.3 V to DVDD + 0.3 V. . . . . . . . . . . . . . . . .

RESET

, HiZ –0.3 V to DVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PVDDA1 to PVSS, PVDDB1 to PVSS –0.3 V to 28 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PVDDA2 to PVSS, PVDDB2 to PVSS –0.3 V to 28 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output DMOS drain-to-source breakdown voltage 28 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating junction temperature range, T

Storage temperature range, T

stg

–40°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

J

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds) 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

8

www.ti.com

yg

SLES039 – JUNE 2002

recommended operating conditions (nominal output power = 2 × 15 W (RMS), TA = 25°C)

TAS5101

thermal data

Shutdown junction temperature, T

Warning junction temperature, T

p

Operating ambient temperature, T

Thermal resistance junction-to-ambient, θ

Thermal resistance junction-to-case, θ

Thermal resistance junction-to-ambient, θ

†

One of the most influential components on the thermal performance of a package is board design. In order to take full advantage of the heat

dissipating abilities of the PowerP AD packages, a board must be used that acts similar to a heat sink and allows for the use of the exposed (and

solderable), deep downset pad. See Appendix A of the PowerP AD Thermally Enhanced Package application note, TI literature number SLMA002

and the Thermal Design of the PowerPad PCB Layout section of the System Design Considerations for True Digital Audio Power Amplifiers

application note, TI literature number SLAA117.

†

PARAMETER MIN NOM MAX UNIT

J(SD)

J(W)

p

A

jc

Commercial 0 25 70

Industrial –40 25 85

2 oz. trace and copper pad with solder 23.5 °C/W

ja

2 oz. trace and copper pad without solder 0.32 °C/W

2 oz. trace and copper pad without solder 44.3 °C/W

ja

150 °C

125 °C

°

°C

RL = 4 Ω to 8 Ω

PARAMETER MIN NOM MAX UNIT

Digital DVDD to DVSS 3 3.3 3.6 V

PVDDA2 to PVSS 16.5 26.5 28

Supply voltage

†

If PVDD is greater than 26.5 V , 15 Watts per channel is still the maximum specified continuous output power.

‡

If using a PVVD power supply less than 16.5 V, connect LDROUTA to PVDDA2 and connect LDROUTB to PVDDB2. Under this condition

H-Bridge forward on-state resistance is increased. This will increase internal power dissipation. Maximum output power may need to be reduced

to meet thermal conditions.

Regulator

PVDDB2 to PVSS 16.5 26.5 28

PVDDA2 to PVSS

PVDDB2 to PVSS

}

}

10.5 16.5

10.5 16.5

V

maximum available power at common load impedance for DAP package unclipped (0 dB) level

LOAD IMPEDANCE

†

Dependent on board design and component selection.

(Ω)

4 26.5 15

6 27 12.85

8 27 9.64

PVDAA1/PVDDB1

(VDC)

APPROXIMATE MAX OUTPUT POWER

(W)

THD+N AT MAX POWER AND 1 kHz INPUT

< 0.1%

< 0.09%

< 0.09%

†

www.ti.com

9

TAS5101

SLES039 – JUNE 2002

static digital specifications

RESET, HiZ, PWM_AP, PWM_AM, PWM_BP, PWM_BM, TA = 25°C, DVDD = 3.3 V

PARAMETERS MIN MAX UNIT

High-level input voltage, V

Low-level input voltage, V

Input leakage current –10 10 µA

IH

IL

ERR0, ERR1, SHUTDOWN, (open drain with internal pullup resistor) TA = 25°C, DVDD = 3.3 V)

PARAMETERS MIN MAX UNIT

Internal pullup resistors from SHUTDOWN, ERR0, ERR1 to DVDD 15 kΩ

Low-level output voltage (IO = 4 mA), V

OL

TAS5010/TAS5101 system performance measured at the speaker terminals

See the TI Literature Number SLAA117 for TAS5010/TAS5101 system performance.

electrical characteristics

2 V

0.8 V

0.4 V

supply, TA = 25°C (F

switching

= 384 kHz, OUTPUTA and OUTPUTB not connected, DVDD = 3.3 V,

PVDDA1 = 26.5 V, PVDDB1 = 26.5 V, PVDDA2 = 26.5 V, PVDDB2 = 26.5 V, 50% input duty cycle)

PARAMETER TYP MAX UNIT

DVDD Operating 2 mA

Supply current

†

13-kΩ resistor from BIAS_A (pin 11) to DVSS and 13-kΩ resistor from BIAS_B (pin 12) to DVSS.

PVDDA1+PVDDB1+

PVDDA2+PVDDB2

Operating

†

20 mA

H-Bridge transistors, PVDDA2 = PVDDB2 = 22 V, DVDD = 3.3 V, TA = 25°C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Drain-to-source breakdown voltage ID = 1 mA, HiZ = 0, Hi-Z state 28 V

Forward on-state resistance, low-side drivers

OUTPUTA and OUTPUTB to PVSS

Forward on-state resistance, high-side drivers

PVDDA1 to OUTPUTA, PVDDB1 to OUTPUTB

On-state resistance matching low side 98%

On-state resistance matching high side 98%

NOTES: 1. Test time should be < 1 ms to avoid temperature change.

2. These parameters are measured with voltage-sensing contacts separate from the current-carrying contacts.

3. Connect PVDDA2 and PVDDB2 to 26.5-V power supply with respect to PVSS. LDROUTA, LDROUTB, BOOTSTRAPA, and

BOOTSTRAPB pins open.

4. Connect PVDDA2 to 26.5-V power supply with respect to PVSS. LDROUTA, LDROUTB, BOOTSTRAPA and BOOTSTRAPB

capacitors are connected respectively. Clock PWM inputs to allow bootstrap capacitors to charge. 93–99% modulation must be used

on PWM_AP , PWM_AM, PWM_BP, and PWM_BM inputs to prevent the activity detector from shutting down the device during this

measurement. Note that F

switching

I

= 2.5 A,

SINK

See Notes 2, 3, and 4,

I

SOURCE

See Notes 2, 3, and 5,

= 384 kHz.

= 2.5 A,

PWM_AP = PWM_BP = 0,

PWM_AM = PWM_BM = 1

PWM_AP = PWM_BP = 1,

PWM_AM = PWM_BM = 0

0.2

0.2 Ω

Ω

electrical characteristics, voltage regulator, TA = 25°C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Output voltage (LDROUTA, LDROUTB)

NOTE 5: These voltage regulators are for internal gate drive circuits only and are not to be used under any circumstances to supply current to

external circuity .

IO = 5 mA, PVDDA2=PVDDB2 = 18 V to 28 V,

See Note 6, DVDD = 3.3 V

14.5 15.3 16 V

10

www.ti.com

SLES039 – JUNE 2002

THERMAL INFORMATION

The thermally enhanced DAP package is based on the 32-pin HTSSOP, but includes a thermal pad (see

Figure 4) to provide an effective thermal contact between the IC and the PWB.

Traditionally, surface mount and power have been mutually exclusive terms. A variety of scaled-down TO-220

type packages have leads formed as gull wings to make them applicable for surface-mount applications. These

packages, however, have two shortcomings: they do not address the very low profile requirements (<2 mm) of

many of today’s advanced systems, and they do not offer a terminal-count high enough to accommodate

increasing integration. On the other hand, traditional low-power surface-mount packages require

power-dissipation derating that severely limits the usable range of many high-performance analog circuits.

The PowerPAD package (thermally enhanced HTSSOP) combines fine-pitch surface-mount technology with

thermal performance comparable to much larger power packages.

The PowerP AD package is designed to optimize the heat transfer to the PWB. Because of the very small size

and limited mass of a HTSSOP package, thermal enhancement is achieved by improving the thermal

conduction paths that remove heat from the component. The thermal pad is formed using a patented lead-frame

design and manufacturing technique to provide a direct connection to the heat-generating IC. When this pad

is soldered or otherwise thermally coupled to an external heat dissipater, high power dissipation in the ultrathin,

fine-pitch, surface-mount package can be reliably achieved.

TAS5101

DIE

Side View (a)

DIE

End View (b)

Thermal

Pad

Bottom View (c)

Figure 3. Views of Thermally Enhanced DAP Package

www.ti.com

11

TAS5101

SLES039 – JUNE 2002

APPLICATION INFORMATION

TAS5010

PWM_BP

PWM_BM

RESET

VALID_L

PWM_AM

PWM_AP

Error

Reporting

C10

C9

R1

R2

TAS5101

1

PWM_AP

2

PWM_AM

3

ERR1

4

ERR0

5

SHUTDOWN

6

DVDD

7

DVSS

8

DVSS

9

DVSS

10

VRFILT

11

BIAS_A

12

BIAS_B

13

HiZ

14

RESET

15

PWM_BM

16

PWM_BP

NOTE:C1, C2 = 1.0 µF

C3, C4 = 470 µF

C5, C8 = 0.033 µF

C6, C7 = 0.1 µF

C9, C10 = 0.1 µF

C11, C12 = 0.1 µF

R1, R2 = 13 kΩ

R3, R4 =4.7 kΩ

L1, L2 = 10 µH

PVDDA2

LDROUTA

BOOTSTRAPA

PVDDA1

PVDDA1

OUTPUTA

OUTPUTA

PVSS

PVSS

OUTPUTB

OUTPUTB

PVDDB1

PVDDB1

BOOTSTRAPB

LDROUTB

PVDDB2

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

C5

C11

26.5 V

C8 C7

C6

26.5 V

L1

L2

C1

C2

26.5 V

Snubber

Circuit

Snubber

Circuit

C3

C4

R3

R4

Figure 4. Typical TAS5101 Application (One Channel Shown)

See the application note, TI literature number SLEA001 for detailed application information.

12

www.ti.com

TAS5101

SLES039 – JUNE 2002

MECHANICAL DATA

DAP (R-PDSO-G**) PowerPAD PLASTIC SMALL-OUTLINE PACKAGE

38 PINS SHOWN

0,65

38

1

1,20 MAX

0,30

0,19

20

19

A

0,15

0,05

0,13

6,20

NOM

M

Thermal Pad

(see Note D)

8,40

7,80

0,15 NOM

Gage Plane

0,25

0°–ā8°

0,75

0,50

Seating Plane

0,10

PINS **

DIM

A MAX

A MIN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion.

D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically

and thermally connected to the backside of the die and possibly selected leads. Thermal pad size is 3,86 mm X 3,91 mm for the

32-pin T AS5101 device.

E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

28

9,80

9,60

30

11,10

10,90

www.ti.com

32

11,10

38

12,60

12,4010,90

4073257/A 07/97

13

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty . Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty . Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. T o minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third–party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party , or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2002, Texas Instruments Incorporated

Loading...

Loading...