Data Manual

June 2002 Digital Audio Products

SLES025A

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty . Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty . Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. T o minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party , or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and is

an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2002, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Functional Block Diagram 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Terminal Assignments—Normal Mode 1–3. . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Terminal Assignments—External MCU Mode 1–4. . . . . . . . . . . . . . . . . . . .

1.5 Ordering Information 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Terminal Functions—Normal Mode 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7 Terminal Functions—External MCU Mode 1–6. . . . . . . . . . . . . . . . . . . . . .

1.8 Device Operation Modes 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.9 Terminal Assignments for Codec Port Interface Modes 1–7. . . . . . . . . . .

2 Description 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Architectural Overview 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Oscillator and PLL 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Clock Generator and Sequencer Logic 2–1. . . . . . . . . . . . . . . .

2.1.3 Adaptive Clock Generator (ACG) 2–1. . . . . . . . . . . . . . . . . . . . .

2.1.4 USB Transceiver 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.5 USB Serial Interface Engine (SIE) 2–1. . . . . . . . . . . . . . . . . . . .

2.1.6 USB Buffer Manager (UBM) 2–2. . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.7 USB Frame Timer 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.8 USB Suspend and Resume Logic 2–2. . . . . . . . . . . . . . . . . . . . .

2.1.9 MCU Core 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.10 MCU Memory 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.11 USB Endpoint Configuration Blocks and Buffer Space 2–2. . .

2.1.12 DMA Controller 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.13 Codec Port Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.14 I

2.1.15 General-Purpose IO Ports (GPIO) 2–3. . . . . . . . . . . . . . . . . . . .

2.1.16 Interrupt Logic 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.17 Reset Logic 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Device Operation 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Clock Generation 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Boot Process 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 USB Enumeration 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 TAS1020B USB Reset Logic 2–9. . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 USB Suspend and Resume Modes 2–10. . . . . . . . . . . . . . . . . . .

2.2.6 Adaptive Clock Generator (ACG) 2–11. . . . . . . . . . . . . . . . . . . . .

2.2.7 USB Transfers 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.8 Microcontroller Unit 2–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

C Interface 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

2.2.9 External MCU Mode Operation 2–24. . . . . . . . . . . . . . . . . . . . . . .

2.2.10 Interrupt Logic 2–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.11 General-Purpose I/O (GPIO) Ports 2–29. . . . . . . . . . . . . . . . . . . .

2.2.12 DMA Controller 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.13 Codec Port Interface 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

2.2.14 I

C Interface 2–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Electrical Specifications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Absolute Maximum Ratings Over Operating

Temperature Ranges 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Recommended Operating Conditions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Electrical Characteristics Over Recommended

Operating Conditions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Timing Characteristics 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Clock and Control Signals Over Recommended

Operating Conditions 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 USB Signals When Sourced by TAS1020B Over

Recommended Operating Conditions 3–2. . . . . . . . . . . . . . . . .

3.4.3 Codec Port Interface Signals (AC ’97 Modes),

= 25°C, DVDD = 3.3 V, AVDD = 3.3 V 3–3. . . . . . . . . . . . . . .

T

A

3.4.4 Codec Port Interface Signals (I2S Modes) Over

Recommended Operating Conditions 3–4. . . . . . . . . . . . . . . . . .

3.4.5 Codec Port Interface Signals (General-Purpose Mode)

Over Recommended Operating Conditions 3–4. . . . . . . . . . . . .

2

3.4.6 I

C Interface Signals Over Recommended

Operating Conditions 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Application Information 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A MCU Memory and Memory-Mapped Registers A–1. . . . . . . . . . . . . . . . . . . . . . .

A.1 MCU Memory Space A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Internal Data Memory A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 External MCU Mode Memory Space A–3. . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4 USB Endpoint Configuration Blocks and Data Buffer Space A–4. . . . . . .

A.4.1 USB Endpoint Configuration Blocks A–4. . . . . . . . . . . . . . . . . . .

A.4.2 Data Buffer Space A–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4.3 USB OUT Endpoint Configuration Bytes A–9. . . . . . . . . . . . . . .

A.4.4 USB IN Endpoint Configuration Bytes A–12. . . . . . . . . . . . . . . . .

A.4.5 USB Control Endpoint Setup Stage Data Packet Buffer A–15. .

A.5 Memory-Mapped Registers A–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.1 USB Registers A–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.2 DMA Registers A–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.3 Adaptive Clock Generator Registers A–25. . . . . . . . . . . . . . . . . . .

A.5.4 Codec Port Interface Registers A–28. . . . . . . . . . . . . . . . . . . . . . .

A.5.5 P3 Mask Register A–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

A.5.6 I

C Interface Registers A–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.7 Miscellaneous Registers A–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B Mechanical Data B–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

List of Illustrations

Figure Title Page

2–1 Adaptive Clock Generator 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 TAS1020B Interrupt, Reset, Suspend, and Resume Logic 2–25. . . . . . . . . . . . . .

2–3 Activation of Setup Stage Transaction Overwrite Interrupt 2–27. . . . . . . . . . . . . .

2–4 GPIO Port 1 and Port 3 Functionality 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Codec Port Interface Parameters – AC ’97 1.0 2–35. . . . . . . . . . . . . . . . . . . . . . . .

2–6 Codec Port Interface Parameters – AIC 2–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Codec Port Interface Parameters – I

2–8 Byte Reversal Example 2–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Connection of the TAS1020B to an AC ’97 Codec 2–40. . . . . . . . . . . . . . . . . . . . .

2–10 Connection of the TAS1020B to Multiple AC ’97 Codecs 2–41. . . . . . . . . . . . . .

2–11 Bit Transfer on the I

2–12 I

2

C START and STOP Conditions 2–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

C Bus 2–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–13 TAS1020B Acknowledge on the I

2–14 Single Byte Write Transfer 2–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–15 Multiple Byte Write Transfer 2–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–16 Single Byte Read Transfer 2–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–17 Multiple Byte Read Transfer 2–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 External Interrupt Timing Waveform 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 USB Differential Driver Timing Waveform 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 BIT_CLK and SYNC Timing Waveforms 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 SYNC, SD_IN, and SD_OUT Timing Waveforms 3–3. . . . . . . . . . . . . . . . . . . . . .

2

3–5I

S Mode Timing Waveforms 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 General-Purpose Mode Timing Waveforms 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 SCL and SDA Timing Waveforms 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Start and Stop Conditions Timing Waveforms 3–5. . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Acknowledge Timing Waveform 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Typical TAS1020B Device Connections 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 Boot Loader Mode Memory Map A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 Normal Operating Mode Memory Map A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–3 USB Endpoint Configuration Blocks and Buffer Space Memory Map A–5. . . . .

2

S2–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

C Bus 2–45. . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Tables

Table Title Page

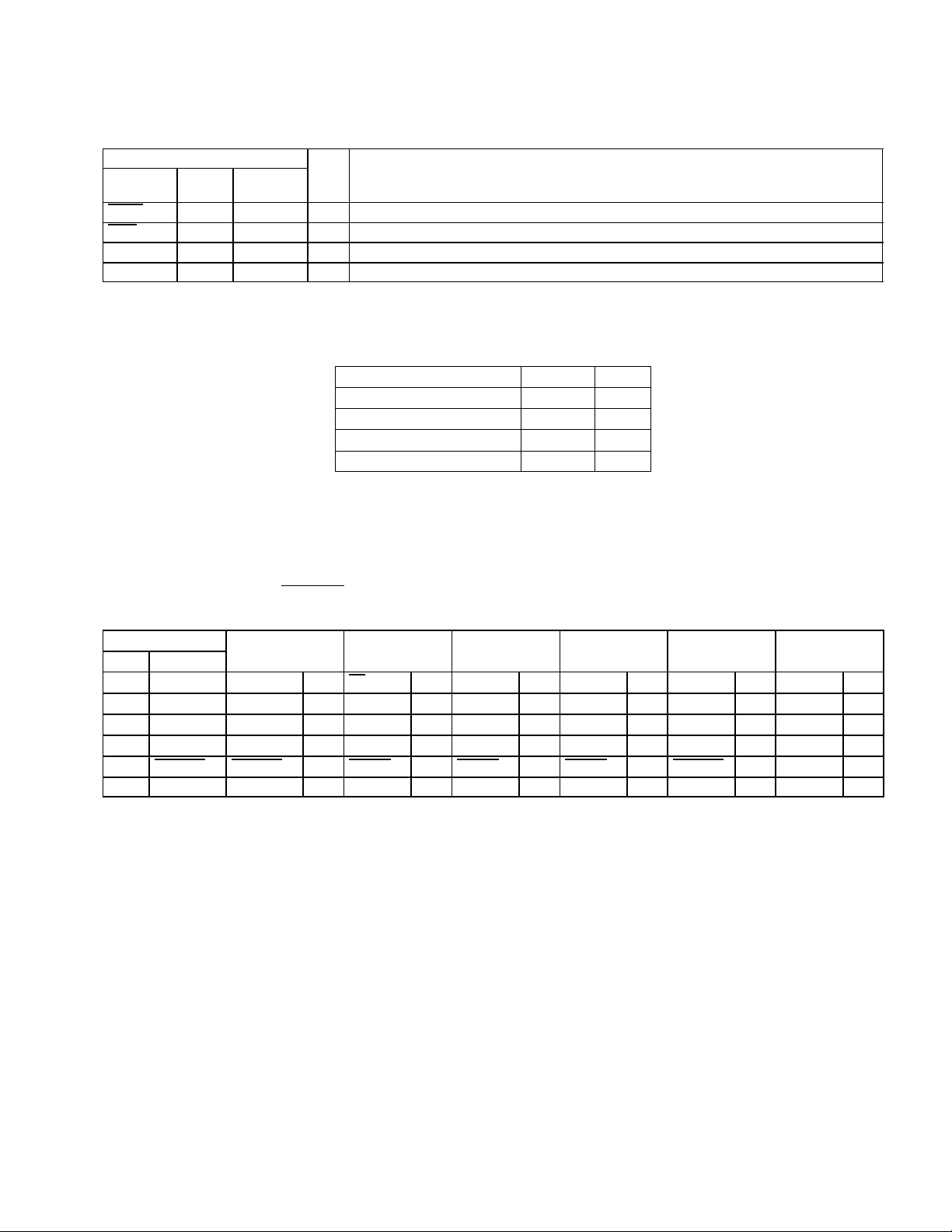

2–1 EEPROM Header 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 ACG Frequency Registers 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Terminal Assignments for Codec Port Interface General-Purpose Mode 2–33. .

2–4 Terminal Assignments for Codec Port Interface AC ’97 1.0 Mode 2–39. . . . . . . .

2–5 Terminal Assignments for Codec Port Interface AC ’97 2.0 Mode 2–40. . . . . . . .

2

2–6 Terminal Assignments for Codec Port Interface I

2–7 SLOT Assignments for Codec Port Interface I

2–8 SLOT Assignments for Codec Port Interface I

2–9 Terminal Assignments for Codec Port Interface AIC Mode 2–43. . . . . . . . . . . . . .

A–1 USB Endpoint Configuration Blocks Address Map A–6. . . . . . . . . . . . . . . . . . . . .

A–2 USB Control Endpoint Setup Data Packet Buffer Address Map A–15. . . . . . . . .

A–3 Memory-Mapped Registers Address Map A–16. . . . . . . . . . . . . . . . . . . . . . . . . . . .

S Modes 2–41. . . . . . . . . . . . .

2

S Mode 4 2–42. . . . . . . . . . . . . . .

2

S Mode 5 2–42. . . . . . . . . . . . . . .

vi

1 Introduction

The TAS1020B integrated circuit (IC) is a universal serial bus (USB) peripheral interface device designed specifically

for applications that require isochronous data streaming. Applications include digital speakers, which require the

streaming of digital audio data between the host PC and the speaker system via the USB connection. The T AS1020B

device is fully compatible with the USB Specification Version 1.1 and the USB Audio Class Specification.

The TAS1020B uses a standard 8052 microcontroller unit (MCU) core with on-chip memory. The MCU memory

includes 8K bytes of program memory ROM that contains a boot loader program. At initialization, the boot loader

program downloads the application program code to a 6,016-byte RAM from either the host PC or a nonvolatile

memory on the printed-circuit board (PCB). The MCU handles all USB control, interrupt and bulk endpoint

transactions. DMA channels are provided to handle isochronous endpoint transactions.

The USB interface includes an integrated transceiver that supports 12 Mb/s (full speed) data transfers. In addition

to the USB control endpoint, support is provided for up to seven IN endpoints and seven OUT endpoints. The USB

endpoints are fully configurable by the MCU application code using a set of endpoint configuration blocks that reside

in on-chip RAM. All USB data transfer types are supported.

The T AS1020B device also includes a codec port interface (C-Port) that can be configured to support several industry

standard serial interface protocols. These protocols include the audio codec (AC) ’97 Revision 1.X, the AC ’97

Revision 2.X and several inter-IC sound (I

A direct memory access (DMA) controller with two channels is provided for streaming the USB isochronous data

packets to/from the codec port interface. Each DMA channel can support one USB isochronous endpoint.

An on-chip phase lock loop (PLL) and adaptive clock generator (ACG) provide support for the USB synchronization

modes, which include asynchronous, synchronous and adaptive.

Other on-chip MCU peripherals include an inter-IC control (I

input/output (GPIO) ports.

2

S) modes.

2

C) serial interface, and two 8-bit general-purpose

The T AS1020B device is implemented in a 3.3-V 0.25 µm CMOS technology.

1.1 Features

• Universal Serial Bus (USB)

• USB specification version 1.1 compatible

• USB audio class specification 1.0 compatible

• Integrated USB transceiver

• Supports 12 Mb/s data rate (full speed)

• Supports suspend/resume and remote wake-up

• Supports control, interrupt, bulk, and isochronous data transfer types

• Supports up to a total of seven IN endpoints and seven OUT endpoints in addition to the control endpoint

• Data transfer type, data buffer size, single or double buffering is programmable for each endpoint

• On-chip adaptive clock generator (ACG) supports asynchronous, synchronous and adaptive

synchronization modes for isochronous endpoints

• T o support synchronization for streaming USB audio data, the ACG can be used to generate the master

clock for the codec

1–1

• Micro-Controller Unit (MCU)

• Standard 8052 8-bit core

• 8K bytes of program memory ROM that contains a boot loader program and a library of commonly used

USB functions

• 6016 bytes of program memory RAM which is loaded by the boot loader program

• 256 bytes of internal data memory RAM

• Two GPIO ports

• MCU handles all USB control, interrupt, and bulk endpoint transfers

• DMA Controller

• Two DMA channels to support streaming USB audio data to/from the codec port interface

• Each channel can support a single USB isochronous endpoint

2

• In the I

S mode the device can support DAC/ADCs at different sampling frequencies

• A circular programmable FIFO used for isochronous audio data streaming

• Codec Port Interface

2

• Configurable to support AC ’97 1.X, AC ’97 2.X, AIC or I

2

S modes can support a combination of one DAC and/or two ADCs

• I

S serial interface formats

• Can be configured as a general-purpose serial interface

• Can support bulk data transfer using DMA for higher throughput

2

C Interface

• I

• Master only interface

• Does not support a multimaster bus environment

• Programmable to 100 kb/s or 400 kb/s data transfer speeds

• Supports wait states to accommodate slow slaves

• General Characteristics

• High performance 48-pin TQFP Package

• On-chip phase-locked loop (PLL) with internal oscillator is used to generate internal clocks from a 6 MHz

crystal input

• Reset output available which is asserted for both system and USB reset

• External MCU mode supports application firmware development

• 8K ROM with boot loader program and commonly used USB functions library

• 3.3 V core and I/O buffers

1–2

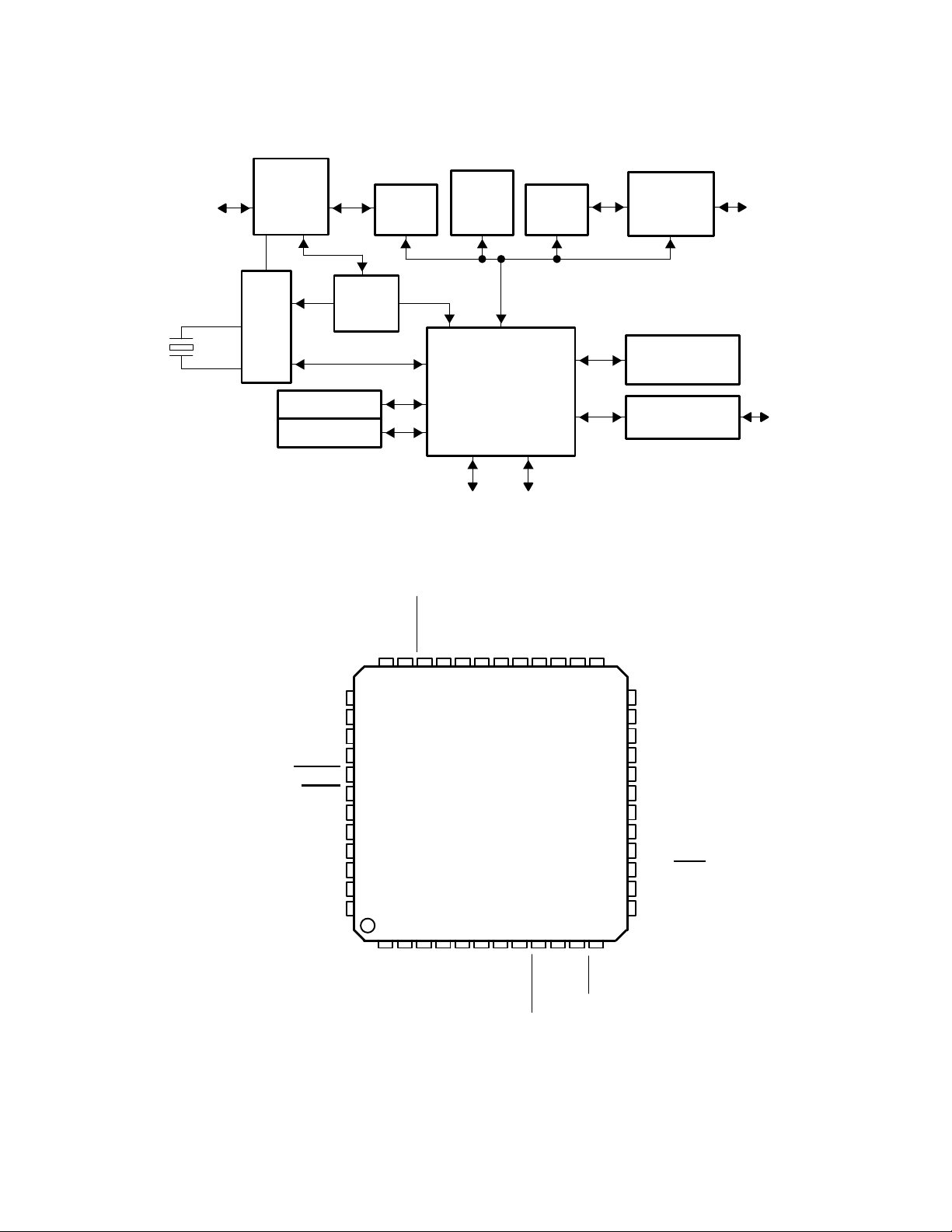

1.2 Functional Block Diagram

USB

6 MHz

USB Serial

SOF

OSC

PLL

ACG

Interface

Engine

8K ROM

6016 Byte RAM

UBM DMA

Suspend

/Resume

Logic

1520 Byte

SRAM

Port–3 Port–1

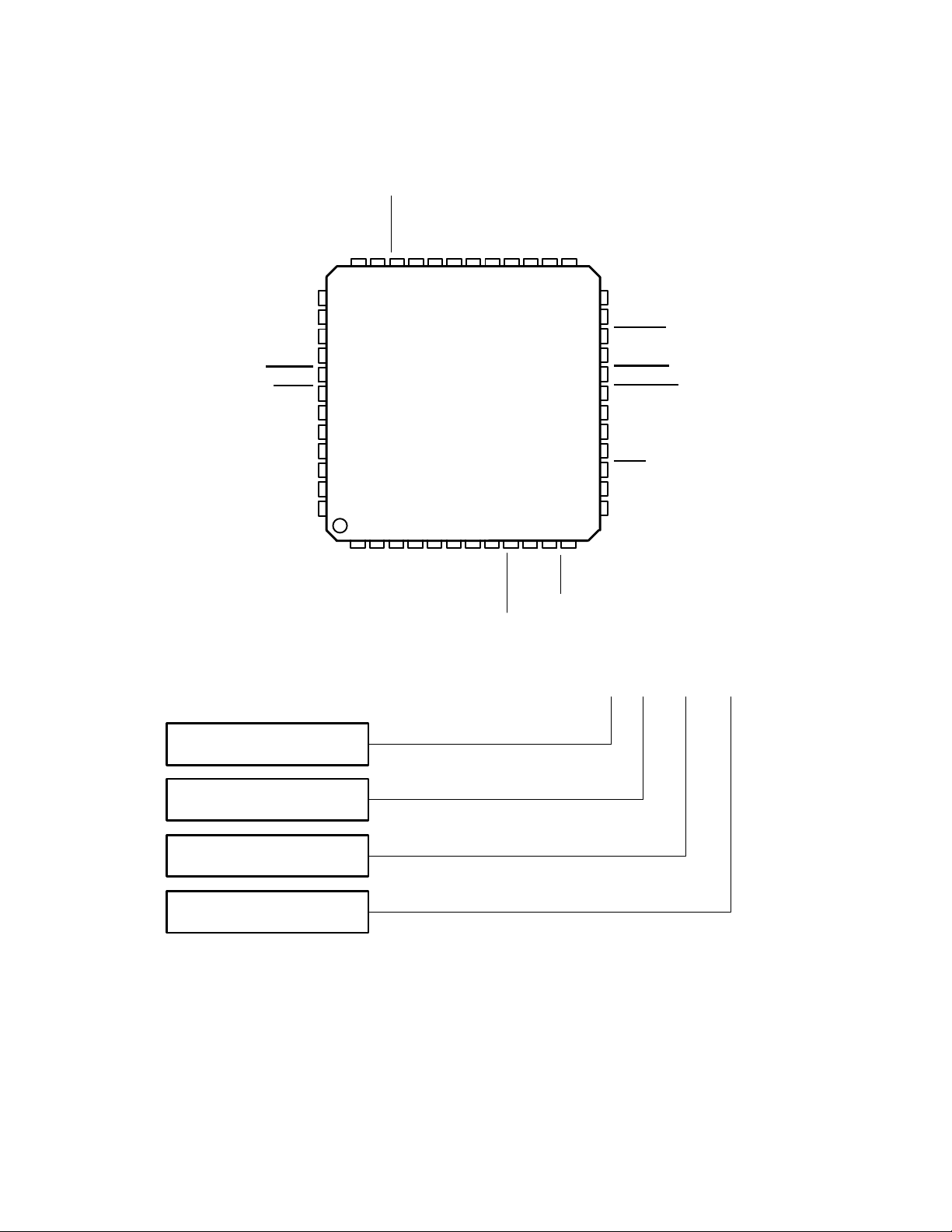

1.3 Terminal Assignments—Normal Mode

PFB PACKAGE (Normal Mode)

CDATI

CSYNC

(TOP VIEW)

DD

DV

CRESET

CSCHNE

8052 Core

P1.7

P1.6

P1.5

SS

DV

P1.4

P1.3

P1.2

CODEC

Interface

Global

Control/Status

Registers

2

I

C

Control

C–Port

I2C Bus

CSCLK

CDATO

MCLKO1

MCLKO2

RESET

VREN

SDA

SCL

AV

SS

XTALO

XTALI

PLLFILI

35 34 33 32 3136 30

37

38

39

40

41

42

43

44

45

46

47

48

23

1

DD

AV

PLLFILO

TAS1020B

5678

4

SS

DV

MCLKI

PUR

DP

DM

DD

DV

28 27 2629

9 10 11 12

TEST

EXTEN

MRESET

25

24

23

22

21

20

19

18

17

16

15

14

13

RSTO

P1.1

P1.0

NC

DV

DD

NC

P3.5

P3.4

P3.3

DV

SS

P3.2/XINT

P3.1

P3.0

1–3

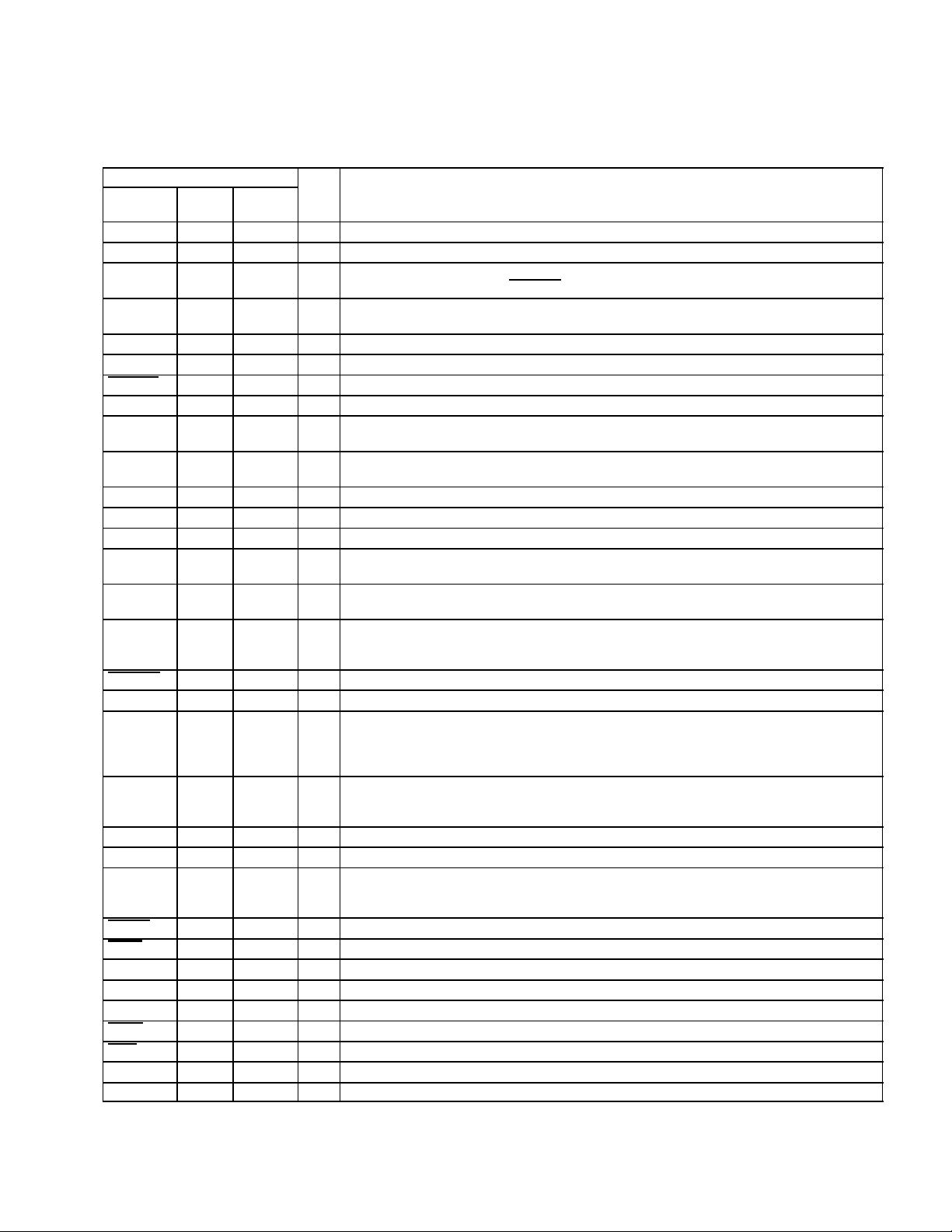

1.4 Terminal Assignments—External MCU Mode

CSCLK

CDATO

MCLKO1

MCLKO2

RESET

VREN

SDA

SCL

AV

SS

XTALO

XTALI

PLLFILI

PFB PACKAGE (External Mode)

(TOP VIEW)

DD

CDATI

CSYNC

35 34 33 32 3136 30

37

38

39

40

41

42

43

44

45

46

47

48

23

1

DD

AV

CRESET

4

MCLKI

MCUAD7

DV

CSCHNE

TAS1020B

5678

SS

DP

PUR

DV

PLLFILO

SS

MCUAD5

MCUAD6

DV

28 27 2629

9

DD

DM

DV

MRESET

MCUAD4

MCUAD3

10 11 12

TEST

EXTEN

MCUAD2

25

24

23

22

21

20

19

18

17

16

15

14

13

RSTO

MCUAD1

MCUAD0

MCURD

DV

DD

MCUWR

MCUINTO

MCUALE

MCUA10

DV

SS

XINT

MCUA9

MCUA8

1.5 Ordering Information

Texas Instruments

Audio Solutions

Peripheral Device

Package Type

TQFP

48 pins PFB

T PFB1020BAS

1–4

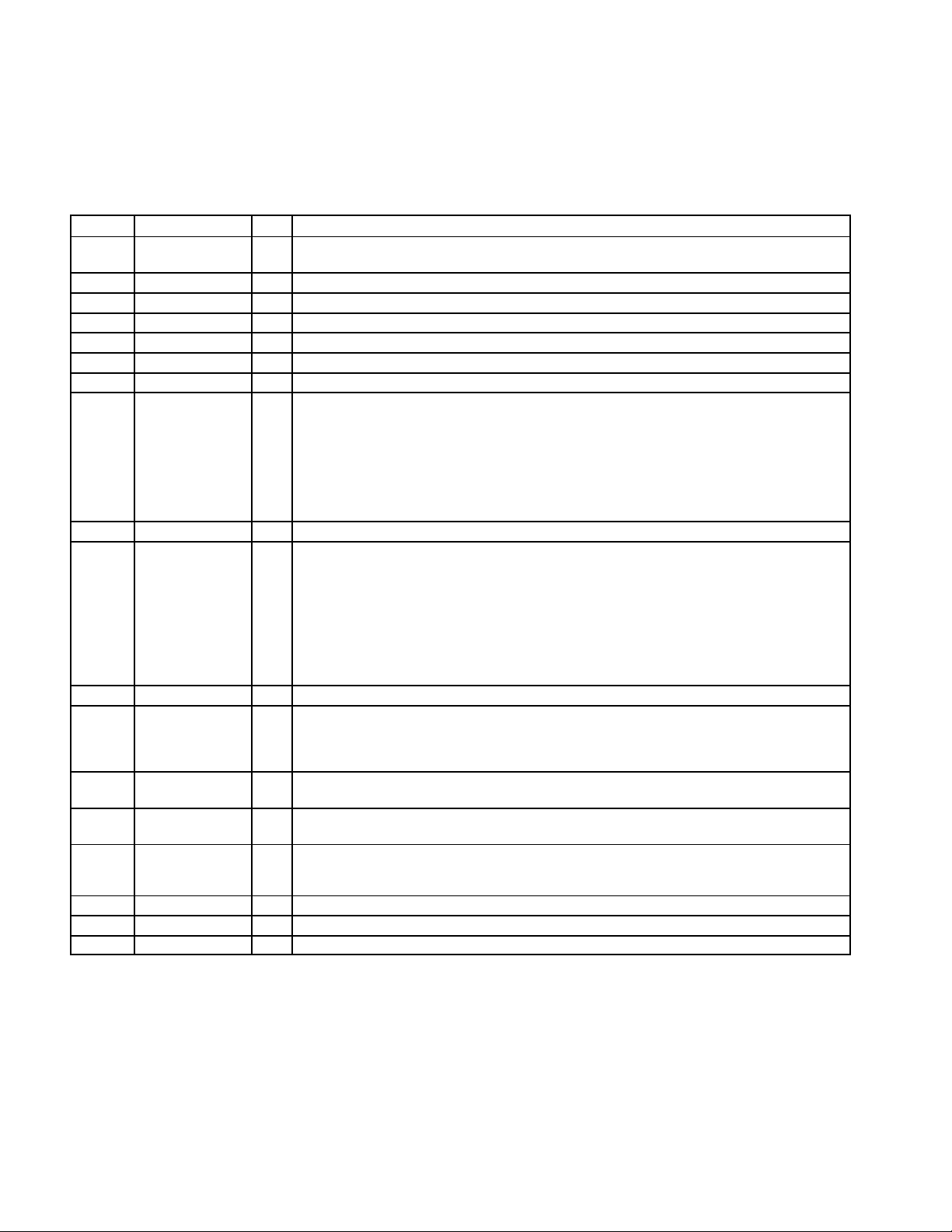

1.6 Terminal Functions—Normal Mode

TERMINAL

NAME

AV

DD

AV

SS

CSCLK CMOS 37 I/O Codec port interface serial clock: CSCLK is the serial clock for the codec port interface used to clock

CSYNC CMOS 35 I/O Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port

CDATO CMOS 38 I/O Codec port interface serial data out

CDATI CMOS 36 I/O Codec port interface serial data in

CRESET CMOS 34 I/O Codec port interface reset output

CSCHNE CMOS 32 I/O Codec port interface secondary channel enable

DP CMOS 6 I/O USB differential pair data signal plus. DP is the positive signal of the bidirectional USB differential

DM CMOS 7 I/O USB differential pair data signal minus. DM is the negative signal of the bidirectional USB differential

DV

DD

DV

SS

EXTEN CMOS 11 I External MCU mode enable: Input used to enable the device for the external MCU mode

MCLKI CMOS 3 I Master clock input. An input that can be used as the master clock for the codec port interface or the

MCLKO1 CMOS 39 O Master clock output 1: The output of the ACG that can be used as the master clock for the codec port

MCLKO2 CMOS 40 O Master clock output 2: An output that can be used as the master clock for the codec port interface and

MRESET CMOS 9 I Master reset: An active low asynchronous reset for the device that resets all logic to the default state

NC 20,22 Not used

P1.[0:7] CMOS 23, 24,

P3.[0:6] CMOS 13, 14,

PLLFILI CMOS 48 I PLL loop filter input: Input to on-chip PLL from external filter components

PLLFILO CMOS 1 O PLL loop filter output: Output from on-chip PLL to external filter components

PUR CMOS 5 O USB data signal plus pullup resistor connect. PUR is used to connect the pullup resistor on the DP

RESET CMOS 41 O General-purpose active-low output which is memory mapped

RSTO CMOS 12 O Reset output: An output that is active while the master reset input or the USB reset is active

SCL CMOS 44 O I2C interface serial clock

SDA CMOS 43 I/O I2C interface serial data

TEST CMOS 10 I Test mode enable: Factory test mode

VREN CMOS 42 O General-purpose active-low output which is memory mapped

XINT CMOS 15 I External interrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU

XTALI CMOS 47 I Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal

XTALO CMOS 46 O Crystal Output: Output from the on-chip oscillator to an external 6-MHz crystal

PIN

TYPE

Power 2 3.3-V analog supply voltage

Power 45 Analog ground

Power 8, 21, 33 3.3-V digital supply voltage

Power 4, 16, 28 Digital ground

NO.

25, 26,

27, 29,

30, 31

15, 17,

18, 19

I/O DESCRIPTION

the CSYNC, CDATO, CDATI, CRESET,

interface.

pair used to connect the TAS1020B device to the universal serial bus.

pair used to connect the TAS1020B device to the universal serial bus.

source for MCLKO2.

interface and the codec.

the codec used in I2S modes for receive. This clock signal can also be used as a miscellaneous

clock.

I/O General-purpose I/O port [bits 0 through 1]: A bidirectional 8-bit I/O port with an internal 100 µA

active pullup

I/O General-purpose I/O port [bits 0 through 1]: A bidirectional I/O port with an internal 100 µA active

pullup

signal from a high-impedance state to 3.3 V . When the DP signal is connected to 3.3-V the host PC

detects the connection of the TAS1020B device to the universal serial bus.

AND CSCHNE signals.

1–5

1.7 Terminal Functions—External MCU Mode

TERMINAL

NAME

AV

DD

AV

SS

CSCLK CMOS 37 I/O Codec port interface serial clock: CSCLK is the serial clock for the codec port interface used to

CSYNC CMOS 35 I/O Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port

CDATO CMOS 38 I/O Codec port interface serial data output

CDATI CMOS 36 I/O Codec port interface serial data input

CRESET CMOS 34 I/O Codec port interface reset output

CSCHNE CMOS 32 I/O Codec port interface secondary channel enable

DP CMOS 6 I/O USB differential pair data signal plus: DP is the positive signal of the bidirectional USB differential

DM CMOS 7 I/O USB differential pair data signal minus. DM is the negative signal of the bidirectional USB differen-

DV

DD

DV

SS

EXTEN CMOS 11 I External MCU mode enable: Input used to enable the device for the external MCU mode. This sig-

MCLKI CMOS 3 I Master clock input: An input that can be used as the master clock for the codec port interface or the

MCLKO1 CMOS 39 O Master clock output 1: The output of the ACG that can be used as the master clock for the codec

MCLKO2 CMOS 40 O Master clock output 2: An output that can be used as the master clock for the codec port interface

MRESET CMOS 9 I Master reset: An active low asynchronous reset for the device that resets all logic to the default

MCUAD

[0:7]

MCUA

[8:10]

MCUALE CMOS 18 I MCU address latch enable: Address latch enable for external MCU access to the TAS1020B exter-

MCUINTO CMOS 19 O MCU interrupt output: Interrupt output to be used for external MCU INTO input signal. All internal

MCUWR CMOS 20 I MCU write strobe: Write strobe for external MCU write access to the TAS1020B external data

MCURD CMOS 22 I MCU read strobe: Read strobe for external MCU read access to the TAS1020B external data

PLLFILI CMOS 48 I PLL loop filter input: Input to on-chip PLL from external filter components.

PLLFILO CMOS 1 O PLL loop filter output: Output to on-chip PLL from external filter components.

PUR CMOS 5 O USB data signal plus pullup resistor connect. PUR is used to connect the pullup resistor on the DP

RESET CMOS 41 O General-purpose active-low output which is memory mapped

RSTO CMOS 12 O Reset output: An output that is active while the master reset input or the USB reset is active.

SCL CMOS 44 O I2C interface serial clock

SDA CMOS 43 I/O I2C interface serial data input/output

TEST CMOS 10 I Test mode enable: Factory text mode

PIN

TYPE

Power 2 – 3.3-V Analog supply voltage

Power 45 – Analog ground

Power 8, 21, 33 – 3.3-V Digital supply voltage

Power 4, 16, 28 – Digital ground

CMOS 23, 24, 25,

CMOS 13, 14, 17 I/O MCU address bus: Multiplexed address bus bits[8:10] for external MCU access to the TAS1020B

NO.

26, 27, 29,

30, 31

I/O DESCRIPTION

clock the CSYNC, CDATO, CDATI, CRESET

interface.

pair used to connect the TAS1020B device to the universal serial bus.

tial pair used to connect the TAS1020B device to the universal serial bus.

nal uses a 3.3 V TTL/LVCMOS input buffer.

source for MCLKO2.

port interface and the codec.

and the codec. This clock signal can also be used as a miscellaneous clock.

state.

I/O MCU multiplexed address/data: Multiplexed address bits[0:7]/data bits[0:7] for external MCU ac-

cess to the TAS1020B external data memory space.

external data memory space.

nal data memory space.

TAS1020B interrupt sources are read together to generate this output signal.

memory space.

memory space.

signal to 3.3V from a high-impedance state. When the DP signal is connected in a 3.3-V state, the

host PC should detect the connection of the TAS1020B device to the universal serial bus.

AND CSCHNE signals.

1–6

1.7 Terminal Functions—External MCU Mode (Continued)

GP

AIC

AC 97 v1.X

AC 97 v2.X

I2S

I2S

TERMINAL

NAME

VREN CMOS 42 O General-purpose active-low output which is memory mapped.

XINT CMOS 15 I External interrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU.

XTALI CMOS 47 I Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal.

XTALO CMOS 46 O Crystal output: Output from the on-chip oscillator to an external 6-MHz crystal.

PIN

TYPE

NO.

I/O DESCRIPTION

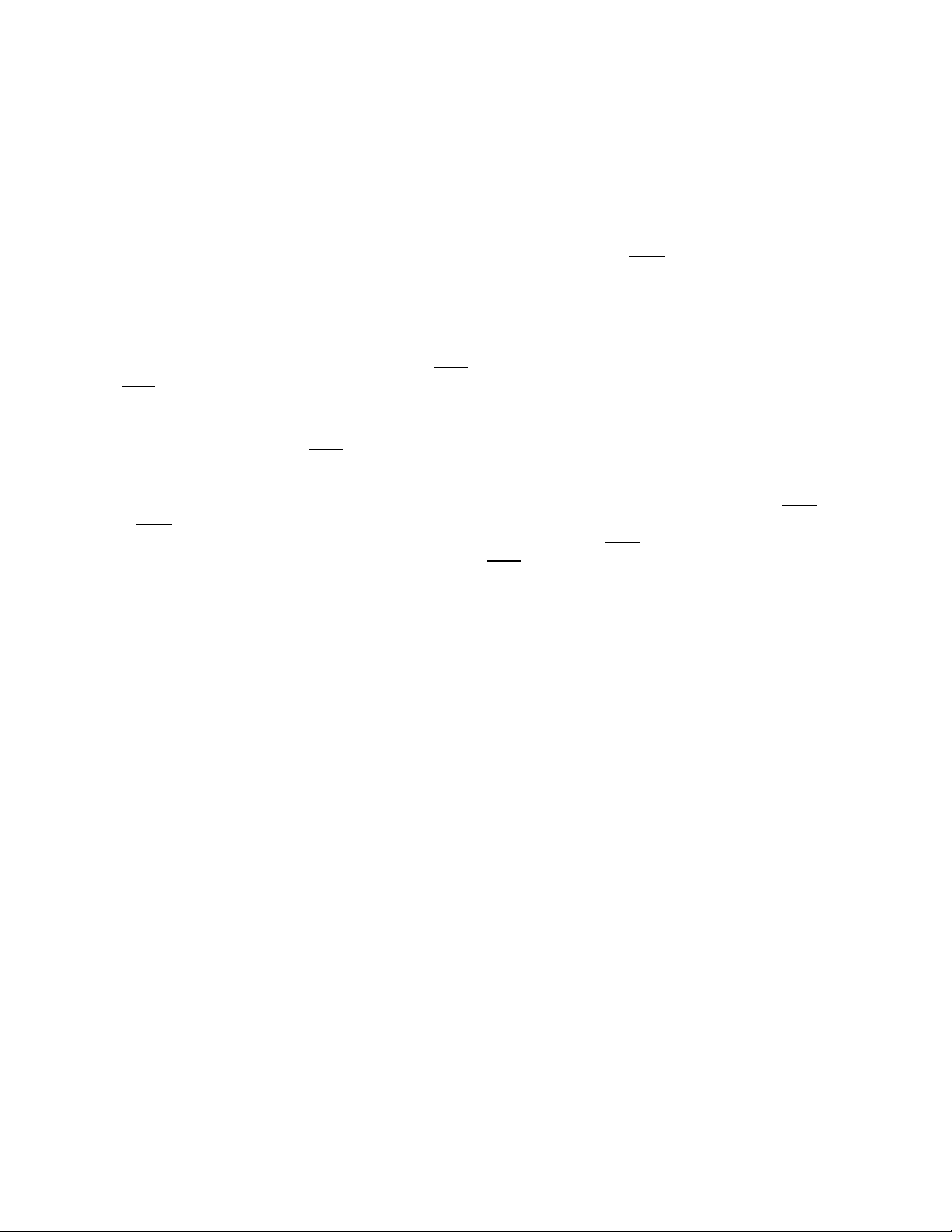

1.8 Device Operation Modes

The EXTEN and TEST pins define the mode that the TAS1020B is in after reset.

MODE EXTEN TEST

Normal mode – internal MCU 0 0

External MCU mode 1 0

Factory test 0 1

Factory test 1 1

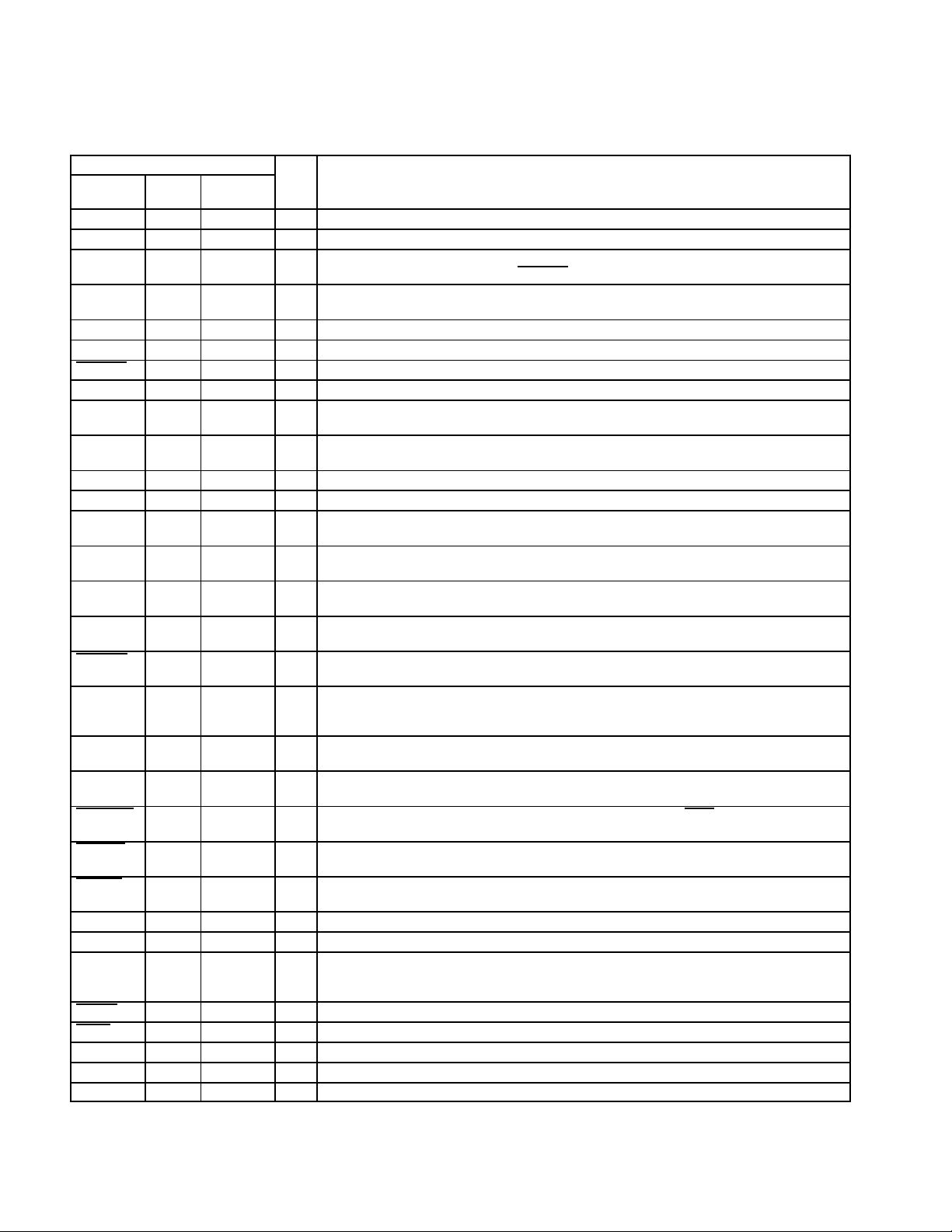

1.9 Terminal Assignments for Codec Port Interface Modes

The codec port interface has five modes of operation that support AC ’97, I2S, and AIC codecs. There is also a

general-purpose mode that is not specific to a serial interface. The mode is programmed by writing to the mode select

field of the codec port interface configuration register 1 (CPTCNF1). The codec port interface terminals CSYNC,

CSCLK, CDATO, CDATI, CRESET

shown in the following table.

, and CSCHNE take on functionality appropriate to the mode programmed as

TERMINAL

NO. NAME

35 CSYNC CSYNC I/O FS O SYNC O SYNC O LRCK O LRCK1 O

37 CSCLK CSCLK I/O SCLK O BIT_CLK I BIT_CLK I SCLK O SCLK1 O

38 CDATO CDATO O DOUT O SD_OUT O SD_OUT O SDOUT1 O SDOUT1 O

36 CDATI CDATI I DIN I SD_IN I SD_IN1 I SDIN1 I SDIN2 I

34 CRESET CRESET O RESET O RESET O RESET O CRESET O SCLK2 O

32 CSCHNE NC O FC O NC O SD_IN2 I SDIN2 I LRCK2 O

NOTES: 1. Signal names and I/O direction are with respect to the TAS1020B device. The signal names used for the TAS1020B terminals for

the various codec port interface modes reflect the nomenclature used by the codec devices.

2. NC indicates no connection for the terminal in a particular mode. The TAS1020B device drives the signal as an output for these

cases.

3. The CSYNC and CSCLK signals can be programmed as either an input or an output in the general-purpose mode.

GP AIC AC ’97 v1.X AC ’97 v2.X

Mode 0

Mode 1

Mode 2

Mode 3

I2S I2S

Mode 4

Mode 5

1–7

1–8

2 Description

2.1 Architectural Overview

2.1.1 Oscillator and PLL

Using an external 6-MHz crystal, the TAS1020B derives the fundamental 48-MHz internal clock signal using an

on-chip oscillator and PLL. Using the PLL output, the other required clock signals are generated by the clock

generator and adaptive clock generator.

2.1.2 Clock Generator and Sequencer Logic

Utilizing the 48-MHz output from the PLL, the clock generator logic generates all internal clock signals, except for the

codec port interface master clock (MCLK) and serial clock (CSCLK) signals. The T AS1020B internal clocks include

the 48-MHz clock, a 24-MHz clock, and a 12-MHz clock. A 12 MHz USB clock is also generated. The USB clock is

the same as the internal 12-MHz clock when the T AS1020B is transmitting data, but is derived from the data when

the T AS1020B is receiving data. T o derive the USB clock when receiving USB data, the T AS1020B utilizes an internal

digital PLL (DPLL) driven from the 48-MHz clock.

The sequencer logic controls the access to the SRAM used for the USB endpoint configuration blocks and the USB

endpoint buffer space. The SRAM can be accessed by the MCU, the USB buffer manager (UBM), or the DMA

channels. The sequencer controls the access to the memory using a round-robin fixed priority arbitration scheme.

This means that the sequencer logic generates grant signals for the MCU, UBM, and DMA channels at a

predetermined fixed frequency.

2.1.3 Adaptive Clock Generator (ACG)

The adaptive clock generator is used to generate a master clock output signal (MCLKO) to be used by the codec port

interface and the codec device. To synchronize data sent to or received from the codec to the USB frame rate, the

MCLKO signal generated by the adaptive clock generator must be used. The synchronization of the MCLKO signal

to the USB frame rate is achieved by the ACG, which, in turn, is controlled by a soft PLL, implemented in the MCU.

One of the tasks performed by the ACG is to maintain count of the number of MCLKO clocks between USB Start of

Frame (SOF) events. This count is monitored by the soft PLL in the MCU. Based on this count, the soft PLL outputs

corrections to the ACG to adjust MCLKO to obtain the correct number of MCLKO clocks between USB SOF events.

MCLKI, the master clock input, can also be selected to source the clocks used by the codec port interface. When

MCLKI is selected, it is used to derive the TAS1020B-sourced versions of the clocks CSCLK and CSYNC. In this

scenario, the codec device would also use the same master clock signal (MCLKI).

2.1.4 USB Transceiver

The TAS1020B provides an integrated transceiver for the USB port. The transceiver includes a differential output

driver, a dif ferential input receiver , and two single ended input buf fers. The transceiver connects to the USB DP and

DM signal terminals.

2.1.5 USB Serial Interface Engine (SIE)

The serial interface engine logic manages the USB packet protocol for packets being received and transmitted by

the T AS1020B. For packets being received, the SIE decodes the packet identifier field (PID) to determine the type

of packet being received and to ensure the PID is valid. The SIE then calculates the cycle redundancy check (CRC)

of the received token and data packets and compares the value to the CRC contained in the packet to verify that the

2–1

packet was not corrupted during transmission. For transmitted token and data packets, the SIE generates the CRC

that is transmitted with the packet. The SIE also generates the synchronization field (SYNC) and the correct PID for

all transmitted packets. Another major function of the SIE is the serial-to-parallel conversion of received data packets

and the parallel-to-serial conversion of transmitted data packets.

2.1.6 USB Buffer Manager (UBM)

The USB buffer manager provides the control logic that interfaces the SIE to the USB endpoint buffers. One of the

major functions of the UBM is to decode the USB function address to determine if the host PC is addressing the

T AS1020B device USB peripheral function. In addition, the endpoint address field and direction signal are decoded

to determine which particular USB endpoint is being addressed. Based on the direction of the USB transaction and

the endpoint number, the UBM will either write or read the data packet to or from the appropriate USB endpoint data

buffer.

2.1.7 USB Frame Timer

The USB frame timer logic receives the start of frame (SOF) packet from the host PC each USB frame. Each frame,

the logic stores the 1 1-bit frame number value from the SOF packet in a register and asserts the internal SOF signal.

The frame number register can be read by the MCU and the value can be used as a time stamp. For USB frames

in which the SOF packet is corrupted or not received, the frame timer logic will generate a pseudo start of frame

(PSOF) signal and increment the frame number register.

2.1.8 USB Suspend and Resume Logic

The USB suspend and resume logic detects suspend and resume conditions on the USB. This logic also provides

the internal signals used to control the TAS1020B device when these conditions occur. The capability to resume

operation from a suspend condition with a locally generated remote wake-up event is also provided.

2.1.9 MCU Core

The T AS1020B uses an 8-bit microcontroller core that is based on the industry standard 8052. The MCU is software

compatible with the 8052, 8032, 80C52, 80C53, and 87C52 MCUs. The 8052 MCU is the processing core of the

T AS1020B and handles all USB control, interrupt and bulk endpoint transfers. Bulk out end-point transfers can also

be handled by one of the two DMA channels.

2.1.10 MCU Memory

In accordance with the industry standard 8052, the TAS1020B MCU memory is organized into program memory,

external data memory and internal data memory . A boot ROM program is used to download the application code to

a 6K byte RAM that is mapped to the program memory space. The external data memory includes the USB endpoint

configuration blocks, USB data buffers, and memory mapped registers. The total external data memory space

available is 1.5K bytes. A total of 256 bytes are provided for the internal data memory.

2.1.11 USB Endpoint Configuration Blocks and Buffer Space

The USB endpoint configuration blocks are used by the MCU to configure and operate the required USB endpoints

for a particular application. In addition to the control end-point, the T AS1020B supports a total of seven IN endpoints

and seven OUT endpoints. A set of six bytes is provided for each endpoint to specify the endpoint type, buffer address,

buffer size, and data packet byte count.

The USB endpoint buffer configuration blocks and buffer space provided totals 1440 bytes. The buffer space to be

used by a particular endpoint is fully configurable by the MCU for a particular application. Therefore, the MCU can

configure each buffer based on the total number of endpoints to be used, the maximum packet size to be used for

each endpoint, and the selection of single or double buffering.

2.1.12 DMA Controller

Two DMA channels are provided to support the streaming of data for USB isochronous IN endpoints, isochronous

OUT endpoints, and bulk OUT endpoints. Each DMA channel can support one USB isochronous IN endpoint, or one

2–2

isochronous OUT endpoint, or one bulk OUT endpoint. The DMA channels are used to stream data between the USB

endpoint data buffers and the codec port interface. The USB endpoint number and direction can be programmed for

each DMA channel. Also, the codec port interface time slots to be serviced by each DMA channel can be

programmed.

2.1.13 Codec Port Interface

The T AS1020B provides a configurable full duplex bidirectional serial interface that can be used to connect to a codec

or other external device types for streaming USB isochronous data. The interface can be configured to support

several different industry standard protocols, including AC ’97 1.X, AC ’97 2.X, AIC, and I

a general-purpose mode to support other protocols.

2

S. The T AS1020B also has

2.1.14 I2C Interface

The I2C interface logic provides a two-wire serial interface that the 8052 MCU can use to access other ICs. The

TAS1020B is an I

interface can be programmed to operate at either 100 kbps or 400 kbps. In addition, the protocol supports 8-bit or

16-bit addressing for accessing the I

means slaves can assert wait state on the I

2

C master device only and supports single byte or multiple byte read and write operations. The

2

C slave device memory locations. The T AS1020B supports I2C wait states. This

2

C bus by pulling the SCL line low.

2.1.15 General-Purpose IO Ports (GPIO)

The T AS1020B provides two general-purpose IO ports that are controlled by the internal 8052 MCU. The two ports

are port 1 and port 3. Port 1 provides true GPIO capability. Each bit of port 1 can be independently used as either

an input or output, and consists of an output buffer , an input buffer, and a pullup resistor. Some of the bits of port 3

also provide true GPIO capability , but, in addition, some of the bits of port 3 also provide alternate input and output

uses. An example of this is P3.2, which is used as the external interrupt (XINT

description of the alternate uses of some of the port 3 bits is presented in Section 2.2.11.

The pullup resistors for port 1 and port 3 can be disabled by bits P1PUDIS and P3PUDIS respectively in the on-chip

register GLOBCTL. In addition, any port 3 pin can be used to wake up the host PC from a low-power suspend mode.

) input to the TAS1020B. A detailed

2.1.16 Interrupt Logic

The interrupt logic monitors the various conditions that can cause an interrupt and asserts the interrupt 0 (INTO) input

on the 8052 MCU core accordingly . All of the TAS1020B internal interrupt sources and the external interrupt (XINT

input are ORed together to generate the INT0 signal. An interrupt vector register is used by the MCU to identify the

interrupt source.

2.1.17 Reset Logic

)

An external master reset (MRESET) input signal that is asynchronous to the internal clocks can be used to reset the

T AS1020B logic. In addition to this master reset, the T AS1020B logic can also be reset by a USB reset from the host

PC if bit FRSTE in the on-chip register USBCTL is set to 1. The T AS1020B also provides a reset output (RSTO

that can be used by external devices. This signal is asserted when either a master reset occurs or when a USB reset

occurs and FRSTE is set to 1.

) signal

2.2 Device Operation

The operation of the T AS1020B is explained in the following sections. For additional information on USB, refer to the

Universal Serial Bus Specification, Version 1.1.

2–3

2.2.1 Clock Generation

The T AS1020B requires an external 6-MHz crystal with load capacitors and PLL loop filter components to derive all

the clocks needed for both USB and codec operation. Figure 4–1 shows the connection of these components to the

T AS1020B. Figure 4–1 also shows a ground shield residing on the top layer of the PCB and underneath the crystal

and its load capacitors and the PLL components. The PLL is an analog PLL, and noise pickup in these components

can translate to phase jitter at the output of the PLL, which in turn can translate to distortion at the codec. A ground

shield is recommended to attenuate the digital noise components on the board as seen at the PLL.

The A V

the digital noise residing on a board, A V

and A VDD pins on the T AS1020B are used exclusively to power the analog PLL. T o maintain isolation from

SS

should be a separate ground plane that connects to the primary ground

SS

plane (DGND) at a single point via a ferrite bead. The ferrite bead should exhibit around 9 Ω of impedance at 100 MHz.

AV

should also be distinct from DVDD. A recommended architecture is to generate DVDD and A VDD from the same

DD

regulator line, with each derived from a RC filter in series with the regulator output. It is finally recommended that the

ground shield for the crystal and its load capacitors and the PLL loop filter components be connected to A V

SS

at a

single point via a ferrite bead of the same type as above.

Using the low frequency 6-MHz crystal and generating the required higher frequency clocks internally in the

TAS1020B is a major advantage with regard to EMI.

2.2.2 Boot Process

The T AS1020B can boot from EEPROM or execute a host boot. Host boot will be used in the following circumstances:

• No EEPROM is present.

• An EEPROM is present, but does not contain a valid header.

• An EEPROM is present, but is a device EEPROM (contains header information only).

2.2.2.1 EEPROM Boot Process

If the target device has an application EEPROM (an EEPROM that contains both header and application data), and

if the header portion of the EEPROM content is valid, the EEPROM application code is downloaded to on-chip RAM.

During the download process, the RAM is mapped to data space, and the boot code that orchestrates the download

is part of the on-chip firmware housed in on-chip ROM. Also, while the application code is being downloaded, the

TAS1020B remains disconnected from the USB bus.

When the download is complete, the firmware sets the ROM disable bit SDW. The setting of this bit maps the RAM

from data space to program space, starting address 0x0000. Having set bit SDW, the firmware then branches to

address 0x0000, which is the reset entry point for the application code. The application code is now running.

The application code then switches on the PUR output. The PUR output pin is connected, through a resistor, to the

positive (DP) line of the differential USB bus. Switching PUR on informs the host that a full speed (12 Mb/s) device

is present on the bus. In the enumeration procedure that follows, the application code reports its run-time device

descriptor set. Following enumeration, the device is actively running its application.

2.2.2.2 Host Boot Process

The DFU code in the TAS1020B fully adheres to the USB Device Class Specification for DFU 1.0. In addition, the

T AS1020B utilizes the communication protocols from the DFU specification to implement a host boot capability for

those applications that do not have an EEPROM resource. In such cases, the TAS1020B, at power-up, reports its

DFU mode descriptor set rather than its run-time descriptor set and directly enters what the DFU specification terms

the DFU Program Mode. The host processor must be cognizant of the fact that the device under enumeration does

not have an EEPROM resource with valid code, and is already in the DFU mode awaiting a download per the DFU

protocol. All of this capability is provided by the ROM-based code (firmware) that resides on the TAS1020B.

Specifically, the host boot process addresses three cases—an EPROM is not present, an EEPROM is present but

the data in the EEPROM is invalid, or an EEPROM is present but the EEPROM is a device EEPROM (contains only

2–4

header data). In all three of these cases, the T AS1020B firmware comes up in the DFU Program Mode. A host boot

ensues, but the final destination of the download depends on the status of the onboard EEPROM.

• If the firmware determines that no EEPROM is present (by noting, when addressing the EEPROM, the

absence of an acknowledge from the EEPROM), a Vendor ID of 0xFFFF and a Product ID of 0xFFFE is

reported during enumeration. The download that follows enumeration is written to the on-chip RAM. The

download from the host must include a header (see Section 2.2.2.3.1), and the header overwrite bit in the

header downloaded must be set to 0. (The header overwrite bit is used to instruct the T AS1020B firmware

as to whether or not the header portion of the download is to be written into the EEPROM. Since, in this case,

no EEPROM is present, this header overwrite bit must be set to 0). It is noted that the host must have prior

knowledge that the target will initialize in the DFU program mode and will require a download of application

code (and header) to RAM.

• If the firmware determines that an EEPROM is present (acknowledges are received from the EEPROM),

but that the header data in the EEPROM is invalid, a Vendor ID of 0xFFFF and a Product ID of 0xFFFE is

reported during enumeration. The download that follows enumeration is written to EEPROM. Since the

EEPROM data was invalid, the host has to set the header overwrite bit in the header portion of the download

to a 1 to ensure that the header is written to the EEPROM. It is noted that the host must have prior knowledge

that the target does have an EEPROM, but that the data in the EEPROM is invalid. This could be a situation

such as the initial download of the application on a production line.

• If the firmware determines that an EEPROM is present, that the header data in the EEPROM is valid, but

that the header data in the EEPROM indicates that the EEPROM is a device EEPROM, the Vendor ID and

Product ID settings in the EEPROM-resident header is reported during enumeration. In addition, the strings

in the header, if applicable, are reported. The EEPROM download that follows enumeration will be written

to the on-chip RAM facility . In addition to downloading the application code to RAM, an option also exists

to download the header portion of the download image to the EEPROM. If the host does not wish to

overwrite the valid header data in the EEPROM, it must set the header overwrite bit in its download header

to a 0. It is noted that the host must have knowledge that the target contains an EEPROM, and that the

EEPROM is a device EEPROM.

2.2.2.3 EEPROM Data Organization

Two types of data can be stored in the EEPROM—header data, which contains USB device information, and

application code. The presence of header data in the EEPROM is mandatory , but the presence of application code

is optional.

2–5

2.2.2.3.1 EEPROM Header

Table 2–1 shows the format and information contained it the header data. As seen from Table 2–1, the header data

begins at address 0x0000 in the EEPROM and precedes the application code.

Table 2–1. EEPROM Header

OFFSET TYPE SIZE VALUE

0 headerChksum 1 Header check sum—derived by adding the header data, excluding the header checksum, in bytes, and

1 HeaderSize 1 Size, in units of bytes, of the header including strings if applied

2 Signature 2 Signature: 0x1234

4 VendorID 2 USB Vendor ID

6 ProductID 2 USB Product ID

8 ProductVersion 1 Product version

9 FirmwareVersion 1 Firmware version

10 UsbAttributes 1 USB attributes:

11 MaxPower 1 Maximum power the device needs in units of 2 mA.

12 Attributes 1 Device attributes:

13 WPageSize 1 Maximum I2C write page size, in units of bytes

14 DataType 1 This value defines if the device is an application EEPROM or a device EEPROM.

15 RpageSize 1 Maximum I2C read page size, in units of bytes. If the value is zero, the whole payLoadSize is read in one

16 payLoadSize 2 Size, in units of bytes, of the application, if using EEPROM as an application EEPROM, otherwise the

xxxx Language string 4 Language string in standard USB string format if applied. If this attribute is applied, the two attributes

xxxx Manufacture string ... Manufacture string in standard USB string format if applied.

xxxx Product string ... Product string in standard USB string format if applied.

xxxx Application Code ... Application code if applied

retaining the lower byte of the sum as the checksum.

Bit 0: If set to 1, the header includes all three strings: language, manufacture, and product strings, if set

to 0, the header does not include any string. The strings, if present, must conform to the USB

string format per USB spec 1.0 or later.

Bit 1 : Not used.

Bit 2: If set to 1, the device can be self powered, if set to 0, cannot be self powered.

Bit 3: If set to 1, the device can be bus powered, if set to 0, cannot be bus powered.

Bit 4 ... 7: Reserved

Bit 0: If set to 1, the CPU clock is 24 MHz, if set to 0, the CPU clock is 12 MHz.

Bit 1: If set to 1, the download version of the header will be written into the EEPROM (download target

has to be EEPROM). If the header is not to be overwritten, or if the target is RAM, this bit must be

cleared to 0.

Bit 2: Not used.

Bit 3: If set to 1, the EEPROM can support a 400 kHz I2C bus, if set to 0, the EEPROM cannot support

a 400 MHz I2C bus.

Bit 4 ... 7: Reserved

0x01: Application EEPROM—contains header and application code.

0x02: Device EEPROM—contains only header.

All other values are invalid.

I2C read setup.

value is 0.

that follow must also be applied. If this attribute is not applied, the following two attributes cannot be

applied.

The header checksum is used by the firmware to detect the presence of a valid header in the EEPROM. The header

size field supports future updates of the header.

2.2.2.3.2 Application Code

Application code is stored as a binary image in the EEPROM following the header information. The binary image must

always be mapped to MCU program space starting at address 0x0000, and must be stored in the EEPROM as a

continuous linear block of data.

2–6

2.2.2.4 I2C Serial EEPROM

The TAS1020B accesses the EEPROM via an I2C serial bus. Thus the EEPROM must be an I2C serial EEPROM.

The ROM boot loader assumes the EEPROM device uses the full 7-bit I

of the address (control code) set to 1010 and the three least significant bits (chip select bits) set to 000.

2

C device address with the upper four bits

2.2.2.5 DFU Upgrade Process

DFU compliance provides a host the capability of upgrading application code currently residing in a target’s onboard

EEPROM memory. The DFU upgrade process provided by the TAS1020B fully conforms to the requirements

specified in USB Device Class Specification For DFU 1.0.

The download must consist of both header and application code. The destination of the download must be defined

by the on-chip application code (as opposed to the application code being downloaded). Under normal

circumstances, the download destination would be EEPROM, but it is possible for the application code to specify

on-chip RAM as the download destination.

If the download destination is to be EEPROM, bit 1 of the Attribute field in the header data being downloaded

determines whether or not the header data in the download image is to be written to the EEPROM. A bit value of 1

results in the header in the EEPROM being overwritten by the header content in the download image. It is important

to note that if the application code targets RAM as the download destination, bit 1 in the Attribute field of the download

image must be 0.

2.2.2.6 Download Error Recovery

Safeguards are incorporated on the T AS1020B ROM to allow recovery from a host download that does not complete

due to a loss of power. Before downloading the application code, the TAS1020B saves the value of the Data Type

field in the EEPROM header and modify the Data Type field to indicate that a download is in progress. After successful

completion of the download, the TAS1020B restores the saved value in the Data Type field. If the download is

terminated prior to successful completion, the Data Type field still indicates that a download is in progress. In the case

of an unsuccessful download the T AS1020B reboots as a DFU device in DFU Program mode and uses the Vendor

and Product ID from the EEPROM header as the vendor and product ID in its USB device descriptor.

The download process consists of the following task flow.

1. Header portion of download is written to EEPROM, if applicable.

2. Header Data Type is retrieved and stored in RAM.

3. Header Data Type is overwritten with a value indicating that a download is in progress.

4. Application portion of download is written to EEPROM (or to RAM).

5. Header Data Type is overwritten with the previously recorded legal value.

If the download should terminate during the downloading of the header to EEPROM, the header checksum results

in the EEPROM being declared invalid on the next boot of the T AS1020B. If the download should terminate during

the downloading of the application code, the Data Type field indicates that a download was in progress and the

TAS1020B enters the DFU program mode on the next boot.

If the T AS1020B remains powered when a premature termination of a download occurs, the TAS1020B remains in

the DFU program mode. In this case, the host can again attempt a download; the TAS1020B does not have to be

rebooted.

2–7

2.2.2.7 ROM Support Functions

In order to conserve RAM memory resources on the T AS1020B, several USB-specific routines have been included

in the firmware resident in the on-chip ROM. The inclusion of these routines frees the application code from having

to implement USB-specific code.

The tasks provided by the ROM code include:

• A USB engine for handling USB control endpoint data transactions and states

• USB protocol handlers to support USB Chapter 9

• USB protocol handlers to support USB HID Class

• USB protocol handlers to support USB DFU Class

• USB protocol handlers to support the common features of USB Audio Class commands

• Feature Unit:

– Set/get volume control

– Set/get mute control

– Set/get bass control

– Set/get treble control

• Mixer unit: set/get input/output gain control

• End point: set/get the audio streaming endpoint sampling frequency

• For unsupported case, the ROM code passes the requests to the application code for processing.

2.2.3 USB Enumeration

USB enumeration is accomplished by interaction between the host PC and the T AS1020B. As described in Section

2.2.2, the TAS1020B can identify itself as an application device by reporting its application Vendor ID and Product

ID, or it can identify itself as a DFU device by reporting a Vendor ID of 0xFFFF and a Product ID of 0xFFFE. If the

TAS1020B fails to detect the presence of an EEPROM, or if an EEPROM is present but does not contain a valid

header, the Vendor ID of 0xFFFF and Product ID of 0xFFFE are reported. If an EEPROM is present, but contains

only valid header data, the Vendor ID and Product ID settings in the EEPROM header are reported, but the T AS1020B

firmware comes up as a DFU device in the DFU program mode. If an EEPROM is present, and contains both a valid

header and application code, the TAS1020B comes up as an application specific device.

For all cases where the TAS1020B comes up in the DFU program mode, once application code has been

downloaded, the TAS1020B is reset by a host-issued USB reset. After this reset, the TAS1020B comes up as an

application device. When the T AS1020B comes up as an application device, the ROM-resident boot loader retrieves

the application code from the EEPROM, if the EEPROM is not a device EEPROM, and then runs the application code.

It is the application code that connects the TAS1020B to the USB. During the enumeration that follows connection

to the USB, the application code identifies the device as an application specific device and the host loads the

appropriate host driver(s).

The boot loader and application code both use the CONT , SDW and FRSTE bits to control the enumeration process.

• The function connect (CONT) bit is set to a 1 by the MCU to connect the T AS1020B device to the USB. When

this bit is set to a 1, the USB DP line pullup resistor (PUR) output signal is enabled. Enabling PUR connects

the pullup on the PCB to the T AS1020B 3.3-V digital supply voltage. (When the T AS1020B powers up, this

bit is cleared to a 0 and the PUR output is in the high-impedance state.) This bit is not affected by subsequent

USB resets.

• The shadow the boot ROM (SDW) bit is set to 1 by the MCU to switch the MCU memory configuration from

boot loader mode to normal operating mode. Once set to 1, this bit is not affected by subsequent USB resets.

• The function reset enable (FRSTE) bit is set to a 1 by the MCU to enable the USB reset to reset all internal

logic including the MCU. However, the shadow the ROM (SDW) and the USB function connect (CONT) bits

are not reset. In addition, when the FRSTE bit is set, the reset output (RSTO

device is active whenever a USB reset occurs. This bit, once set, is not affected by subsequent USB resets.

) signal from the TAS1020B

2–8

2.2.4 TAS1020B USB Reset Logic

There are two mechanisms provided by the T AS1020B—an external reset MRESET and a USB reset. The reset logic

used in the TAS1020B is presented in Figure 2–2.

MRESET is a global reset that results in all the TAS1020B logic and the 8052 MCU core being reset. This input to

the TAS1020B is typically used to implement a power-on reset at the application of power, but it can also be used

with reset pushbutton switches and external circuits to implement global resets at any time. MRESET

asynchronous reset that must be active for a minimum time period of one microsecond.

The T AS1020B can also detect a USB reset condition. When this reset occurs, the TAS1020B responds by setting

the function reset (RSTR) bit in the USB status register (USBSTA). However, the extent to which the internal logic

is reset depends on the setting of the function reset enable bit (FRSTE) in the USB control register (USBCTL).

If the MCU has set FRSTE to 1, incoming USB resets are treated as global resets, with all T AS1020B logic and the

8052 MCU core being reset. However, the shadow the ROM (SDW) and the USB function connect (CONT) bits are

not reset. Also, if the USB reset results in a global reset being issued, an interrupt to the 8052 MCU is not generated.

But if the MCU has cleared FRSTE, incoming USB resets is treated as interrupts to the MCU (via INT0

corresponding function reset bit RSTR in the USB interrupt mask register USBMSK has been set by the MCU. If

neither FRSTE or RSTR has been set by the MCU, USB resets have no effect on the T AS1020B, other than resetting

the USB serial interface engine (SIE) and the USB buffer manager (UBM) in the TAS1020B.

Regardless of the status of FRSTE and bit RSTR in the USB interrupt mask register USBMSK, the function reset bit

RSTR in the USB status register USBST A is always set whenever a USB reset condition is detected. If the USB reset

results in the generation of a global reset, the global reset clears the function reset bit RSTR in USBST A. If, instead,

the USB reset results in an interrupt being generated, RSTR in register USBST A is cleared when the MCU writes to

the interrupt vector register VECINT while in the USB reset interrupt service routine (VECINT = 0x17).

is an

) if the

The TAS1020B has two reset outputs—RSTO

every time a USB reset occurs and bit FRSTE in the USB control register USBCTL is set. CRESET

as a codec reset. Although labeled a reset line, it has no direct relationship to MRESET

and CRESET. RSTO is activated every time MRESET is active, and

is typically used

or detected USB resets.

Instead, it is activated and deactivated when the on-chip 8052 MCU core writes a 0 and a 1, respectively , to the CRST

bit in the codec port interface control and status register CPTCTL.

2–9

2.2.5 USB Suspend and Resume Modes

The TAS1020B can recognize a suspend state. Figure 2–2 shows the logical implementation of the suspend and

resume modes in the T AS1020B. The T AS1020B enters a suspend mode if a constant idle state (j state) is observed

on the USB bus for a period of 5 ms. USB compliance also requires that a device enter a suspend state, drawing only

suspend current from the bus, after no more than 10 ms of bus inactivity , The TAS1020B supports this requirement

by creating a suspend interrupt to the on-chip MCU after a suspend condition has been present for 5 ms. Upon

receiving this interrupt, the MCU firmware can then take the steps necessary to assure that the device enters a

suspend state within the next 5 ms.

There are two ways for the T AS1020B device to exit the suspend mode: 1) detection of USB resume signaling and

2) proactively performing a local remote wake-up event.

2.2.5.1 USB Suspend Mode

When a suspend condition is detected on the USB, the suspend/resume logic sets the function suspend request bit

(SUSR) in the USB status register, resulting in the generation of the function suspend request interrupt SUSR. To

enter the low-power suspend state and disable all T AS1020B device clocks, the MCU firmware, upon receiving the

SUSR interrupt, must set the idle mode bit (IDL), which is bit 0 in the MCU power control (PCON) register. Setting

the IDL bit results in the T AS1020B suspending all internal clocks, including the clocks to the MCU. The MCU thus

suspends instruction execution while in the idle mode.

The MCU must not set the IDL bit while in the SUSR interrupt service routine (ISR), or while in any other ISR. As

described in Section 2.2.5.3, it is intended that the receipt of an INT0

state. But if the MCU has suspended instruction execution while in an ISR, subsequent INT0

as the MCU is still servicing an interrupt. For this reason then, it is necessary that IDL not be set while processing

an ISR. (As described in Section 2.2.5.3, an external wake-up event will resume clocks within the TAS1020B. But

even if the clocks to the MCU resume, if the MCU does not recognize INT0

core itself remains in the suspend state).

interrupt at the MCU result in exiting the suspend

activity is not recognized,

, the IDL bit remains set and thus the MCU

The SUSR bit is cleared while in the SUSR ISR by writing to the interrupt vector register VECINT . While servicing the

SUSR ISR, the VECINT output is 0x16 – the USB function suspend interrupt vector. As shown in Figure 2–2, the

occurrence of a write to VECINT, while the USB function suspend interrupt vector is being output, results in clearing

bit SUSR of the USB status register. (The data written to VECINT is of no consequence; the clearing action takes place

upon decoding the write transaction to VECINT).

2.2.5.2 USB Resume Mode

When the TAS1020B is in a suspend state, any non-idle signaling on the USB is detected by the suspend/resume

logic and device operation resumes. When the resume signal is detected, the T AS1020B clocks are enabled and the

function resume request bit (RESR) is set, resulting in the generation of the function resume request interrupt. The

function resume request interrupt to the MCU automatically clears the idle mode bit IDL in the PCON register, and

as a result the MCU exits the suspend state and becomes fully functional, with all internal clocks active. After the RETI

from the ISR, the next instruction to be executed is the one following the instruction that set the IDL bit. The RESR

bit is cleared while in the RESR ISR by writing to the interrupt vector register VECINT.

2.2.5.3 USB Remote Wake-Up Mode

The TAS1020B device has the capability to remotely wake up the USB by generating resume signaling upstream,

providing the host has granted permission to generate remote wake-ups via a SET_FEATURE

DEVICE_REMOTE_W AKEUP control transaction. If remote wakeup capability has been granted, the MCU firmware,

upon awakening from a suspend state, has to activate the remote wake-up request bit RWUP in the USB control

register USBCTL. Activation of RWUP consists of the MCU firmware writing a 1 followed by a 0 to RWUP. This action

creates a pulse, which results in the T AS1020B generating resume signaling upstream by driving a k state (non-idle)

onto the USB bus. The USB specification requires that remote wake-up resume signaling not be generated until the

2–10

suspend state has been active for at least 5 ms. In addition, the specification requires that the remote wake-up resume

signaling be generated for at least 1ms but for no more than 15 ms. The 5 ms requirement is met by not entering the

suspend mode until an idle state, or j state, is detected, uninterrupted, for 5 ms. The RWUP pulse results in driving

a k state onto the USB bus for 1 to 2 ms, and thus the 15 ms requirement is also met. Moreover, if an application wishes

to extend the duration of the k state on the USB bus, it need only extend the pulse width of RWUP. The resulting

duration of the resume signaling is the duration of the RWUP pulse plus 1 to 2 ms.

The condition that activates a remote wake-up is a transition from 1 to 0 on one of the P3 port bits whose

corresponding mask bit has been set to zero. (When in the suspend mode, the XINT

input is treated as port bit P3.2).

As seen in Figure 2–2, the P3 mask register bits are gated with the P3 port input lines from the I/O port cells. The

gated P3 port bits are then all ORed together and the output is ANDed with the suspend signal. The output of this

logic drives the clock input of a flip-flop, and when the output of this logic transitions from 0 to 1, the flip-flop is set

to 1. The setting of this flip-flop to 1 results in the TAS1020B exiting the suspend state and resuming all clocks,

including those to the MCU core. The output of this flip-flop is also gated with bit XINTEN in the global control register

GLOBCTL, and the output of this gate drives the INT0

an INT0

interrupt to the MCU only if bit XINTEN has been set. Therefore, before entering a suspend state, the firmware

interrupt logic. This means that a remote wake-up generates

must set XINTEN if remote wake-up capability is to be enabled.

The wake-up interrupt is seen by the firmware as an XINT

an output value of 0x1F. If the XINT

pin is to be used as an event marker during normal operation, and if one of the

interrupt; that is, the interrupt vector register VECINT has

P3 port bits is to be used for a wake-up interrupt, the firmware must be able to distinguish between a wake-up interrupt

and a normal XINT

register. If this bit is set, the interrupt event is a wake-up interrupt; otherwise, the interrupt is a normal XINT

If an XINT

event should occur during a suspend mode, the event is ignored if the mask bit for P3.2 is set. (During a

suspend mode the TAS1020B clocks are disabled, and thus an incoming XINT

through the synchronization logic and activate the MCU INT0

interrupt. One technique would be to examine the state of the IDL bit in the MCU power control

interrupt.

interrupt event does not propagate

input).

2.2.6 Adaptive Clock Generator (ACG)

The adaptive clock generator is used to generate two programmable master clock output signals (MCLKO and

MCLKO2) that can be used by the codec port interface and the codec device. Two separate and programmable

frequency synthesizers provide the two master clocks. This allows the TAS1020B to support different record and

playback rates for those devices that require separate master clocks to implement different rates. For isochronous

transactions, the ACG can also support USB asynchronous, synchronous, and adaptive modes of operation. The

ACG keeps count of the number of master clock events between USB SOF time marks, and the DCNTX/Y field of

the endpoint register IEPDCNTX/Y keeps track of the number of samples received between USB SOF time marks.

Synchronous isochronous operation can be accomplished by adjusting one of the two frequency synthesizers until

the correct number of master clock events is obtained between USB SOF time marks. Similarly, monitoring the

number of samples received between USB SOF events can accommodate adaptive isochronous operation. Here the

frequency synthesizer is adjusted to obtain the proper codec output rate for the number of samples received. The

TAS1020B can also accommodate asynchronous isochronous operation, and the input MCLKI is provided for this

case. For asynchronous isochronous operation, the external clock pin MCLKI is used to derive the data and sync

signal to the codec. However, the external clock that provides the input to pin MCLKI, instead of the master clock

output (MCLKO or MCLKO2) from the ACG, must also source the codec’s MCLK.

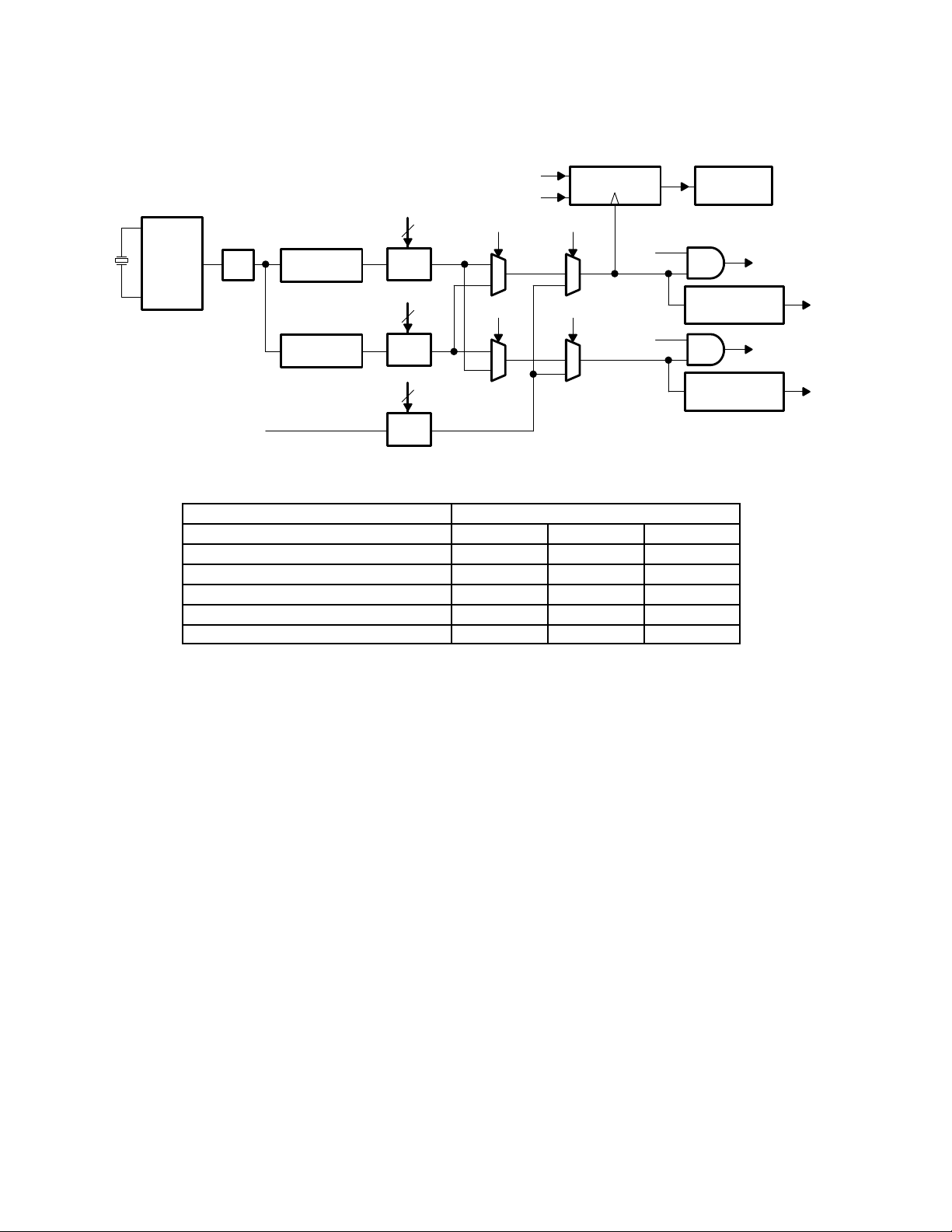

A block diagram of the adaptive clock generator is shown in Figure 2–1. Each frequency synthesizer circuit generates

a programmable clock with a frequency range of 12–25 MHz, and each frequency synthesizer output feeds a

divide-by-M-circuit, which can be programmed to divide by 1 to 16. As a result, the frequency range of each master

clock is 750 kHz to 25 MHz. Also, the duty cycle of each master clock is 50% for all programmable frequencies.

As indicated in Figure 2–1, multiplexers precede the master clocks MCLKO and MCLKO2. These multiplexers

provide the option of using the output of either frequency synthesizer (after division by the divide-by-M circuit) or the

MCLKI input (after division by the divide-by-I circuit) to source each master clock. Each master clock is also assigned

its own divide circuit to generate its associated CSCLK. The C-port serial clock (CSCLK) is derived by setting the

divide by B value in codec port interface configuration register CPTNCF4 [2:0] and the C-port serial clock2 (CSCLK2)

is derived by setting the divide by B2 value in codec port receive interface configuration register 4 CPTRXCNF4 [2:0].

2–11

In addition, although not shown in Figure 2–1, each master clock is assigned its own CSYNC generator, with the

length and polarity of each CSYNC separately programmable.

6 MHz

Oscillator

PLL

MCLKI

Frequency

Synthesizer

Frequency

Synthesizer

ACG1DCTL[7:4]

Divide

1

by M1

ACG2DCTL[7:4]

Divide

2

by M2

ACG1DCTL[2:0]

Divide

by I

SOF

PSOF

4

4

3

ACGCTL[4]

ACGCTL[1]

16-Bit Counter

ACGCTL[3]

ACGCTL[6]

ACGCTL[0]

ACGCTL[7]

Figure 2–1. Adaptive Clock Generator

The ACG is controlled by the following registers. Refer to section A.5.3 for details.

FUNCTIONAL REGISTER ACTUAL BYTE-WIDE REGISTERS

24-bit frequency register #1 ACG1FRQ2 ACG1FRQ1 ACG1FRQ0

16-bit capture register ACGCAPH ACGCAPL

8-bit synthesizer 1 divider control register ACG1DCTL

8-bit ACG control register ACGCTL

24-bit frequency register #2 ACG2FRQ2 ACG2FRQ1 ACG2FRQ0

8-bit synthesizer 2 divider control register ACG2DCTL

ACGCAPH

ACGCAPL

MCLK0

Divide by B

CPTCNF4 [2:0]

MCLK02

Divide by B2

CPTRXCNF4 [2:0]

CSCLK

CSCLK2

The main functional modules of the ACG are described in the following sections.

2.2.6.1 Programmable Frequency Synthesizer

The 24-bit ACG frequency register value is used to program the frequency synthesizer, and the value of the frequency

register can be updated by the MCU while the ACG is running. The high resolution of each frequency value

programmed allows the firmware to adjust the frequency value by +LSB or more to lock onto the USB start-of-frame

(SOF) signal and achieve a synchronous mode of operation, a necessity for streaming audio applications. The 24-bit

frequency register value is updated and used by the frequency synthesizer only when MCU writes to the ACGFRQ0

register. The proper way to update a frequency value then is to write the least significant byte (ACGFRQ0) last.