Page 1

Stellaris® LM3S9D90 Evaluation Kit User’s Manual

User’s Manual

EK-LM3S9D90-00 Copyright ©2011 Texas Instruments

Page 2

Copyright

Copyright © 2011 Texas Instruments, Inc. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments. ARM and

Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.

Texas Instruments

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

2 July 5, 2011

Page 3

Table of Contents

Chapter 1: Stellaris® LM3S9D90 Evaluation Kit Overview ......................................... ... .... ... ........................7

Kit Contents.................................. ... .... ... ... ... ................................................. ... ... ... .... ........................................ 8

Using the EK-LM3S9D90....................................................................................................................................8

Features..............................................................................................................................................................8

Chapter 2: Hardware Description.................................................................................................................. 11

Evaluation Board ..............................................................................................................................................11

Functional Description ........... ... ... .... ... ... ... .... ... ... ... ... .... ................................................... .............................11

In-Circuit Debug Interface Board ......................................................................................................................14

Functional Description ........... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ................................................................ 14

Chapter 3: Software Development ................................................................................................................ 17

Software Description.........................................................................................................................................17

Source Code.....................................................................................................................................................17

Tool Options .....................................................................................................................................................17

Programming the EK-LM3S9D90 Board...........................................................................................................17

Appendix A: Schematics................................................................................................................................19

Appendix B: Connection Details...................................................................................................................25

Component Locations.......................................................................................................................................25

Board Dimensions .. ... ... ... ... .... ................................................... .... ...................................................................26

Board Connectivity........... .................................................... .............................................................................27

References .......................................................................................................................................................27

Appendix C: Microcontroller GPIO Assignments........................................................................................29

July 5, 2011 3

Page 4

List of Figures

Figure 1-1. LM3S9D90 Evaluation Board..........................................................................................................7

Figure 1-2. In-Circuit Debug Interface Board.....................................................................................................7

Figure 2-1. EK-LM3S9D90 Evaluation Board Block Diagram..........................................................................11

Figure 2-2. GPIO Pads.................................... ... ................................................... .... ......................................12

Figure 2-3. JTAG/SWD Connector..................................................................................................................12

Figure 2-4. PWR/UART Connector........... ... .... ... ... ... ... .................................................... ... .... ... ... ... ................13

Figure 2-5. In Circuit Debug (ICDI) Board Block Diagram...............................................................................14

Figure 2-6. JTAG/SWD Connector J1 .............................................................................................................15

Figure 2-7. JTAG/SWD Connector J3 .............................................................................................................15

Figure 2-8. PWR/UART Connector........... ... .... ... ... ... ... .................................................... ... .... ... ... ... ................15

Figure B-1. EK-LM3S9D90 Evaluation Board Component Locations.............................................................. 25

Figure B-2. BD-ICDI Board Component Locations .......................................................................................... 25

Figure B-3. EK-LM3S9D90 Evaluation Board Dimensions .............................................................................. 26

Figure B-4. In-Circuit Debug Interface Board Dimensions...............................................................................26

Figure B-5. ICDI – EK-LM3S9D90 Board Connectivity....................................................................................27

4 July 5, 2011

Page 5

List of Tables

Table C-1. EK-LM3S9D90 Evaluation Board GPIO Usage.............................................................................29

July 5, 2011 5

Page 6

6 July 5, 2011

Page 7

CHAPTER 1

Stellaris® LM3S9D90 Evaluation Kit Overview

Texas Instruments' Stellaris® LM3S9D90 Evaluation Board Kit (EK-LM3S9D90) is a low-cost

platform for evaluation of the LM3S9D90 microcontroller. The kit includes two boards, the

EK-LM3S9D90 evaluation board, and the In-Circuit Debug Interface (BD-ICDI) board.

The EK-LM3S9D90 board includes the LM3S9D90 ARM® Cortex™-M3 Microcontroller, a 10/100

Mbit Ethernet port, a full-speed USB-OTG port, connectors for inteface to the BD- ICDI boar d, and

oversized pads for easy connection to the microcontroller GPIO ports.

The BD-ICDI board is a USB full-speed JTAG/SWD debugger board. It includes a USB miniB

connector for connection to a USB PC port, and two shrouded header connectors for connectio n to

the EK-LM3S9D90 board.

Development of software for the EK-LM3S9D90 is simplified by using Texas Instruments’

comprehensive St ellarisW are® peripheral dr iver library and ARM development too ls from our tools

partners. The Stellaris® LM3S9D90 Evaluation Board Kit includes the two boards described, a

documentation CD, and cables. All design files are provided on the EK-LM3S9D90 CD.

Figure 1-1. LM3S9D90 Evaluation Board

Figure 1-2. In-Circuit Debug Interface Board

July 5, 2011 7

Page 8

Stellaris® LM3S9D90 Evaluation Kit Overview

Kit Contents

The EK-LM3S9D90 evaluation kit comes with the following:

EK-LM3S9D90 evaluation board

In-Circuit Debug Interface (BD-ICDI) board

– Connects to USB port on PC and to 10-pin, fine-pitch ARM JTAG connector on the

EK-LM3S9D90 evaluation board

– Secondary 8-pin Power/UART connector provides power and virtual comm-port capability

to the EK-LM3S9D90 evaluation board.

Cables

– USB miniB to USB-A cable

– USB-OTG to USB-A cable

– 10-pin ribbon cable for JTAG/SWD connection

– 8-pin ribbon cable for Power/UART connection

CD containing:

– A supported version of one of the following (including a toolchain-specific Quickstart

guide):

• Keil™ RealView® Microcontroller Development Kit (MDK-ARM)

• IAR Embedded Workbench

• Sourcery CodeBench development tools

• Code Red Technologies development tools

• Texas Instruments’ Code Composer Studio™ IDE

– Complete documentation

– Quickstart application source code

– Stellaris® Firmwa re Development Package with example source code

Using the EK-LM3S9D90

The recommended steps for using the EK-LM3S9D90 evaluation kit are:

1. Follow the Quickstart guide included in the kit. The Quickstart guide will help get the

EK-LM3S9D90 Evaluation Board up and running in minutes.

2. Use your preferred ARM tool-chain an d the Stellari s Peri ph e ral Driv er Li bra r y to

develop an application. Software applications are loaded using the BD-ICDI board. See

Chapter 3, “Software Development,” for the programming procedure. The StellarisWare

Peripheral Driver Library Software Reference Manual contains specific information on

software structure and function.

3. Customize and integrate the hardware to suit an end applicatio n. This user's manual is an

important reference for understanding circuit operation and completing hardware modification.

Features

The EK-LM3S9D90 evaluation kit provides the following features:

8 July 5, 2011

Page 9

Stellaris® LM3S9D90 Evaluation Kit User’s Manual

LM3S9D90 high-performance Stellaris microcontroller and large memory

– 32-bit ARM® Cortex™-M3 core

– 512 KB single-cycle Flash memory, 96 KB single-cycle SRAM

Ethernet 10/100 port with two LED indicators

USB 2.0 Fu ll-Speed OTG port

Virtual serial communications port capability

Oversized board pads for GPIO access

User pushbutton and LED

Detachable ICDI board can be used for debugging other Stellaris boards

Easy to customize

– Includes full source code, example applicat ion s, and desi gn files

– Develop using tools supporting FastMATH from Keil, IAR, Code Sourcery, and Code Red

(using a Stellaris evaluation kit or preferred ARM Cortex-M3 debugger)

– Supported by Texas Instruments’ StellarisWare peripheral driver library

July 5, 2011 9

Page 10

Stellaris® LM3S9D90 Evaluation Kit Overview

10 July 5, 2011

Page 11

Stellaris

LM3S9D90

Ethernet 10/100

5V

GPIOs

USB – O TG

3.3V

Regulator

USB Power

Switch

JTAG/SWD

PWR/UART

UART0

BOARD PADs

RESET

DPDT

VBUS

4.19MHz

25MHz

16MHz

RTCMOSC

Ethernet

USER LED

USER PUSHBUTTO N

USB

JTAG

CHAPTER 2

Hardware Description

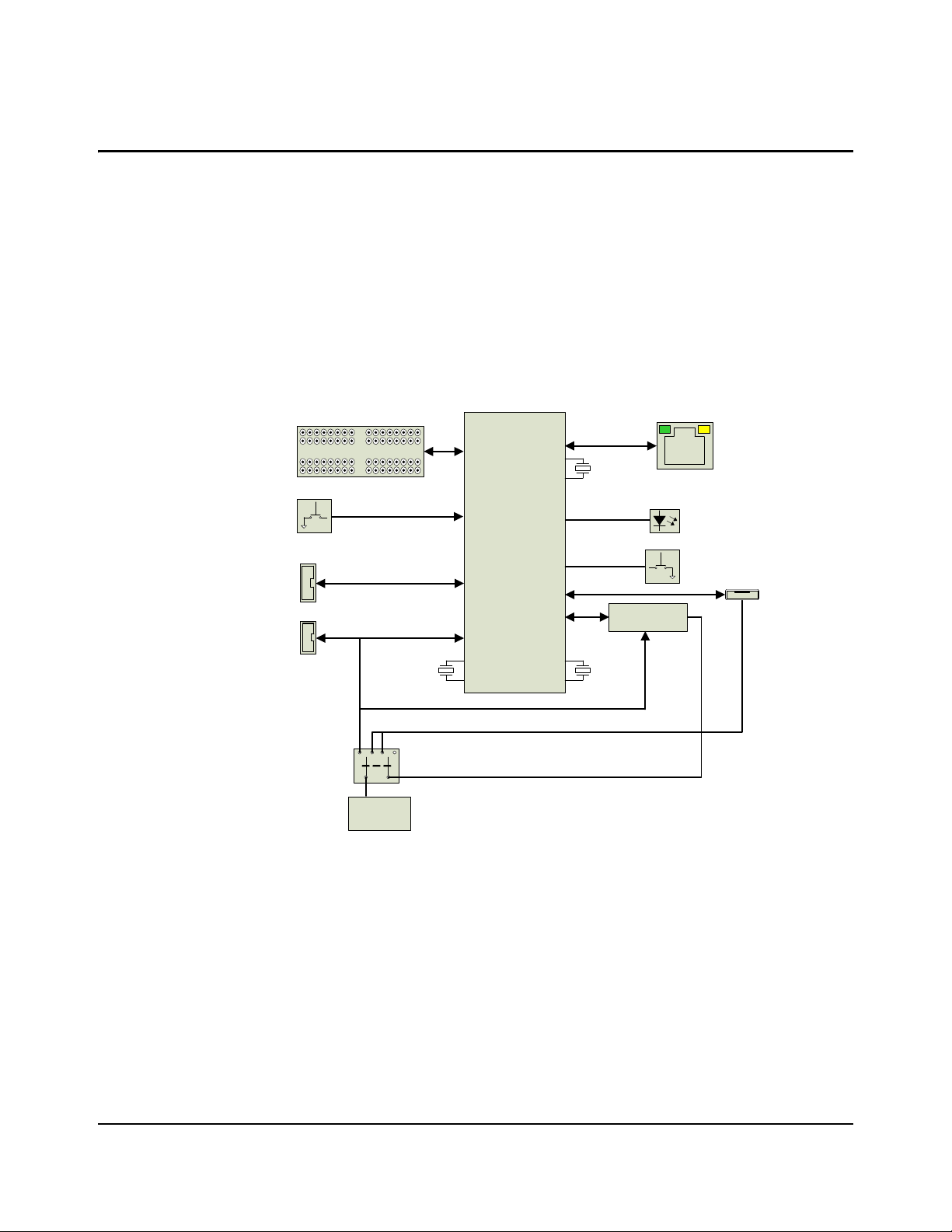

The EK-LM3S9D90 evaluation kit contains two boards: the EK-LM3S9D90 evaluation board and

the BD-ICDI JTAG debug board as described in more detail in this chapter.

Evaluation Board

The EK-LM3S9D90 evaluation board uses the Stellaris® LM3S9D90 microcontroller an d incl ud e s

a 10/100 Ethernet port and a USB 2.0 full-speed OTG port. The board is intende d for use with the

ICDI board, but can be used as a standalone board as well. Figure 2-1 shows the block diagram.

Figure 2-1. EK-LM3S9D90 Evaluation Board Block Diagram

Functional Description

Microcontroller, Reset, GPIO Pads, and JTAG (Schematic page 20)

July 5, 2011 11

Microcontroller

The evaluation board uses the S tella ris LM3S9D90 micr ocontroller. A 16 MHz crystal provides the

main oscillator clock which can directly drive the ARM core clock or can drive an internal PLL to

increase the core clock up to 80 MHz. A 25 MHz crystal is used for the Ethernet clock and a

4.194304 MHz crystal is used for the real-time clock.

The LM3S9D90 microcontroller has an internal LDO voltage regulator that supplies power for

internal use. This rail requires only three capacitors for decoupling and is not connected to any

other circuits.

Page 12

Hardware Description

GPIO Pads – Top left

SHDN

VBA

T

WAKE

PD1

PD0

PD2PD3

PD4

PD5

PD6

PD7

PC5

P

C

4

PC7

P

C6

HIB

GPIO Pads – Bottom le ft

P

A

4

PA

7

PA6

5

V

R

5V

PB2PB3PB4PB5PB6P

B7

P

A1

P

A0

P

A

3

P

A2

PA5

GND

GND

GPIO Pads – Top right

VBUS

PG7

PH0PH1

PH2

PH5

PH6

PH7

PJ

1PJ0

PJ2

P

G0

PG1

GPIO Pads – Bottom right

P

E

4

P

E

7

P

E

6

P

F1

P

F0

PF2

PF3PF4PF5

PE1

PE

0

P

E

3

PE2

P

E5

3

.3V

G

N

D

TMS/SWDIO

TCK/SWCLK

TDO/SWO

TDI

RSTn GND

GND

GND

3.3V

N/C

12

910

In

In

Out

I/O

In

Out

Reset

A reset switch and R-C network connects to the microcontroller’s RSTn input. The reset signal is

also connected to the JTAG/SWD connector J1 to allow reset control from the debugger.

GPIO Pads

Four groups of oversized board pads with a 0.1” spacing provide access to GPIO signals and

standard 0.1” pitch headers can be soldered to these pads. Pads are labeled with the

corresponding GPIO signal, and pads with no labels are unconnected. Note that GPIO signals

required for operation of the Ethernet port, USB port, and JTAG port are reserved for board use

and are not available on these pads. Figure 2-2 shows the pad groups.

Figure 2-2. GPIO Pads

GPIO Jumpers

Some of the GPIO signals used by the board are connected to board jumpers and can be

disconnected to provide additional user GPIO s. GPI Os PA0/PA1/PB4/PD0/PF2/PF3 are

connected to jumpers JR1-JR6 respectively. Each signal can be freed by cutting the trace of the

corresponding jumper (cut at white line on silkscreen). The jumper pads have the same footprint

as an 0603 SMT resistor. To reconnect a previously cut jumper, solder a 0 ohm resistor to the

corresponding jumper footprint.

JTAG/SWD

The JTAG/SWD connector J1 is used for program download and debug. This is a 2x5 fine pitch

(0.050”) ARM JTAG connector, see (Figure 2-3) for signal definition. The LM3S9D90

microcontroller supports JTAG debug, Serial Wire Debug (SWD), and Serial Wire Out (SWO) trace

with this connector. The ICDI board connects via a 10-wire ribbon cable to this connector.

Figure 2-3. JTAG/SWD Connector

12 July 5, 2011

Page 13

Stellaris® LM3S9D90 Evaluation Kit User’s Manual

VCP_TX

VCP_RX

GND

GND

DBG1

12

78

DBG2

5V 5V

In

Out

Out

Out

PWR/UART

The PWR/UART connector J2 is used to provide 5 V power from the ICDI board and also to

connect the LM3S9D90 UART0 signals. This is a 2x4 fine pitch (0.050") connector, see

(Figure 2-4) for signal definition. The UART0 signa ls are connected to GPIO jumpers JR1 and JR2

and can be disconnected from connector J2 if required, see “GPIO Jumpers” on page 12. The

ICDI board connects via an 8-wire ribbon cable to this connector.

Figure 2-4. PWR/UART Connector

Ethernet, USB, Power and Miscellaneous (Schematic page 21)

Page 2 of the schematics contains th e Ethernet RJ45 connector, USB power switch and USB OTG

connector, 3.3 V regulator, and power switch selector.

Ethernet Port

The on-board RJ45 connector provides a 10/100 base T Ethernet port. The RJ45 connector

includes integrated LEDs and magnetics. The LEDs are connected to GPIO jumpers JR4 an d JR5

and can be disconnected from the RJ45 connector if required, see GPIO Jumpers section.

USB Port

The on-board USB microAB connector provides a USB 2.0 full-speed port. To use as an On-TheGo (OTG) port, the power selector switch SW3 lever must be set to EXT. This selects an external

5 V power source to provide power to the board and the USB power switch. If the SW3 le ver is set

to USB, power to the board is received from USB, the on-board USB power switch output is

disconnected from USB, and the board can only be used as a USB device. When using the

USB-OTG port in Host mode, the current provided to a USB device should be limited to 100 mA or

less when powered from the ICDI board. If powered from the 5 V test pad, then this can be

increased to 500 mA.

Board Power

The board requires 5 V for operation, and switch SW3 is used to select the power source. If the

switch lever is moved towards the USB label on the board, power is received from the USB

connector. If the switch lever is moved towards the EXTernal board label, the board is powered

from the PWR/UART connector and the ICDI board provide s power to this connector . DC regulator

U2 generates 3.3 V for powering the board circuits and includes power indicator LED D1.

User Devices

Pushbutton switch SW2 and LED D2 are available for the user and connected to PB4 and PD0

respectively. These GPIOs are connected to GPIO jumpers JR3 and JR4 and can be

disconnected from SW2 and D2 if required, see GPIO Jumpers section.

July 5, 2011 13

Page 14

Hardware Description

FTDI

PortA

3.3V

Regulator

USB

RESET

VBUS

6MHz

OSC

JTAG/SWD

PWR/UART

JTAG/SWD

MUX

EEPROM

PortB

POWER

2x4

2x10

JTAG/SWD

2x5

ACTIVE

DEBUG

USB

In-Circuit Debug Interface Board

The ICDI board is used to download and debug progr ams on the EK-LM3S9D90 evaluation board,

but can also be used for debug of other Stellaris boards. A block diagram is shown in Figure 2-5.

Figure 2-5. In Circuit Debug (ICDI) Board Block Diagram

Functional Description

USB to JTAG/SWD, Power (Schematic page 22)

USB

An FTDI USB to serial protocol chip is used for the USB 2.0 full-speed device controller. This is

connected to a USB miniB connector and to a set of buffers/multiplexers. A 1-kbit serial EEPROM

contains USB configuration data which is read at power up.

Power

The board receives 5 V power from the USB bus. A DC regulator generates 3.3 V for on-board

circuits, when on LED D1 (POWER) is lit on.

Headers

Three headers are on-board, a 10-pin JTAG/SWD header J1, an 8-pin PWR/UART header J2, and

an optional 20-pin JT AG/SWD head er J3. The 10-pin and 8-pin headers are use d to connect to the

EK-LM3S9D90 evaluation board.

JTAG/SWD

JTAG/SWD connector J1 connects to the EK-LM3S9D90 evaluation board with a ribbon cable for

program download and debug. This is a 2x5 fine pitch (0.050”) ARM JTAG connector, see

(Figure 2-6) for signal definition.The ICDI supports JTAG debug, SWD (Serial Wire Debug), and

SWO (Serial Wire Out) trace with this connector.

Optional JTAG/SWD connector J3 is a 2x10 standard pitch (0.1”) ARM JTAG connector directly

connected to J1, see (Figure 2 -7) for signal definition. This allows the ICDI to connect to targets

that use a 2x10 connector. It also allows the use of an external 2x10 debugger on targets with the

fine pitch connector, including the EK-LM3S9D90. The signal direction shown for J1 and J3

14 July 5, 2011

Page 15

Stellaris® LM3S9D90 Evaluation Kit User’s Manual

TMS/SWDIO

TCK/SWCLK

TDO/SWO

TDI

SRSTn GND

GND

GND

VSENSE

N/C

12

910

In

Out

Out

Out

In

I/O

TMS/SWDIO

TCK/SWCLK

TDO/SWO

TDI

SRSTn

12

1920

GND

GND

GND

GND

GND

GND

GND

GND

GND

N/C

N/C

N/C

N/C

N/C VSENSE

In

Out

Out

Out

In

I/O

VCP_TX

VCP_RX

GND

GND

DBG1

1

2

78

DBG2

5V 5V

In

Out

Out

Out

applies when the ICDI is used as the JTAG/SWD debugger and LED D2 (DEBUG ACTIVE) is lit

on. In this case only one of the two connectors J1/J3 should be used.

The ICDI can also be used as a 20-pin to 10-pin adapter for external JTAG debuggers. Note that

the DEBUG ACTIVE LED must be off before connecting any external JTAG debuggers.

Figure 2-6. JTAG/SWD Connector J1

Figure 2-7. JTAG/SWD Connector J3

Pushbutton

Pushbutton SW1 (RESET) is provided to manually generate the SRSTn signal to the target

device. The SRSTn signal can also be generated under program control.

PWR/UART

The PWR/UART connector J2 connects to the EK-LM3S9D90 evaluation board with a ribbon

cable and provides 5 V power and a virtual comm un i cations port connection. This is a 2 x 4 fine

pitch (0.050”) connector, see (Figure 2-8) for signal definition. Signals DBG1/DBG2 are reserved.

Figure 2-8. PWR/UART Connector

July 5, 2011 15

Page 16

Hardware Description

JTAG / SWD Multiplexer (Schematic page 23)

Buffers

A set of tri-state buffers is used to multiplex JTAG and SWD signals, and also multiplex the UART

VCP_TX signal with the SWO signal. LED D2 (DEBUG ACTIVE) is lit on when these buffers are

enabled. To avoid signal contention, external JTAG debuggers should not be connected when

DEBUG ACTIVE is on.

16 July 5, 2011

Page 17

CHAPTER 3

Software Development

This chapter provides general information on software development as well as instructions for

Flash memory programming.

Software Description

The software provided with the EK-LM3S9D90 provides access to all of the peripheral devices

supplied in the design. The Stellar isW are® Peripheral Driver Library is used to operate the on-ch ip

peripherals.

The software includes a set of example applications that utilize the StellarisW are Peripheral Driver

Library. These applications demonstrate the capabilities of the LM3S9D90 microcontroller, as well

as providing a starting point for the development of the final application for use on the

EK-LM3S9D90.

Source Code

The complete source code is included on the EK-LM3S9D90 CD. Refer to the Quickstart Guide for

a detailed description of hardware setup and how to install the source code. The source code and

binary files are installed in the DriverLib tree.

Tool Options

The source code installation includes directories containing projects and/or makefiles for the

following tool-chains:

Keil ARM RealView® Microcontroller Development System

IAR Embedded Workbench for ARM

Code So ur ce ry G+ +

Code Red Technology Red Suite

Generic Gnu C compiler

Evaluation versions of these tools may be downloaded from www.ti.com/stellaris. Due to code size

restrictions, the evaluation tools may not build all example p rograms. A full license is necessary to

re-build or debug all examples.

Instructions on installing and using each of the evaluation tools can be found in the Quickstart

guides (for example, Quickstart-Keil, Quickstart-IAR) which are available for download from the

evaluation kit section of our web site at www.ti.com/stellaris.

For detailed information on using the tools refer to the documentation included in the tool chain

installation or visit the website of the tools supplier.

Programming the EK-LM3S9D90 Board

The EK-LM3S9D90 software package includes pre-built binaries for each of the example

applications. If you installed DriverLib to the defaul t installation path of C:/DriverLib, you can find

the example applications in “C:/DriverLib /b o ar ds / ek-tempest”. The ICDI board is used along with

Stellaris LM Flash Programmer tool to program applications on the EK-LM3S9D90 board.

July 5, 2011 17

Page 18

Software Development

T o program example applications into the EK-LM3S9D90 evaluation board using the ICDI

board:

1. Install LM Flash Programmer on a Windows PC.

2. Connect the 10-wire ribbon cable to the 10-pin header on the ICDI board and to the 10-pin

header on the EK-LM3S9D90 board. The red stripe on the ribbon cable should be facing the

bottom of the connectors (see Figure B-5 on page 27).

3. Connect the 8-wire ribbon cable to the 8-pin header on the ICDI board and to the 8-pin heade r

on the EK-LM3S9D90 board. The red stri pe on the ribbon cable should be facing the bottom of

the connectors (see Figure B -5 on page 27).

4. Verify that slide switch SW3 on the EK-LM3S9D90 board is set to EXTernal.

5. Connect the USB cable A-plug to an available port on the PC and the miniB-plug to the ICDI

board.

6. Verify that POWER LED D1 on the ICDI board is lit and POWER LED D1 on the

EK-LM3S9D90 board is also lit.

7. Run LM Flash Programmer.

8. In the Configuration tab, use the Quick Set control to select LM3S9D90 Evaluation Board.

9. Move to the Program tab and click the Browse button. Navigate to the example applications

directory (the default location is “C:/DriverLib/boards/ek-tempest/).

10. Each example application has its own directory. Navigate into the example directory that you

want to load and then into the directory which co ntains the binary (*.bin) files. Select the binary

file and click Open.

11. Set the “Erase Method” to “Erase Necessary Pages” and check the “Verify After Program” box.

12. Next, click the Program button to start the Erase, Download and Verify process. The DEBUG

ACTIVE LED (D2) on the ICDI will turn on at this time.

13. Program execution will start once Verify is complete.

The EK-LM3S9D90 design uses a S tellaris® microcontroller to handle networ king, USB-OTG, and

peripheral functions. The entire circuit is built on a compact four-layer printed circuit board. All

design files are provided on the EK-LM3S9D90 CD.

18 July 5, 2011

Page 19

APPENDIX A

Schematics

This section contains the schematics for the EK-LM3S9D90 evaluation board and also the

BD-ICDI debug board.

EK-LM3S9D90 Evaluation Board

Microcontroller, Reset, and Headers on page 20

Ethernet, USB, and Power on page 21

BD-ICDI Board

USB to JTAG, SWD, Headers, and Power on page 22

JTAG/SWD Multiplexer on page 23

July 5, 2011 19

Page 20

Microcontroller, Reset, and Headers

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

SheetDate: of

6/17/2011

12

C

Designer:

Drawn by:

Approved:

Drawing Title:

Page Title:

Size

Arnaldo Cruz

Arnaldo Cruz

*

0001

EK-LM3S9B90 and EK-LM3S9D90 Evaluation Board

Tempest, Reset, Test Pads

B

108 Wild Basin Rd.

Suite 350

Austin, TX 78746

TI AEC - Austin

C18

18pF

C17

18pF

C16

18pF

C15

18pF

RSTn

OSCin

OSCout

XTALN

XTALP

R8

12.4K

R7

9.1k

USBDP

USBDM

3.3V

C22

1uF

C19

0.1uF

C7

0.1uFC80.1uFC90.1uF

C10

0.1uF

C11

0.1uF

C6

1uF

C13

0.1uF

C20

0.1uF

C23

0.1uF

XOSC0

XOSC1

R9 1M

C5

18pF

C4

18pF

Y3

4.194304 MHz

ETH_TXOP

ETH_TXON

ETH_MDIO

ETH_LED0

ETH_LED1

ETH_RXIP

ETH_RXIN

USBPWR

USBFLT

USBID

3.3V

TMS

TCK

TDO

TDI

C1

0.1uF

VBUS

PF4

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PB2

PB3

PH0

PH1

PH2

PH5

PH6

PH7

PJ0

PJ1

PJ2

WAKEn

PG0

PG1

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PC4

PC5

PC6

PC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PG7

3.3V

R6

10K

C2

0.1uF

R4 10K

PC0

PC1

PC2

PC3

R3 10K

R2 10K

R1 10K

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PF2

PF3

PF4

PF5

PH0

PH1

PH2

PH5

PH6

PH7

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PG0 PG1

PG7

1

4

2

3

RESET

SW1

PJ0

PJ1

PJ2

PE0

PF5

VBAT

RSTn

3.3V

R5

10K

HIBn

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC4

PC5

PC6

PC7

WAKEn

VBAT

HIBn

LM3S9B90/LM3S9D90

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4

25

PC5

24

PC6

23

PC7

22

PD0

10

PD1

11

PD2

12

PD3

13

PD4

97

PD5

98

PD6

99

PD7

100

GND

9

GND

21

ERBIAS

33

RST

64

LDO

7

OSC0

48

OSC1

49

PB0/USB0ID

66

PB1/USB0VBUS

67

PB2/I2C0SCL

72

PB3/I2C0SDA

65

PB4

92

PB5

91

PB6

90

PB7

89

PE0

74

PE1

75

PE2

95

PE3

96

PE4

6

PE5

5

PA6

34

PA7

35

PE6

2

PE7

1

PF0

47

PF1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

PF4

42

PG0

19

PG1

18

XTALNPHY

17

XTALPPHY

16

PF5

41

RXIP

40

RXIN

37

PG7

36

PH0

86

PH1

85

PH2

84

PH3/USB0EPEN

83

AVDD

3

AGND

4

VDD33

8

VDD33

20

VDD33

32

VDD33

44

VDD33

56

VDD33

68

VDD33

81

VDD33

93

GND

45

GND

57

GND

69

GND

82

GND

94

CVDD

38

CVDD

88

HIB

51

PH4/USB0PFLT

76

USB0DP

71

USB0DM

70

USB0RBIAS

73

PH5

63

PH6

62

PH7

15

PJ0

14

PJ1

87

PJ2

39

WAKEn

50

XOSC0

52

XOSC1

53

GND

54

VBAT

55

U1

5V

1 2

Y1

16.000 MHz

C12

0.1uF

C14

0.1uF

SHDNn

VBUS

3.3V

R24

10K

1 2

Y2

25.000 MHz

JTAG/SWD

1

3

5

7

9

2

4

6

8

10

J1

HDR 2X5-MH-SHRD

VCP_RX

5V

PWR/UART

1

3

5

7

2

4

6

8

J2

HDR 2X4-MH-SHRD

DBG1DBG2

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP41

TP42

TP43

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

TP56

TP57

TP58

TP59

TP60

TP61

TP62

TP63

TP64

TP65

TP66

TP67

TP68

FB1

120ohm @ 100 MHz

PA0

PA1

VCP_RX

VCP_TX

PB4

PD0

USR_PBn

USR_LED

JR1

JR2

JR3

JR4

VCP_TX

JR5

JR6

PF2

PF3

PF2

PF3

C3

0.1uF

3.3V

Revision History

Revision

A

2/24/2009 First release for prototypes.

Date Description

B

4/15/2009 Released to production.

R23 10

CVDD

5VR

C

1/21/2010 DC regulators U2 and U4 replaced for TI parts.

6/17/2011 Add option to install either LM3S9B90 or LM3S9D90

July 5, 2011 20

Page 21

Ethernet, USB, and Power

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

SheetDate: of

6/17/2011

12

C

Designer:

Drawn by:

Approved:

Drawing Title:

Page Title:

Size

Arnaldo Cruz

Arnaldo Cruz

*

0001

EK-LM3S9B90 and EK-LM3S9D90 Evaluation Board

Tempest, Reset, Test Pads

B

108 Wild Basin Rd.

Suite 350

Austin, TX 78746

TI AEC - Austin

C18

18pF

C17

18pF

C16

18pF

C15

18pF

RSTn

OSCin

OSCout

XTALN

XTALP

R8

12.4K

R7

9.1k

USBDP

USBDM

3.3V

C22

1uF

C19

0.1uF

C7

0.1uFC80.1uFC90.1uF

C10

0.1uF

C11

0.1uF

C6

1uF

C13

0.1uF

C20

0.1uF

C23

0.1uF

XOSC0

XOSC1

R9 1M

C5

18pF

C4

18pF

Y3

4.194304 MHz

ETH_TXOP

ETH_TXON

ETH_MDIO

ETH_LED0

ETH_LED1

ETH_RXIP

ETH_RXIN

USBPWR

USBFLT

USBID

3.3V

TMS

TCK

TDO

TDI

C1

0.1uF

VBUS

PF4

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PB2

PB3

PH0

PH1

PH2

PH5

PH6

PH7

PJ0

PJ1

PJ2

WAKEn

PG0

PG1

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PC4

PC5

PC6

PC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PG7

3.3V

R6

10K

C2

0.1uF

R4 10K

PC0

PC1

PC2

PC3

R3 10K

R2 10K

R1 10K

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PF2

PF3

PF4

PF5

PH0

PH1

PH2

PH5

PH6

PH7

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PG0 PG1

PG7

1

4

2

3

RESET

SW1

PJ0

PJ1

PJ2

PE0

PF5

VBAT

RSTn

3.3V

R5

10K

HIBn

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC4

PC5

PC6

PC7

WAKEn

VBAT

HIBn

LM3S9B90/LM3S9D90

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4

25

PC5

24

PC6

23

PC7

22

PD0

10

PD1

11

PD2

12

PD3

13

PD4

97

PD5

98

PD6

99

PD7

100

GND

9

GND

21

ERBIAS

33

RST

64

LDO

7

OSC0

48

OSC1

49

PB0/USB0ID

66

PB1/USB0VBUS

67

PB2/I2C0SCL

72

PB3/I2C0SDA

65

PB4

92

PB5

91

PB6

90

PB7

89

PE0

74

PE1

75

PE2

95

PE3

96

PE4

6

PE5

5

PA6

34

PA7

35

PE6

2

PE7

1

PF0

47

PF1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

PF4

42

PG0

19

PG1

18

XTALNPHY

17

XTALPPHY

16

PF5

41

RXIP

40

RXIN

37

PG7

36

PH0

86

PH1

85

PH2

84

PH3/USB0EPEN

83

AVDD

3

AGND

4

VDD33

8

VDD33

20

VDD33

32

VDD33

44

VDD33

56

VDD33

68

VDD33

81

VDD33

93

GND

45

GND

57

GND

69

GND

82

GND

94

CVDD

38

CVDD

88

HIB

51

PH4/USB0PFLT

76

USB0DP

71

USB0DM

70

USB0RBIAS

73

PH5

63

PH6

62

PH7

15

PJ0

14

PJ1

87

PJ2

39

WAKEn

50

XOSC0

52

XOSC1

53

GND

54

VBAT

55

U1

5V

1 2

Y1

16.000 MHz

C12

0.1uF

C14

0.1uF

SHDNn

VBUS

3.3V

R24

10K

1 2

Y2

25.000 MHz

JTAG/SWD

1

3

5

7

9

2

4

6

8

10

J1

HDR 2X5-MH-SHRD

VCP_RX

5V

PWR/UART

1

3

5

7

2

4

6

8

J2

HDR 2X4-MH-SHRD

DBG1DBG2

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP41

TP42

TP43

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

TP56

TP57

TP58

TP59

TP60

TP61

TP62

TP63

TP64

TP65

TP66

TP67

TP68

FB1

120ohm @ 100 MHz

PA0

PA1

VCP_RX

VCP_TX

PB4

PD0

USR_PBn

USR_LED

JR1

JR2

JR3

JR4

VCP_TX

JR5

JR6

PF2

PF3

PF2

PF3

C3

0.1uF

3.3V

Revision History

Revision

A

2/24/2009 First release for prototypes.

Date Description

B

4/15/2009 Released to production.

R23 10

CVDD

5VR

C

1/21/2010 DC regulators U2 and U4 replaced for TI parts.

6/17/2011 Add option to install either LM3S9B90 or LM3S9D90

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

Sheet

Date:

of

6/17/2011

22

C

Drawing Title:

Page Title:

Size

B

Ethernet, USB, Power

EK-LM3S9B90 and EK-LM3S9D90 Evaluation Board

0001

C25

0.1uF

C32

0.01uF

C26

0.01uF

C31

0.1uF

R13

49.9

R16

49.9

3.3V

6

5

8

4

2

3

1

7

1CT:1

TX+

TXRX+

RX-

1CT:1

Y+

Y-

G+

G-

3

8

7

4

5

6

11

12

2

1

GL

GR

9

10

NC

GND

ETHERNET 10/100

J6

PulseJack_RJ45_SMT

R10

10K

R11

330

R12

330

R14

49.9

R17

49.9

ETH_RXIP

ETH_RXIN

ETH_TXOP

ETH_TXON

ETH_MDIO

ETH_LED0

ETH_LED1

3.3V

R21 10K

5V

R20

330

PWR

D1

GREEN_LED

R18

330

USR

D2

GREEN_LED

3.3V

R15

10K

1

4

2

3

USR PB

SW2

OC

3

VIN

5

EN

4

GND

2

VOUT

1

U3

TPS2051B

R22

10K

3.3V

R19

10K

VOUT

USBPWR

USBFLT

C38

4.7uF

USR_PBn

USR_LED

SHDNn

VBUS

5V

C27

10pF

C28

10pF

C29

10pF

C30

10pF

USBDP

USBDM

VBUS

USBID

FB2

120ohm @ 100 MHz

FB3

120ohm @ 100 MHz

C36

0.1uF

C35

0.1uF

C33

4.7uF

C34

4.7uF

C37

4.7uF

2

1

3

5

4

6

SW3

Switch DPDT

VUSB

VBUS D- D+ ID G

12345

J5

USB Micro AB

G1 G2

100 Mil Mask

FID3

40 Mil Pad

100 Mil Mask

FID1

40 Mil Pad

100 Mil Mask

FID2

40 Mil Pad

Fiducials

R25 10

R26 10

CVDD

Note:

U4 required on ly for LM3S9B90-B1.

See errata. Do not install for all

other devices/revisions.

Note:

R25-R26 = 10 ohms for LM3S9B90-B1, see errata.

R25-R26 = 0 ohms for LM3S9B90-C.

5VR

VIN1VOUT

5

EN

3

GND2FB

4

U4

TPS73101

VIN8VOUT

1

EN

5

GND4NR

3

NC

2

NC

6

NC

7

TPAD

TPAD

U2

TPS73633DRB

July 5, 2011 21

Page 22

USB to JTAG, SWD, Headers, and Power

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

SheetDate: of

6/17/2011

12

C

Designer:

Drawn by:

Approved:

Drawing Title:

Page Title:

Size

Arnaldo Cruz

Arnaldo Cruz

*

0001

EK-LM3S9B90 and EK-LM3S9D90 Evaluation Board

Tempest, Reset, Test Pads

B

108 Wild Basin Rd.

Suite 350

Austin, TX 78746

TI AEC - Austin

C18

18pF

C17

18pF

C16

18pF

C15

18pF

RSTn

OSCin

OSCout

XTALN

XTALP

R8

12.4K

R7

9.1k

USBDP

USBDM

3.3V

C22

1uF

C19

0.1uF

C7

0.1uFC80.1uFC90.1uF

C10

0.1uF

C11

0.1uF

C6

1uF

C13

0.1uF

C20

0.1uF

C23

0.1uF

XOSC0

XOSC1

R9 1M

C5

18pF

C4

18pF

Y3

4.194304 MHz

ETH_TXOP

ETH_TXON

ETH_MDIO

ETH_LED0

ETH_LED1

ETH_RXIP

ETH_RXIN

USBPWR

USBFLT

USBID

3.3V

TMS

TCK

TDO

TDI

C1

0.1uF

VBUS

PF4

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PB2

PB3

PH0

PH1

PH2

PH5

PH6

PH7

PJ0

PJ1

PJ2

WAKEn

PG0

PG1

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PC4

PC5

PC6

PC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PG7

3.3V

R6

10K

C2

0.1uF

R4 10K

PC0

PC1

PC2

PC3

R3 10K

R2 10K

R1 10K

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PF2

PF3

PF4

PF5

PH0

PH1

PH2

PH5

PH6

PH7

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PG0 PG1

PG7

1

4

2

3

RESET

SW1

PJ0

PJ1

PJ2

PE0

PF5

VBAT

RSTn

3.3V

R5

10K

HIBn

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC4

PC5

PC6

PC7

WAKEn

VBAT

HIBn

LM3S9B90/LM3S9D90

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4

25

PC5

24

PC6

23

PC7

22

PD0

10

PD1

11

PD2

12

PD3

13

PD4

97

PD5

98

PD6

99

PD7

100

GND

9

GND

21

ERBIAS

33

RST

64

LDO

7

OSC0

48

OSC1

49

PB0/USB0ID

66

PB1/USB0VBUS

67

PB2/I2C0SCL

72

PB3/I2C0SDA

65

PB4

92

PB5

91

PB6

90

PB7

89

PE0

74

PE1

75

PE2

95

PE3

96

PE4

6

PE5

5

PA6

34

PA7

35

PE6

2

PE7

1

PF0

47

PF1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

PF4

42

PG0

19

PG1

18

XTALNPHY

17

XTALPPHY

16

PF5

41

RXIP

40

RXIN

37

PG7

36

PH0

86

PH1

85

PH2

84

PH3/USB0EPEN

83

AVDD

3

AGND

4

VDD33

8

VDD33

20

VDD33

32

VDD33

44

VDD33

56

VDD33

68

VDD33

81

VDD33

93

GND

45

GND

57

GND

69

GND

82

GND

94

CVDD

38

CVDD

88

HIB

51

PH4/USB0PFLT

76

USB0DP

71

USB0DM

70

USB0RBIAS

73

PH5

63

PH6

62

PH7

15

PJ0

14

PJ1

87

PJ2

39

WAKEn

50

XOSC0

52

XOSC1

53

GND

54

VBAT

55

U1

5V

1 2

Y1

16.000 MHz

C12

0.1uF

C14

0.1uF

SHDNn

VBUS

3.3V

R24

10K

1 2

Y2

25.000 MHz

JTAG/SWD

1

3

5

7

9

2

4

6

8

10

J1

HDR 2X5-MH-SHRD

VCP_RX

5V

PWR/UART

1

3

5

7

2

4

6

8

J2

HDR 2X4-MH-SHRD

DBG1DBG2

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP41

TP42

TP43

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

TP56

TP57

TP58

TP59

TP60

TP61

TP62

TP63

TP64

TP65

TP66

TP67

TP68

FB1

120ohm @ 100 MHz

PA0

PA1

VCP_RX

VCP_TX

PB4

PD0

USR_PBn

USR_LED

JR1

JR2

JR3

JR4

VCP_TX

JR5

JR6

PF2

PF3

PF2

PF3

C3

0.1uF

3.3V

Revision History

Revision

A

2/24/2009 First release for prototypes.

Date Description

B

4/15/2009 Released to production.

R23 10

CVDD

5VR

C

1/21/2010 DC regulators U2 and U4 replaced for TI parts.

6/17/2011 Add option to install either LM3S9B90 or LM3S9D90

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

SheetDate: of

5/18/2009

12

B

Designer:

Drawn by:

Approved:

Drawing Title:

Page Title:

Size

Arnaldo Cruz

Arnaldo Cruz

*

0001

In Circuit Debug Interface (ICDI) Board

USB to JTAG, SWD

B

108 Wild Basin Rd.

Suite 350

Austin, TX 78746

Texas Instruments

1 2

Y1

6.000MHz

3.3V

3.3V

5V

5V

R5 27

R7

1.50k

R9 2.21k

USBP

USBM

5V

VCP_RX

VCP_TX_SWO

R13

330

VCP_RX

5V

5V

3.3V

C12

4.7uF

C11

4.7uF

5V

VIN4VOUT

5

SHDN

3

GND2NR

1

U3

PQ1LA333MSPQ

C7

18pF

C8

18pF

PWR/UART

1

3

5

7

2

4

6

8

J2

HDR 2X4-MH-SHRD

R15

330

PWR

D1

GREEN_LED

FB1

120ohm @ 100 MHz

5V D- D+ ID G

123

4G25

G1

G3 G4

J4

USB_MINI_B_RECEPTACLE

XTI

XTO

UDM

UDP

EECS

EESK

EEDATA

FT_SK

FT_DO

FT_DI

FT_CS

DBGENn

DBGMOD

VCP_TX_SWO

SWO_EN

TCK

TDI

TDO_SWO

TMS_SWDIO

VCP_TX

12

34

56

78

910

1112

1314

1516

1718

1920

JTAG/SWD

J3

2X10 HDR-SHRD

JTAG/SWD

1

3

5

7

9

2

4

6

8

10

J1

HDR 2X5-MH-SHRD

TCK

TMS

TDI

TDO

SRSTn

3.3V

DBG1

DBG1

DBG2

1

4

2

3

RESET

SW1

12 11

13

U5D

SN74LVC125A

DBGRSTn

SRSTn

VSENSE

R12

475

CS

1

SK

2

DI

3

DO

4

GND

5

NC

7

ORG

6

VCC

8

1K 64X16

U2

CAT93C46

FB2

120ohm @ 100 MHz

VBUS

DBG2

DEBUG ACTIVE

D2

GREEN_LED

R1

10KR210KR310KR410K

R11 10K

R8

10K

R10

10K

R14

10K

R6 27

C1

0.1uF

C9

0.1uF

C2

0.1uF

C3

0.1uFC40.1uFC50.1uFC60.1uF

C13

0.1uF

GND

18

GND

25

GND

34

ADBUS0

24

ADBUS1

23

ADBUS2

22

ADBUS3

21

ADBUS4

20

ADBUS5

19

ADBUS6

17

ADBUS7

16

ACBUS0

15

ACBUS1

13

ACBUS2

12

ACBUS3

11

BDBUS0

40

BDBUS1

39

BDBUS2

38

BDBUS3

37

BDBUS4

36

BDBUS5

35

BDBUS6

33

BDBUS7

32

BCBUS0

30

BCBUS1

29

BCBUS2

28

BCBUS3

27

SI/WUA

10

SI/WUB

26

GND

9

AGND

45

VCC

3

VCC

42

VCCIOA

14

VCCIOB

31

AVCC

46

PWREN#

41

XTOUT

44

XTIN

43

EECS

48

EESK

1

EEDATA

2

TEST

47

RESET#

4

RSTOUT#

5

3V3OUT

6

USBDM

8

USBDP

7

U1

FT2232

Revision History

Revision

A 2/24/2009 First release for prototypes.

Date Description

B 4/03/2009 Released for production.

R19 10

July 5, 2011 22

Page 23

JTAG/SWD Multiplexer

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

SheetDate: of

6/17/2011

12

C

Designer:

Drawn by:

Approved:

Drawing Title:

Page Title:

Size

Arnaldo Cruz

Arnaldo Cruz

*

0001

EK-LM3S9B90 and EK-LM3S9D90 Evaluation Board

Tempest, Reset, Test Pads

B

108 Wild Basin Rd.

Suite 350

Austin, TX 78746

TI AEC - Austin

C18

18pF

C17

18pF

C16

18pF

C15

18pF

RSTn

OSCin

OSCout

XTALN

XTALP

R8

12.4K

R7

9.1k

USBDP

USBDM

3.3V

C22

1uF

C19

0.1uF

C7

0.1uFC80.1uFC90.1uF

C10

0.1uF

C11

0.1uF

C6

1uF

C13

0.1uF

C20

0.1uF

C23

0.1uF

XOSC0

XOSC1

R9 1M

C5

18pF

C4

18pF

Y3

4.194304 MHz

ETH_TXOP

ETH_TXON

ETH_MDIO

ETH_LED0

ETH_LED1

ETH_RXIP

ETH_RXIN

USBPWR

USBFLT

USBID

3.3V

TMS

TCK

TDO

TDI

C1

0.1uF

VBUS

PF4

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PB2

PB3

PH0

PH1

PH2

PH5

PH6

PH7

PJ0

PJ1

PJ2

WAKEn

PG0

PG1

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PC4

PC5

PC6

PC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PG7

3.3V

R6

10K

C2

0.1uF

R4 10K

PC0

PC1

PC2

PC3

R3 10K

R2 10K

R1 10K

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PF0

PF1

PF2

PF3

PF4

PF5

PH0

PH1

PH2

PH5

PH6

PH7

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PG0 PG1

PG7

1

4

2

3

RESET

SW1

PJ0

PJ1

PJ2

PE0

PF5

VBAT

RSTn

3.3V

R5

10K

HIBn

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC4

PC5

PC6

PC7

WAKEn

VBAT

HIBn

LM3S9B90/LM3S9D90

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4

25

PC5

24

PC6

23

PC7

22

PD0

10

PD1

11

PD2

12

PD3

13

PD4

97

PD5

98

PD6

99

PD7

100

GND

9

GND

21

ERBIAS

33

RST

64

LDO

7

OSC0

48

OSC1

49

PB0/USB0ID

66

PB1/USB0VBUS

67

PB2/I2C0SCL

72

PB3/I2C0SDA

65

PB4

92

PB5

91

PB6

90

PB7

89

PE0

74

PE1

75

PE2

95

PE3

96

PE4

6

PE5

5

PA6

34

PA7

35

PE6

2

PE7

1

PF0

47

PF1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

PF4

42

PG0

19

PG1

18

XTALNPHY

17

XTALPPHY

16

PF5

41

RXIP

40

RXIN

37

PG7

36

PH0

86

PH1

85

PH2

84

PH3/USB0EPEN

83

AVDD

3

AGND

4

VDD33

8

VDD33

20

VDD33

32

VDD33

44

VDD33

56

VDD33

68

VDD33

81

VDD33

93

GND

45

GND

57

GND

69

GND

82

GND

94

CVDD

38

CVDD

88

HIB

51

PH4/USB0PFLT

76

USB0DP

71

USB0DM

70

USB0RBIAS

73

PH5

63

PH6

62

PH7

15

PJ0

14

PJ1

87

PJ2

39

WAKEn

50

XOSC0

52

XOSC1

53

GND

54

VBAT

55

U1

5V

1 2

Y1

16.000 MHz

C12

0.1uF

C14

0.1uF

SHDNn

VBUS

3.3V

R24

10K

1 2

Y2

25.000 MHz

JTAG/SWD

1

3

5

7

9

2

4

6

8

10

J1

HDR 2X5-MH-SHRD

VCP_RX

5V

PWR/UART

1

3

5

7

2

4

6

8

J2

HDR 2X4-MH-SHRD

DBG1DBG2

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP41

TP42

TP43

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

TP56

TP57

TP58

TP59

TP60

TP61

TP62

TP63

TP64

TP65

TP66

TP67

TP68

FB1

120ohm @ 100 MHz

PA0

PA1

VCP_RX

VCP_TX

PB4

PD0

USR_PBn

USR_LED

JR1

JR2

JR3

JR4

VCP_TX

JR5

JR6

PF2

PF3

PF2

PF3

C3

0.1uF

3.3V

Revision History

Revision

A

2/24/2009 First release for prototypes.

Date Description

B

4/15/2009 Released to production.

R23 10

CVDD

5VR

C

1/21/2010 DC regulators U2 and U4 replaced for TI parts.

6/17/2011 Add option to install either LM3S9B90 or LM3S9D90

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number: Rev

Sheet

Date:

of

4/9/2009

22

B

Drawing Title:

Page Title:

Size

B

JTAG, SWD Mux

In Circuit Debug Interface (ICDI) Board

0001

3.3V

FT_SK

FT_DO

FT_DI

FT_CS

DBGENn

DBGMOD

VCP_TX_SWO

SWO_EN

2 3

1

U4A

SN74LVC125A

5 6

4

U5B

SN74LVC125A

98

10

U5C

SN74LVC125A

12 11

13

U4D

SN74LVC125A

147

VCC

GND

U5E

SN74LVC125A

2 3

1

U5A

SN74LVC125A

147

VCC

GND

U4E

SN74LVC125A

56

4

U4B

SN74LVC125A

9 8

10

U4C

SN74LVC125A

2 3

1

U6A

SN74LVC126A

5 6

4

U6B

SN74LVC126A

98

10

U6C

SN74LVC126A

1211

13

U6D

SN74LVC126A

147

VCC

GND

U6E

SN74LVC126A

3.3V

TCK

TDI

TDO_SWO

TMS_SWDIO

VCP_TX

3.3V

R16 27

R17 27

R18 27

R20

10K

R21

10K

R22

10K

C14

0.1uF

C15

0.1uF

C16

0.1uF

100 Mil Mask

FID3

40 Mil Pad

100 Mil Mask

FID1

40 Mil Pad

100 Mil Mask

FID2

40 Mil Pad

Fiducials

July 5, 2011 23

Page 24

24 July 5, 2011

Page 25

APPENDIX B

Connection Details

This appendix contains the following sections:

Component Locations (see page 25)

Board Dimensions (see page 26)

Board Connectivity (see page 27)

References (see page 27)

Component Locations

Figure B-1. EK-LM3S9D90 Evaluation Board Component Locations

Figure B-2. BD-ICDI Board Component Locations

July 5, 2011 25

Page 26

Board Dimensions

4.00

1.40

0.07

0.07

0.07

0.07

0.07

0.07

0. 34

Ø 0.100

2.50

1.40

0.07

0.07

0.07

0.07

Ø 0.100

0.07

Board Dimensions

Figure B-3. EK-LM3S9D90 Evaluation Board Dimensions

Figure B-4. In-Circuit Debug Interface Board Dimensions

26 July 5, 2011

Page 27

Board Connectivity

BD-ICDI

Board

EK-LM3S9D90

Evaluation Board

8-wire cable

JTAG/SWD

PWR/UART

10-wire cable

Figure B-5. ICDI – EK-LM3S9D90 Board Connectivity

References

In addition to this document, the following references are included on the Stellaris Evaluation Kit

CD-ROM and are also available for download at www.ti.com/stellaris

Stellaris LM3S9D90 Data Sheet, publication DS-LM3S9D90

StellarisWare Driver Library

StellarisWare Driver Library User’s Manual, publication SW-DRL-UG

Additional references include:

FT2232D Dual USB/UART FIFO IC Datasheet, version 0.91, 2006, Future Technology

Devices International Ltd.

Information on development tool being used:

Stellaris® LM3S9D90 Evaluation Kit User’s Manual

:

July 5, 2011 27

– RealView MDK web site, www.keil.com/arm/rvmdkkit.asp

– IAR Embedded Workbench web site, www.iar.com

– Sourcery CodeBench development tools web site,

www.codesourcery.com/gnu_toolchains/arm

– Code Red Techn olo gie s de velop m en t to ols we b site , www.code-red-tech.com

– Texas Instruments’ Code Composer Studio™ IDE web site, www.ti.com/ccs

Page 28

References

28 July 5, 2011

Page 29

APPENDIX C

Microcontroller GPIO Assignments

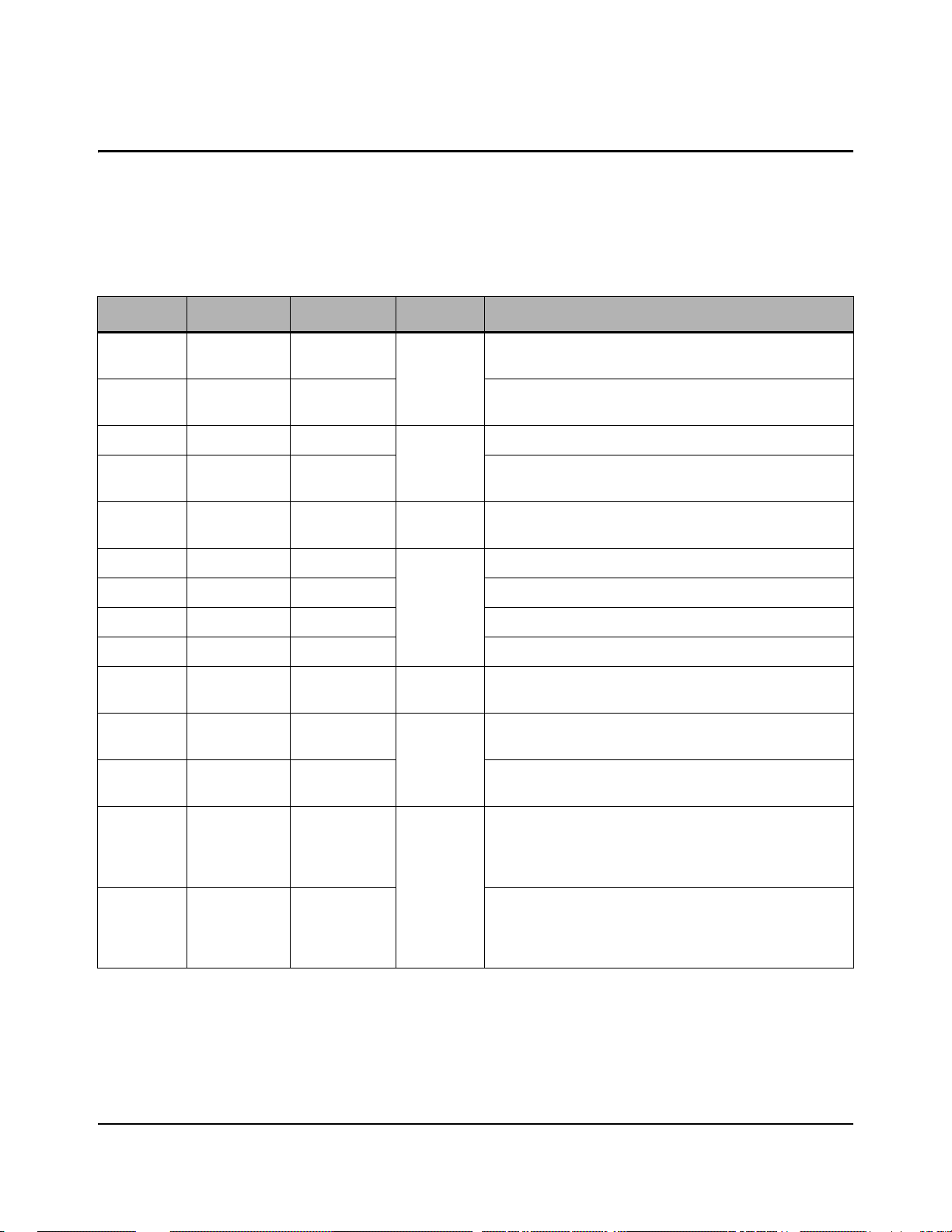

The following table shows the LM3S9D90 GPIOs used by the EK-LM3S9D90 board. All other

GPIOs are available for use and accessible on the test pads.

Table C-1. EK-LM3S9D90 Evaluation Board GPIO Usage

Port Function Board Signal Usage Description

PA0 U0RX VCP_RX

UART

PA1 U0TX VCP_TX

PB0 USB0ID USBID

PB1 USB0VBUS VBUS

PB4 GPIO USR_PBn User

PC0 TCK/SWCLK PC0

PC1 TMS/SWDIO PC1 JTAG TMS input or SWD bidirectional signal SWDIO

PC2 TDI PC2 JTAG TDI signal input.

PC3 TDO/SWO PC3 JTAG TDO output or SWD trace signal SWO output.

PD0 GPIO USR_LED User

PF2 LED1 ETH_LED1

PF3 LED0 ETH_LED0

USB

JTAG/

SWD

Ethernet

Virtual Communications port receive signal from J2

header. To disconnect from header cut JR1 jumper.

Virtual Communications port transmit signal to J2

header. To disconnect from header cut JR2 jumper.

USBID signal from the USB-On-the-Go connector J5.

USB VBUS input signal from USB-OTG connector J5 for

sensing VBUS levels.

Input from user pushbutton SW2. To disconn ect from

pushbutton cut JR3 jumper.

JT AG or SWD clock input

Output to user LED D2. To disconnect from LED cut JR4

jumper.

Output to RJ45 jack J6 yellow LED. To disconnect from

LED cut JR5 jumper.

Output to RJ45 jack J6 green LED. To disconnect from

LED cut JR6 jumper.

Output to USB-OTG power switch U3. When set high it

PH3 USB0EPEN USBPWR

USB

PH4 U SB0PFLT USBPFLT

July 5, 2011 29

enables the USB-OTG power switch to provide USB

VBUS power to USB-OTG connector J5. When set low

power switch U3 is disabled.

Overcurrent input status from USB-OTG power switch

U3. When high the power switch status is normal. When

low an overcurrent condition has been detected by the

switch.

Page 30

30 July 5, 2011

Page 31

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications

Amplifiers amplifier.ti.com Computers and Peripherals www.ti.com/computers

Data Converters dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps

DLP® Products www.dlp.com Energy and Lighting www.ti.com/energy

DSP dsp.ti.com Industrial www.ti.com/industrial

Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface interface.ti.com Security www.ti.com/security

Logic logic.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com Wireless www.ti.com/wireless-apps

RF/IF and ZigBee® Solutions www.ti.com/lprf

TI E2E Community Home Page e2e.ti.com

Automotive

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2011, Texas Instruments Incorporated

Page 32

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Texas Instruments:

EKC-LM3S9D90 EKI-LM3S9D90 EKK-LM3S9D90 EKT-LM3S9D90 EKS-LM3S9D90

Loading...

Loading...