Page 1

Stellaris® LM3S9B96 Development Kit

User’s Manual

DK-LM3S9B96-05 Copyright © 2009–2010 Texas Instruments

Page 2

Copyright

Copyright © 2009–2010 Texas Instruments, Inc. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments.

ARM and Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property

of others.

Texas Instruments

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

2 September 5, 2010

Page 3

Stellaris® LM3S9B96 Development Kit User’s Manual

Table of Contents

Chapter 1: Stellaris® LM3S9B96 Development Board Overview .................................................................7

Features..............................................................................................................................................................7

Development Kit Contents................................................................................................................................10

Block Diagram .................................................................................................................................................. 11

Development Board Specifications...................................................................................................................11

Chapter 2: Stellaris® LM3S9B96 Development Board Hardware Description..........................................13

LM3S9B96 Microcontroller Overview ..................................... ... .... ................................................ ...................13

Jumpers and GPIO Assignments.................................................................................................................. 13

Clocking........................................................................................................................................................14

Reset.............................................................................................................................................................15

Power Supplies.............................................................................................................................................15

USB...............................................................................................................................................................15

Debugging.....................................................................................................................................................16

Color QVGA LCD Touch Panel.....................................................................................................................17

2

I

S Audio ... ... ................................................. ... ... ... ... .... ................................................ ................................19

User Switch and LED.......................................... ... ... .... ... ... ..........................................................................19

Chapter 3: Stellaris® LM3S9B96 Development Board External Peripheral Interface (EPI) ..................... 21

SDRAM Expansion Board ......................................................... .... ... ................................................................21

Flash and SRAM Memory Expansion Board ....................................................................................................21

FPGA Expansion Board................ ... .... ... ... ... .... ... ................................................... .... ... ...................................21

EM2 Expansion Board......................................................................................................................................21

Chapter 4: Using the In-Circuit Debugger Interface....................................................................................23

Appendix A: Stellaris® LM3S9B96 Development Board Schematics........................................................ 25

Appendix B: Stellaris® LM3S9B96 Development Board Component Locations......................................33

Appendix C: Stellaris® LM3S9B96 Development Board Connection Details ...........................................35

DC Power Jack....................................................................... ... .... ... ... ... .... ... ................................................... 35

ARM Target Pinout ........................................................................................................................................... 35

Appendix D: Stellaris® LM3S9B96 Development Board Microcontroller GPIO Assignments ................37

Appendix E: Stellaris® LM3S9B96 Flash and SRAM Memory Expansion Board ..................................... 41

Features............................................................................................................................................................41

Installation......................................................................................................................................................... 41

Hardware Description ....................................................................................................................................... 43

Functional Description ..................... ... ... ... .... ................................................... ... .... ......................................43

Memory Map.............................. ... ... .... ... ... ... .... ... ................................................ ... .... ... ...................................45

Component Locations.......................................................................................................................................46

Schematics.......................................................................................................................................................46

Appendix F: Stellaris® LM3S9B96 FPGA Expansion Board.......................... ... .... ... ... ... ....... ... ... ... .... ... ... ... 49

Features............................................................................................................................................................49

Installation......................................................................................................................................................... 50

Hardware Description ....................................................................................................................................... 52

FPGA............................................................................................................................................................ 52

Camera.........................................................................................................................................................52

September 5, 2010 3

Page 4

SRAM............................................................................................................................................................52

Configuration PROM........................................ ... ..........................................................................................52

Configuration Pushbutton ............................................................................................................................. 52

Test Port .......................................................................................................................................................53

Camera Connector........................................................................................................................................53

5 V Power Pin...............................................................................................................................................53

24-MHz Oscillator .........................................................................................................................................53

External Peripheral Interface (EPI) Module ..................................................................................................53

Using the Widget Interface ...............................................................................................................................53

Writing Your Own Stellaris Application .........................................................................................................53

Memory Map.............................. ... ... .... ... ... ... .... ... ................................................ ... .... ... ...................................54

Register Descriptions.................................................................................................................................... 55

Loading a New Image to the FPGA..................................................................... ... .... ... ... ... .... ... ... ...................61

Installing the Software...................................................................................................................................62

Modifying the Default Image.........................................................................................................................62

Default FPGA Image Blocks.........................................................................................................................62

EPI Signal Descriptions .......................................... ... ... .... ... .............................................................................63

Component Locations.......................................................................................................................................64

Schematics.......................................................................................................................................................65

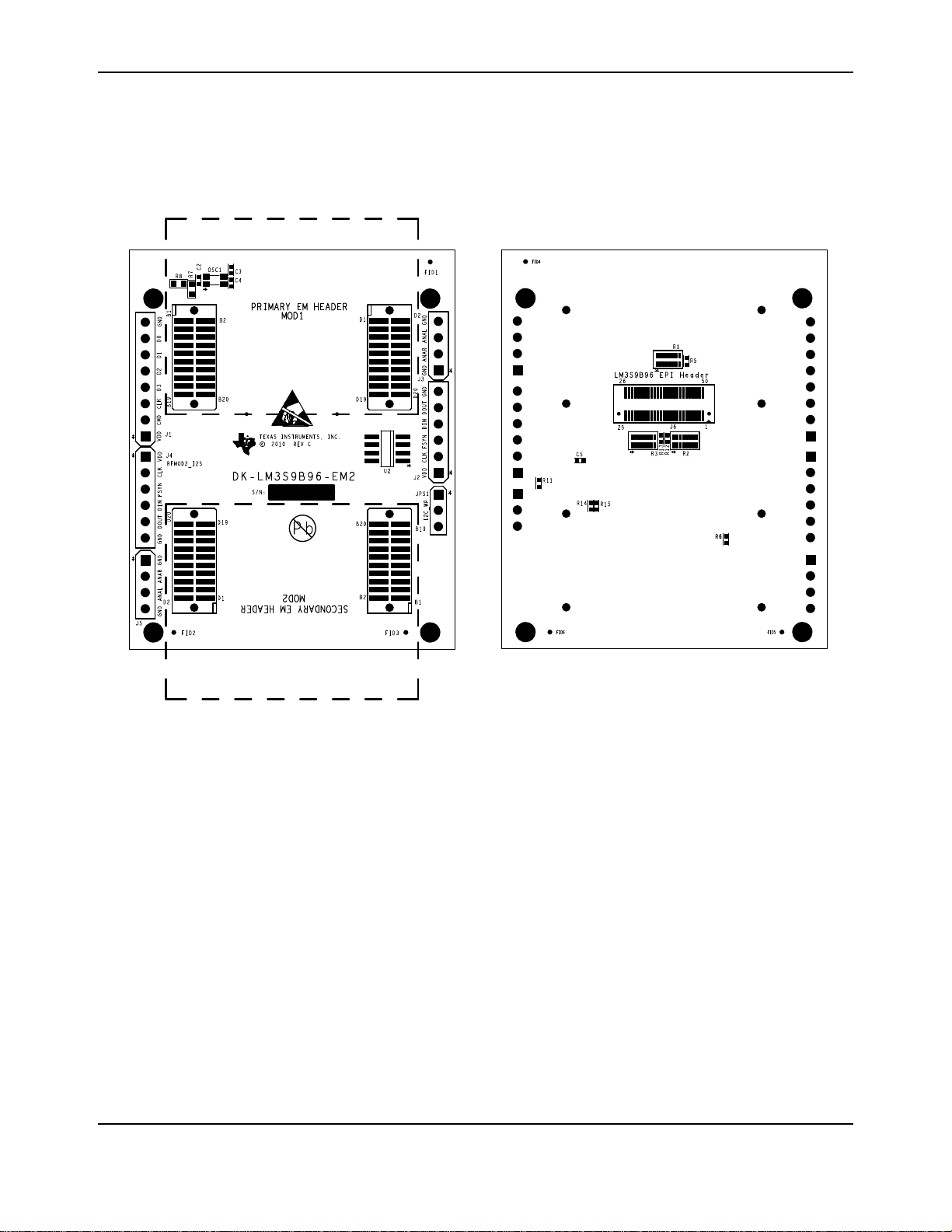

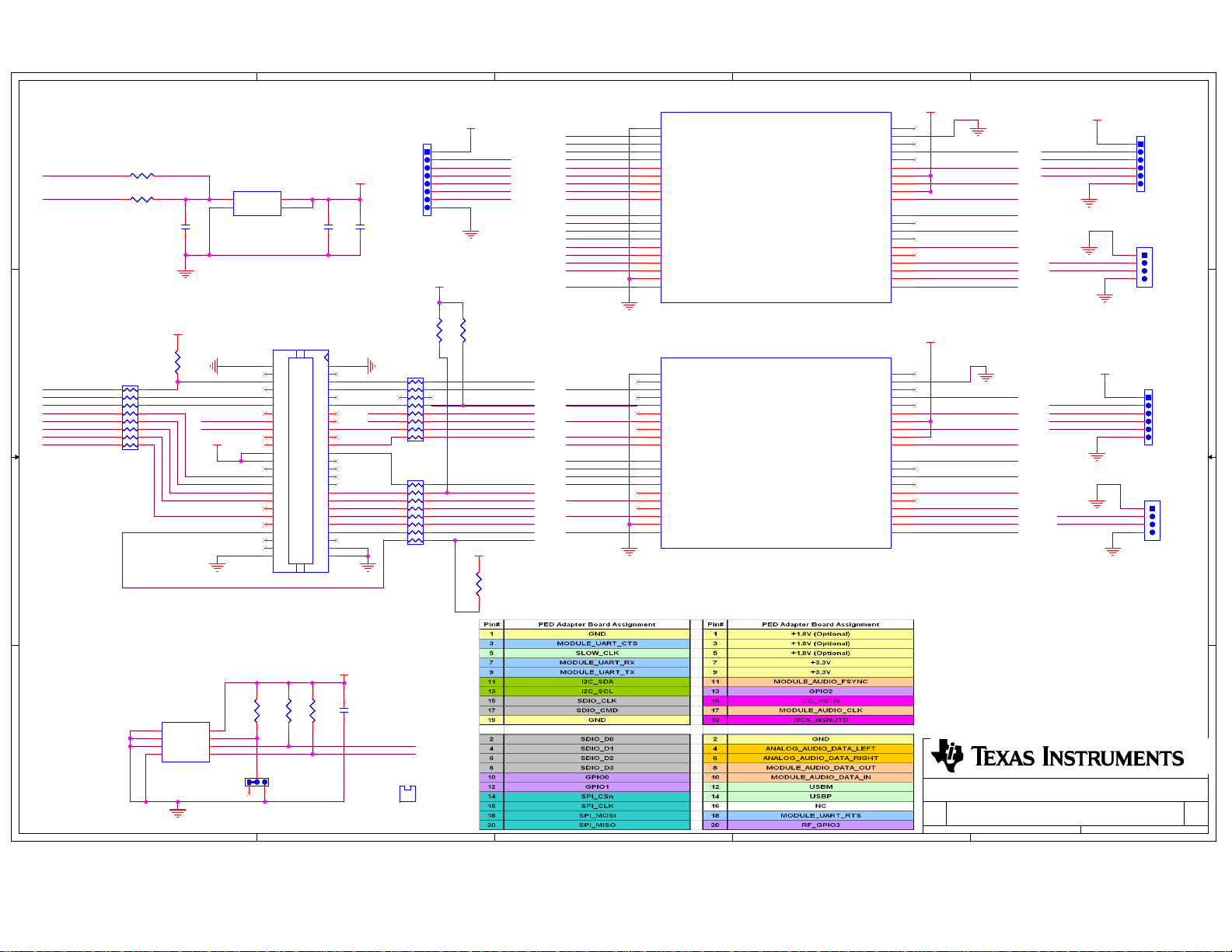

Appendix G: Stellaris® LM3S9B96 EM2 Expansion Board.........................................................................69

Features............................................................................................................................................................69

Installation......................................................................................................................................................... 69

Installation of EM Modules onto the EM2 Expansion Board.............................................................................72

Hardware Description ....................................................................................................................................... 74

Primary EM Header ......................................................................................................................................74

Secondary EM Header..................................................................................................................................75

CAT24C01 EEPROM....................................................................................................................................75

2

I

S Header....................................................... ... ... ... ................................................. ... ................................75

Analog Audio Header... ... .... ... ... .................................................... ... ... .... ... ... ................................................ 75

SDIO Header ................................................................................................................................................75

EPI Signal Descriptions .......................................... ... ... .... ... .............................................................................75

Component Locations.......................................................................................................................................77

Schematics.......................................................................................................................................................77

Appendix H: References ................................................................................................................................79

4 September 5, 2010

Page 5

Stellaris® LM3S9B96 Development Kit User’s Manual

List of Figures

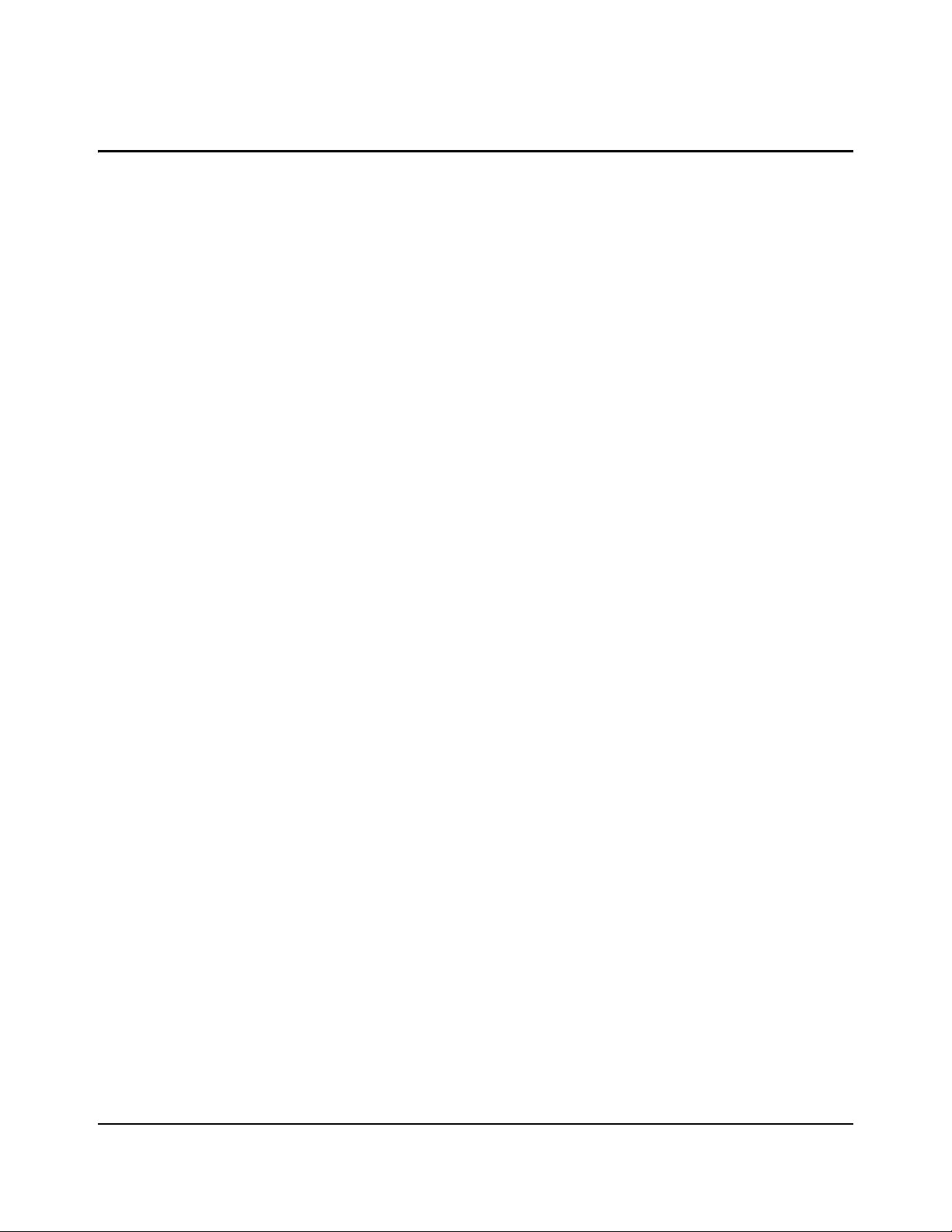

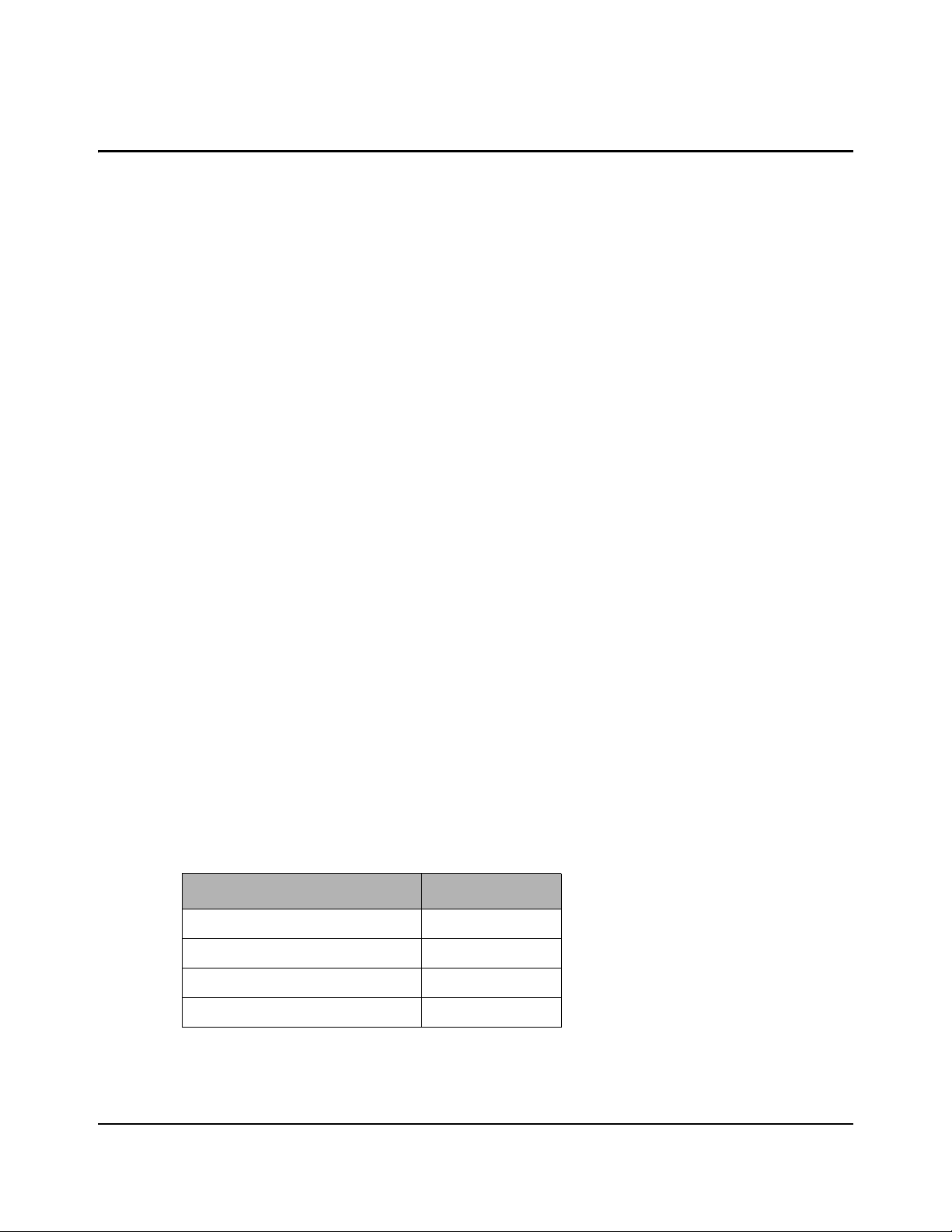

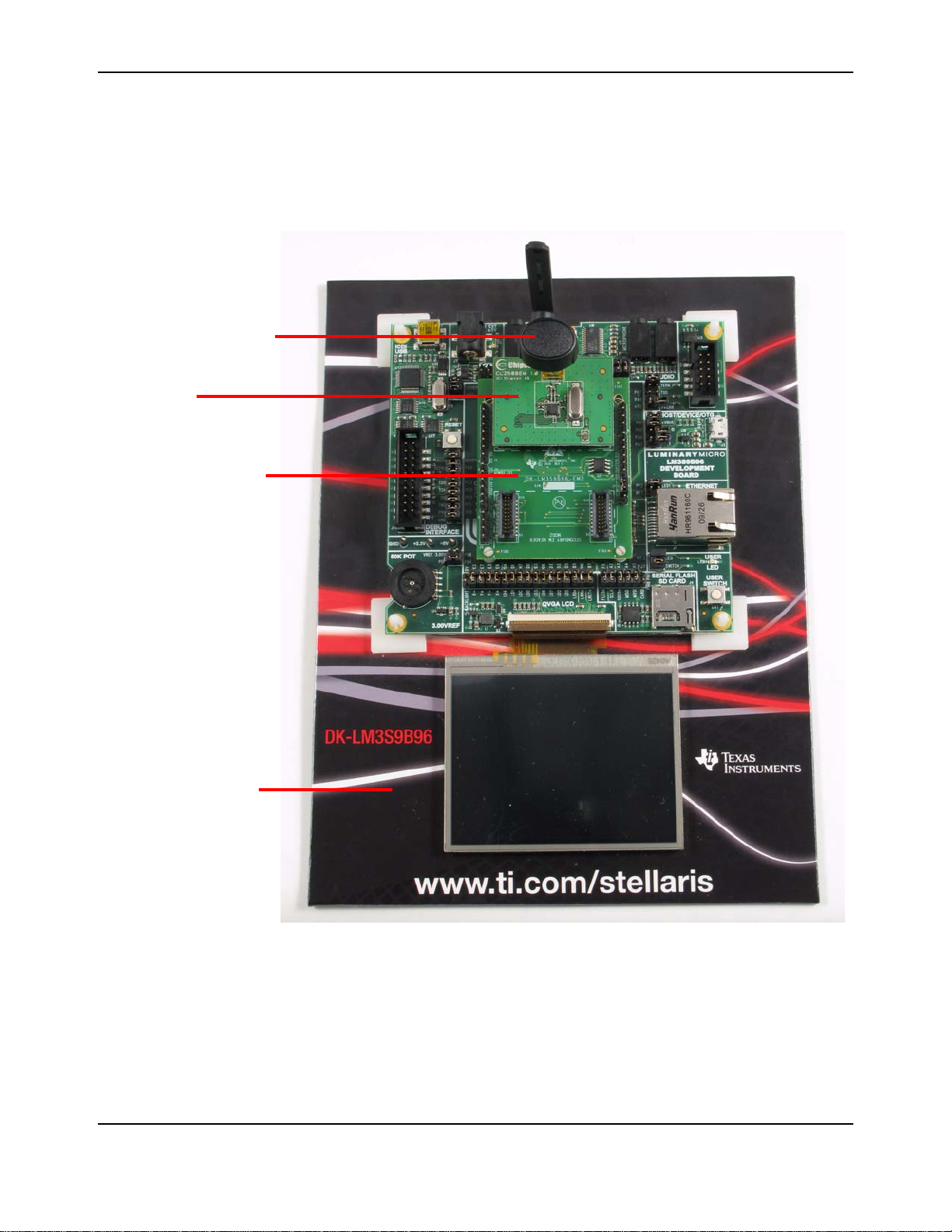

Figure 1-1. DK-LM3S9B96 Development Board.............................................................. ... .... ... ... ... ..................9

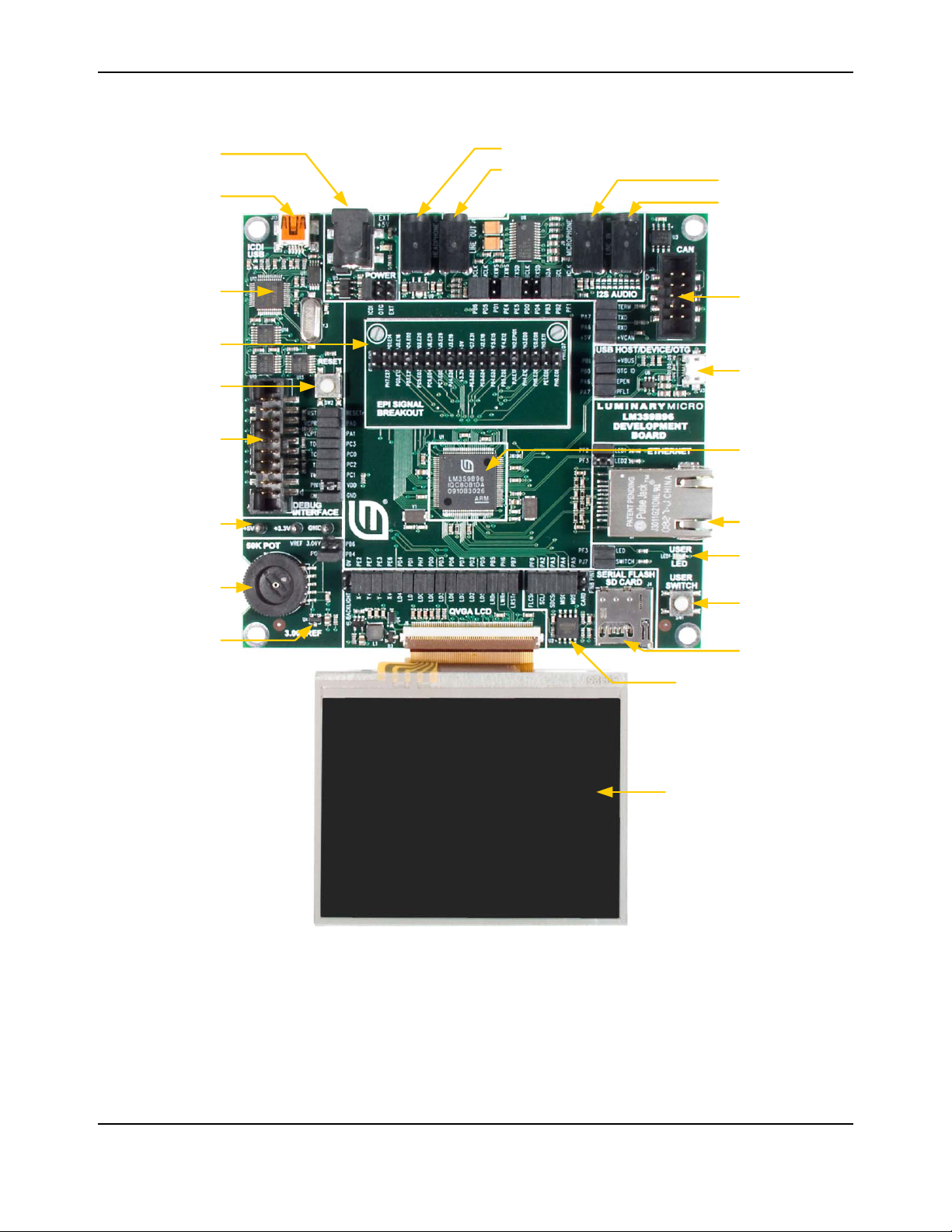

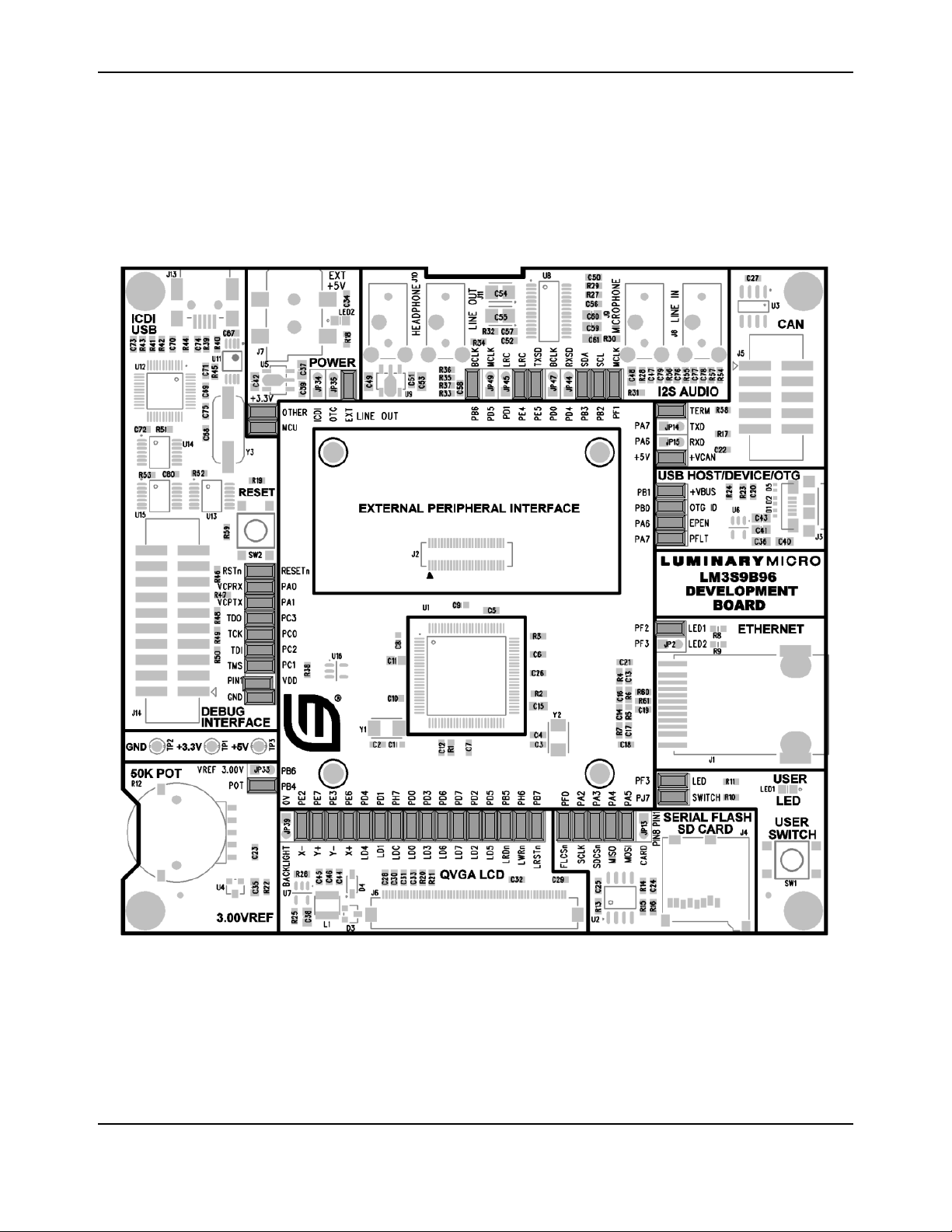

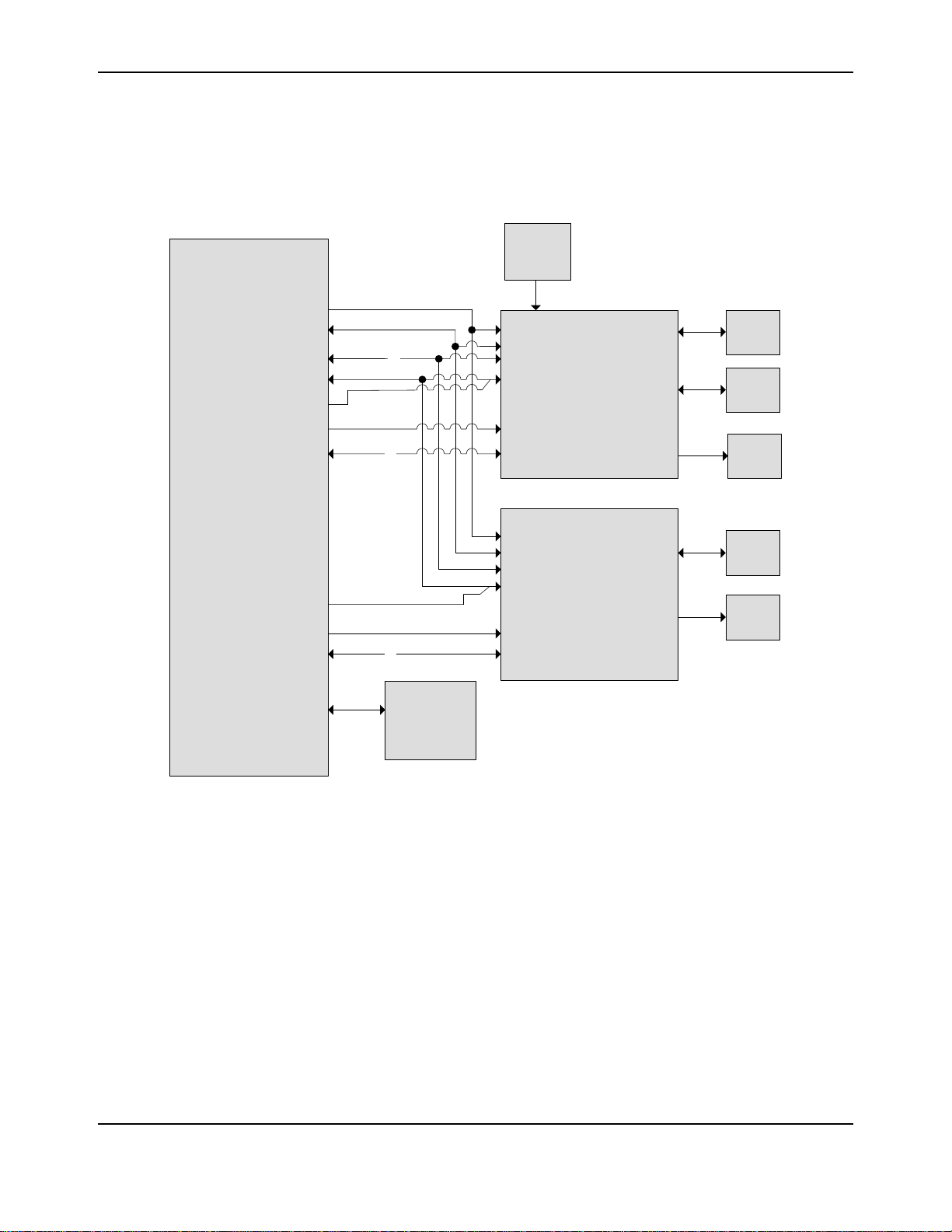

Figure 1-2. DK-LM3S9B96 Development Board Block Diagram .....................................................................11

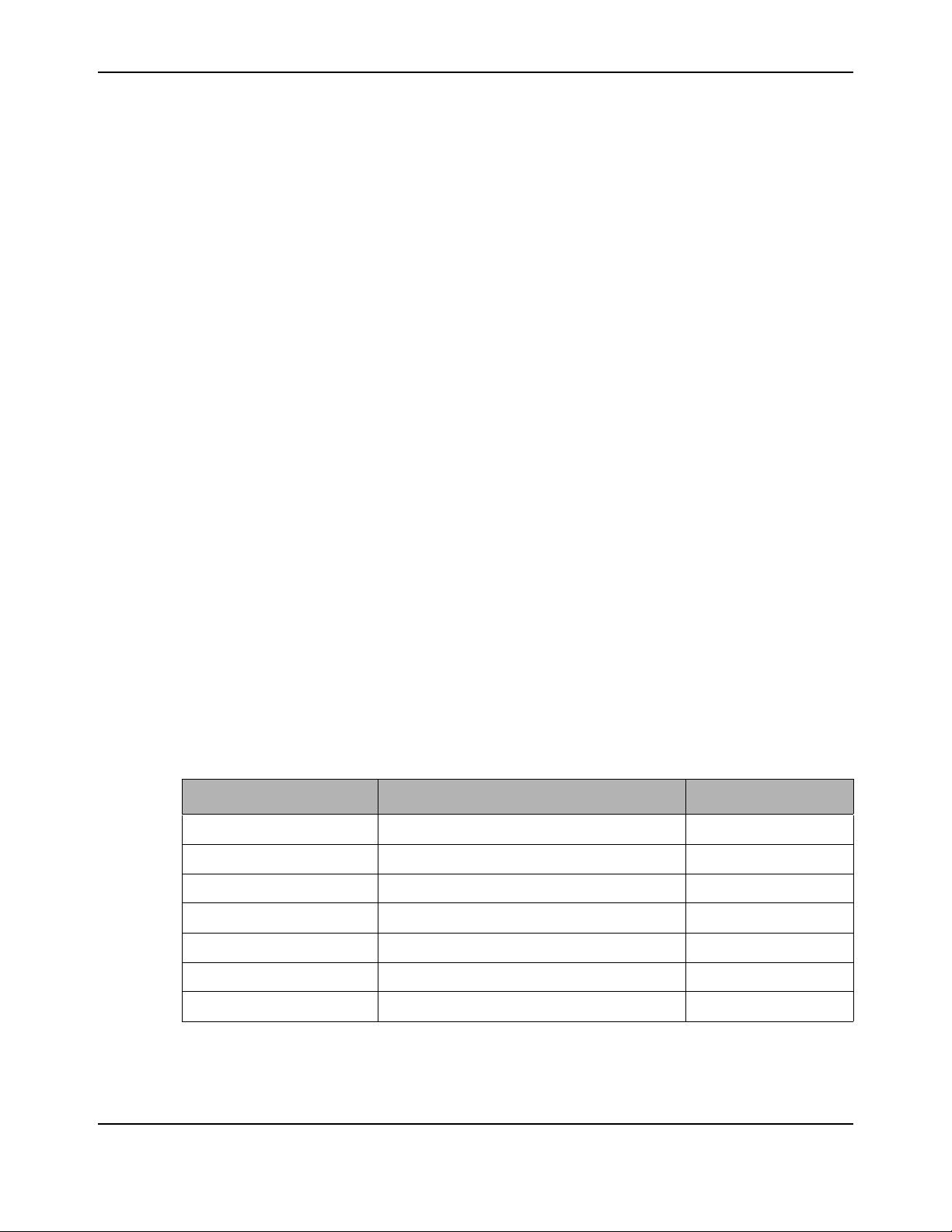

Figure 2-1. Factory Default Jumper Settings... ... ... ..........................................................................................14

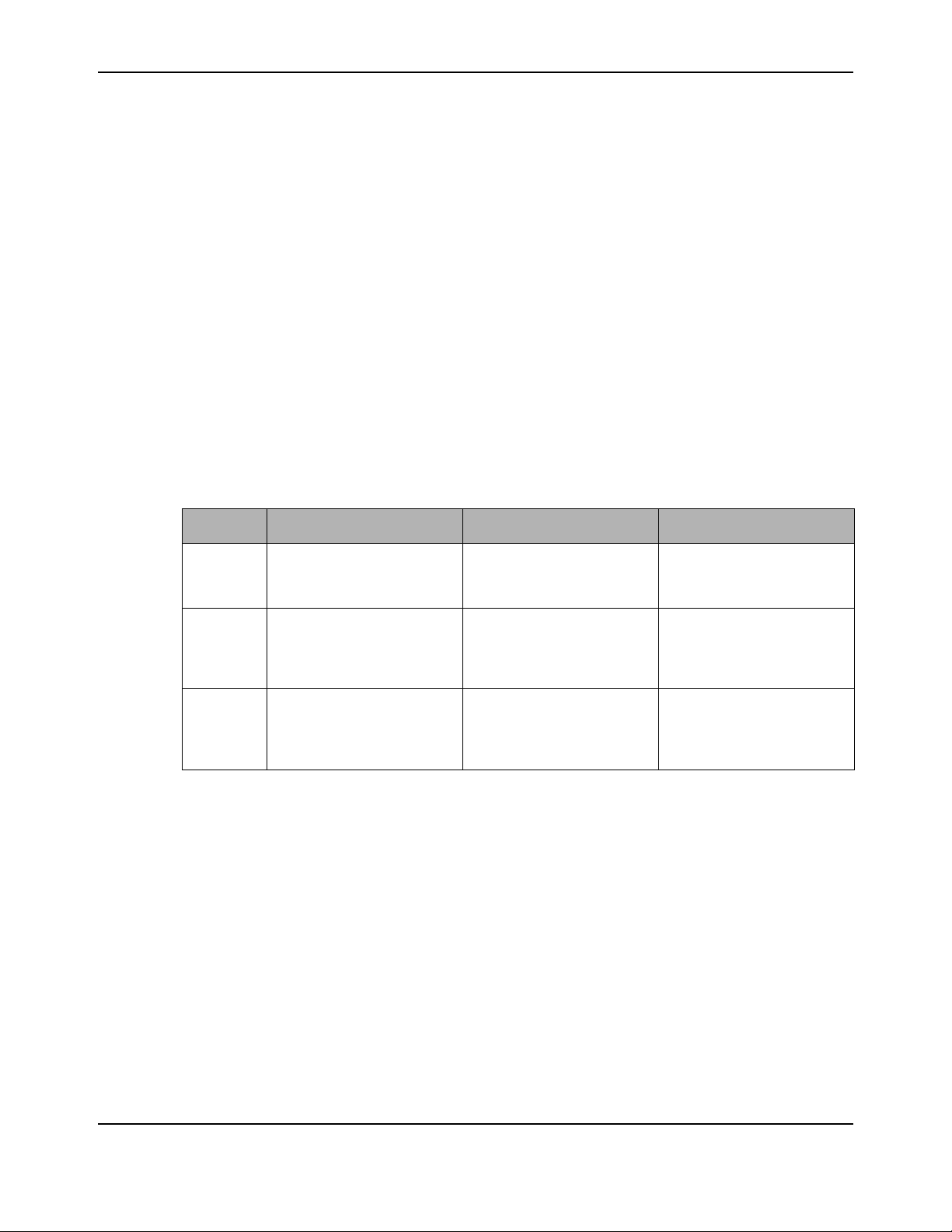

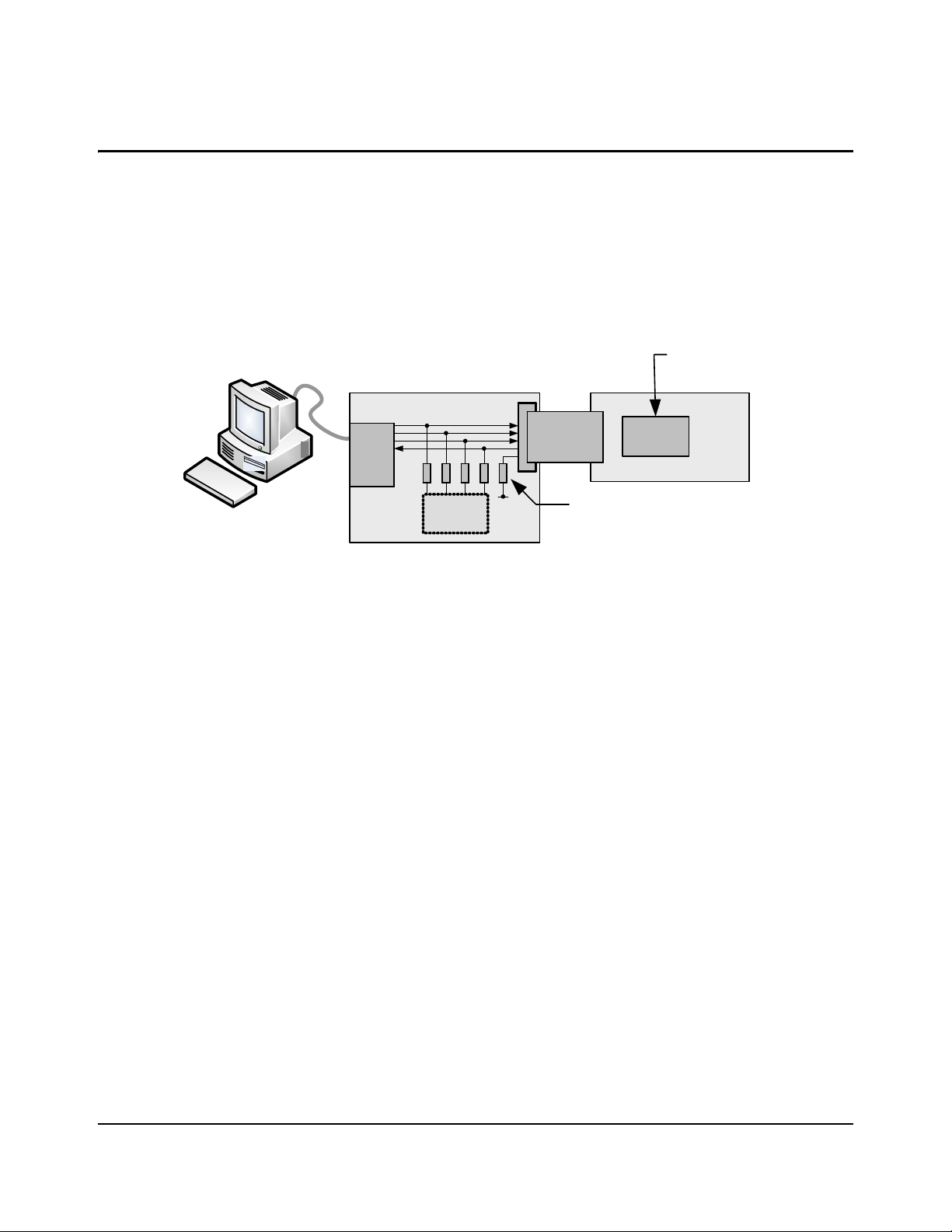

Figure 4-1. ICD Interface Out Mode ................................................................................................................23

Figure B-1. Component Placement Plot for Top........................................ ... ................................................... 34

Figure E-1. Flash and SRAM Memory Expansion Board.................................................................................41

Figure E-2. Removing EPI Board from DK-LM3S9B96 Development Board...................................................42

Figure E-3. Flash/SRAM/LCD IF Expansion Board Block Diagram.................................................................43

Figure E-4. Component Placement Plot for Top and Bottom...........................................................................46

Figure F-1. FPGA Expansion Board ...................... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ................49

Figure F-2. Removing EPI Board from DK-LM3S9B96 Development Board................................................... 51

Figure F-3. FPGA Expansion Board Block Diagram........ ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... 52

Figure F-4. FPGA Boundary Scan................................................ ... ... ... .... ... ... ... ... .... ... ... ................................61

Figure F-5. Component Placement Plot for Top..............................................................................................64

Figure F-6. Component Placement Plot for Bottom.........................................................................................65

Figure G -1. EM2 Expansion Board...................... ... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ... ..........................................69

Figure G-2. Removing EPI Board from DK-LM3S9B96 Development Board...................................................70

Figure G -3. EM2 Expansion Board...................... ... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ... ..........................................71

Figure G-4. Assembled DK-LM3S9B96 Development Board with EM2 Expansion Board...............................71

Figure G-5. Connecting an EM Module to the EM2 Expansion Board ............................................................. 72

Figure G-6. Fully Assembled DK-LM3S9B96 Board with EM2 Expansion Board an d Wireless EM Module ...73

Figure G -7. EM2 Expansion Board Block Diagram................................................ .... ... ... ... .... ... ... ... ... .... .........74

Figure G-8. Component Placement Plot for Top and Bottom...........................................................................77

September 5, 2010 5

Page 6

List of Tables

Table 2-1. Board Features and Peripherals that are Disconnected in Factory Default Configuration............13

Table 2-2. USB-Related Signals.....................................................................................................................15

Table 2-3. Hardware Debugging Configurations ............................................................................................ 16

Table 2-4. Debug-Related Signals .................................................................................................................17

Table 2-5. LCD-Related Signals..................................................................................................................... 18

Table 2-6. I

Table 2-7. Navigation Switch-Related Signals ...............................................................................................19

Table C-1. Debug Interface Pin Assignments.................................................................................................35

Table D-1. Microcontroller GPIO Assignments ...............................................................................................37

Table E-1. Flash and SRAM Memory Expansion Board Memory Map..................................... ... ... ... .... ... ... ... 45

Table E-2. LCD Latch Register....................................................................................................................... 45

Table F-1. FPGA Expansion Board Memory Map..........................................................................................54

Table F-2. Version Register............................................................................................................................ 55

Table F -3. System Control Register ........................... .... ... ... .................................................... ... ...................56

Table F-4. Interrupt Enable Register ..............................................................................................................57

Table F-5. Interrupt Status Register ...............................................................................................................57

Table F-6. Test Pad Register..........................................................................................................................58

Table F-7. LCD Control Register .................................................................................................................... 59

Table F -8. EPI Signal Descriptions ................... ............................................................................................. 63

Table G-1. EPI Signal Descriptions.................... ... ... ... .... ... ... ... .................................................... ...................75

2

S Audio-Related Signals................................... ... .... ... ... ... .................................................... ...... 19

6 September 5, 2010

Page 7

CHAPTER 1

Stellaris® LM3S9B96 Development Board Overview

The Stellari s® LM3S9B96 Develop ment Board prov ides a plat form for developing systems around

the advanced capabilities of the LM3S9B96 ARM® Cortex™-M3-based microcontroller.

The LM3S9B96 is a member of the Stellaris Tempest-class microcontroller family. Tempest-class

devices include capabilities such as 80 MHz clock speeds, an External Peripheral Interface (EPI)

and Audio I

DK-LM3S9B96 board includes a rich set of peripherals found on other Stellaris boards.

The development board includes an on-board in-circuit debug interface (ICDI) that supports both

JT AG and SWD debugging. A stand ard ARM 20-pin debug header suppor ts an array of debugging

solutions.

The Stellaris® LM3S9B96 Development Kit accelerates development of Tempest-class

microcontrollers. The kit also includes extensive example applications and complete source code.

Features

The Stellaris® LM3S9B96 Development Board includes the following features.

Simple set-up—USB cable provides debugging, communication, and power

Flexible development platform with a wide range of peripherals

2

S interfaces. In addition to new hardware to support these features, the

Color LCD graphics display

– TFT LCD module with 320 x 240 resolution

– Resistive touch interface

80 MHz LM3S9B96 microcontroller with 256 K Flash, 96 K SRAM, and integrated Ethernet

MAC+PHY, USB OTG, and CAN communications

– – 8 MB SDRAM (plug-in EPI option board)

– – EPI break-out board (plug-in option board)

1 MB serial Flash memory

Precision 3.00 V voltage reference

SAFERTOS™ operating system in microcontroller ROM

2

I

S stereo audio codec

– Line In/Out

– Headphone Out

– Microphone In

Controller Area Network (CAN) Interface

10/100 BaseT Ethernet

USB On-The-Go (OTG) Connector

– Device, Host, and OTG modes

September 5, 2010 7

Page 8

User LED and push button

Thumbwheel potentiometer (can be used for menu navigation)

MicroSD card slot

Supports a range of debugging options

– Integrated In-circuit Debug Interface (ICDI)

– JTAG, SWD, and SWO all supported

– Standard ARM® 20-pin JT AG debug connector

USB Virtual COM Port

Jumper shunts to conveniently reallocate I/O resources

Develop using tools supporting Keil™ RealView® Microcontroller Development Kit

(MDK-ARM), IAR Embedded Workbench, Code Sourcery GCC development to ols, Code Red

Technologies development tools, or Texas Instruments’ Code Composer Studio™ IDE

Supported by StellarisWare® software including the graphics library, the USB library, and the

peripheral driver library

Optional expansion boards that work with the External Peripheral Interface (EPI) of the

DK-LM3S9B96 development board extend the capabilities of this development platform (each

board sold separately)

– Stellaris® Flash and SRAM Memory Expansion Board (DK-LM3S9B96-FS8) (sold

separately)

• Provides Flash memory, SRAM, and an improved performance LCD interface

For more information on the DK-LM3S9B96-FS8 memory expansion board, see

Appendix E, “Stellaris® LM3S9B96 Flash and SRAM Memory Expansion Board,” on

page 41.

– Stellaris® FPGA Expansion Board (DK-LM3S9B96-FPGA) (sold separately)

• Provides machine-to-machine (M2M), high-bandwidth, parallel interface capability of

the Stellaris microcontroller

• Allows users to control and display the FPGA expansion board’s video on the

DK-LM3S9B96 development board’s large, 3.5” touchscreen display

For more information on the DK-LM3S9B96-FPGA expansion board, see

Appendix F, “Stellaris® LM3S9B96 FPGA Expansion Board,” on page 49.

– Stellaris® EM2 Expansion Board (DK-LM3S9B96-EM2) (sold separately)

• Provides a transition between the Stellaris External Peripheral Interface (EPI)

connector and the RF Evaluation Module (EM) connecto r

• Enables wireless application development using Low Power RF an d RF ID

evaluation modules on the Stellaris DK-LM3S9B96 platform

For more information on the DK-LM3S9B96-EM2 e xpansion board, see Appendix G,

“Stellaris® LM3S9B96 EM2 Expansion Board,” on page 69.

8 September 5, 2010

Page 9

Figure 1-1. DK-LM3S9B96 Development Board

Debug I nterface

USB Connector for

Debug and/or Power

Stellaris

LM3S39B96

Microcontroller

CAN Bus Interface

3 .5 " LCD T ouc h Panel

USB connector wi th

Host, De vice an d

On-the-Go modes

10/ 100 Et hernet

User LED

microSD Card Slot

Potentiometer

5 VDC supply input

JTAG/SWD In/

Out C onnector

User Switch

Reset switch

Power and

Ground Test

Points

3 .00V Analog

Reference

Headphone Out put

Audi o Li ne Output

Microphone Input

Audi o Li ne I n put

1MB Serial Fl ash Mem ory

Stellaris® LM3S9B96 Development Kit User’s Manual

September 5, 2010 9

Page 10

Development Kit Contents

The Stellaris® LM3S9B96 Development Kit contains everything needed to develop and run a

range of applications using Stellaris microcontrollers:

LM3S9B96 development board

8 MB SDRAM expansion board

EPI signal breakout board

Retractable Ethernet cable

USB Mini-B cable for debugger use

USB Micro-B cable for OTG-to-PC connection

USB Micro-A to USB A adapter for USB Host

USB Flash memory stick

microSD Card

20-position ribbon cable

CD containing:

– A supported version of one of the following (including a toolchain-specific Quickstart

guide):

• Keil™ RealView® Microcontroller Development Kit (MDK-ARM)

• IAR Embedded Workbench

• Code Sourcery GCC development tools

• Code Red Te chnologies development tools

• Texas Instruments’ Code Composer Studio™ IDE

– Complete documentation

– Quickstart application source code

– Stellaris® Firmware Development Package with example source code

10 September 5, 2010

Page 11

Stellaris® LM3S9B96 Development Kit User’s Manual

USB

USB

USB

T

Stellaris

Tempest-cl ass

LM 3S9B96

Microcontroller

QVGA

Color LCD Module

I/O Signal Break-out

Switch

LED

Tempest LM 3S9B96 D evelo pment Bo ard

I/O Signal B reak-out

I/O signals

Dual

USB

Device

Controller

Debug

JTAG/SWD

Output/Input

Debug USB

Reset

+3.3V

Regulator

SWD/JTAG Mux

UART0

Debug

USB

Control+5V host supply

USB

micro-AB

connector

OTG/Host/Device

T

a

r

g

e

t

C

a

b

l

e

MicroSD

card slot

1GB

1MB

Serial

Flash

EPI

Touch

RJ45

Jack+

Magnetics

Ethernet

Pot

Thumb

wheel

Pot

8MB SDRAM

Headphone

Jack

Line Out

Jack

I2S

Audio

CODEC

Line Output

Phones

Block Diagram

Figure 1-2. DK-LM3S9B96 Development Board Block Diagram

Development Board Specifications

Board supply voltage: 4.75–5.25 Vdc from one of the following sources:

– Debugger (ICDI) USB cable (connected to a PC)

– USB Micro-B cable (connected to a PC)

– DC power jack (2.1x 5.5mm from exte rn al po we r su pp ly)

Break-out power output: 3.3 Vdc (100 mA max)

September 5, 2010 11

Page 12

Dimensions (excluding LCD panel):

– 4.50” x 4.25” x 0.60” (LxWxH) with SDRAM board

– 4.50” x 4.25” x 0.75” (LxWxH) with EPI breakout board

Analo g Re fe re nc e: 3. 0 V +/-0.2 %

RoHS status: Compliant

NOTE: When the LM3S9B96 Development Board is used in USB Host mode, the host connector

is capable of supplying power to the connected USB device. The available supply current

is limited to ~200 mA unless the development board is powered from an external 5 V

supply with a =600mA rating.

12 September 5, 2010

Page 13

CHAPTER 2

Stellaris® LM3S9B96 Development Board Hardware Description

In addition to an LM3S9B96 microcontroller, the development board includes a range of useful

peripheral features and an integrated in-circuit debug interface (ICDI). This chapter describe s how

these peripherals operate and interface to the microcontroller

LM3S9B96 Microcontroller Overview

The Stellaris LM3S9B96 is an ARM Cortex-M3-based microcontroller with 256-KB flash memory,

80-MHz operation, Ethernet, USB, EPI, SAFERTOS™ in ROM, and a wide range of peripherals.

See the LM3S9B96 Microcontroller Data Sheet (order number DS-LM3S9B96) for complete

microcontroller details.

The LM3S9B96 microcontroller is factory-programmed with a quickstart demo program. The

quickstart program resides in on-chip flash memory and runs each time power is applied, unless

the quickstart has been replaced with a user program.

Jumpers and GPIO Assignments

Each peripheral circuit on the development board is interfaced to the LM3S9B96 microcontroller

through a 0.1” pitch jumper/shunt. Figure 2-1 on page 14 shows the fact ory default positions of the

jumpers. The jumpers must be in these positions for the quickstart demo program to function

correctly.

The development board offers capabilities that the LM3S9B96 cannot support simultaneously due

to pin count and GPIO multiplexing limitations. For example, as configured, the board does not

support SDRAM and I

jumpers associated with I

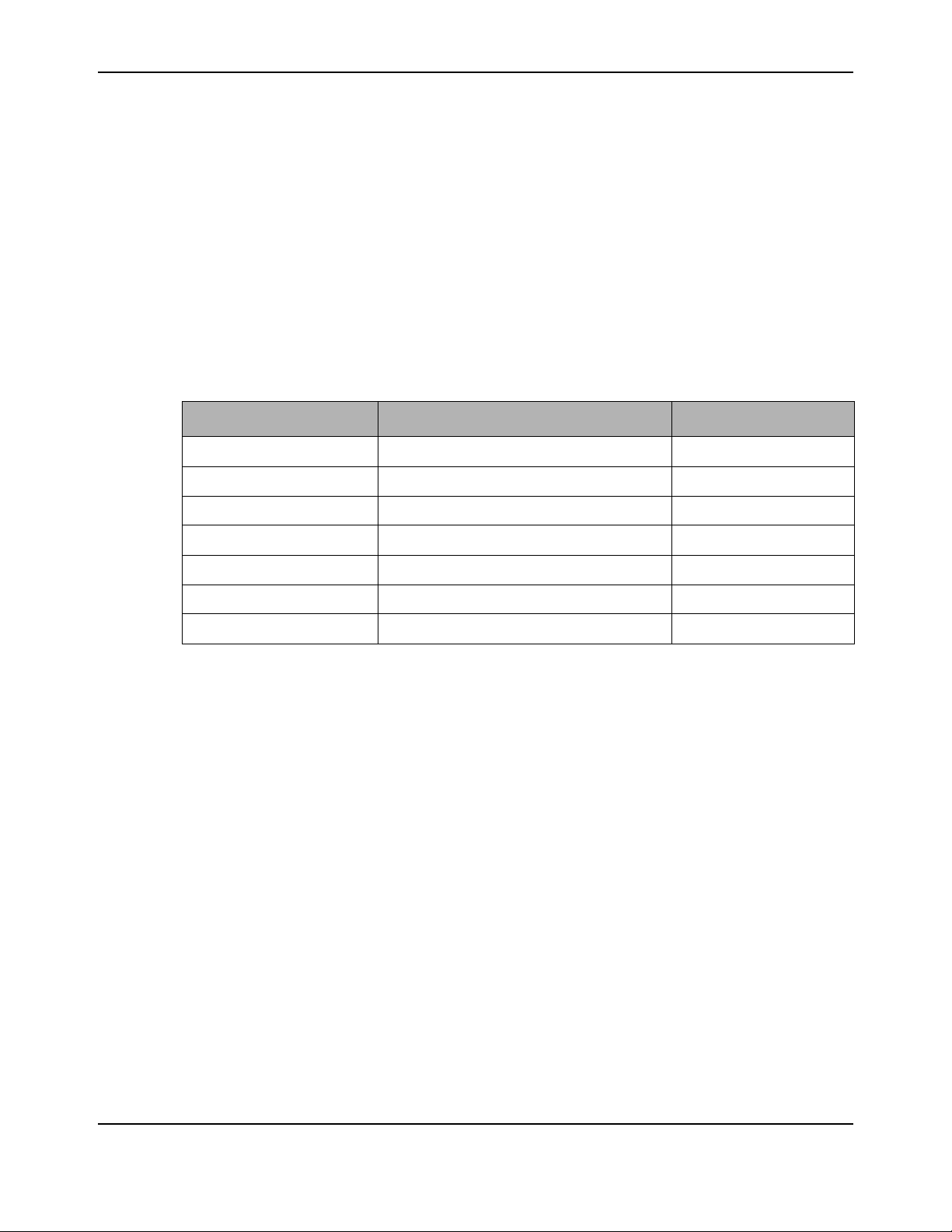

Table 2-1 lists all features and peripherals that are disconnected in the factor y de fa ult

configuration. Using these peripherals requires that other peripherals be disconnected.

Appendix D, “Stellaris® LM3S9B96 Development Board Microcontroller GPIO Assignments,” on

page 37 lists alternative jumper configurations used in conjunction with some of the

StellarisWare™ example applications for this board.

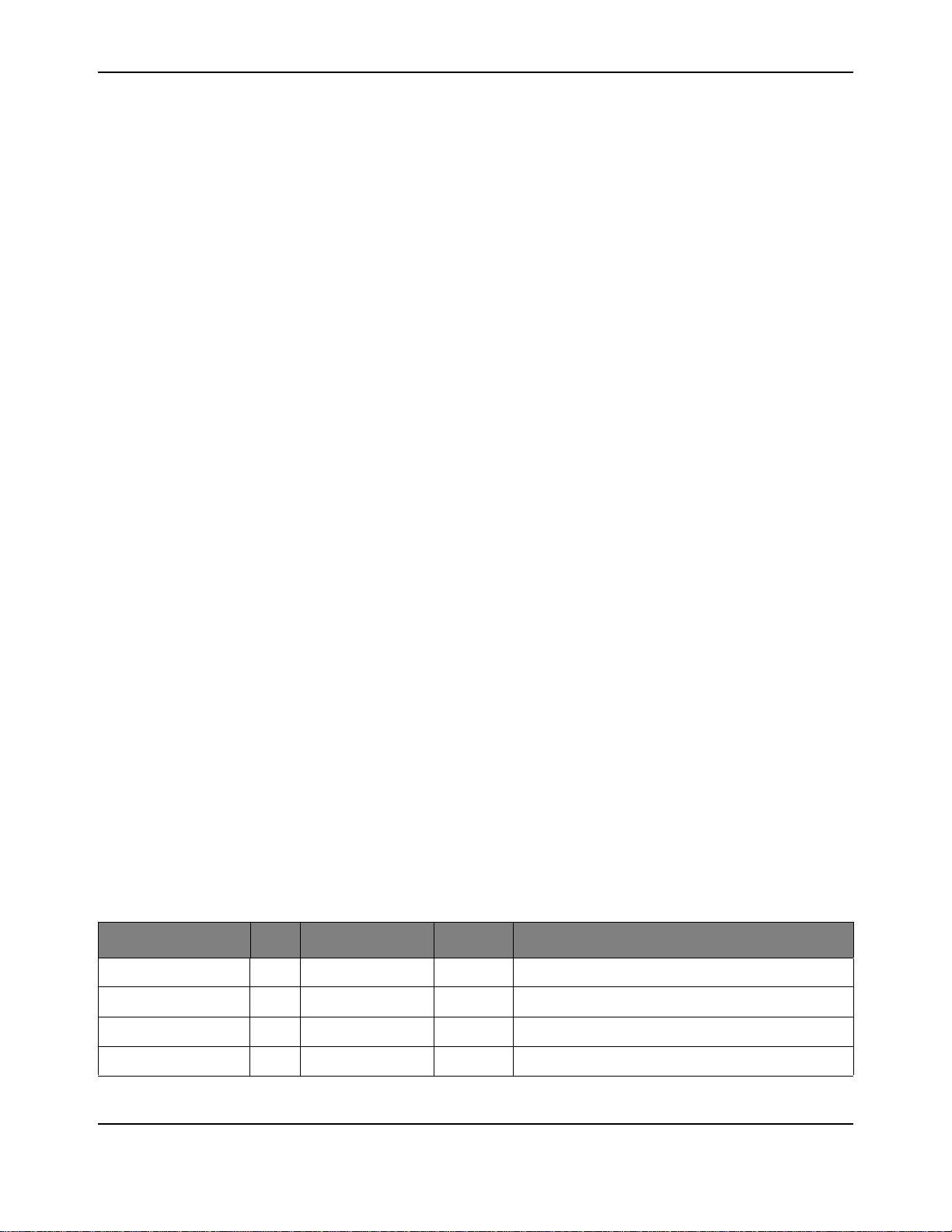

Table 2-1. Board Features and Peripherals that are Disconnected in Factory Default

Configuration

Peripheral Jumpers

2

I

S Receive (Audio Input) JP44, 45, 47, 49

Controller Area Network (CAN) JP14, 15

Ethernet Yellow Status LED (LED2) JP2

Analog 3.0V Reference JP33

See Appendix D, “Stellaris® LM3S9B96 Development Board Microcontroller GPIO Assignments,”

on page 37, for a complete list of GPIO assignments. The table lists all default and alternate

2

S receive (microphone or line input) functions at the sa me ti me . The

2

S receive are omitted in the default configuration.

September 5, 2010 13

Page 14

assignments that are supported by the 0.1” jumpers and PCB routing. The LM3S9B96 has

additional internal multiplexing that enables additional configurations which may require discrete

wiring between peripherals and GPIO pins.

The ICDI section of the board has a GND-GND jumper that serves no function other than to

provide a convenient place to ‘park’ a spare jumper. This jumper may be reused as required.

Figure 2-1. Factory Default Jumper Settings

Clocking

The development board uses a 16.0-MHz (Y2) crystal to complete the LM3S9B96

microcontroller's main internal clock circuit. An internal PLL, configured in software, multiples this

clock to higher frequencies for core and peripheral timing.

A 25.0-MHz (Y1) crystal provides an accurate timebase for the Ethernet PHY.

14 September 5, 2010

Page 15

Reset

The RESETn signal into the LM3S9B96 microcontroller connects to the reset switch (SW2) and to

the ICDI circuit for a debugger-controlled reset.

External reset is asserted (active low) under any one of the three following conditions:

Power-on reset (filtered by an R-C network)

Reset push switch SW2 held down

By the ICDI circuit (U12 FT2232, U13D 74LVC125A) when instructed by the debugger (this

capability is optional, and may not be supported by all debuggers)

The LCD module has special Reset timing requirement s requiring a ded icated control line from the

microcontroller.

Power Supplies

The development board requires a regulated 5.0 V power source. Jumpers JP34-36 select the

power source, with the default source being the ICDI USB connector . Only one +5 V source should

be selected at any time to avoid conflict between the power sources.

When using USB in Host mode, the power source should be set to either ICDI or to EXT if a +5 V

power supply (not included in the kit) is available.

Stellaris® LM3S9B96 Development Kit User’s Manual

USB

The development board has two main power rails. A +3.3 V supply powers the microcontroller and

most other circuitry. +5 V is used by the OTG USB port and In-circuit Debug Interface (ICDI) USB

controller. A low drop-out (LDO) regulator (U5) converts the +5 V power rail to +3.3 V. Both rails

are routed to test loops for easy access.

The LM3S9B96’s full-speed USB controller supports On-the-Go, Host, and Device configurations.

See Table 2-2 for USB-related signals. The 5-pin microAB OTG connector supports all three

interfaces in conjunction with the cables included in the kit.

The USB port has additional ESD protection diode arrays (D1, D2,D5) for up to 15 kV of ESD

protection.

Table 2-2. USB-Related Signals

Microcontroller Pin Board Function Jumper Name

Pin 70 USB0DM USB Data- Pin 71 USB0DP USB Data+ Pin 73 USB0RBIAS USB bias resistor Pin 66 USB0ID OTG ID signal (input to microcontroller) OTG ID

Pin 67 USB0VBUS Vbus Level monitoring +VBUS

Pin 34 USB0EPE Host power enable (active high) EPEN

Pin 35 USB0PFLT Host power fault signal (active low) PFLT

U6, a fault-protected switch, controls and monitors power to the USB host port. USB0EPEN, the

control signal from the microcontroller , has a pull-down resistor to en sure host-p ort power rema ins

off during reset. The power switch will immediately cut power if the attached USB device draws

September 5, 2010 15

Page 16

more than 1 Amp, or if the switches’ thermal limits are exceeded by a device drawing more than

500 mA. USB0PFLT indicates the over-current status back to the microcontroller.

The development board can be either a bus-po wered USB device or self-powered USB device

depending on the power-supply configuration jumpers.

When using the development board in USB-host mode, power to the EVB should be supplied by

the In-circuit Debugger (ICDI) USB cable or by a +5 V source connected to the DC power jack.

Note that the LM3S9B96’s USB capabilities are completely independent from the In-Circuit Debug

Interface USB functionality.

Debugging

Stellaris microcontrollers support programming and debugging using either JTAG or SWD. JTAG

uses the TCK, TMS, TDI, and TDO signals. SWD requires fewer signals (SWCLK, SWDIO, and,

optionally, SWO for trace). The debugger determines which debug protocol is used.

Debugging Modes

The LM3S9B96 development board supports a range of hardware debugging configurations.

Table 2-3 summarizes these configurations.

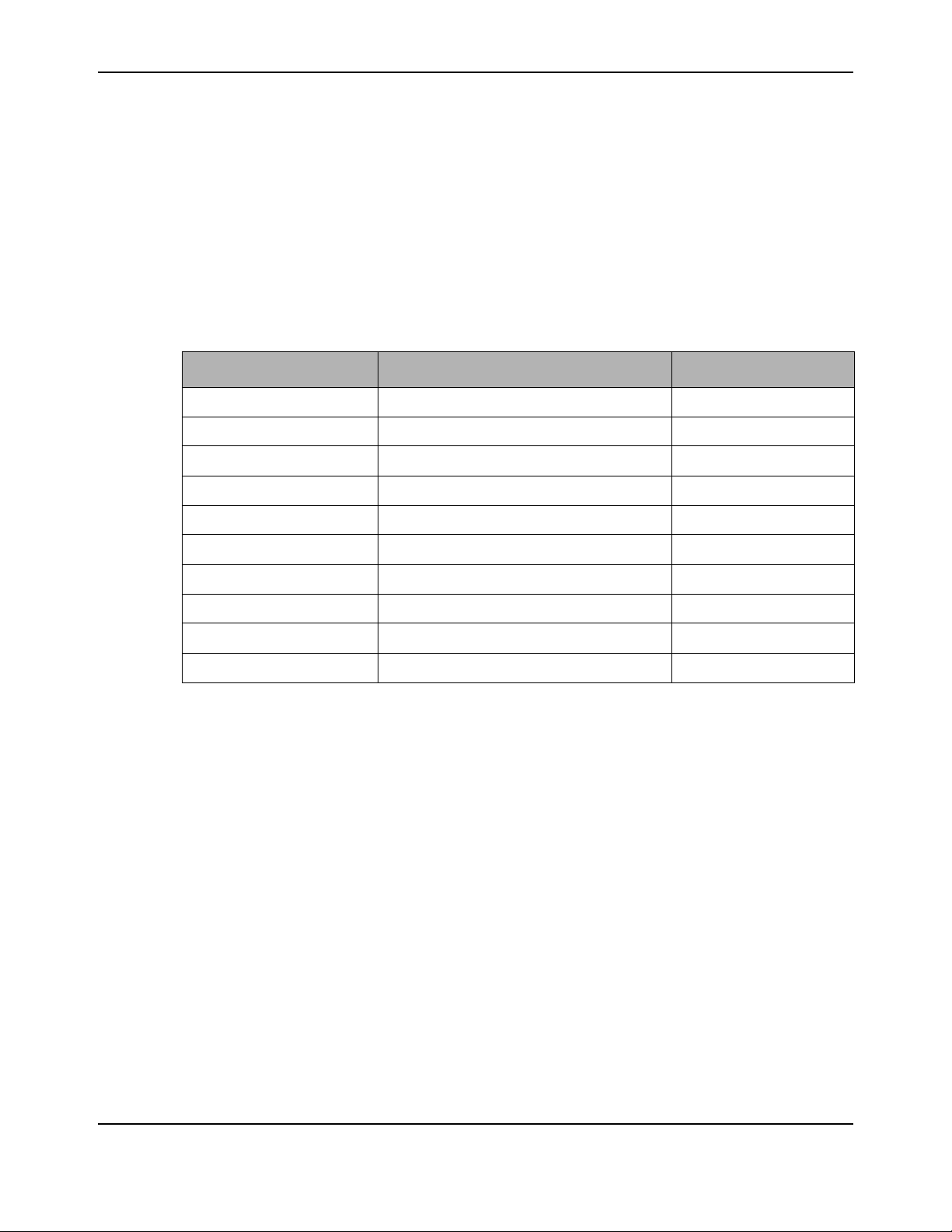

Table 2-3. Hardware Debugging Configurations

Mode Debug Function Use Selected by...

1 Internal ICDI Debug on-board LM3S9B96

2 ICDI out to JTAG/ SWD

header

3 In from JT AG/SWD header For users who prefer an

Debug In Considerations

Debug Mode 3 supports board debugging using an external debug interface such as a Segger

J-Link or Keil ULINK. Most debuggers use Pin 1 of the Debug connec to r to se nse the target

voltage and, in some cases, power the output logic circuit. Installing the VDD/PIN1 jumper will

apply 3.3 V power to this pin in order to support external debuggers.

Debug USB Overview

An FT2232 device from Future Technology Devices International Ltd implements USB-to-serial

conversion. The FT2232 is factory-configured to implement a JTAG/SWD port (synchronous

serial) on channel A and a Virtual COM Port (VCP) on channel B. This feature allows two

simultaneous communications links between the host computer an d the target device using a

single USB cable. Separate Windows drivers for each func tion are provided on the Docume ntation

and Software CD.

microcontroller over Debug

USB interface.

The development board is

used as a USB to SWD/

JTAG interface to an

external target.

external debug interface

(ULINK, JLINK, etc.) with the

development board.

Default mode

Remove jumpers on TCk,

TMS, TDI, TDO, and PIN1

Connecting an external

debugger to the JTAG/SWD

header

The In-Circuit Debug Interface USB capabilities are completely independent from the LM3S9B96’s

on-chip USB functionality.

16 September 5, 2010

Page 17

A small serial EEPROM holds the FT2232 configuration data. The EEPROM is not accessible by

the LM3S9B96 microcontroller. For full details on FT2232 operation, go to www.ftdichip.com.

USB to JTAG/SWD

The FT2232 USB device performs JT AG/SWD serial operations under th e control of the debugger.

A simple logic circuit multiplexes SWD and JTAG functions and, when working in SWD mode,

provides direction control for the bidirectional data line.

Virtual COM Port

The Virtual COM Port (VCP) allows Windows applications (such as HyperTe rm in al) to

communicate with UART0 on the LM3S9B96 over USB. Once the FT2232 VCP driver is in stalled,

Windows assigns a COM port number to the VCP channel. Table 2-4 shows the debug-related

signals.

Table 2-4. Debug-Related Signals

Microcontroller Pin Board Function Jumper Name

Pin 77 TDO/SWO JT AG data out or trace data out TDO

Pin 78 TDI JTAG data in TDI

Pin 79 TMS/SWDIO JT AG TMS or SWD data in/out TMS

Stellaris® LM3S9B96 Development Kit User’s Manual

Pin 80 TCK/SWCLK JTAG Clock or SWD clock TCK

Pin 26 PA0/U0RX Virtual Com port data to LM3S9B96 VCPRX

Pin 27 PA1/U0TX Virtual Com port data from LM3S9B96 VCPTX

Pin 64 RSTn System Reset RSTn

Serial Wire Out (SWO)

The development board supports the Cortex-M3 Serial-Wire Output (SWO) trace capabilities.

Under debugger control, on-board logic can route the SWO datastream to the VCP transmit

channel. The debugger software can then decode and interpret the trace information received

from the Virtual Com Port. The normal VCP connection to UART0 is interrupted when using SWO.

Not all debuggers support SWO.

See the Stellaris LM3S9B96 Microcontroller Data Sheet for additional information on the Trace

Port Interface Unit (TPIU).

Color QVGA LCD Touch Panel

The development board features a TFT Liquid Crystal graphics display with 320 x 240 pixel

resolution. The display is protected during shipping by a thin, protective plastic film which should

be removed before use.

Features

Features of the LCD module include:

Kitronix K350QVG-V1-F display

320 x RGB x 240 dots

3.5” 262 K colors

September 5, 2010 17

Page 18

Wide temperature range

White LED backlight

Integrated RAM

Resist ive to uc h panel

Control Interface

The Color LCD module has a built-in controller IC with a multi-mode parallel interface. The

development board uses an 8-bit 8080 type interface with GPIO Port D providing the data bus.

Table 2-4 shows the LCD-related signals.

Table 2-5. L CD-Related Signals

Microcontroller Pin Board Function Jumper Name

PE6/ADC1 Touch X+ X+

PE3 Touch Y- YPE2 Touch X- XPE7/ADC0 Touch Y+ Y+

PB7 LCD Reset LRSTn

PD0..7 LCD Data Bus 0..7 LD0..7

PH7 LCD Data/Control Select LDC

PB5 LCD Read Strobe LRDn

PH6 LCD Write Strobe LWRn

- Backlight control BLON

Backlight

The white LED backlight must be powered for the display to be clearly visible. U7 (FAN5331B)

implements a 20 mA constant-current LED power source to the backlight. The backlight is not

normally controlled by the microcontroller, however, the control signal is available on a header. A

jumper may be installed to disable the backlight by connecting it to GND. Alternatively, a wire may

be used to control this signal from a spare microcontroller GPIO line.

Because the FAN5331B operates in a constant current mode, its output voltage will jump up if the

LCD should become disconnected. To prevent over-voltage failure of the IC or diode D3, a zener

(D4) clamps the voltage. The current will limit to 20 mA, but the total board current will be higher

than when the LCD panel is connected. To avoid over-heating the backlighting circuit, install the

BLON jumper to completely shut-down the backlighting circuit.

Power

The LCD module has internal bias voltage generators and requires only a single 3.3 V dc supply.

Resistive Touch Panel

The 4-wire resistive touch panel interfaces directly to the microcontroller, using 2 ADC channe ls

and 2 GPIO signals. See the StellarisW are™ source code for additio nal information on touch panel

implementation.

18 September 5, 2010

Page 19

I2S Audio

The LM3S9B96 development board has advanced audio capabilities using an I2S-connected

Audio TLV320AIC23 CODEC. The factory default configuration has Audio output (Line Out and/or

Headphone output) enabled. Four additional I

and/or Microphone). All four audio interfaces are through 1/8” (3.5mm) stereo jacks. Table 2-6

shows the I

Table 2-6. I

Stellaris® LM3S9B96 Development Kit User’s Manual

2

S signals are required for Audio input (Line Input

2

S audio-related signals.

2

S Audio-Related Signals

Microcontroller Pin Board Function Jumper Name

I2C0SDA CODEC Configuration Data SDA

I2C0SCL CODEC Configuration Clock SCL

I2STXSD Audio Out Serial Data TXSD

I2STXWS Audio Out Framing signal TXWS

I2STXSCK Audio Out Bit Clock BCLK

I2STXMCLK Audio Out System Clock MCLK

I2SRXSD Audio In Serial Data RXSD

I2SRXWS Audio In Framing signal RXWS

I2SRXSCK Audio In Bit Clock BCLK

I2SRXMCLK Audio In System Clock MCLK

a

b

b

b

b

a. Shares GPIO line with Analog voltage reference. Jumper installed by default.

b. Shares GPIO line with LCD data bus – Port D. Jumper omitted by default.

The Audio CODEC has a number of control registers which are configured using the I

signals. CODEC settings can only be written, but not read, using I

example applications for programming information and the TLV320AIX23B data sheet for

complete register details.

The Headphone output can be connected dir ectly to any stand ard headphones. The Lin e Output is

suitable for connection to an external amplifier, including PC desktop speaker sets.

User Switch and LED

The development board provides a user push-switch and LED (see Table 2-7).

Table 2-7. Navigation Switch-Related Signals

Microcontroller Pin Board Function Jumper Name

PJ7 User Switch SWITCH

PF3 User LED LED

a. Shared with Ethernet Jack Yellow LED. This jumper is installed by default.

2

2

C. See the StellarisW are™

a

C bus

September 5, 2010 19

Page 20

20 September 5, 2010

Page 21

CHAPTER 3

Stellaris® LM3S9B96 Development Board External Peripheral Interface (EPI)

The External Peripheral Interface (EPI) is a high-speed 8/16/32- bit parallel bus for connecting

external peripherals or memory without glue logic. Supported modes include SDRAM, SRAM, and

Flash memories, as well as Host-bus and FIFO mo d es.

The LM3S9B96 development kit includes an 8 MB SDRAM board in addition to an EPI break-out

board. Other EPI expansion boards may be availabl e.

SDRAM Expansion Board

The SDRAM board provides 8 MB of memory (4M x 16) which, once configured, becomes part of

the LM3S9B96’s memory map at either 0x6000 .0 0 00 or 0x80 00 .0 00 0 . Th e SDRAM inte r face

multiplexes DQ00..14 and AD/BA0..14 without requiring external latches or buffers. Of the 32 EPI

signals, only 24 are used in SDRAM mode, with the remaining signals used for non-EPI functions

on the board.

Flash and SRAM Memory Expansion Board

The optional Flash and SRAM Memory Expansion Board (DK-LM3S9B9 6-FS8) is a plug-in fo r th e

DK-LM3S9B96 development board. This expansion board works with the External Peripheral

Interface (EPI) of the Stellari s microcontroller and provides Flash memory, SRAM, and an

improved performance LCD interface.

For more information on the Flash and SRAM Memory Expansion Board (sold separately), see

Appendix E, “Stellaris® LM3S9B96 Flash and SRAM Memory Expansion Board,” on page 41.

FPGA Expansion Board

The FPGA Expansion Board (DK-LM3S9B96-FPGA) is an optional expansion board which

connects directly to the External Peripheral Interface (EPI) port of the Stellaris DK-LM3S9B96

development board to demonstrate the machine-to-machine (M2M), high-bandwidth, parallel

interface capability of the Stellaris microcontroller. Right out of the box, users are able to control

and display the FPGA expansion board’s video on the DK- LM3S9B96 development bo ard’s large,

3.5” touchscreen display.

For more information on the FPGA Expansion Board (sold separately), see Append ix F , “S tellaris®

LM3S9B96 FPGA Expansion Board,” on page 49.

EM2 Expansion Board

The EM2 Expansion Board (DK-LM3S9B96-EM2) is an optional expansion boar d wh ich connects

directly to the External Peripheral Interface (EPI) port of the Stellaris DK-LM3S9B96 development

board. The EM2 Expansion Board provides a transition between the Stellaris External Peripheral

Interface (EPI) connector and the RF Evaluation Module (EM) connector. The DK-LM3S9B96-EM2

enables wireless application development using Low Power RF and RF ID evaluation modules on

the Stellaris DK-LM3S9B96 platform.

For more information on the EM2 Expansion Board (sold separately), see Appendix G, “Stellaris®

LM3S9B96 EM2 Expansion Board,” on page 69.

September 5, 2010 21

Page 22

22 September 5, 2010

Page 23

LM3S9B96 Dev Board

Target

Board

Stellaris

MCU

USB

to

JTAG/

SWD

PC with IDE/

debugger

Stellaris

MCU

JT AG or SW D c onnec t s to t he

ext ernal m ic roc ont roller

Rem ov e jum pers to us e I C D I Out F eat ure

`

TCK

TMS

TDI

TDO

Target

Cable

VDD

+3.3 V

CHAPTER 4

Using the In-Circuit Debugger Interface

The Stellaris® LM3S9B96 Development Kit can operate as an In-Circuit Debugger Interface

(ICDI). ICDI acts as a USB to the JTAG/SWD adaptor, allowing debugging of any external target

board that uses a S tellaris mi crocontroller. See “Debugging Modes” on page 16 for a description of

how to enter ICDI Out mode.

Figure 4-1. ICD Interface Out Mode

The debug interface operates in either serial-wire debug (SWD) or JTAG mode, depending on the

configuration in the debugger IDE.

The IDE/debugger does not distinguish between the on-board Stellaris microcontroller and an

external Stellaris microcontroller. The only requirement is that the correct Stellaris device is

selected in the project configuration.

The Stellaris target board should have a 2x10 0.1” pin header with signals as indicated in

Table C-1 on page 35. This applies to both an external Stellaris microcontroller target (Debug

Output mode) and to external JTAG/SWD debuggers (Debug Input mode).

ICDI does not control RST (device reset) or TRST (test reset) signals. Both reset functions are

implemented as commands over JTAG/SWD, so these signals are usually not necessary.

September 5, 2010 23

Page 24

24 September 5, 2010

Page 25

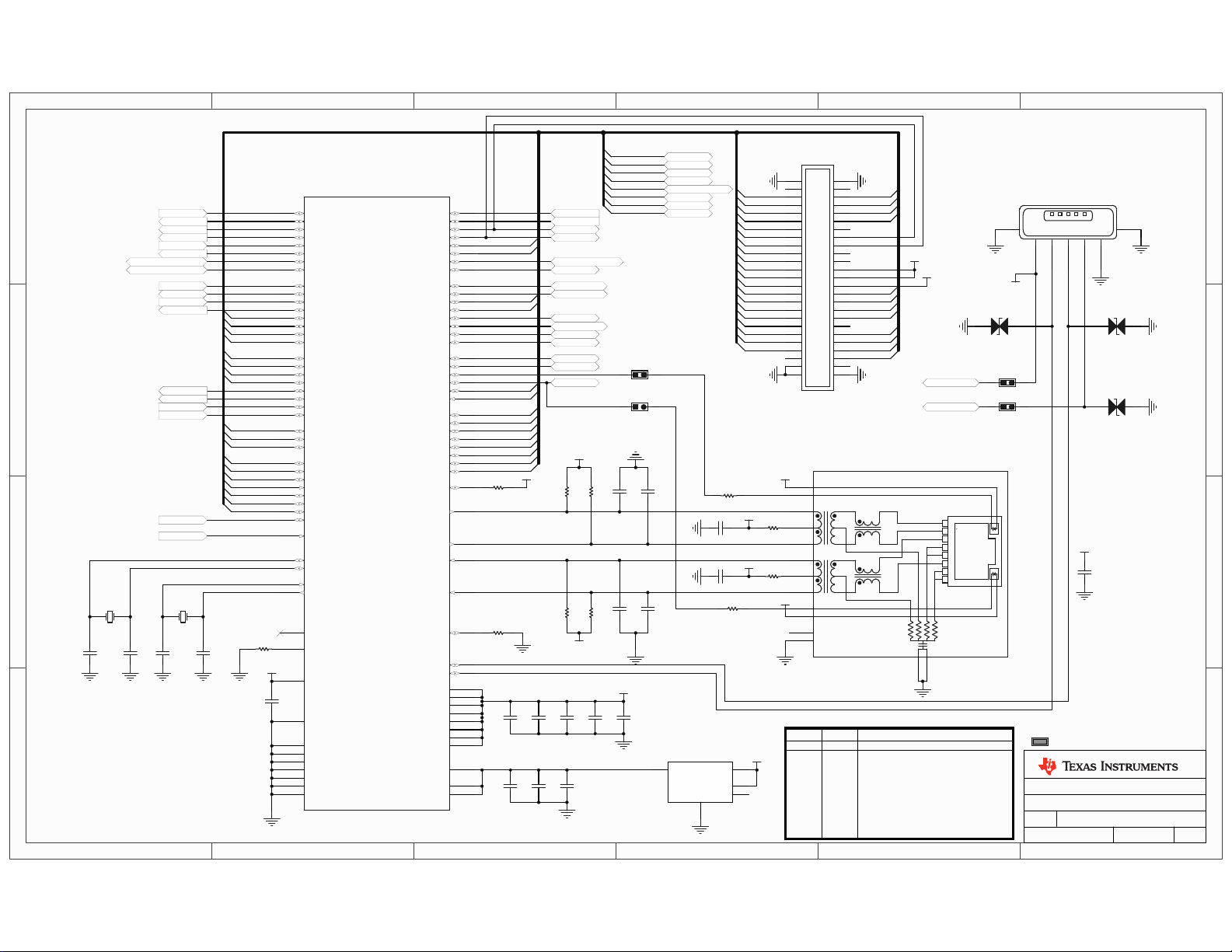

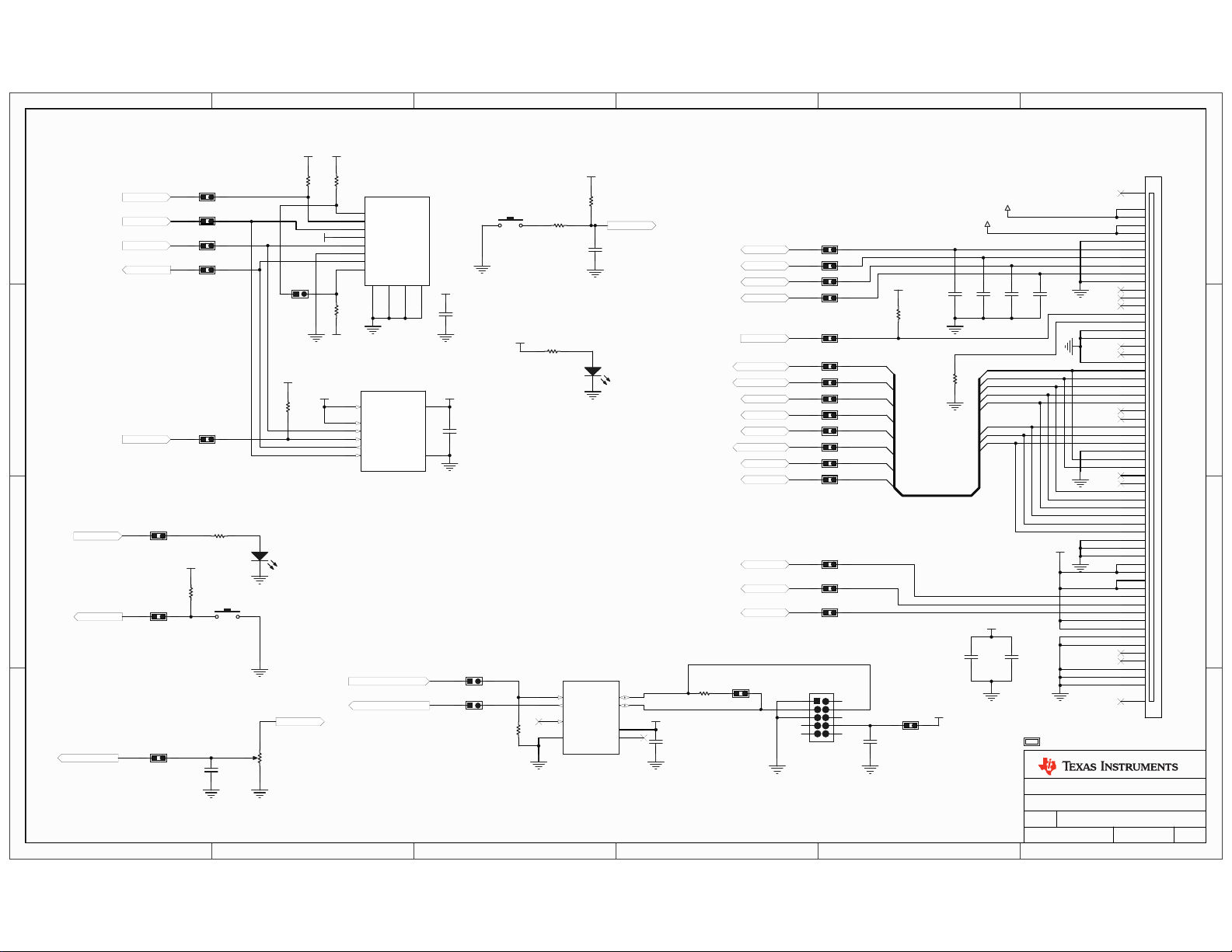

APPENDIX A

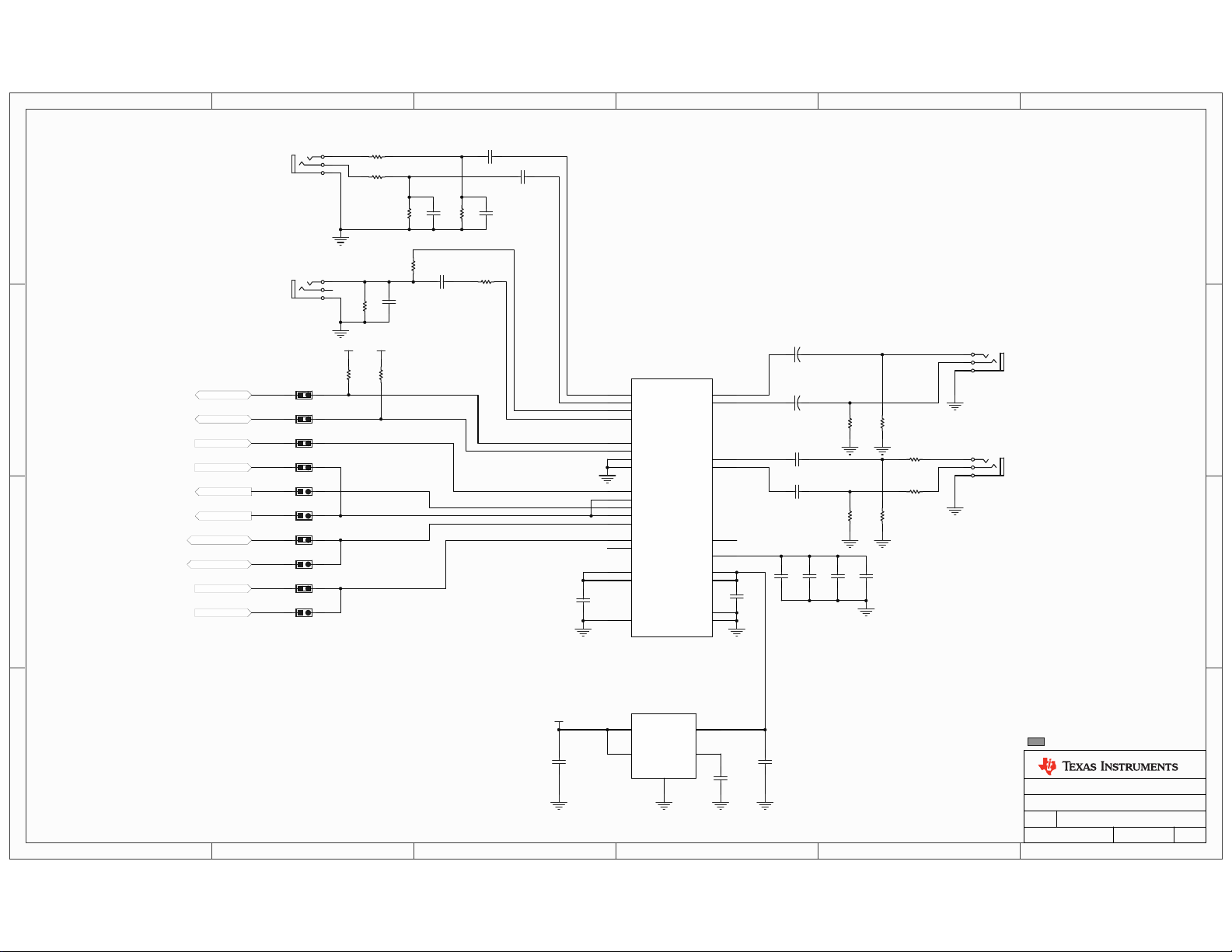

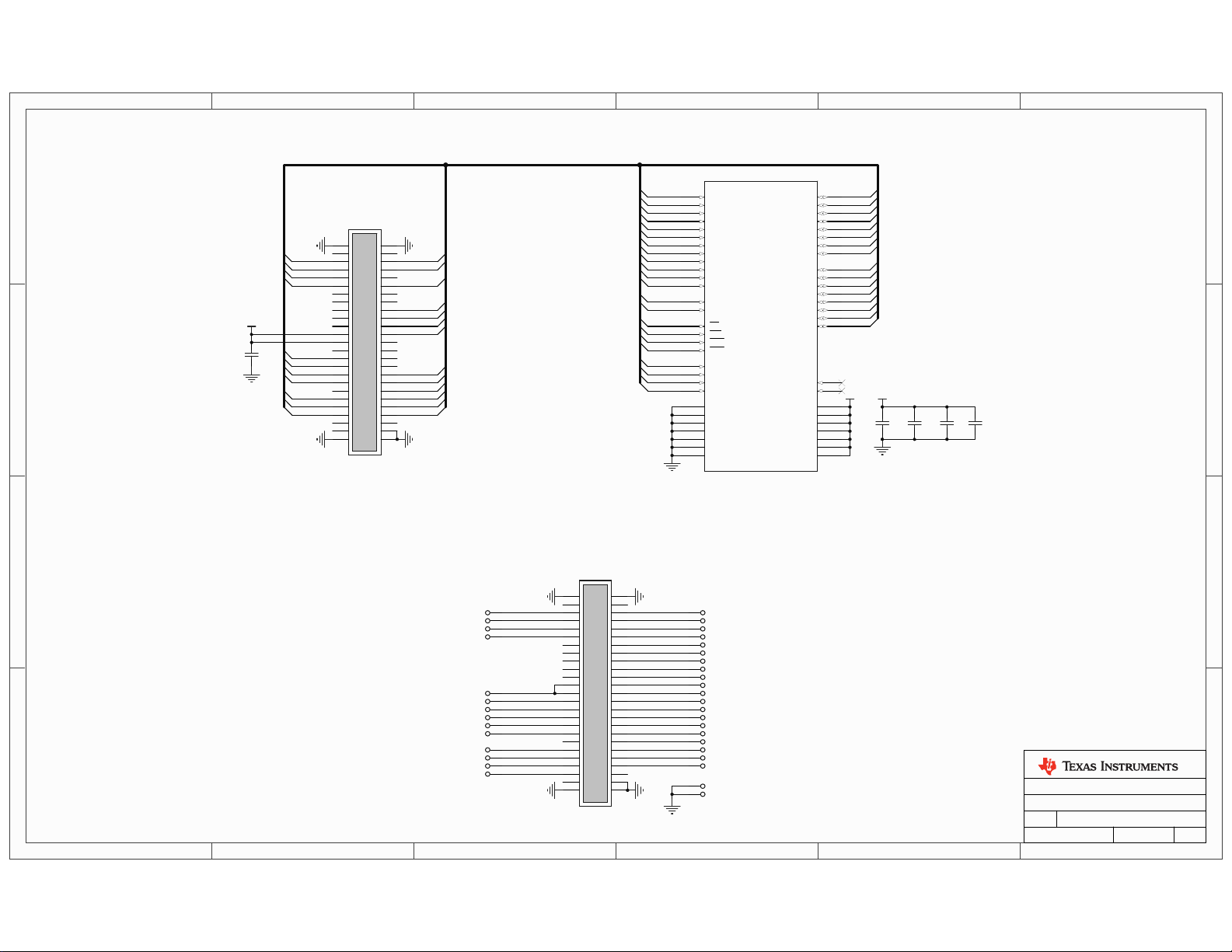

Stellaris® LM3S9B96 Development Board Schematics

This section contains the schematics for the DK-LM3S9B96 development board.

Micro, EPI connector, USB, and Ethernet on page 26

LC D CAN, Ser i al Me m ory, and User I/O on page 2 7

Power Supplies on page 28

2

I

S Audio Expansion Board on page 29

EPI and SDRAM Expansion Boards on page 30

In-circuit Debug Interface (ICDI) on page 31

September 5, 2010 25

Page 26

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 1 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

Micro, EPI connector, USB and Ethernet

B

A

DB-LM3S9B96

10PFC110PF

C2

PC0/TCK

PC1/TMS

PC2/TDI

PC3/TDO

6

5

8

4

2

3

1

7

1CT:1

TX+

TXRX+

RX-

1CT:1

Y+

Y-

G+

G-

3

8

7

4

5

6

11

12

2

1

GL

GR

9

10

NC

GND

J1

J3011G21DNL

R6

49.9

+3.3V

R4

49.9

R5

49.9R749.9

C18

0.1UF

+3.3V

C19

0.1UF

+3.3V

C17

10pF

C13

10pF

C16

10pF

R8

330

R2

10K

M+3.3V

Stellaris Microcontroller

R9

330

+3.3V

+3.3V

PF2/LED1

1 2

Y1

25.00MHz

C14

10pF

10PFC310PF

C4

+3.3V

C5

0.1UF

PJ2/EPI18

PJ1/EPI17

PJ0/EPI16

PG7/EPI31

PC4/EPI02

PC5/EPI03

PC6/EPI04

PC7/EPI05

PE0/EPI08

PE1/EPI09

PH4/EPI10

PH5/EPI11

PG0/EPI13

C7

0.01UFC90.1UF

C11

2.2UF

PH0/EPI06

PH1/EPI07

PF4/EPI12

PH3/EPI00

PH2/EPI01

R3

9.10K

OSC1

OSC0

XTALP

XTLN

M+3.3V

PB4/ADC10/EPI23

PB5/EPI22

PA5/SSI0TX

PA4/SSI0RX

PA2/SSI0CLK

Ethernet 10/100baseT

PG1/EPI14

PF5/EPI15

Y2

16.00MHz

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25 26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

J2

DF12D-50DP

EPI Expansion Connector

PD2/EPI20

PD3/EPI21

PH6/EPI26

PH7/EPI27

PE2/EPI24

PE3/EPI25

PH4/EPI10

PH3/EPI00

PH2/EPI01

PH1/EPI07

PH0/EPI06

PJ1/EPI17

PB5/EPI22

PB4/ADC10/EPI23

PE2/EPI24

PE3/EPI25

PJ3/EPI19

PJ4/EPI28

PJ5/EPI29

PJ6/EPI30

PD2/EPI20

PD3/EPI21

PH7/EPI27

PJ0/EPI16

PG1/EPI14

PG0/EPI13

PC4/EPI02

PC5/EPI03

PC6/EPI04

PC7/EPI05

PH6/EPI26

PH5/EPI11

PE0/EPI08

PE1/EPI09

+3.3V

PG7/EPI31

PJ2/EPI18

PF5/EPI15

PF4/EPI12

+5V

Revision Date Description

History

0 11 Mar 09 Initial Prototype

R1

12.4K

RESETn

PJ3/EPI19

PJ4/EPI28

PJ5/EPI29

PJ6/EPI30

PA3

PA1/U0TX

PA0/U0RX

PE4/I2STXWS

PE5/I2STXSD

PE6/ADC1

PE7/ADC0

PJ7

PB0/USBID

PB1/USBVBUS

PB2/I2C0SCL

PB3/I2C0SDA

PD0/I2SRXSCK

PD4/I2SRXSD

PD6

PD7

PB6/TXSCK/AVREF

PB7/NMI

PF0

PF1/TXMCLK

LED2

JP2

PF3/LED0

VBUS D- D+ ID G

123

4G25

G1

J3

USB Micro AB

USB On-the-Go

+VBUS

PB0/USBID

OTG ID

JP4

+VBUS

JP3

PB1/USBVBUS

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4/EPI0S02

25

PC5/EPI0S03

24

PC6/EPI0S04

23

PC7/EPI0S05

22

PD0

10

PD1

11

PD2/EPI0S20

12

PD3/EPI0S21

13

PE2/EPI0S24

95

PE3/EPI0S25

96

PD6

99

PD7

100

GND

9

PH7/EPI0S27

15

GND

21

ERBIAS

33

RST_n

64

LDO

7

OSC0

48

OSC1

49

PB0/USB0ID

66

PB1/USB0VBUS

67

USB0DM

70

USB0DP

71

PB4/EPI0S23

92

PB5/EPI0S22

91

PB6/AVREF

90

PB7/NMI

89

PB2/CCP0

72

USB0RBIAS

73

PE0/EPI0S08

74

PE1/EPI0S09

75

PE4/ADC3

6

PE5/ADC2

5

PA6/USB0EPEN

34

PA7/USB0PFLT

35

PE6/ADC1

2

PE7/ADC0

1

PF0

47

PF1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

PF5/EPI0S15

41

PG0/EPI0S13

19

PG1/EPI0S14

18

XTLN

17

XTLP

16

PF4/EPI0S12

42

RXIP

40

RXIN

37

PG7/EPI0S31

36

PH0/EPI0S06

86

PH1/EPI0S07

85

PH2/EPI0S01

84

PH3/EPI0S00

83

VDDA

3

PD5

98

PD4

97

GNDA

4

VDD

8

VDD

20

VDD

32

VDD

44

VDD

56

VDD

68

VDD

81

VDD

93

PJ2/EPI0S18

39

GND

45

PJ6

54

GND

57

PH5/EPI0S11

63

GND

69

GND

82

PJ1/EPI0S17

87

GND

94

PJ0/EPI0S16

14

VDD25

38

PH6/EPI0S26

62

VDD25

88

PJ3

50

NC

51

PJ4

52

PJ5

53

PJ7

55

PB3

65

PH4/EPI0S10

76

U1

LM3S9B96

C6

0.01UFC80.01UF

C12

0.1UF

C10

0.1UF

M+3.3V

C15

2.2UF

C21

0.01UF

+3.3V

PD2/EPI20

PD3/EPI21

PB4/ADC10/EPI23

PB5/EPI22

PE2/EPI24

PE3/EPI25

LED1

JP1

PH6/EPI26

PH7/EPI27

PA7/USBPFLT/CAN0TX

PA6/USBEPE/CAN0RX

PD1/I2SRXWS

PD5/I2SRXMCLK

PE2/EPI24

PE3/EPI25

PD2/EPI20

PD3/EPI21

PB4/ADC10/EPI23

PB5/EPI22

PH6/EPI26

PH7/EPI27

1 2

D2

B72590D0050H160

1 2

D5

B72590D0050H160

12

D1

B72590D0050H160

Indicates factory-default jumper position.

15 Apr 09 First production release

GND

2

VIN

1

VOUT

5

PG

4

EN

3

U16

FAN2558S12X

+5V

U16 Required only for

LM3S9B96 Rev B1.

See errata.

R60

10

R61

10

R60-61 = 10 Ohms for LM3S9B96 Rev B1 (see errata)

R60,R11 = 0 Ohms for LM3S9B96 Rev C

Note:

A

Schematic page 1

Page 27

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 2 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

LCD, CAN, Serial Memory, User IO

B

A

DB-LM3S9B96

Reset

SW2

SW-B3S1000

RESETn

R19

10K

+3.3V

User Switch

R18

330

Power

+3.3V

SW1

SW-B3S1000

microSD Card Slot

N/C DATA2

1

CS DATA3

2

DI CMD

3

VDD

4

CLOCK

5

GND

6

DO DATA0

7

RSV DATA1

8

FR19FR210FR311FR4

12

J4

2908-05WB-MG

+3.3V

C24

0.1UF

+3.3V

R15

10K

R16

10K

+3.3V

+3.3V

LED2

Green

C26

0.1UF

XR

YD

XL

YU

LCD_RSTn

CSn

SPICLK

SPISDI

HSYNC

VSYNC

DCLK

AVDD

VCC

DC

RD

WR

PS0

PS1

PS2

PS3

OE

LED_K

LED_A

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LD8

LD10

LD11

LD12

LD13

LD14

LD15

LD16

LD17

LCD_D0

LCD_D1

LCD_D2

LCD_D3

LCD_D4

LCD_D5

LCD_D6

LCD_D7

LD0

LD9

TOUCH_YP

TOUCH_YN

TOUCH_XP

TOUCH_XN

ILED+

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

1

M1

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

M2

J6

FPC_Socket_60pin

QVGA LCD Panel

R21

10K

PB7/NMI

+3.3V

Thumbwheel Potentiometer

C32

0.1UF

C29

0.1UF

QVGA LCD Panel

with touch interface

LCD_D[0..7]

C28

0.01UF

C30

0.01UF

C31

0.01UF

C33

0.01UF

+3.3V

R12

50K

ILED-

C23

0.1UF

R14

10K

+3.3V

8-bit 8080 mode

PE6/ADC1

PE3/EPI25

PE2/EPI24

PE7/ADC0

X+

JP16

Y-

JP17

X-

JP18

Y+

JP19

LD0

JP21

LD1

JP22

LD2

JP23

LD3

JP24

LD4

JP25

LD5

JP26

LD6

JP27

LD7

JP28

PD2/EPI20

PD3/EPI21

PD6

PD7

LCD_D0

LCD_D1

LCD_D2

LCD_D3

LCD_D4

LCD_D5

LCD_D6

LCD_D7

LDC

JP29

LRDn

JP30

LWRn

JP31

PH7/EPI27

PH6/EPI26

LCD_DC

LCD_RDn

LCD_WRn

R11

330

PF3/LED0

User LED

LED1

Green

POT

JP7

SWITCH

JP6

PJ7

PB4/ADC10/EPI23

LED

JP5

SI

5

SCK

6

nWP

3

nCE

1

nHOLD7VDD

8

VSS

4

SO

2

U2

W25X80AVSSIG-ND

C25

0.1UF

+3.3V+3.3V

R13

10K

+3.3V

1MB Serial Flash

PA5/SSI0TX

PA2/SSI0CLK

PA4/SSI0RX

PA3

SDCSn

JP9

MOSI

JP10

SCLK

JP11

MISO

JP12

FLCSn

JP8

PF0

SD_CSn

MOSI

MISO

SSICLK

FLASH_CSn

CANH

7

CANL

6

TXD

1

RXD

4

RS

8

GND2VREF

5

VCC

3

U3

SN65HVD1050D

+5V

CAN Transceiver

C27

0.1UF

TXD

JP14

RXD

JP15

1 2

3 4

5 6

7 8

9 10

J5

CANH

CANL

VREF_3.0V

PA7/USBPFLT/CAN0TX

PA6/USBEPE/CAN0RX

R17

10K

LRSTn

JP20

R20

10K

+3.3V

R10

10K

+3.3V

PD1/I2SRXWS

CARD

JP13

PD4/I2SRXSD

PD5/I2SRXMCLK

PB5/EPI22

+VCAN

JP32

+5V

CAN Connector

+VCAN

PD0/I2SRXSCK

TERM

JP58

R58

120

C22

0.1UF

Indicates factory-default jumper position.

R59

100

Schematic page 2

Page 28

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 3 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

Power Supplies

B

A

DB-LM3S9B96

DBG+5V

VBUS Fault Protected Switch

+VBUS

GND

2

IN

5

EN

4

OCn

3

OUT

1

U6

TPS2051BDBV

C40

2.2UF

C41

2.2UF

C43

2.2UF

SHDN

4

VIN5SW

1

GND

2

FB

3

U7

FAN5333B

ILED+

D3

FYV0704SMTF

+5V

C38

2.2UF

10uH

L1

NR4018T100M

LED Backlight Controller

C45

0.1UF

C46

0.1UF

C44

0.1UF

R26

15

R25

10K

ILED-

24V

D4

BZT52C24

+5V

EPEN

JP37

PFLT

JP38

Backlight

JP39

PA7/USBPFLT/CAN0TX

PA6/USBEPE/CAN0RX

USB0EPE

USB0PFLT

0.01UF

C39

C42

2.2UF

C37

2.2UF

VOUT

5

NR

1

ON

3

GND

2

VIN

4

U5

PQ1LA333MSPQ

C36

2.2UF

+5V

ICDI

JP34

OTG

JP35

EXT

JP36

+5V

+5V DC INPUT

PJ-002BH-SMT

1

2

3

J7

+VBUS

CATHODE

1

ANODE

2

NC

3

U4

LM4040B30IDB

VREF 3.00V

JP33

R22

1.5K

+3.3V

C35

2.2UF

3.0V 0.2% Voltage Reference

Main +3.3V Supply

Power Source Selection

R24

10K

R23

10K

+3.3V

VREF_3.0V

PB6/TXSCK/AVREF

C34

0.1UF

GND

TP2

BLON

5.0V

TP3

+5V

C20

0.1UF

Indicates factory-default jumper position.

+3.3V

3.3V

TP1

P3V

JP60

M3V

JP61

M+3.3V

GND

JP59

Schematic page 3

Page 29

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 4 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

I2S Audio Expansion Board

B

A

DB-LM3S9B96

1

3

2

J11

STX-3000

BVDD

1

BCLK

3

DOUT

6

DIN

4

LRCIN

5

LRCOUT

7

CLKOUT

2

HPVDD

8

LHPOUT

9

RHPOUT

10

HPGND

11

LOUT

12

ROUT

13

AVDD

14

AGND

15

VMID

16

MICBIAS

17

MICIN

18

RLINEIN

19

LLINEIN

20

nCS

21

MODE

22

SDIN

23

SCLK

24

XTI/MCLK

25

XTO

26

DVDD

27

DGND

28

U8

TLV320AIC23BPW

C57

0.47UF

C58

0.47UF

R33

47K

R35

47K

R36

100

R37

100

Audio Line Output

1

3

2

J10

STX-3000

4V

+

C55

220UF

4V

+

C54

220UF

R32

47K

R34

47K

C56

0.1UF

C59

2.2UF

C60

2.2UF

C61

2.2UF

C50

0.1UF

1

3

2

J9

STX-3000

R31

4.7K

R28

10K

27PF

C47

C48

2.2UF

MICIN

R30

10K

MICBIAS

Audio Headphone Output

Microphone Input

MCLK

LRC

RXSD

BITCLK

TXSD

Analog +3.3V 50mA Power Supply

C52

0.1UF

Line Input

SDA

JP40

PB3/I2C0SDA

PB2/I2C0SCL

PE5/I2STXSD

PE4/I2STXWS

PD4/I2SRXSD

PD1/I2SRXWS

PF1/TXMCLK

SCL

JP41

TXSD

JP42

TXWS

JP43

RXSD

JP44

RXWS

JP45

PB6/BCLK

JP46

0.01UF

C51

C53

2.2UF

C49

2.2UF

VOUT

5

NR

1

ON

3

GND

2

VIN

4

U9

PQ1LA333MSPQ

+5V

R27

4.7K

R29

4.7K

+3.3V +3.3V

PD5/I2SRXMCLK

PB6/TXSCK/AVREF

PD0/BCLK

JP47

PD0/I2SRXSCK

1

3

2

J8

STX-3000

R54

4.7K

R55

4.7K

R56

4.7K

R57

4.7K

27PF

C76

27PF

C78

C77

0.47UF

C79

0.47UF

PD5/MCLK

JP49

PF1/MCLK

JP48

Indicates factory-default jumper position.

Rework 2: Loop TXWS to RXWS.

Schematic page 4

Page 30

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 5 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

EPI and SDRAM Expansion Boards

B

A

DB-LM3S9B96

A0

23

DQ0

2

BA0

20

BA1

21

CLK

38

CKE

37

WE

16

DQMH

39

NC

40

RAS

18

CAS

17

VSS

28

VSSQ

6

VSSQ

12

VSSQ

46

VSSQ

52

VSS

41

VSS

54

VDDQ

3

VDDQ

9

VDDQ

43

VDDQ

49

VDD

1

VDD

14

VDD

27

A1

24

A2

25

A3

26

A4

29

A5

30

A6

31

A7

32

A8

33

A9

34

A10

22

A11

35

NC

36

DQ1

4

DQ2

5

DQ3

7

DQ4

8

DQ5

10

DQ6

11

DQ7

13

DQ8

42

DQ9

44

DQ10

45

DQ11

47

DQ12

48

DQ13

50

DQ14

51

DQ15

53

CS

19

DQML

15

U10

MT48LC4M16A2

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

D12

BA0/D13

BA1/D14

D15

AD8

AD9

AD10

AD11

CSn

WEn

RASn

CASn

SDCLK

SDCKE

DQM1

DQM0

BA0/D13

BA1/D14

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

+3.3V

8MB SDRAM

C65

0.1UF

C64

0.01UF

C63

0.01UF

C66

0.1UF

+3.3V

Expansion Connector

SDRAM Expansion Board

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

2526

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

J12

DF12A-50DS

+3.3V

C62

2.2UF

AD2

AD3

AD4

AD5

SDCLK

CASn

D15

D12

AD9

AD8

AD11

BA0/D13

BA1/D14

DQM0

SDCKE

CSn

WEn

RASn

DQM1

AD6

AD7

AD1

AD0

AD10

Expansion Connector

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

2526

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

J15

DF12A-50DS

EPI Signal Breakout Board

X_PH4/EPI10

X_PH3/EPI00

X_PH2/EPI01

X_PH1/EPI07

X_PH0/EPI06

X_PJ1/EPI17

X_PB5/EPI22

X_PB4/EPI23

X_PE2/EPI24

X_PE3/EPI25

X_PJ3/EPI19

X_PJ4/EPI28

X_PJ5/EPI29

X_PJ6/EPI30

X_PD2/EPI20

X_PD3/EPI21

X_PH7/EPI27

X_PJ0/EPI16

X_PG1/EPI14

X_PG0/EPI13X_PC4/EPI02

X_PC5/EPI03

X_PC6/EPI04

X_PC7/EPI05

X_PH6/EPI26

X_PH5/EPI11

X_PE0/EPI08

X_PE1/EPI09

X_PG7/EPI31

X_PJ2/EPI18

X_PF5/EPI15

X_PF4/EPI12

X+3.3V

X+5V

Schematic page 5

Page 31

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

4/23/2009 6 6

Drawing Title:

Page Title:

Size

LM3S9B96 Development Board

In-circuit Debug Interface (ICDI)

B

A

DB-LM3S9B96

GND

18

GND

25

GND

34

ADBUS0

24

ADBUS1

23

ADBUS2

22

ADBUS3

21

ADBUS4

20

ADBUS5

19

ADBUS6

17

ADBUS7

16

ACBUS0

15

ACBUS1

13

ACBUS2

12

ACBUS3

11

BDBUS0

40

BDBUS1

39

BDBUS2

38

BDBUS3

37

BDBUS4

36

BDBUS5

35

BDBUS6

33

BDBUS7

32

BCBUS0

30

BCBUS1

29

BCBUS2

28

BCBUS3

27

SI/WUA

10

SI/WUB

26

GND

9

AGND

45

VCC

3

VCC

42

VCCIOA

14

VCCIOB

31

AVCC

46

PWREN#

41

XTOUT

44

XTIN

43

EECS

48

EESK

1

EEDATA

2

TEST

47

RESET#

4

RSTOUT#

5

3V3OUT

6

USBDM

8

USBDP

7

U12

FT2232D

+3.3V

DBG+5V

R41 27

R42 27

+3.3V

+3.3V

DBG_JTAG_EN

R39

10K

R40

1.5K

R44

1.5K

R45

330

+5V

+5V

+5V+5V

FT_TCK

FT_TDI/DI

FT_TDO/DO

FT_TMS/OUTEN

0.1UF

C71

0.1UF

C72

0.1UF

C73

0.1UF

C74

0.1UF

C75

0.1UF

C70

USB Device Controller

Channel A : JTAG / SW Debug

Channel B : Virtual Com Port

5V D- D+ ID G

123

475

6

J13

54819-0572

FT_SRSTN

Debugger USB Interface

R43

USBSH

CS

1

SK

2

DI

3

DO

4

GND

5

ORG

6

NC

7

VCC

8

1K 64X16

U11

CAT93C46

1 2

Y3

6.00MHz

27PF

C68

27PF

C69

SWO_EN

0.01UF

C67

2 3

1

U14A

SN74LVC125A

5 6

4

U13B

SN74LVC125A

98

10

U13C

SN74LVC125A

12 11

13

U14D

SN74LVC125A

2 3

1

U13A

SN74LVC125A

56

4

U14B

SN74LVC125A

9 8

10

U14C

SN74LVC125A

2 3

1

U15A

SN74LVC126A

5 6

4

U15B

SN74LVC126A

98

10

U15C

SN74LVC126A

1211

13

U15D

SN74LVC126A

VCP_TX_SWO

DBGENn

12 11

13

U13D

SN74LVC125A

12

34

56

78

910

1112

1314

1516

1718

1920

J14

2X10 HDR-SHRD

+3.3V

TDI

TCK

R46

27

TMS_SWDIO

SRSTN

TDO_SWO

VCP_TX

R47

27

R48

27

R49

27

R50

27

PIN1

JP57

TCK

JP50

PC0/TCK

PC1/TMS

PC2/TDI

PC3/TDO

TMS

JP51

TDI

JP52

TDO

JP53

TCK

TDI

TMS_SWDIO

TDO_SWO

TDI

TMS_SWDIO

TCK

TDO_SWO

SRSTN

R38

10K

+3.3v

RESETn

RSTn

JP54

SRSTN

PA1/U0TX

VCPTX

JP55

PA0/U0RX

VCPRX

JP56

VCP_RX

VCP_RX

VCP_TX

JTAG/SWD In/Out

147

VCC

GND

U14E

SN74LVC125A

147

VCC

GND

U13E

SN74LVC125A

147

VCC

GND

U15E

SN74LVC126A

+3.3V +3.3V +3.3V

0.1UF

C80

+3.3V

R51

10K

+3.3V

R52

10K

R53

10K

Indicates factory-default jumper position.

Schematic page 6

Page 32

32 September 5, 2010

Page 33

APPENDIX B

Stellaris® LM3S9B96 Development Board Component Locations

This appendix contains details on compo nent locations, including:

Component placement plot for top (Figure B-1)

September 5, 2010 33

Page 34

Figure B-1. Component Placement Plot for Top

34 September 5, 2010

Page 35

Center Positive (+)

APPENDIX C

Stellaris® LM3S9B96 Development Board Connection Details

This appendix contains the following sections:

DC Power Jack (see page 35)

ARM Target Pinout (see page 35)

DC Power Jack

The EVB provides a DC power jack for connecting an external +5 V regulated (+/-5%) power

source.

The socket is 5.5 mm dia with a 2.1 mm pin.

ARM Target Pinout

In ICDI input and output mode, the Stellaris® LM3S9B96 Development Kit supports ARM’s

standard 20-pin JTAG/SWD configuration. The same pin configuration can be used for debugging

over serial-wire debug (SWD) and JTAG interfaces.

Table C-1. Debug Interface Pin Assignments

Function Pin Number

TDI 5

TDO/SWO 13

TMS/SWDIO 7

TCK/SWCLK 9

System Reset 15

VDD 1

GND 4, 6, 8, 10, 12, 14, 16, 18, 20

No Connect 2, 3, 11, 17, 19

Insert Jumper VDD/PIN1 Jumper (JP57) only wh en using th e d evelo pme nt boar d with a n exter na l

debug interface such as a ULINK or JLINK.

September 5, 2010 35

Page 36

36 September 5, 2010

Page 37

APPENDIX D

Stellaris® LM3S9B96 Development Board Microcontroller GPIO Assignments

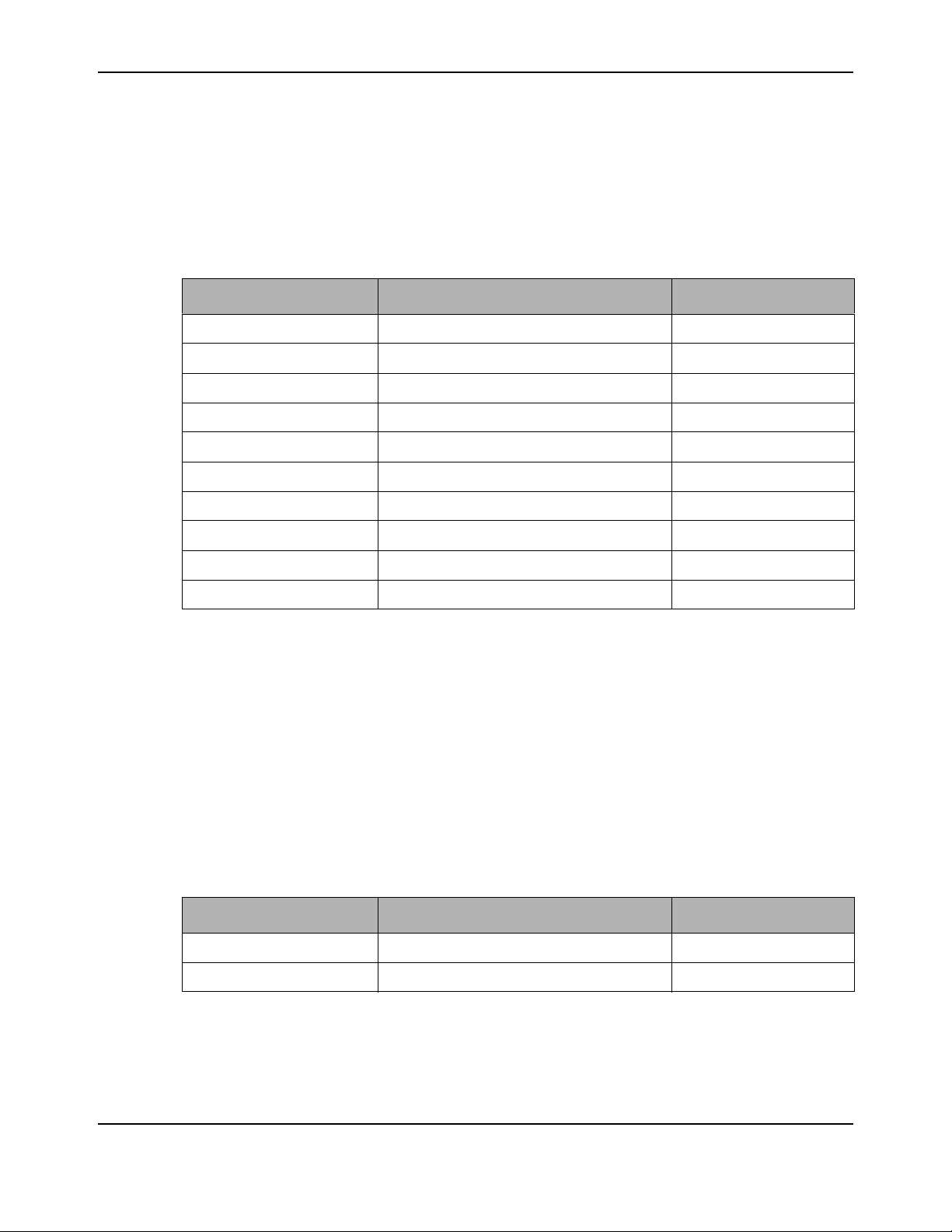

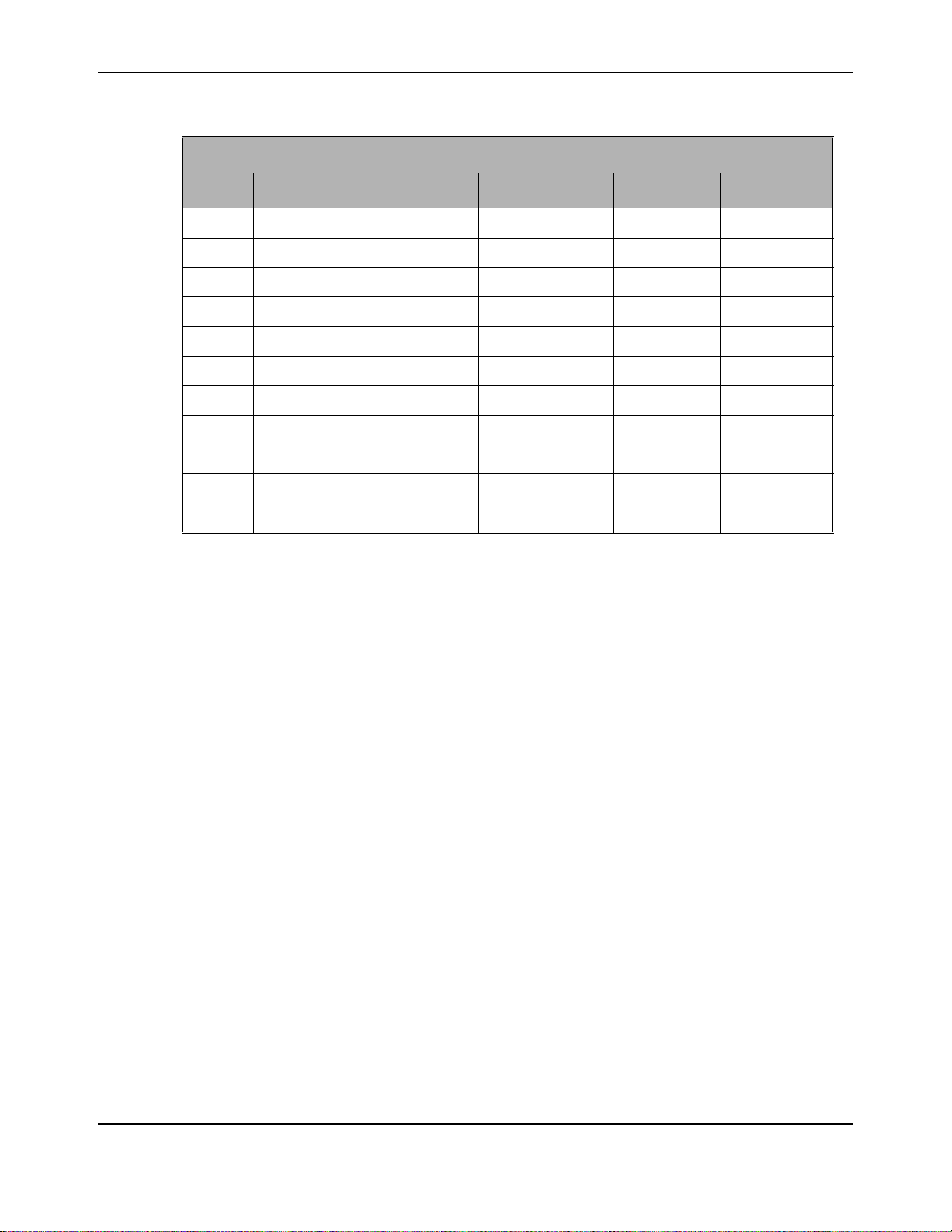

Table D-1 shows the pin assignments for the LM3S9B96 microcontroller.

Table D-1. Microcontroller GPIO Assignments

LM3S9B96 GPIO Pin Development Board Use

Number Description Default Function Default Use Alt. Function Alternate Use

26 PA0 U0Rx Virtual Com Port

27 PA1 U0Tx Virtual Com Port

28 PA2 SSI0Clk SPI

29 PA3 SSI0Fss SD Card CSn

30 PA4 SSI0Rx SPI

31 PA5 SSI0Tx SPI

34 PA6 USB0EPEN USB Pwr Enable CAN0RX

35 PA7 USB0PFLT USB Pwr Fault CAN0TX

66 PB0 USB0ID USB OTG ID

67 PB1 USB0VBUS USB Vbus

72 PB2 I2C0SCL Audio I2C

65 PB3 I2C0SDA Audio I2C

92 PB4 ADC10 Potentiometer EPI0S23 EPI Breakout

91 PB5 PB5 LCD RDn EPI0S22 EPI Breakout

90 PB6 PB6 I2STXSCK AVREF Ext Volt Ref

89 PB7 PB7 LCD RST

80 PC0 TCK/SWCLK JTAG

79 PC1 TMS/SWDIO JTAG

78 PC2 TDI JTAG

77 PC3 TDO/SWO JTAG

25 PC4 EPI0S2 SDRAM D02 EPI0S02

24 PC5 EPI0S3 SDRAM D03 EPI0S03

23 PC6 EPI0S4 SDRAM D04 EPI0S04

22 PC7 EPI0S5 SDRAM D05 EPI0S05

September 5, 2010 37

Page 38

Table D-1. Microcontroller GPIO Assignments (Continued)

LM3S9B96 GPIO Pin Development Board Use

Number Description Default Function Default Use Alt. Function Alternate Use

10 PD0 PD0 LCD Data 0 I2SRXSCK I2S Audio In

11 PD1 PD1 LCD Data 1 I2S0RXWS I2S Audio In

12 PD2 PD2 LCD Data 2 EPI0S20 EPI Breakout

13 PD3 PD3 LCD Data 3 EPI0S21 EPI Breakout

97 PD4 PD4 LCD Data 4 I2SRXSD I2S Audio In

98 PD5 PD5 LCD Data 5 I2SRXMCLK I2S Audio In

99 PD6 PD6 LCD Data 6

100 PD7 PD7 LCD Data 7

74 PE0 EPI0S8 SDRAM D8 EPI0S08

75 PE1 EPI0S9 SDRAM D9 EPI0S09

95 PE2 PE2 Touch XN EPI0S24

96 PE3 PE3 Touch YN EPI0S25

6 PE4 I2STXWS I2S Audio Out

5 PE5 I2STXSD I2S Audio Out

2 PE6 ADC1 ADC Touch XP

1 PE7 ADC0 ADC Touch YP

47 PF0 PF0 Flash CSn

61 PF1 I2STXMCLK I2S Audio Out

60 PF2 LED1 Green Enet LED

59 PF3 PF3 User LED LED0 Yw Enet LED

42 PF4 EPI0S12 SDRAM D12

41 PF5 EPI0S15 SDRAM D15

19 PG0 EPI0S13 SDRAM D13

18 PG1 EPI0S14 SDRAM D14

36 PG7 EPI0S31 SDRAM CLK

86 PH0 EPI0S06 SDRAM D06

85 PH1 EPI0S07 SDRAM D07

84 PH2 EPI0S01 SDRAM D01

83 PH3 EPI0S00 SDRAM D00

76 PH4 EPI0S10 SDRAM D10

38 September 5, 2010

Page 39

Stellaris® LM3S9B96 Development Kit User’s Manual