Page 1

Stellaris® LM3S6965 Evaluation Board

User’s Manual

EK-LM3S6965-06 Copyright © 2007–2010 Texas Instruments

Page 2

Copyright

Copyright © 2007–2010 Texas Instruments, Inc. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments.

RM and Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property

A

of others.

Texas Instruments

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

2 January 6, 2010

Page 3

Stellaris® LM3S6965 Evaluation Board

Table of Contents

Chapter 1: Stellaris® LM3S6965 Evaluation Board ....................................................................................... 7

Features..............................................................................................................................................................8

Block Diagram ....................................................................................................................................................8

Evaluation Kit Contents ...................................................................................................................................... 9

Evaluation Board Specifications .....................................................................................................................9

Features of the LM3S6965 Microcontroller.........................................................................................................9

Chapter 2: Hardware Description.................................................................................................................. 11

LM3S6965 Microcontroller......................... ... .... ... ... ... ... .... ... ... ... .......................................................................11

Device Overview...........................................................................................................................................11

Ethernet ........................................................................................................................................................11

Clocking........................................................................................................................................................ 11

Reset.............................................................................................................................................................11

Power Supplies.............................................................................................................................................12

Debugging.....................................................................................................................................................12

USB Device Controller Functions ..................................................................................................................... 13

Device Overview...........................................................................................................................................13

USB to JTAG/SWD............. ... ... ... .... ... ... .................................................... ................................................... 13

Virtual COM Port........................................................................................................................................... 13

Serial Wire Out..............................................................................................................................................13

Organic LED Display ........................................................................................................................................ 13

Features........................................................................................................................................................ 13

Control Interface ...........................................................................................................................................14

Power Supply................................................................................................................................................ 14

Design Guidelines............................................... .................................................... ......................................14

Further Reference.........................................................................................................................................14

Other Peripherals............. ... .................................................... ..........................................................................14

Speaker.........................................................................................................................................................14

MicroSD Card Slot.................................................... .... ................................................... .............................14

Push Switches ............. ... .... ... ... .................................................... ................................................................ 14

User LED ............... ................................................ ... .... ... ... ... .... ... ... ............................................................. 15

Bypassing Peripherals............................................................... .... ...................................................................15

Interfacing to the EVB....................................................................................................................................... 15

Using the In-Circuit Debugger Interface ...........................................................................................................16

Appendix A: Schematics................................................................................................................................17

Appendix B: Connection Details...................................................................................................................23

Component Locations.......................................................................................................................................23

Evaluation Board Dimensions...........................................................................................................................24

I/O Breakout Pads ............................................................................................................................................24

Recommended Connectors.............................................................. ... ... .......................................................... 25

ARM Target Pinout ........................................................................................................................................... 26

References .......................................................................................................................................................26

January 6, 2010 3

Page 4

List of Figures

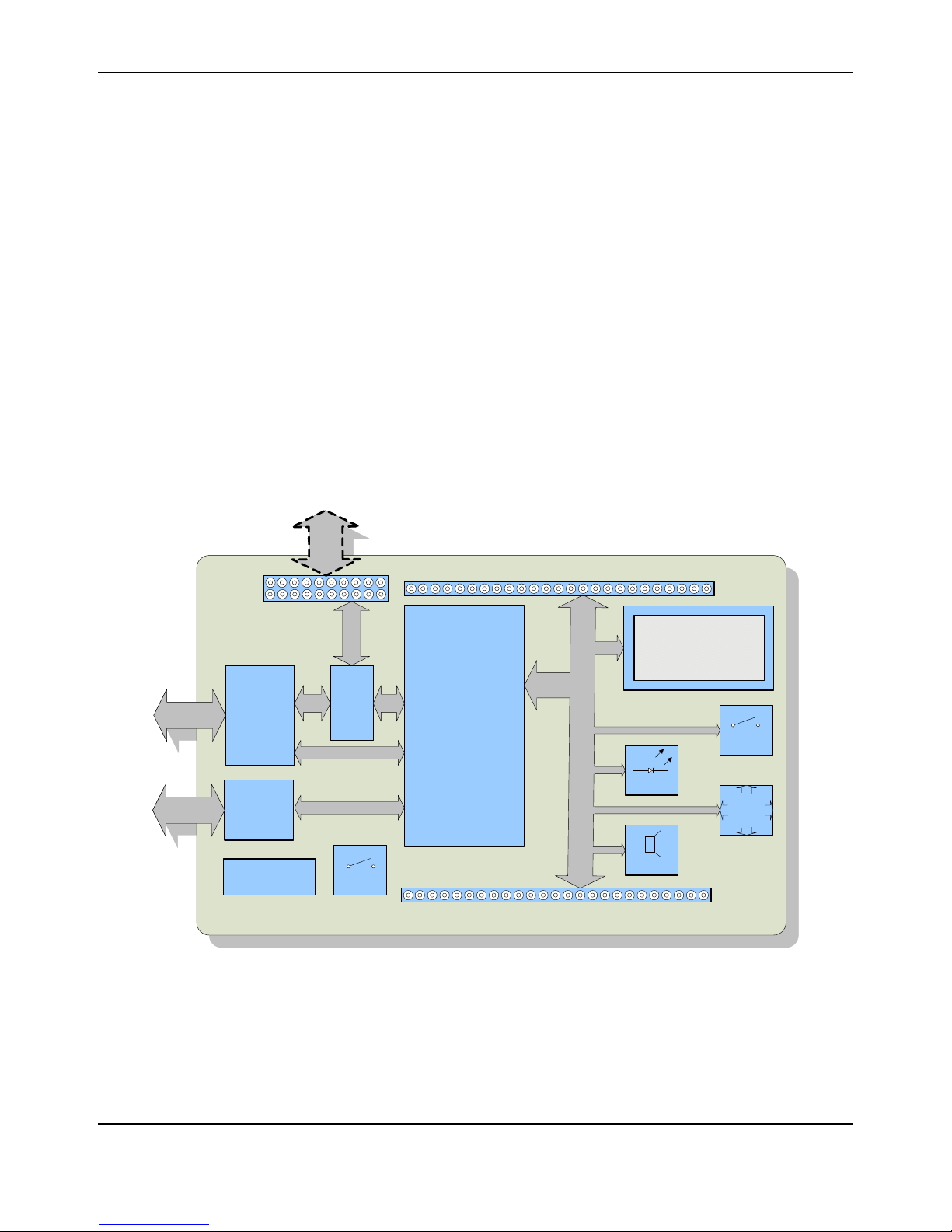

Figure 1-1. Stellaris LM3S6965 Evaluation Board Layout.................................................................................7

Figure 1-2. LM3S6965 Evaluation Board Block Diagram.................................................................................. 8

Figure 2-1. ICD Interface Mode ....................................................................................................................... 16

Figure B-1. Component Locations ...................................................................................................................23

Figure B-2. Evaluation Board Dimensions ............................. ... .... ... ... ... .... ... ... ................................................ 24

4 January 6, 2010

Page 5

Stellaris® LM3S6965 Evaluation Board

List of Tables

Table 2-1. Stellaris LM3S6965 Evaluation Board Hardware Debugging Configurations ... .... ... ... ...... .... ... ... ... 12

Table 2-2. Isolating On-Board Hardware........................................................................................................15

Table B-1. I/O Breakout Pads.........................................................................................................................25

Table B-2. Recommended Connectors................. ... ... .... ... .................................................... ... ... ... ... .............25

Table B-3. 20-Pin JTAG/SWD Configuration..................................................................................................26

January 6, 2010 5

Page 6

6 January 6, 2010

Page 7

P

l

a

c

e

hol

de

r

I

m

a

ge

86%'HYLFH

,QWHUIDFH

EDVH7(WKHUQHW-DFN

PLFUR6'&DUG0HPRU\6ORW

SLQ,2

EUHDNRXW

KHDGHU

SLQ,2

EUHDNRXW

KHDGHU

1DYLJDWLRQ

6ZLWFKHV

6HOHFWVZLWFK

6WDWXV/('

6SHDNHU

'HEXJRXW/('

5HVHWVZLWFK

3RZHU/('

2/('*UDSKLFV

'LVSOD\

-7$*6:'

LQSXWDQG

RXWSXW

6WHOODULV

70

/06

0LFURFRQWUROOHU

,QFLUFXLW'HEXJ

,QWHUIDFH

CHAPTER 1

Stellaris® LM3S6965 Evaluation Board

The Stellaris® LM3S6965 Evaluation Board is a compact and versatile evaluation platform for the

Stellaris LM3S6965 ARM® Cortex™-M3-based microcontrolle r. The evaluation kit uses the

LM3S6965 microcontroller’s fully integrated 10/100 Ethernet controller to demonstrate an

embedded web server.

You can use the board either as an evaluation platform or as a low-cost in-circuit debug interface

(ICDI). In debug interface mode, the on-board microcontroller is bypassed, allowing programming

or debugging of an external targ et. The kit is also comp atible with high-performance extern al JT AG

debuggers.

This evaluation kit enables quick evaluation, prototype development, and creation of applicationspecific designs for Ethernet networks. The kit also includes extensive source-code examples,

allowing you to start building C code applications quickly.

Figure 1-1. Stellaris LM3S6965 Evaluation Board Layou t

January 6, 2010 7

Page 8

Features

USB

USB

Stellaris

LM3S6965

Microcontroller

Dual

USB

Device

Controller

I

/

O

S

i

g

n

a

l

s

OLED Display

128 x 96

Debug

Nav

Switch

Switch

LED

I/O Signal Break-out

I/O Si gnal Break-out

JTAG/SWD

Output/Input

USB Cable

Reset

+3.3V

Regulator

SWD/JTAG

Mux

UART0

T

a

r

g

e

t

C

a

b

l

e

Speaker

RJ45

Jack+

Magnetics

CAT5 Cable

Features

The Stellaris LM3S6965 Evaluation Board includes the following features:

Stellaris LM3S6965 microcon tr oller with fully-integrated 10/100 embedded Ethernet controller

Simple setup; USB cable provides serial communication, debugging, and power

OLED graphics display with 128 x 96 pixel resolution

User LED, navigation switches, and select pushbuttons

Magnetic speaker

LM3S6965 I/O available on labeled break-out pads

Standard ARM® 20-pin JTAG debug connector with input and output modes

USB interface for debugging and power supply

MicroSD card slot

Block Diagram

Figure 1-2. LM3S6965 Evaluation Board Block Diagram

8 January 6, 2010

Page 9

Evaluation Kit Contents

The evaluation kit contains everything needed to develop and run applications for S tellaris

microcontrollers including:

LM3S6965 Evaluation Board (EVB)

USB cable

20-pin JTAG/SWD target cable

CD containing:

– A supported version of one of the following (including a toolchain-specific Quickstart

guide):

• Keil™ RealView® Microcontroller Development Kit (MDK-ARM)

• IAR Embedded Workbench

• Code Sourcery GCC development tools

• Code Red Technologies development tools

• Texas Instruments’ Code Composer Studio™ IDE

– Complete documentation

Stellaris® LM3S6965 Evaluation Board

– Quickstart application source code

– Stellaris® Firmware Development Package with example source code

Evaluation Board Specifications

Board supply voltage: 4.37–5.25 Vdc from USB connector

Boar d su pp ly curre nt : 250 mA typ (fully active, CPU at 50 MHz)

Break-out power output: 3.3 Vdc (60 mA max), 15 Vdc (15 mA max)

Dimensions: 4.0” x 2.45” x 0.7” (LxWxH)

RoHS status: Compliant

Features of the LM3S6965 Microcontroller

32-bit RISC performance using ARM® Cortex™-M3 v7M architecture

– 50-MHz operation

– Hardware-division and single-cycle-multiplication

– Integrated Nested Vectored Interrupt Controller (NVIC)

– 42 interrupt channels with eight priority levels

256 KB single-cycle Flash

64 KB single-cycle SRAM

Four general-purpose 32-bit timers

Integrated Ethernet MAC and PHY

Three fully programmable 16C550-type UARTs

Four 10-bit channels (inputs) when used as single-ended inputs

January 6, 2010 9

Page 10

Features of the LM3S6965 Microcontroller

Two independent integrated analog comparators

Two I

2

C modules

Three PWM generator blocks

– One 16-bit counter

– Two comparators

– Produces two independent PWM signals

– One dead-band generator

Two QEI modules with position integrator for tracking encoder position

0 to 42 GPIOs, depending on user configuration

On-chip low drop-out (LDO) voltage regulator

10 January 6, 2010

Page 11

CHAPTER 2

Hardware Description

In addition to a microcontroller, the Stellaris LM3S6965 evaluation board includes a range of useful

peripherals and an integrated ICDI. This chapter describes how these peripherals operate and

interface to the MCU.

LM3S6965 Microcontroller

Device Overview

The heart of the EVB is a Stellaris LM3S6965 ARM Cortex-M3-based microcontroller. The

LM3S6965 offers 256 KB Flash memory, 50-MHz operation, an Ethernet controller, and a wide

range of peripherals. Refer to the LM3S6965 data sheet (order number DS-LM3S6965) for

complete device details.

The LM3S6965 microcontroller is factory programmed with a quickstart demo program. The

quickstart program resides in the LM3S6965 on-chip Fl ash memory and runs each time power is

applied, unless the quickstart has been replaced with a user progr am.

Ethernet

A key feature of the LM3S6965 microcontroller is its fully integrated Ethernet controller. Only a

RJ45 jack with integrated magnetics and a few passive components are needed to complete the

10/100baseT interface. The RJ45 jack incorporates LEDs that indicate traffic and link status.

These are automatically managed by on-chip microcontroller hardware. Alternatively, the LEDs

can be software controlled by configuring those pins as general-purpose outputs.

Clocking

Reset

The LM3S6965 supports automatic MDI/MDI-X so the EVB can connect directly to a network or to

another Ethernet device without requiring a cross-over cable.

The LM3S6965 microcontroller has four on-chip oscillators, three are implemented on the EVB. A

8.0-MHz crystal completes the LM3S6965’s main internal clock circuit. An intern al PLL, configured

in software, multiples this clock to 50-MHz for core and peripheral timing.

A small, 25-MHz crystal is used by the LM3S6965 microcontroller for Ethernet physical layer

timing and is independent of the main oscillator.

The LM3S6965 microcontroller shares its external reset input with the OLED display. In the EVB,

reset sources are gated through the CPLD, though in a typical application a simple wired-OR

arrangement is sufficient.

Reset is asserted (active low) under any one of three conditions:

Power-on reset

Reset push switch SW1 held down

Internal debug mode—By the USB device controller (U4 FT2232) when instructed by

debugger

January 6, 2010 11

Page 12

Hardware Description

Power Supplies

The LM3S6965 is powered from a +3.3-V supply. A low drop-out (LDO) regulator regulates +5-V

power from the USB cable to +3.3-V. +3.3-V power is available for powering external circuits.

A +15-V rail is available when the OLED display is active. The speaker and OLED display

boost-converter operate directly from the +5-V rail.

Debugging

Stellaris microcontrollers support programming and debugging using either JTAG or SWD. JTAG

uses the signals TCK, TMS, TDI, and TDO. SWD requires fewer signals (SWCLK, SWDIO, and,

optionally, SWO, for trace). The debugger determines which debug protocol is used.

Debugging Modes

The LM3S6965 evaluation board supports a range of hardware debugging configurations.

Table 2-1 summarizes these configurations.

Table 2-1. Stellaris LM3S6965 Evaluation Board Hardware Debugging Configurations

Mode Debug Function Use Selected by

1 Internal ICDI Debug on-board LM3S6965

2 ICDI out to JTAG/SWD

header

3 In from JTAG/SWD header For users who prefer an

Modes 2 and 3 automatically detect the presence of an exter nal deb ug cable . When the d ebugg er

software is connected to the EVB's USB controller, the EVB automatically selects Mode 2 and

illuminates the red Debug Out LED.

Debug In Considerations

Debug Mode 3 supports evaluation boa rd debug ging using an external d ebug interface. Mode 3 is

automatically selected when a device such as a Segger J-Link or Keil ULINK is connected.

Boards marked Revision D or later automatically configure pin 1 to be a 3.3-V reference, if an

external debugger is connected. To determine the revision of your board, locate the product

number on the bottom of the board; for example, EK-LM3S6965-D. The last character of the

product number identifies the board revision.

microcontroller over USB

interface.

The EVB is used as a USB to

SWD/JTAG interface to an

external target.

external debug interface

(ULINK, JLINK, etc.) with the

EVB.

Default mode

Connecting to an external

target and starting debug

software. The red Debug Out

LED will be ON.

Connecting an external

debugger to the JTAG/SWD

header.

A configuration or board-level change may be necessary when using an external debug interface

with revisions A through C of this evaluation board. Because the evaluation board supports both

debug out and debug in modes, pin 1 of the 20-pin JTAG/SWD header is, by default, not

connected to +3.3 V. Consequently, devices requiring a voltage o n pin 1 to p ower their line buffers

may not work.

Two solutions exist. Some debugger interfaces (such as ULINK) have an internal power jumper

that, in this case, should be set to internal +3.3-V power. Refer to debugger interface

12 January 6, 2010

Page 13

documentation for full details. However, if your debugger interface does not have a selectable

power source, it may be necessary to inst a ll a 0-Ω re sistor on th e e v aluatio n b oar d to route p ower

to pin 1. Refer to the schematics and board drawing in the appendix of this manual for the location

of this resistor.

USB Device Controller Functions

Device Overview

An FT2232 device from Future Technology Devices International Ltd manages USB-to-serial

conversion. The FT2232 is factory configured to implement a JT AG/SWD po rt (synchronous serial)

on channel A and a Virtual COM Port (VCP) on channel B. This feature allows two simultaneous

communications links between the host computer an d the t ar get device using a single USB cable .

Separate Windows drivers for each function are provided on the Document atio n and Sof tware CD.

A small serial EEPROM holds the FT2232 configuration data. The EEPROM is not accessible by

the LM3S6965 microcontroller.

For full details on FT2232 operation, go to www.ftdichip.com.

USB to JTAG/SWD

The FT2232 USB device performs JT AG/SWD serial operations under th e control of the debugger.

A CPLD (U2) multiplexes SWD and JTAG functions and, when working in SWD mode, provides

direction control for the bidirectional data line.

Stellaris® LM3S6965 Evaluation Board

Virtual COM Port

The Virtual COM Port (VCP) allows Windows applications (such as HyperTerminal) to

communicate with UART0 on the LM3S6965 over USB. Once the FT2232 VCP driver is installed,

Windows assigns a COM port number to the VCP channel.

Serial Wire Out

The evaluation board supports the Cortex-M3 serial-wire output (SWO) trace capabilities. Under

debugger control, the CPLD can route the SWO datastream to the virtual communication port

(VCP) transmit channel. The debugger can then decode and interpret the trace information

received from the VCP. The normal VCP connection to UART0 is interrupted when using SWO. Not

all debuggers support SWO. Refer to the S tellaris LM 3S6965 dat a sheet for a dditional infor mation

on the trace port interface unit (TPIU).

Organic LED Display

The EVB features an organic LED (OLED) graphics display with 128 x 96 pixel resolution. OLED is

a new technology that offers many advantages over LCD display technology.

Features

RiT P14201 series display

128 colu mn s by 96 row s

High-contrast (typ. 500:1)

Excellent brightness (120 cd/m

2

)

Fast 10 us response

January 6, 2010 13

Page 14

Hardware Description

Control Interface

The OLED display has a built-in controller IC with synchronous serial and parallel interfaces.

Synchronous serial (SSI) is used on the EVB as it requires fewer microcontroller pins. Data cannot

be read from the OLED controller; only one data line is necessary. Note that the SSI port is shared

with the microSD card slot. The Stellaris® Firmware Development Package (included on the

Documentation and Software CD) contains complete drivers with source-code for the OLED

display.

Power Supply

A +15-V supply is needed to bias the OLED display. A FAN5331 device from Fairchild combines

with a few external components to complete a boost converter. When the OLED display is

operating, a small amount of power can be drawn from the +15-V rail to power other devices.

Design Guidelines

The OLED display has a lifetime of about 13,000 hours. It is also prone to degradation due to

burn-in, similar to CRT and plasma displays. The quickstart application includes both a screen

saver and a power-down mode to extend display life. These factors should be considered when

developing EVB applications that use the OLED display.

When using the EVB as an in-circuit debug interface (ICDI), the OLED display is held in reset to

reduce power consumption and eliminate display wear-out.

Further Reference

For additional information on the RiT OLED display, visit www.ritekdisplay.com.

Other Peripherals

Speaker

A small, magnetic audio transducer connects through a MOSFET to PD1/PWM1, allowing a range

of options for generating simple and complex tones. Use of the +5-V rail reduces switching noise

on the +3.3-V rail.

MicroSD Card Slot

Removable Flash cards are an ideal media for storing data such as web p age content. Th e source

code on the CD includes example code for reading data from standard FAT formatted SD cards.

All data and control transactions use the SD card’s SPI mode. Note that the SD card specification

does not require that a card supports the SPI mode, but most cards do so in practice. Cards from

several vendors have been used with the EVB.

MicroSD cards are very small and require careful handling. the SD card slot on the EVB is a pushpush type (push to insert; push again to eject).

Note: To avoid damage, remove power before inserting or removing cards.The EVB does not

implement SD card power control.

Push Switches

The EVB has five general-purpose input switches. Four are arranged in a navigation-style

configuration. The fifth functions as a Select switch.

14 January 6, 2010

Page 15

User LED

A user LED (LED3) is provided for general use. The LED is connected to PC5/CCP1, allowing the

option of either GPIO or PWM control (brightness control). Refer to the Quickstart Application

source code for an example of PWM control.

Bypassing Peripherals

Excluding Ethernet, the EVB’s on-board peripheral circuits require 16 GPIO lines. Two additional

GPIO lines are assigned to Ethernet LEDs. Th is leaves 20 GPIO lines and 4 ADC channels

immediately available for connection to external circuits. If an application requires more GPIO

lines, the on-board hardware can be disconnected. The EVB is populated with 16 jumper links,

which can be cut with a knife to isolate on-board hardware. The pro cess can be reversed by

installing 0603- 0-ohm chip resistors.

Important: The quickstart application will not run if one or more jumpers are removed.

Table 2-2. Isolating On-Board Hardware

MCU Pin EVB Function To Isolate, Remove...

Pin 26 PA0/U0RX Virtual COM port receive JP1

Pin 27 PA1/U0TX Virtual COM port transmit JP2

Stellaris® LM3S6965 Evaluation Board

Pin 10 PD0/IDX0 SD card chip select JP3

Pin 11 PD1/PWM1 Sound JP4

Pin 30 PA4/SSI0RX SD card data out JP5

Pin 31 PA5/SSI0TX SD card and OLED display data in JP6

Pin 28 PA2/SSI0CLK SD card and OLED display clock JP7

Pin 22 PC7/PHB0 OLED display data/control select JP8

Pin 29 PA3/SSI0FSS OLED display chip select JP9

Pin 73 PE1/PWM5 Down switch JP10

Pin 74 PE2/PHB1 Left switch JP11

Pin 72 PE0/PWM4 Up switch JP12

Pin 75 PE3/PHA1 Right switch JP13

Pin 61 PF1/IDX1 Select switch JP14

Pin 47 PF0/PWM0 User LED JP15

Pin 23 PC6/CCP3 Enable +15 V JP16

Interfacing to the EVB

An array of accessible I/O signals makes it easy to interface the EVB to external circuits. All

LM3S6965 I/O lines (except those with both JTAG and SWD functions) are brought out to 0.1”

pitch pads. For quick reference, silk-screened labels on the PCB show primary pin functions.

Table B-1 on page 25 has a complete list of I/O signals as well as recommended connectors.

January 6, 2010 15

Page 16

Hardware Description

Evaluation Board

Target

Board

Stellaris

MCU

Target

Cable

`

USB

PC with IDE/

debugger

Stellaris

MCU

TC K/SWC LK by pas s es t he

on- board m ic roc ont roller

JT AG or SWD c onnec t s t o t he

ext ernal m icroc on troller

Connec t ing Pin 18 t o GN D s ets

ext ernal debug m ode

Most LM3S6965 I/O signals are +5-V tolerant. Refer to the LM3S6965 data sheet for detailed

electrical specifications.

Using the In-Circuit Debugger Interface

The Stellaris LM3S6965 Evaluation Kit can operate as an In-Circuit Debugger Interface (ICDI).

ICDI acts as a USB to the JTAG/SWD adaptor, allowing debugging of any external target board

that uses a Stellaris microcontroller. See “Debugging Modes” on page 12 for a description of how

to enter Debug Out mode.

Figure 2-1. ICD Interface Mode

The debug interface operates in either Serial-Wire Debug (SWD) or full JTAG mode, depending on

the configuration in the debugger IDE.

The IDE/debugger does not distinguish between the on-EVB Stellaris microcontroller and an

external Stellaris microcontroller. The only requirement is that the correct Stellaris device is

selected in the project configuration.

16 January 6, 2010

Page 17

APPENDIX A

Schematics

This section contains the schematics for the LM3S6965 evaluation board:

LM3S6965 Micro and 10/100 Ethernet on page 18

OLED Display, Switches, and Audio on page 19

USB, Debugger Interfaces, and Power on page 20

JTAG Logic with Auto Mode Detect and Hibernate on page 21

January 6, 2010 17

Page 18

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

3/26/2008 1 3

Drawing Title:

Page Title:

Size

Ethernet Evaluation Board

LM3S6965 Micro and 10/100 Ethernet

B

D

1

Revision Date Description

History

18PF

C8

18PF

C9

INT_TCK

TMS/SWDIO

PC2/TDI

PC3/TDO

ADC3

ADC2

ADC1

ADC0

MCURSTn

6

5

8

4

2

3

1

7

1CT:1

TX+

TXRX+

RX-

1CT:1

Y+

Y-

G+

G-

3

8

7

4

5

6

11

12

2

1

GL

GR

9

10

NC

GND

P4

J3011G21DNL

R3

49.9

+3.3V

C7

0.01UF

R2

49.9

R6

49.9R749.9

C3

0.1UF

+3.3V

C4

0.1UF

+3.3V

C6

10pF

C1

10pFC210pF

C18

0.01UF

C13

0.01UF

C14

0.01UF

C16

0.1UF

C15

0.1UF

C12

0.1UF

+3.3V

+3.3V

R4

330

PA1/U0Tx

PA2/SSI0CLK

PA3/SSI0FSS

PA4/SSI0RX

PA5/SSI0TX

PA0/U0Rx

R1

10K

+3.3V

Stellaris Microcontroller

R5

330

+3.3V

+3.3V

PA6/I2CSCL

PA7/I2CSDA

TMS/SWDIO

PC2/TDI

PC3/TDO

PC4/PhA0

PC5/C1+/C0o

PC6/CCP3

PC7/PhB0

PE0/PWM4

PE1/PWM5

PE2/PhB1

PE3/PhA1

PG0/U2RX

PG1/U2TX

PF1/IDX1

PF0/PWM0

PD7/CCP1

PD6/FAULT

PD5/CCP2

PD4/CCP0

PD3/U1TX

PD2/U1RX

PD1/PWM1

PD0/IDX0

PB7/TRST

PB6/C0+

PB5/C1-

PB4/C0-

PB3/I2CSDA

PB2/I2C0SCL

PB1/PWM3

PB0/PWM2

PF2/LED1

PF3/LED0

C19

0.1UF

C20

4.7UF

C17

4.7UF

Ethernet 10/100baseT

1 2

Y1

25.00MHz

JP1

JP2

PA0/U0Rx

PA1/U0Tx

VCP_RX

VCP_TX

JP7

JP9

SSICLK

OLEDCSn

PA2/SSI0CLK

PA3/SSI0FSS

JP6

SSITX

PA5/SSI0TX

On-board Peripheral Si gn als

free GPIO lines as required.

JP14

SELECT_SWn

JP15

LED

JP12

UP_SWn

JP10

DOWN_SWn

JP11

JP13

LEFT_SWn

RIGHT_SWn

Jumpers can be cut to

JP4

SOUND

JP5

SSIRX

PA4/SSI0RX

OSC32IN

OSC32OUT

JP8

OLEDDC

JP3

CARDCSn

PF1/IDX1

PF0/PWM0

PE0/PWM4

PE1/PWM5

PE2/PhB1

PE3/PhA1

PD1/PWM1

PD0/IDX0

PD4/CCP0

PD6/FAULT

PC7/PhB0

C5

10pF

12

3334 3635

59 60

ADC3

ADC1

PD0/IDX0

PD2/U1RX

PG1/U2TX

PC7/PhB0

PC5/C1+/C0o

PA1/U0Tx

PA3/SSI0FSS

PA5/SSI0TX

PA7/I2CSDA

PB4/C0PD5/CCP2

PD7/CCP1

ADC0

ADC2

PD1/PWM1

PD3/U1TX

PG0/U2RX

PC6/CCP3

PC4/PhA0

PA0/U0Rx

PA2/SSI0CLK

PA4/SSI0RX

PA6/I2CSCL

+3.3V

+5V

+15V

PB5/C1- PB6/C0+

PB7/TRST PC2/TDI

PC3/TDO PE3/PhA1

PE2/PhB1

PE0/PWM4 PE1/PWM5

PB2/I2C0SCL PB3/I2CSDA

PB1/PWM3

PF1/IDX1 PB0/PWM2

PF3/LED0 PF2/LED1

OSC32OUT

OSC32IN

+3.3V

PF0/PWM0

I/O Break-out Headers

R33

10K

+3.3V

1 2

Y3

8.00MHz

18PF

C40

18PF

C41

A 5/12/07 First Production Release

B 6/29/07 Improve SWD out feature, add SWO support, 1-bit

C 8/09/07 Change to RiT 128x96 OLED display

OLED display option.

JP16

EN+15V

PC6/CCP3

Install R271/25/08

+3.3V

R35

12.4K

PA0/U0RX

26

PA1/U0TX

27

PA2/SSI0CLK

28

PA3/SSI0FSS

29

PA4/SSI0RX

30

PA5/SSI0TX

31

PC0/TCK/SWCLK

80

PC1/TMS/SWDIO

79

PC2/TDI

78

PC3/TDO/SWO

77

PC4/PhA0

25

PC5/C1+/C0o

24

PC6/CCP3

23

PC7/PhB0

22

PD0/IDX0

10

PD1/PWM1

11

PD2/U1RX

12

PD3/U1TX

13

PD4/CCP0

95

PD5/CCP2

96

PD6/FAULT

99

PD7/CCP1

100

GND

9

GND

15

GND

21

GND

33

RST

64

LDO

7

MOSCin

48

MOSCout

49

PB0/PWM2

66

PB1/PWM3

67

PB2/I2C0SCL

70

PB3/I2C0SDA

71

PB4/C0-

92

PB5/C1-

91

PB6/C0+

90

PB7/TRST

89

PE0/PWM4

72

PE1/PWM5

73

PE2/PhB1

74

PE3/PhA1

75

ADC3

6

ADC2

5

PA6/I2C1SCL

34

PA7/I2C1SDA

35

ADC1

2

ADC0

1

PF0/PWM0

47

PF1/IDX1

61

PF2/LED1

60

PF3/LED0

59

MDIO

58

TXON

46

TXOP

43

ERBIAS

41

PG0/U2RX

19

PG1/U2TX

18

XTALNPHY

17

XTALPPHY

16

GND

42

RXIP

40

RXIN

37

VDD33

36

GND

86

GND

85

VDD33

84

VDD33

83

AVDD

3

AVDD

98

AGND

97

AGND

4

VDD33

8

VDD33

20

VDD33

32

VDD33

44

VDD33

56

VDD33

68

VDD33

81

VDD33

93

GND

39

GND

45

GND

54

GND

57

GND

63

GND

69

GND

82

GND

87

GND

94

VDD25

14

VDD25

38

VDD25

62

VDD25

88

WAKE

50

HIB

51

XOSC0

52

XOSC1

53

VBAT

55

CMOD0

65

CMOD1

76

U1

LM3S6965

12.4K 1% resistor required on Pin 41 for

compatibility with future LM3S6965 revisions.

See Product Change Notification.

Add R35 for future compatibility.3/25/08D

Tie R6/R7 to +3.3V. Add TVCC con tr o l.

Schematic page 1

Page 19

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

3/26/2008 2 3

Drawing Title:

Page Title:

Size

Ethernet Evaluation Board

OLED Display, Switches and Audio

B

D

2

R18

330

DBGOUTLED

Reset

SW1

SW-B3S1000

SELECT_SWn

UP_SWn

DOWN_SWn

LEFT_SWn

RIGHT_SWn

RESET_SWn

R15

10K

+3.3V

Select

Up

Down

Left

Right

Debug Out

R16

330

LED

Status

R20

330

Power

R9

2.2

+5V

Q1

NDS331N

R12

10K

SOUND

Speaker Circuit

Status LEDs

User Switches

+3.3V

D1

MBR0520

SW2

SW-B3S1000

SW3

SW-B3S1000

SW4

SW-B3S1000

SW5

SW-B3S1000

SW6

SW-B3S1000

microSD Card Slot

1

2

3

4

5

6

7

8

9

101112

P3

2908-05WB-MG

+3.3V

C28

0.1UF

+3.3V

CARDCSn

SSITX

SSICLK

SSIRX

R17

10K

R19

10K

+3.3V

+3.3V

1

2

BZ1

NFT-03A

LED2

Green

LED3

Red

LED4

Green

C30

OMIT

R14

200K

SSITX

SSICLK

+3.3V

128x96 OLED Graphics Display

C26

4.7UF

MCURSTn

OLEDDC

+15V

OLEDCSn

C23

0.1UF

C21

0.1UF

RGS13128096WH000

NC

1

VCIR

2

VCOMH

3

LVSS

4

VSS

5

BS1

6

BS2

7

IREF

8

CSn

9

RESn

10

D/Cn

11

R/Wn

12

E

13

D0/SCLK

14

D1/SDIN

15

D2

16

D3

17

D4

18

D5

19

D6

20

D7

21

VDDIO

22

VDD

23

VCC

24

NC

25

U2

OLED-RIT-128X96

+15V 50mA Power Supply for OLED Display

+15V

FB

3

VIN

5

SHDNn4GND

2

SW

1

U7

FAN5331

+5V

C24

4.7UF

C25

4.7UF

D2

MBR0520

0.1UF

C22

120pF

C27

R13

200K

R11

17.8K

EN+15V

R10

10K

10uH

L1

NR4018T100M

+3.3V

Schematic page 2

Page 20

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Document Number:

RevSheetDate:

of

3/26/2008 3 3

Drawing Title:

Page Title:

Size

Ethernet Evaluation Board

USB, Debugger Interfaces and Power

B

D

3

FB1

60ohm @ 100 MHz

GND

18

GND

25

GND

34

ADBUS0

24

ADBUS1

23

ADBUS2

22

ADBUS3

21

ADBUS4

20

ADBUS5

19

ADBUS6

17

ADBUS7

16

ACBUS0

15

ACBUS1

13

ACBUS2

12

ACBUS3

11

BDBUS0

40

BDBUS1

39

BDBUS2

38

BDBUS3

37

BDBUS4

36

BDBUS5

35

BDBUS6

33

BDBUS7

32

BCBUS0

30

BCBUS1

29

BCBUS2

28

BCBUS3

27

SI/WUA

10

SI/WUB

26

GND

9

AGND

45

VCC

3

VCC

42

VCCIOA

14

VCCIOB

31

AVCC

46

PWREN#

41

XTOUT

44

XTIN

43

EECS

48

EESK

1

EEDATA

2

TEST

47

RESET#

4

RSTOUT#

5

3V3OUT

6

USBDM

8

USBDP

7

U4

FT2232D

+3.3v

USB+5V

R21 27

R22 27

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

P2

Header 10X2

+3.3V

+3.3V

DBG_JTAG_EN

R24

10K

R25

1.5K

R23

1.5K

R30

330

+5V

+5V

+5V+5V

XTDI

XTMS

TCK

TDI/DI

TDO/DO

TMS/OUTEN

+3.3V+5V

0.1UF

C37

0.1UF

C33

0.1UF

C34

0.1UF

C35

0.1UF

C36

0.1UF

C31

USB Device Controller

Channel A : JTAG / SW Debug

Channel B : Virtual Com Port

USB +5V to +3.3V 500mA Power Supply

R31

27

R29

27

R26

27

XTCK

R28

27

VCP_RX

VCP_TX

TCK/SWCLK

PC2/TDI

PC3/TDO

TMS/SWDIO

C32

0.01UF

5V D- D+ ID G

123

475

6

P1

54819-0519

+3.3V

SRSTN

TARGETCABLEn

XTDO

R27

27

TP4

TP3

TP2

TP1

TP5

TP6

+3.3V

PLD JTAG TEST POINTS

PLD_TCK

PLD_TMS

PLD_TDI

PLD_TDO

VOUT

4

SENSE

5

VIN2

6

GND

2

NC

3

GND

7

VIN1

1

U6

LP8345ILD-3.3

USB+5V

R32

4.7K

+3.3v

Debug Interface Logic

JP18

PC3/TDO

TCK/SWCLK

TMS/SWDIO

PC2/TDI

C38

4.7UF

C39

4.7UF

JTAG/SWD Interface

Input/Output

USB Interface

TDI

1

A5

2

A6

3

A7

4

GND (Bank 0)5VCCO (Bank 0)

6

A8

7

A9

8

A10

9

A11

10

TCK

11

VCC

12

GND

13

A12

14

A1315A1416A15

17

CLK1/I18CLK2/I

19

B0

20

B1

21

B2

22

B3

23

B4

24

TMS

25

B5

26

B6

27

B7

28

GND (Bank 1)29VCCO (Bank 1)

30

B8

31

B9

32

B10

33

B11

34

TDO35VCC

36

GND

37

B12

38

B1339B1440B15/GOE1

41

CLK3/I42CLK0/I

43

A0/GOE0

44

A1

45

A2

46

A3

47

A4

48

Bank 0 Bank 1

U3

LC4032V-75TN48C

+3.3V

PC2/TDI

MCURSTn

DBGOUTLED

TARGETCABLEn

PC3/TDO

RESET_SWn

0.1UF

C29

+3.3V

TMS/SWDIO

TCK/SWCLK

Omit

JP17

USBSH

CS

1

SK

2

DI

3

DO4GND

5

ORG

6

NC

7

VCC

8

1K 64X16

U5

CAT93C46

1 2

Y2

6.00MHz

18PF

C10

18PF

C11

PB7/TRST

0.1UF

C42

R34

4.7K

+3.3V

INT_TCK

SWO_EN

VCP_TX_SWO

MODE

MODE is reserved

for future use.

R8

4.7K

+3.3V

XVCC

Schematic page 3

Page 21

A B C D E F G H

A B C D E F G H

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

I102

I100

C

DQ

I96

I105

I104

I36

I35

I18

A

B

S

I89

A

B

S

I85

A

B

S

I17

A

B

S

I114

15

I107

38

I106

33

I86

44

I2

21

I70

7

I42

31

I90

34

I3

47

I6

46

I92

32

I16

24

I108

16

I13

26

I15

9

I74

14

I91

10

I7

45

I37

3

I5

4

I4

48

I87

41

I8

40

I115

I9

I99

I111

I112

I95

I109

I20

FTDI_DBG

DBGOUT

VCP_TX

ITCK

SWO_EN

FTDI_TCK XTCK

FTDI_TDI_DO U0TX

XTDO

FTDI_TDO_DI

JTAGEN

FTDI_TMS

XTDI

JTAGEN

FTDI_DBG

FTDIJTAGEN

SWDEN

FTDI_SRSTn

XTMS

FTDI_DBG

DBGOUT

DBGLED

INTDBG

TEST

TRSTn

RSTSW

MCURSTn

RC

EXTCABLEn TVCC

HIBn

DRVEN

Sept 28, 2007

JTAG Logic with Auto Mode Detect, Hibernate and TVcc Control

LM

3S6965 Evaluation Kit

Texas Instruments, Inc.

Schematic page 4

Page 22

22 January 6, 2010

Page 23

APPENDIX B

Connection Details

This appendix contains the following sections:

Component Locations

Evaluation Board Dimensions

I/O Breakout Pads

ARM Target Pinout

Component Locations

Figure B-1. Component Locations

January 6, 2010 23

Page 24

Evaluation Board Dimensions

Evaluation Board Dimensions

Figure B-2. Evaluation Board Dimensions

I/O Breakout Pads

The LM3S6965 EVB has 44 I/O pads, 14 power pads, and 2 crystal connections, for a total of 60

pads. Connection can be made by soldering wires directly to these pads, or by using 0.1” pitch

headers and sockets.

24 January 6, 2010

Page 25

Stellaris® LM3S6965 Evaluation Kit

Note: In Table B-2, an asterisk (*) by a signal name (also on the EVB PCB) indicates the signal is

normally used for on-board functions. Normally, you should cut the associated jumper (JP1-15)

before using an assigned signal for external interfacing.

Table B-1. I/O Breakout Pads

Description

PD4/CCP0 34 33 PB4/C0- +12 V 35 36 GND

PD6/FAULT 32 31 PD5/CCP2 PB5/C1- 37 38 PB6/C0+

GND 30 29 PD7/CCP1 PB7/TRST

ADC1 28 27 ADC0 PC3/TDO*4142PE3/PHA1*

ADC3 26 25 ADC2 PE2/PHB1* 43 44 GND

IDX0* 24 23 GND PE0/PWM4* 45 46 PE1/PWM5*

PD2/U1RX 22 21 PD1/PWM1* PB2/SCL0 47 48 PB3/SDA0

PG1/U2TX 20 19 PD3/U1TTX PB1/PWM3 49 50 GND

PC7/PHB0*1817PG0/U2RX PF1/IDX1* 51 52 PB0/PWM2

PC5/C1+ 16 15 PC6/CCP3* PF3/LED0 53 54 PF2/LED1

GND 14 13 PC4/PHA0 GND 55 56 OSC32

+3.3 V 12 11 PA0/U0RX* GND 57 58 OSC32

PA1/U0TX*109PA2/SSICLK* PF0/PWM0* 59 60 +3.3 V

PA3/SFSS*87PA4/SSIRX*

Pad

No.

Pad

No.

Description Description

Pad

No.

39 40 PC2/TDI*

Pad

No.

Description

PA5/SSITX*6 5PA6/SCL1

PA7/SDA1 43GND

GND 21+5V

Recommended Connectors

Connection can be made by soldering wires directly to pads or using 0.1” pitch headers and

sockets.

Table B-2. Recommended Connectors

Pins 1-34 (2 x 17 way) PCB Socket Sullins PPPC172LFBN-RC Digikey S7120-ND

Cable Socket 3M 89134-0101 Digikey MKC34A-ND

Pin Header Sullins PEC17DAAN Digikey S2012E-17-ND

Pins 35-06 (2 x 13 way) PCB Socket Sullins PPPC132LFBN-RC Digikey S7116-ND

Cable Socket 3M 89126-0101 Digikey MKC26A-ND

Pin Header Sullins PEC13DAAN Digikey S2012-13-ND

January 6, 2010 25

Page 26

ARM Target Pinout

ARM Target Pinout

In ICDI input and output mode, the Stellaris LM3S6965 Evaluation Kit supports ARM’s standard

20-pin JTAG/SWD configuration. The same pin configuration can be used for debugging over

Serial Wire Debug (SWD) and JTAG interfaces. The debugger software, running on the PC,

determines which interface protocol is used.

The Stellaris target board should have a 2x10 0.1” pin header with signals as indicated in

Table B-3. This applies to both an external Stellaris MCU target (Debug output mode) and to

external JTAG/SWD debuggers (Debug input mode).

Table B-3. 20-Pin JTAG/SWD Configuration

Function Pin Pin Function

VCC 12nc

nc 3 4 GND

TDI 56GND

TMS 78GND

TCK 910GND

NC 11 12 GND

TDO 13 14 GND

nc 15 16 GND

nc 17 18 GND

nc 19 20 GND

ICDI does not control RST

implemented as commands over JTAG/SWD, so these signals are not necessary.

It is recommended that connections be made to all GND pins; however, both targets and external

debug interfaces must connect pin 18 and at least one other GND pin to GND.

References

In addition to this document, the following references are included on the Stellaris® LM3S6965

Evaluation Kit documentation CD-ROM and are also available for download at www.ti.com/

stellaris:

Stellaris LM3S6965 Evaluation Kit Quickst art Guide for appropriate tool kit (s ee “Evaluation Kit

Contents,” on page 10)

(device reset) or TRST (test reset) signals. Both reset functions are

Stellaris LM3S6965 Read Me First for the CAN Evaluation Kit

StellarisWare® Driver Library, Order number SW-DRL

StellarisWare® Driver Library User’s Manual, publication number SW-DRL-UG

Stellaris LM3S6965 Data Sheet, publication DS-LM3S6965

26 January 6, 2010

Page 27

Stellaris® LM3S6965 Evaluation Kit

Additional references include:

Future Technology Devices Incorporated FT2232C Datasheet

Information on development tool being used:

– RealView MDK web site, www.keil.com/arm/rvmdkkit.asp

– IAR Embedded Workbench web site, www.iar.com

– Code Sourcery GCC development tools web site,

www.codesourcery.com/gnu_toolchains/arm

– Code Red Technologies developm en t to ols we b site, www.code-red-tech.com

– Texas Instruments’ Code Composer Studio™ IDE web site, www.ti.com/ccs

January 6, 2010 27

Loading...

Loading...