Page 1

TEXAS INSTRUMENTS-ADVANCE INFORMATION

Stellaris® LM3S1R21 Microcontroller

DATA SHEET

DS-LM3S1R21-6790

Copyright © 2007-2010 Texas Instruments

Incorporated

Page 2

Copyright

Copyright © 2007-2010 Texas Instruments Incorporated All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments

Incorporated. ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the

property of others.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specications

are subject to change without notice.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor

products and disclaimers thereto appears at the end of this data sheet.

Texas Instruments Incorporated

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

http://www-k.ext.ti.com/sc/technical-support/product-information-centers.htm

Texas Instruments-Advance Information

February 09, 20102

Page 3

Stellaris® LM3S1R21 Microcontroller

Table of Contents

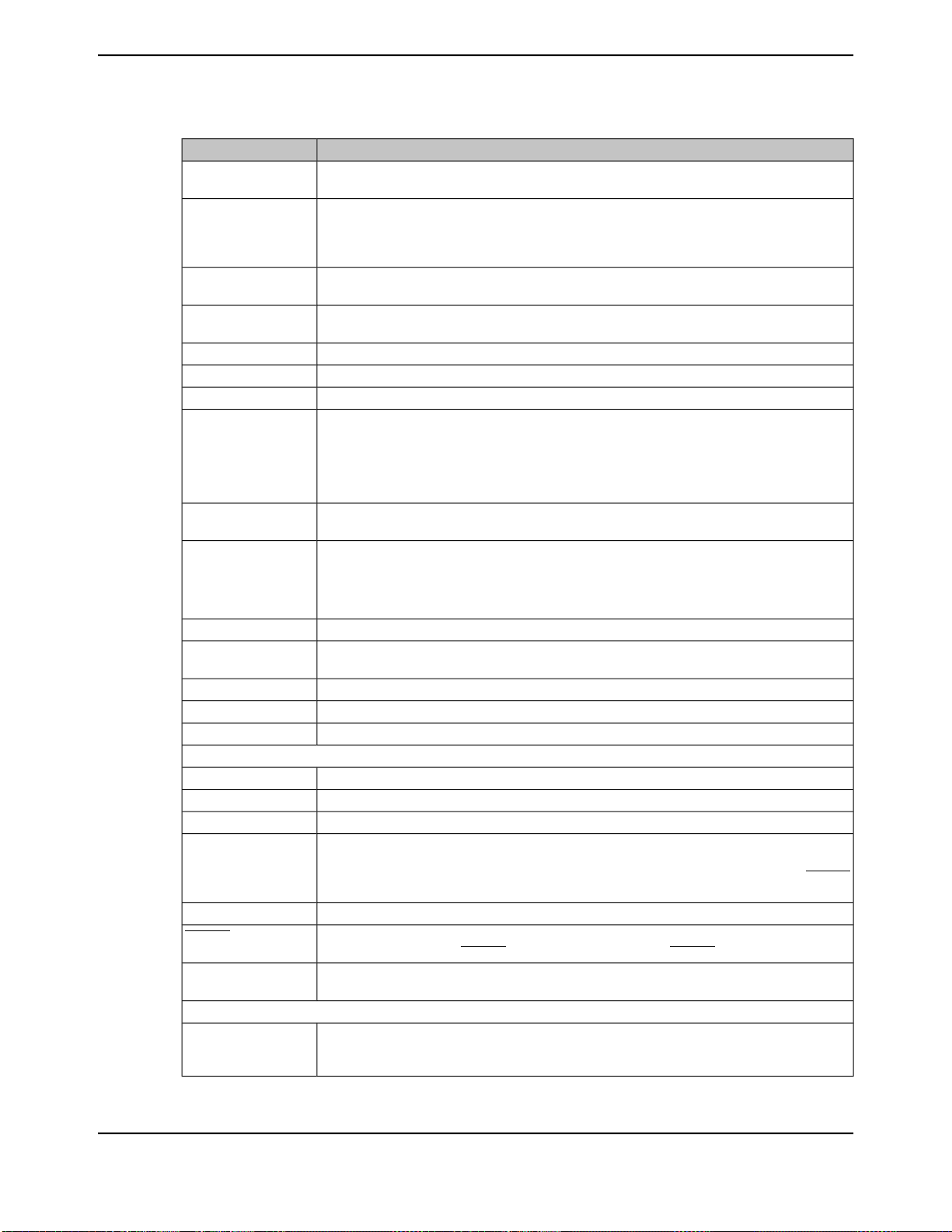

Revision History .............................................................................................................................23

About This Document .................................................................................................................... 27

Audience .............................................................................................................................................. 27

About This Manual ................................................................................................................................ 27

Related Documents ............................................................................................................................... 27

Documentation Conventions .................................................................................................................. 27

1 Architectural Overview .......................................................................................... 30

1.1 Functional Overview ...................................................................................................... 32

1.1.1 ARM Cortex™-M3 ......................................................................................................... 32

1.1.2 On-Chip Memory ........................................................................................................... 34

1.1.3 External Peripheral Interface ......................................................................................... 35

1.1.4 Serial Communications Peripherals ................................................................................ 36

1.1.5 System Integration ........................................................................................................ 39

1.1.6 Analog .......................................................................................................................... 44

1.1.7 JTAG and ARM Serial Wire Debug ................................................................................ 46

1.1.8 Packaging and Temperature .......................................................................................... 47

1.2 Target Applications ........................................................................................................ 47

1.3 High-Level Block Diagram ............................................................................................. 47

1.4 Additional Features ....................................................................................................... 49

1.4.1 Memory Map ................................................................................................................ 49

1.4.2 Hardware Details .......................................................................................................... 49

2 ARM Cortex-M3 Processor Core ........................................................................... 50

2.1 Block Diagram .............................................................................................................. 51

2.2 Functional Description ................................................................................................... 51

2.2.1 Programming Model ...................................................................................................... 51

2.2.2 Serial Wire and JTAG Debug ......................................................................................... 58

2.2.3 Embedded Trace Macrocell (ETM) ................................................................................. 58

2.2.4 Trace Port Interface Unit (TPIU) ..................................................................................... 58

2.2.5 ROM Table ................................................................................................................... 59

2.2.6 Memory Protection Unit (MPU) ....................................................................................... 59

2.2.7 Nested Vectored Interrupt Controller (NVIC) .................................................................... 59

2.2.8 System Timer (SysTick) ................................................................................................. 60

3 Memory Map ........................................................................................................... 63

4 Interrupts ................................................................................................................. 66

5 JTAG Interface ........................................................................................................ 69

5.1 Block Diagram .............................................................................................................. 70

5.2 Signal Description ......................................................................................................... 70

5.3 Functional Description ................................................................................................... 71

5.3.1 JTAG Interface Pins ...................................................................................................... 71

5.3.2 JTAG TAP Controller ..................................................................................................... 73

5.3.3 Shift Registers .............................................................................................................. 73

5.3.4 Operational Considerations ............................................................................................ 74

5.4 Initialization and Configuration ....................................................................................... 76

5.5 Register Descriptions .................................................................................................... 77

Texas Instruments-Advance Information

3February 09, 2010

Page 4

Table of Contents

5.5.1 Instruction Register (IR) ................................................................................................. 77

5.5.2 Data Registers .............................................................................................................. 79

6 System Control ....................................................................................................... 81

6.1 Signal Description ......................................................................................................... 81

6.2 Functional Description ................................................................................................... 81

6.2.1 Device Identification ...................................................................................................... 82

6.2.2 Reset Control ................................................................................................................ 82

6.2.3 Non-Maskable Interrupt ................................................................................................. 86

6.2.4 Power Control ............................................................................................................... 86

6.2.5 Clock Control ................................................................................................................ 87

6.2.6 System Control ............................................................................................................. 93

6.3 Initialization and Configuration ....................................................................................... 95

6.4 Register Map ................................................................................................................ 95

6.5 Register Descriptions .................................................................................................... 96

7 Hibernation Module .............................................................................................. 172

7.1 Block Diagram ............................................................................................................ 173

7.2 Signal Description ....................................................................................................... 173

7.3 Functional Description ................................................................................................. 174

7.3.1 Register Access Timing ............................................................................................... 175

7.3.2 Clock Source .............................................................................................................. 175

7.3.3 Battery Management ................................................................................................... 176

7.3.4 Real-Time Clock .......................................................................................................... 177

7.3.5 Non-Volatile Memory ................................................................................................... 177

7.3.6 Power Control Using HIB ............................................................................................. 177

7.3.7 Power Control Using VDD3ON Mode ........................................................................... 178

7.3.8 Initiating Hibernate ...................................................................................................... 178

7.3.9 Interrupts and Status ................................................................................................... 178

7.4 Initialization and Configuration ..................................................................................... 179

7.4.1 Initialization ................................................................................................................. 179

7.4.2 RTC Match Functionality (No Hibernation) .................................................................... 180

7.4.3 RTC Match/Wake-Up from Hibernation ......................................................................... 180

7.4.4 External Wake-Up from Hibernation .............................................................................. 180

7.4.5 RTC or External Wake-Up from Hibernation .................................................................. 180

7.4.6 Register Reset ............................................................................................................ 181

7.5 Register Map .............................................................................................................. 181

7.6 Register Descriptions .................................................................................................. 182

8 Internal Memory ................................................................................................... 199

8.1 Block Diagram ............................................................................................................ 199

8.2 Functional Description ................................................................................................. 199

8.2.1 SRAM ........................................................................................................................ 200

8.2.2 ROM .......................................................................................................................... 200

8.2.3 Flash Memory ............................................................................................................. 200

8.3 Flash Memory Initialization and Configuration ............................................................... 202

8.3.1 Flash Memory Programming ........................................................................................ 202

8.3.2 32-Word Flash Memory Write Buffer ............................................................................. 203

8.3.3 Nonvolatile Register Programming ............................................................................... 204

8.4 Register Map .............................................................................................................. 205

8.5 Flash Memory Register Descriptions (Flash Control Offset) ............................................ 206

Texas Instruments-Advance Information

February 09, 20104

Page 5

Stellaris® LM3S1R21 Microcontroller

8.6 Memory Register Descriptions (System Control Offset) .................................................. 217

9 Micro Direct Memory Access (μDMA) ................................................................ 233

9.1 Block Diagram ............................................................................................................ 234

9.2 Functional Description ................................................................................................. 234

9.2.1 Channel Assignments .................................................................................................. 235

9.2.2 Priority ........................................................................................................................ 236

9.2.3 Arbitration Size ............................................................................................................ 236

9.2.4 Request Types ............................................................................................................ 236

9.2.5 Channel Configuration ................................................................................................. 237

9.2.6 Transfer Modes ........................................................................................................... 239

9.2.7 Transfer Size and Increment ........................................................................................ 247

9.2.8 Peripheral Interface ..................................................................................................... 247

9.2.9 Software Request ........................................................................................................ 247

9.2.10 Interrupts and Errors .................................................................................................... 248

9.3 Initialization and Configuration ..................................................................................... 248

9.3.1 Module Initialization ..................................................................................................... 248

9.3.2 Configuring a Memory-to-Memory Transfer ................................................................... 248

9.3.3 Configuring a Peripheral for Simple Transmit ................................................................ 250

9.3.4 Configuring a Peripheral for Ping-Pong Receive ............................................................ 251

9.3.5 Configuring Alternate Channels .................................................................................... 254

9.4 Register Map .............................................................................................................. 254

9.5 μDMA Channel Control Structure ................................................................................. 255

9.6 μDMA Register Descriptions ........................................................................................ 262

10 General-Purpose Input/Outputs (GPIOs) ........................................................... 291

10.1 Signal Description ....................................................................................................... 291

10.2 Functional Description ................................................................................................. 296

10.2.1 Data Control ............................................................................................................... 297

10.2.2 Interrupt Control .......................................................................................................... 298

10.2.3 Mode Control .............................................................................................................. 299

10.2.4 Commit Control ........................................................................................................... 299

10.2.5 Pad Control ................................................................................................................. 300

10.2.6 Identification ............................................................................................................... 300

10.3 Initialization and Configuration ..................................................................................... 300

10.4 Register Map .............................................................................................................. 301

10.5 Register Descriptions .................................................................................................. 304

11 External Peripheral Interface (EPI) ..................................................................... 347

11.1 EPI Block Diagram ...................................................................................................... 348

11.2 Signal Description ....................................................................................................... 349

11.3 Functional Description ................................................................................................. 351

11.3.1 Non-Blocking Reads .................................................................................................... 352

11.3.2 DMA Operation ........................................................................................................... 353

11.4 Initialization and Configuration ..................................................................................... 353

11.4.1 SDRAM Mode ............................................................................................................. 354

11.4.2 Host Bus Mode ........................................................................................................... 358

11.4.3 General-Purpose Mode ............................................................................................... 367

11.5 Register Map .............................................................................................................. 375

11.6 Register Descriptions .................................................................................................. 376

Texas Instruments-Advance Information

5February 09, 2010

Page 6

Table of Contents

12 General-Purpose Timers ...................................................................................... 419

12.1 Block Diagram ............................................................................................................ 420

12.2 Signal Description ....................................................................................................... 420

12.3 Functional Description ................................................................................................. 423

12.3.1 GPTM Reset Conditions .............................................................................................. 423

12.3.2 32-Bit Timer Operating Modes ...................................................................................... 424

12.3.3 16-Bit Timer Operating Modes ...................................................................................... 425

12.3.4 DMA Operation ........................................................................................................... 431

12.4 Initialization and Configuration ..................................................................................... 431

12.4.1 32-Bit One-Shot/Periodic Timer Mode ........................................................................... 431

12.4.2 32-Bit Real-Time Clock (RTC) Mode ............................................................................. 432

12.4.3 16-Bit One-Shot/Periodic Timer Mode ........................................................................... 432

12.4.4 16-Bit Input Edge-Count Mode ..................................................................................... 433

12.4.5 16-Bit Input Edge Timing Mode .................................................................................... 433

12.4.6 16-Bit PWM Mode ....................................................................................................... 434

12.5 Register Map .............................................................................................................. 434

12.6 Register Descriptions .................................................................................................. 435

13 Watchdog Timers ................................................................................................. 466

13.1 Block Diagram ............................................................................................................ 467

13.2 Functional Description ................................................................................................. 467

13.2.1 Register Access Timing ............................................................................................... 468

13.3 Initialization and Configuration ..................................................................................... 468

13.4 Register Map .............................................................................................................. 468

13.5 Register Descriptions .................................................................................................. 469

14 Analog-to-Digital Converter (ADC) ..................................................................... 491

14.1 Block Diagram ............................................................................................................ 492

14.2 Signal Description ....................................................................................................... 492

14.3 Functional Description ................................................................................................. 493

14.3.1 Sample Sequencers .................................................................................................... 493

14.3.2 Module Control ............................................................................................................ 494

14.3.3 Hardware Sample Averaging Circuit ............................................................................. 496

14.3.4 Analog-to-Digital Converter .......................................................................................... 496

14.3.5 Differential Sampling ................................................................................................... 498

14.3.6 Internal Temperature Sensor ........................................................................................ 501

14.3.7 Digital Comparator Unit ............................................................................................... 501

14.4 Initialization and Configuration ..................................................................................... 506

14.4.1 Module Initialization ..................................................................................................... 506

14.4.2 Sample Sequencer Configuration ................................................................................. 507

14.5 Register Map .............................................................................................................. 507

14.6 Register Descriptions .................................................................................................. 509

15 Universal Asynchronous Receivers/Transmitters (UARTs) ............................. 565

15.1 Block Diagram ............................................................................................................ 566

15.2 Signal Description ....................................................................................................... 566

15.3 Functional Description ................................................................................................. 568

15.3.1 Transmit/Receive Logic ............................................................................................... 569

15.3.2 Baud-Rate Generation ................................................................................................. 569

15.3.3 Data Transmission ...................................................................................................... 570

15.3.4 Serial IR (SIR) ............................................................................................................. 570

Texas Instruments-Advance Information

February 09, 20106

Page 7

Stellaris® LM3S1R21 Microcontroller

15.3.5 ISO 7816 Support ....................................................................................................... 571

15.3.6 Modem Handshake Support ......................................................................................... 571

15.3.7 LIN Support ................................................................................................................ 573

15.3.8 FIFO Operation ........................................................................................................... 574

15.3.9 Interrupts .................................................................................................................... 574

15.3.10 Loopback Operation .................................................................................................... 575

15.3.11 DMA Operation ........................................................................................................... 575

15.4 Initialization and Configuration ..................................................................................... 576

15.5 Register Map .............................................................................................................. 577

15.6 Register Descriptions .................................................................................................. 578

16 Synchronous Serial Interface (SSI) .................................................................... 627

16.1 Block Diagram ............................................................................................................ 628

16.2 Signal Description ....................................................................................................... 628

16.3 Functional Description ................................................................................................. 629

16.3.1 Bit Rate Generation ..................................................................................................... 630

16.3.2 FIFO Operation ........................................................................................................... 630

16.3.3 Interrupts .................................................................................................................... 630

16.3.4 Frame Formats ........................................................................................................... 631

16.3.5 DMA Operation ........................................................................................................... 638

16.4 Initialization and Configuration ..................................................................................... 639

16.5 Register Map .............................................................................................................. 640

16.6 Register Descriptions .................................................................................................. 641

17 Inter-Integrated Circuit (I2C) Interface ................................................................ 669

17.1 Block Diagram ............................................................................................................ 670

17.2 Signal Description ....................................................................................................... 670

17.3 Functional Description ................................................................................................. 671

17.3.1 I2C Bus Functional Overview ........................................................................................ 671

17.3.2 Available Speed Modes ............................................................................................... 673

17.3.3 Interrupts .................................................................................................................... 674

17.3.4 Loopback Operation .................................................................................................... 675

17.3.5 Command Sequence Flow Charts ................................................................................ 675

17.4 Initialization and Configuration ..................................................................................... 682

17.5 Register Map .............................................................................................................. 683

17.6 Register Descriptions (I2C Master) ............................................................................... 684

17.7 Register Descriptions (I2C Slave) ................................................................................. 697

18 Analog Comparators ............................................................................................ 706

18.1 Block Diagram ............................................................................................................ 706

18.2 Signal Description ....................................................................................................... 707

18.3 Functional Description ................................................................................................. 708

18.3.1 Internal Reference Programming .................................................................................. 708

18.4 Initialization and Configuration ..................................................................................... 710

18.5 Register Map .............................................................................................................. 710

18.6 Register Descriptions .................................................................................................. 710

19 Pin Diagram .......................................................................................................... 718

20 Signal Tables ........................................................................................................ 720

20.1 100-Pin LQFP Package Pin Tables ............................................................................... 720

20.2 108-Pin BGA Package Pin Tables ................................................................................ 743

Texas Instruments-Advance Information

7February 09, 2010

Page 8

Table of Contents

21 Operating Characteristics ................................................................................... 767

22 Electrical Characteristics .................................................................................... 768

22.1 DC Characteristics ...................................................................................................... 768

22.1.1 Maximum Ratings ....................................................................................................... 768

22.1.2 Recommended DC Operating Conditions ...................................................................... 768

22.1.3 On-Chip Low Drop-Out (LDO) Regulator Characteristics ................................................ 769

22.1.4 Hibernation Module Characteristics .............................................................................. 769

22.1.5 Flash Memory Characteristics ...................................................................................... 769

22.1.6 GPIO Module Characteristics ....................................................................................... 770

22.1.7 Current Specifications .................................................................................................. 770

22.2 AC Characteristics ....................................................................................................... 771

22.2.1 Load Conditions .......................................................................................................... 771

22.2.2 Clocks ........................................................................................................................ 771

22.2.3 JTAG and Boundary Scan ............................................................................................ 774

22.2.4 Reset ......................................................................................................................... 775

22.2.5 Sleep Modes ............................................................................................................... 777

22.2.6 Hibernation Module ..................................................................................................... 777

22.2.7 General-Purpose I/O (GPIO) ........................................................................................ 778

22.2.8 External Peripheral Interface (EPI) ............................................................................... 778

22.2.9 Analog-to-Digital Converter .......................................................................................... 783

22.2.10 Synchronous Serial Interface (SSI) ............................................................................... 785

22.2.11 Inter-Integrated Circuit (I2C) Interface ........................................................................... 786

22.2.12 Ethernet Controller ...................................................................................................... 787

22.2.13 Analog Comparator ..................................................................................................... 788

A Boot Loader .......................................................................................................... 789

A.1 Boot Loader Overview ................................................................................................. 789

A.2 Serial Interfaces .......................................................................................................... 789

A.2.1 Serial Configuration ..................................................................................................... 789

A.2.2 Serial Packet Handling ................................................................................................ 790

A.2.3 Serial Commands ........................................................................................................ 791

B ROM DriverLib Functions .................................................................................... 794

B.1 DriverLib Functions Included in the Integrated ROM ...................................................... 794

C Register Quick Reference ................................................................................... 828

D Ordering and Contact Information ..................................................................... 850

D.1 Ordering Information .................................................................................................... 850

D.2 Part Markings .............................................................................................................. 850

D.3 Kits ............................................................................................................................. 851

D.4 Support Information ..................................................................................................... 851

E Package Information ............................................................................................ 852

Texas Instruments-Advance Information

February 09, 20108

Page 9

List of Figures

Figure 1-1. Stellaris®LM3S1R21 Microcontroller High-Level Block Diagram ............................ 48

Figure 2-1. CPU Block Diagram ............................................................................................. 51

Figure 2-2. TPIU Block Diagram ............................................................................................ 59

Figure 5-1. JTAG Module Block Diagram ................................................................................ 70

Figure 5-2. Test Access Port State Machine ........................................................................... 73

Figure 5-3. IDCODE Register Format ..................................................................................... 79

Figure 5-4. BYPASS Register Format .................................................................................... 79

Figure 5-5. Boundary Scan Register Format ........................................................................... 80

Figure 6-1. Basic RST Configuration ...................................................................................... 83

Figure 6-2. External Circuitry to Extend Power-On Reset ........................................................ 84

Figure 6-3. Reset Circuit Controlled by Switch ........................................................................ 84

Figure 6-4. Power Architecture .............................................................................................. 87

Figure 6-5. Main Clock Tree .................................................................................................. 89

Figure 7-1. Hibernation Module Block Diagram ..................................................................... 173

Figure 7-2. Clock Source Using Crystal ................................................................................ 176

Figure 7-3. Clock Source Using Dedicated Oscillator and VDD3ON Mode .............................. 176

Figure 8-1. Internal Memory Block Diagram .......................................................................... 199

Figure 9-1. μDMA Block Diagram ......................................................................................... 234

Figure 9-2. Example of Ping-Pong μDMA Transaction ........................................................... 240

Figure 9-3. Memory Scatter-Gather, Setup and Configuration ................................................ 242

Figure 9-4. Memory Scatter-Gather, μDMA Copy Sequence .................................................. 243

Figure 9-5. Peripheral Scatter-Gather, Setup and Configuration ............................................. 245

Figure 9-6. Peripheral Scatter-Gather, μDMA Copy Sequence ............................................... 246

Figure 10-1. Digital I/O Pads ................................................................................................. 296

Figure 10-2. Analog/Digital I/O Pads ...................................................................................... 297

Figure 10-3. GPIODATA Write Example ................................................................................. 298

Figure 10-4. GPIODATA Read Example ................................................................................. 298

Figure 11-1. EPI Block Diagram ............................................................................................. 349

Figure 11-2. SDRAM Non-Blocking Read Cycle ...................................................................... 356

Figure 11-3. SDRAM Normal Read Cycle ............................................................................... 357

Figure 11-4. SDRAM Write Cycle ........................................................................................... 358

Figure 11-5. Host-Bus Read Cycle, MODE = 0x1, WRHIGH = 1, RDHIGH = 1 .......................... 365

Figure 11-6. Host-Bus Write Cycle, MODE = 0x1, WRHIGH = 1, RDHIGH = 1 .......................... 365

Figure 11-7. Host-Bus Write Cycle with Multiplexed Address and Data, MODE = 0x0, WRHIGH

= 1, RDHIGH = 1 ............................................................................................... 366

Figure 11-8. Continuous Read Mode Accesses ...................................................................... 366

Figure 11-9. Write Followed by Read to External FIFO ............................................................ 367

Figure 11-10. Two-Entry FIFO ................................................................................................. 367

Figure 11-11. Single-Cycle Write Access, FRM50=0, FRMCNT=0, WRCYC=0 ........................... 371

Figure 11-12. Two-Cycle Read, Write Accesses, FRM50=0, FRMCNT=0, RDCYC=1,

WRCYC=1 ........................................................................................................ 371

Figure 11-13. Read Accesses, FRM50=0, FRMCNT=0, RDCYC=1 ............................................ 372

Figure 11-14. FRAME Signal Operation, FRM50=0 and FRMCNT=0 ......................................... 372

Figure 11-15. FRAME Signal Operation, FRM50=0 and FRMCNT=1 ......................................... 372

Figure 11-16. FRAME Signal Operation, FRM50=0 and FRMCNT=2 ......................................... 373

Figure 11-17. FRAME Signal Operation, FRM50=1 and FRMCNT=0 ......................................... 373

Stellaris® LM3S1R21 Microcontroller

Texas Instruments-Advance Information

9February 09, 2010

Page 10

Table of Contents

Figure 11-18. FRAME Signal Operation, FRM50=1 and FRMCNT=1 ......................................... 373

Figure 11-19. FRAME Signal Operation, FRM50=1 and FRMCNT=2 ......................................... 373

Figure 11-20. iRDY Signal Operation, FRM50=0, FRMCNT=0, and RD2CYC=1 ......................... 374

Figure 11-21. EPI Clock Operation, CLKGATE=1, WR2CYC=0 ................................................. 374

Figure 11-22. EPI Clock Operation, CLKGATE=1, WR2CYC=1 ................................................. 375

Figure 12-1. GPTM Module Block Diagram ............................................................................ 420

Figure 12-2. 16-Bit Input Edge-Count Mode Example .............................................................. 427

Figure 12-3. 16-Bit Input Edge-Time Mode Example ............................................................... 429

Figure 12-4. 16-Bit PWM Mode Example ................................................................................ 430

Figure 12-5. Timer Daisy Chain ............................................................................................. 430

Figure 13-1. WDT Module Block Diagram .............................................................................. 467

Figure 14-1. ADC Module Block Diagram ............................................................................... 492

Figure 14-2. Internal Voltage Conversion Result ..................................................................... 497

Figure 14-3. External Voltage Conversion Result .................................................................... 498

Figure 14-4. Differential Sampling Range, V

Figure 14-5. Differential Sampling Range, V

Figure 14-6. Differential Sampling Range, V

Figure 14-7. Internal Temperature Sensor Characteristic ......................................................... 501

Figure 14-8. Low-Band Operation (CIC=0x0 and/or CTC=0x0) ................................................ 504

Figure 14-9. Mid-Band Operation (CIC=0x1 and/or CTC=0x1) ................................................. 505

Figure 14-10. High-Band Operation (CIC=0x3 and/or CTC=0x3) ................................................ 506

Figure 15-1. UART Module Block Diagram ............................................................................. 566

Figure 15-2. UART Character Frame ..................................................................................... 569

Figure 15-3. IrDA Data Modulation ......................................................................................... 571

Figure 15-4. LIN Message ..................................................................................................... 573

Figure 15-5. LIN Synchronization Field ................................................................................... 574

Figure 16-1. SSI Module Block Diagram ................................................................................. 628

Figure 16-2. TI Synchronous Serial Frame Format (Single Transfer) ........................................ 632

Figure 16-3. TI Synchronous Serial Frame Format (Continuous Transfer) ................................ 632

Figure 16-4. Freescale SPI Format (Single Transfer) with SPO=0 and SPH=0 .......................... 633

Figure 16-5. Freescale SPI Format (Continuous Transfer) with SPO=0 and SPH=0 .................. 633

Figure 16-6. Freescale SPI Frame Format with SPO=0 and SPH=1 ......................................... 634

Figure 16-7. Freescale SPI Frame Format (Single Transfer) with SPO=1 and SPH=0 ............... 635

Figure 16-8. Freescale SPI Frame Format (Continuous Transfer) with SPO=1 and SPH=0 ........ 635

Figure 16-9. Freescale SPI Frame Format with SPO=1 and SPH=1 ......................................... 636

Figure 16-10. MICROWIRE Frame Format (Single Frame) ........................................................ 637

Figure 16-11. MICROWIRE Frame Format (Continuous Transfer) ............................................. 638

Figure 16-12. MICROWIRE Frame Format, SSIFss Input Setup and Hold Requirements ............ 638

Figure 17-1. I2C Block Diagram ............................................................................................. 670

Figure 17-2. I2C Bus Configuration ........................................................................................ 671

Figure 17-3. START and STOP Conditions ............................................................................. 672

Figure 17-4. Complete Data Transfer with a 7-Bit Address ....................................................... 672

Figure 17-5. R/S Bit in First Byte ............................................................................................ 672

Figure 17-6. Data Validity During Bit Transfer on the I2C Bus ................................................... 673

Figure 17-7. Master Single TRANSMIT .................................................................................. 676

Figure 17-8. Master Single RECEIVE ..................................................................................... 677

Figure 17-9. Master TRANSMIT with Repeated START ........................................................... 678

Figure 17-10. Master RECEIVE with Repeated START ............................................................. 679

IN_ODD

IN_ODD

IN_ODD

= 1.5 V ...................................................... 499

= 0.75 V .................................................... 500

= 2.25 V .................................................... 500

Texas Instruments-Advance Information

February 09, 201010

Page 11

Stellaris® LM3S1R21 Microcontroller

Figure 17-11. Master RECEIVE with Repeated START after TRANSMIT with Repeated

START .............................................................................................................. 680

Figure 17-12. Master TRANSMIT with Repeated START after RECEIVE with Repeated

START .............................................................................................................. 681

Figure 17-13. Slave Command Sequence ................................................................................ 682

Figure 18-1. Analog Comparator Module Block Diagram ......................................................... 706

Figure 18-2. Structure of Comparator Unit .............................................................................. 708

Figure 18-3. Comparator Internal Reference Structure ............................................................ 709

Figure 19-1. 100-Pin LQFP Package Pin Diagram .................................................................. 718

Figure 19-2. 108-Ball BGA Package Pin Diagram (Top View) ................................................... 719

Figure 22-1. Load Conditions ................................................................................................ 771

Figure 22-2. JTAG Test Clock Input Timing ............................................................................. 774

Figure 22-3. JTAG Test Access Port (TAP) Timing .................................................................. 775

Figure 22-4. External Reset Timing (RST) .............................................................................. 775

Figure 22-5. Power-On Reset Timing ..................................................................................... 776

Figure 22-6. Brown-Out Reset Timing .................................................................................... 776

Figure 22-7. Software Reset Timing ....................................................................................... 776

Figure 22-8. Watchdog Reset Timing ..................................................................................... 776

Figure 22-9. MOSC Failure Reset Timing ............................................................................... 777

Figure 22-10. Hibernation Module Timing with Internal Oscillator Running in Hibernation ............ 778

Figure 22-11. Hibernation Module Timing with Internal Oscillator Stopped in Hibernation ............ 778

Figure 22-12. SDRAM Initialization and Load Mode Register Timing .......................................... 780

Figure 22-13. SDRAM Read Timing ......................................................................................... 780

Figure 22-14. SDRAM Write Timing ......................................................................................... 781

Figure 22-15. Host-Bus 8/16 Mode Read Timing ...................................................................... 782

Figure 22-16. Host-Bus 8/16 Mode Write Timing ....................................................................... 782

Figure 22-17. General-Purpose Mode Read and Write Timing ................................................... 783

Figure 22-18. General-Purpose Mode iRDY Timing .................................................................. 783

Figure 22-19. ADC Input Equivalency Diagram ......................................................................... 784

Figure 22-20. SSI Timing for TI Frame Format (FRF=01), Single Transfer Timing

Measurement .................................................................................................... 785

Figure 22-21. SSI Timing for MICROWIRE Frame Format (FRF=10), Single Transfer ................. 786

Figure 22-22. SSI Timing for SPI Frame Format (FRF=00), with SPH=1 ..................................... 786

Figure 22-23. I2C Timing ......................................................................................................... 786

Figure 22-24. Station Management Write Timing ...................................................................... 787

Figure 22-25. Station Management Read Timing ...................................................................... 787

Figure 22-26. MII Receive Timing ............................................................................................ 788

Figure 22-27. MII Transmit Timing ........................................................................................... 788

Figure E-1. 100-Pin LQFP Package ...................................................................................... 852

Figure E-2. 108-Ball BGA Package ...................................................................................... 854

Texas Instruments-Advance Information

11February 09, 2010

Page 12

Table of Contents

List of Tables

Table 1. Revision History .................................................................................................. 23

Table 2. Documentation Conventions ................................................................................ 27

Table 2-1. 16-Bit Cortex-M3 Instruction Set Summary ............................................................ 52

Table 2-2. 32-Bit Cortex-M3 Instruction Set Summary ............................................................ 54

Table 3-1. Memory Map ....................................................................................................... 63

Table 4-1. Exception Types .................................................................................................. 66

Table 4-2. Interrupts ............................................................................................................ 67

Table 5-1. Signals for JTAG_SWD_SWO (100LQFP) ............................................................. 70

Table 5-2. Signals for JTAG_SWD_SWO (108BGA) .............................................................. 71

Table 5-3. JTAG Port Pins State after Power-On Reset or RST assertion ................................ 72

Table 5-4. JTAG Instruction Register Commands ................................................................... 77

Table 6-1. Signals for System Control & Clocks (100LQFP) ................................................... 81

Table 6-2. Signals for System Control & Clocks (108BGA) ..................................................... 81

Table 6-3. Reset Sources .................................................................................................... 82

Table 6-4. Clock Source Options .......................................................................................... 88

Table 6-5. Possible System Clock Frequencies Using the SYSDIV Field ................................. 90

Table 6-6. Examples of Possible System Clock Frequencies Using the SYSDIV2 Field ............ 90

Table 6-7. Examples of Possible System Clock Frequencies with DIV400=1 ........................... 91

Table 6-8. System Control Register Map ............................................................................... 95

Table 6-9. RCC2 Fields that Override RCC fields ................................................................. 115

Table 7-1. Signals for Hibernate (100LQFP) ........................................................................ 173

Table 7-2. Signals for Hibernate (108BGA) .......................................................................... 174

Table 7-3. Hibernation Module Clock Operation ................................................................... 179

Table 7-4. Hibernation Module Register Map ....................................................................... 182

Table 8-1. Flash Memory Protection Policy Combinations .................................................... 201

Table 8-2. User-Programmable Flash Memory Resident Registers ....................................... 204

Table 8-3. Flash Register Map ............................................................................................ 205

Table 9-1. μDMA Channel Assignments .............................................................................. 235

Table 9-2. Request Type Support ....................................................................................... 236

Table 9-3. Control Structure Memory Map ........................................................................... 238

Table 9-4. Channel Control Structure .................................................................................. 238

Table 9-5. μDMA Read Example: 8-Bit Peripheral ................................................................ 247

Table 9-6. μDMA Interrupt Assignments .............................................................................. 248

Table 9-7. Channel Control Structure Offsets for Channel 30 ................................................ 249

Table 9-8. Channel Control Word Configuration for Memory Transfer Example ...................... 249

Table 9-9. Channel Control Structure Offsets for Channel 7 .................................................. 250

Table 9-10. Channel Control Word Configuration for Peripheral Transmit Example .................. 251

Table 9-11. Primary and Alternate Channel Control Structure Offsets for Channel 8 ................. 252

Table 9-12. Channel Control Word Configuration for Peripheral Ping-Pong Receive

Example ............................................................................................................ 253

Table 9-13. μDMA Register Map .......................................................................................... 254

Table 10-1. GPIO Pins With Non-Zero Reset Values .............................................................. 292

Table 10-2. GPIO Pins and Alternate Functions (100LQFP) ................................................... 292

Table 10-3. GPIO Pins and Alternate Functions (108BGA) ..................................................... 294

Table 10-4. GPIO Pad Configuration Examples ..................................................................... 300

Table 10-5. GPIO Interrupt Configuration Example ................................................................ 301

Texas Instruments-Advance Information

February 09, 201012

Page 13

Stellaris® LM3S1R21 Microcontroller

Table 10-6. GPIO Pins With Non-Zero Reset Values .............................................................. 302

Table 10-7. GPIO Register Map ........................................................................................... 303

Table 10-8. GPIO Pins With Non-Zero Reset Values .............................................................. 315

Table 10-9. GPIO Pins With Non-Zero Reset Values .............................................................. 321

Table 10-10. GPIO Pins With Non-Zero Reset Values .............................................................. 323

Table 10-11. GPIO Pins With Non-Zero Reset Values .............................................................. 326

Table 10-12. GPIO Pins With Non-Zero Reset Values .............................................................. 333

Table 11-1. Signals for External Peripheral Interface (100LQFP) ............................................ 349

Table 11-2. Signals for External Peripheral Interface (108BGA) .............................................. 350

Table 11-3. EPI SDRAM Signal Connections ......................................................................... 355

Table 11-4. Capabilities of Host Bus 8 and Host Bus 16 Modes .............................................. 359

Table 11-5. EPI Host-Bus 8 Signal Connections .................................................................... 360

Table 11-6. EPI Host-Bus 16 Signal Connections .................................................................. 361

Table 11-7. EPI General Purpose Signal Connections ........................................................... 369

Table 11-8. External Peripheral Interface (EPI) Register Map ................................................. 375

Table 12-1. Available CCP Pins ............................................................................................ 420

Table 12-2. Signals for General-Purpose Timers (100LQFP) .................................................. 421

Table 12-3. Signals for General-Purpose Timers (108BGA) .................................................... 422

Table 12-4. 16-Bit Timer With Prescaler Configurations ......................................................... 426

Table 12-5. Timers Register Map .......................................................................................... 435

Table 13-1. Watchdog Timers Register Map .......................................................................... 469

Table 14-1. Signals for ADC (100LQFP) ............................................................................... 492

Table 14-2. Signals for ADC (108BGA) ................................................................................. 493

Table 14-3. Samples and FIFO Depth of Sequencers ............................................................ 494

Table 14-4. Differential Sampling Pairs ................................................................................. 498

Table 14-5. ADC Register Map ............................................................................................. 507

Table 15-1. Signals for UART (100LQFP) ............................................................................. 567

Table 15-2. Signals for UART (108BGA) ............................................................................... 567

Table 15-3. Flow Control Mode ............................................................................................. 572

Table 15-4. UART Register Map ........................................................................................... 577

Table 16-1. Signals for SSI (100LQFP) ................................................................................. 629

Table 16-2. Signals for SSI (108BGA) ................................................................................... 629

Table 16-3. SSI Register Map .............................................................................................. 640

Table 17-1. Signals for I2C (100LQFP) ................................................................................. 670

Table 17-2. Signals for I2C (108BGA) ................................................................................... 670

Table 17-3. Examples of I2C Master Timer Period versus Speed Mode ................................... 674

Table 17-4. Inter-Integrated Circuit (I2C) Interface Register Map ............................................. 683

Table 17-5. Write Field Decoding for I2CMCS[3:0] Field ......................................................... 689

Table 18-1. Signals for Analog Comparators (100LQFP) ........................................................ 707

Table 18-2. Signals for Analog Comparators (108BGA) .......................................................... 707

Table 18-3. Internal Reference Voltage and ACREFCTL Field Values ..................................... 709

Table 18-4. Analog Comparators Register Map ..................................................................... 710

Table 20-1. GPIO Pins With Default Alternate Functions ........................................................ 720

Table 20-2. Signals by Pin Number ....................................................................................... 720

Table 20-3. Signals by Signal Name ..................................................................................... 728

Table 20-4. Signals by Function, Except for GPIO ................................................................. 736

Table 20-5. GPIO Pins and Alternate Functions ..................................................................... 741

Table 20-6. Signals by Pin Number ....................................................................................... 743

Texas Instruments-Advance Information

13February 09, 2010

Page 14

Table of Contents

Table 20-7. Signals by Signal Name ..................................................................................... 752

Table 20-8. Signals by Function, Except for GPIO ................................................................. 759

Table 20-9. GPIO Pins and Alternate Functions ..................................................................... 764

Table 21-1. Temperature Characteristics ............................................................................... 767

Table 21-2. Thermal Characteristics ..................................................................................... 767

Table 21-3. ESD Absolute Maximum Ratings ........................................................................ 767

Table 22-1. Maximum Ratings .............................................................................................. 768

Table 22-2. Recommended DC Operating Conditions ............................................................ 768

Table 22-3. LDO Regulator Characteristics ........................................................................... 769

Table 22-4. Hibernation Module DC Characteristics ............................................................... 769

Table 22-5. Flash Memory Characteristics ............................................................................ 769

Table 22-6. GPIO Module DC Characteristics ........................................................................ 770

Table 22-7. Preliminary Current Consumption ....................................................................... 770

Table 22-8. Phase Locked Loop (PLL) Characteristics ........................................................... 771

Table 22-9. Actual PLL Frequency ........................................................................................ 772

Table 22-10. PIOSC Clock Characteristics .............................................................................. 772

Table 22-11. 30-kHz Clock Characteristics .............................................................................. 772

Table 22-12. Hibernation Clock Characteristics ....................................................................... 772

Table 22-13. HIB Oscillator Input Characteristics ..................................................................... 773

Table 22-14. Main Oscillator Clock Characteristics .................................................................. 773

Table 22-15. MOSC Oscillator Input Characteristics ................................................................ 773

Table 22-16. System Clock Characteristics with ADC Operation ............................................... 773

Table 22-17. JTAG Characteristics ......................................................................................... 774

Table 22-18. Reset Characteristics ......................................................................................... 775

Table 22-19. Sleep Modes AC Characteristics ......................................................................... 777

Table 22-20. Hibernation Module AC Characteristics ............................................................... 777

Table 22-21. GPIO Characteristics ......................................................................................... 778

Table 22-22. EPI SDRAM Characteristics ............................................................................... 779

Table 22-23. EPI SDRAM Interface Characteristics ................................................................. 779

Table 22-24. EPI Host-Bus 8 and Host-Bus 16 Interface Characteristics ................................... 781

Table 22-25. EPI General-Purpose Interface Characteristics .................................................... 782

Table 22-26. ADC Characteristics ........................................................................................... 783

Table 22-27. ADC Module External Reference Characteristics ................................................. 784

Table 22-28. ADC Module Internal Reference Characteristics .................................................. 785

Table 22-29. SSI Characteristics ............................................................................................ 785

Table 22-30. Ethernet Station Management ............................................................................ 787

Table 22-31. Ethernet MII ...................................................................................................... 787

Table 22-32. Analog Comparator Characteristics ..................................................................... 788

Table 22-33. Analog Comparator Voltage Reference Characteristics ........................................ 788

Table D-1. Part Ordering Information ................................................................................... 850

Texas Instruments-Advance Information

February 09, 201014

Page 15

Stellaris® LM3S1R21 Microcontroller

List of Registers

System Control .............................................................................................................................. 81

Register 1: Device Identification 0 (DID0), offset 0x000 ....................................................................... 97

Register 2: Brown-Out Reset Control (PBORCTL), offset 0x030 .......................................................... 99

Register 3: Raw Interrupt Status (RIS), offset 0x050 .......................................................................... 100

Register 4: Interrupt Mask Control (IMC), offset 0x054 ...................................................................... 102

Register 5: Masked Interrupt Status and Clear (MISC), offset 0x058 .................................................. 104

Register 6: Reset Cause (RESC), offset 0x05C ................................................................................ 106

Register 7: Run-Mode Clock Configuration (RCC), offset 0x060 ......................................................... 108

Register 8: XTAL to PLL Translation (PLLCFG), offset 0x064 ............................................................. 112

Register 9: GPIO High-Performance Bus Control (GPIOHBCTL), offset 0x06C ................................... 113

Register 10: Run-Mode Clock Configuration 2 (RCC2), offset 0x070 .................................................... 115

Register 11: Main Oscillator Control (MOSCCTL), offset 0x07C ........................................................... 118

Register 12: Deep Sleep Clock Configuration (DSLPCLKCFG), offset 0x144 ........................................ 119

Register 13: Precision Internal Oscillator Calibration (PIOSCCAL), offset 0x150 ................................... 121

Register 14: Precision Internal Oscillator Statistics (PIOSCSTAT), offset 0x154 .................................... 123

Register 15: Device Identification 1 (DID1), offset 0x004 ..................................................................... 124

Register 16: Device Capabilities 0 (DC0), offset 0x008 ........................................................................ 126

Register 17: Device Capabilities 1 (DC1), offset 0x010 ........................................................................ 127

Register 18: Device Capabilities 2 (DC2), offset 0x014 ........................................................................ 129

Register 19: Device Capabilities 3 (DC3), offset 0x018 ........................................................................ 131

Register 20: Device Capabilities 4 (DC4), offset 0x01C ....................................................................... 133

Register 21: Device Capabilities 5 (DC5), offset 0x020 ........................................................................ 135

Register 22: Device Capabilities 6 (DC6), offset 0x024 ........................................................................ 136

Register 23: Device Capabilities 7 (DC7), offset 0x028 ........................................................................ 137

Register 24: Device Capabilities 8 ADC Channels (DC8), offset 0x02C ................................................ 141

Register 25: Device Capabilities 9 ADC Digital Comparators (DC9), offset 0x190 ................................. 142

Register 26: Non-Volatile Memory Information (NVMSTAT), offset 0x1A0 ............................................. 143

Register 27: Run Mode Clock Gating Control Register 0 (RCGC0), offset 0x100 ................................... 144

Register 28: Sleep Mode Clock Gating Control Register 0 (SCGC0), offset 0x110 ................................. 146

Register 29: Deep Sleep Mode Clock Gating Control Register 0 (DCGC0), offset 0x120 ....................... 148

Register 30: Run Mode Clock Gating Control Register 1 (RCGC1), offset 0x104 ................................... 150

Register 31: Sleep Mode Clock Gating Control Register 1 (SCGC1), offset 0x114 ................................. 153

Register 32: Deep-Sleep Mode Clock Gating Control Register 1 (DCGC1), offset 0x124 ....................... 156

Register 33: Run Mode Clock Gating Control Register 2 (RCGC2), offset 0x108 ................................... 159

Register 34: Sleep Mode Clock Gating Control Register 2 (SCGC2), offset 0x118 ................................. 161

Register 35: Deep Sleep Mode Clock Gating Control Register 2 (DCGC2), offset 0x128 ....................... 163

Register 36: Software Reset Control 0 (SRCR0), offset 0x040 ............................................................. 165

Register 37: Software Reset Control 1 (SRCR1), offset 0x044 ............................................................. 167

Register 38: Software Reset Control 2 (SRCR2), offset 0x048 ............................................................. 170

Hibernation Module ..................................................................................................................... 172

Register 1: Hibernation RTC Counter (HIBRTCC), offset 0x000 ......................................................... 183

Register 2: Hibernation RTC Match 0 (HIBRTCM0), offset 0x004 ....................................................... 184

Register 3: Hibernation RTC Match 1 (HIBRTCM1), offset 0x008 ....................................................... 185

Register 4: Hibernation RTC Load (HIBRTCLD), offset 0x00C ........................................................... 186

Register 5: Hibernation Control (HIBCTL), offset 0x010 ..................................................................... 187

Texas Instruments-Advance Information

15February 09, 2010

Page 16

Table of Contents

Register 6: Hibernation Interrupt Mask (HIBIM), offset 0x014 ............................................................. 190

Register 7: Hibernation Raw Interrupt Status (HIBRIS), offset 0x018 .................................................. 192

Register 8: Hibernation Masked Interrupt Status (HIBMIS), offset 0x01C ............................................ 194

Register 9: Hibernation Interrupt Clear (HIBIC), offset 0x020 ............................................................. 196

Register 10: Hibernation RTC Trim (HIBRTCT), offset 0x024 ............................................................... 197

Register 11: Hibernation Data (HIBDATA), offset 0x030-0x12C ............................................................ 198

Internal Memory ........................................................................................................................... 199

Register 1: Flash Memory Address (FMA), offset 0x000 .................................................................... 207

Register 2: Flash Memory Data (FMD), offset 0x004 ......................................................................... 208

Register 3: Flash Memory Control (FMC), offset 0x008 ..................................................................... 209