TEXAS INSTRUMENTS-PRODUCTION DATA

Stellaris® LM3S1110 Microcontroller

DATA SHEET

DS-LM3S1110-7787

Copyright © 2007-2010 Texas Instruments

Incorporated

Copyright

Copyright ©2007-2010 Texas Instruments Incorporated All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments

Incorporated. ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the

property of others.

PRODUCTION DATA information is current as of publication date. Products conform to specications per the terms of Texas Instruments standard

warranty. Production processing does not necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor

products and disclaimers thereto appears at the end of this data sheet.

Texas Instruments Incorporated

108 Wild Basin, Suite 350

Austin, TX 78746

http://www.ti.com/stellaris

http://www-k.ext.ti.com/sc/technical-support/product-information-centers.htm

Texas Instruments-Production Data

September 04, 20102

Stellaris® LM3S1110 Microcontroller

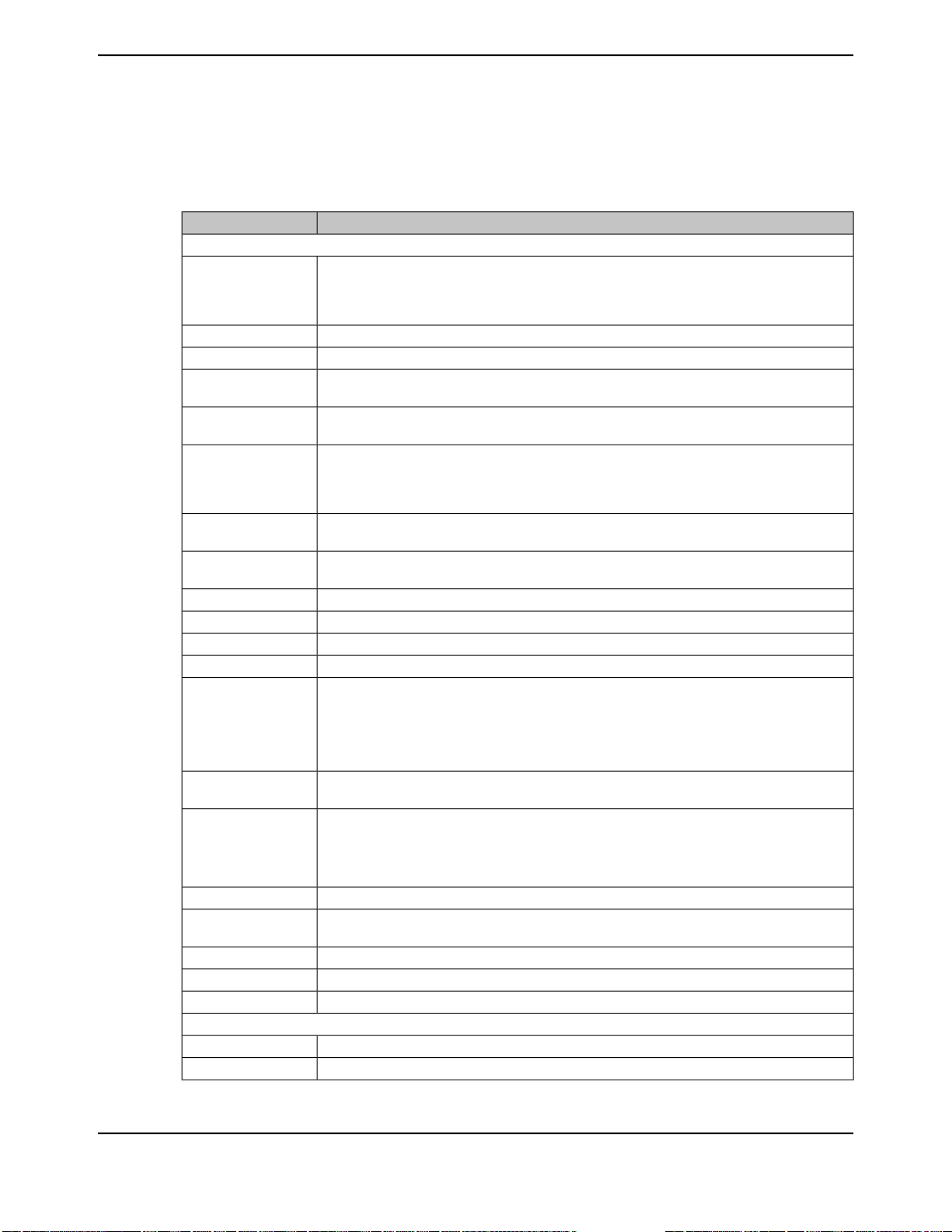

Table of Contents

Revision History ............................................................................................................................. 19

About This Document .................................................................................................................... 23

Audience .............................................................................................................................................. 23

About This Manual ................................................................................................................................ 23

Related Documents ............................................................................................................................... 23

Documentation Conventions .................................................................................................................. 24

1 Architectural Overview .......................................................................................... 26

1.1 Product Features .......................................................................................................... 26

1.2 Target Applications ........................................................................................................ 32

1.3 High-Level Block Diagram ............................................................................................. 32

1.4 Functional Overview ...................................................................................................... 34

1.4.1 ARM Cortex™-M3 ......................................................................................................... 34

1.4.2 Motor Control Peripherals .............................................................................................. 35

1.4.3 Analog Peripherals ........................................................................................................ 35

1.4.4 Serial Communications Peripherals ................................................................................ 35

1.4.5 System Peripherals ....................................................................................................... 36

1.4.6 Memory Peripherals ...................................................................................................... 37

1.4.7 Additional Features ....................................................................................................... 37

1.4.8 Hardware Details .......................................................................................................... 38

2 The Cortex-M3 Processor ...................................................................................... 39

2.1 Block Diagram .............................................................................................................. 40

2.2 Overview ...................................................................................................................... 41

2.2.1 System-Level Interface .................................................................................................. 41

2.2.2 Integrated Configurable Debug ...................................................................................... 41

2.2.3 Trace Port Interface Unit (TPIU) ..................................................................................... 42

2.2.4 Cortex-M3 System Component Details ........................................................................... 42

2.3 Programming Model ...................................................................................................... 43

2.3.1 Processor Mode and Privilege Levels for Software Execution ........................................... 43

2.3.2 Stacks .......................................................................................................................... 43

2.3.3 Register Map ................................................................................................................ 44

2.3.4 Register Descriptions .................................................................................................... 45

2.3.5 Exceptions and Interrupts .............................................................................................. 58

2.3.6 Data Types ................................................................................................................... 58

2.4 Memory Model .............................................................................................................. 58

2.4.1 Memory Regions, Types and Attributes ........................................................................... 59

2.4.2 Memory System Ordering of Memory Accesses .............................................................. 60

2.4.3 Behavior of Memory Accesses ....................................................................................... 60

2.4.4 Software Ordering of Memory Accesses ......................................................................... 61

2.4.5 Bit-Banding ................................................................................................................... 62

2.4.6 Data Storage ................................................................................................................ 64

2.4.7 Synchronization Primitives ............................................................................................. 65

2.5 Exception Model ........................................................................................................... 66

2.5.1 Exception States ........................................................................................................... 66

2.5.2 Exception Types ............................................................................................................ 67

2.5.3 Exception Handlers ....................................................................................................... 70

Texas Instruments-Production Data

3September 04, 2010

Table of Contents

2.5.4 Vector Table .................................................................................................................. 70

2.5.5 Exception Priorities ....................................................................................................... 71

2.5.6 Interrupt Priority Grouping .............................................................................................. 71

2.5.7 Exception Entry and Return ........................................................................................... 71

2.6 Fault Handling .............................................................................................................. 74

2.6.1 Fault Types ................................................................................................................... 74

2.6.2 Fault Escalation and Hard Faults .................................................................................... 75

2.6.3 Fault Status Registers and Fault Address Registers ........................................................ 75

2.6.4 Lockup ......................................................................................................................... 76

2.7 Power Management ...................................................................................................... 76

2.7.1 Entering Sleep Modes ................................................................................................... 76

2.7.2 Wake Up from Sleep Mode ............................................................................................ 77

2.8 Instruction Set Summary ............................................................................................... 77

3 Cortex-M3 Peripherals ........................................................................................... 81

3.1 Functional Description ................................................................................................... 81

3.1.1 System Timer (SysTick) ................................................................................................. 81

3.1.2 Nested Vectored Interrupt Controller (NVIC) .................................................................... 82

3.1.3 System Control Block (SCB) .......................................................................................... 84

3.1.4 Memory Protection Unit (MPU) ....................................................................................... 84

3.2 Register Map ................................................................................................................ 89

3.3 System Timer (SysTick) Register Descriptions ................................................................ 91

3.4 NVIC Register Descriptions ........................................................................................... 95

3.5 System Control Block (SCB) Register Descriptions ........................................................ 108

3.6 Memory Protection Unit (MPU) Register Descriptions .................................................... 137

4 JTAG Interface ...................................................................................................... 147

4.1 Block Diagram ............................................................................................................ 148

4.2 Functional Description ................................................................................................. 148

4.2.1 JTAG Interface Pins ..................................................................................................... 148

4.2.2 JTAG TAP Controller ................................................................................................... 150

4.2.3 Shift Registers ............................................................................................................ 151

4.2.4 Operational Considerations .......................................................................................... 151

4.3 Initialization and Configuration ..................................................................................... 154

4.4 Register Descriptions .................................................................................................. 154

4.4.1 Instruction Register (IR) ............................................................................................... 154

4.4.2 Data Registers ............................................................................................................ 156

5 System Control ..................................................................................................... 159

5.1 Functional Description ................................................................................................. 159

5.1.1 Device Identification .................................................................................................... 159

5.1.2 Reset Control .............................................................................................................. 159

5.1.3 Power Control ............................................................................................................. 162

5.1.4 Clock Control .............................................................................................................. 163

5.1.5 System Control ........................................................................................................... 169

5.2 Initialization and Configuration ..................................................................................... 170

5.3 Register Map .............................................................................................................. 170

5.4 Register Descriptions .................................................................................................. 172

6 Hibernation Module .............................................................................................. 217

6.1 Block Diagram ............................................................................................................ 218

Texas Instruments-Production Data

September 04, 20104

Stellaris® LM3S1110 Microcontroller

6.2 Functional Description ................................................................................................. 218

6.2.1 Register Access Timing ............................................................................................... 218

6.2.2 Clock Source .............................................................................................................. 219

6.2.3 Battery Management ................................................................................................... 220

6.2.4 Real-Time Clock .......................................................................................................... 221

6.2.5 Non-Volatile Memory ................................................................................................... 221

6.2.6 Power Control ............................................................................................................. 221

6.2.7 Initiating Hibernate ...................................................................................................... 222

6.2.8 Interrupts and Status ................................................................................................... 222

6.3 Initialization and Configuration ..................................................................................... 222

6.3.1 Initialization ................................................................................................................. 223

6.3.2 RTC Match Functionality (No Hibernation) .................................................................... 223

6.3.3 RTC Match/Wake-Up from Hibernation ......................................................................... 223

6.3.4 External Wake-Up from Hibernation .............................................................................. 223

6.3.5 RTC/External Wake-Up from Hibernation ...................................................................... 224

6.4 Register Map .............................................................................................................. 224

6.5 Register Descriptions .................................................................................................. 224

7 Internal Memory ................................................................................................... 237

7.1 Block Diagram ............................................................................................................ 237

7.2 Functional Description ................................................................................................. 237

7.2.1 SRAM Memory ............................................................................................................ 237

7.2.2 Flash Memory ............................................................................................................. 238

7.3 Flash Memory Initialization and Configuration ............................................................... 239

7.3.1 Flash Programming ..................................................................................................... 239

7.3.2 Nonvolatile Register Programming ............................................................................... 240

7.4 Register Map .............................................................................................................. 241

7.5 Flash Register Descriptions (Flash Control Offset) ......................................................... 242

7.6 Flash Register Descriptions (System Control Offset) ...................................................... 250

8 General-Purpose Input/Outputs (GPIOs) ........................................................... 263

8.1 Functional Description ................................................................................................. 263

8.1.1 Data Control ............................................................................................................... 264

8.1.2 Interrupt Control .......................................................................................................... 265

8.1.3 Mode Control .............................................................................................................. 266

8.1.4 Commit Control ........................................................................................................... 266

8.1.5 Pad Control ................................................................................................................. 266

8.1.6 Identification ............................................................................................................... 266

8.2 Initialization and Configuration ..................................................................................... 266

8.3 Register Map .............................................................................................................. 267

8.4 Register Descriptions .................................................................................................. 269

9 General-Purpose Timers ...................................................................................... 304

9.1 Block Diagram ............................................................................................................ 304

9.2 Functional Description ................................................................................................. 305

9.2.1 GPTM Reset Conditions .............................................................................................. 306

9.2.2 32-Bit Timer Operating Modes ...................................................................................... 306

9.2.3 16-Bit Timer Operating Modes ...................................................................................... 307

9.3 Initialization and Configuration ..................................................................................... 311

9.3.1 32-Bit One-Shot/Periodic Timer Mode ........................................................................... 311

9.3.2 32-Bit Real-Time Clock (RTC) Mode ............................................................................. 312

Texas Instruments-Production Data

5September 04, 2010

Table of Contents

9.3.3 16-Bit One-Shot/Periodic Timer Mode ........................................................................... 312

9.3.4 16-Bit Input Edge Count Mode ..................................................................................... 313

9.3.5 16-Bit Input Edge Timing Mode .................................................................................... 313

9.3.6 16-Bit PWM Mode ....................................................................................................... 314

9.4 Register Map .............................................................................................................. 314

9.5 Register Descriptions .................................................................................................. 315

10 Watchdog Timer ................................................................................................... 340

10.1 Block Diagram ............................................................................................................ 341

10.2 Functional Description ................................................................................................. 341

10.3 Initialization and Configuration ..................................................................................... 342

10.4 Register Map .............................................................................................................. 342

10.5 Register Descriptions .................................................................................................. 343

11 Universal Asynchronous Receivers/Transmitters (UARTs) ............................. 364

11.1 Block Diagram ............................................................................................................ 365

11.2 Functional Description ................................................................................................. 365

11.2.1 Transmit/Receive Logic ............................................................................................... 365

11.2.2 Baud-Rate Generation ................................................................................................. 366

11.2.3 Data Transmission ...................................................................................................... 367

11.2.4 Serial IR (SIR) ............................................................................................................. 367

11.2.5 FIFO Operation ........................................................................................................... 368

11.2.6 Interrupts .................................................................................................................... 368

11.2.7 Loopback Operation .................................................................................................... 369

11.2.8 IrDA SIR block ............................................................................................................ 369

11.3 Initialization and Configuration ..................................................................................... 369

11.4 Register Map .............................................................................................................. 370

11.5 Register Descriptions .................................................................................................. 371

12 Synchronous Serial Interface (SSI) .................................................................... 405

12.1 Block Diagram ............................................................................................................ 405

12.2 Functional Description ................................................................................................. 405

12.2.1 Bit Rate Generation ..................................................................................................... 406

12.2.2 FIFO Operation ........................................................................................................... 406

12.2.3 Interrupts .................................................................................................................... 406

12.2.4 Frame Formats ........................................................................................................... 407

12.3 Initialization and Configuration ..................................................................................... 414

12.4 Register Map .............................................................................................................. 415

12.5 Register Descriptions .................................................................................................. 416

13 Analog Comparators ............................................................................................ 442

13.1 Block Diagram ............................................................................................................ 442

13.2 Functional Description ................................................................................................. 443

13.2.1 Internal Reference Programming .................................................................................. 443

13.3 Initialization and Configuration ..................................................................................... 444

13.4 Register Map .............................................................................................................. 445

13.5 Register Descriptions .................................................................................................. 445

14 Pin Diagram .......................................................................................................... 453

15 Signal Tables ........................................................................................................ 455

15.1 100-Pin LQFP Package Pin Tables ............................................................................... 455

15.2 108-Pin BGA Package Pin Tables ................................................................................ 466

Texas Instruments-Production Data

September 04, 20106

Stellaris® LM3S1110 Microcontroller

15.3 Connections for Unused Signals ................................................................................... 477

16 Operating Characteristics ................................................................................... 479

17 Electrical Characteristics .................................................................................... 480

17.1 DC Characteristics ...................................................................................................... 480

17.1.1 Maximum Ratings ....................................................................................................... 480

17.1.2 Recommended DC Operating Conditions ...................................................................... 480

17.1.3 On-Chip Low Drop-Out (LDO) Regulator Characteristics ................................................ 481

17.1.4 GPIO Module Characteristics ....................................................................................... 481

17.1.5 Power Specifications ................................................................................................... 481

17.1.6 Flash Memory Characteristics ...................................................................................... 483

17.1.7 Hibernation ................................................................................................................. 483

17.2 AC Characteristics ....................................................................................................... 483

17.2.1 Load Conditions .......................................................................................................... 483

17.2.2 Clocks ........................................................................................................................ 484

17.2.3 JTAG and Boundary Scan ............................................................................................ 485

17.2.4 Reset ......................................................................................................................... 487

17.2.5 Sleep Modes ............................................................................................................... 489

17.2.6 Hibernation Module ..................................................................................................... 489

17.2.7 General-Purpose I/O (GPIO) ........................................................................................ 489

17.2.8 Synchronous Serial Interface (SSI) ............................................................................... 490

17.2.9 Analog Comparator ..................................................................................................... 491

A Serial Flash Loader .............................................................................................. 493

A.1 Serial Flash Loader ..................................................................................................... 493

A.2 Interfaces ................................................................................................................... 493

A.2.1 UART ......................................................................................................................... 493

A.2.2 SSI ............................................................................................................................. 493

A.3 Packet Handling .......................................................................................................... 494

A.3.1 Packet Format ............................................................................................................ 494

A.3.2 Sending Packets ......................................................................................................... 494

A.3.3 Receiving Packets ....................................................................................................... 494

A.4 Commands ................................................................................................................. 495

A.4.1 COMMAND_PING (0X20) ............................................................................................ 495

A.4.2 COMMAND_GET_STATUS (0x23) ............................................................................... 495

A.4.3 COMMAND_DOWNLOAD (0x21) ................................................................................. 495

A.4.4 COMMAND_SEND_DATA (0x24) ................................................................................. 496

A.4.5 COMMAND_RUN (0x22) ............................................................................................. 496

A.4.6 COMMAND_RESET (0x25) ......................................................................................... 496

B Register Quick Reference ................................................................................... 498

C Ordering and Contact Information ..................................................................... 514

C.1 Ordering Information .................................................................................................... 514

C.2 Part Markings .............................................................................................................. 514

C.3 Kits ............................................................................................................................. 515

C.4 Support Information ..................................................................................................... 515

D Package Information ............................................................................................ 516

D.1 108-Ball BGA Package ................................................................................................ 516

D.1.1 Package Dimensions ................................................................................................... 516

D.1.2 Tray Dimensions ......................................................................................................... 518

Texas Instruments-Production Data

7September 04, 2010

Table of Contents

D.1.3 Tape and Reel Dimensions .......................................................................................... 519

D.2 100-Pin LQFP Package ............................................................................................... 520

D.2.1 Package Dimensions ................................................................................................... 520

D.2.2 Tray Dimensions ......................................................................................................... 522

D.2.3 Tape and Reel Dimensions .......................................................................................... 523

Texas Instruments-Production Data

September 04, 20108

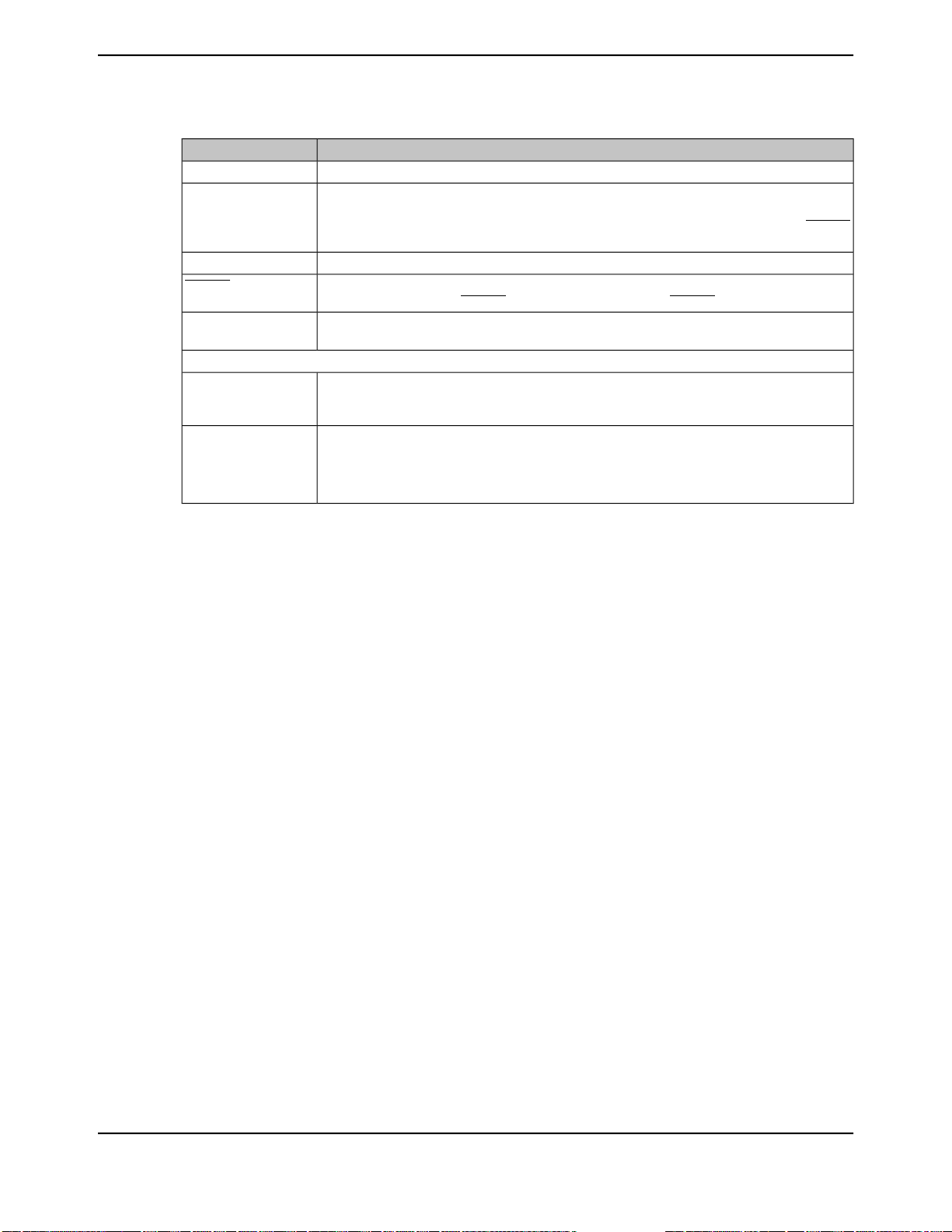

List of Figures

Figure 1-1. Stellaris®LM3S1110 Microcontroller High-Level Block Diagram ............................. 33

Figure 2-1. CPU Block Diagram ............................................................................................. 41

Figure 2-2. TPIU Block Diagram ............................................................................................ 42

Figure 2-3. Cortex-M3 Register Set ........................................................................................ 44

Figure 2-4. Bit-Band Mapping ................................................................................................ 64

Figure 2-5. Data Storage ....................................................................................................... 65

Figure 2-6. Vector table ......................................................................................................... 70

Figure 2-7. Exception Stack Frame ........................................................................................ 72

Figure 3-1. SRD Use Example ............................................................................................... 87

Figure 4-1. JTAG Module Block Diagram .............................................................................. 148

Figure 4-2. Test Access Port State Machine ......................................................................... 151

Figure 4-3. IDCODE Register Format ................................................................................... 157

Figure 4-4. BYPASS Register Format ................................................................................... 157

Figure 4-5. Boundary Scan Register Format ......................................................................... 158

Figure 5-1. Basic RST Configuration .................................................................................... 160

Figure 5-2. External Circuitry to Extend Power-On Reset ....................................................... 161

Figure 5-3. Reset Circuit Controlled by Switch ...................................................................... 161

Figure 5-4. Power Architecture ............................................................................................ 163

Figure 5-5. Main Clock Tree ................................................................................................ 166

Figure 6-1. Hibernation Module Block Diagram ..................................................................... 218

Figure 6-2. Clock Source Using Crystal ................................................................................ 220

Figure 6-3. Clock Source Using Dedicated Oscillator ............................................................. 220

Figure 7-1. Flash Block Diagram .......................................................................................... 237

Figure 8-1. GPIO Port Block Diagram ................................................................................... 264

Figure 8-2. GPIODATA Write Example ................................................................................. 265

Figure 8-3. GPIODATA Read Example ................................................................................. 265

Figure 9-1. GPTM Module Block Diagram ............................................................................ 305

Figure 9-2. 16-Bit Input Edge Count Mode Example .............................................................. 309

Figure 9-3. 16-Bit Input Edge Time Mode Example ............................................................... 310

Figure 9-4. 16-Bit PWM Mode Example ................................................................................ 311

Figure 10-1. WDT Module Block Diagram .............................................................................. 341

Figure 11-1. UART Module Block Diagram ............................................................................. 365

Figure 11-2. UART Character Frame ..................................................................................... 366

Figure 11-3. IrDA Data Modulation ......................................................................................... 368

Figure 12-1. SSI Module Block Diagram ................................................................................. 405

Figure 12-2. TI Synchronous Serial Frame Format (Single Transfer) ........................................ 408

Figure 12-3. TI Synchronous Serial Frame Format (Continuous Transfer) ................................ 408

Figure 12-4. Freescale SPI Format (Single Transfer) with SPO=0 and SPH=0 .......................... 409

Figure 12-5. Freescale SPI Format (Continuous Transfer) with SPO=0 and SPH=0 .................. 409

Figure 12-6. Freescale SPI Frame Format with SPO=0 and SPH=1 ......................................... 410

Figure 12-7. Freescale SPI Frame Format (Single Transfer) with SPO=1 and SPH=0 ............... 411

Figure 12-8. Freescale SPI Frame Format (Continuous Transfer) with SPO=1 and SPH=0 ........ 411

Figure 12-9. Freescale SPI Frame Format with SPO=1 and SPH=1 ......................................... 412

Figure 12-10. MICROWIRE Frame Format (Single Frame) ........................................................ 413

Figure 12-11. MICROWIRE Frame Format (Continuous Transfer) ............................................. 414

Figure 12-12. MICROWIRE Frame Format, SSIFss Input Setup and Hold Requirements ............ 414

Stellaris® LM3S1110 Microcontroller

Texas Instruments-Production Data

9September 04, 2010

Table of Contents

Figure 13-1. Analog Comparator Module Block Diagram ......................................................... 442

Figure 13-2. Structure of Comparator Unit .............................................................................. 443

Figure 13-3. Comparator Internal Reference Structure ............................................................ 444

Figure 14-1. 100-Pin LQFP Package Pin Diagram .................................................................. 453

Figure 14-2. 108-Ball BGA Package Pin Diagram (Top View) ................................................... 454

Figure 17-1. Load Conditions ................................................................................................ 484

Figure 17-2. JTAG Test Clock Input Timing ............................................................................. 486

Figure 17-3. JTAG Test Access Port (TAP) Timing .................................................................. 486

Figure 17-4. JTAG TRST Timing ............................................................................................ 487

Figure 17-5. External Reset Timing (RST) .............................................................................. 487

Figure 17-6. Power-On Reset Timing ..................................................................................... 488

Figure 17-7. Brown-Out Reset Timing .................................................................................... 488

Figure 17-8. Software Reset Timing ....................................................................................... 488

Figure 17-9. Watchdog Reset Timing ..................................................................................... 488

Figure 17-10. Hibernation Module Timing ................................................................................. 489

Figure 17-11. SSI Timing for TI Frame Format (FRF=01), Single Transfer Timing

Figure 17-12. SSI Timing for MICROWIRE Frame Format (FRF=10), Single Transfer ................. 491

Figure 17-13. SSI Timing for SPI Frame Format (FRF=00), with SPH=1 ..................................... 491

Figure D-1. 108-Ball BGA Package Dimensions .................................................................... 516

Figure D-2. 108-Ball BGA Tray Dimensions ........................................................................... 518

Figure D-3. 108-Ball BGA Tape and Reel Dimensions ............................................................ 519

Figure D-4. 100-Pin LQFP Package Dimensions ................................................................... 520

Figure D-5. 100-Pin LQFP Tray Dimensions .......................................................................... 522

Figure D-6. 100-Pin LQFP Tape and Reel Dimensions ........................................................... 523

Measurement .................................................................................................... 490

Texas Instruments-Production Data

September 04, 201010

List of Tables

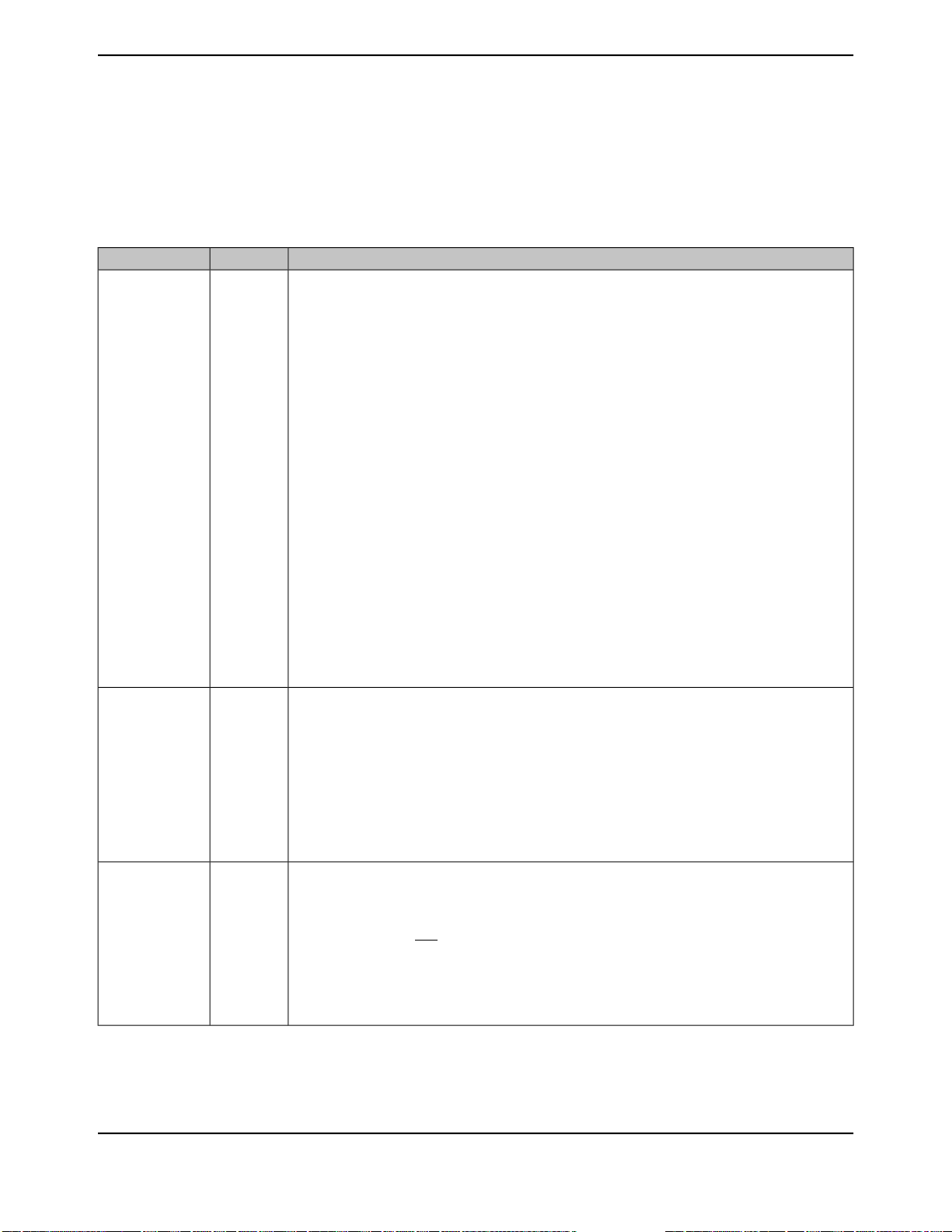

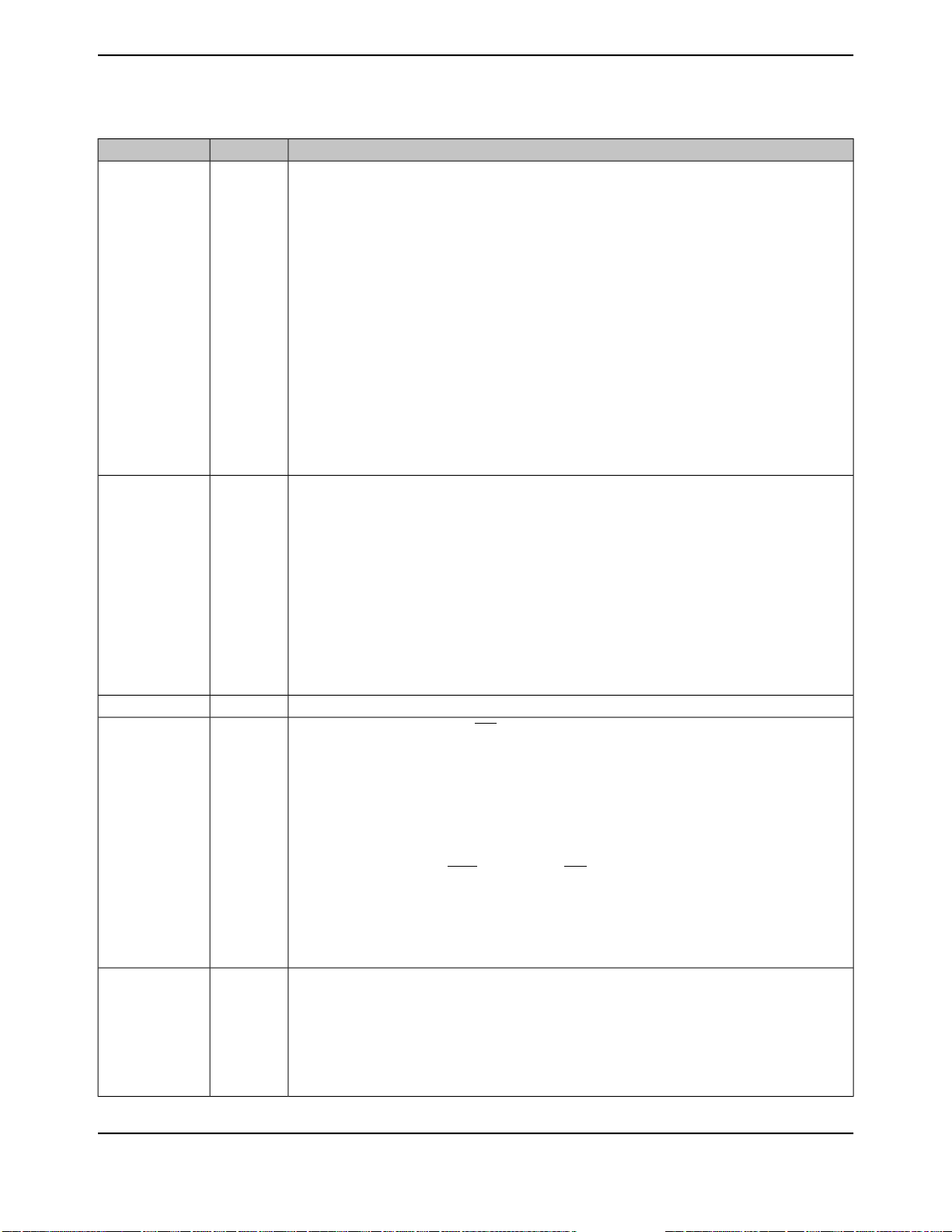

Table 1. Revision History .................................................................................................. 19

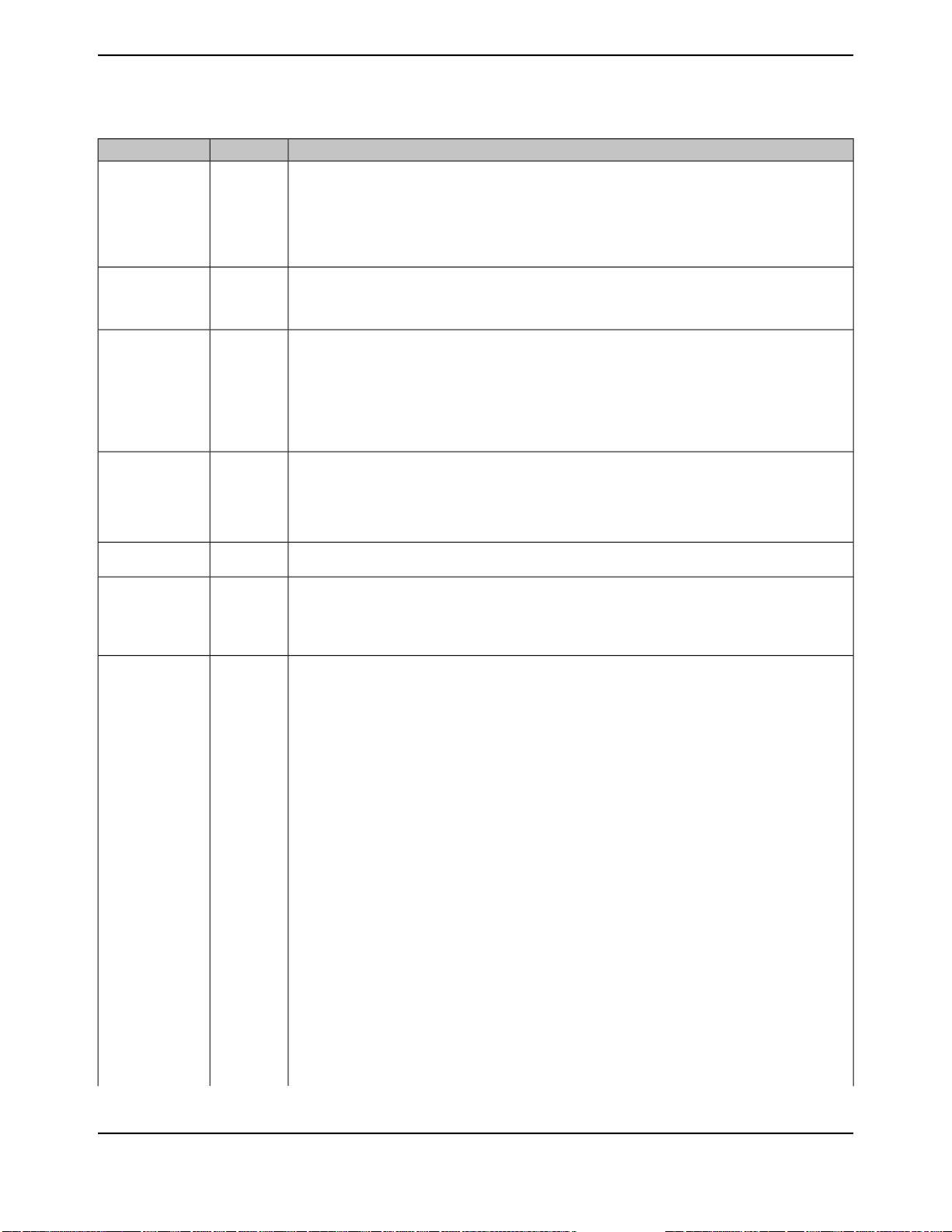

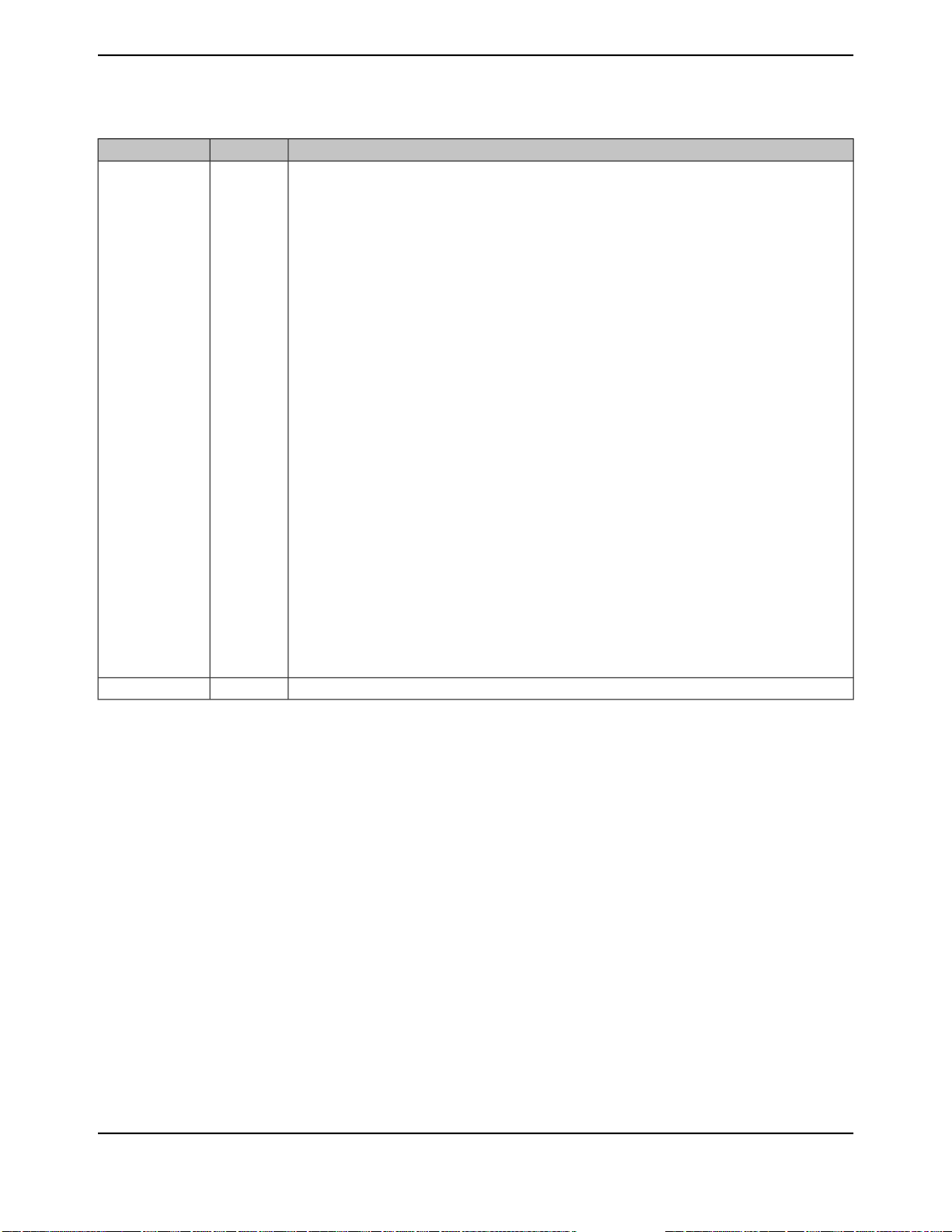

Table 2. Documentation Conventions ................................................................................ 24

Table 2-1. Summary of Processor Mode, Privilege Level, and Stack Use ................................ 44

Table 2-2. Processor Register Map ....................................................................................... 45

Table 2-3. PSR Register Combinations ................................................................................. 50

Table 2-4. Memory Map ....................................................................................................... 58

Table 2-5. Memory Access Behavior ..................................................................................... 60

Table 2-6. SRAM Memory Bit-Banding Regions .................................................................... 62

Table 2-7. Peripheral Memory Bit-Banding Regions ............................................................... 62

Table 2-8. Exception Types .................................................................................................. 68

Table 2-9. Interrupts ............................................................................................................ 69

Table 2-10. Exception Return Behavior ................................................................................... 73

Table 2-11. Faults ................................................................................................................. 74

Table 2-12. Fault Status and Fault Address Registers .............................................................. 75

Table 2-13. Cortex-M3 Instruction Summary ........................................................................... 77

Table 3-1. Core Peripheral Register Regions ......................................................................... 81

Table 3-2. Memory Attributes Summary ................................................................................ 84

Table 3-3. TEX, S, C, and B Bit Field Encoding ..................................................................... 87

Table 3-4. Cache Policy for Memory Attribute Encoding ......................................................... 88

Table 3-5. AP Bit Field Encoding .......................................................................................... 88

Table 3-6. Memory Region Attributes for Stellaris®Microcontrollers ........................................ 88

Table 3-7. Peripherals Register Map ..................................................................................... 89

Table 3-8. Interrupt Priority Levels ...................................................................................... 115

Table 3-9. Example SIZE Field Values ................................................................................ 144

Table 4-1. JTAG Port Pins Reset State ............................................................................... 149

Table 4-2. JTAG Instruction Register Commands ................................................................. 154

Table 5-1. Clock Source Options ........................................................................................ 164

Table 5-2. Possible System Clock Frequencies Using the SYSDIV Field ............................... 167

Table 5-3. Examples of Possible System Clock Frequencies Using the SYSDIV2 Field .......... 167

Table 5-4. System Control Register Map ............................................................................. 171

Table 5-5. RCC2 Fields that Override RCC fields ................................................................. 185

Table 6-1. Hibernation Module Register Map ....................................................................... 224

Table 7-1. Flash Protection Policy Combinations ................................................................. 238

Table 7-2. User-Programmable Flash Memory Resident Registers ....................................... 240

Table 7-3. Flash Register Map ............................................................................................ 241

Table 8-1. GPIO Pad Configuration Examples ..................................................................... 267

Table 8-2. GPIO Interrupt Configuration Example ................................................................ 267

Table 8-3. GPIO Register Map ........................................................................................... 268

Table 9-1. Available CCP Pins ............................................................................................ 305

Table 9-2. 16-Bit Timer With Prescaler Configurations ......................................................... 308

Table 9-3. Timers Register Map .......................................................................................... 314

Table 10-1. Watchdog Timer Register Map ............................................................................ 342

Table 11-1. UART Register Map ........................................................................................... 370

Table 12-1. SSI Register Map .............................................................................................. 415

Table 13-1. Internal Reference Voltage and ACREFCTL Field Values ..................................... 444

Table 13-2. Analog Comparators Register Map ..................................................................... 445

Stellaris® LM3S1110 Microcontroller

Texas Instruments-Production Data

11September 04, 2010

Table of Contents

Table 15-1. Signals by Pin Number ....................................................................................... 455

Table 15-2. Signals by Signal Name ..................................................................................... 459

Table 15-3. Signals by Function, Except for GPIO ................................................................. 462

Table 15-4. GPIO Pins and Alternate Functions ..................................................................... 465

Table 15-5. Signals by Pin Number ....................................................................................... 466

Table 15-6. Signals by Signal Name ..................................................................................... 470

Table 15-7. Signals by Function, Except for GPIO ................................................................. 473

Table 15-8. GPIO Pins and Alternate Functions ..................................................................... 476

Table 15-9. Connections for Unused Signals (100-pin LQFP) ................................................. 477

Table 15-10. Connections for Unused Signals, 108-pin BGA .................................................... 478

Table 16-1. Temperature Characteristics ............................................................................... 479

Table 16-2. Thermal Characteristics ..................................................................................... 479

Table 16-3. ESD Absolute Maximum Ratings ........................................................................ 479

Table 17-1. Maximum Ratings .............................................................................................. 480

Table 17-2. Recommended DC Operating Conditions ............................................................ 480

Table 17-3. LDO Regulator Characteristics ........................................................................... 481

Table 17-4. GPIO Module DC Characteristics ........................................................................ 481

Table 17-5. Detailed Power Specifications ............................................................................ 482

Table 17-6. Flash Memory Characteristics ............................................................................ 483

Table 17-7. Hibernation Module DC Characteristics ............................................................... 483

Table 17-8. Phase Locked Loop (PLL) Characteristics ........................................................... 484

Table 17-9. Actual PLL Frequency ........................................................................................ 484

Table 17-10. Clock Characteristics ......................................................................................... 484

Table 17-11. Crystal Characteristics ....................................................................................... 485

Table 17-12. JTAG Characteristics ......................................................................................... 485

Table 17-13. Reset Characteristics ......................................................................................... 487

Table 17-14. Sleep Modes AC Characteristics ......................................................................... 489

Table 17-15. Hibernation Module AC Characteristics ............................................................... 489

Table 17-16. GPIO Characteristics ......................................................................................... 490

Table 17-17. SSI Characteristics ............................................................................................ 490

Table 17-18. Analog Comparator Characteristics ..................................................................... 491

Table 17-19. Analog Comparator Voltage Reference Characteristics ........................................ 492

Table C-1. Part Ordering Information ................................................................................... 514

Texas Instruments-Production Data

September 04, 201012

Stellaris® LM3S1110 Microcontroller

List of Registers

The Cortex-M3 Processor ............................................................................................................. 39

Register 1: Cortex General-Purpose Register 0 (R0) ........................................................................... 46

Register 2: Cortex General-Purpose Register 1 (R1) ........................................................................... 46

Register 3: Cortex General-Purpose Register 2 (R2) ........................................................................... 46

Register 4: Cortex General-Purpose Register 3 (R3) ........................................................................... 46

Register 5: Cortex General-Purpose Register 4 (R4) ........................................................................... 46

Register 6: Cortex General-Purpose Register 5 (R5) ........................................................................... 46

Register 7: Cortex General-Purpose Register 6 (R6) ........................................................................... 46

Register 8: Cortex General-Purpose Register 7 (R7) ........................................................................... 46

Register 9: Cortex General-Purpose Register 8 (R8) ........................................................................... 46

Register 10: Cortex General-Purpose Register 9 (R9) ........................................................................... 46

Register 11: Cortex General-Purpose Register 10 (R10) ....................................................................... 46

Register 12: Cortex General-Purpose Register 11 (R11) ........................................................................ 46

Register 13: Cortex General-Purpose Register 12 (R12) ....................................................................... 46

Register 14: Stack Pointer (SP) ........................................................................................................... 47

Register 15: Link Register (LR) ............................................................................................................ 48

Register 16: Program Counter (PC) ..................................................................................................... 49

Register 17: Program Status Register (PSR) ........................................................................................ 50

Register 18: Priority Mask Register (PRIMASK) .................................................................................... 54

Register 19: Fault Mask Register (FAULTMASK) .................................................................................. 55

Register 20: Base Priority Mask Register (BASEPRI) ............................................................................ 56

Register 21: Control Register (CONTROL) ........................................................................................... 57

Cortex-M3 Peripherals ................................................................................................................... 81

Register 1: SysTick Control and Status Register (STCTRL), offset 0x010 ............................................. 92

Register 2: SysTick Reload Value Register (STRELOAD), offset 0x014 ................................................ 94

Register 3: SysTick Current Value Register (STCURRENT), offset 0x018 ............................................. 95

Register 4: Interrupt 0-31 Set Enable (EN0), offset 0x100 .................................................................... 96

Register 5: Interrupt 32-43 Set Enable (EN1), offset 0x104 .................................................................. 97

Register 6: Interrupt 0-31 Clear Enable (DIS0), offset 0x180 ................................................................ 98

Register 7: Interrupt 32-43 Clear Enable (DIS1), offset 0x184 .............................................................. 99

Register 8: Interrupt 0-31 Set Pending (PEND0), offset 0x200 ........................................................... 100

Register 9: Interrupt 32-43 Set Pending (PEND1), offset 0x204 ......................................................... 101

Register 10: Interrupt 0-31 Clear Pending (UNPEND0), offset 0x280 ................................................... 102

Register 11: Interrupt 32-43 Clear Pending (UNPEND1), offset 0x284 .................................................. 103

Register 12: Interrupt 0-31 Active Bit (ACTIVE0), offset 0x300 ............................................................. 104

Register 13: Interrupt 32-43 Active Bit (ACTIVE1), offset 0x304 ........................................................... 105

Register 14: Interrupt 0-3 Priority (PRI0), offset 0x400 ......................................................................... 106

Register 15: Interrupt 4-7 Priority (PRI1), offset 0x404 ......................................................................... 106

Register 16: Interrupt 8-11 Priority (PRI2), offset 0x408 ....................................................................... 106

Register 17: Interrupt 12-15 Priority (PRI3), offset 0x40C .................................................................... 106

Register 18: Interrupt 16-19 Priority (PRI4), offset 0x410 ..................................................................... 106

Register 19: Interrupt 20-23 Priority (PRI5), offset 0x414 ..................................................................... 106

Register 20: Interrupt 24-27 Priority (PRI6), offset 0x418 ..................................................................... 106

Register 21: Interrupt 28-31 Priority (PRI7), offset 0x41C .................................................................... 106

Register 22: Interrupt 32-35 Priority (PRI8), offset 0x420 ..................................................................... 106

Texas Instruments-Production Data

13September 04, 2010

Table of Contents

Register 23: Interrupt 36-39 Priority (PRI9), offset 0x424 ..................................................................... 106

Register 24: Interrupt 40-43 Priority (PRI10), offset 0x428 ................................................................... 106

Register 25: Software Trigger Interrupt (SWTRIG), offset 0xF00 .......................................................... 108

Register 26: CPU ID Base (CPUID), offset 0xD00 ............................................................................... 109

Register 27: Interrupt Control and State (INTCTRL), offset 0xD04 ........................................................ 110

Register 28: Vector Table Offset (VTABLE), offset 0xD08 .................................................................... 114

Register 29: Application Interrupt and Reset Control (APINT), offset 0xD0C ......................................... 115

Register 30: System Control (SYSCTRL), offset 0xD10 ....................................................................... 117

Register 31: Configuration and Control (CFGCTRL), offset 0xD14 ....................................................... 119

Register 32: System Handler Priority 1 (SYSPRI1), offset 0xD18 ......................................................... 121

Register 33: System Handler Priority 2 (SYSPRI2), offset 0xD1C ........................................................ 122

Register 34: System Handler Priority 3 (SYSPRI3), offset 0xD20 ......................................................... 123

Register 35: System Handler Control and State (SYSHNDCTRL), offset 0xD24 .................................... 124

Register 36: Configurable Fault Status (FAULTSTAT), offset 0xD28 ..................................................... 128

Register 37: Hard Fault Status (HFAULTSTAT), offset 0xD2C .............................................................. 134

Register 38: Memory Management Fault Address (MMADDR), offset 0xD34 ........................................ 136

Register 39: Bus Fault Address (FAULTADDR), offset 0xD38 .............................................................. 137

Register 40: MPU Type (MPUTYPE), offset 0xD90 ............................................................................. 138

Register 41: MPU Control (MPUCTRL), offset 0xD94 .......................................................................... 139

Register 42: MPU Region Number (MPUNUMBER), offset 0xD98 ....................................................... 141

Register 43: MPU Region Base Address (MPUBASE), offset 0xD9C ................................................... 142

Register 44: MPU Region Base Address Alias 1 (MPUBASE1), offset 0xDA4 ....................................... 142

Register 45: MPU Region Base Address Alias 2 (MPUBASE2), offset 0xDAC ...................................... 142

Register 46: MPU Region Base Address Alias 3 (MPUBASE3), offset 0xDB4 ....................................... 142

Register 47: MPU Region Attribute and Size (MPUATTR), offset 0xDA0 ............................................... 144

Register 48: MPU Region Attribute and Size Alias 1 (MPUATTR1), offset 0xDA8 .................................. 144

Register 49: MPU Region Attribute and Size Alias 2 (MPUATTR2), offset 0xDB0 .................................. 144

Register 50: MPU Region Attribute and Size Alias 3 (MPUATTR3), offset 0xDB8 .................................. 144

System Control ............................................................................................................................ 159

Register 1: Device Identification 0 (DID0), offset 0x000 ..................................................................... 173

Register 2: Brown-Out Reset Control (PBORCTL), offset 0x030 ........................................................ 175

Register 3: LDO Power Control (LDOPCTL), offset 0x034 ................................................................. 176

Register 4: Raw Interrupt Status (RIS), offset 0x050 .......................................................................... 177

Register 5: Interrupt Mask Control (IMC), offset 0x054 ...................................................................... 178

Register 6: Masked Interrupt Status and Clear (MISC), offset 0x058 .................................................. 179

Register 7: Reset Cause (RESC), offset 0x05C ................................................................................ 180

Register 8: Run-Mode Clock Configuration (RCC), offset 0x060 ......................................................... 181

Register 9: XTAL to PLL Translation (PLLCFG), offset 0x064 ............................................................. 184

Register 10: Run-Mode Clock Configuration 2 (RCC2), offset 0x070 .................................................... 185

Register 11: Deep Sleep Clock Configuration (DSLPCLKCFG), offset 0x144 ........................................ 187

Register 12: Device Identification 1 (DID1), offset 0x004 ..................................................................... 188

Register 13: Device Capabilities 0 (DC0), offset 0x008 ........................................................................ 190

Register 14: Device Capabilities 1 (DC1), offset 0x010 ........................................................................ 191

Register 15: Device Capabilities 2 (DC2), offset 0x014 ........................................................................ 193

Register 16: Device Capabilities 3 (DC3), offset 0x018 ........................................................................ 195

Register 17: Device Capabilities 4 (DC4), offset 0x01C ....................................................................... 197

Register 18: Run Mode Clock Gating Control Register 0 (RCGC0), offset 0x100 ................................... 198

Register 19: Sleep Mode Clock Gating Control Register 0 (SCGC0), offset 0x110 ................................. 199

Texas Instruments-Production Data

September 04, 201014

Stellaris® LM3S1110 Microcontroller

Register 20: Deep Sleep Mode Clock Gating Control Register 0 (DCGC0), offset 0x120 ....................... 200

Register 21: Run Mode Clock Gating Control Register 1 (RCGC1), offset 0x104 ................................... 201

Register 22: Sleep Mode Clock Gating Control Register 1 (SCGC1), offset 0x114 ................................. 203

Register 23: Deep Sleep Mode Clock Gating Control Register 1 (DCGC1), offset 0x124 ....................... 205

Register 24: Run Mode Clock Gating Control Register 2 (RCGC2), offset 0x108 ................................... 207

Register 25: Sleep Mode Clock Gating Control Register 2 (SCGC2), offset 0x118 ................................. 209

Register 26: Deep Sleep Mode Clock Gating Control Register 2 (DCGC2), offset 0x128 ....................... 211

Register 27: Software Reset Control 0 (SRCR0), offset 0x040 ............................................................. 213

Register 28: Software Reset Control 1 (SRCR1), offset 0x044 ............................................................. 214

Register 29: Software Reset Control 2 (SRCR2), offset 0x048 ............................................................. 216

Hibernation Module ..................................................................................................................... 217

Register 1: Hibernation RTC Counter (HIBRTCC), offset 0x000 ......................................................... 225

Register 2: Hibernation RTC Match 0 (HIBRTCM0), offset 0x004 ....................................................... 226

Register 3: Hibernation RTC Match 1 (HIBRTCM1), offset 0x008 ....................................................... 227

Register 4: Hibernation RTC Load (HIBRTCLD), offset 0x00C ........................................................... 228

Register 5: Hibernation Control (HIBCTL), offset 0x010 ..................................................................... 229

Register 6: Hibernation Interrupt Mask (HIBIM), offset 0x014 ............................................................. 231

Register 7: Hibernation Raw Interrupt Status (HIBRIS), offset 0x018 .................................................. 232

Register 8: Hibernation Masked Interrupt Status (HIBMIS), offset 0x01C ............................................ 233

Register 9: Hibernation Interrupt Clear (HIBIC), offset 0x020 ............................................................. 234

Register 10: Hibernation RTC Trim (HIBRTCT), offset 0x024 ............................................................... 235

Register 11: Hibernation Data (HIBDATA), offset 0x030-0x12C ............................................................ 236

Internal Memory ........................................................................................................................... 237

Register 1: Flash Memory Address (FMA), offset 0x000 .................................................................... 243

Register 2: Flash Memory Data (FMD), offset 0x004 ......................................................................... 244

Register 3: Flash Memory Control (FMC), offset 0x008 ..................................................................... 245

Register 4: Flash Controller Raw Interrupt Status (FCRIS), offset 0x00C ............................................ 247

Register 5: Flash Controller Interrupt Mask (FCIM), offset 0x010 ........................................................ 248

Register 6: Flash Controller Masked Interrupt Status and Clear (FCMISC), offset 0x014 ..................... 249

Register 7: USec Reload (USECRL), offset 0x140 ............................................................................ 251

Register 8: Flash Memory Protection Read Enable 0 (FMPRE0), offset 0x130 and 0x200 ................... 252

Register 9: Flash Memory Protection Program Enable 0 (FMPPE0), offset 0x134 and 0x400 ............... 253

Register 10: User Debug (USER_DBG), offset 0x1D0 ......................................................................... 254

Register 11: User Register 0 (USER_REG0), offset 0x1E0 .................................................................. 255

Register 12: User Register 1 (USER_REG1), offset 0x1E4 .................................................................. 256

Register 13: Flash Memory Protection Read Enable 1 (FMPRE1), offset 0x204 .................................... 257

Register 14: Flash Memory Protection Read Enable 2 (FMPRE2), offset 0x208 .................................... 258

Register 15: Flash Memory Protection Read Enable 3 (FMPRE3), offset 0x20C ................................... 259

Register 16: Flash Memory Protection Program Enable 1 (FMPPE1), offset 0x404 ............................... 260

Register 17: Flash Memory Protection Program Enable 2 (FMPPE2), offset 0x408 ............................... 261

Register 18: Flash Memory Protection Program Enable 3 (FMPPE3), offset 0x40C ............................... 262

General-Purpose Input/Outputs (GPIOs) ................................................................................... 263

Register 1: GPIO Data (GPIODATA), offset 0x000 ............................................................................ 270

Register 2: GPIO Direction (GPIODIR), offset 0x400 ......................................................................... 271

Register 3: GPIO Interrupt Sense (GPIOIS), offset 0x404 .................................................................. 272

Register 4: GPIO Interrupt Both Edges (GPIOIBE), offset 0x408 ........................................................ 273

Register 5: GPIO Interrupt Event (GPIOIEV), offset 0x40C ................................................................ 274

Register 6: GPIO Interrupt Mask (GPIOIM), offset 0x410 ................................................................... 275

Texas Instruments-Production Data

15September 04, 2010

Table of Contents

Register 7: GPIO Raw Interrupt Status (GPIORIS), offset 0x414 ........................................................ 276

Register 8: GPIO Masked Interrupt Status (GPIOMIS), offset 0x418 ................................................... 277

Register 9: GPIO Interrupt Clear (GPIOICR), offset 0x41C ................................................................ 278

Register 10: GPIO Alternate Function Select (GPIOAFSEL), offset 0x420 ............................................ 279

Register 11: GPIO 2-mA Drive Select (GPIODR2R), offset 0x500 ........................................................ 281

Register 12: GPIO 4-mA Drive Select (GPIODR4R), offset 0x504 ........................................................ 282

Register 13: GPIO 8-mA Drive Select (GPIODR8R), offset 0x508 ........................................................ 283

Register 14: GPIO Open Drain Select (GPIOODR), offset 0x50C ......................................................... 284

Register 15: GPIO Pull-Up Select (GPIOPUR), offset 0x510 ................................................................ 285

Register 16: GPIO Pull-Down Select (GPIOPDR), offset 0x514 ........................................................... 286

Register 17: GPIO Slew Rate Control Select (GPIOSLR), offset 0x518 ................................................ 287

Register 18: GPIO Digital Enable (GPIODEN), offset 0x51C ................................................................ 288

Register 19: GPIO Lock (GPIOLOCK), offset 0x520 ............................................................................ 289

Register 20: GPIO Commit (GPIOCR), offset 0x524 ............................................................................ 290

Register 21: GPIO Peripheral Identification 4 (GPIOPeriphID4), offset 0xFD0 ....................................... 292

Register 22: GPIO Peripheral Identification 5 (GPIOPeriphID5), offset 0xFD4 ....................................... 293

Register 23: GPIO Peripheral Identification 6 (GPIOPeriphID6), offset 0xFD8 ....................................... 294

Register 24: GPIO Peripheral Identification 7 (GPIOPeriphID7), offset 0xFDC ...................................... 295

Register 25: GPIO Peripheral Identification 0 (GPIOPeriphID0), offset 0xFE0 ....................................... 296

Register 26: GPIO Peripheral Identification 1 (GPIOPeriphID1), offset 0xFE4 ....................................... 297

Register 27: GPIO Peripheral Identification 2 (GPIOPeriphID2), offset 0xFE8 ....................................... 298

Register 28: GPIO Peripheral Identification 3 (GPIOPeriphID3), offset 0xFEC ...................................... 299

Register 29: GPIO PrimeCell Identification 0 (GPIOPCellID0), offset 0xFF0 .......................................... 300

Register 30: GPIO PrimeCell Identification 1 (GPIOPCellID1), offset 0xFF4 .......................................... 301

Register 31: GPIO PrimeCell Identification 2 (GPIOPCellID2), offset 0xFF8 .......................................... 302

Register 32: GPIO PrimeCell Identification 3 (GPIOPCellID3), offset 0xFFC ......................................... 303

General-Purpose Timers ............................................................................................................. 304

Register 1: GPTM Configuration (GPTMCFG), offset 0x000 .............................................................. 316

Register 2: GPTM TimerA Mode (GPTMTAMR), offset 0x004 ............................................................ 317

Register 3: GPTM TimerB Mode (GPTMTBMR), offset 0x008 ............................................................ 319

Register 4: GPTM Control (GPTMCTL), offset 0x00C ........................................................................ 321

Register 5: GPTM Interrupt Mask (GPTMIMR), offset 0x018 .............................................................. 324

Register 6: GPTM Raw Interrupt Status (GPTMRIS), offset 0x01C ..................................................... 326

Register 7: GPTM Masked Interrupt Status (GPTMMIS), offset 0x020 ................................................ 327

Register 8: GPTM Interrupt Clear (GPTMICR), offset 0x024 .............................................................. 328

Register 9: GPTM TimerA Interval Load (GPTMTAILR), offset 0x028 ................................................. 330

Register 10: GPTM TimerB Interval Load (GPTMTBILR), offset 0x02C ................................................ 331

Register 11: GPTM TimerA Match (GPTMTAMATCHR), offset 0x030 ................................................... 332

Register 12: GPTM TimerB Match (GPTMTBMATCHR), offset 0x034 .................................................. 333

Register 13: GPTM TimerA Prescale (GPTMTAPR), offset 0x038 ........................................................ 334

Register 14: GPTM TimerB Prescale (GPTMTBPR), offset 0x03C ....................................................... 335

Register 15: GPTM TimerA Prescale Match (GPTMTAPMR), offset 0x040 ........................................... 336

Register 16: GPTM TimerB Prescale Match (GPTMTBPMR), offset 0x044 ........................................... 337

Register 17: GPTM TimerA (GPTMTAR), offset 0x048 ........................................................................ 338

Register 18: GPTM TimerB (GPTMTBR), offset 0x04C ....................................................................... 339

Watchdog Timer ........................................................................................................................... 340

Register 1: Watchdog Load (WDTLOAD), offset 0x000 ...................................................................... 344

Register 2: Watchdog Value (WDTVALUE), offset 0x004 ................................................................... 345

Texas Instruments-Production Data

September 04, 201016

Stellaris® LM3S1110 Microcontroller

Register 3: Watchdog Control (WDTCTL), offset 0x008 ..................................................................... 346

Register 4: Watchdog Interrupt Clear (WDTICR), offset 0x00C .......................................................... 347

Register 5: Watchdog Raw Interrupt Status (WDTRIS), offset 0x010 .................................................. 348

Register 6: Watchdog Masked Interrupt Status (WDTMIS), offset 0x014 ............................................. 349

Register 7: Watchdog Test (WDTTEST), offset 0x418 ....................................................................... 350

Register 8: Watchdog Lock (WDTLOCK), offset 0xC00 ..................................................................... 351

Register 9: Watchdog Peripheral Identification 4 (WDTPeriphID4), offset 0xFD0 ................................. 352

Register 10: Watchdog Peripheral Identification 5 (WDTPeriphID5), offset 0xFD4 ................................. 353

Register 11: Watchdog Peripheral Identification 6 (WDTPeriphID6), offset 0xFD8 ................................. 354

Register 12: Watchdog Peripheral Identification 7 (WDTPeriphID7), offset 0xFDC ................................ 355

Register 13: Watchdog Peripheral Identification 0 (WDTPeriphID0), offset 0xFE0 ................................. 356

Register 14: Watchdog Peripheral Identification 1 (WDTPeriphID1), offset 0xFE4 ................................. 357