Texas Instruments SNJ54LVT646FK, SNJ54LVT646JT, SNJ54LVT646W Datasheet

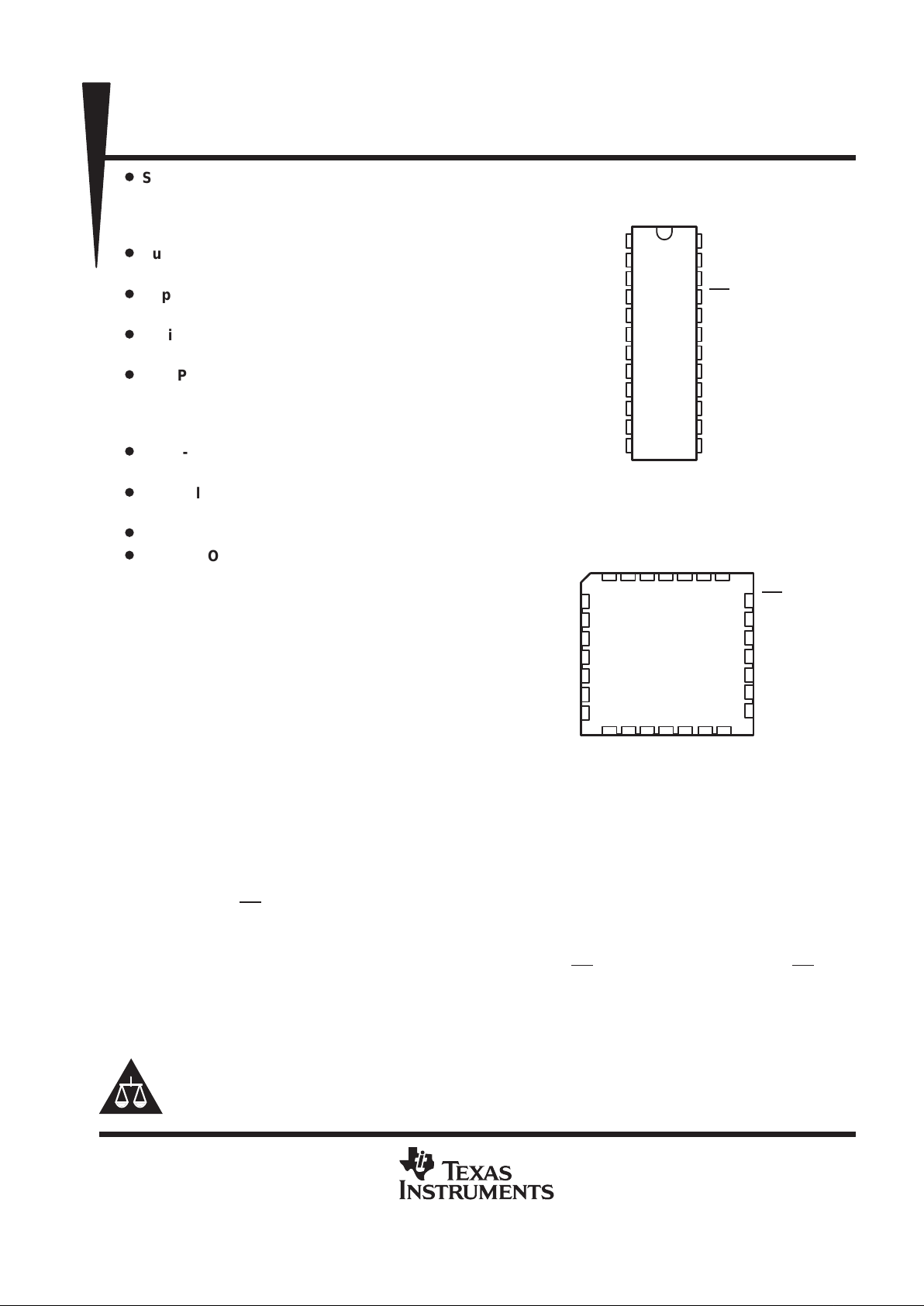

SN54LVT646...JT OR W PACKAGE

SN74LVT646. . . DB, DW, OR PW PACKAGE

(TOP VIEW)

5

6

7

8

9

10

11

25

24

23

22

21

20

19

432128

12 13 14 15

16

OE

B1

B2

NC

B3

B4

B5

A1

A2

A3

NC

A4

A5

A6

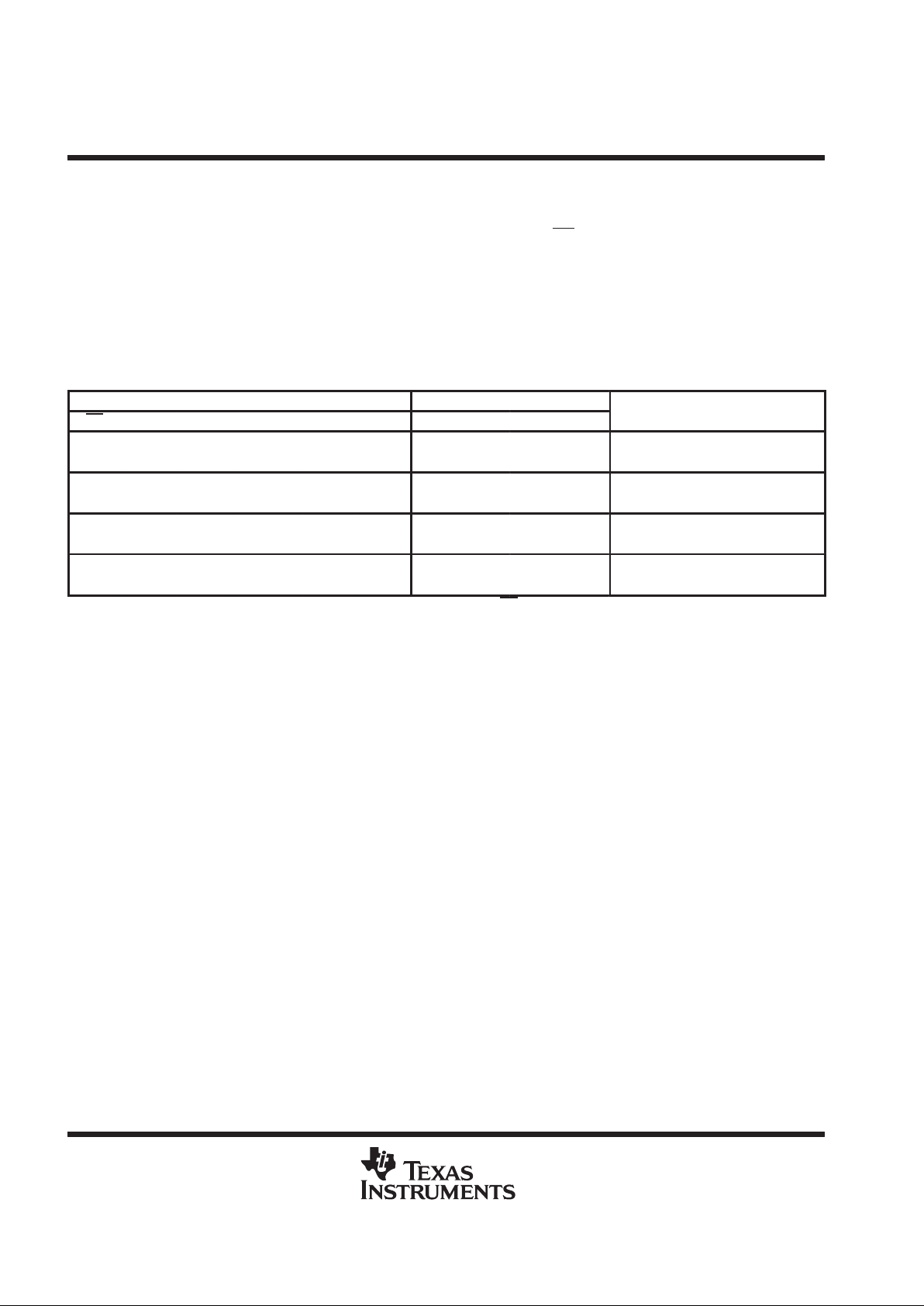

SN54LVT646. . . FK PACKAGE

(TOP VIEW)

DIR

SAB

CLKAB

B8

B7

A8

GND

NC

NC

CLKBA

SBA

V

A7

B6

17 18

27 26

NC – No internal connection

CC

CLKAB

SAB

DIR

A1

A2

A3

A4

A5

A6

A7

A8

GND

V

CC

CLKBA

SBA

OE

B1

B2

B3

B4

B5

B6

B7

B8

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

SN54LVT646, SN74LVT646

3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCBS140D – MA Y 1992 – REVISED JULY 1995

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

State-of-the-Art Advanced BiCMOS

Technology (ABT) Design for 3.3-V

Operation and Low Static Power

Dissipation

D

Support Mixed-Mode Signal Operation (5-V

Input and Output Voltages With 3.3-V VCC)

D

Support Unregulated Battery Operation

Down to 2.7 V

D

T ypical V

OLP

(Output Ground Bounce)

< 0.8 V at V

CC

= 3.3 V, TA = 25°C

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883C, Method 3015; Exceeds

200 V Using Machine Model

(C = 200 pF, R = 0)

D

Latch-Up Performance Exceeds 500 mA

Per JEDEC Standard JESD-17

D

Bus-Hold Data Inputs Eliminate the Need

for External Pullup Resistors

D

Support Live Insertion

D

Package Options Include Plastic

Small-Outline (DW), Shrink Small-Outline

(DB), and and Thin Shrink Small-Outline

(PW) Packages, Ceramic Chip Carriers

(FK), Ceramic Flat (W) Packages, and

Ceramic (JT) DIPs

description

These bus transceivers and registers are

designed specifically for low-voltage (3.3-V) V

CC

operation, but with the capability to provide a TTL

interface to a 5-V system environment.

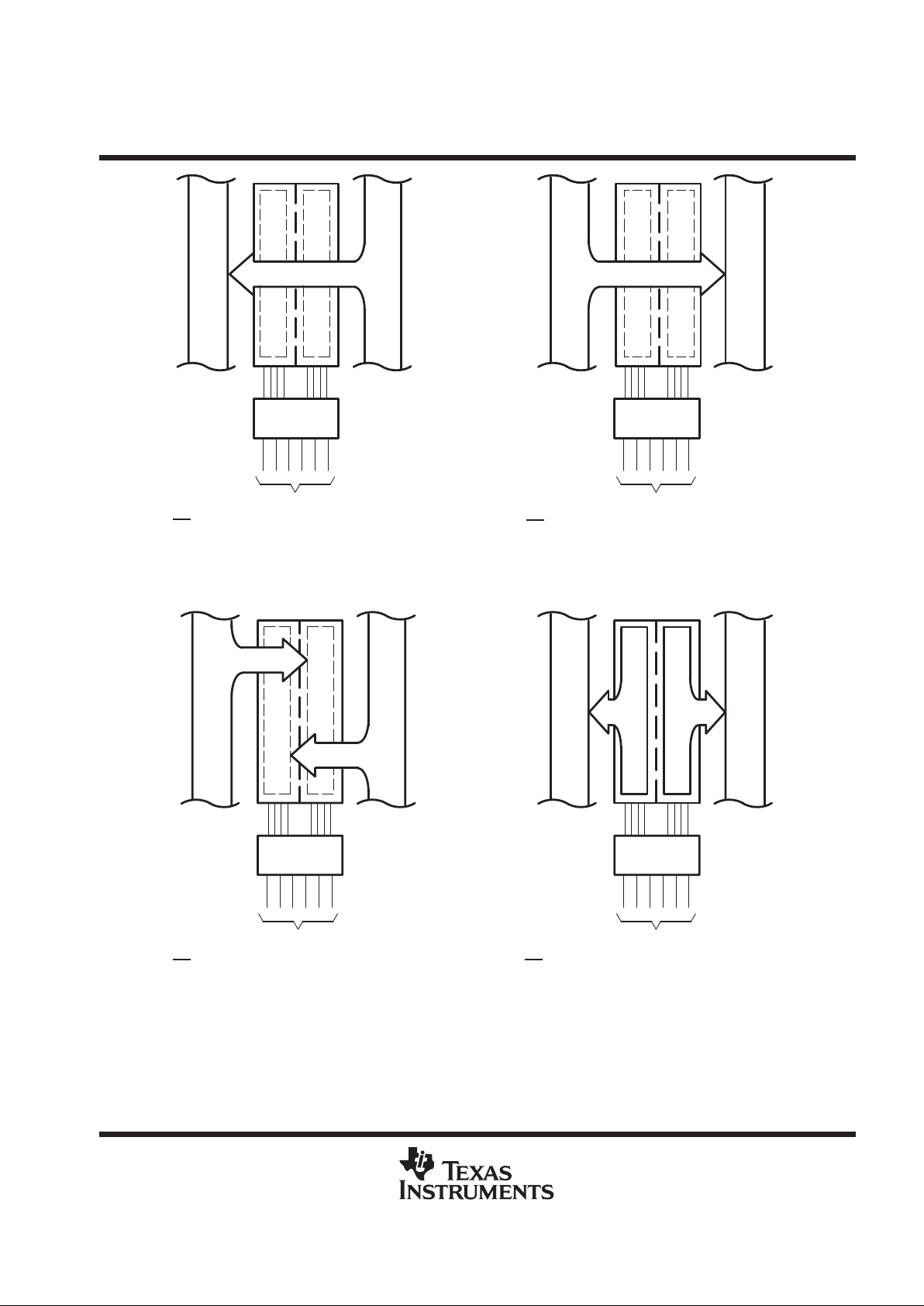

The ’LVT646 consist of bus transceiver circuits,

D-type flip-flops, and control circuitry arranged for

multiplexed transmission of data directly from the

input bus or from the internal registers. Data on the A or B bus is clocked into the registers on the low-to-high

transition of the appropriate clock (CLKAB or CLKBA) input. Figure 1 illustrates the four fundamental

bus-management functions that can be performed with the ′LVT646.

Output-enable (OE

) and direction-control (DIR) inputs are provided to control the transceiver functions. In the

transceiver mode, data present at the high-impedance port may be stored in either register or in both.

The select-control (SAB and SBA) inputs can multiplex stored and real-time (transparent mode) data. The

direction control (DIR) determines which bus receives data when OE is low. In the isolation mode (OE high),

A data may be stored in one register and/or B data may be stored in the other register.

When an output function is disabled, the input function is still enabled and may be used to store and transmit

data. Only one of the two buses, A or B, may be driven at a time.

Copyright 1995, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN54LVT646, SN74LVT646

3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCBS140D – MA Y 1992 – REVISED JULY 1995

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

T o ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74L VT646 is available in TI’s shrink small-outline package (DB), which provides the same I/O pin count

and functionality of standard small-outline packages in less than half the printed-circuit-board area.

The SN54L VT646 is characterized for operation over the full military temperature range of –55°C to 125°C. The

SN74LVT646 is characterized for operation from –40°C to 85°C.

FUNCTION TABLE

INPUTS

DATA I/Os

OE DIR CLKAB CLKBA SAB SBA A1–A8 B1–B8

OPERATION OR FUNCTION

X X ↑ X X X Input Unspecified

†

Store A, B unspecified

†

X XX ↑ X X Unspecified

†

Input Store B, A unspecified

†

H X ↑ ↑ X X Input Input Store A and B data

H X H or L H or L X X Input disabled Input disabled Isolation, hold storage

L L X X X L Output Input Real-time B data to A bus

L L X H or L X H Output Input Stored B data to A bus

L H X X L X Input Output Real-time A data to B bus

L H H or L X H X Input Output Stored A data to B bus

†

The data output functions may be enabled or disabled by various signals at the OE and DIR inputs. Data input functions are always enabled;

i.e., data at the bus pins is stored on every low-to-high transition of the clock inputs.

SN54LVT646, SN74LVT646

3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCBS140D – MA Y 1992 – REVISED JULY 1995

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

21

L

3

DIR

L

1

CLKAB

X

23

CLKBA

X

2

SAB

X

22

SBA

L

REAL-TIME TRANSFER

BUS B TO BUS A

21

L

3

DIR

H

1

CLKAB

X

23

CLKBA

X

2

SAB

L

22

SBA

X

REAL-TIME TRANSFER

BUS A TO BUS B

21

X

3

DIR

X

1

CLKAB23CLKBA

X

2

SAB

X

22

SBA

X

STORAGE FROM

A, B, OR A AND B

21

L

3

DIR

L

1

CLKAB

X

23

CLKBA

H or L

2

SAB

X

22

SBA

H

TRANSFER STORED DATA

TO A AND/OR B

X

H

X

X

XX

X

X

X

L H H or L X H X

↑

↑

↑↑

BUS B

BUS A

BUS B

BUS A

BUS B

BUS A

BUS B

BUS A

OE

OE

OEOE

Figure 1. Bus-Management Functions

Pin numbers shown are for the DB, DW, JT, PW, and W packages.

Loading...

Loading...