SN75LVDS88B

TFT LCD PANEL TIMING CONTROLLER

WITH LVDS INTERF ACE

SLLS407 – FEBRUARY 2000

D

Flatlink Interface Utilizes Low Power

Differential Signalling(LVDS)

D

Suitable for Notebook Application

D

XGA Resolution

D

Six Bit System Interface

D

Support Mainstream Data and Gate Drivers

D

Optional Configurable Pins

description

The SN75L VDS88B (LVDS panel timing controller) integrates a Flatlink signal interface with a TFT LCD timing

controller. It resides in the LCD panel and provides interface between the graphic controller and a TFT LCD

panel.

The SN75L VDS88B accepts host data through 3 pairs of inputs (18-bits) making up the LVDS bus, which is a

low-EMI high-throughput interface. SN75L VDS88B then reformats the received image data into a specific data

format and synchronous timing suitable for driving LCD panel column and row drivers. This device supports

XGA resolution.

The SN75LVDS88B is easily configured by several selection terminals and is equipped with default timing

specifications to support mainstream gate and source drivers on the market.

D

Low Voltage CMOS 3.3 V T echnology

D

65 MHz Phase-Lock Input

D

100-pin TQFP Package for Compact LCD

Module

D

Tolerates 4 kV HBM ESD for LVDS Pins and

2 kV HBM for Others

D

Improved Jitter Tolerance

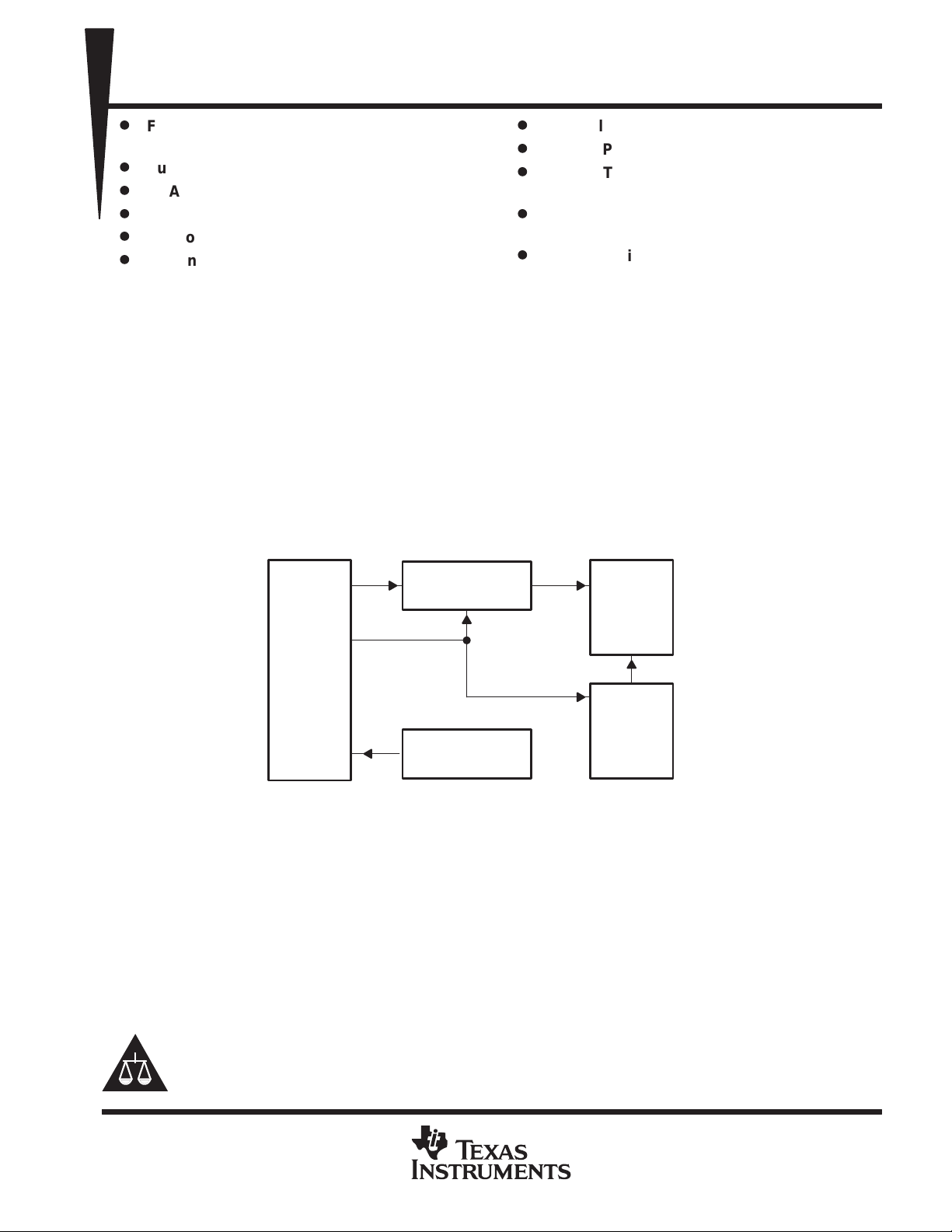

block diagram

Flatlink

(18-bit)

Data Alignment

SYNC

CTRL

Interface

Source

Data

Format

Timing

Signal

Generator

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Flatlink is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 2000, Texas Instruments Incorporated

1

SN75LVDS88B

TFT LCD PANEL TIMING CONTROLLER

WITH LVDS INTERF ACE

SLLS407 – FEBRUARY 2000

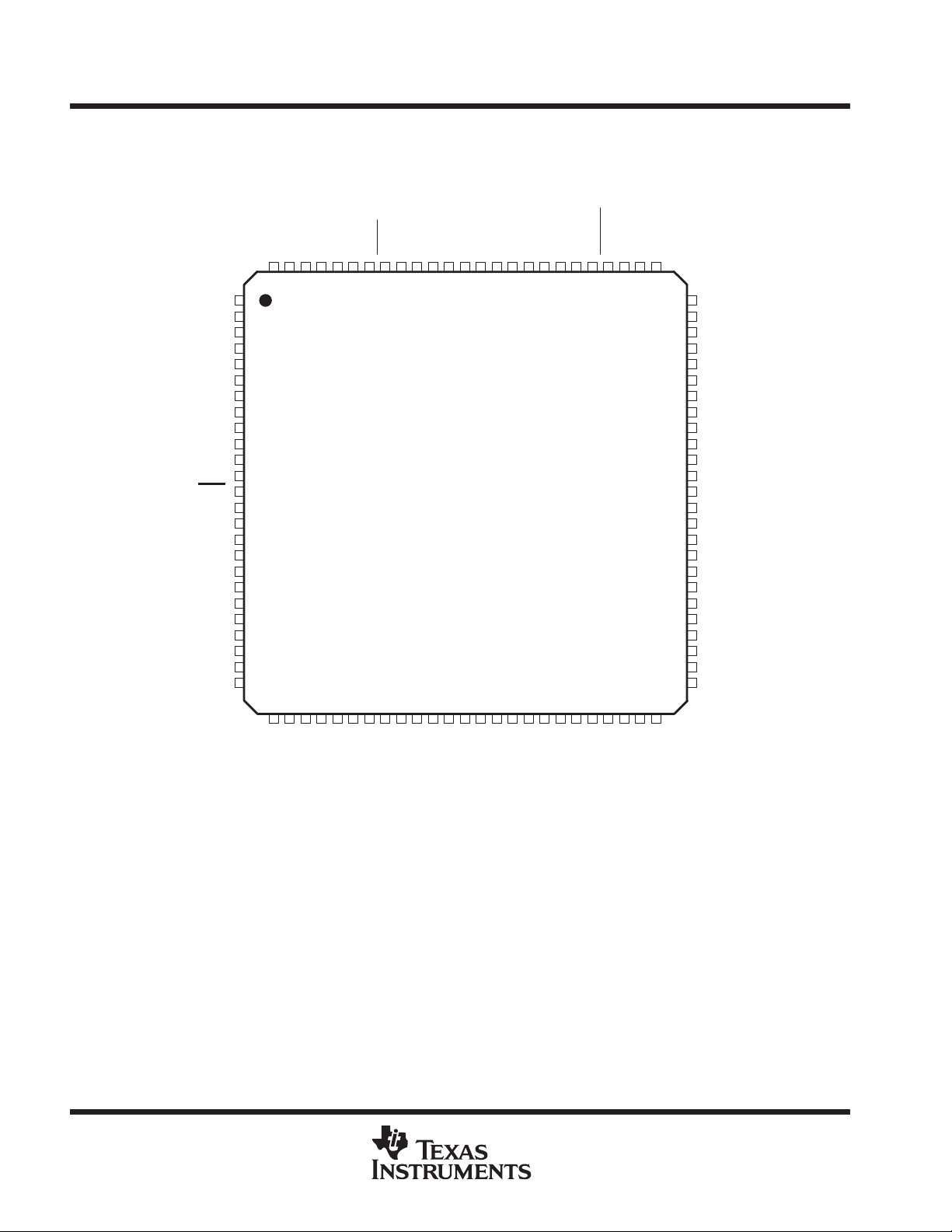

pin assignment

TQFP PACKAGE

(TOP VIEW)

MODE2

TP1

CPV

VSS

STV

OE1

REV_E

VDD

REV_O

OE2

TP2

VSSIO

CLK

VDDIO

TEST2

ER5(EB5)

VSSIO

ER4(EB4)

ER3(EB3)

VDDIO

ER2(EB2)

ER1(EB1)

VSSIO

ER0(EB0)

EG5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

TEST1

MODE1NCVSS

98

99

100

28

27

26

DBS

96

97

30

29

POLEN

VDDA

RSTZ

93

94

95

33

32

31

GNDANCCLKP

92

GND1

NC

90

91

89

88

CLKM

87

SN75LVDS88B

38

39

37

36

35

34

A2P

86

40

A2M

85

41

A1P

84

42

A1M

83

43

A0P

82

44

A0M

GNDD

80

81

46

45

SHTDN

VDDDNCNC

77

78

79

49

48

47

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

VDD

OPOL

VSS

OB0(OR0)

VDD

OB1(OR1)

OB2(OR2)

VSSIO

OB3(OR3)

OB4(OR4)

VDDIO

OB5(OR5)

OG0

VSSIO

OG1

OG2

VDDIO

OG3

OG4

VSSIO

OG5

OR0(OB0)

VDDIO

OR1(OB1)

OR2(OB2)

SP

EG4

EG3

EG2

EG1

EG0

VDDIO

VSSIO

VDDIO

EB5(ER5)

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

VSSIO

EB3(ER3)

EB4(ER4)

EB2(ER2)

VDDIO

EB1(ER1)

EB0(ER0)

EPOL

VSSIO

CLK

VDDIO

VSSIO

OR5(OB3)

OR4(OB4)

OR3(OB3)

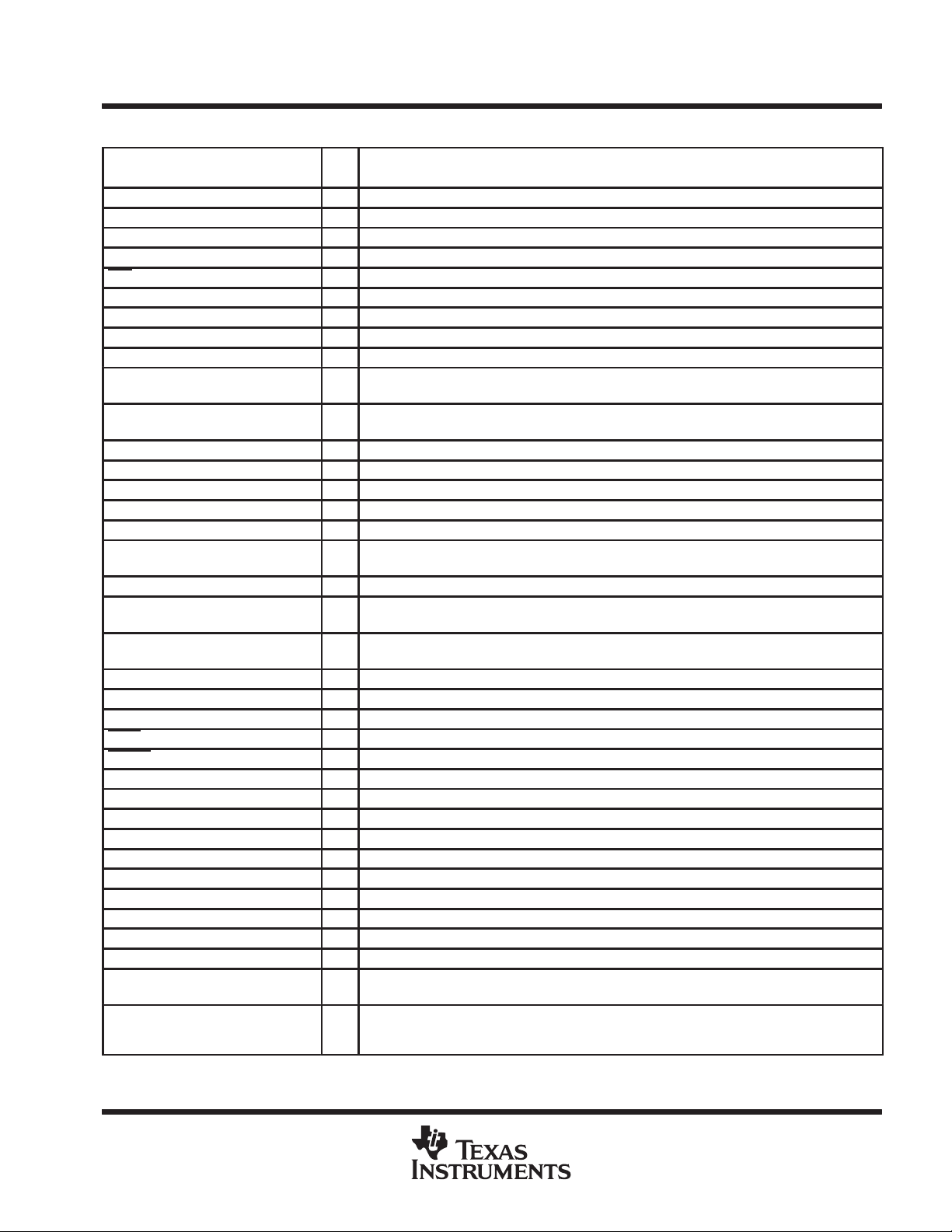

I/O

DESCRIPTION

TFT LCD PANEL TIMING CONTROLLER

Terminal Functions

TERMINAL

NAME NO.

A0M/A0P 81,82 I Flatlink 1st data pair

A1M/A1P 83, 84 I Flatlink 2nd data pair

A2M/A2P 85, 86 I Flatlink 3rd data pair

CLK 44 O CD bus clock

CLK 13 O CD bus clock (180 degree out of phase)

CLKM/CLKP 87, 88 I Flatlink clock pair

CPV 3 O Gate driver clock

DBS 97 I Data bus sequence

EPOL 42 O Even RGB data stream polarity indicator

ER0..ER5

(EB0)..(EB5)

(ER0)..(ER5)

EB0..EB5

GND1 91 P PLL ground for LVDS

MODE1 99 I Default timing selection pin 1

MODE2 1 I Default timing selection pin 2

NC 76, 77, 89, 90, 98 NC NC terminals

OE1, OE2 6, 10 O Gate driver output enable

OG0..OG5 63, 61, 60,

OPOL 74 O Odd RGB data stream polarity indicator

OR0..OR5

(OB0)..(OB5)

(OR0)..(OR5)

OB0..OB5

POLEN 95 I Output data polarity control enable /disable

REV_E 7 O CD line/dot inversion control signal

REV_O 9 O CD line/dot inversion control signal (180 degree of phase)

RSTZ 93 I Reset, active low

SHTDN 79 I System shutdown control, active low

SP 46 O Data bus starting pulse

STV 5 O Gate driver starting pulse

TEST1, TEST2 100, 15 I Test points

TP1, TP2 2, 11 O CD output control signal

VDDA 94 P PLL power for LVDS

GNDA 92 P Analog ground for LVDS

VDDD 78 P Digital power supply for LVDS

GNDD 80 P Digital power ground for L VDS

VDD 8,71,75 P Digital power

VSS 4,73,96 P Digital ground

VDDIO 14, 20, 28, 34,

VSSIO 12, 17, 23, 31,

†

Terminals must be connected to ground.

24, 22, 21,

19, 18, 16

41,39,38

36,35,33

58, 57, 55

54, 52, 51,

50, 49, 47

72, 70, 69

67, 66, 64

40, 45, 53, 59, 65

37, 43, 48, 56,

62, 68

O Even red (blue) data bus, controlled by DBS Pin, 0 = red, 1 = blue

O Even blue (red) data bus, controlled by DBS Pin, 0 = blue, 1 = red

†

O Odd green data bus

O Odd red (blue) data bus, controlled by DBS Pin, 0 = red, 1 = blue

O Odd blue (red) data bus, controlled by DBS Pin, 0 = blue, 1 = red

†

P I/O power

P I/O ground

SN75LVDS88B

WITH LVDS INTERF ACE

SLLS407 – FEBRUARY 2000

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

SN75LVDS88B

PIN NAME

PIN NO

DESCRIPTION

TFT LCD PANEL TIMING CONTROLLER

WITH LVDS INTERF ACE

SLLS407 – FEBRUARY 2000

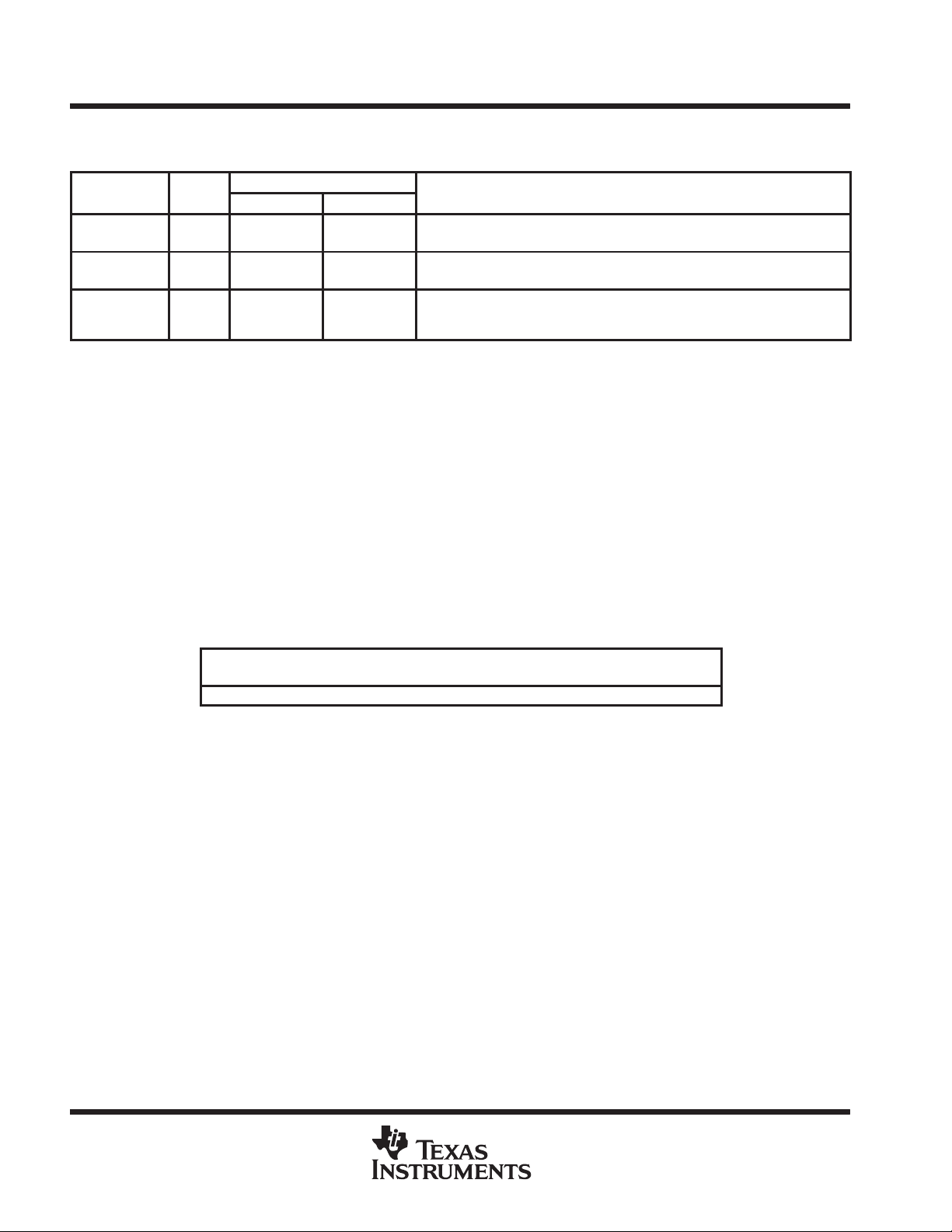

options

output control

INTERNAL CONNECTION

.

REQUIRED SUGGESTED

MODE1

MODE2

POLEN Pulldown 0 = Output data reverse disable

DBS 97 Pulldown Data bus sequence

NOTE: NC pin 76 is internally pulldown and NC pins 77 and 98 are internally pullup.

991Pullup

Pulldown

Default timing selection pin 1

Default timing selection pin 2

1 = Output data reverse enable

0 = normal (RGB)

1 = reverse (BGR)

CC

†

+ 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

Supply voltage range, V

Voltage range at any terminal –0.5 V to V

‡

–0.5 V to 4 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

Continuous power dissipation See Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

Electrostatic discharge: Class 3 A 4 kV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Class 2 B 200 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

‡

All voltage values are with respect to the GND terminals unless otherwise noted.

DISSIPATION RATING TABLE

PACKAGE

PFD 1.548 W 12 mW 1.012 W

§

This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with

no air flow.

TA ≤ 25°C

POWER RATING

OPERATING FACTOR

ABOVE TA = 25°C

§

TA = 70°C

POWER RATING

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...