Texas Instruments SN74LVC652ADBLE, SN74LVC652ADBR, SN74LVC652ADGVR, SN74LVC652ADW, SN74LVC652ADWR Datasheet

...

SN54LVC652A, SN74LVC652A

OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCAS303H – JANUARY 1993 – REVISED AUGUST 1998

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

EPIC

(Enhanced-Performance Implanted

CMOS) Submicron Process

D

T ypical V

OLP

(Output Ground Bounce)

< 0.8 V at V

CC

= 3.3 V, TA = 25°C

D

T ypical V

OHV

(Output VOH Undershoot)

> 2 V at V

CC

= 3.3 V, TA = 25°C

D

Support Mixed-Mode Signal Operation on

All Ports (5-V Input/Output Voltage With

3.3-V V

CC

)

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

Package Options Include Plastic

Small-Outline (DW), Shrink Small-Outline

(DB), Thin Shrink Small-Outline (PW)

Packages, and Ceramic Chip Carriers (FK)

description

The SN54LVC652A octal bus transceiver and

register is designed for 2.7-V to 3.6-V V

CC

operation, and the SN74LVC652A octal bus

transceiver and register is designed for 1.65-V to

3.6-V V

CC

operation.

These devices consist of bus transceiver circuits,

D-type flip-flops, and control circuitry arranged for

multiplexed transmission of data directly from the

data bus or from the internal storage registers.

Output-enable (OEAB and OEBA

) inputs are

provided to control the transceiver functions.

Select-control (SAB and SBA) inputs are provided

to select whether real-time or stored data is

transferred. The circuitry used for select control

eliminates the typical decoding glitch that occurs

in a multiplexer during the transition between stored and real-time data. A low input selects real-time data, and

a high input selects stored data. Figure 1 illustrates the four fundamental bus-management functions that are

performed with the ’LVC652A.

Data on the A or B data bus, or both, is stored in the internal D-type flip-flops by low-to-high transitions at the

appropriate clock (CLKAB or CLKBA) inputs, regardless of the select- or enable-control pins. When SAB and

SBA are in the real-time transfer mode, it is possible to store data without using the internal D-type flip-flops by

simultaneously enabling OEAB and OEBA

. In this configuration, each output reinforces its input. When all other

data sources to the two sets of bus lines are at high impedance, each set of bus lines remains at its last state.

Inputs can be driven from either 3.3-V or 5-V devices. This feature allows the use of these devices as translators

in a mixed 3.3-V/5-V system environment.

Copyright 1998, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

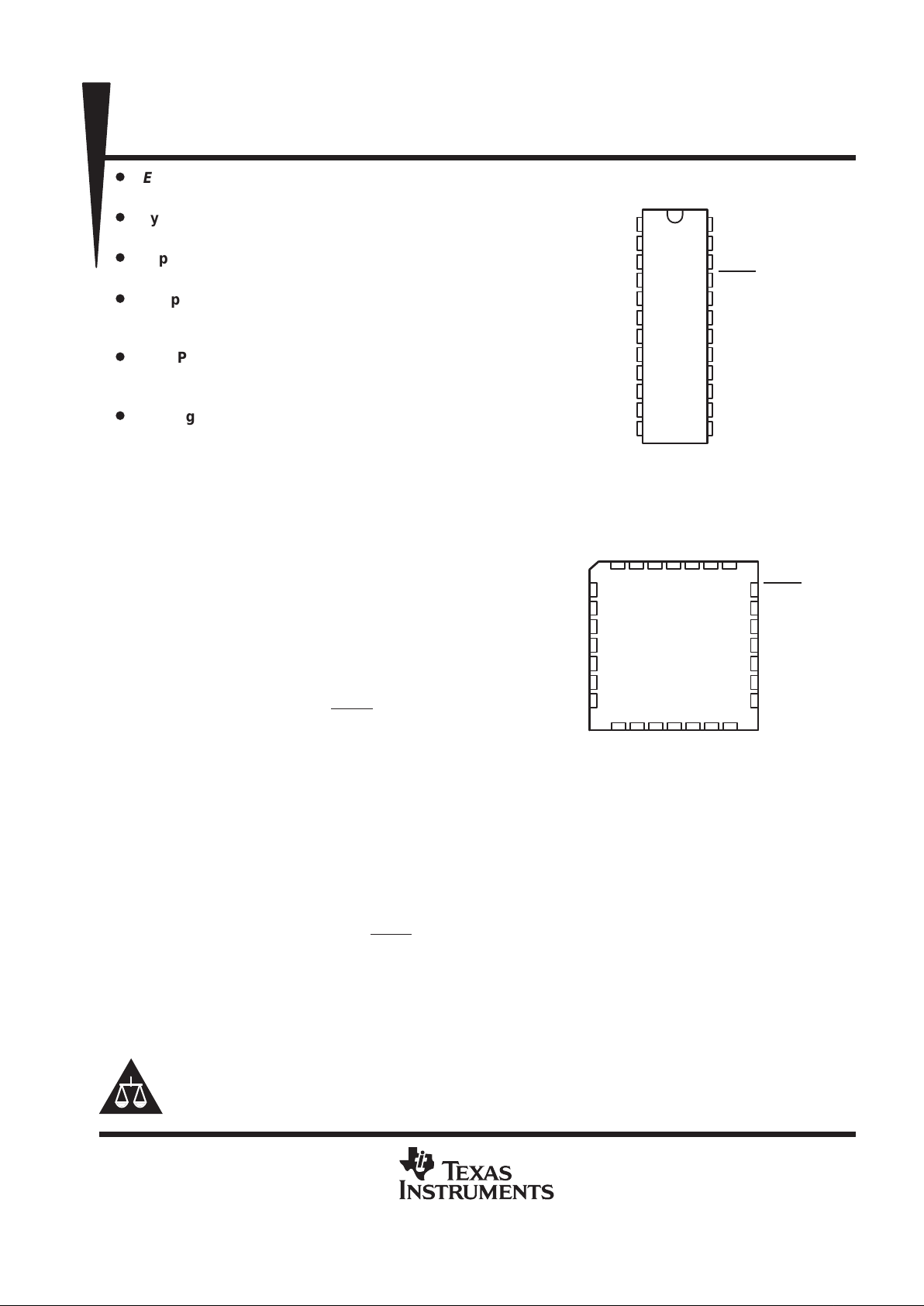

SN74LVC652A. . . DB, DW, OR PW PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

CLKAB

SAB

OEAB

A1

A2

A3

A4

A5

A6

A7

A8

GND

V

CC

CLKBA

SBA

OEBA

B1

B2

B3

B4

B5

B6

B7

B8

SN54LVC652A. . . FK PACKAGE

(TOP VIEW)

3212827

12 13

5

6

7

8

9

10

11

25

24

23

22

21

20

19

OEBA

B1

B2

NC

B3

B4

B5

A1

A2

A2

NC

A4

A5

A6

426

14 15 16 17 18

A7

A8

GND

NC

B8B7B6

OEAB

SAB

CLKABNCCLKBA

SBA

V

CC

NC – No internal connection

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SN54LVC652A, SN74LVC652A

OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCAS303H – JANUARY 1993 – REVISED AUGUST 1998

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

To ensure the high-impedance state during power up or power down, OEBA should be tied to VCC through a

pullup resistor and OEAB should be tied to GND through a pulldown resistor; the minimum value of the resistor

is determined by the current-sinking/current-sourcing capability of the driver.

The SN54L VC652A is characterized for operation over the full military temperature range of –55°C to 125°C.

The SN74LVC652A is characterized for operation from –40°C to 85°C.

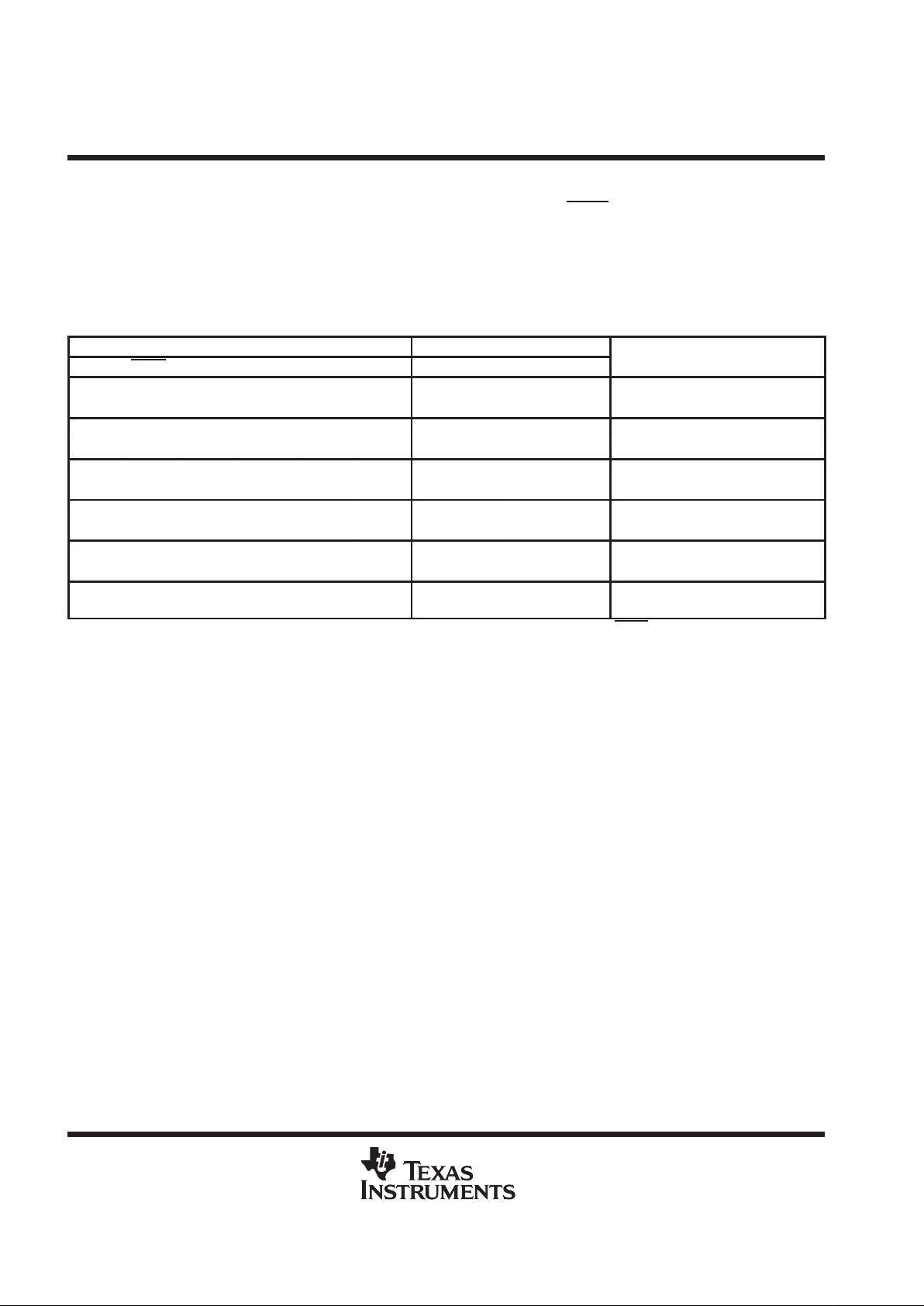

FUNCTION TABLE

INPUTS

DATA I/O

†

OEAB OEBA CLKAB CLKBA SAB SBA A1–A8 B1–B8

OPERATION OR FUNCTION

L H H or L H or L X X Input Input Isolation

L H ↑↑X X Input Input Store A and B data

X H ↑ H or L X X Input Unspecified

‡

Store A, hold B

H H ↑↑X

‡

X Input Output Store A in both registers

L X H or L ↑ X X Unspecified

‡

Input Hold A, store B

L L ↑↑XX

‡

Output Input Store B in both registers

L L X X X L Output Input Real-time B data to A bus

L L X H or L X H Output Input Stored B data to A bus

H H X X L X Input Output Real-time A data to B bus

H H H or L X H X Input Output Stored A data to B bus

H L H or L H or L H H Output Output

Stored A data to B bus and

stored B data to A bus

†

The data-output functions can be enabled or disabled by a variety of level combinations at OEAB or OEBA. Data-input functions always are

enabled; i.e., data at the bus terminals is stored on every low-to-high transition of the clock inputs.

‡

Select control = L; clocks can occur simultaneously.

Select control = H; clocks must be staggered to load both registers.

SN54LVC652A, SN74LVC652A

OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCAS303H – JANUARY 1993 – REVISED AUGUST 1998

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

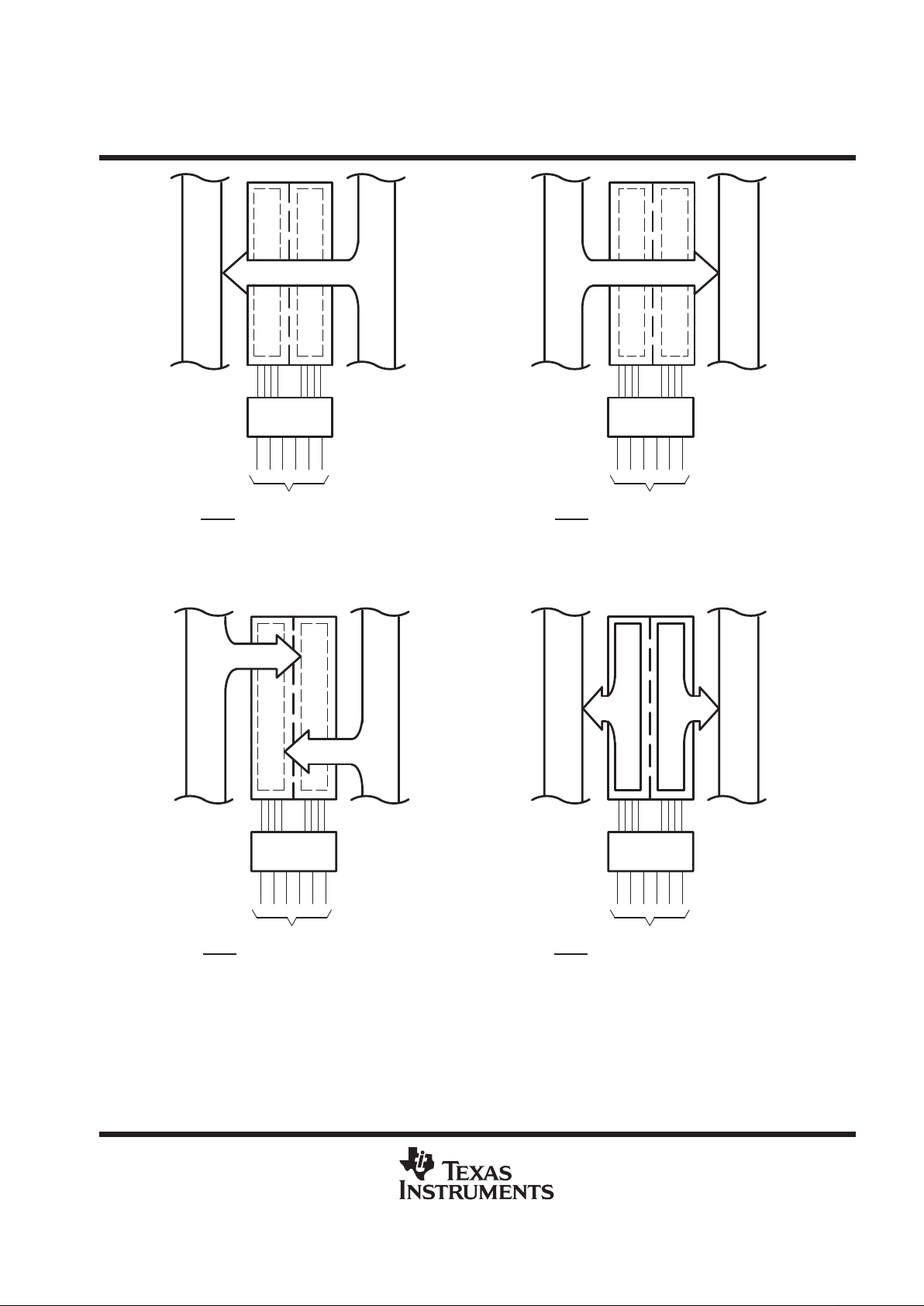

BUS B

BUS A

BUS B

BUS A

BUS B

BUS A

BUS B

BUS A

OEAB

X

L

L

OEAB

LL

CLKABXCLKBAXSABXSBA

L

CLKABXCLKBAXSABLSBA

X

H

CLKAB CLKBAXSABXSBA

X

CLKAB CLKBA SAB SBA

X

H

XX

X

X

X

H L H or L H H

↑

↑

↑↑

OEBA

OEBA

HH

OEAB OEBA

OEAB OEBA

H or L

REAL-TIME TRANSFER

BUS B TO BUS A

REAL-TIME TRANSFER

BUS A TO BUS B

STORAGE FROM

A, B, OR A AND B

TRANSFER STORED DATA

TO A AND/OR B

3 21 1 23 2 22 1 23 2 22321

3 21 23 2 22 3 21 1 2 22

1

23

Figure 1. Bus-Management Functions

SN54LVC652A, SN74LVC652A

OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCAS303H – JANUARY 1993 – REVISED AUGUST 1998

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

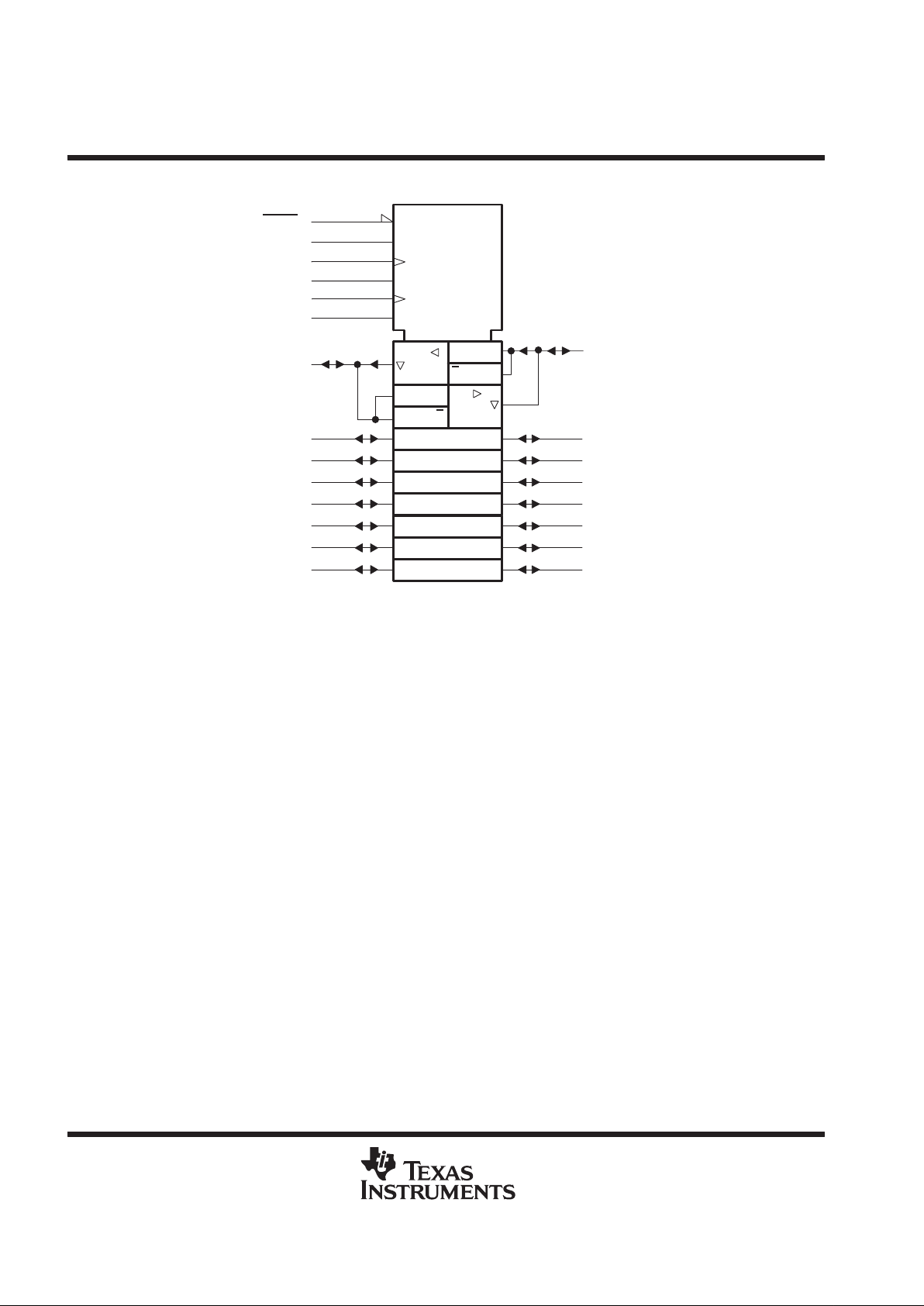

logic symbol

†

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the DB, DW, and PW packages.

OEBA

EN1 [BA]

21

G5

22

SBA

A1

4

B1

20

4D

EN2 [AB]

3

OEAB

23

CLKBA

1

CLKAB

G7

2

SAB

5

7

7

5

1

1

6D ≥1

≥1

1

2

C6

C4

A2

5

B2

19

A3

6

B3

18

A4

7

B4

17

A5

8

B5

16

A6

9

B6

15

A7

10

B7

14

A8

11

B8

13

Loading...

Loading...