Texas Instruments SN74LV574ADBR, SN74LV574ADGVR, SN74LV574ADW, SN74LV574ADWR, SN74LV574APWR Datasheet

SN54LV574A, SN74LV574A

OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOPS

WITH 3-STATE OUTPUTS

SCLS412B – APRIL 1998 – REVISED SEPTEMBER 1998

D

EPIC

(Enhanced-Performance Implanted

CMOS) Process

D

Typical V

< 0.8 V at V

D

Typical V

> 2 V at V

D

Latch-Up Performance Exceeds 250 mA

(Output Ground Bounce)

OLP

= 3.3 V, TA = 25°C

CC

(Output VOH Undershoot)

OHV

= 3.3 V, TA = 25°C

CC

Per JESD 17

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

Package Options Include Plastic

Small-Outline (DW, NS), Shrink

Small-Outline (DB), Thin Very Small-Outline

(DGV), and Thin Shrink Small-Outline (PW)

Packages, Ceramic Flat (W) Packages, Chip

Carriers (FK), and DIPs (J)

description

The ’LV574A devices are octal edge-triggered

D-type flip-flops designed for 2-V to 5.5-V V

operation.

These devices feature 3-state outputs designed

specifically for driving highly capacitive or

relatively low-impedance loads. The devices are

particularly suitable for implementing buffer

registers, I/O ports, bidirectional bus drivers, and

working registers.

CC

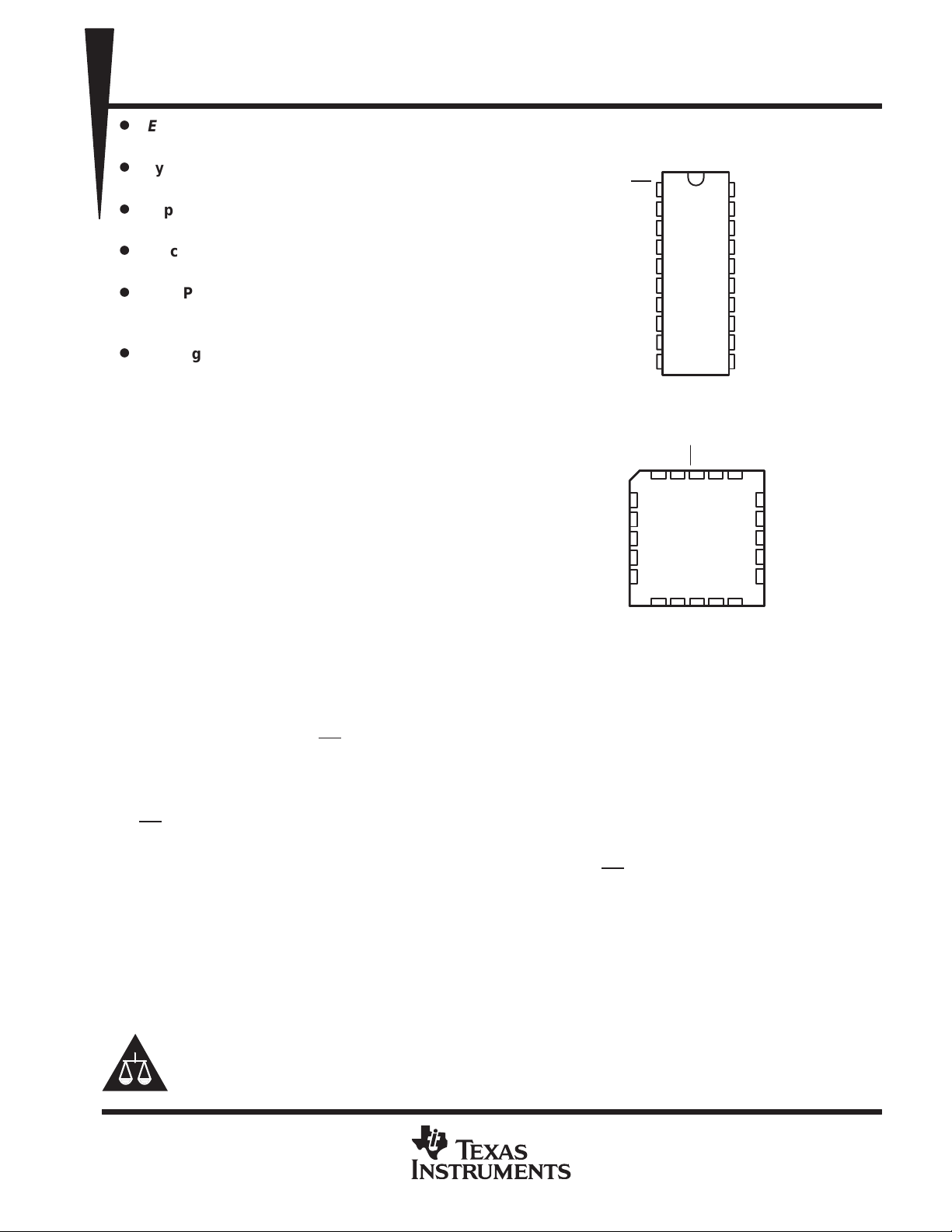

SN74LV574A. . . DB, DGV, DW, NS, OR PW PACKAGE

SN54LV574A...J OR W PACKAGE

(TOP VIEW)

OE

1

1D

2

2D

3

3D

4

4D

5

5D

6

6D

7

7D

8

9

8D

GND

SN54LV574A. . . FK PACKAGE

3D

4D

5D

6D

7D

10

(TOP VIEW)

2D1DOE

3212019

4

5

6

7

8

910111213

8D

GND

20

19

18

17

16

15

14

13

12

11

CLK

V

8Q

CC

V

CC

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

CLK

18

17

16

15

14

7Q 1Q

2Q

3Q

4Q

5Q

6Q

On the positive transition of the clock (CLK) input, the Q outputs are set to the logic levels set up at the data

(D) inputs.

A buffered output-enable (OE

) input can be used to place the eight outputs in either a normal logic state (high

or low logic levels) or high-impedance state. In the high-impedance state, the outputs neither load nor drive the

bus lines significantly . The high-impedance state and increased drive provide the capability to drive bus lines

without need for interface or pullup components.

OE

does not affect the internal operations of the flip-flops. Old data can be retained or new data can be entered

while the outputs are in the high-impedance state.

T o ensure the high-impedance state during power up or power down, OE

should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN54LV574A is characterized for operation over the full military temperature range of –55°C to 125°C.

The SN74LV574A is characterized for operation from –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

UNLESS OTHERWISE NOTED this document contains PRODUCTION

DATA information current as of publication date. Products conform to

specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all

parameters.

Copyright 1998, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

1

SN54LV574A, SN74LV574A

OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOPS

WITH 3-STATE OUTPUTS

SCLS412B – APRIL 1998 – REVISED SEPTEMBER 1998

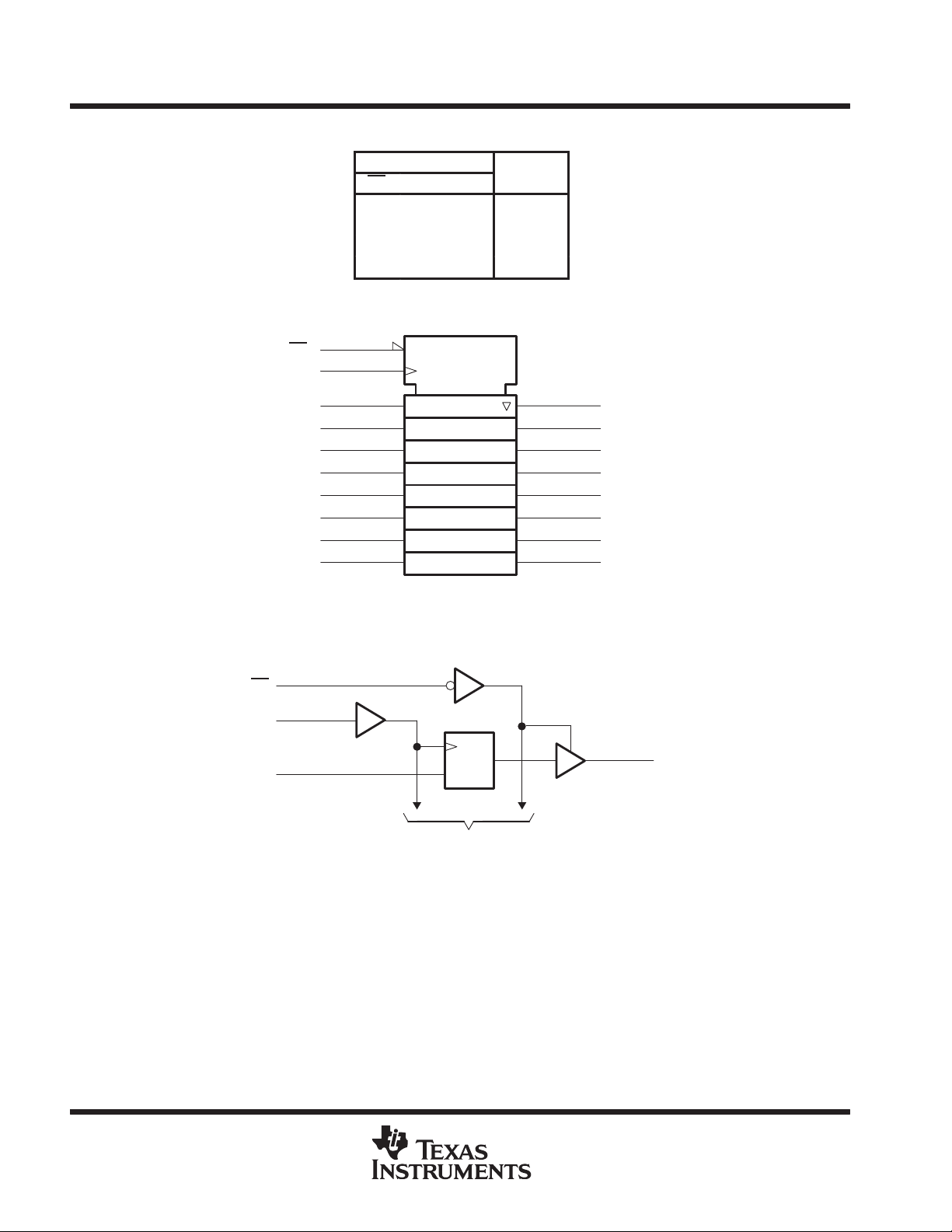

FUNCTION TABLE

(each flip-flop)

INPUTS

OE CLK D

L ↑ H H

L ↑ LL

LH or L X Q

H X X Z

OUTPUT

Q

0

logic symbol

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

†

OE

CLK

1D

2D

3D

4D

5D

6D

7D

8D

1

11

2

3

4

5

6

7

8

9

EN

C1

1D

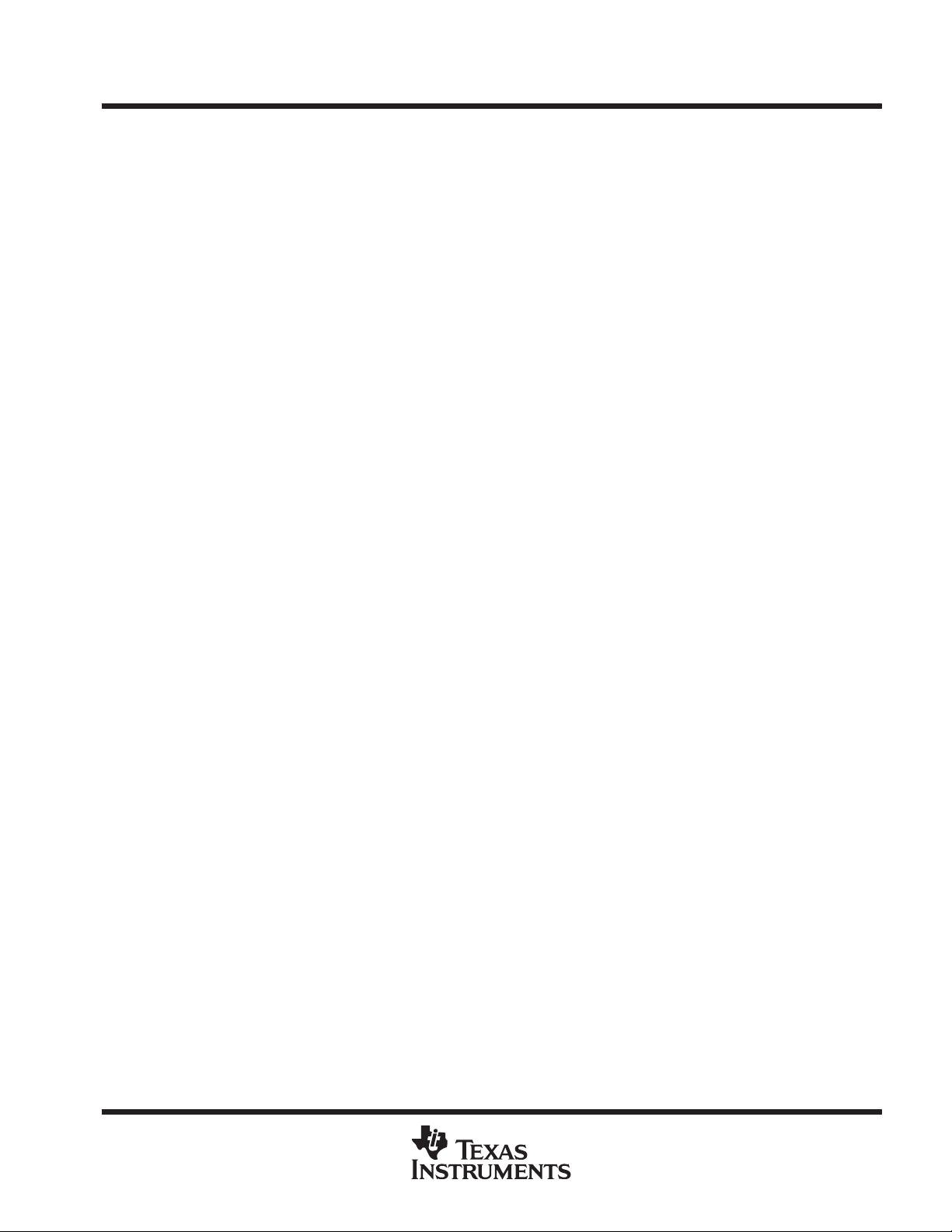

logic diagram (positive logic)

1

OE

11

CLK

C1

1D

2

1D

19

18

17

16

15

14

13

12

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

19

1Q

To Seven Other Channels

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54LV574A, SN74LV574A

OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOPS

WITH 3-STATE OUTPUTS

SCLS412B – APRIL 1998 – REVISED SEPTEMBER 1998

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

Input voltage range, V

Output voltage range applied in the high or low state, V

Output voltage range applied in high-impedance or power-off state, V

Input clamp current, I

Output clamp current, I

Continuous output current, I

Continuous current through V

Package thermal impedance, θ

Storage temperature range, T

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. This value is limited to 7 V maximum.

3. The package thermal impedance is calculated in accordance with JESD 51.

–0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

(see Note 1) –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

(VI < 0 or VI > VCC) ±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IK

(VO < 0 or VO > VCC) ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OK

(VO = 0 to VCC) ±35 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

or GND ±70 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

(see Note 3): DB package 115°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

JA

(see Notes 1 and 2) –0.5 V to VCC + 0.5 V. . . . . .

O

(see Note 1) –0.5 V to 7 V. . . . . . .

O

DGV package 146°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DW package 97°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NS package 100°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PW package 128°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

†

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Loading...

Loading...