SN54F299, SN74F299

8-BIT UNIVERSAL SHIFT/STORAGE REGISTERS

WITH 3-STATE OUTPUTS

SDFS071A – MARCH 1987 – REVISED OCTOBER 1993

• Four Modes of Operation:

Hold (Store)

Shift Right

Shift Left

Load Data

• Operates With Outputs Enabled or at High

Impedance

• 3-State Outputs Drive Bus Lines Directly

• Can Be Cascaded for N-Bit Word Lengths

• Direct Overriding Clear

• Applications:

Stacked or Push-Down Registers

Buffer Storage

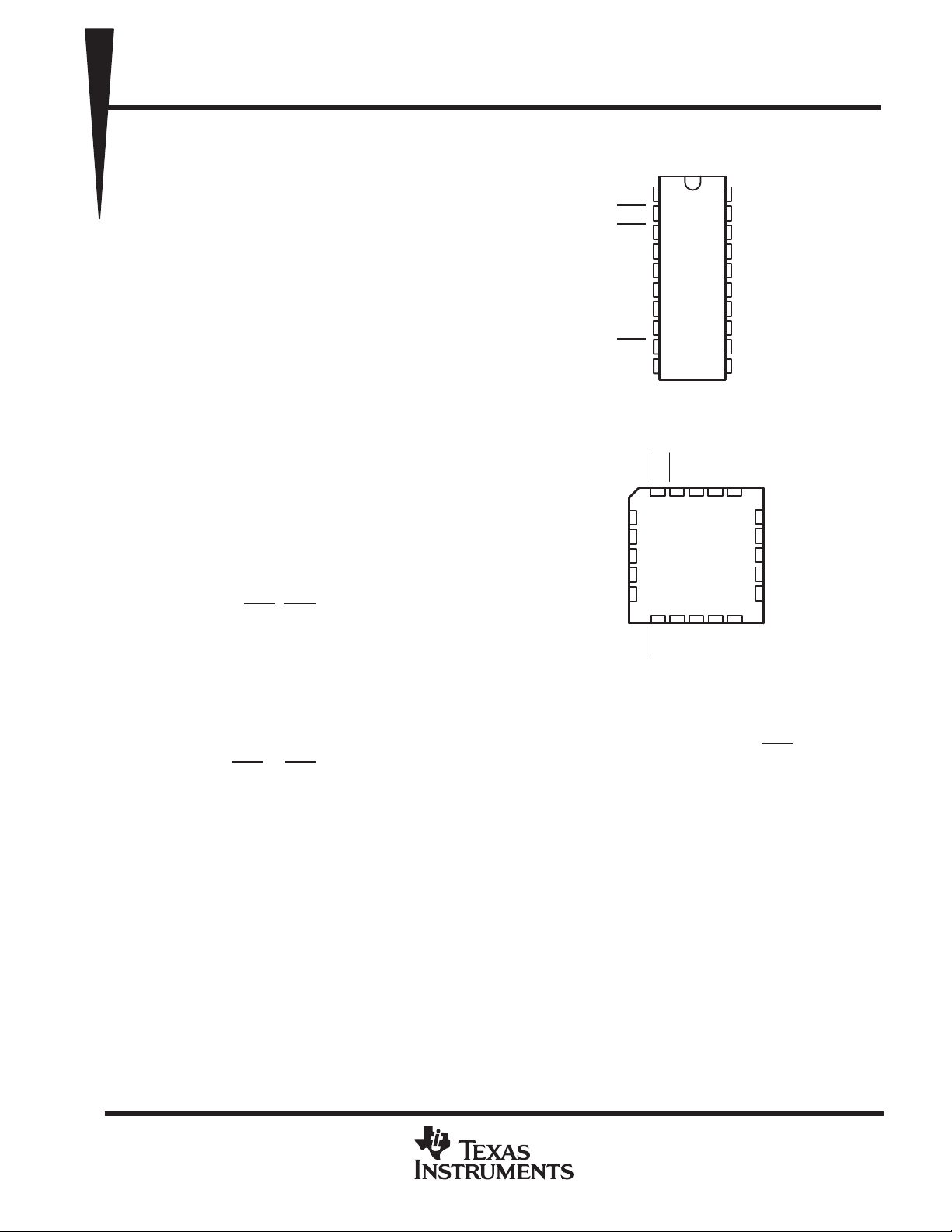

SN54F299 ...J PACKAGE

SN74F299 . . . DW OR N PACKAGE

G/Q

OE1

OE2

E/Q

C/Q

A/Q

Q

CLR

GND

S0

G

E

C

A

A′

(TOP VIEW)

1

20

2

19

3

18

4

17

5

16

6

15

7

14

8

13

9

12

10

11

V

CC

S1

SL

Q

H′

H/Q

F/Q

D/Q

B/Q

CLK

SR

H

F

D

B

Accumulator Registers

• Package Options Include Plastic

Small-Outline Packages, Ceramic Chip

SN54F299 . . . FK PACKAGE

(TOP VIEW)

Carriers, and Standard Plastic and Ceramic

300-mil DIPs

description

These 8-bit universal shift/storage registers

feature multiplexed I/O ports to achieve full 8-bit

data handling in a single 20-pin package. Two

function-select (S0, S1) inputs and two

output-enable (OE1

choose the modes of operation listed in the

function table.

, OE2) inputs can be used to

G/Q

E/Q

C/Q

A/Q

Q

3212019

4

G

5

E

6

C

7

A

8

A′

OE2

910111213

CLR

OE1

GND

S0

SR

CC

V

CLK

S1

18

17

16

15

14

B

B/Q

SL

Q

H′

H/Q

F/Q

D/Q

H

F

D

Synchronous parallel loading is accomplished by

taking both S0 and S1 high. This places the 3-state

outputs in a high-impedance state and permits

data that is applied on the I/O ports to be clocked into the register. Reading out of the register can be

accomplished while the outputs are enabled in any mode. Clearing occurs when the clear (CLR

Taking either OE1

or OE2 high disables the outputs but has no effect on clearing, shifting, or storage of data.

) input is low.

The SN54F299 is characterized for operation over the full military temperature range of –55°C to 125°C. The

SN74F299 is characterized for operation from 0°C to 70°C.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1993, Texas Instruments Incorporated

2–1

SN54F299, SN74F299

MODE

8-BIT UNIVERSAL SHIFT/STORAGE REGISTERS

WITH 3-STATE OUTPUTS

SDFS071A – MARCH 1987 – REVISED OCT OBER 1993

FUNCTION TABLE

INPUTS I/O PORTS OUTPUTS

CLR S1 S0 OE1†OE2†CLK SL SR A/QAB/QBC/QCD/QDE/QEF/QFG/QGH/QHQA′Q

L

X

L

L

L

L

X

Clear

L

H

Hold

Shift

RightHHLLHH

Shift

LeftHHHHLL

Load H H H X X ↑ X X a b c d e f g h a h

NOTE: a ...h = the level of the steady-state input at inputs A through H, respectively. This data is loaded into the flip-flops while the flip-flop outputs

†

When one or both output-enable inputs are high the eight I/O terminals are disabled to the high-impedance state; however, sequential operation

or clearing of the register is not affected.

HHLXL

are isolated from the I/O terminals.

L

H

X

L

X

L

L

L

L

L

L

X

X

L

X

X

X

X

X

L

XLXXXXQ

L

L

↑↑XXHLHLQ

L

L

↑↑HLXXQ

L

X

L

L

L

L

L

L

L

L

X

L

L

L

L

L

L

L

L

X

X

X

X

X

X

X

X

X

Q

Q

Q

Q

Q

Q

Q

A0

B0

C0

D0

E0

F0

Q

Q

Q

Q

Q

A0

B0

C0

D0

Q

An

Q

An

Q

Bn

Bn

Cn

Q

Cn

Q

Q

Bn

Bn

Dn

Dn

Cn

Q

Cn

Q

En

Q

En

Q

Q

Q

Q

E0

Q

Q

Dn

Q

Q

Dn

Q

Q

Fn

Q

Q

Fn

F0

En

En

Gn

Gn

G0

Q

G0

Q

Fn

Q

Fn

Q

Hn

Q

Hn

H0

Q

H0

Q

Gn

Q

Gn

HLQ

Q

Q

Q

L

L

L

A0

A0

HLQ

Bn

Bn

H′

L

L

L

Q

H0

Q

H0

Gn

Q

Gn

H

L

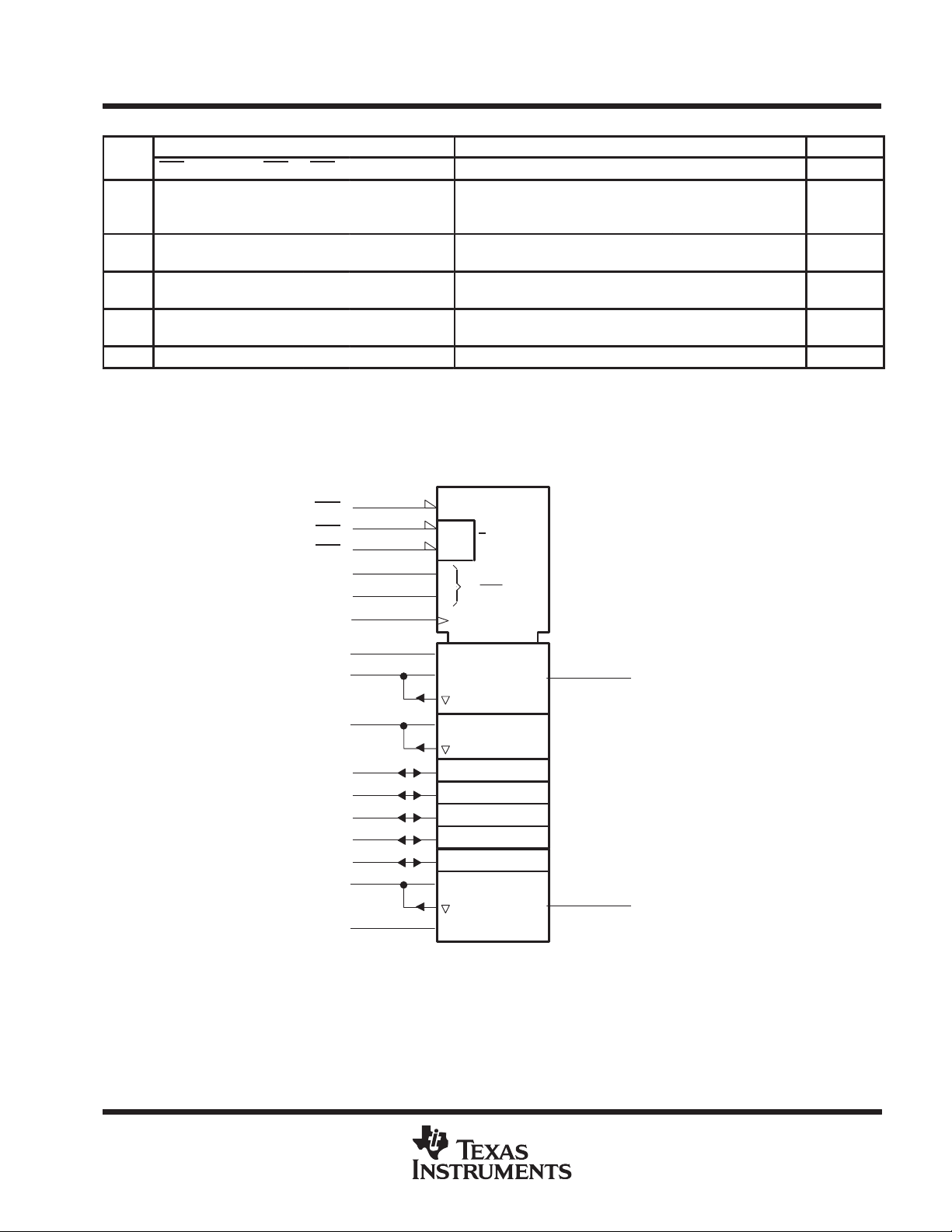

logic symbol

‡

CLR

OE1

OE2

CLK

A/Q

B/Q

C/Q

D/Q

E/Q

F/Q

G/Q

H/Q

S0

S1

SR

SL

9

2

3

1

19

12

11

7

A

13

B

6

C

14

D

5

E

15

F

4

G

16

H

18

R

&

0

M

1

C4/1→/2→

1,4D

3,4D

5

3,4D

5

3,4D

5

2,4D

SRG8

3

EN5

0

3

17

8

Q

A′

Q

H′

‡

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

2–2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

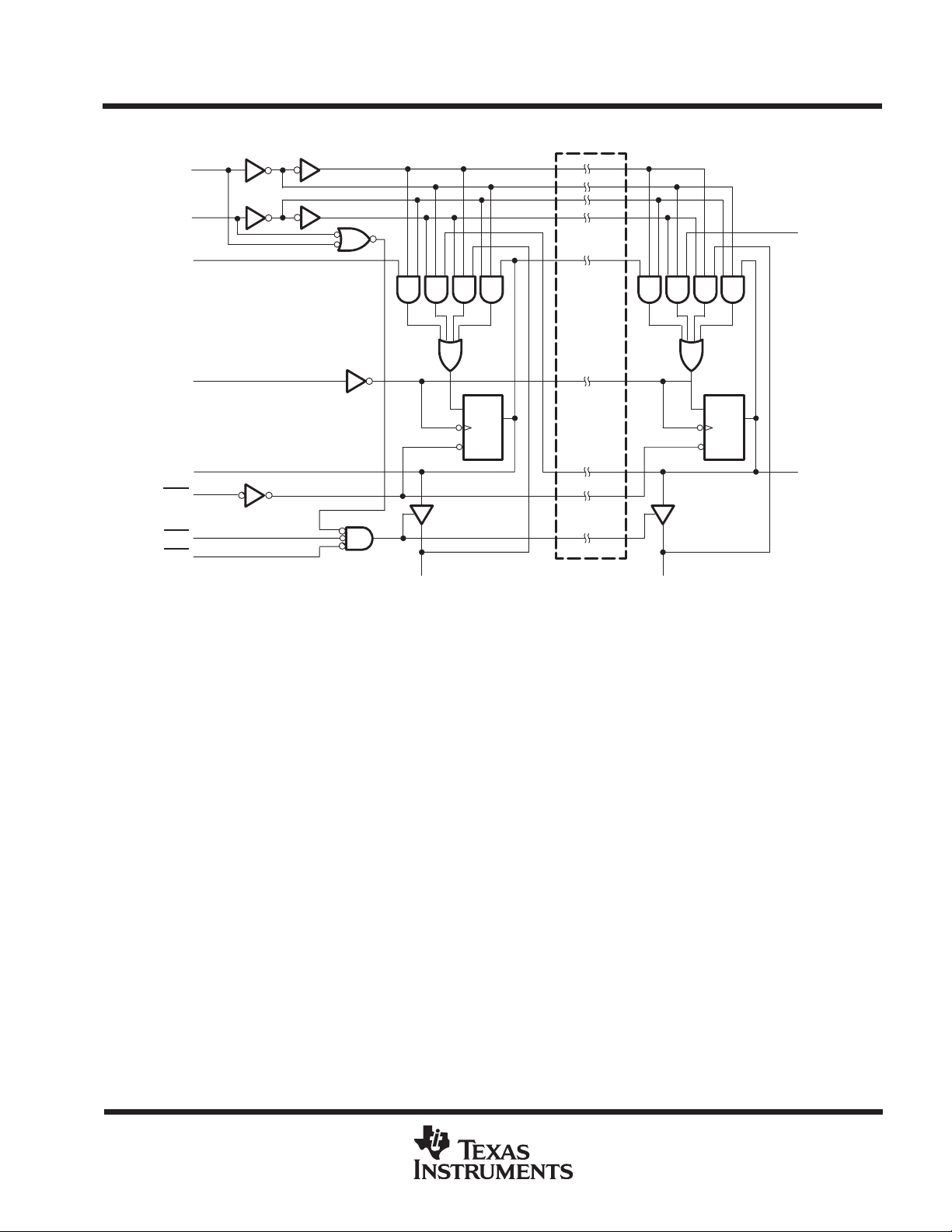

logic diagram (positive logic)

1

S0

19

S1

11

SR

(shift right

serial input)

12

CLK

SN54F299, SN74F299

8-BIT UNIVERSAL SHIFT/STORAGE REGISTERS

WITH 3-STATE OUTPUTS

SDFS071A – MARCH 1987 – REVISED OCTOBER 1993

18

SL

(shift left

serial input)

Six

Identical

Channels

Not

†

Shown

1D

C1

RR

8

Q

A′

9

CLR

2

OE1

3

OE2

†

I/O ports not shown: B/QB (13), C/QC (6), D/QD (14), E/QE (5), F/QF (15), and G/QG (4).

716

A/Q

A

H/Q

1D

C1

17

Q

H′

H

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

Input voltage range, V

Input current range –30 mA to 5 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the disabled or power-off state –0.5 V to 5.5 V. . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high state –0.5 V to V

Current into any output in the low state: Q

Operating free-air temperature range: SN54F299 –55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‡

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The input voltage ratings may be exceeded provided the input current ratings are observed.

–0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

(see Note 1) –1.2 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

or QH′ 40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A′

SN54F299 (Q

SN74F299 (Q

thru QH) 40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

thru QH) 48 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

SN74F299 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‡

CC

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2–3

Loading...

Loading...