Texas Instruments SN74CBTLV3251D, SN74CBTLV3251DBQR, SN74CBTLV3251DR, SN74CBTLV3251PWR Datasheet

FUNCTION

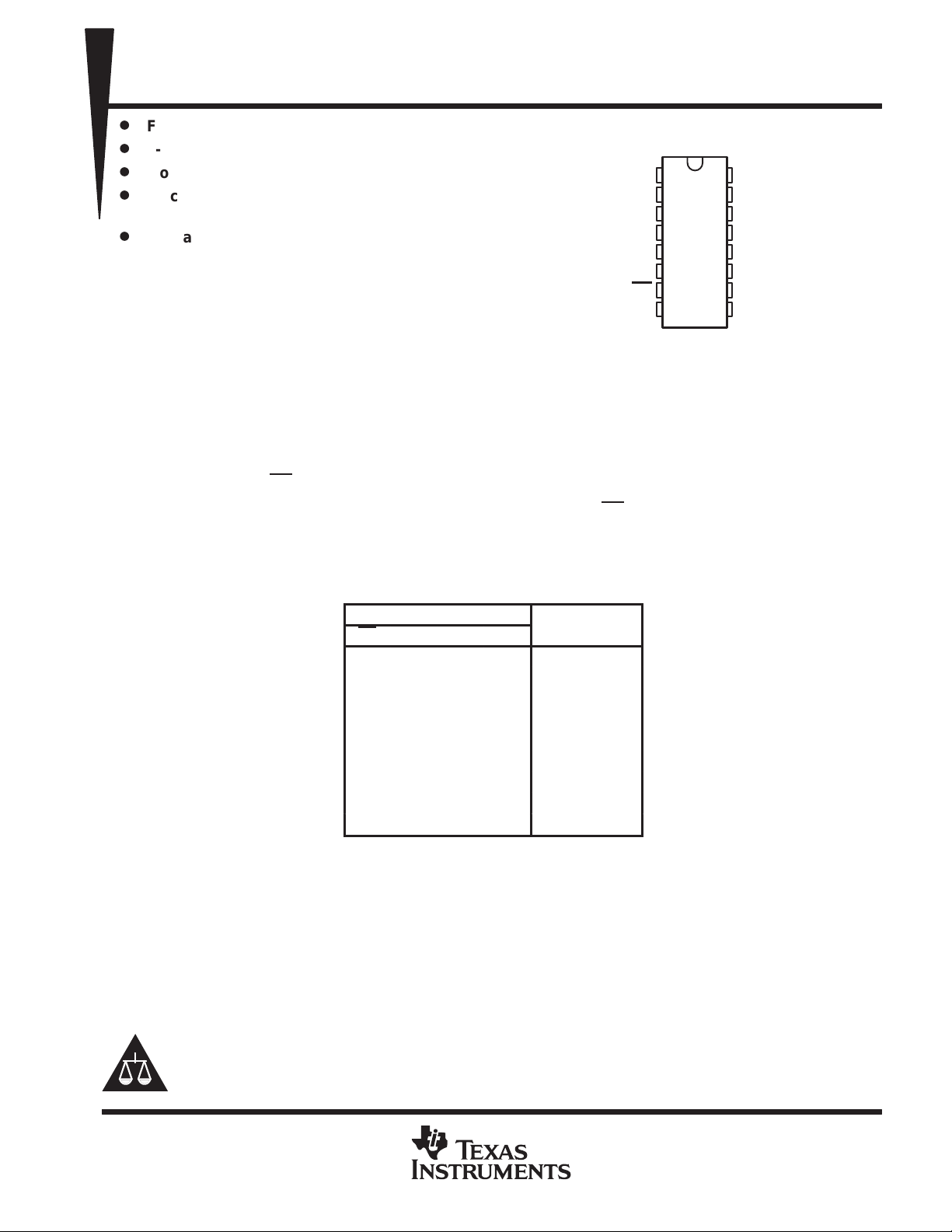

SN74CBTLV3251

LOW-VOLTAGE 1-OF-8 FET MULTIPLEXER/DEMULTIPLEXER

SCDS054E – MARCH 1998 – REVISED NOVEMBER 1999

D

Functionally Equivalent to QS3251

D

5-Ω Switch Connection Between Two Ports

D

Isolation Under Power-Off Conditions

D

Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

D

Package Options Include Thin Very

Small-Outline (DGV), Small-Outline (D),

Shrink Small-Outline (DBQ), and Thin

Shrink Small-Outline (PW) Packages

D, DBQ, DGV, OR PW PACKAGE

B4

B3

B2

B1

NC

OE

GND

(TOP VIEW)

1

2

3

4

5

A

6

7

8

16

15

14

13

12

11

10

V

CC

B5

B6

B7

B8

S0

S1

9

S2

description

The SN74CBTLV3251 device is a 1-of-8

high-speed FET multiplexer/demultiplexer. The

low on-state resistance of the switch allows

connections to be made with minimal propagation

delay .

The select inputs (S0, S1, S2) control the data flow. The FET multiplexers/demultiplexers are disabled when

the output-enable (OE

) input is high.

T o ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74CBTLV3251 is characterized for operation from –40°C to 85°C.

NC – No internal connection

FUNCTION TABLE

INPUTS

OE S2 S1 S0

L L L L A port = B1 port

L L L H A port = B2 port

L L H L A port = B3 port

L L H H A port = B4 port

L H L L A port = B5 port

L H L H A port = B6 port

L H H L A port = B7 port

L H H H A port = B8 port

H X X X Disconnect

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1999, Texas Instruments Incorporated

1

SN74CBTLV3251

LOW-VOLTAGE 1-OF-8 FET MULTIPLEXER/DEMULTIPLEXER

SCDS054E – MARCH 1998 – REVISED NOVEMBER 1999

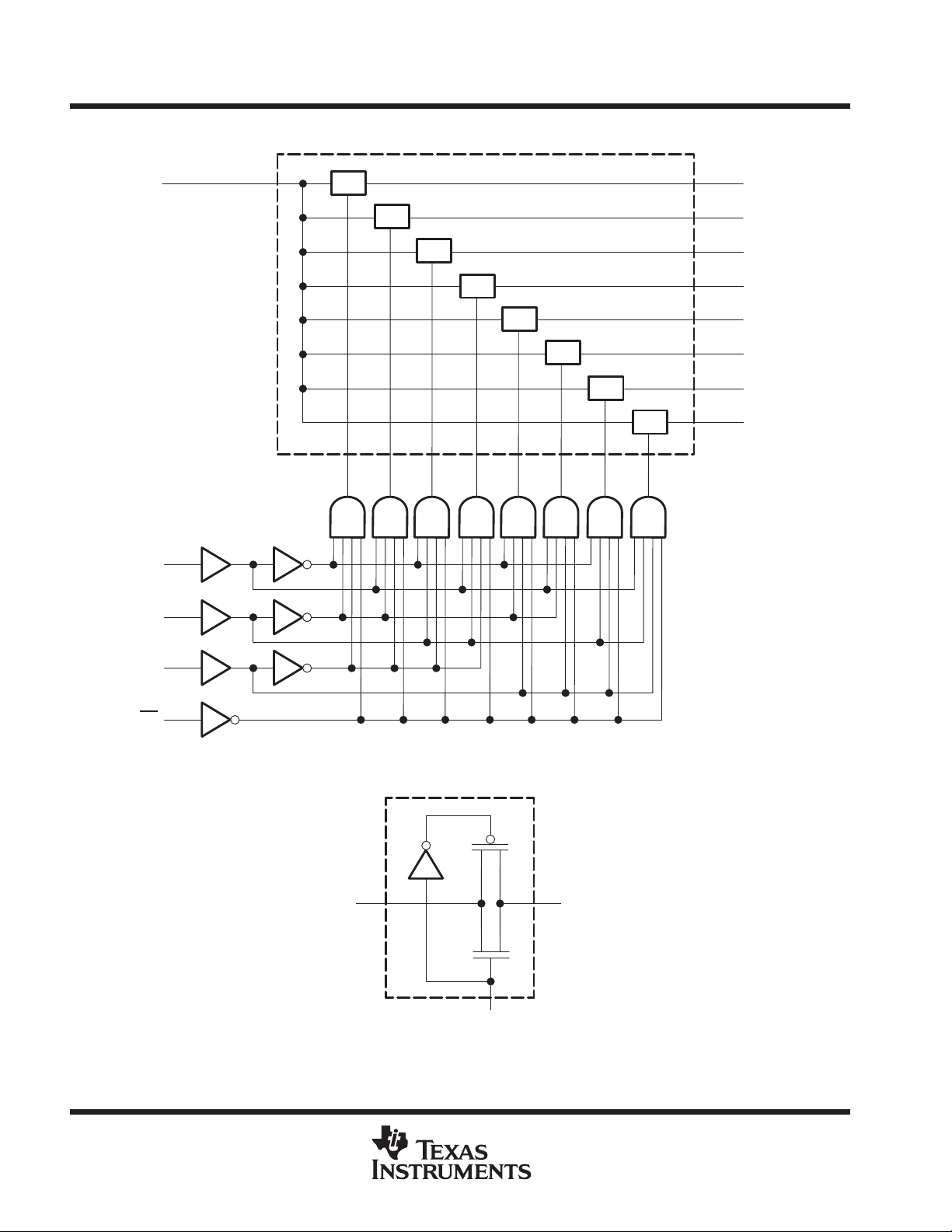

logic diagram (positive logic)

S0

S1

5

A

11

10

SW

SW

SW

SW

SW

SW

SW

SW

15

14

13

12

4

B1

3

B2

2

B3

1

B4

B5

B6

B7

B8

9

S2

7

OE

simplified schematic, each FET switch

A

B

(OE)

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...