Texas Instruments SN74ALVCHG162280DBBR, SN74ALVCHG162280GR Datasheet

SN74ALVCHG162280

16-BIT TO 32-BIT REGISTERED BUS EXCHANGER

WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093C – FEBRUARY 1997 – REVISED JUNE 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Member of the Texas Instruments

Widebus

Family

D

EPIC

(Enhanced-Performance Implanted

CMOS) Sub-Micron Process

D

A-Port Outputs Have Equivalent 50-Ω

Series Resistors and B-Port Outputs Have

Equivalent 20-Ω Series Resistors, So No

External Resistors Are Required

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

Latch-Up Performance Exceeds 250 mA Per

JESD 17

D

Bus-Hold On Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

D

Packaged in Thin Very Small-Outline

Package

NOTE: For order entry:

The DBB package is abbreviated to G.

For tape and reel:

The DBBR package is abbreviated to GR.

description

The SN74ALVCHG162280 is a 16-bit to 32-bit

registered bus exchanger. This device is intended

for use in applications where data must be

transferred from a narrow high-speed bus to a

wide lower-frequency bus. It is designed

specifically for low-voltage (3.3-V) V

CC

operation.

The device provides synchronous data exchange

between the two ports, A and B. Data is stored in

the internal registers on the low-to-high transition

of the clock (CLK) input. For data transfer in the

B-to-A direction, the select (SEL

) input selects 1B

or 2B data for the A outputs.

For data transfer in the A-to-B direction, a

two-stage pipeline is provided in the 1B path, with

a single storage register in the 2B path. Data flow

is controlled by the active-low output-enable (OE)

and direction-control (DIR) inputs. DIR is

registered to synchronize the bus direction

changes with the clock.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus and EPIC are trademarks of Texas Instruments Incorporated.

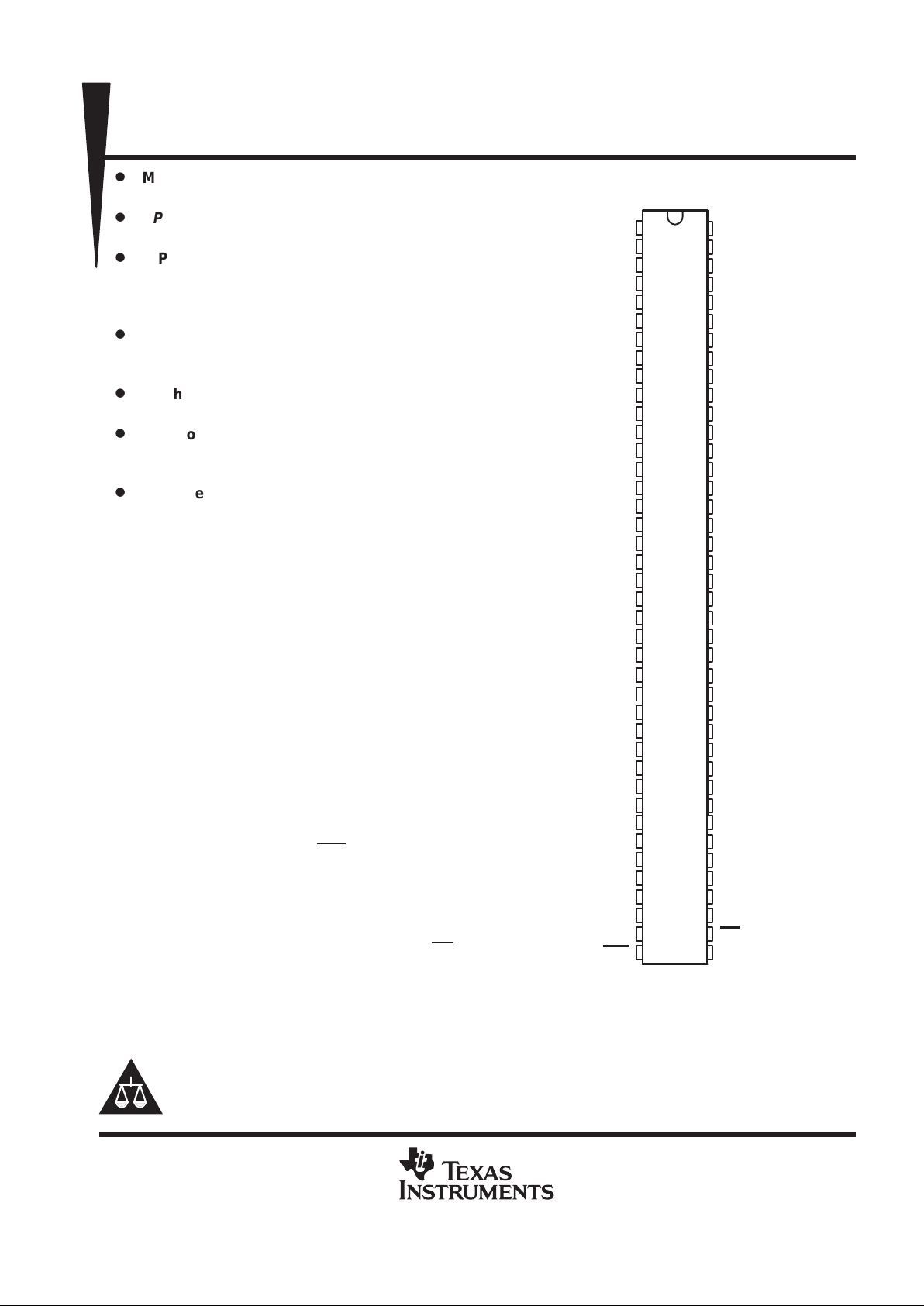

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

V

CC

GND

2B7

1B7

2B6

GND

1B6

2B5

1B5

V

CC

2B4

1B4

2B3

1B3

GND

2B2

1B2

2B1

1B1

V

CC

GND

2D2

1D2

2D1

1D1

V

CC

C1

C2

A1

GND

A2

A3

A4

V

CC

A5

A6

A7

GND

CLK

SEL

V

CC

GND

1B8

2B8

1B9

GND

2B9

1B10

2B10

V

CC

1B11

2B11

1B12

2B12

GND

1B13

2B13

1B14

2B14

V

CC

GND

1B15

2B15

1B16

2B16

V

CC

A16

A15

A14

GND

A13

A12

A11

V

CC

A10

A9

A8

GND

OE

DIR

DBB PACKAGE

(TOP VIEW)

SN74ALVCHG162280

16-BIT TO 32-BIT REGISTERED BUS EXCHANGER

WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093C – FEBRUARY 1997 – REVISED JUNE 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

Two mask bits are provided for both data bytes. The data (D) outputs are controlled by OE.

The A-port N-channel output transistors are sized at 450 µm and the P-channel output transistors are sized at

700 µm. All A-port outputs have equivalent 50-Ω series resistors. The B-port N-channel output transistors are

sized at 225 µm, and the P-channel output transistors are sized at 560 µm. All B-port outputs have equivalent

20-Ω series resistors.

T o ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The switching characteristics are based on 25-pF (A port) and 80-pF (B and D ports) loads, but are tested with

the standard 50-pF load.

The SN74ALVCHG162280 is characterized for operation from 0°C to 70°C.

SN74ALVCHG162280

16-BIT TO 32-BIT REGISTERED BUS EXCHANGER

WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093C – FEBRUARY 1997 – REVISED JUNE 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

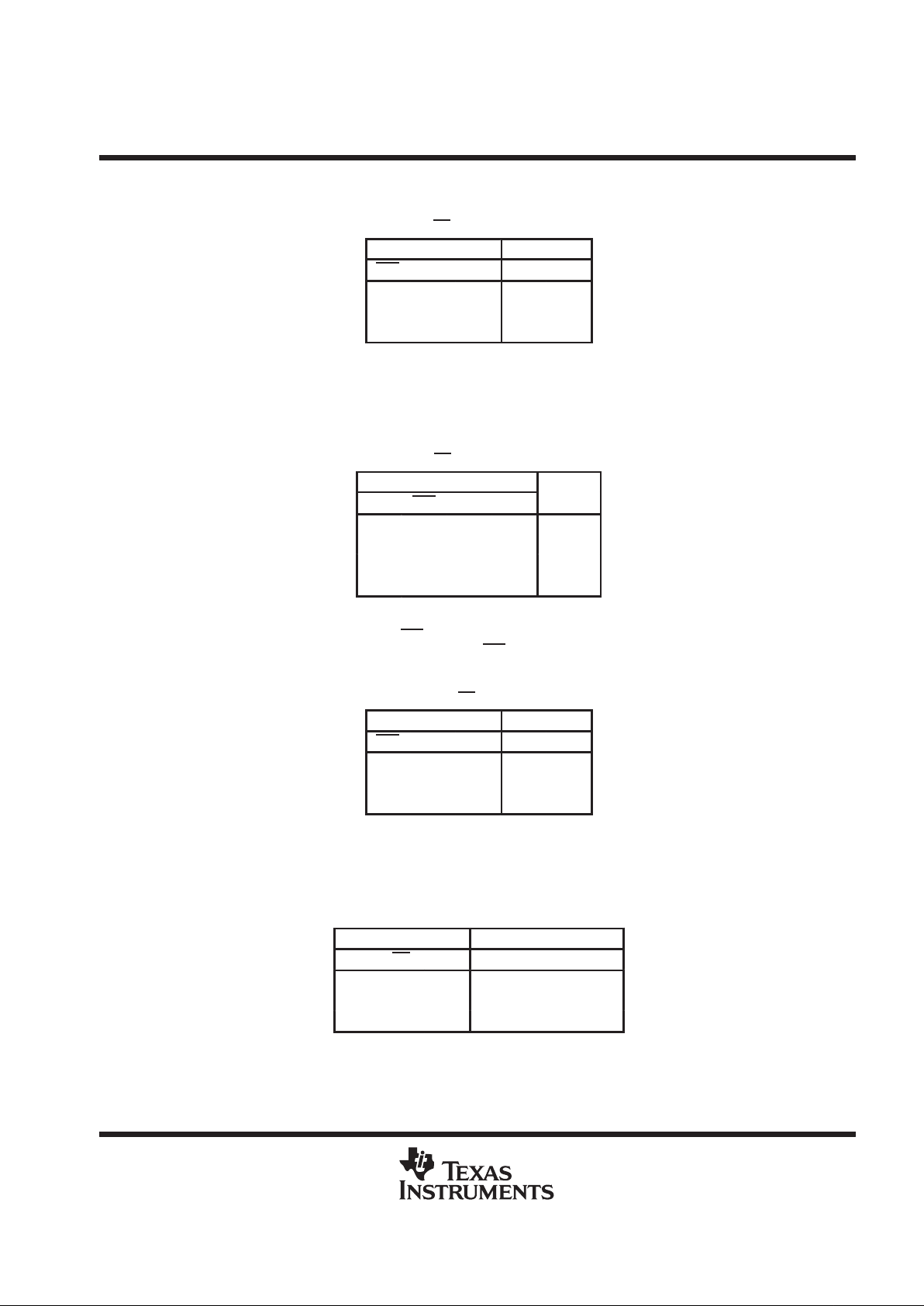

Function Tables

A-TO-B STORAGE

(OE

= L, DIR = H)

INPUTS

OUTPUTS

SEL CLK A 1B 2B

H X X 1B

0

†

2B

0

†

L ↑ LL‡L

L ↑ H H

‡

H

†

Output level before indicated

steady-state input conditions were

established

‡

Two CLK edges are needed to propagate

the data.

B-TO-A STORAGE

(OE

= L, DIR = L)

INPUTS

OUTPUT

CLK SEL 1B 2B

A

↑ H X L L

§

↑ HXH H

§

↑ LLX L

↑ L H X H

§

Two CLK edges are needed to propagate the

data. The data is loaded in the first register

when SEL

is low and propagates to the

second register when SEL

is high.

C-TO-D STORAGE

(OE

= L)

INPUTS

OUTPUTS

SEL CLK C 1D 2D

H X X 1D

0

†

2D

0

†

L ↑ LL‡L

L ↑ H H

‡

H

†

Output level before indicated

steady-state input conditions were

established

‡

Two CLK edges are needed to propagate

the data.

OUTPUT ENABLE

INPUTS

OUTPUTS

CLK OE DIR A 1B, 2B 1D, 2D

↑ H X Z Z Z

↑ LHZActive Active

↑ L L Active Z Active

Loading...

Loading...