Texas Instruments SN74ALVCH16952DGGR, SN74ALVCH16952DGVR, SN74ALVCH16952DL Datasheet

SN74ALVCH16952

16-BIT REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS

SCES011D – JULY 1995 – REVISED FEBRUARY 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Member of the Texas Instruments

Widebus

Family

D

EPIC

(Enhanced-Performance Implanted

CMOS) Submicron Process

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

Latch-Up Performance Exceeds 500 mA Per

JESD 17

D

Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

D

Package Options Include Plastic 300-mil

Shrink Small-Outline (DL), Thin Shrink

Small-Outline (DGG), and Thin Very

Small-Outline (DGV) Packages

description

This 16-bit registered transceiver is designed for

1.65-V to 3.6-V V

CC

operation.

The SN74ALVCH16952 contains two sets of

D-type flip-flops for temporary storage of data

flowing in either direction. This device can be used

as two 8-bit transceivers or one 16-bit transceiver.

Data on the A or B bus is stored in the registers on

the low-to-high transition of the clock (CLKAB or

CLKBA) input provided that the clock-enable

(CLKENAB

or CLKENBA) input is low. Taking the

output-enable (OEAB

or OEBA) input low

accesses the data on either port.

T o ensure the high-impedance state during power

up or power down, OE

should be tied to V

CC

through a pullup resistor; the minimum value of

the resistor is determined by the current-sinking

capability of the driver.

Active bus-hold circuitry is provided to hold

unused or floating data inputs at a valid logic level.

The SN74ALVCH16952 is characterized for

operation from –40°C to 85°C.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus and EPIC are trademarks of Texas Instruments Incorporated.

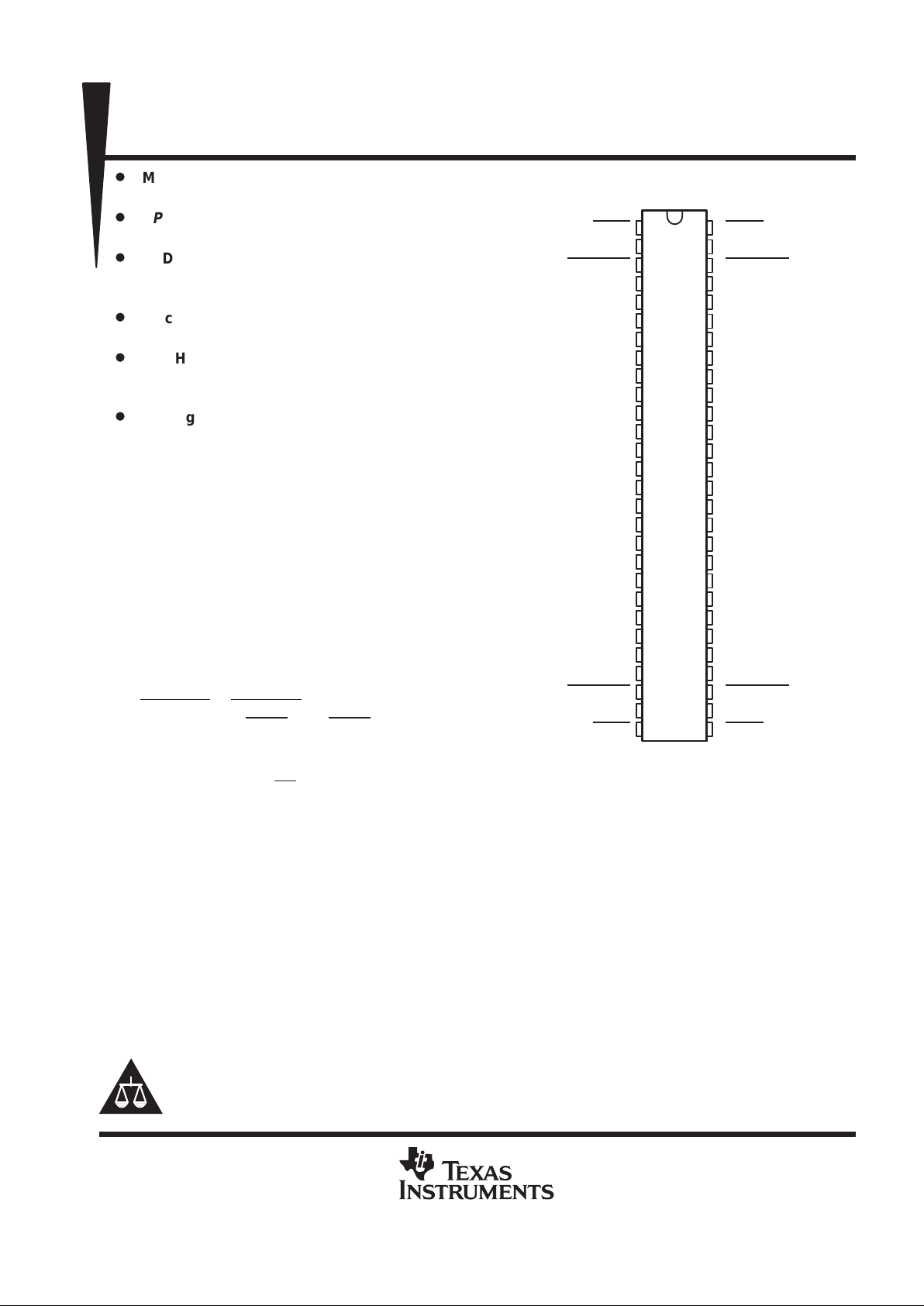

DGG, DGV, OR DL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1OEAB

1CLKAB

1CLKENAB

GND

1A1

1A2

V

CC

1A3

1A4

1A5

GND

1A6

1A7

1A8

2A1

2A2

2A3

GND

2A4

2A5

2A6

V

CC

2A7

2A8

GND

2CLKENAB

2CLKAB

2OEAB

1OEBA

1CLKBA

1CLKENBA

GND

1B1

1B2

V

CC

1B3

1B4

1B5

GND

1B6

1B7

1B8

2B1

2B2

2B3

GND

2B4

2B5

2B6

V

CC

2B7

2B8

GND

2CLKENBA

2CLKBA

2OEBA

SN74ALVCH16952

16-BIT REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS

SCES011D – JULY 1995 – REVISED FEBRUARY 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

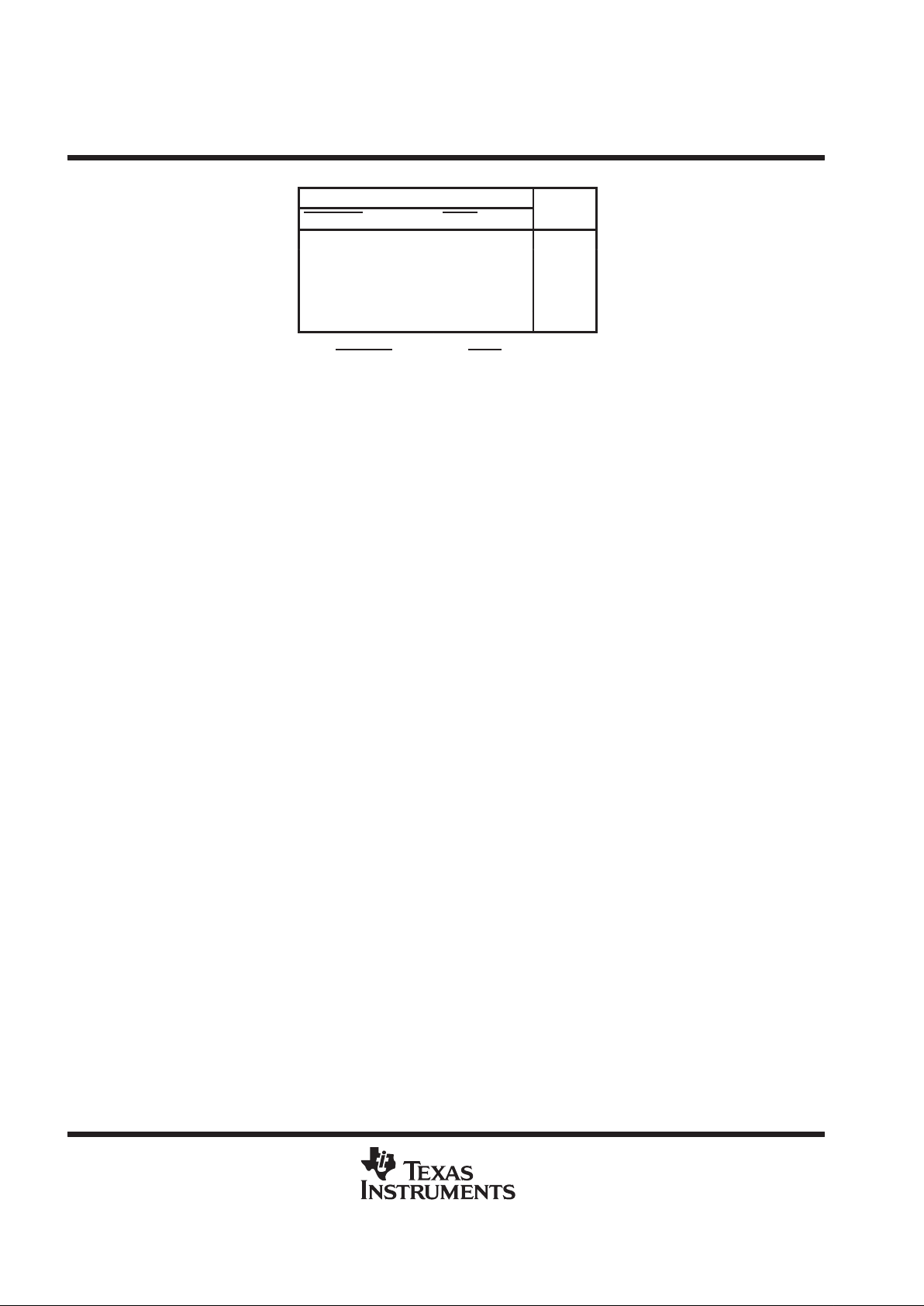

FUNCTION TABLE

†

INPUTS

OUTPUT

CLKENAB CLKAB OEAB

A

B

H X L X B

0

‡

X LLXB

0

‡

L ↑LL L

L ↑ LH H

X X HX Z

†

A-to-B data flow is shown; B-to-A data flow is similar, but

uses CLKENBA

, CLKBA, and OEBA.

‡

Level of B before the indicated steady-state input

conditions were established

SN74ALVCH16952

16-BIT REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS

SCES011D – JULY 1995 – REVISED FEBRUARY 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

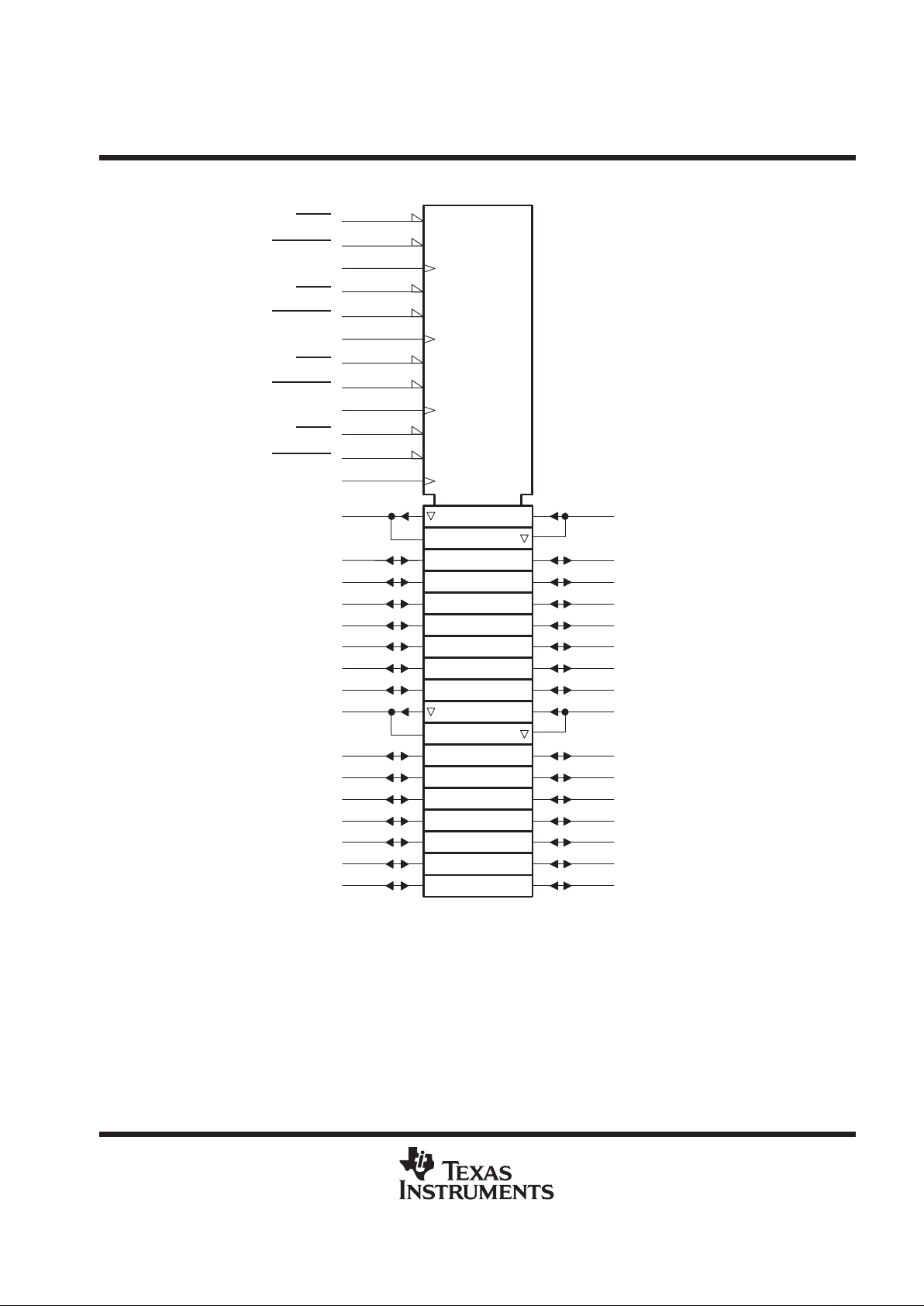

logic symbol

†

1OEBA

1CLKENBA

1OEAB

1CLKENAB

2OEBA

2CLKENBA

2OEAB

2CLKENAB

G8

26

27

2CLKAB

8C12

1A1

5

6D

1A2

6

1A3

8

1A4

9

1A5

10

1A6

12

1A7

13

1A8

14

1B1

52

5D

1B6

45

1B7

44

1B8

43

1B2

51

1B3

49

1B4

48

1B5

47

EN10

28

G7

31

30

2CLKBA

7C11

EN9

29

G2

3

2

1CLKAB

2C6

EN4

1

G1

54

55

1CLKBA

1C5

EN3

56

2A1

15

12D

2A2

16

2A3

17

2A4

19

2A5

20

2A6

21

2A7

23

2A8

24

2B1

42

11D

2B6

36

2B7

34

2B8

33

2B2

41

2B3

40

2B4

38

2B5

37

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

4

10

9

3

SN74ALVCH16952

16-BIT REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS

SCES011D – JULY 1995 – REVISED FEBRUARY 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

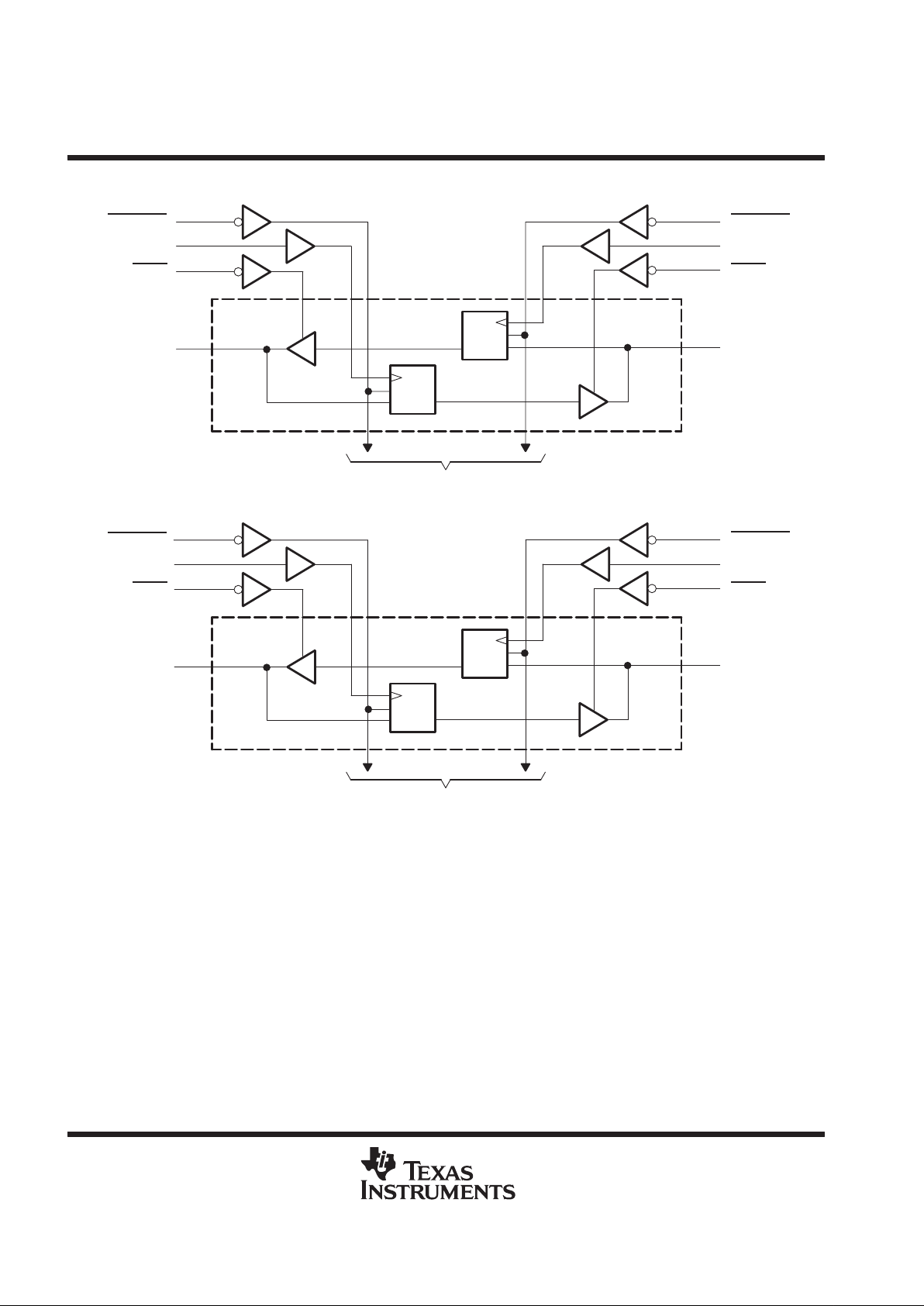

logic diagram (positive logic)

One of Eight

Channels

1A1

One of Eight

Channels

To Seven Other Channels

1CLKAB

1CLKBA

1OEBA

1OEAB

1B1

1CLKENAB

1CLKENBA

To Seven Other Channels

2CLKAB

2CLKBA

2OEBA

2OEAB

2A1

2B1

2CLKENAB

2CLKENBA

3

2

56

5

26

27

29

15

C1

CE

1D

54

55

1

52

31

30

28

42

C1

CE

1D

C1

CE

1D

C1

CE

1D

Loading...

Loading...