Datasheet SN74ALVCH16260DGGR, SN74ALVCH16260DL, SN74ALVCH16260DLR Datasheet (Texas Instruments)

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Member of the Texas Instruments

Widebus

Family

D

EPIC

(Enhanced-Performance Implanted

CMOS) Submicron Process

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

Latch-Up Performance Exceeds 250 mA Per

JESD 17

D

Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

D

Package Options Include Plastic Shrink

Small-Outline (DL) and Thin Shrink

Small-Outline (DGG) Packages

description

This 12-bit to 24-bit multiplexed D-type latch is

designed for 1.65-V to 3.6-V

CC

operation.

The SN74AL VCH16260 is used in applications in

which two separate data paths must be

multiplexed onto, or demultiplexed from, a single

data path. Typical applications include

multiplexing and/or demultiplexing address and

data information in microprocessor or

bus-interface applications. This device also is

useful in memory-interleaving applications.

Three 12-bit I/O ports (A1–A12, 1B1–1B12, and

2B1–2B12) are available for address and/or data

transfer. The output-enable (OE1B

, OE2B, and

OEA

) inputs control the bus transceiver functions.

The OE1B

and OE2B control signals also allow

bank control in the A-to-B direction.

Address and/or data information can be stored using the internal storage latches. The latch-enable (LE1B,

LE2B, LEA1B, and LEA2B) inputs are used to control data storage. When the latch-enable input is high, the

latch is transparent. When the latch-enable input goes low, the data present at the inputs is latched and remains

latched until the latch-enable input is returned high.

T o ensure the high-impedance state during power up or power down, OE

should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH16260 is characterized for operation from –40°C to 85°C.

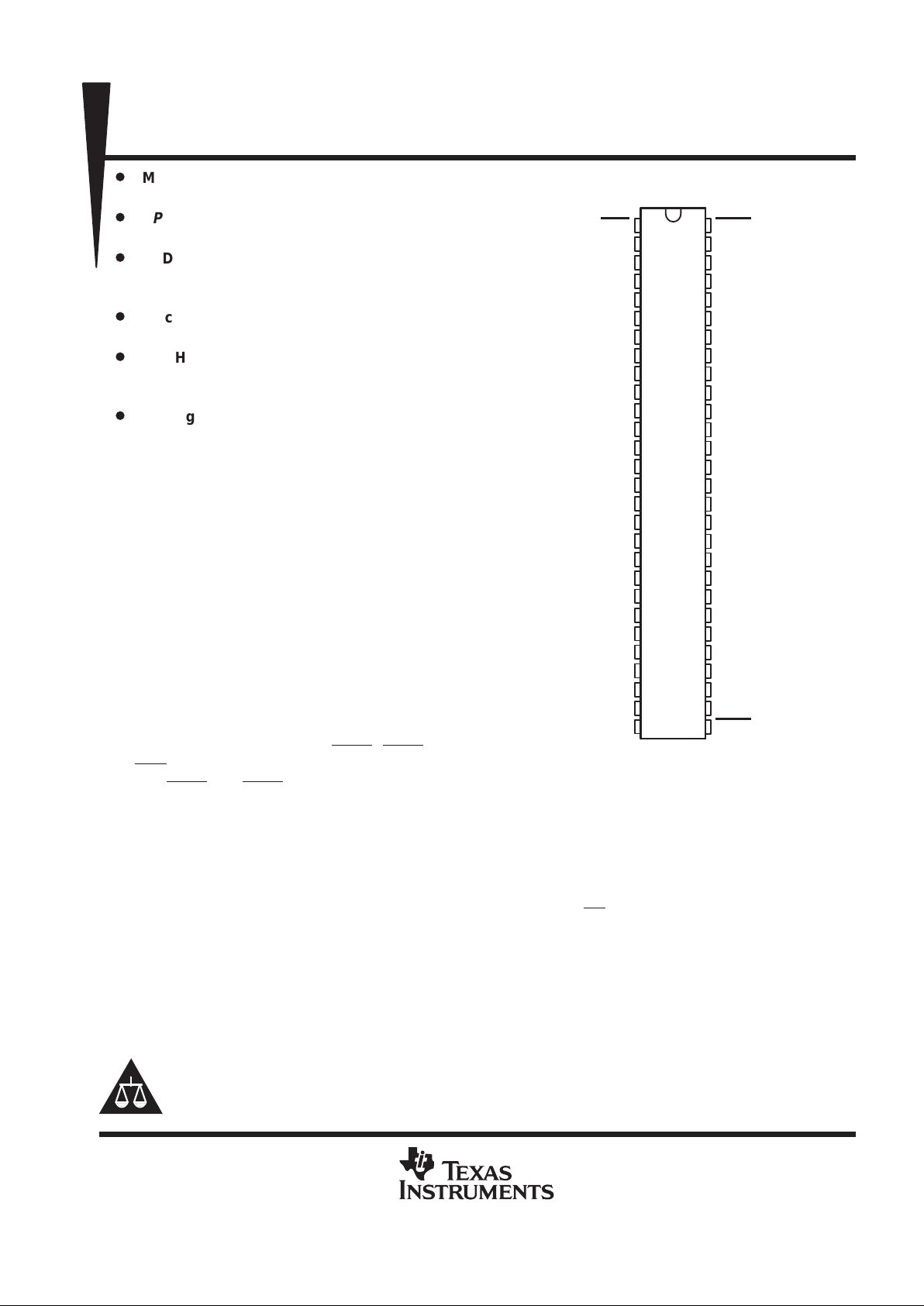

DGG OR DL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

OEA

LE1B

2B3

GND

2B2

2B1

V

CC

A1

A2

A3

GND

A4

A5

A6

A7

A8

A9

GND

A10

A1 1

A12

V

CC

1B1

1B2

GND

1B3

LE2B

SEL

OE2B

LEA2B

2B4

GND

2B5

2B6

V

CC

2B7

2B8

2B9

GND

2B10

2B1 1

2B12

1B12

1B1 1

1B10

GND

1B9

1B8

1B7

V

CC

1B6

1B5

GND

1B4

LEA1B

OE1B

EPIC and Widebus are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1999, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

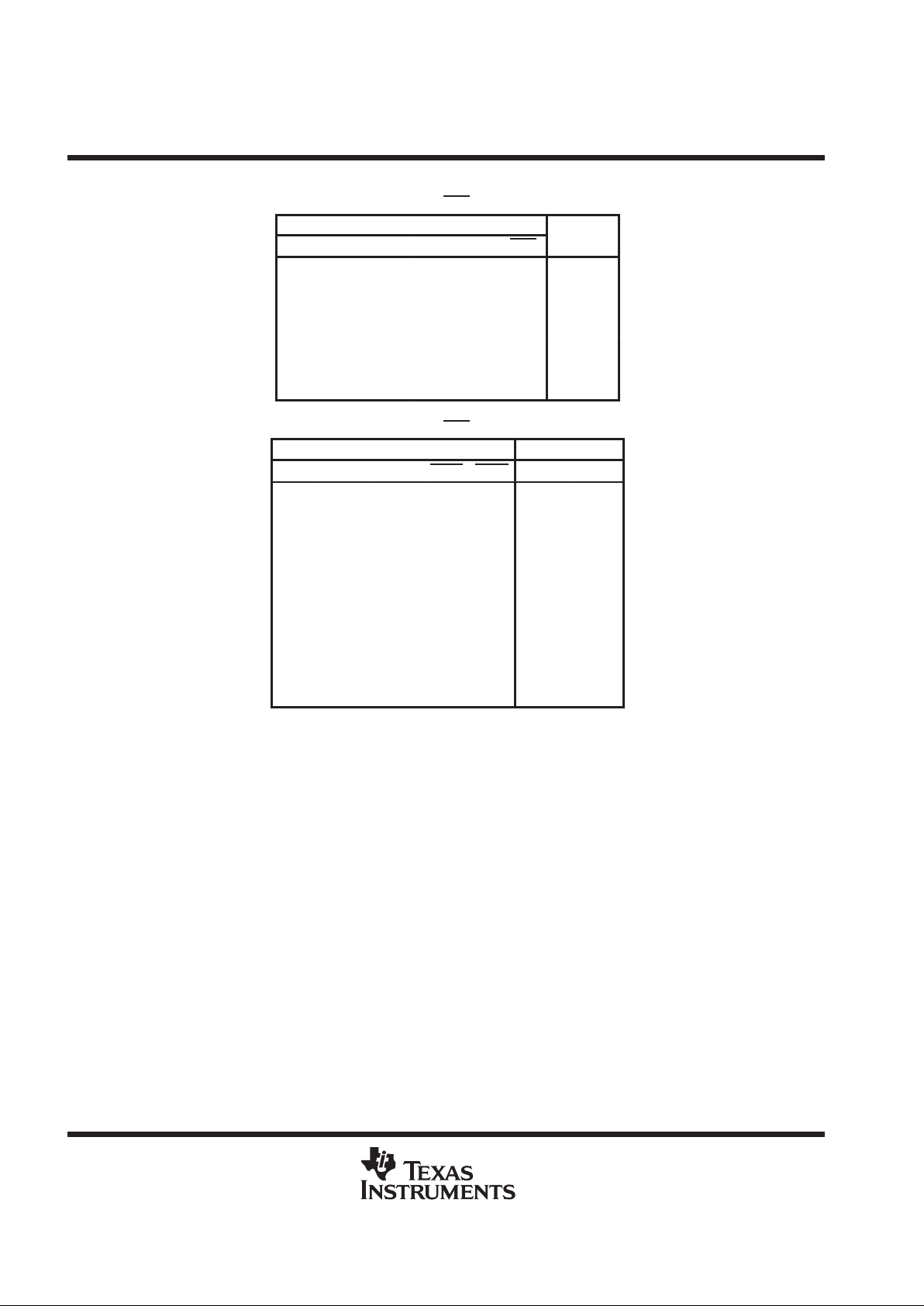

Function Tables

B TO A (OEB = H)

INPUTS

OUTPUT

1B 2B SEL LE1B LE2B OEA

A

H X H H X L H

L XHHXL L

XXHLXL A

0

XHLXHL H

XLLXHL L

XXLXLL A

0

XXXXXH Z

A TO B (OEA = H)

INPUTS

OUTPUTS

A LEA1B LEA2B OE1B OE2B 1B 2B

H H H L L H H

L HHLLLL

HHLLLH2B

0

L HLLLL2B

0

H LHLL1B

0

H

LLHLL1B

0

L

XLLLL1B

02B0

X XXHHZZ

XX X L H Active Z

X XXHLZActive

X X X L L Active Active

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

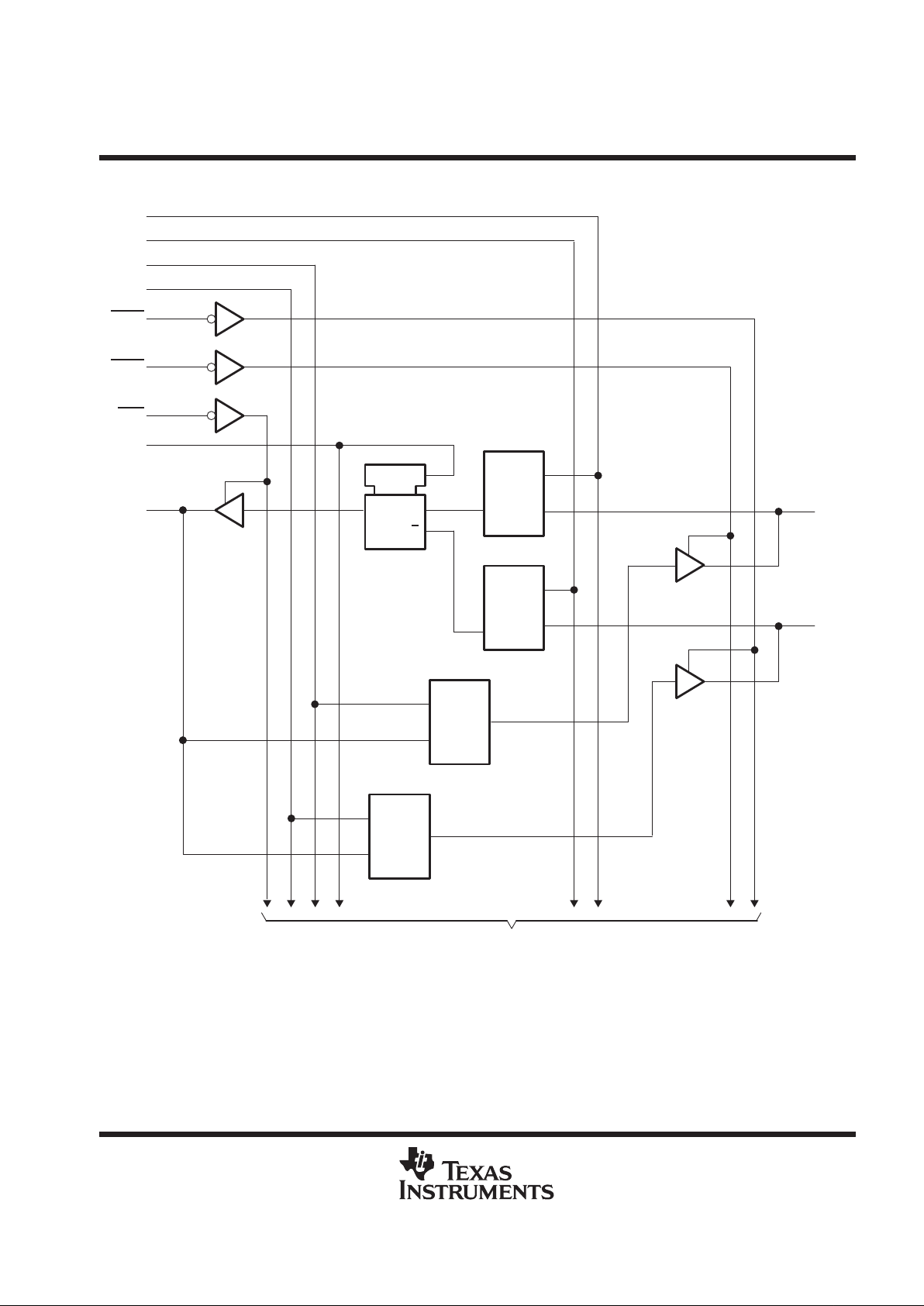

logic diagram (positive logic)

C1

1D

C1

1D

C1

1D

C1

1D

To 11 Other Channels

LE1B

LE2B

LEA1B

LEA2B

OE2B

OE1B

OEA

SEL

A1 1B1

2B1

27

2

30

55

56

29

1

28

8

23

6

G1

1

1

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage range, V

CC

–0.5 V to 4.6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

: Except I/O ports (see Note 1) –0.5 V to 4.6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O ports (see Notes 1 and 2) –0.5 V to V

CC

+ 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, V

O

(see Notes 1 and 2) –0.5 V to VCC + 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(VI < 0) –50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, I

OK

(VO < 0) –50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous output current, I

O

±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through each V

CC

or GND ±100 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance, θ

JA

(see Note 3): DGG package 81°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DL package 74°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. This value is limited to 4.6 V maximum.

3. The package thermal impedance is calculated in accordance with JESD 51.

recommended operating conditions (see Note 4)

MIN MAX UNIT

V

CC

Supply voltage 1.65 3.6 V

VCC = 1.65 V to 1.95 V 0.65 × V

CC

V

IH

High-level input voltage

VCC = 2.3 V to 2.7 V

1.7

V

VCC = 2.7 V to 3.6 V 2

VCC = 1.65 V to 1.95 V 0.35 × V

CC

V

IL

Low-level input voltage

VCC = 2.3 V to 2.7 V 0.7

V

VCC = 2.7 V to 3.6 V 0.8

V

I

Input voltage 0 V

CC

V

V

O

Output voltage 0 V

CC

V

VCC = 1.65 V –4

p

VCC = 2.3 V –12

IOHHigh-level output current

VCC = 2.7 V –12

mA

VCC = 3 V –24

VCC = 1.65 V 4

p

VCC = 2.3 V 12

IOLLow-level output current

VCC = 2.7 V 12

mA

VCC = 3 V 24

∆t/∆v Input transition rise or fall rate 10 ns/V

T

A

Operating free-air temperature –40 85 °C

NOTE 4: All unused control inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs

, literature number SCBA004.

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER TEST CONDITIONS

V

CC

MIN TYP†MAX UNIT

IOH = –100 µA 1.65 V to 3.6 V VCC–0.2

IOH = –4 mA 1.65 V 1.2

IOH = –6 mA 2.3 V 2

V

OH

2.3 V 1.7

V

IOH = –12 mA

2.7 V 2.2

3 V 2.4

IOH = –24 mA 3 V 2

IOL = 100 µA 1.65 V to 3.6 V 0.2

IOL = 4 mA 1.65 V 0.45

IOL = 6 mA 2.3 V 0.4

V

OL

2.3 V 0.7

V

I

OL

= 12

mA

2.7 V 0.4

IOL = 24 mA 3 V 0.55

I

I

VI = VCC or GND 3.6 V ±5 µA

VI = 0.58 V 1.65 V 25

VI = 1.07 V 1.65 V –25

VI = 0.7 V 2.3 V 45

I

I(hold)

VI = 1.7 V 2.3 V –45

µA

()

VI = 0.8 V 3 V 75

VI = 2 V 3 V –75

VI = 0 to 3.6 V

‡

3.6 V ±500

I

OZ

§

VO = VCC or GND 3.6 V ±10 µA

I

CC

VI = VCC or GND, IO = 0 3.6 V 40 µA

∆I

CC

One input at VCC – 0.6 V, Other inputs at VCC or GND 3 V to 3.6 V 750 µA

C

i

Control inputs VI = VCC or GND 3.3 V 3.5 pF

C

io

A or B ports VO = VCC or GND 3.3 V 9 pF

†

All typical values are at VCC = 3.3 V, TA = 25°C.

‡

This is the bus-hold maximum dynamic current. It is the minimum overdrive current required to switch the input from one state to another.

§

For I/O ports, the parameter IOZ includes the input leakage current.

timing requirements over recommended operating free-air temperature range (unless otherwise

noted) (see Figures 1 through 3)

VCC = 1.8 V

VCC = 2.5 V

± 0.2 V

VCC = 2.7 V

VCC = 3.3 V

± 0.3 V

UNIT

MIN MAX MIN MAX MIN MAX MIN MAX

t

w

Pulse duration, LE1B, LE2B, LEA1B, or LEA2B high

¶

3.3 3.3 3.3 ns

t

su

Setup time, data before LE1B, LE2B, LEA1B, or

LEA2B

¶

1.4 1.1 1.1 ns

t

h

Hold time, data after LE1B, LE2B, LEA1B, or LEA2B

¶

1.6 1.9 1.5 ns

¶

This information was not available at the time of publication.

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

switching characteristics over recommended operating free-air temperature range (unless

otherwise noted) (see Figures 1 through 3)

PARAMETER

FROM

TO

VCC = 1.8 V

VCC = 2.5 V

± 0.2 V

VCC = 2.7 V

VCC = 3.3 V

± 0.3 V

UNIT

(INPUT)

(OUTPUT)

TYP MIN MAX MIN MAX MIN MAX

A or B B or A

†

1 5.4 5.1 1.2 4.3

t

pd

LE A or B

†

1 5.6 5.2 1 4.4

ns

SEL A

†

1 6.9 6.6 1.1 5.6

t

en

OE

A or B

†

1 6.7 6.4 1 5.4 ns

t

dis

OE

A or B

†

1 5.7 5 1.3 4.6 ns

†

This information was not available at the time of publication.

operating characteristics, T

A

= 25°C

VCC = 1.8 V VCC = 2.5 V VCC = 3.3 V

PARAMETER

TEST CONDITIONS

TYP TYP TYP

UNIT

Power dissipation

All outputs enabled

p

†

37 41

p

C

pd

capacitance

All outputs disabled

C

L

= 50 pF,f = 10 MHz

†

4 7

pF

†

This information was not available at the time of publication.

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

V

CC

= 1.8 V

VCC/2

VCC/2

VCC/2VCC/2

VCC/2VCC/2

VCC/2

VCC/2

V

OH

V

OL

t

h

t

su

From Output

Under Test

CL = 30 pF

(see Note A)

LOAD CIRCUIT

S1

Open

GND

1 kΩ

1 kΩ

Output

Control

(low-level

enabling)

Output

Waveform 1

S1 at 2 × V

CC

(see Note B)

Output

Waveform 2

S1 at GND

(see Note B)

t

PZL

t

PZH

t

PLZ

t

PHZ

0 V

VOL + 0.15 V

VOH – 0.15 V

0 V

V

CC

0 V

0 V

t

w

V

CC

V

CC

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

VOLTAGE WAVEFORMS

PULSE DURATION

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

Timing

Input

Data

Input

Input

t

pd

t

PLZ/tPZL

t

PHZ/tPZH

Open

2 × V

CC

GND

TEST S1

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω, tr ≤ 2 ns, tf ≤ 2 ns.

D. The outputs are measured one at a time with one transition per measurement.

E. t

PLZ

and t

PHZ

are the same as t

dis

.

F. t

PZL

and t

PZH

are the same as ten.

G. t

PLH

and t

PHL

are the same as tpd.

0 V

V

CC

VCC/2

t

PHL

VCC/2 VCC/2

V

CC

0 V

V

OH

V

OL

Input

Output

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VCC/2 VCC/2

t

PLH

2 × V

CC

V

CC

Figure 1. Load Circuit and Voltage Waveforms

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

V

CC

= 2.5 V ± 0.2 V

VCC/2

VCC/2

VCC/2VCC/2

VCC/2VCC/2

VCC/2

VCC/2

V

OH

V

OL

t

h

t

su

From Output

Under Test

CL = 30 pF

(see Note A)

LOAD CIRCUIT

S1

Open

GND

500 Ω

500 Ω

Output

Control

(low-level

enabling)

Output

Waveform 1

S1 at 2 × V

CC

(see Note B)

Output

Waveform 2

S1 at GND

(see Note B)

t

PZL

t

PZH

t

PLZ

t

PHZ

0 V

VOL + 0.15 V

VOH – 0.15 V

0 V

V

CC

0 V

0 V

t

w

V

CC

V

CC

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

VOLTAGE WAVEFORMS

PULSE DURATION

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

Timing

Input

Data

Input

Input

t

pd

t

PLZ/tPZL

t

PHZ/tPZH

Open

2 × V

CC

GND

TEST S1

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω, tr ≤ 2 ns, tf ≤ 2 ns.

D. The outputs are measured one at a time with one transition per measurement.

E. t

PLZ

and t

PHZ

are the same as t

dis

.

F. t

PZL

and t

PZH

are the same as ten.

G. t

PLH

and t

PHL

are the same as tpd.

0 V

V

CC

VCC/2

t

PHL

VCC/2 VCC/2

V

CC

0 V

V

OH

V

OL

Input

Output

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VCC/2 VCC/2

t

PLH

2 × V

CC

V

CC

Figure 2. Load Circuit and Voltage Waveforms

SN74ALVCH16260

12-BIT TO 24-BIT MULTIPLEXED D-TYPE LATCH

WITH 3-STATE OUTPUTS

SCES046E – JULY 1995 – REVISED FEBRUARY 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

V

CC

= 2.7 V AND 3.3 V ± 0.3 V

V

OH

V

OL

t

h

t

su

From Output

Under Test

CL = 50 pF

(see Note A)

LOAD CIRCUIT

S1

6 V

Open

GND

500 Ω

500 Ω

t

PLH

t

PHL

Output

Control

(low-level

enabling)

Output

Waveform 1

S1 at 6 V

(see Note B)

Output

Waveform 2

S1 at GND

(see Note B)

t

PZL

t

PZH

t

PLZ

t

PHZ

2.7 V

0 V

V

OH

V

OL

0 V

VOL + 0.3 V

VOH – 0.3 V

0 V

2.7 V

0 V

0 V

2.7 V

0 V

t

w

Input

2.7 V

2.7 V

3 V

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

PULSE DURATION

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

Timing

Input

Data

Input

Output

Input

t

pd

t

PLZ/tPZL

t

PHZ/tPZH

Open

6 V

GND

TEST S1

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω, tr ≤2.5 ns, tf ≤2.5 ns.

D. The outputs are measured one at a time with one transition per measurement.

E. t

PLZ

and t

PHZ

are the same as t

dis

.

F. t

PZL

and t

PZH

are the same as ten.

G. t

PLH

and t

PHL

are the same as tpd.

1.5 V

1.5 V

1.5 V

1.5 V 1.5 V

1.5 V 1.5 V

1.5 V

1.5 V

1.5 V 1.5 V

1.5 V

1.5 V

Figure 3. Load Circuit and Voltage Waveforms

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...