SN74ALS990

8-BIT D-TYPE TRANSPARENT READ-BACK LATCH

SDAS027B – APRIL 1984 – REVISED JANUARY 1995

Copyright 1995, Texas Instruments Incorporated

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

• 3-State I/O-Type Read-Back Inputs

• Bus-Structured Pinout

• True Logic Outputs

• Package Options Include Plastic

Small-Outline (DW) Packages and Standard

Plastic (N) 300-mil DIPs

description

This 8-bit latch is designed specifically for storing

the contents of the input data bus and providing

the capability of reading back the stored data onto

the input data bus.

The eight latches are transparent D-type latches.

While the latch-enable (LE) input is high, the

Q outputs follow the data (D) inputs.

Read back is provided through the output-enable (OERB

) input. When OERB is taken low, the data present at

the output of the data latches is allowed to pass back onto the input data bus. When OERB

is taken high, the

output of the data latches is isolated from the D inputs. OERB

does not affect the internal operation of the latches;

however, precautions should be taken not to create a bus conflict.

The SN74ALS990 is characterized for operation from 0°C to 70°C.

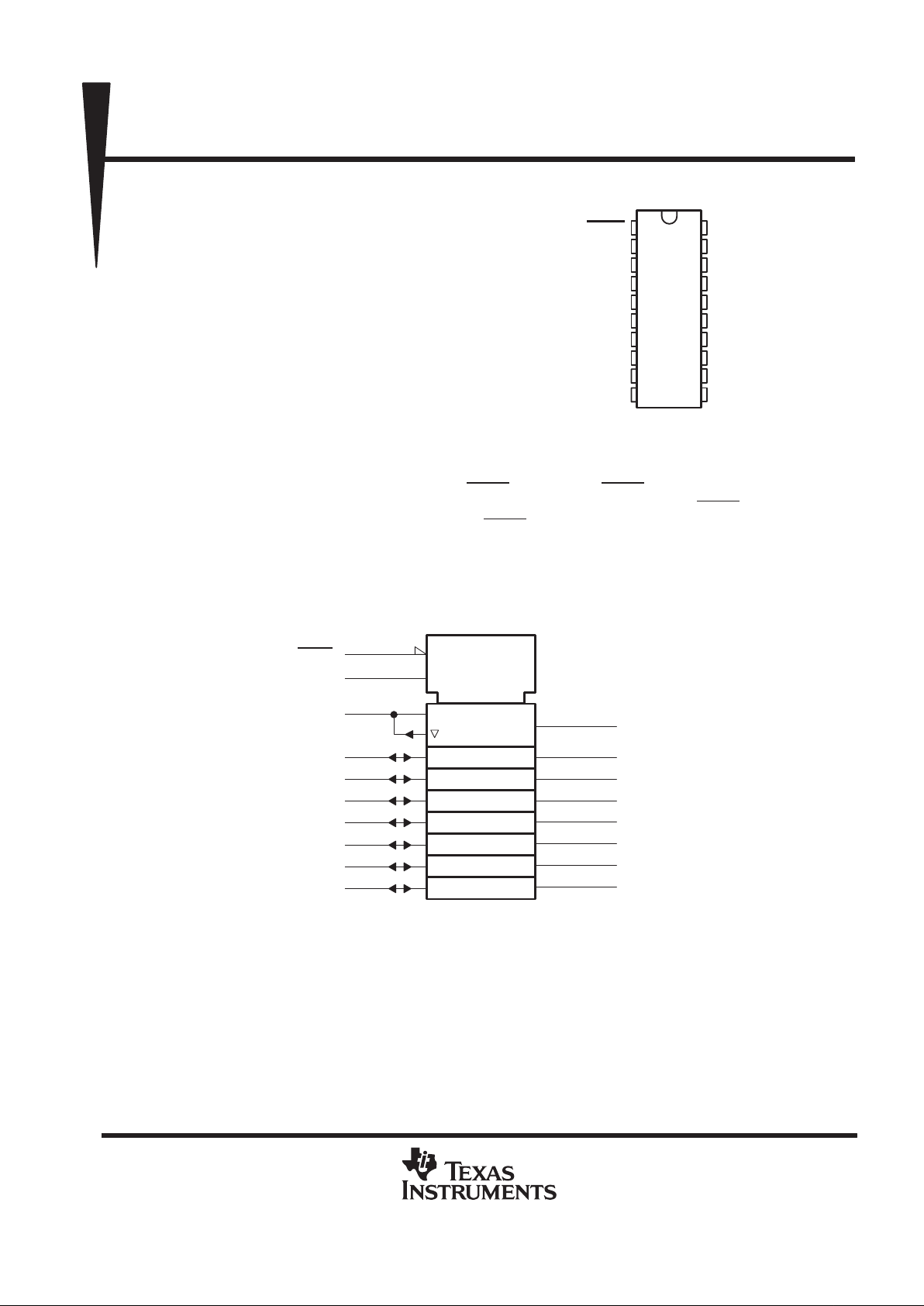

logic symbol

†

C1

11

LE

2D

3

3D

4

4D

5

5D

6

6D

7

7D

8

8D

9

5Q

15

6Q

14

7Q

13

8Q

12

2Q

18

3Q

17

4Q

16

1Q

19

1D

2

1D

EN2

1

OERB

2

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

DW OR N PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

OERB

1D

2D

3D

4D

5D

6D

7D

8D

GND

V

CC

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

LE

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN74ALS990

8-BIT D-TYPE TRANSPARENT READ-BACK LATCH

SDAS027B – APRIL 1984 – REVISED JANUARY 1995

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

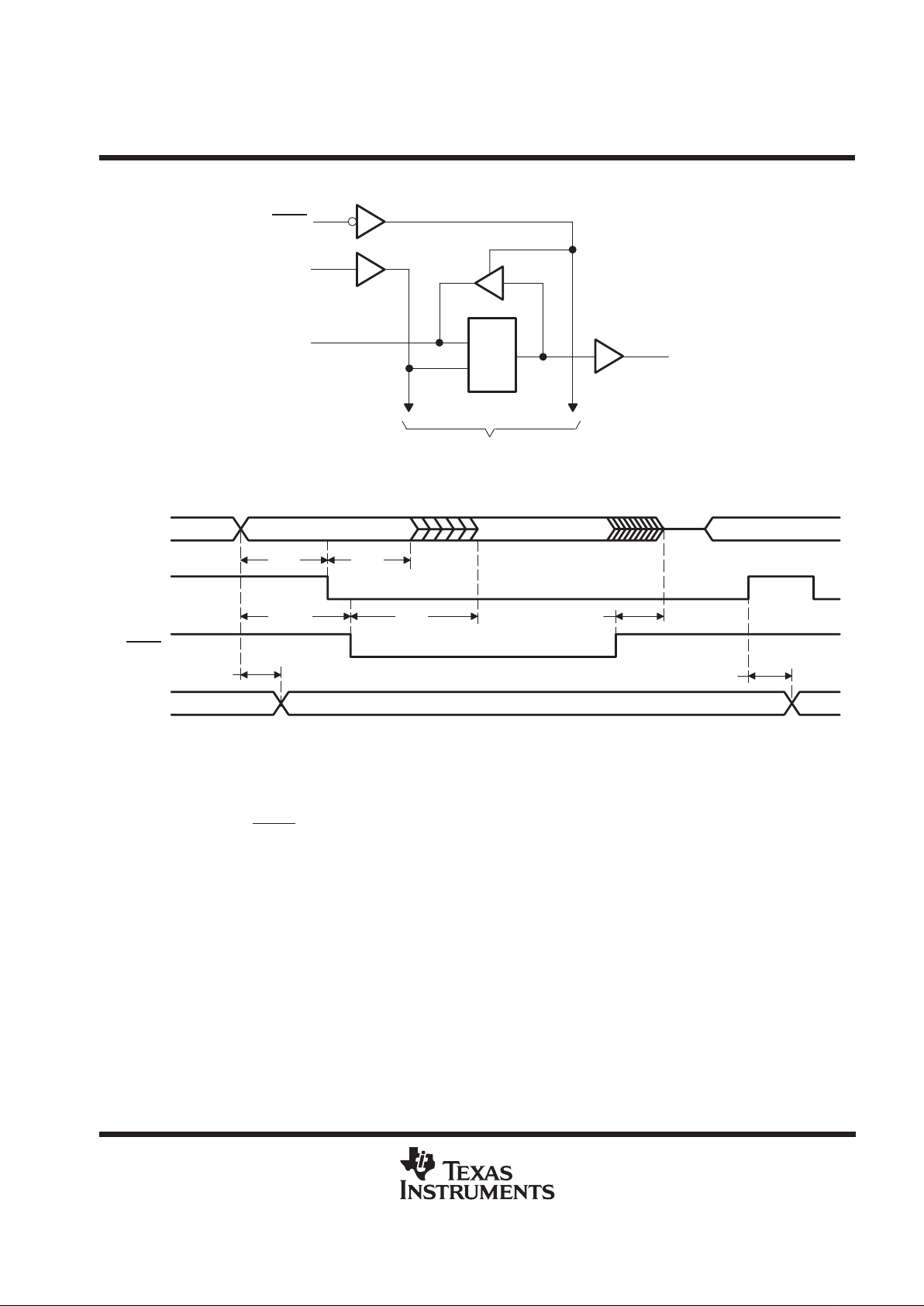

logic diagram (positive logic)

1D

C1

To Seven Other Channels

1

11

2

19

OERB

LE

1D

1Q

timing diagram

Data Bus

LE

OERB

Q

t

su

t

h

t

pd

t

dis

Input Data Read Back Input Data

t

pd

t

su

†

t

en

†

This setup time ensures that the read-back circuit will not create a conflict on the input data bus.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

‡

Supply voltage, V

CC

7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage, V

I

(OERB and LE) 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage applied to D inputs 5.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

‡

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Loading...

Loading...