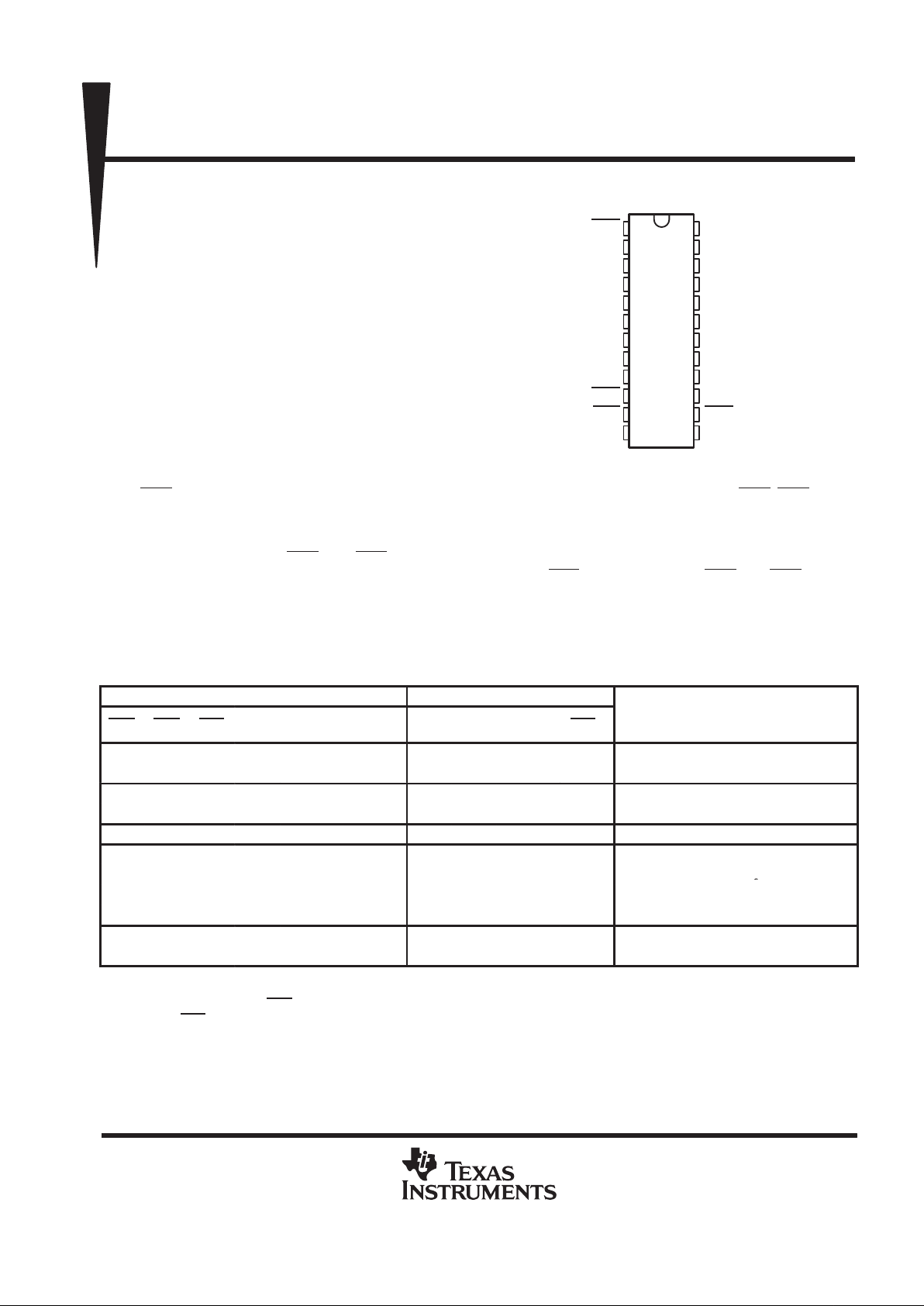

DW OR NT PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OEA

A1

A2

A3

A4

A5

A6

A7

A8

ERR

CLR

GND

V

CC

B1

B2

B3

B4

B5

B6

B7

B8

PARITY

OEB

CLK

SN74ALS29833

8-BIT TO 9-BIT PARITY BUS TRANSCEIVER

SDAS119D – FEBRUARY 1987 – REVISED JANUAR Y 1995

Copyright 1995, Texas Instruments Incorporated

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

• Functionally Similar to AMD’s AM29833

• High-Speed Bus Transceiver With Parity

Generator/Checker

• Parity-Error Flag With Open-Collector

Outputs

• Register for Storing the Parity-Error Flag

• Package Options Include Plastic

Small-Outline (DW) Packages and Standard

Plastic (NT) 300-mil DIPs

description

The SN74ALS29833 is an 8-bit to 9-bit parity

transceiver designed for two-way communication

between data buses. When data is transmitted

from the A bus to the B bus, a parity bit is

generated. When data is transmitted from the B bus to the A bus with its corresponding parity bit, the parity-error

(ERR

) output indicates whether or not an error in the B data has occurred. The output-enable (OEA, OEB) inputs

can be used to disable the device so that the buses are effectively isolated.

A 9-bit parity generator/checker generates a parity-odd (P ARITY) output and monitors the parity of the I/O ports

with an open-collector ERR

flag. ERR is clocked into the register on the rising edge of the clock (CLK) input.

The error-flag register is cleared with a low pulse on the clear (CLR

) input. When both OEA and OEB are low,

data is transferred from the A bus to the B bus and inverted parity is generated. Inverted parity is a forced error

condition that gives the designer more system diagnostic capability.

The SN74ALS29833 is characterized for operation from 0°C to 70°C.

FUNCTION TABLE

INPUTS

OUTPUT AND I/O

OEB OEA CLR

CLK

Ai

∑ of Hs

Bi

†

∑ of Ls

A B PARITY

ERR

‡

FUNCTION

Odd

L

p

LHX

X

Even

NANAAHNA

A data to B bus and generate parit

y

Odd

H

p

HLH↑NA

Even

BNANALB data to A bus and check parit

y

X X L X X X X NA NA H Clear error-flag register

H No↑ X NC

LNo↑ X

H

H

H

H ↑ Odd

XZZ

Z

H

Isolati

on

§

H ↑ Even L

Odd

H

A data to B bus and generate inverted

LLX

X

Even

NANAALNA

g

parity

NA = not applicable, NC = no change, X = don’t care

†

Summation of high-level inputs includes PARITY along with Bi inputs.

‡

Output states shown assume ERR

was previously high.

§

In this mode, ERR

, when clocked, shows inverted parity of the A bus.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN74ALS29833

8-BIT TO 9-BIT PARITY BUS TRANSCEIVER

SDAS119D – FEBRUAR Y 1987 – REVISED JANUAR Y 1995

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

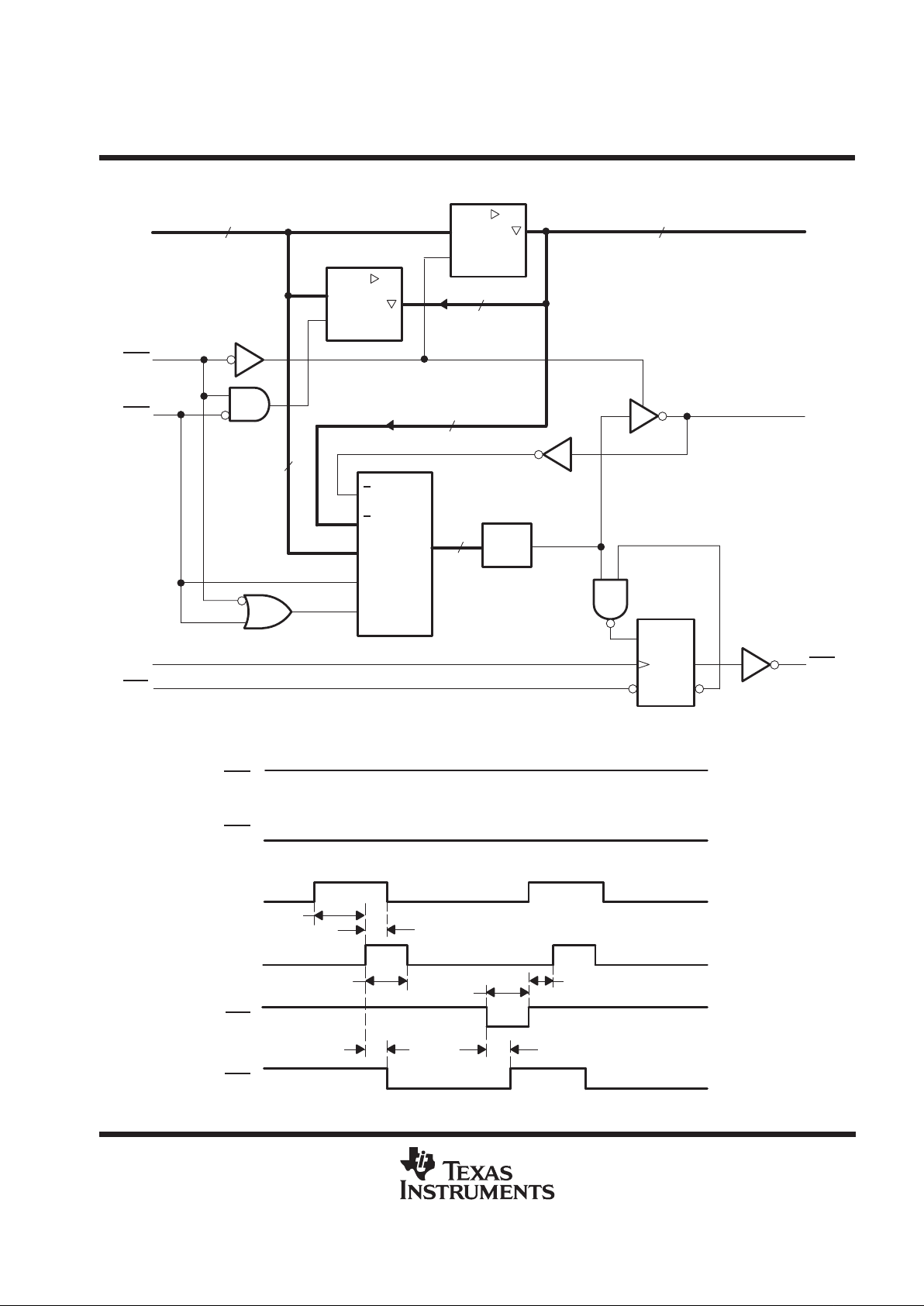

logic diagram (positive logic)

8x

EN

A1–A8

OEA

OEB

CLK

CLR

G1

1

1

1

1

MUX

2K

EN

8x

B1–B8

PARITY

ERR

88

8

8

8

9

P

R

C1

1D

14

1

13

11

15

10

2–9 16–23

error-flag waveforms

ERR

CLR

CLK

Bi + PARITY

OEA

OEB

Even

H

Odd

L

H

L

H

L

H

L

H

L

t

su

t

PLH

t

w

t

w

t

h

t

su

t

PHL

Loading...

Loading...