Texas Instruments SN74ALS236N Datasheet

SN74ALS236

64 × 4

ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORY

SDAS107C – OCTOBER 1986 – REVISED APRIL 1998

D

Asynchronous Operation

D

Organized as 64 Words by 4 Bits

D

Data Rates up to 30 MHz

D

3-State Outputs

D

Package Options Include Plastic

Small-Outline Package (DW), Plastic

J-Leaded Chip Carriers (FN), and Standard

Plastic 300-mil DIPs (N)

description

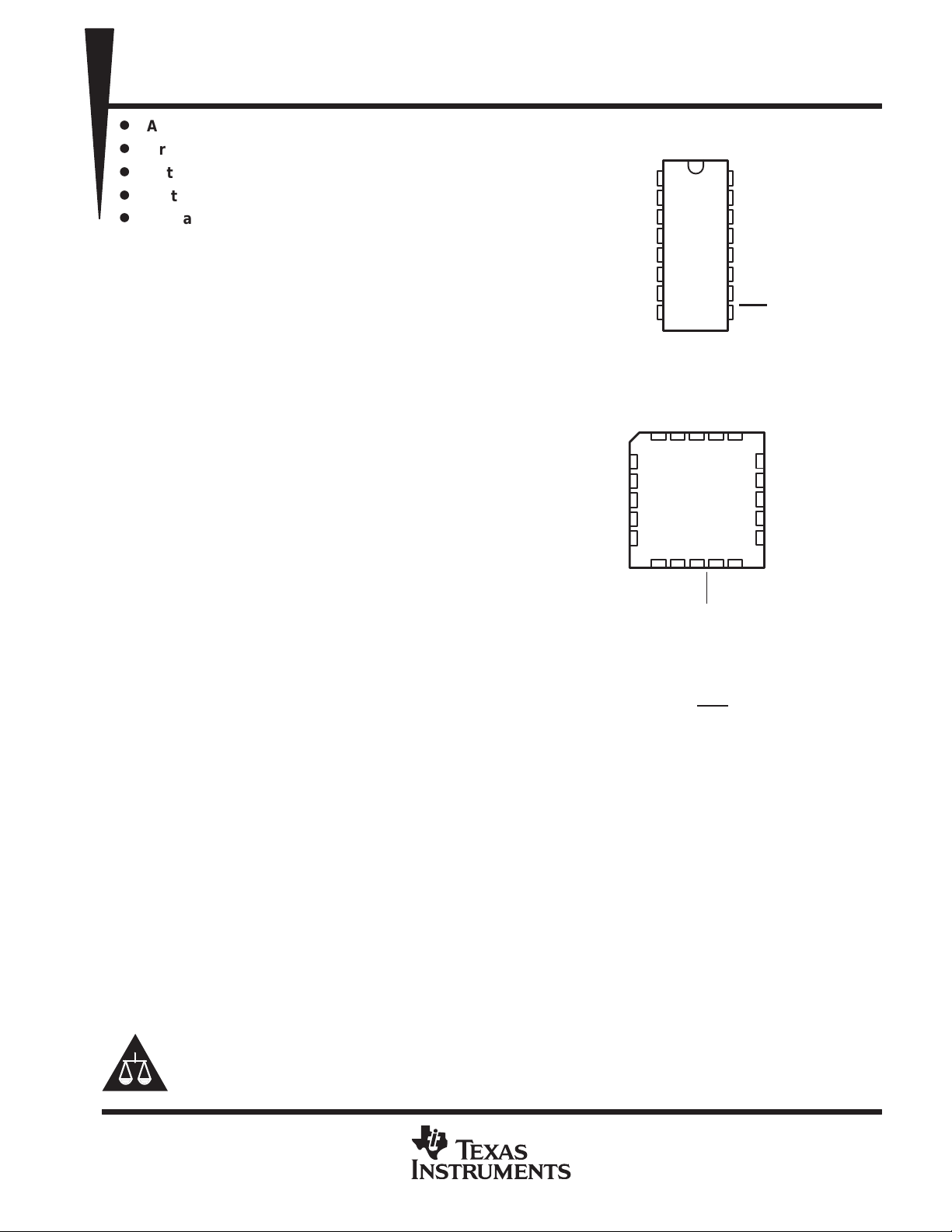

DW OR N PACKAGE

(TOP VIEW)

1

NC

IR

SI

D0

D1

D2

D3

GND

16

2

15

3

14

4

13

5

12

6

11

7

10

8

V

CC

SO

OR

Q0

Q1

Q2

Q3

RST

9

The SN74ALS236 is a 256-bit memory utilizing

advanced low-power Schottky IMPACT

technology. It features high speed with fast

FN PACKAGE

(TOP VIEW)

fall-through times and is organized as 64 words by

4 bits.

A first-in, first-out (FIFO) memory is a storage

device that allows data to be written into and read

from its array at independent data rates. The

SN74ALS236 is designed to process data at rates

up to 30 MHz in a bit-parallel format, word by

word.

SI

D0

NC

D1

D2

IR

3 2 1 20 19

4

5

6

7

8

910111213

NC

NC

V

CC

SO

18

17

16

15

14

OR

Q0

NC

Q1

Q2

Data is written into memory on the rising edge of

the shift-in (SI) input. When SI goes low, the first

data word ripples through to the output (see

Figure 1). As the FIFO fills up, the data words

NC – No internal connection

D3

GND

NC

RST

Q3

stack up in the order they were written. When the

FIFO is full, additional shift-in pulses have no

effect. Data is shifted out of memory on the falling

edge of the shift-out (SO) input (see Figure 2). When the FIFO is empty , additional SO pulses have no ef fect.

The last data word remains at the outputs until a new word falls through or reset (RST

) goes low.

Status of the SN74ALS236 FIFO memory is monitored by the output-ready (OR) and input-ready (IR) flags.

When OR is high, valid data is available at the outputs. OR is low when SO is high and stays low when the FIFO

is empty . IR is high when the inputs are ready to receive more data. IR is low when SI is high and stays low when

the FIFO is full.

When the FIFO is empty, input data is shifted to the output automatically when SI goes low. If SO is held high

during this time, the OR flag pulses high, indicating valid data at the outputs (see Figure 3).

When the FIFO is full, data is shifted in automatically by holding SI high and taking SO low. One propagation

delay after SO goes low, IR goes high. If SI is still high when IR goes high, data at the inputs is automatically

shifted in. Since IR is normally low when the FIFO is full and SI is high, only a high-level pulse is seen on the

IR output (see Figure 4).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IMPACT is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1998, Texas Instruments Incorporated

1

SN74ALS236

64 × 4

ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORY

SDAS107C – OCTOBER 1986 – REVISED APRIL 1998

description (continued)

The FIFO must be reset after power up with a low-level pulse on the master reset (RST) input. This sets IR high

and OR low, signifying that the FIFO is empty. Resetting the FIFO sets the outputs to a low logic level (see

Figure 1). If SI is high when RST

SI goes low. If SI goes low before RST

are noninverting with respect to the data inputs.

The SN74ALS236 is characterized for operation from 0°C to 70°C.

goes high, the input data is shifted in and IR goes low and remains low until

goes high, the input data is not shifted in and IR goes high. Data outputs

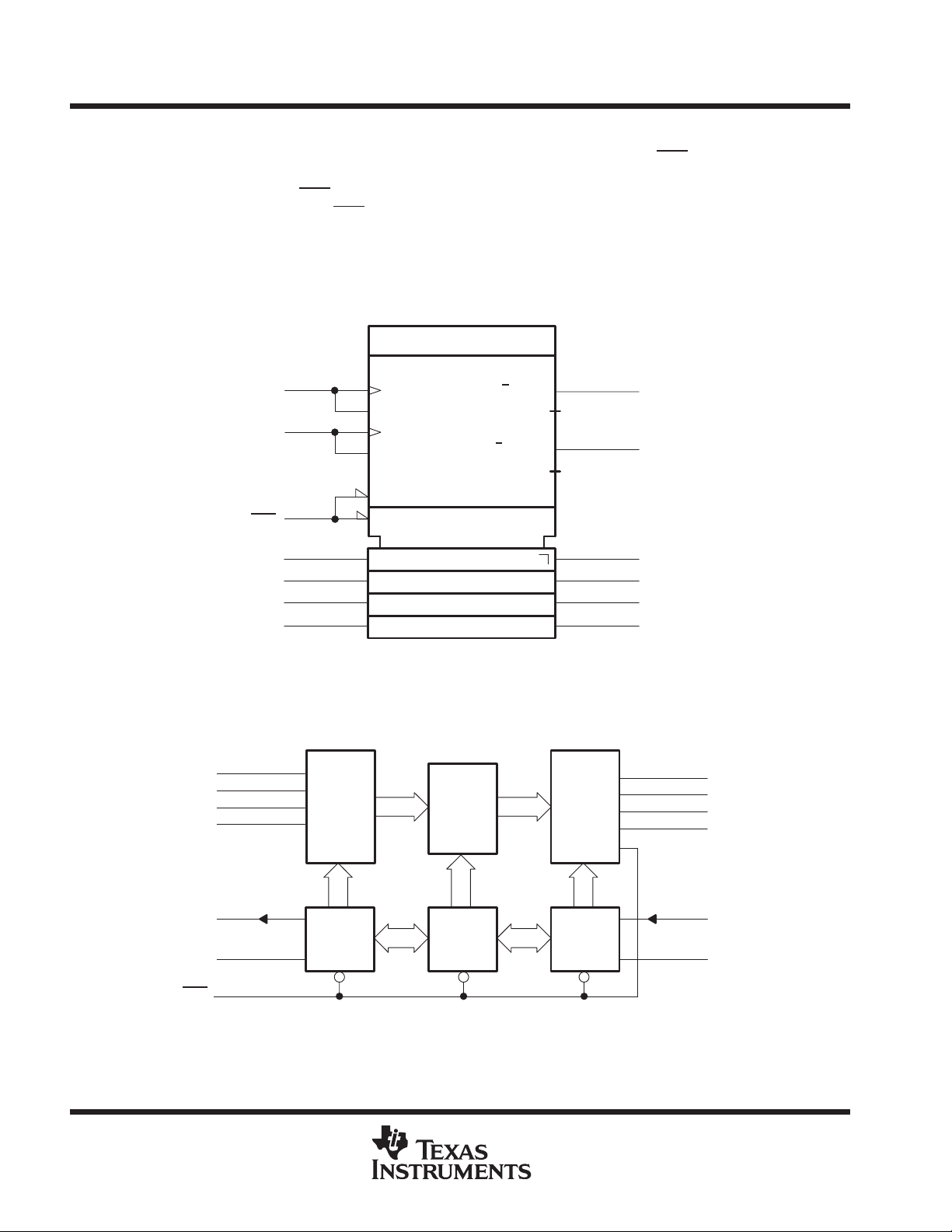

logic symbol

†

This symbol is in accordance with ANSI/IEEE Standard 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the DW and N packages.

†

FIFO 64 × 4

3

SI

15

SO

9

RST

4

D0 Q0

5

D1

6

D2

7

D3

5 + /C1

G2

4 –

G3

CT = 0

R

1D

CTR

(CT > 0) G4

(CT < 64) G5

CT > 0

3

CT < 64

2

functional block diagram

14

13

12

11

10

OR

2

IR

Q1

Q2

Q3

4

D0

5

D1

6

D2

7

D3

2

IR

3

SI

RST

Pin numbers shown are for the DW and N packages.

2

9

FIFO

Input

Stage

Input-

Control

Logic

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

62 × 4 Bit

Register

Register-

Control

Logic

FIFO

Output

Stage

OutputControl

Logic

13

12

11

10

15

14

Q0

Q1

Q2

Q3

SO

OR

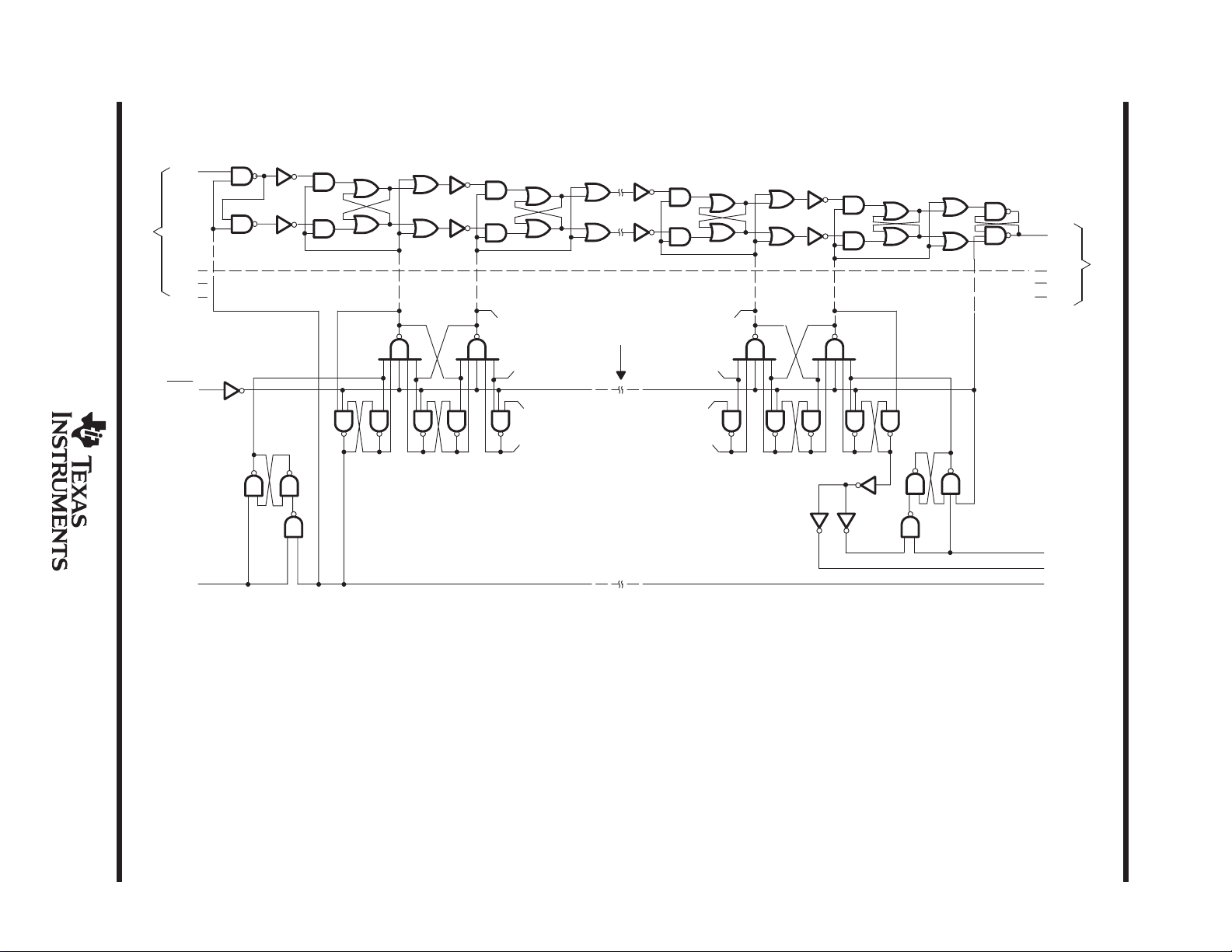

logic diagram (positive logic)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D0

Data Inputs

D1

D2

D3

RST

SI

Word 64 Word 63 Word 3 Word 2

Words 4 – 62

Same as 3 or 63

Word 1

Q0

Q1

Q2

Q3

SO

OR

IR

Data Outputs

ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORY

SDAS107C – OCTOBER 1986 – REVISED APRIL 1998

SN74ALS236

64 × 4

3

SN74ALS236

64 × 4

ASYNCHRONOUS FIRST-IN, FIRST-OUT MEMORY

SDAS107C – OCTOBER 1986 – REVISED APRIL 1998

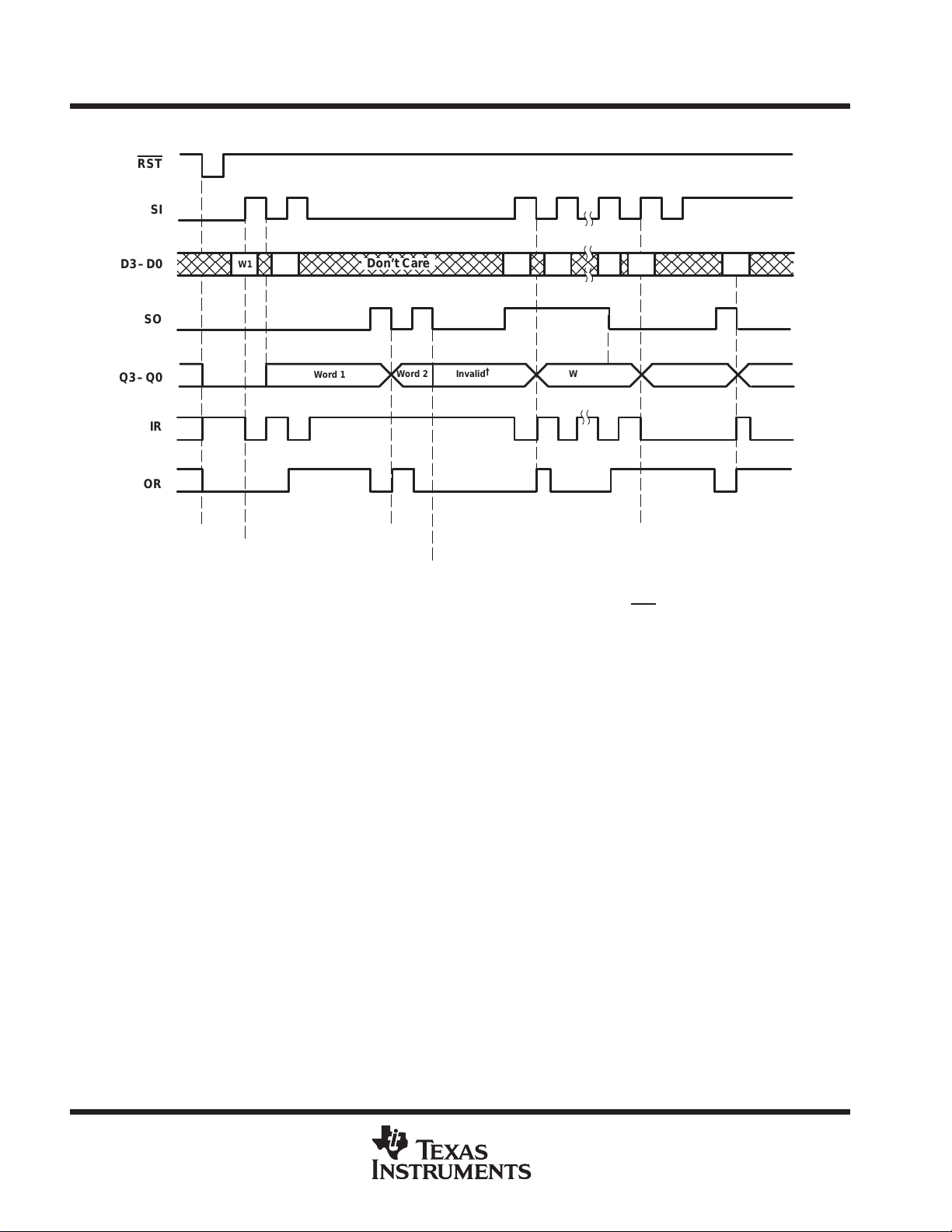

timing diagram

RST

SI

W1

D3–D0

SO

Q3–Q0

IR

OR

Clear

Shift In

†

The last data word shifted out of the FIFO remains at the output until a new word falls through or an RST pulse clears the FIFO.

‡

While the output data is considered valid only when the OR flag is high, the stored data remains at the outputs. Any additional words written

into the FIFO stack up behind the first word and do not appear at the output until SO is taken low.

W2 W1 W2 W63 W64 W1

Word 1

W1

Don’t Care

Word 2 Invalid

Shift Out

W2

Empty

†

Word 1

‡

Word 2 Word 3

Full

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...