Texas Instruments SN74AHCT16541DGGR, SN74AHCT16541DGVR, SN74AHCT16541DL, SN74AHCT16541DLR Datasheet

SN54AHCT16541, SN74AHCT16541

16-BIT BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCLS339H – MARCH 1996 – REVISED JANUARY 2000

D

Members of the Texas Instruments

D

Widebus

EPIC

Family

(Enhanced-Performance Implanted

CMOS) Process

D

Inputs Are TTL-Voltage Compatible

D

Distributed VCC and GND Pins Minimize

High-Speed Switching Noise

D

Flow-Through Architecture Optimizes PCB

Layout

D

Latch-Up Performance Exceeds 250 mA Per

JESD 17

D

Package Options Include Plastic Shrink

Small-Outline (DL), Thin Shrink

Small-Outline (DGG), and Thin Very

Small-Outline (DGV) Packages and 380-mil

Fine-Pitch Ceramic Flat (WD) Package

Using 25-mil Center-to-Center Spacings

description

The ’AHCT16541 devices are noninverting 16-bit

buffers composed of two 8-bit sections with

separate output-enable signals. For either 8-bit

buffer section, the two output-enable (1OE1 and

1OE2

or 2OE1 and 2OE2) inputs must both be low

for the corresponding Y outputs to be active. If

either output-enable input is high, the outputs of

that 8-bit buffer section are in the high-impedance

state.

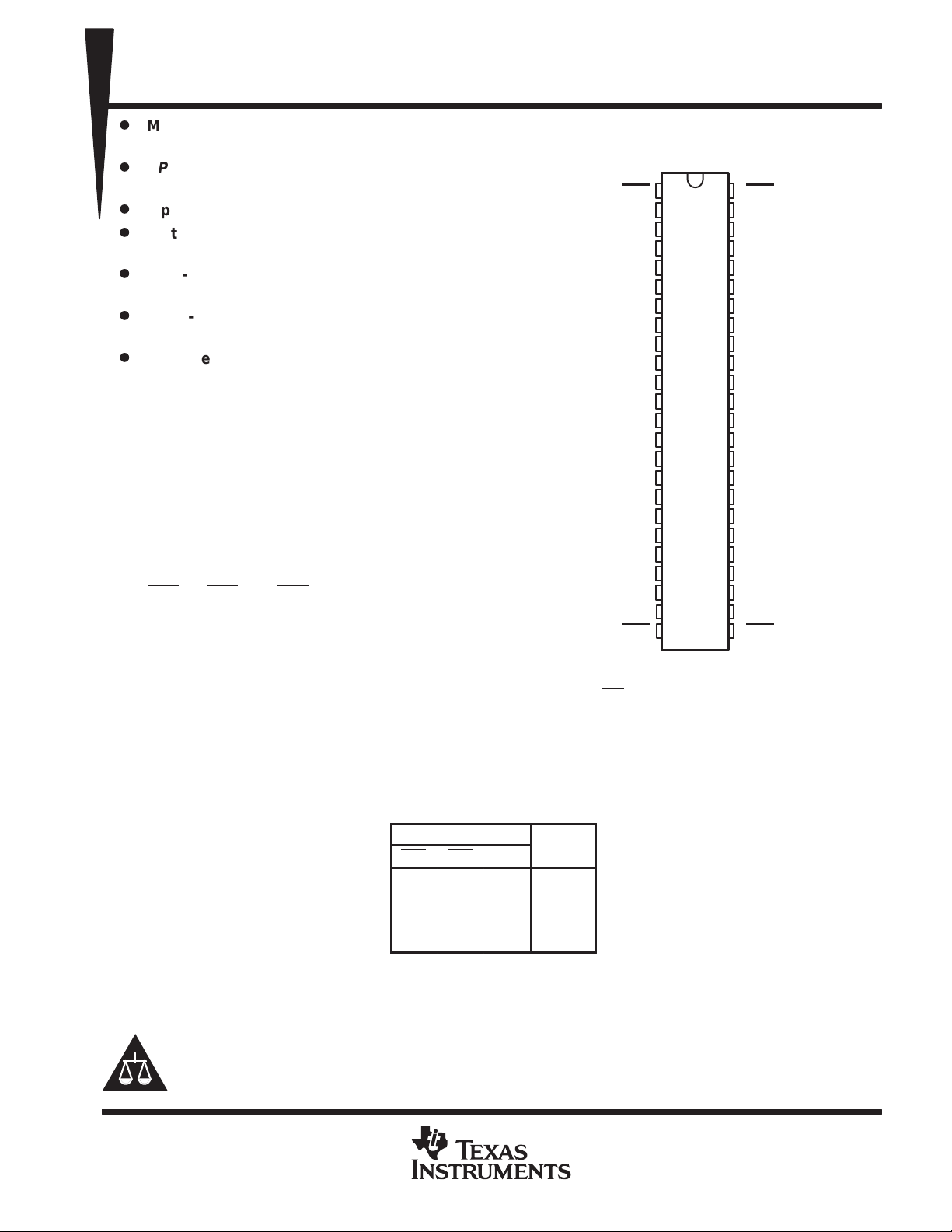

SN54AHCT16541 . . . WD PACKAGE

SN74AHCT16541 . . . DGG, DGV, OR DL PACKAGE

1OE1

1Y1

1Y2

GND

1Y3

1Y4

V

CC

1Y5

1Y6

GND

1Y7

1Y8

2Y1

2Y2

GND

2Y3

2Y4

V

CC

2Y5

2Y6

GND

2Y7

2Y8

2OE1

(TOP VIEW)

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25

1OE2

1A1

1A2

GND

1A3

1A4

V

CC

1A5

1A6

GND

1A7

1A8

2A1

2A2

GND

2A3

2A4

V

CC

2A5

2A6

GND

2A7

2A8

2OE2

T o ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN54AHCT16541 is characterized for operation over the full military temperature range of –55°C to 125°C.

The SN74AHCT16541 is characterized for operation from –40°C to 85°C.

FUNCTION TABLE

(each 8-bit buffer/driver)

INPUTS

OE2 A

OE1

L L L L

L LH H

H XX Z

X H X Z

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC and Widebus are trademarks of Texas Instruments Incorporated.

UNLESS OTHERWISE NOTED this document contains PRODUCTION

DATA information current as of publication date. Products conform to

specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all

parameters.

OUTPUT

Y

Copyright 2000, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

1

SN54AHCT16541, SN74AHCT16541

16-BIT BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCLS339H – MARCH 1996 – REVISED JANUARY 2000

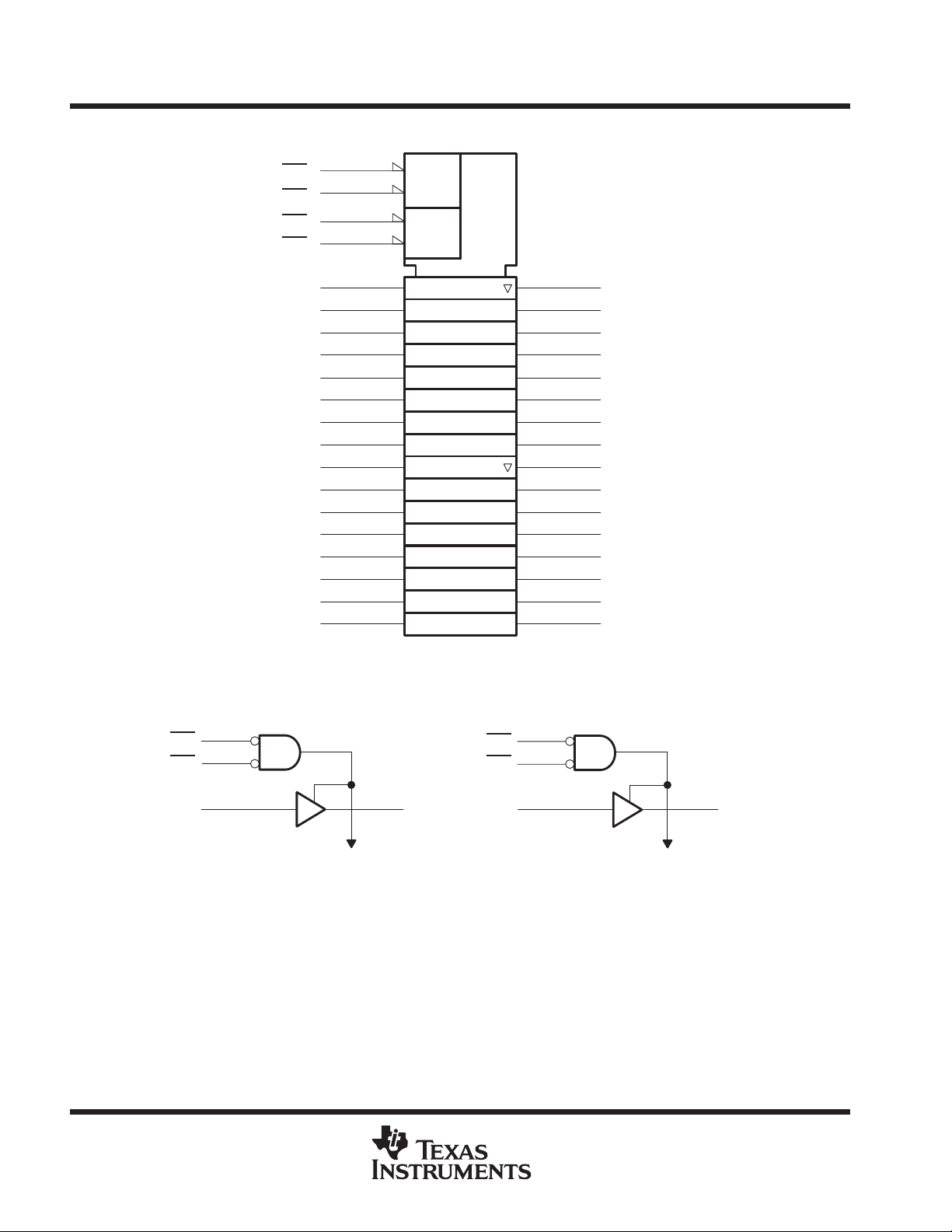

logic symbol

†

1OE1

1OE2

2OE1

2OE2

1

48

24

25

47

1A1 1Y1

46

1A2

44

1A3 1Y3

43

1A4 1Y4

41

1A5 1Y5

40

1A6 1Y6

38

1A7 1Y7

37

1A8 1Y8

36

2A1 2Y1

35

2A2

33

2A3 2Y3

32

2A4 2Y4

30

2A5 2Y5

29

2A6 2Y6

27

2A7

26

2A8 2Y8

&

&

EN1

EN2

111

2

3

1Y2

5

6

8

9

11

12

2

13

14

16

17

19

20

22

23

2Y2

2Y7

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

logic diagram (positive logic)

1

1OE1

48

1OE2

47

1A1 1Y1

To Seven Other Channels To Seven Other Channels

2

2OE1

2OE2

2A1

24

25

36

13

2Y1

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...