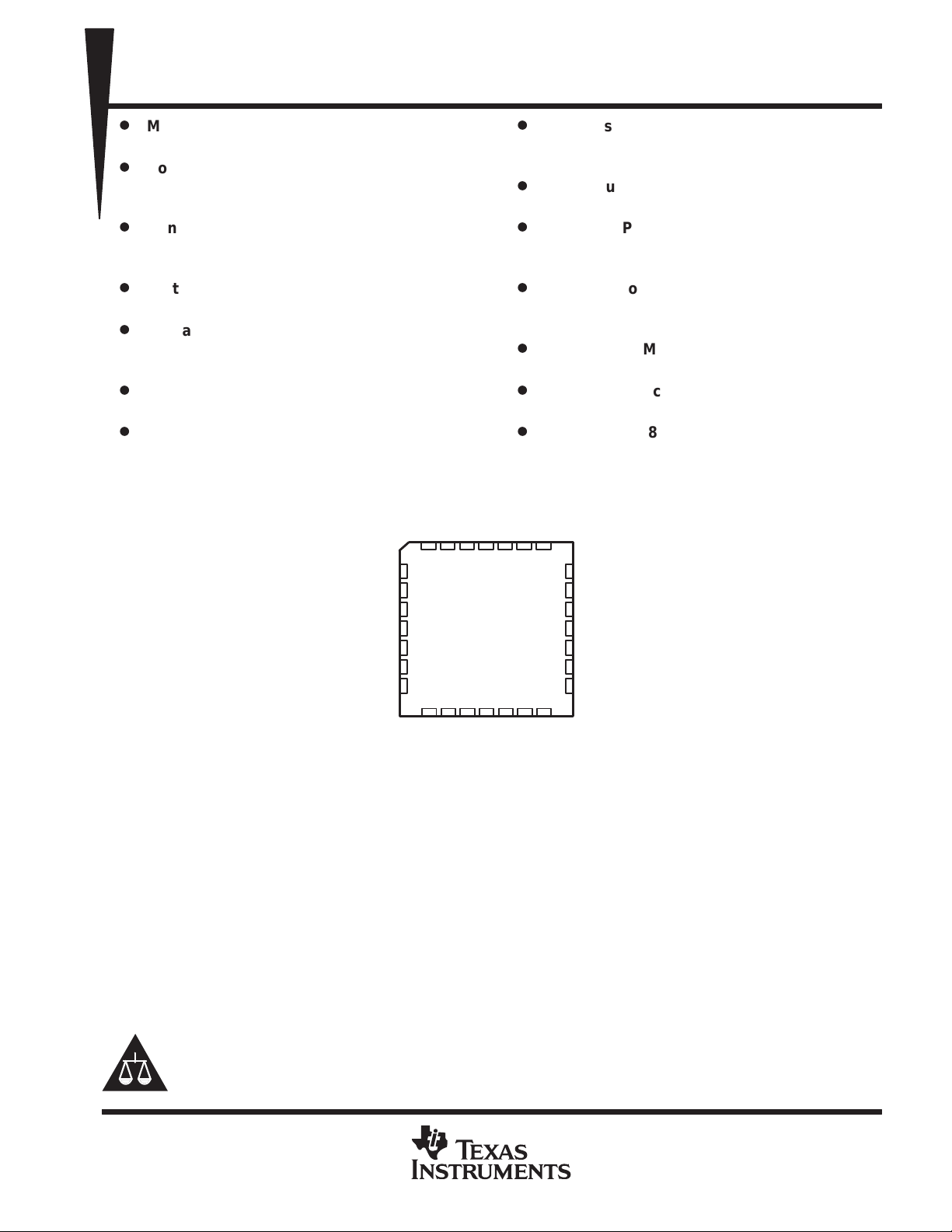

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

D

Member of the Texas Instruments

Family of Testability Products

D

Compatible With the IEEE Standard

1149.1-1990 (JTAG) Test Access Port and

Boundary-Scan Architecture

D

Contains a 1024-Word by 16-Bit

Random-Access Memory (RAM) to Store

the States of a Digital Bus

D

Test Operations Are Synchronous to the

Test Clock or System Clock(s)

D

Contains T exas Instruments Event

Qualification Module for Real-Time System

Test

D

Eight Protocols for On-Line Signal

Monitoring and Test Operations

D

Inputs Are TTL-Voltage Compatible

SCOPE

D

D

D

D

D

D

D

FN PACKAGE

(TOP VIEW)

SN74ACT8994

DIGITAL BUS MONITOR

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

Performs Parallel-Signature Analysis (PSA)

of Data Inputs With User-Definable

Feedback

Data Inputs Are Maskable During PSA

Operations

Cascaded PSA Mode Allows Compression

of Parallel Data Paths Greater Than 16 Bits

in Width

Direct Memory Access (DMA) Speeds

Memory and Register File Read/Write

Operations

Power-Down Mode When RAM Is Idling

Reduces Power Dissipation

EPIC

(Enhanced-Performance Implanted

CMOS) 1-µm Process

Packaged in 28-Pin Plastic Chip Carriers

GND

EQO

CC

PIO

EQI

25

24

23

22

21

20

19

D15

D8

D9

D10

D11

D12

D13

D14

D1

D0

CLK1

CLK2

CLK3

TMS

TCK

D2D3D4D5VD6D7

3212827

426

5

6

7

8

9

10

11

12 13 14 15 16 1718

TDI

TDO

description

The SN74ACT8994 digital bus monitor (DBM) is a member of the Texas Instruments SCOPE testability

integrated-circuit family. This family of components supports IEEE Standard 1149.1-1990 (JTAG) boundary

scan to facilitate testing of complex circuit-board assemblies. The DBM is a boundary-scannable device

designed to monitor and/or store the values of a digital bus up to 16 bits in width. It resides in parallel with the

bus being monitored.

Data at the D-input pins can be stored in a scannable random-access memory (RAM). Up to 1024 words of

16 bits can be stored. A parallel-signature analysis (PSA) can be performed on the data or on the contents of

memory . The PSA operations use a linear-feedback shift-register technique to compress data into a signature.

The user can configure the device to mask any combination of data inputs and control the feedback used during

PSA operations.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCOPE and EPIC are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1996, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

1

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

description (continued)

The DBM receives instructions via the IEEE Standard 1 149.1-1990 test access port (TAP) interface. The TAP

interface consists of test clock (TCK), test mode select (TMS), test data input (TDI), and test data output (TDO)

pins.

The DBM can be operated in the off-line mode or the on-line mode. In the off-line mode, the device performs

test operations independent of system conditions. Off-line test operations include parallel-signature analysis

(PSA) on the contents of RAM and external test.

In the on-line mode, the DBM can be configured to perform test operations that are initiated based on system

conditions and that operate synchronously to a logical combination of one or more system clocks. The device

allows sample, storage, and/or PSA operations to be performed according to one of eight protocols. Compare

patterns, which can be stored in the event-qualification module (EQM), allow the user to define specific values

of the 16-bit bus for which the test operations are to be performed.

The 1024-word by 16-bit RAM and the EQM register files can be serially accessed using

IEEE-Standard-1149.1-1990-compatible read and write instructions. However, direct memory access (DMA)

instructions also are provided to speed transfer of large amounts of data to and from the RAM and EQM.

The polynomial input/output (PIO) is a bidirectional pin used to cascade more than one DBM to provide

signature analysis on a bus larger than 16 bits.

The SN74ACT8994 is characterized for operation from 0°C to 70°C.

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

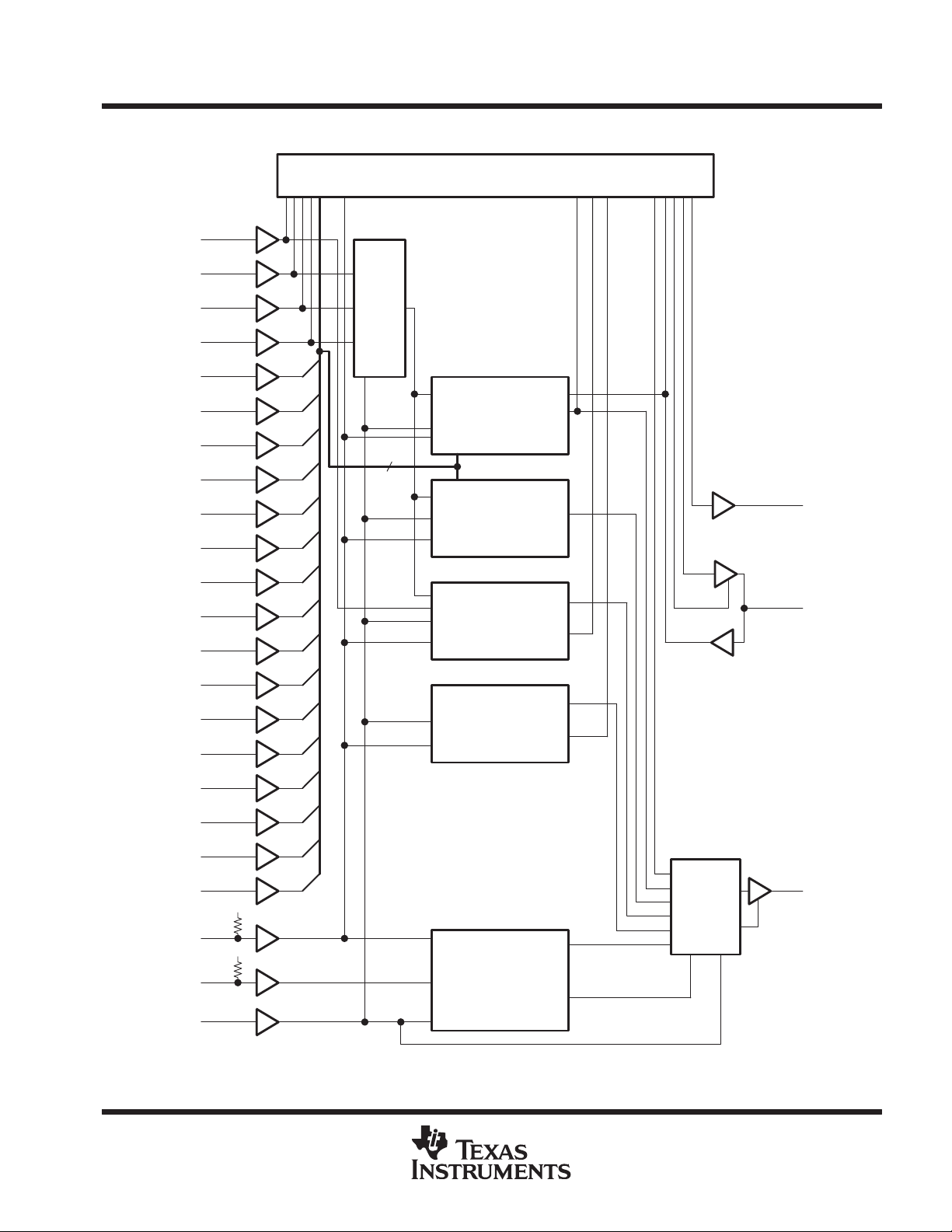

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

functional block diagram

17

EQI

7

CLK1

8

CLK2

9

CLK3

6

D0

5

D1

4

D2

3

D3

2

D4

1

D5

Boundary-Scan Register

PCI

Test-Cell Register

16

RAM

SN74ACT8994

DIGITAL BUS MONITOR

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

15

EQO

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

TDI

TMS

TCK

27

16

13

PIO

TDO

26

25

24

23

22

21

20

19

18

V

CC

12

V

CC

10

11

EQM

Control/

Bypass/

Header Registers

TDO

MUX

TAP Controller/

Instruction Register

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

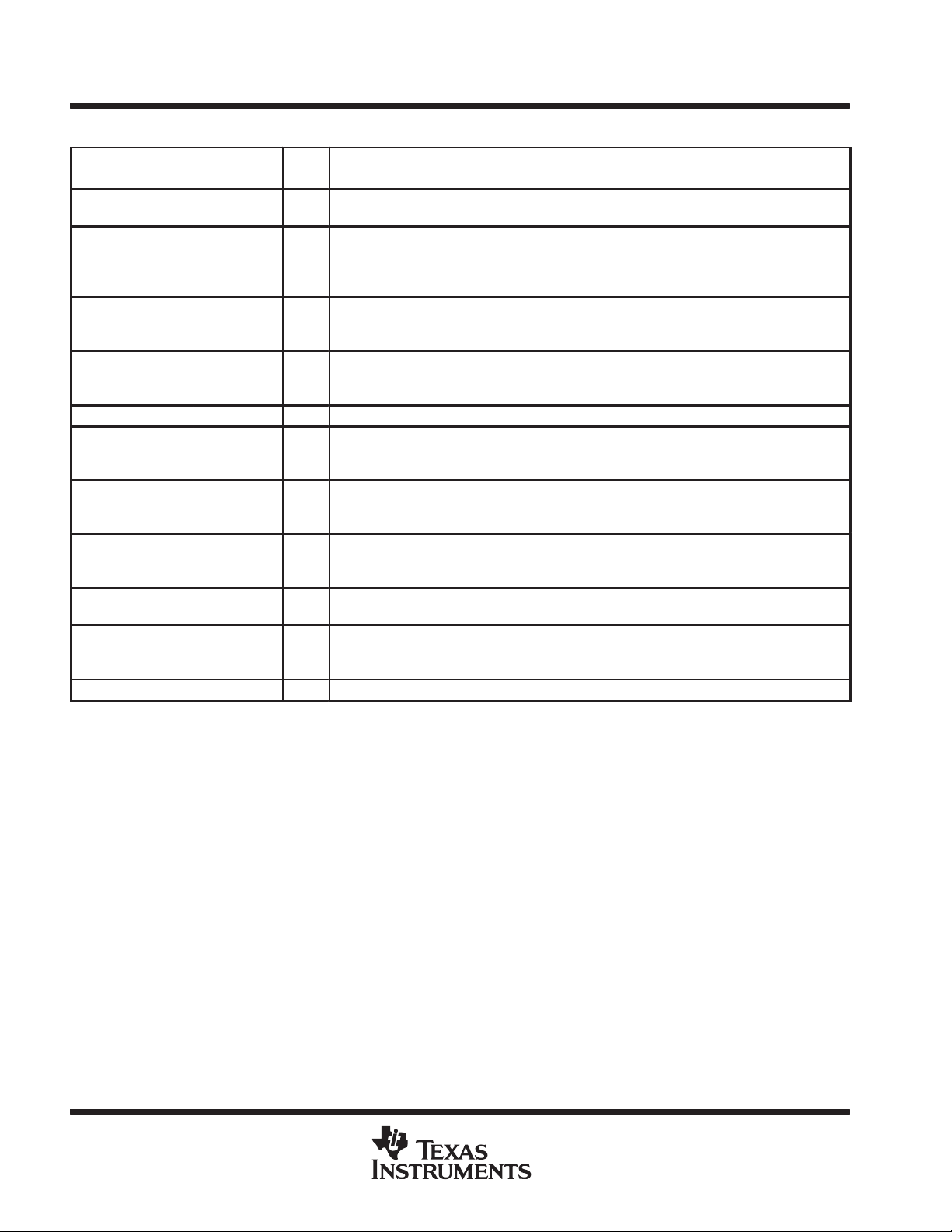

SN74ACT8994

I/O

DESCRIPTION

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

Terminal Functions

TERMINAL

NAME NO.

CLK1, CLK2, CLK3 7, 8, 9 I

D0, D1, D2, D3, D4,

D5, D6, D7, D8, D9,

D10, D11, D12,

D13, D14, D15

EQI 17 I

EQO 15 O

GND 14 Ground

PIO 16 I/O

TCK 11 I

TDI 12 I

TDO 13 O

TMS 10 I

V

CC

6, 5, 4, 3, 2,

1, 27, 26, 25

24, 23, 22,

21, 20, 19, 18

28 Supply voltage

Clock 1, 2, and 3. CLK1–CLK3 provide various types of system clock and control signals to the

DBM for the purpose of synchronizing test operations to the system under test.

Data bus inputs. D15–D0 form the 16-bit digital bus that is monitored by the DBM. Data that

appears at this bus can be compressed into a 16-bit signature and/or stored in the 1024-word

I

RAM. Each data bit can be individually masked during test operations.

Event-qualification input. EQI is used to receive an external (global) event signal from

user-defined event-qualification logic. EQI can be configured to initiate test operations in the

on-line mode.

Event-qualification output. EQO is used to transmit any of several internally generated status

signals. EQO can be configured to transmit internal (local) event signals to external (global)

event-qualification logic.

Polynominal input/output. PIO is used to cascade more than one DBM to provide signature

analysis on a bus larger than 16 bits. Its configuration as an input or output for a particular DBM

device depends on the significance (most, middle, or least) of that DBM in the scan path.

Test clock. One of four pins required by IEEE Standard 1149.1-1990. Scan operations of the

DBM are synchronous to TCK. Data is captured on the rising edge of TCK, and outputs change

on the falling edge of TCK.

T est data input. One of four pins required by IEEE Standard 1 149.1-1990. TDI is the serial input

for shifting data through the instruction register or selected data register. An internal pullup

forces TDI to a high level if left unconnected.

Test data output. One of four pins required by IEEE Standard 1149.1-1990. TDO is the serial

output for shifting data through the instruction register or selected data register.

Test mode select. One of four pins required by IEEE standard 1149.1-1990. TMS directs the

DBM through its TAP controller states. An internal pullup forces TMS to a high level if left

unconnected.

detailed description

The general architecture of the DBM is shown in the functional block diagram. The DBM contains eight data

registers and an instruction register that are accessed serially through the TAP. The TAP controller is a

finite-state machine that issues control and enable signals throughout the device, based on its current state.

The instruction register (IR) provides additional control signals that are specific to the current instruction. Test

data is transmitted serially from TDI through the scan path to TDO. The IR or one of the eight data registers is

always selected in the scan path by the TAP control signals issued to the TDO multiplexer.

The 1024-word RAM can be used to store data from the bus being monitored during test operations. The RAM

is accessed via the TAP interface when the RAM register (RAMR) is selected in the scan path.

The event-qualification module (EQM) contains two data registers that contain configuration, compare, and

mask data associated with on-line test operations. The EQM also contains the state machines for the eight

protocols that include various start/stop, start/pause/resume, and do-while algorithms. These protocols

operate synchronously to the clock signal generated by the programmable clock interface (PCI). The PCI

generates a clock signal from one of 32 different logical combinations of CLK1, CLK2, CLK3, and TCK. The user

configures the PCI through the control register (CTLR).

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

detailed description (continued)

The test-cell register (TCR) is a data register that performs PSA operations on the data bus or on the contents

of RAM. During PSA operations, the TCR is a linear-feedback shift register. The CTLR configures the data

masking and controls the feedback for PSA operations. The boundary-scan register (BSR), header register

(HR), and bypass register (BR) are data registers that can be serially accessed through the TAP interface.

instruction register

The 8-bit instruction register (IR) contains the DBM current instruction, which controls all operations of the

device. When the IR is placed in the scan path, the IR status word is loaded into the IR and shifted out on TDO

when the new instruction is shifted in.

The IR status word contains four status bits. The IRERR

exhibit even parity is loaded into the IR. The OVF status bit is asserted when the RAM address counter is

incremented past its maximum value of 3FFh (register value given in hexadecimal format, indicated by the letter

h following the value). The RUN and EOT status bits pertain to on-line testing and are asserted when a protocol

is active (RUN) or the end of the protocol is reached (EOT).

boundary-scan register

The boundary-scan register (BSR) is a 24-bit register that includes one boundary-scan cell (BSC) for each of

the non-JT AG input and output pins of the device, two BSCs for PIO (one for input data and one for output data),

and one BSC for the PIO direction signal. The BSR is used to capture the data appearing at the device periphery

and to apply test data to the device outputs.

bypass register

The bypass register (BR) is a 1-bit register required by IEEE Standard 1 149.1-1990. It provides an abbreviated

scan path through the DBM when the current test operations do not require it to access one of the other data

registers.

control register

The 45-bit control register (CTLR) issues configuration, control, and enable signals to the device. Data shifted

into the CTLR configures the data mask and feedback for PSA operations. It also configures the programmable

clock interface and selects the test operations to be performed (see test operations).

event-qualification register 1

Event-qualification register 1 (EQR1) is a 32-bit register that configures the DBM for on-line testing

(event-qualified testing). Data shifted into EQR1 selects and controls one of eight event-qualification protocols

and configures the event and status signals. The event signal triggers test operations according to the protocol

being executed. The status signal is output via EQO. EQR1 also contains the loop counter, which controls the

number of times an event-qualification protocol is executed.

status bit is asserted when an opcode that does not

event-qualification register 2

Event-qualification register 2 (EQR2) is used to load the event counter, expected data, and mask data

(16-word-deep register files) for event-qualified tests. Depending on the current instruction, it is either 48 or 56

bits in length and can be thought of as three 16-bit data segments and two 4-bit address segments. One 4-bit

address segment addresses the event counter, while the other 4-bit address segment addresses the expected

data and mask data.

The register files can be accessed using IEEE-Standard-1149.1-1990-compatible instructions or DMA

instructions. When using IEEE-Standard-1 149.1-1990-compatible instructions, EQR2 is configured as a 56-bit

register. The data appearing in the 16-bit data segments is loaded into or out of the addresses specified by the

register’s two 4-bit address segments.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

event-qualification register 2 (continued)

During execution of the DMA instructions, EQR2 is configured as a 48-bit register containing only the three

16-bit data segments. Using DMA instructions allows a continuous stream of data to be loaded or unloaded from

the register files. After each 48th bit of the data stream has been shifted to or from the register files, the register

file addresses are automatically incremented and the first data bit of the next address is shifted.

header register

The header register (HR) is an 8-bit register that initiates DMA write operations on the RAM and on the EQR2

register files. When a DMA write instruction is active, the data being shifted from TDI to TDO is compared against

the current value of the HR and the DMA write operation begins after a match is found. When the value of the

HR is set to 00h, DMA write operations can only be initiated by the T AP and are not initiated by the TDI-to-TDO

data flow.

random-access memory register

The random-access memory register (RAMR) is used to access the 1024-word RAM. Depending on the current

instruction, it is either 16 bits or 26 bits in length and can be thought of as a 16-bit data segment and a 10-bit

address segment.

The RAMR can be accessed using IEEE-Standard-1 149.1-1990-compatible instructions or DMA instructions.

When using the IEEE-Standard-1 149.1-1990-compatible instructions, RAMR is configured as a 26-bit register.

The data appearing in the 16-bit data segment is loaded into or out of the address specified by the register’s

10-bit address.

During execution of the DMA instructions, RAMR is configured as a 16-bit register containing only the 16-bit

data segment. Using DMA instructions allows a continuous stream of data to be loaded or unloaded from the

register. After each 16th bit of the data stream has been shifted to or from the register, the address is

automatically incremented and the first data bit of the next address is shifted.

test-cell register

The test-cell register (TCR) is a 16-bit register. It can perform PSA operations on the data inputs or on the

contents of RAM. The resulting signature can be scanned out and compared against an expected value. The

TCR is also used during test operations to capture the current value of the data bus.

test operations

The primary function of the DBM is to perform test operations while monitoring a digital bus. The test operations

can be initiated by system conditions (on-line mode) or independent of system conditions (off-line mode). The

description of each of the system test operations follows.

sample

The data at the D inputs is captured in the test-cell register and can be shifted out via TDO for inspection.

parallel-signature analysis

A parallel-signature analysis (PSA) is performed on the data appearing at the D inputs. The test-cell register

is configured as a linear-feedback shift register that compresses the data into a signature. The user can

configure the device to mask data bits from PSA operations and control the feedback of the linear-feedback shift

register. When an input is masked, it is ignored and has no effect on the generated signature.

trace

The data at the D inputs is stored in the RAM. The RAM address is automatically incremented after each write

cycle. The device can be configured to clear the RAM address to 000h at the beginning of test execution. It also

can be configured to allow write cycles to continue after the maximum address 3FFh is reached (thus clearing

the address to 000h and overwriting data).

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IOHHigh-level output current

mA

IOLLow-level output current

mA

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

trace/PSA

The trace and PSA operations are executed simultaneously . All the configuration options for the trace and PSA

operations are available for trace/PSA.

In the off-line mode, system test operations are performed via the T AP controller. This is done independent of

system conditions.

In the on-line mode, the device is configured to perform system test operations that are dependent on system

conditions (event-qualified testing) and synchronous to the system clock(s). Eight different event-qualification

protocols offer a wide range of test schemes that control when system test operations take place.

An event can be configured as a match between expected data from the register files and data at the D inputs

(local event-qualified testing). Mask data bits from the register files allow any combination of bits to be ignored

when the compare takes place. The EQI pin can also be configured as an event to trigger system test operations

(global event-qualified testing). The device can be configured to output one of several different status signals

via EQO. These are used for global event-qualified testing.

The DBM has instructions that enable the user to perform a self-test on the RAM. This is done by filling the RAM

with known values and performing a PSA on its contents. Instructions are included to expedite the loading of

the RAM with known values, as well as to perform PSA on the contents of the RAM.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1) –0.5 V to V

Output voltage range, VO (see Note 1) –0.5 V to V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, IIK (VI < 0 or VI > VCC) ±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, IOK (VO < 0 or V

Continuous output current, I

Maximum power dissipation at T

Storage temperature range, T

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 75 mils.

For more information, refer to the

Book

, literature number SCBD002.

(VO = 0 to VCC) ±25 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

= 55°C (in still air) (see Note 2) 1.1 W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

Package Thermal Considerations

> VCC) ±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

application note in the

ABT Advanced BiCMOS T echnology Data

recommended operating conditions

MIN MAX UNIT

V

CC

V

IH

V

IL

V

I

V

O

T

A

Supply voltage 4.5 5.5 V

High-level input voltage 2 V

Low-level input voltage 0.8 V

Input voltage 0 V

Output voltage 0 V

p

p

Operating free-air temperature 0 70 °C

EQO –4

PIO, TDO –16

EQO 4

PIO, TDO 16

CC

CC

V

V

†

CC

CC

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

SN74ACT8994

V

V

EQO

V

5.5 V

V

V

V

V

PIO, TDO

V

V

EQO

V

4.5 V to 5.5 V

V

V

PIO, TDO

V

V

I

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

electrical characteristics over recommended operating free-air temperature range

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

= 4.5

CC

=

CC

OH

= 4.5

CC

= 5.5

CC

=

CC

OL

= 4.5 V to 5.5

CC

CLK, D, EQI, TCK VCC = 5.5 V, VI = VCC or GND ±1

I

I

I

OZ

CC

∆I

C

C

C

* On products compliant to MIL-PRF-38535, this parameter does not apply.

†

Typical values are at VCC = 5 V, TA = 25_C.

‡

For I/O pins, the parameter IOZ includes the input-leakage current.

CC

i

io

o

TDI, TMS VCC = 5.5 V, VI = V

TDI, TMS VCC = 5.5 V, VI = GND –0.1 –20

‡

PIO, TDO VCC = 5.5 V, VO = VCC or GND ±5 µA

RAM disabled VCC = 5.5 V, VI = VCC or GND, IO = 0 200 µA

RAM enabled VCC = 5.5 V, VI = VCC or GND, IO = 0 200 mA

VCC = 5.5 V, One input at 3.4 V,

Other inputs at VCC or GND

VI = VCC or GND 4

VO = VCC or GND 7

VO = VCC or GND 6

IOH = –3 mA

IOH = –4 mA 3.7

IOH = –3 mA

IOH = –4 mA 4.7

IOH = –11 mA

IOH = –16 mA 3.7

IOH = –11 mA

IOH = –16 mA 4.7

IOL = 3 mA

IOL = 4 mA 0.5

IOL = 11 mA

IOL = 16 mA 0.5

CC

µA

±1

1 mA

*

*

*

pF

pF

pF

timing requirements over recommended ranges of supply voltage and operating free-air

temperature (see Figure1)

MIN MAX UNIT

Any CLK (except during PSARAM instruction)

f

clock

t

w

t

su

t

h

t

d

§

The PSARAM instruction performs a parallel-signature analysis on the contents of RAM. This instruction is provided to allow self-test of the RAM.

Clock frequency

Pulse duration Any CLK or TCK high or low 7 ns

Setup time

Hold time

Delay time Power up to TCK↑ 100 ns

TCK (except during PSARAM instruction)

Any CLK or TCK (during PSARAM instruction)

TDI before TCK↑ 2

TMS before TCK↑ 4

Any D before any CLK or TCK

EQI before any CLK or TCK 4

PIO before any CLK or TCK 1

TDI after TCK↑ 5

TMS after TCK↑ 3

Any D after any CLK or TCK

EQI after any CLK or TCK 2

PIO after any CLK or TCK 5

§

§

§

0 50

0 50

0 17

5

3

MHz

ns

ns

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Any CLK

EQO

ns

Any CLK

PIO

ns

Any CLK

TDO

ns

Any D

EQO

ns

TCK↓

EQO

ns

TCK↓

PIO

ns

TCK↓

TDO

ns

TCK↓

PIO

ns

TCK↓

TDO

ns

TCK↓

PIO

ns

TCK↓

TDO

ns

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature (see Figure 1)

PARAMETER

Any CLK (except during PSARAM instruction)

f

max

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PZH

t

PZL

t

PZH

t

PZL

t

PHZ

t

PLZ

t

PHZ

t

†

The PSARAM instruction performs a parallel-signature analysis on the contents of RAM. This instruction is provided to allow self test of the RAM.

PLZ

TCK (except during PSARAM instruction)

Any CLK or TCK (during PSARAM instruction)

FROM

(INPUT)

†

†

†

TO

(OUTPUT)

MIN MAX UNIT

50

50

17

7 18

7 17

9 22

9 22

9 20

8 19

5 17

4 15

5 16

5 15

8 19

8 19

3 12

3 11

5 18

5 18

3 11

2 10

6 16

5 15

9 16

8 15

MHz

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9

SN74ACT8994

DIGITAL BUS MONITOR

IEEE STD 1149.1 (JTAG) SCAN-CONTROLLED LOGIC/SIGNATURE ANALYZER

SCAS196E – JULY 1990 – REVISED DECEMBER 1996

PARAMETER MEASUREMENT INFORMATION

V

From Output

Under Test

Timing Input

CL = 50 pF

(see Note A)

1 kΩ

LOAD CIRCUIT

1.5 V

S1

CC

Open

GND

3 V

0 V

Input

1.5 V 1.5 V

TEST S1

t

PLH/tPHL

t

PLZ/tPZL

t

PHZ/tPZH

t

VOLTAGE WAVEFORMS

PULSE DURATION

Open

V

GND

w

CC

3 V

0 V

50% V

CC

t

h

t

su

Data Input

Input

t

PLH

Output

PROPAGATION DELAY TIMES

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω, tr ≤ 3 ns, tf≤ 3 ns.

For testing pulse duration: tr = tf = 1 to 3 ns. Pulse polarity can be either high-to-low-to-high or low-to-high-to-low.

D. The outputs are measured one at a time with one transition per measurement.

1.5 V 1.5 V

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

1.5 V 1.5 V

VOLTAGE WAVEFORMS

t

PHL

50% V

3 V

0 V

3 V

0 V

V

CC

V

OH

OL

Output

Control

(low-level

enabling)

Output

Waveform 1

S1 at V

(see Note B)

Waveform 2

(see Note B)

CC

Output

S1 at GND

t

PZL

t

PZH

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

t

PLZ

50% V

t

PHZ

50% V

CC

CC

1.5 V1.5 V

10% V

90% V

CC

CC

3 V

0 V

≈ V

V

OL

V

OH

≈ 0 V

CC

10

Figure 1. Load Circuit and Voltage Waveforms

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICA TIONS USING SEMICONDUCT OR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...