SN54ABT18652, SN74ABT18652

SCAN TEST DEVICES WITH

18-BIT BUS TRANSCEIVERS AND REGISTERS

SCBS132A – AUGUST 1992 – REVISED OCTOBER 1992

• Members of the Texas Instruments

SCOPE

Family of Testability Products

• Members of the Texas Instruments

Widebus

Family

• Compatible With the IEEE Standard

1149.1-1990 (JTAG) Test Access Port and

Boundary-Scan Architecture

• Include D-Type Flip-Flops and Control

Circuitry to Provide Multiplexed

Transmission of Stored and Real-Time Data

• Two Boundary-Scan Cells per I/O for

Greater Flexibility

• State-of-the-Art

Significantly Reduces Power Dissipation

EPIC-ΙΙB

1A3

1A4

1A5

GND

1A6

1A7

1A8

1A9

NC

V

CC

2A1

2A2

2A3

GND

2A4

2A5

2A6

BiCMOS Design

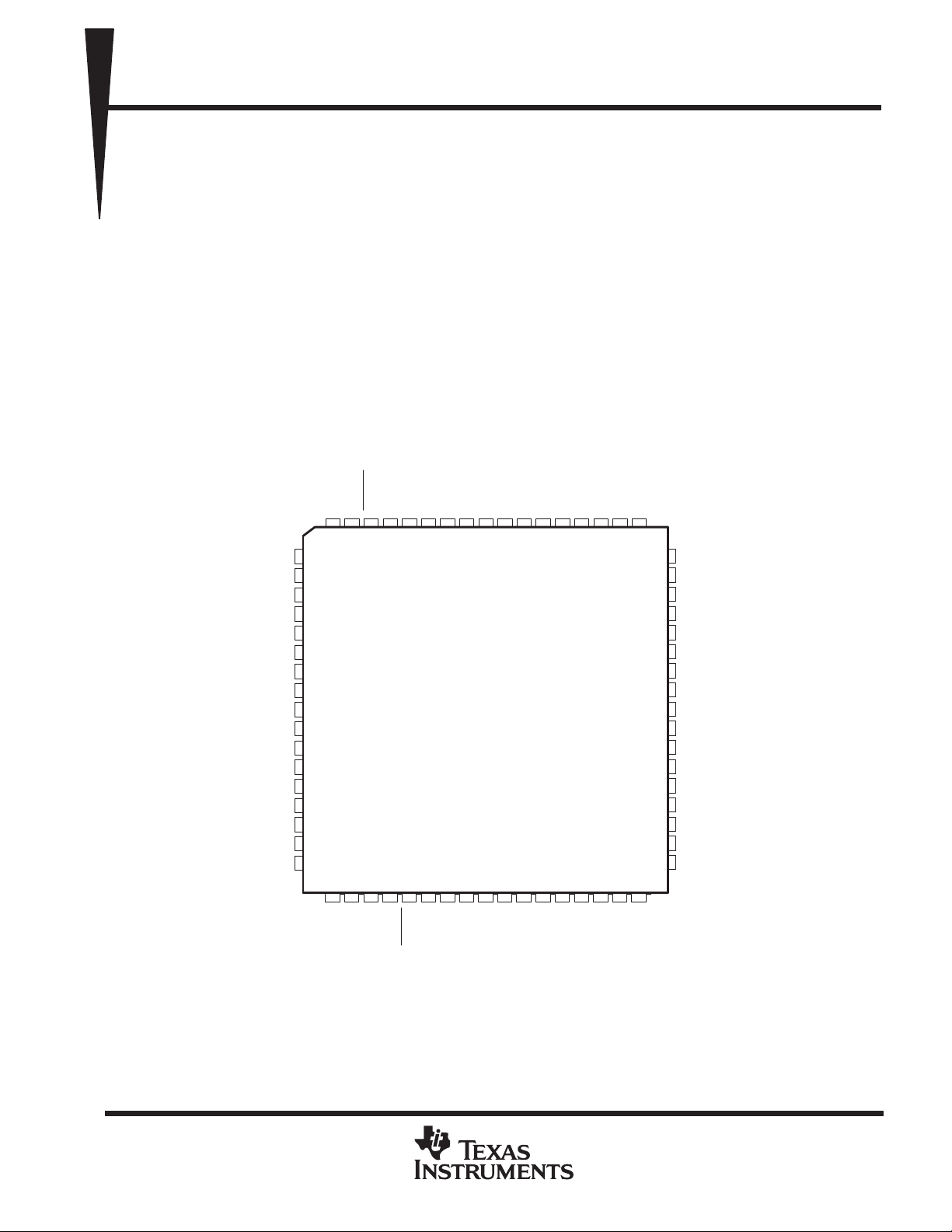

SN54ABT18652 . . . HV PACKAGE

1A2

1A1

1OEBA

GND

67 66 65 64 6368 62 60 59 5861

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

19 20

21

22 23 24 25

1SAB

(TOP VIEW)

VNCTMS

1CLKAB

TDO

•

• Packaged in 64-Pin Plastic Shrink Quad Flat

CC

26 27 28 29 30

1SBA

1CLKBA

57 561855 54 53 52

SCOPE

Instruction Set

– IEEE Standard 1149.1-1990 Required

Instructions, Optional INTEST, and

P1149.1A CLAMP and HIGHZ

– Parallel Signature Analysis at Inputs With

Masking Option

– Pseudo-Random Pattern Generation

From Outputs

– Sample Inputs/Toggle Outputs

– Binary Count From Outputs

– Device Identification

– Even-Parity Opcodes

Pack (PM) and 68-Pin Ceramic Quad Flat

Pack (HV)

1OEAB

GND

1B1

1B2

1B3

1B4

51

1B5

50

1B6

49

GND

48

1B7

47

1B8

46

1B9

45

V

44

CC

NC

43

2B1

42

2B2

41

2B3

40

2B4

39

GND

38

2B5

37

2B6

36

2B7

35

31 32 33 34

PRODUCT PREVIEW

2A7

NC – No internal connection

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

CC

NC

2A8

2A9

GND

2OEBA

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2SAB

2CLKAB

TDI

V

TCK

2CLKBA

GND

2SBA

2B9

2B8

2OEAB

Copyright 1992, Texas Instruments Incorporated

1

SN54ABT18652, SN74ABT18652

SCAN TEST DEVICES WITH

18-BIT BUS TRANSCEIVERS AND REGISTERS

SCBS132A – AUGUST 1992 – REVISED OCTOBER 1992

1A3

1A4

1A5

GND

1A6

1A7

1A8

1A9

V

CC

2A1

2A2

PRODUCT PREVIEW

2A3

GND

2A4

2A5

2A6

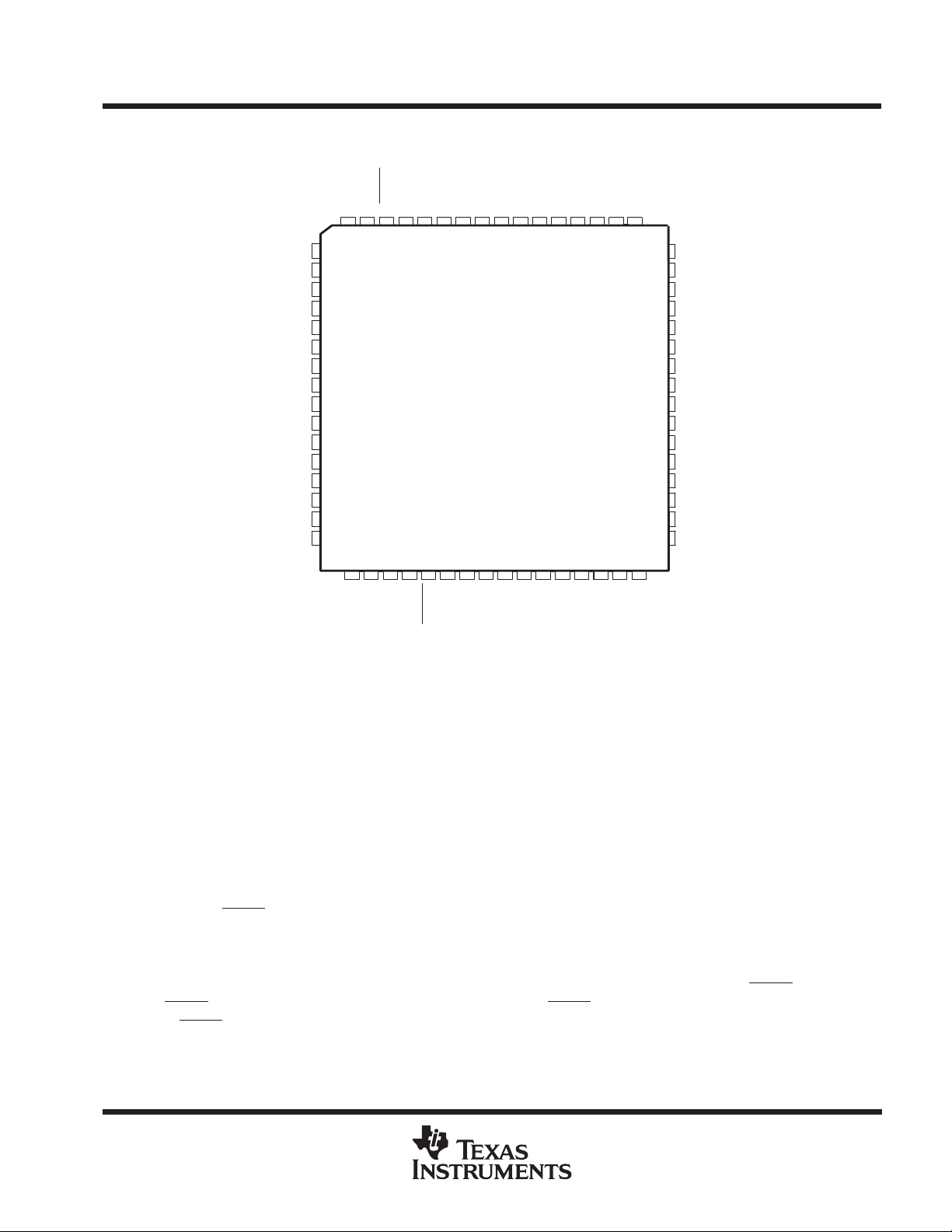

SN74ABT18652 ...PM PACKAGE

1OEBA

1A2

1A1

63 62 61 60 5964 58 56 55 5457

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18 19

GND

1SAB

21 22 23 24

20

(TOP VIEW)

CC

1CLKAB

TDO

V

1SBA

TMS

25 26 27 28 29

1OEAB

1CLKBA

53 521751 50 49

1B1

GND

30 31 32

1B2

1B3

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1B4

1B5

1B6

GND

1B7

1B8

1B9

V

CC

2B1

2B2

2B3

2B4

GND

2B5

2B6

2B7

CC

2A7

2A8

2A9

GND

2OEAB

2SAB

2CLKAB

TDI

V

TCK

2CLKBA

GND

2SBA

2B9

2OEAB

2B8

description

The SN54ABT18652 and SN74ABT18652 scan test devices with 18-bit bus transceivers and registers are

members of the T exas Instruments SCOPE testability IC family . This family of devices supports IEEE Standard

1149.1-1990 boundary scan to facilitate testing of complex circuit board assemblies. Scan access to the test

circuitry is accomplished via the 4-wire test access port (TAP) interface.

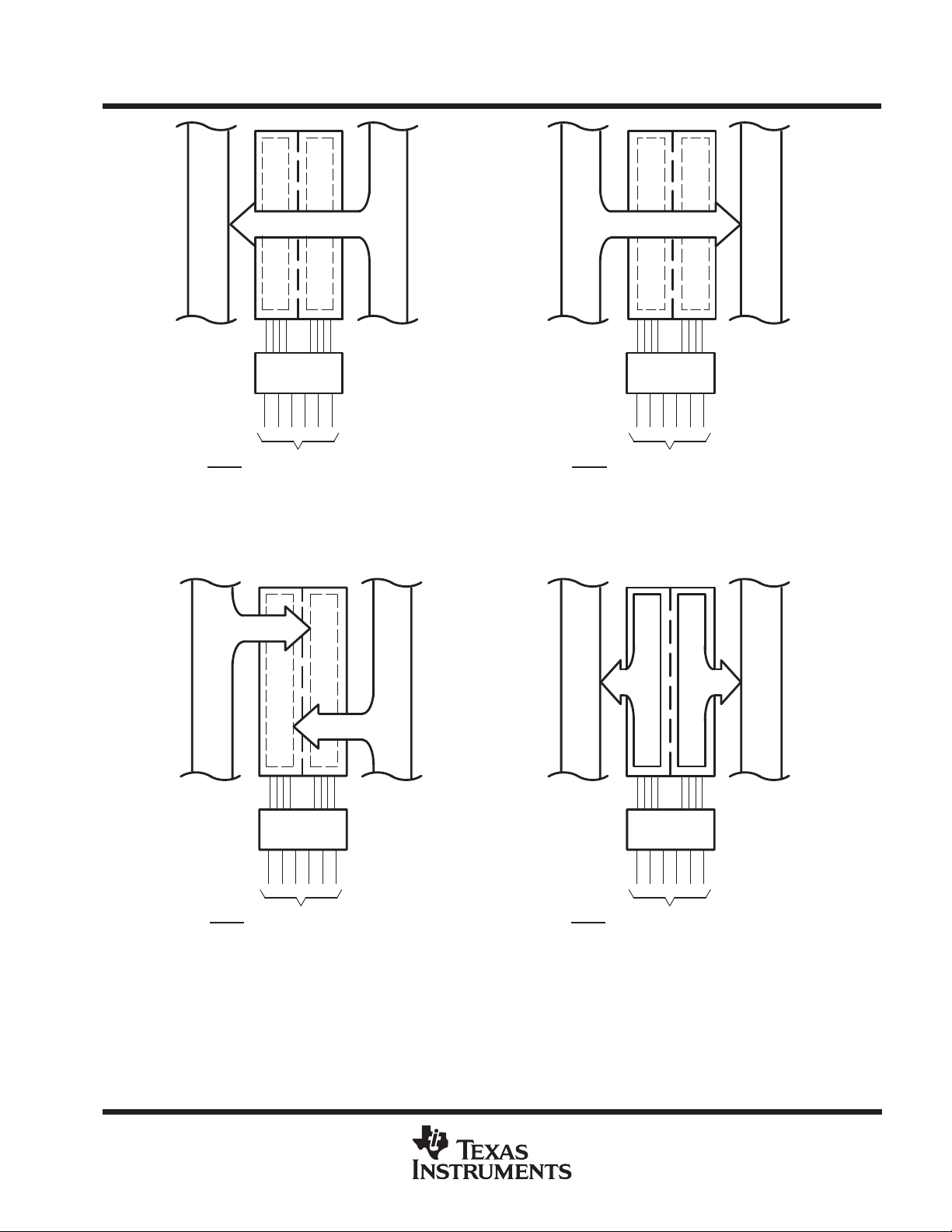

In the normal mode, these devices are 18-bit bus transceivers and registers that allow for multiplexed

transmission of data directly from the input bus or from the internal registers. They can be used either as two

9-bit transceivers or one 18-bit transceiver. The test circuitry can be activated by the TAP to take snapshot

samples of the data appearing at the device pins or to perform a self test on the boundary test cells. Activating

the TAP in the normal mode does not affect the functional operation of the SCOPE bus transceivers and

registers.

Data flow in each direction is controlled by clock (CLKAB and CLKBA), select (SAB and SBA), and output-enable

(OEAB and OEBA

the low-to-high transition of CLKAB. When SAB is low, real-time A data is selected for presentation to the B bus

(transparent mode). When SAB is high, stored A data is selected for presentation to the B bus (registered mode).

When OEAB is high, the B outputs are active. When OEAB is low, the B outputs are in the high-impedance state.

Control for B-to-A data flow is similar to that for A-to-B data flow but uses CLKBA, SBA, and OEBA

the OEBA input is active-low, the A outputs are active when OEBA is low and are in the high-impedance state

when OEBA

with the ′ABT18652.

) inputs. For A-to-B data flow, data on the A bus is clocked into the associated registers on

inputs. Since

is high. Figure 1 illustrates the four fundamental bus-management functions that can be performed

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54ABT18652, SN74ABT18652

OPERATION OR FUNCTION

SCAN TEST DEVICES WITH

18-BIT BUS TRANSCEIVERS AND REGISTERS

SCBS132A – AUGUST 1992 – REVISED OCTOBER 1992

description (continued)

In the test mode, the normal operation of the SCOPE bus transceivers and registers is inhibited, and the test

circuitry is enabled to observe and control the I/O boundary of the device. When enabled, the test circuitry can

perform boundary scan test operations according to the protocol described in IEEE Standard 1149.1-1990.

Four dedicated test pins are used to observe and control the operation of the test circuitry: test data input (TDI),

test data output (TDO), test mode select (TMS), and test clock (TCK). Additionally , the test circuitry can perform

other testing functions such as parallel signature analysis on data inputs and pseudo-random pattern generation

from data outputs. All testing and scan operations are synchronized to the TAP interface.

Additional flexibility is provided in the test mode through the use of two boundary scan cells (BSCs) for each

I/O pin. This allows independent test data to be captured and forced at either bus (A or B). A PSA/COUNT

instruction is also included to ease the testing of memories and other circuits where a binary count addressing

scheme is useful.

The SN54ABT18652 is characterized over the full military temperature range of –55°C to 125°C. The

SN74ABT18652 is characterized for operation from –40°C to 85°C.

FUNCTION TABLE

(normal mode, each 9-bit section)

INPUTS

OEAB OEBA CLKAB CLKBA SAB SBA A1 THRU A9 B1 THRU B9

L H L L X X Input disabled Input disabled Isolation

L H ↑↑X X Input Input Store A and B data

X H ↑ L X X Input Unspecified

H H ↑↑X

L XL ↑ X X Unspecified

L L ↑↑XX‡Output Input Store B in both registers

L L X X X L Output Input Real-time B data to A bus

L L X L X H Output Input Stored B data to A bus

H H X X L X Input Output Real-time A data to B bus

H H L X H X Input Output Stored A data to B bus

H L L L H H Output Output

†

The data output functions can be enabled or disabled by a variety of level combinations at the OEAB or OEBA

always enabled; i.e., data at the bus pins is stored on every low-to-high transition on the clock inputs.

‡

Select control = L: clocks can occur simultaneously.

Select control = H: clocks must be staggered in order to load both registers.

‡

X Input Output Store A in both registers

DATA I/O

†

†

Input Hold A, store B

Store A, hold B

Stored A data to B bus and

stored B data to A bus

inputs. Data input functions are

PRODUCT PREVIEW

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

SN54ABT18652, SN74ABT18652

SCAN TEST DEVICES WITH

18-BIT BUS TRANSCEIVERS AND REGISTERS

SCBS132A – AUGUST 1992 – REVISED OCTOBER 1992

BUS A

PRODUCT PREVIEW

OEAB

OEBA

LL

CLKABXCLKBAXSABXSBA

REAL-TIME TRANSFER

BUS B TO BUS A

BUS B

L

BUS A

OEAB OEBA

HH

BUS B

CLKABXCLKBAXSABLSBA

X

REAL-TIME TRANSFER

BUS A TO BUS B

OEAB

X

L

L

BUS A

CLKAB CLKBAXSABXSBA

OEBA

H

X

H

↑

XX

STORAGE FROM

A, B, OR A AND B

↑

↑↑

BUS B

OEAB OEBA

X

X

X

X

HL L HH

BUS A

TRANSFER STORED DA TA

Figure 1. Bus-Management Functions

BUS B

CLKAB CLKBA SAB SBA

L

TO A AND/OR B

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Loading...

Loading...