SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

4:28 Data Channel Expansion at up to

1.820 Gigabits per Second Throughput

D

Suited for Point-to-Point Subsystem

Communication With Very Low EMI

D

4 Data Channels and Clock Low-Voltage

Differential Channels in and 28 Data and

Clock Out Low-Voltage TTL Channels Out

D

Operates From a Single 3.3-V Supply and

250 mW (Typ)

D

5-V Tolerant SHTDN Input

D

Rising Clock Edge Triggered Outputs

D

Bus Pins Tolerate 4-kV HBM ESD

D

Packaged in Thin Shrink Small-Outline

Package With 20 Mil Terminal Pitch

D

Consumes <1 mW When Disabled

D

Wide Phase-Lock Input Frequency Range

20 MHz to 65 MHz

D

No External Components Required for PLL

D

Meets or Exceeds the Requirements of

ANSI EIA/TIA-644 Standard

D

Industrial Temperature Qualified

TA = –40°C to 85°C

D

Replacement for the DS90CR286

description

The SN65LVDS94 LVDS serdes (serializer/deserializer) receiver contains four serial-in 7-bit

parallel-out shift registers, a 7× clock synthesizer,

and five low-voltage differential signaling (LVDS)

line receivers in a single integrated circuit. These

functions allow receipt of synchronous data from

a compatible transmitter, such as the SN65L VDS93 and SN65L VDS95, over five balanced-pair conductors and

expansion to 28 bits of single-ended LVTTL synchronous data at a lower transfer rate.

When receiving, the high-speed LVDS data is received and loaded into registers at the rate seven times the

L VDS input clock (CLKIN). The data is then unloaded to a 28-bit wide LVTTL parallel bus at the CLKIN rate. A

phase-locked loop clock synthesizer circuit generates a 7× clock for internal clocking and an output clock for

the expanded data. The SN65LVDS94 presents valid data on the rising edge of the output clock (CLKOUT).

The SN65L VDS94 requires only five line termination resistors for the differential inputs and little or no control.

The data bus appears the same at the input to the transmitter and output of the receiver with the data

transmission transparent to the user(s). The only user intervention is the possible use of the shutdown/clear

(SHTDN

) active-low input to inhibit the clock and shut off the LVDS receivers for lower power consumption. A

low level on this signal clears all internal registers to a low level.

The SN65LVDS94 is characterized for operation over ambient air temperatures of –40°C to 85°C.

Copyright 2000, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

D22

D23

D24

GND

D25

D26

D27

LVDSGND

A0M

A0P

A1M

A1P

LVDSV

CC

LVDSGND

A2M

A2P

CLKINM

CLKINP

A3M

A3P

LVDSGND

PLLGND

PLLV

CC

PLLGND

SHTDN

CLKOUT

D0

GND

V

CC

D21

D20

D19

GND

D18

D17

D16

V

CC

D15

D14

D13

GND

D12

D11

D10

V

CC

D9

D8

D7

GND

D6

D5

D4

D3

V

CC

D2

D1

DGG PACKAGE

(TOP VIEW)

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

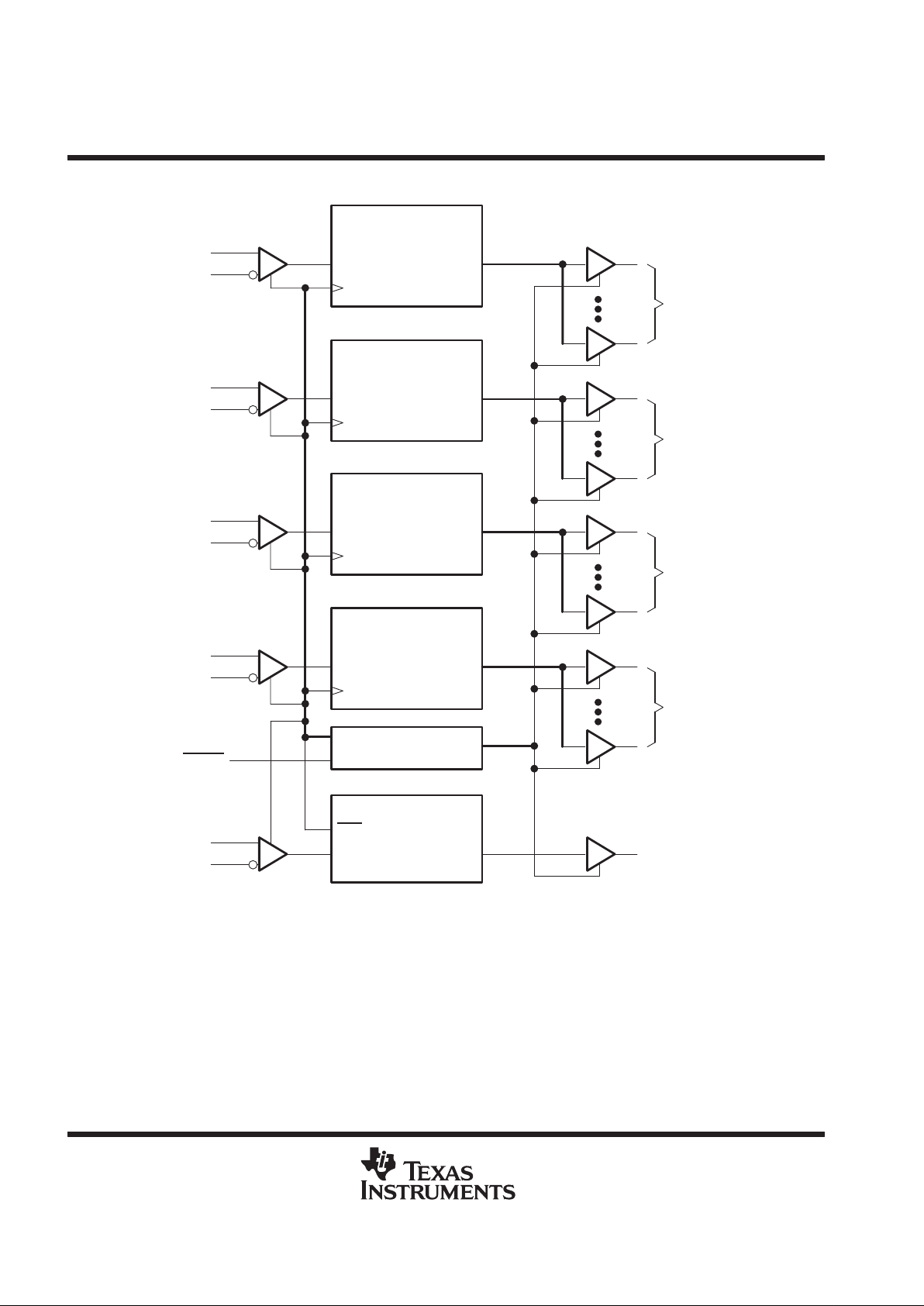

functional block diagram

Serial In

CLK

Serial-In/Parallel-Out

Shift Register

A,B, ...G

A0P

A0M

Serial In

CLK

Serial-In/Parallel-Out

Shift Register

A,B, ...G

A1P

A1M

Serial In

CLK

Serial-In/Parallel-Out

Shift Register

A,B, ...G

A2P

A2M

Serial In

CLK

Serial-In/Parallel-Out

Shift Register

A,B, ...G

A3P

A3M

Clock In

CLK

7× Clock/PLL

Clock Out

CLKINP

CLKINM

Control Logic

SHTDN

D0

D1

D2

D3

D4

D6

D7

D8

D9

D12

D13

D14

D15

D18

D19

D20

D21

D22

D24

D25

D26

D27

D5

D10

D11

D16

D17

D23

CLKOUT

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKOUT

D0-1

D7 D6 D4 D3 D2 D1 D0 D7+1

D86-1

D18 D15 D14 D13 D12 D9 D8 D18+1

D19-1

D26 D25 D24 D22 D21 D20 D19 D26+1

D27-1

D23 D17 D16 D11 D10 D5 D27 D23+1

Current Cycle Next CyclePrevious Cycle

A3

A2

A1

A0

CLKIN

Dn Dn-1 Dn Dn+1

Figure 1. SN65LVDS94 Load and Shift Sequences

equivalent input and output schematic diagrams

300 kΩ300 kΩ

7 V

AnMAnP

V

CC

7 V

V

CC

7 V

300 kΩ

50 Ω

SHTDN

50 Ω

7 V

V

CC

D Output

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range, VCC (see Note 1) –0.3 V to 4 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range at any terminal (except SHTDN) –0.5 V to V

CC

+ 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range at SHTDN

terminal –0.5 V to V

CC

+ 3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Electrostatic discharge (see Note 2): Bus pins (Class 3A) 4 KV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus pins (Class 2B) 200 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

All pins (Class 3A) 3 KV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

All pins (Class 2B) 200 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation (see Dissipation Rating Table). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

–40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the GND terminals unless otherwise noted.

2. This rating is measured using MIL-STD-883C Method, 3015.7.

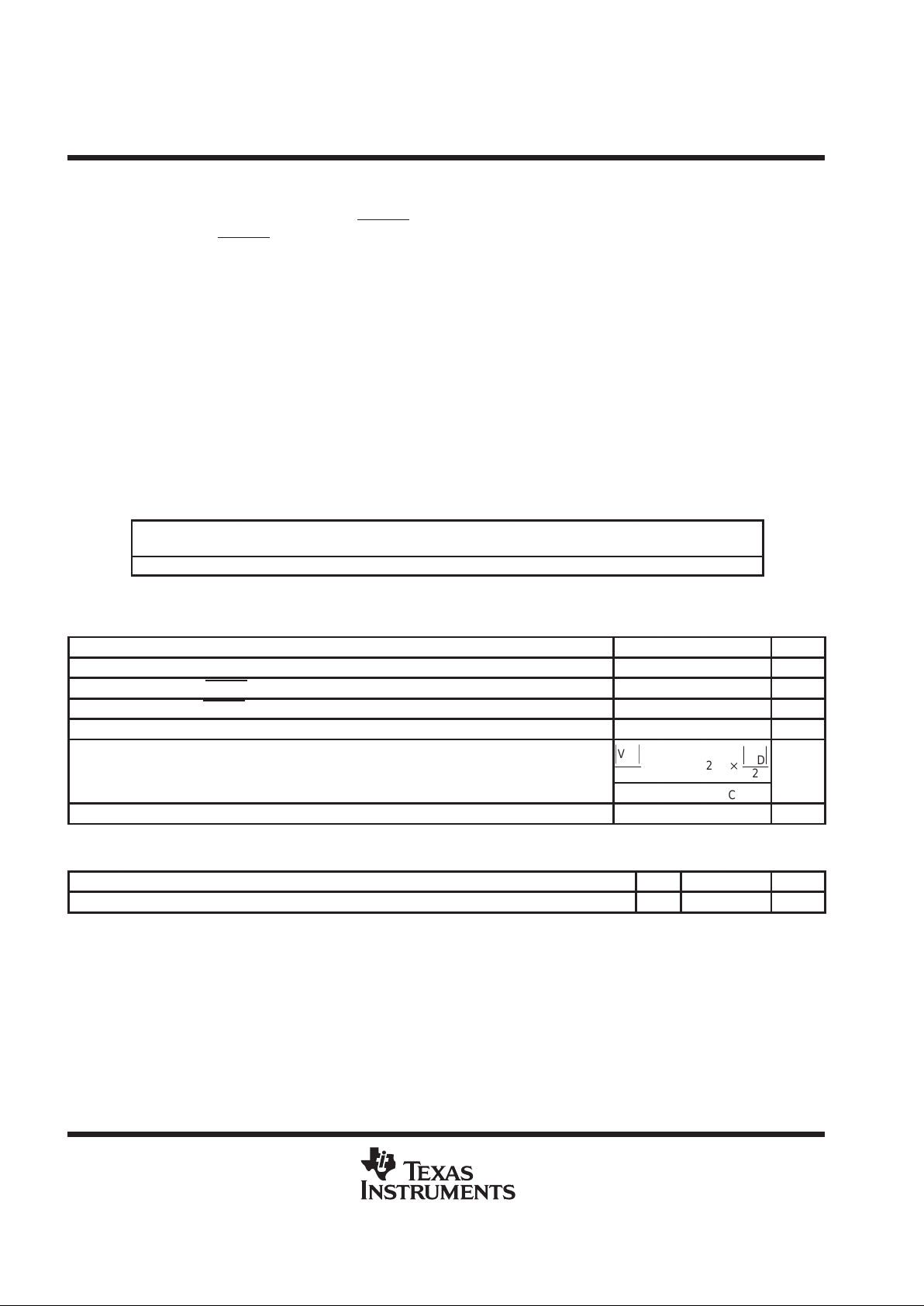

DISSIPATION RATING T ABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

‡

ABOVE TA = 25°C

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

DGG 1377 mW 11 mW/°C 882 mW 717 mW

‡

This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

recommended operating conditions

MIN NOM MAX UNIT

Supply voltage, V

CC

3 3.3 3.6 V

High-level input voltage (SHTDN), V

IH

2 V

Low-level input voltage (SHTDN), V

IL

0.8 V

Magnitude of differential input voltage, VID 0.1 0.6 V

Common–mode input voltage, VIC (see Figures 2 and 3)

Ť

V

ID

Ť

2

2.4

Ť

V

ID

Ť

2

V

VCC–0.8

Operating free–air temperature, T

A

–40 85 °C

timing requirements

MIN NOM MAX UNIT

t

c

§

Input clock period 15.4 t

c

50 Vns

§

tc is defined as the mean duration of a minimum of 32,000 clock periods.

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

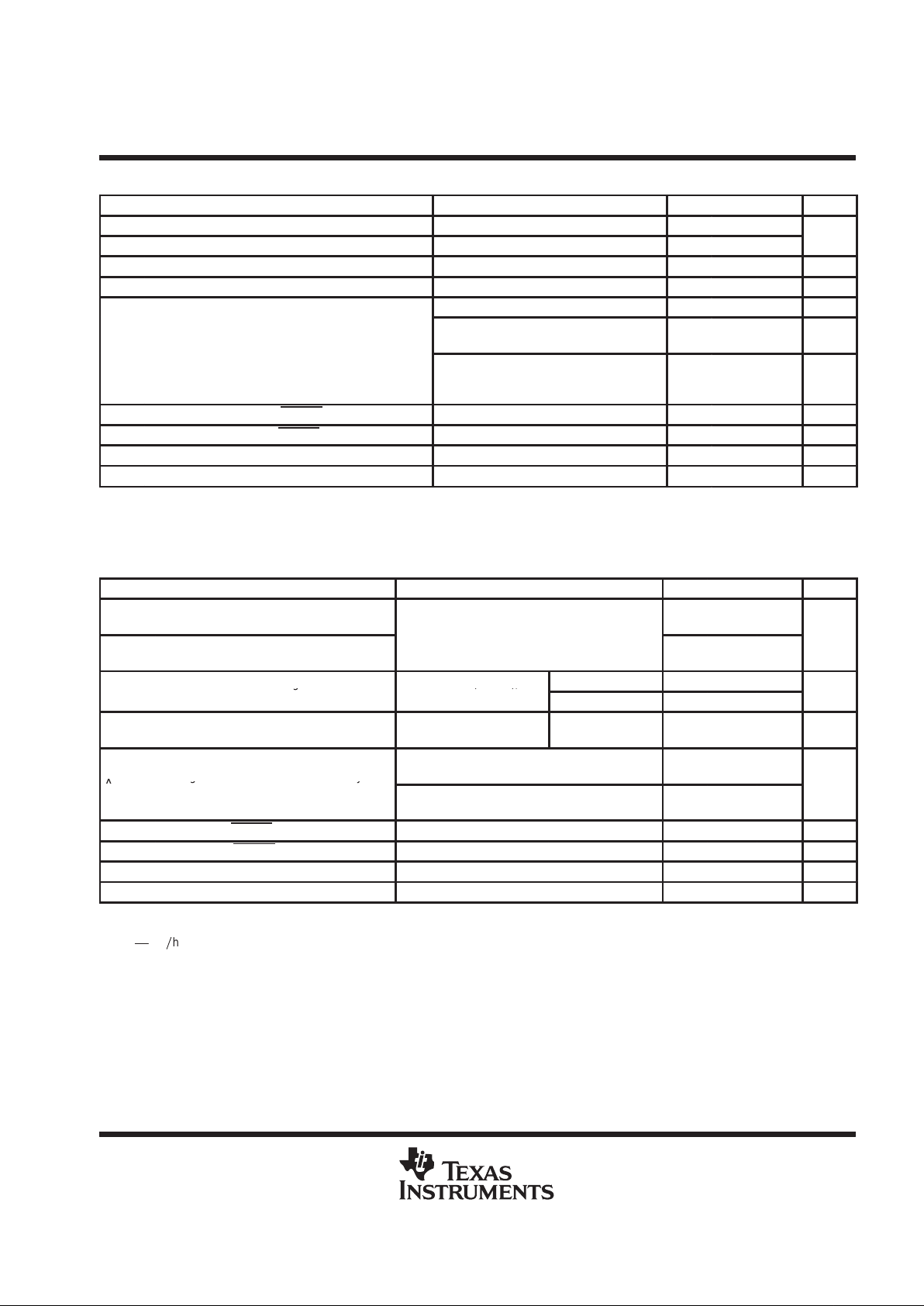

electrical characteristics over recommended operating conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

V

IT+

Positive-going differential input voltage threshold 100

V

IT–

Negative-going differential input voltage threshold

‡

–100

mV

V

OH

High-level output voltage IOH = –4 mA 2.4 V

V

OL

Low-level output voltage IOL = 4 mA 0.4 V

Disabled, all inputs open 280 µA

Enabled, AnP at 1 V and AnM at 1.4 V ,

tc = 15.38 ns

62 84 mA

ICCQuiescent current (average)

Enabled, CL = 8 pF (5 places),

Worst-case pattern (see Figure 4),

tc = 15.38 ns

107 mA

I

IH

High-level input current (SHTDN) VIH = V

CC

±20 µA

I

IL

Low-level input current (SHTDN) VIL = 0 V ±20 µA

I

IN

Input current (A inputs) 0 V ≤ VI ≤ 2.4 V ±20 µA

I

OZ

High-impedance output current VO = 0 V or V

CC

±10 µA

†

All typical values are VCC = 3.3 V, TA = 25°C.

‡

The algebraic convention, in which the less-positive (more-negative) limit is designated minimum, is used in this data sheet for the negative-going

input voltage threshold only.

switching characteristics over recommended operating conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

t

su

Data setup time, D0 through D27 to

CLKOUT

p

4 6

t

h

Data hold time, CLKOUT to D0 through

D27

C

L

= 8

pF

See Figure 5

4 6

ns

Receiver input skew margin

§

t

= 15.38 ns (±0.2%),

TA = 0°C to 85°C 490 800

p

t

RSKM

g

(see Figure 7)

c

( ),

|Input clock jitter| <50 ps

¶

TA = –40°C to 0°C 390

ps

t

d

Delay time, input clock to output clock

(see Figure 7)

tc = 15.38 ns (±0.2%) 3.7 ns

Change in output clock period from cycle

tc = 15.38 + 0.75 sin (2π500E3t)±0.05 ns,

See Figure 7

±80

p

∆t

C(O)

gy

to cycle

#

tc = 15.38 + 0.75 sin (2≠3E6t) ±0.05 ns,

See Figure 7

±300

ps

t

en

Enable time, SHTDN to phase lock See Figure 8 1 ms

t

dis

Disable time, SHTDN to Off state See FIgure 9 400 ns

t

t

Output transition time (tr or tf) CL = 8 pF 3 ns

t

w

Output clock pulse duration 0.43 t

c

ns

§

t

RSKM

is the timing margin available to allocate to the transmitter and interconnection skews and clock jitter. It is defined by

t

c

14

–tsńh.

¶

|Input clock jitter| is the magnitude of the change in the input clock period.

#

∆t

C(O)

is the change in the output clock period from one cycle to the next cycle observed over 15,000 cycles.

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

AP

AM

V

ID

V

IAM

V

IAP

V

IC

(V

IAP

+ V

IAM

)/2

Figure 2. Voltage Definitions

|VID|– Differential Input Voltage and VCC – V

COMMON-MODE INPUT VOLTAGE

vs

DIFFERENTIAL INPUT VOLTAGE AND V

CC

1.5

1

0.5

0

0.1 0.30.2 0.4

2.5

0

0.5 0.6

2

MIN

MAX at 3 V

MAX at >3.15 V

– Common-Mode Input Voltage – V

V

IC

Figure 3. Recommended VIC Versus VID and V

CC

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

CLKIN/

CLKOUT

EVEN Dn

ODD Dn

T

Figure 4. Worst-Case Power Test Pattern

‡

The worst-case test pattern produces nearly the maximum switching frequency for all of the LV-TTL outputs.

70%

t

su

CLKOUT

D0–27

30%

70%

30%

V

OH

V

OH

V

OL

V

OL

t

h

Figure 5. Setup and Hold Time Measurements

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

An

and An

CLKIN

7×CLK

(Internal)

CLKOUT

t

s

t

h

4/7 tc ± t

RSKM

3/7 tc ± t

RSKM

t

c

t

d

0 V

≅ 300 mV

tr < 1 ns

V

OH

1.4 V

90%

10%

≅ –300 mV

CLKIN or An

CLKOUT

V

OL

Tektronix

HFS9003/HFS9DG1

Stimulus System

(Repeating Patterns

1110111 and 0001000)

DUT

Tektronix Microwave

Logic Multi-BERT-100RX

Word Error Detector

D0–D27

CLKOUTCLKIN

An

CLKIN is advanced or delayed with respect to data until errors are observed at the receiver outputs.

The magnitude of the advance or delay is t

RSKM

.

Figure 6. Receiver Input Skew Margin and td Definitions

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

HP8656B Signal

Generator,

0.1 MHz–990 MHz

RF Output

OutputModulation Input CLKOUT

HP8665A Synthesized

Signal Generator,

0.1 MHz–4200 MHz

Device Under

Test

CLKIN Input

DTS2070C

Digital Time

Scope

Device

Under

Test

VCO

Reference

Modulation

v(t) = A sin(2πf

mod

t)

Σ

+

+

Figure 7. Output Clock Jitter Test Setup

CLKIN

An

SHTDN

Dn

t

en

Invalid

Valid

Figure 8. Enable Time Waveforms

t

dis

CLKIN

SHTDN

CLKOUT

Figure 9. Disable Time Waveforms

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

I

CC

60

40

20

0

30 40 50 60 70

80

100

120

f – Frequency – MHz

– Supply Current – mA

140

WORST-CASE SUPPLY CURRENT

vs

FREQUENCY

VCC = 3.3 V

VCC = 3 V

VCC = 3.6 V

Figure 10

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

16-bit bus extension

In a 16-bit bus application (Figure 11), TTL data and clock coming from bus transceivers that interface the

backplane bus arrive at the Tx parallel inputs of the L VDS serdestransmitter. The clock associated with the bus

is also connected to the device. The on-chip PLL synchronizes this clock with the parallel data at the input. The

data is then multiplexed into three different line drivers which perform the TTL to LVDS conversion. The clock

is also converted to L VDS and presented to a separate driver. This synchronized LVDS data and clock at the

receiver, which recovers the LVDS data and clock, performs a conversion back to TTL. Data is then

demultiplexed into a parallel format. An on-chip PLL synchronizes the received clock with the parallel data, and

then all are presented to the parallel output port of the receiver.

SN74FB2032

8

D0–D7

8

D8–D15

SN75L0DS93

LVDS

Interface

0 To 10 Meters

(Media Dependent)

TTL

Interface

16-Bit

BTL Bus

Interface

CLK

Backplane

Bus

8

D0–D7

8

D8–D15

CLK

Backplane

Bus

TTL

Interface

16-Bit

BTL Bus

Interface

XMIT Clock RCV Clock

SN74FB2032

SN75LV0S94

SN74FB2032

SN74FB2032

Figure 11. 16-Bit Bus Extension

16-bit bus extension with parity

In the previous application we did not have a checking bit that would provide assurance that the data crosses

the link. If we add a parity bit to the previous example, we would have a diagram similar to the one in Figure 12.

The device following the SN74FB2032 is a low cost parity generator. Each transmit-side transceiver/parity

generator takes the L VTTL data from the corresponding transceiver, performs a parity calculation over the byte,

and then passes the bits with its calculated parity value on the parallel input of the LVDS serdes transmitter.

Again, the on-chip PLL synchronizes this transmit clock with the eighteen parallel bits (16 data + 2 parity) at the

input. The synchronized LVDS data/parity and clock arrive at the receiver.

The receiver performs the conversion from L VDS to LVTTL and the transceiver/parity generator performs the

parity calculations. These devices compare their corresponding input bytes with the value received on the parity

bit. The transceiver/parity generator will assert its parity error output if a mismatch is detected.

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

SN74FB2032

8

D0–D7

8

D8–D15

SN75LVDS93

LVDS

Interface

0 To 10 Meters

(Media Dependent)

TTL

Interface

W/Parity

16-Bit

BTL Bus

Interface

CLK

Backplane

Bus

8

D0–D7

8

D8–D15

CLK

Backplane

Bus

TTL

Interface

16-Bit

BTL Bus

Interface

XMIT Clock RCV Clock

9 Bit Latchable

Transceiver/ With

Parity Generator

Parity

Parity

TTL

Interface

Parity

Parity

Parity

Error

TTL

Interface

W/Parity

SN74FB2032

9 Bit Latchable

Transceiver/ With

Parity Generator

SN74FB2032

SN74FB2032

9 Bit Latchable

Transceiver/ With

Parity Generator

9 Bit Latchable

Transceiver/ With

Parity Generator

SN75LVDS94

Figure 12. 16-Bit Bus Extension With Parity

low cost virtual backplane transceiver

Figure 13 represents L VDS serdes in an application as a virtual backplane transceiver (VBT). The concept of

a VBT can be achieved by implementing individual LVDS serdes chipsets in both directions of subsystem

serialized links.

Depending on the application, the designer will face varying choices when implementing a VBT. In addition to

the devices shown in Figure 13, functions such as parity and delay lines for control signals could be included.

Using additional circuitry, half-duplex or full-duplex operation can be achieved by configuring the clock and

control lines properly.

The designer may choose to implement an independent clock oscillator at each end of the link and then use

a PLL to synchronize LVDS serdes’s parallel I/O to the backplane bus. Resynchronizing FIFOs may also be

required.

Bus

Transceivers

LVDS Serdes

Transmitter

LVDS Serdes

Receiver

Bus

Transceivers

TTL

Inputs

Up To

21 or 28

Bits

LVDS

Serial Links

4 or 5

Pairs

TTL

Outputs

Up To

21 or 28

Bits

Bus

Transceivers

LVDS Serdes

Transmitter

LVDS Serdes

Receiver

Bus

Transceivers

Backplane

Bus

Backplane

Bus

Figure 13. Virtual Backplane Transceiver

SN65LVDS94

LVDS SERDES RECEIVER

SLLS298E – MAY 1998 – REVISED FEBRUAR Y 2000

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MECHANICAL DATA

DGG (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

4040078/F 12/97

48 PIN SHOWN

0,25

0,15 NOM

Gage Plane

6,00

6,20

8,30

7,90

0,75

0,50

Seating Plane

25

0,27

0,17

24

A

48

1

1,20 MAX

M

0,08

0,10

0,50

0°–8°

56

14,10

13,90

48

DIM

A MAX

A MIN

PINS **

12,40

12,60

64

17,10

16,90

0,15

0,05

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Loading...

Loading...