www.ti.com

Flatlink 3Gä

1

4

7

*

3

6

9

#

2

5

8

0

Application

Processor

with

RGB

Video

Interface

LVDS302

LVDS301

LCD

Driver

DATACLK

PROGRAMMABLE 27-BIT DISPLAY SERIAL INTERFACE TRANSMITTER

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

FEATURES

• FlatLink™3G serial interface technology

• Compatible with FlatLink3G receivers such as

SN65LVDS302

• Input supports 24-bit RGB video mode

interface

• 24-Bit RGB Data, 3 Control Bits, 1 Parity Bit

and 2 Reserved Bits Transmitted over 1, 2 or 3

Differential Lines

• SubLVDS Differential Voltage Levels

• Effective Data Throughput up to 1755 Mbps

• Three Operating Modes to Conserve Power

– Active-Mode QVGA 17.4 mW (typ)

– Active-Mode VGA 28.8 mW (typ)

FPC cabling typically interconnects the

SN65LVDS301 with the display. Compared to

parallel signaling, the LVDS301 outputs significantly

reduce the EMI of the interconnect by over 20 dB.

The electromagnetic emission of the device itself is

very low and meets the meets SAE J1752/3

'M'-spec. (see Figure 37 )

The SN65LVDS301 supports three power modes

(Shutdown, Standby and Active) to conserve power.

When transmitting, the PLL locks to the incoming

pixel clock PCLK and generates an internal

high-speed clock at the line rate of the data lines.

The parallel data are latched on the rising or falling

edge of PCLK as selected by the external control

signal CPOL. The serialized data is presented on the

serial outputs D0, D1, D2 with a recreated PCLK

generated from the internal high-speed clock, output

– Shutdown Mode ≈ 0.5 µ A (typ) on the CLK output. If PCLK stops, the device enters

– Standby Mode ≈ 0.5 µ A (typ)

• Bus Swap for Increased PCB Layout

Flexibility

• 1.8-V Supply Voltage

• ESD Rating > 2 kV (HBM)

• Typical Application: Host-Controller to

Display-Module Interface

• Pixel Clock Range of 4 MHz–65 MHz

a standby mode to conserve power

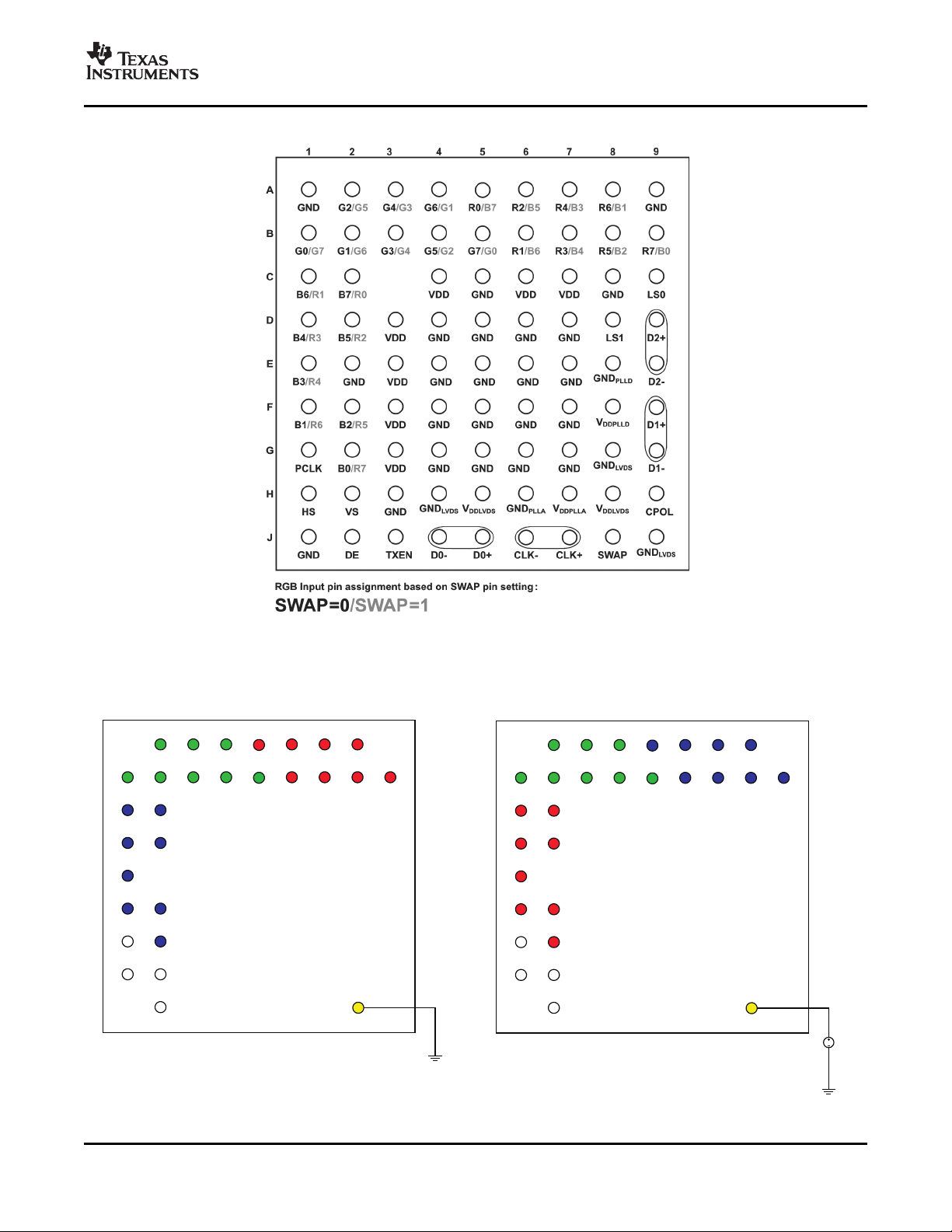

The parallel (CMOS) input bus offers a bus-swap

feature. The SWAP pin configures the input order of

the pixel data to be either R[7:0]. G[7:0], B[7:0], VS,

HS, DE or B[0:7]. G[0:7], R[0:7], VS, HS, DE. This

gives a PCB designer the flexibility to better match

the bus to the host controller pinout or to put the

transmitter device on the top side or the bottom side

of the PCB.

• Failsafe on all CMOS Inputs

• Packaging: 80 Pin 5mm × 5mm µ BGA

®

• Very low EMI meets SAE J1752/3 'M'-spec

DESCRIPTION

The SN65LVDS301 serializer device converts 27

parallel data inputs to 1, 2, or 3 Sub Low-Voltage

Differential Signaling (SubLVDS) serial outputs. It

loads a shift register with 24 pixel bits and 3 control

bits from the parallel CMOS input interface. In

addition to the 27 data bits, the device adds a parity

bit and two reserved bits into a 30-bit data word.

Each word is latched into the device by the pixel

clock (PCLK). The parity bit (odd parity) allows a

receiver to detect single bit errors. The serial shift

register is uploaded at 30, 15, or 10 times the

pixel-clock data rate depending on the number of

serial links used. A copy of the pixel clock is output

on a separate differential output.

FlatLink is a trademark of Texas Instruments.

µ BGA is a registered trademark of Tessera, Inc..

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 2006, Texas Instruments Incorporated

www.ti.com

[0..26]

0

1

PLL

multiplier

TXEN

PCLK

VS

HS

B[0:7]

G[0:7]

R[0:7]

DE

LS1

8

8

8

SubLVDS

D0+

D0−

SubLVDS

D2+

D2−

SubLVDS

CLK+

CLK−

SubLVDS

D1+

D1−

LS0

CPOL

SWAP

Parity

Calc

1

0

iPCLK

Bit28=0

Bit27=0

3x10, 2x15, or 1x30−bit parallel to serial conversion

Bit29

Glitch

supression

Control /

standby Monitor

x1

x10, x15, or x30

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

DESCRIPTION (CONTINUED)

Two Link Select lines LS0 and LS1 control whether 1, 2 or 3 serial links are used. The TXEN input may be used

to put the SN65LVDS301 in a shutdown mode. The SN65LVDS301 enters an active Standby mode if the input

clock PCLK stops. This minimizes power consumption without the need for controlling an external pin. The

SN65LVDS301 is characterized for operation over ambient air temperatures of –40 ° C to 85 ° C. All CMOS inputs

offer failsafe features to protect them from damage during power-up and to avoid current flow into the device

inputs during power-up. An input voltage of up to 2.165 V can be applied to all CMOS inputs while V

between 0V and 1.65V.

Functional Block Diagram

is

DD

2

Submit Documentation Feedback

www.ti.com

PINOUT - TOP VIEW

9

8764 5321

A

D

C

B

G

F

E

H

J

G0

B7

R7

B0

DE

HS VS

PCLK

B5

B1B4B2

B3

B6

R1

G6

G5G3

G2

G1 R3R6R5

R2 R4

G7

R0G4

SN65LVDS301

TopView

SWAP

SWAP=0

9

8764 5321

A

D

C

B

G

F

E

H

J

G7

R0

B0

R7

DE

HS VS

PCLK

R2

R6R3R5

R4

R1

B6

G1

G2G4

G5

G6 B4B1B2

B5 B3

G0

B7G3

SN65LVDS301

TopView

SWAP

SWAP=1

1.8V

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

SWAP PIN FUNCTIONALITY

The SWAP pin allows the pcb designer to reverse the RGB bus to minimize potential signal crossovers in the

PCB routing. The two drawings beneath show the RGB signal pin assignment based on the SWAP-pin setting.

Figure 1. SWAP PIN = 0 Figure 2. SWAP PIN = 1

Submit Documentation Feedback

3

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

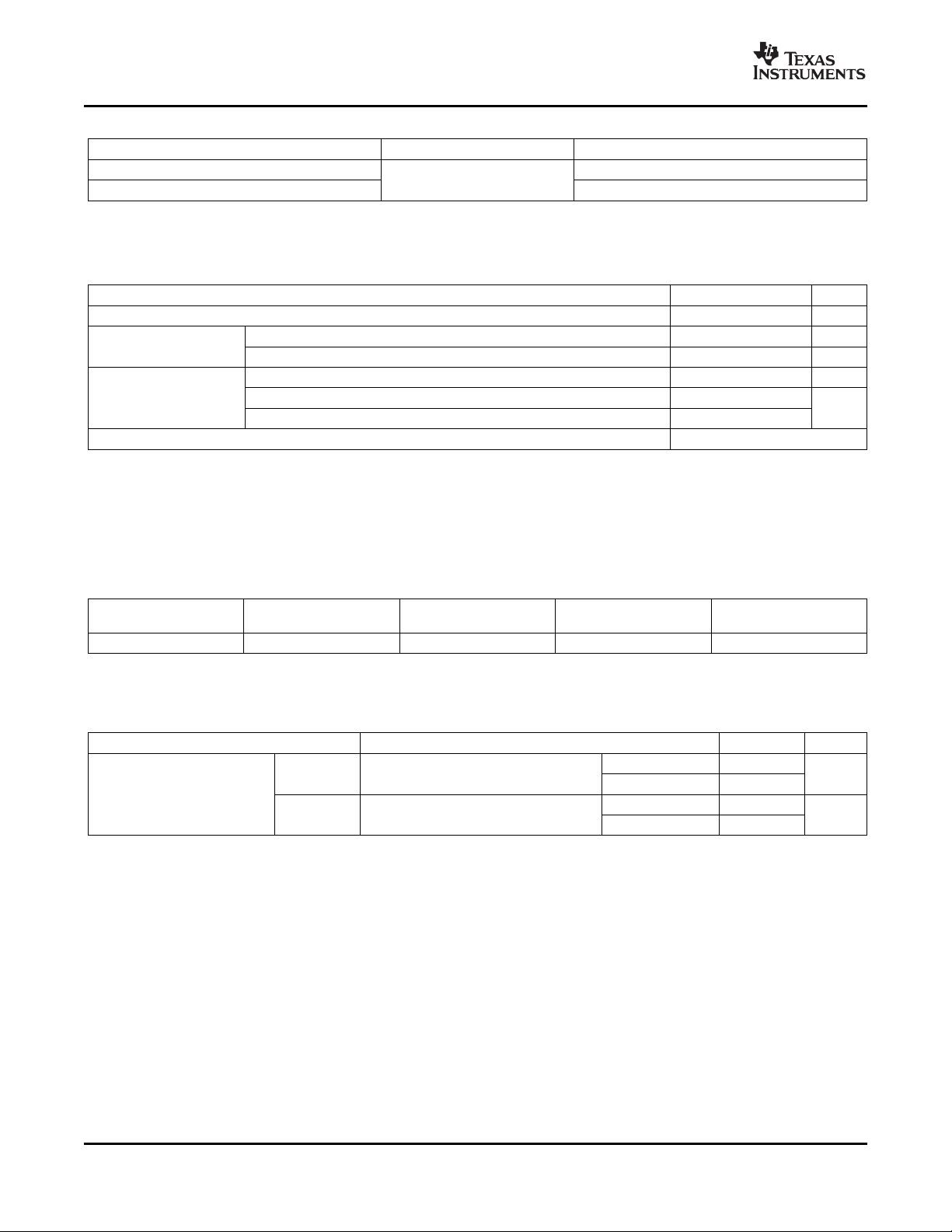

Table 1. NUMERIC PIN LIST

PIN SWAP SIGNAL PIN SWAP . . SIGNAL PIN SWAP SIGNAL

A1 — GND 0 B6 0 B1

A2

A3

A4

A5

A6

A7 D1

A8 D2

0 G2 1 R1 1 R6

1 G5 0 B7 0 B2

0 G4 1 R0 1 R5

1 G3 C3 UNPOPULATED F3 — VDD

0 G6 C4 — VDD F4 — GND

1 G1 C5 — GND F5 — GND

0 R0 C6 — VDD F6 — GND

1 B7 C7 — VDD F7 — GND

0 R2 C8 — GND F8 — V

1 B5 C9 — LS0 F9 — D1+

0 R4 0 B4 G1 — PCLK

1 B3 1 R3 0 B0

0 R6 0 B5 1 R7

1 B1 1 R2 G3 — V

A9 — GND D3 — VDD G4 — GND

B1

B2

B3

B4 E1

B5

B6

B7

B8

B9

0 G0 D4 — GND G5 — GND

1 G7 D5 — GND G6 — GND

0 G1 D6 — GND G7 — GND

1 G6 D7 — GND G8 — GND

0 G3 D8 — LS1 G9 — D1–

1 G4 D9 — D2+ H1 — HS

0 G5 0 B3 H2 — VS

1 G2 1 R4 H3 — GND

0 G7 E2 — GND H4 — GND

1 G0 E3 — VDD H5 — V

0 R1 E4 — GND H6 — GND

1 B6 E5 — GND H7 — V

0 R3 E6 — GND H8 — V

1 B4 E7 — GND H9 — CPOL

0 R5 E8 — GND

1 B2 E9 — D2– J2 — DE

0 R7 J3 — TXEN

1 B0 J4 — D0–

C1 F1

C2 F2

PLLD

G2

J1 — GND

J5 — D0+

J6 — CLK–

J7 — CLK+

J8 — SWAP

J9 — GND

DDPLLD

DD

LVDS

LVDS

DDLVDS

PLLA

DDPLLA

DDLVDS

LVDS

4

Submit Documentation Feedback

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

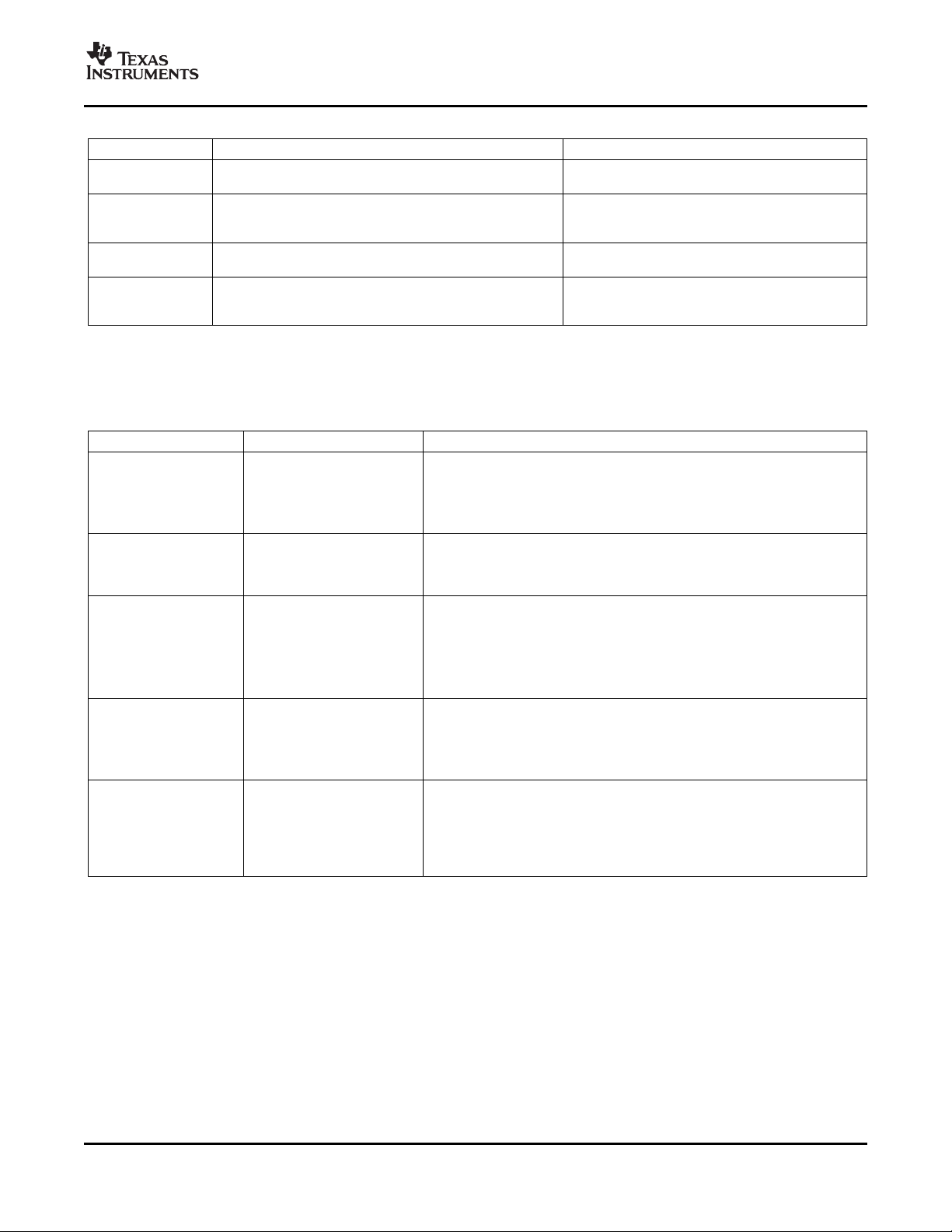

TERMINAL FUNCTIONS

NAME I/O DESCRIPTION

D0+, D0– SubLVDS Data Link (active during normal operation)

D1+, D1–

SubLVDS Out

D2+, D2–

CLK+, CLK– SubLVDS output Clock; clock polarity is fixed

R0–R7 Red Pixel Data (8); pin assignment depends on SWAP pin setting

G0–G7 Green Pixel Data (8); pin assignment depends on SWAP pin setting

B0–B7 Blue Pixel Data (8); pin assignment depends on SWAP pin setting

HS Horizontal Sync

VS Vertical Sync

DE Data Enable

PCLK Input Pixel Clock; rising or falling clock polarity is selected by control input CPOL

LS0, LS1 Link Select (Determines active SubLVDS Data Links and PLL Range) See Table 2

CMOS IN

TXEN

CPOL CMOS In

SWAP CMOS In

V

DD

GND Supply Ground

V

DDLVDS

GND

LVDS

V

DDPLLA

GND

PLLA

V

DDPLLD

GND

PLLD

Power Supply

(1)

(1) For a multilayer pcb, it is recommended to keep one common GND layer underneath the device and connect all ground terminals

directly to this plane.

SubLVDS Data Link (active during normal operation when LS0 = high and LS1 = low, or

LS0 = low and LS1=high; high impedance if LS0 = LS1 = low)

SubLVDS Data Link (active during normal operation when LS0 = low and LS1 = high,

high-impedance when LS1 = low)

Disables the CMOS Drivers and Turns Off the PLL, putting device in shutdown mode

1 – Transmitter enabled

0 – Transmitter disabled

(Shutdown)

Note: The TXEN input incorporates glitch-suppression logic to avoid device malfunction

on short input spikes. It is necessary to pull TXEN high for longer than 10 µ s to enable

the transmitter. It is necessary to pull the TXEN input low for longer than 10 µ s to

disable the transmitter. At power up, the transmitter is enabled immediately if TXEN = 1

and disabled if TXEN = 0

Input Clock Polarity Selection

0 – rising edge clocking

1 – falling edge clocking

Bus Swap swaps the bus pins to allow device placement on top or bottom of pcb. See

pinout drawing for pin assignments.

0 – data input from B0...R7

1 – data input from R7...B0

Supply Voltage

SubLVDS I/O supply Voltage

SubLVDS Ground

PLL analog supply Voltage

PLL analog GND

PLL digital supply Voltage

PLL digital GND

Submit Documentation Feedback

5

www.ti.com

D0+/– CHANNEL

CLK+

B7

B6

R7

R6

R5

R4

R3

R2 R1

R0

G7 G6 G5 G4G3G2 G1 G0

B5

B4

B3

B2 B1

B0

VS HS DE

0 0

CP R7

R6

CP

00

CLK–

R7

R6

R5

R4

R3

R2 R1

R0

G7 G6 G5 G4 VS0CP

0

B7

B6

G3

G2 G1 G0

B5

B4

B3

B2 B1

B0

HS DE

0

CP R7

R6

G3

G2

CLK+

CLK–

D0+/– Channel

D1+/– Channel

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

FUNCTIONAL DESCRIPTION

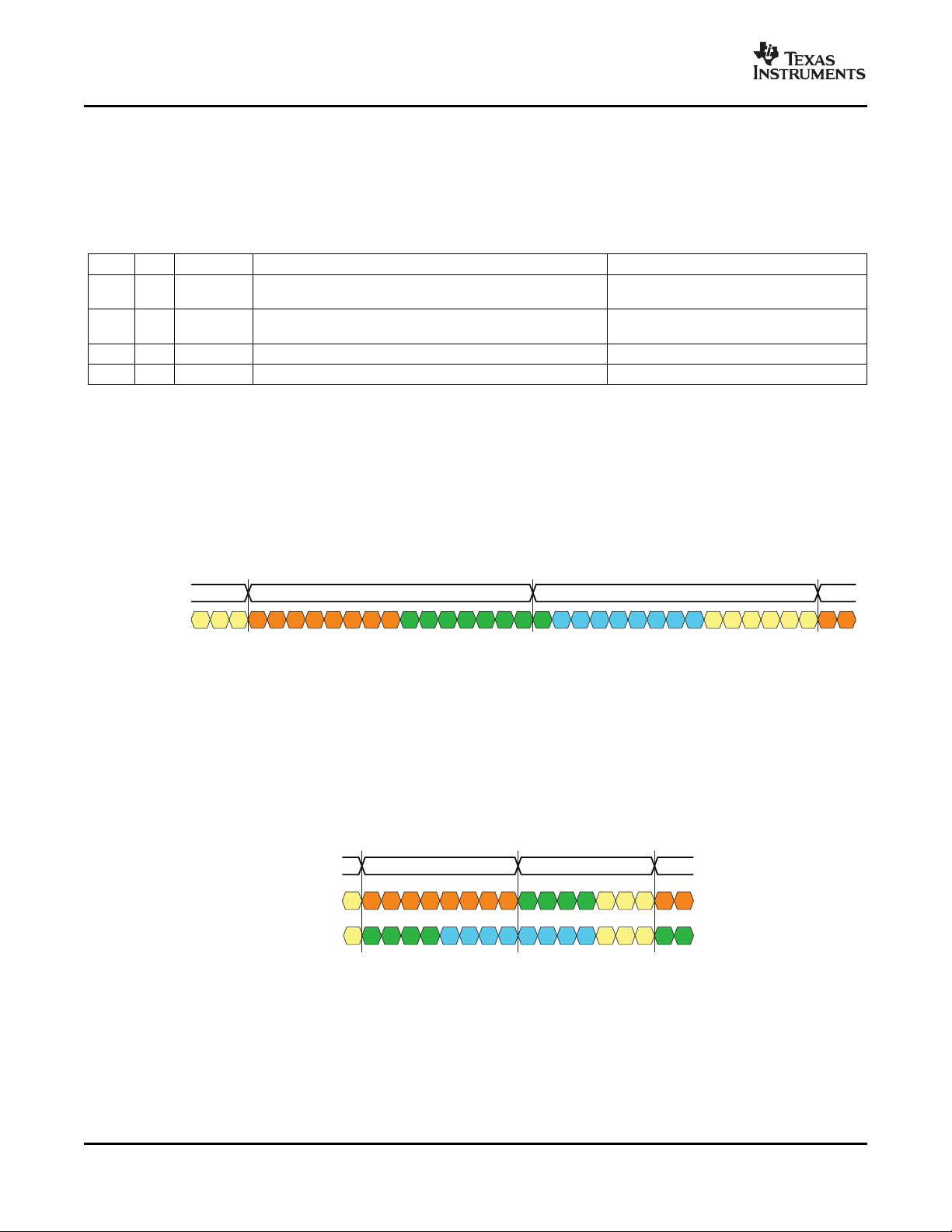

Serialization Modes

The SN65LVDS301 transmitter has three modes of operation controlled by link-select pins LS0 and LS1.

Table 2 shows the serializer modes of operation.

Table 2. Logic Table: Link Select Operating Modes

LS1 LS0 Mode of Operation Data Links Status

0 0 1ChM 1-channel mode (30-bit serialization rate) D0 active;

0 1 2ChM 2-channel mode (15-bit serialization rate) D0, D1 active;

1 0 3ChM 3-channel mode (10-bit serialization rate) D0, D1, D2 active

1 1 Reserved Reserved

1-Channel Mode

While LS0 and LS1 are held low, the SN65LVDS301 transmits payload data over a single SubLVDS data pair,

D0. The PLL locks to PCLK and internally multiplies the clock by a factor of 30. The internal high-speed clock is

used to serialize (shift out) the data payload on D0. Two reserved bits and the parity bit are added to the data

frame. Figure 3 illustrates the timing and the mapping of the data payload into the 30-bit frame. The internal

high-speed clock is divided by a factor of 30 to recreate the pixel clock, and presented on the SubLVDS CLK

output. While in this mode, the PLL can lock to a clock that is in the range of 4 MHz through 15 MHz. This mode

is intended for smaller video display formats (e.g. QVGA to HVGA) that do not require the full bandwidth

capabilities of the SN65LVDS301.

D1, D2 high-impedance

D2 high-impedance

Figure 3. Data and Clock Output in 1-Channel Mode (LS0 and LS1 = low).

2-Channel Mode

While LS0 is held high and LS1 is held low, the SN65LVDS301 transmits payload data over two SubLVDS data

pairs, D0 and D1. The PLL locks to PCLK and internally multiplies it by a factor of 15. The internal high-speed

clock is used to serialize the data payload on D0, and D1. Two reserved bits and the parity bit are added to the

data frame. Figure 4 illustrates the timing and the mapping of the data payload into the 30-bit frame and how the

frame becomes split into the two output channels. The internal high-speed clock is divided by 15 to recreate the

pixel clock, and presented on SubLVDS CLK. The PLL can lock to a clock that is in the range of 8 MHz through

30 MHz in this mode. Typical applications for using the 2-channel mode are HVGA and VGA displays.

Figure 4. Data and Clock Output in 2-Channel Mode (LS0 = high; LS1 = low).

6

Submit Documentation Feedback

www.ti.com

D0+/-CHANNEL

CLK+

B7 B6

R7 R6 R5 R4 R3 R2 R1 R0

G7 G6 G5 G4 G3 G2 G1 G0

B5 B4 B3 B2 B1 B0

VS

HS

DE

CP

0

0

CP

0

0

CLK-

B7 B6

R7 R6

G7 G6D1+/-CHANNEL

D2+/-CHANNEL

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

3-Channel Mode

While LS0 is held low and LS1 is held high, the SN65LVDS301 transmits payload data over three SubLVDS

data pairs D0, D1, and D2. The PLL locks to PCLK, and internally multiplies it by 10. The internal high-speed

clock is used to serialize the data payload on D0, D1, and D2. Two reserved bits and the parity bit are added to

the data frame. Figure 5 illustrates the timing and the mapping of the data payload into the 30-bit frame and how

the frame becomes split over the three output channels. The internal high speed clock is divided back down by a

factor of 10 to recreate the pixel clock and presented on SubLVDS CLK output. While in this mode, the PLL can

lock to a clock in the range of 20 MHz through 65 MHz. The 3-channel mode supports applications with very

large display resolutions such as VGA or XGA.

Figure 5. Data and Clock Output in 3-Channel Mode (LS0 = low; LS1 = high).

Powerdown Modes

The SN65LVDS301 Transmitter has two powerdown modes to facilitate efficient power management.

Shutdown Mode

The SN65LVDS301 enters Shutdown mode when the TXEN pin is asserted low. This turns off all transmitter

circuitry, including the CMOS input, PLL, serializer, and SubLVDS transmitter output stage. All outputs are

high-impedance. Current consumption in Shutdown mode is nearly zero.

Standby Mode

The SN65LVDS301 enters the Standby mode if TXEN is high and the PCLK input signal frequency is less than

500kHz. All circuitry except the PCLK input monitor is shut down, and all outputs enter high-impedance mode.

The current consumption in Standby mode is very low. When the PCLK input signal is completely stopped, the

IDDcurrent consumption is less than 10 µ A. The PCLK input must not be left floating.

NOTE:

A floating (left open) CMOS input allows leakage currents to flow from V

To prevent large leakage current, a CMOS gate must be kept at a valid logic level,

either V

or VIL. This can be achieved by applying an external voltage of V

IH

all SN65LVDS301 inputs.

to GND.

DD

or V

IH

to

IL

Submit Documentation Feedback

7

www.ti.com

Standby

Mode

Transmit

Mode

Acquire

Mode

TXENHigh>10 sm

PowerUp

TXEN=0

PowerUp

TXEN=1

CLK Active

PLL AchievedLock

Shutdown

Mode

TXENLow

>10 sm

TXENLow

>10 sm

TXENLow

>10 sm

PCLK

StopsorLost

PCLK

StopsorLost

PCLK

Active

PowerUp

TXEN=1

CLKInactive

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Active Modes

When TXEN is high and the PCLK input clock signal is faster than 3 MHz, the SN65LVDS301 enters Active

mode. Current consumption in Active mode depends on operating frequency and the number of data transitions

in the data payload.

Acquire Mode (PLL approaches lock)

The PLL is enabled and attempts to lock to the input Clock. All outputs remain in high-impedance mode. When

the PLL monitor detects stable PLL operation, the device switches from Acquire to Transmit mode. For proper

device operation, the pixel clock frequency must fall within the valid f

operating conditions. If the pixel clock frequency is larger than 3 MHz but smaller than f

SN65LVDS301 PLL is enabled. Under such conditions, it is possible for the PLL to lock temporarily to the pixel

clock, causing the PLL monitor to release the device into transmit mode. If this happens, the PLL may or may

not be properly locked to the pixel clock input, potentially causing data errors, frequency oscillation, and PLL

deadlock (loss of VCO oscillation).

Transmit Mode

After the PLL achieves lock, the device enters the normal transmit mode. The CLK pin outputs a copy of PCLK.

Based on the selected mode of operation, the D0, D1, and D2 outputs carry the serialized data. In 1-channel

mode, outputs D1 and D2 remain high-impedance. In the 2-channel mode, output D2 remains high-impedance.

Parity Bit Generation

The SN65LVDS301 transmitter calculates the parity of the transmit data word and sets the parity bit accordingly.

The parity bit covers the 27 bit data payload consisting of 24 bits of pixel data plus VS, HS and DE. The two

reserved bits are not included in the parity generation. ODD Parity bit signaling is used. The transmitter sets the

Parity bit if the sum of the 27 data bits result in an even number of ones. The Parity bit is cleared otherwise. This

allows the receiver to verify Parity and detect single bit errors.

PCLK

range specified under recommended

(min), the

PCLK

Status Detect and Operating Modes Flow diagram

The SN65LVDS301 switches between the power saving and active modes in the following way:

8

Figure 6. Status Detect and Operating Modes Flow Diagram

Submit Documentation Feedback

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Table 3. Status Detect and Operating Modes Descriptions

Mode Characteristics Conditions

Shutdown Mode Least amount of power consumption

off); All outputs are high-impedance

Standby Mode Low power consumption (only clock activity circuit active; PLL TXEN is high; PCLK input signal is missing or

is disabled to conserve power); All outputs are inactive

high-impedance

Acquire Mode PLL tries to achieve lock; All outputs are high-impedance TXEN is high; PCLK input monitor detected input

Transmit Mode Data transfer (normal operation); Transmitter serializes data TXEN is high and PLL is locked to incoming clock

and transmits data on serial output; unused outputs remain

high-impedance

(1) In Shutdown Mode, all SN65LVDS301 internal switching circuits (e.g., PLL, serializer, etc.) are turned off to minimize power

consumption. The input stage of any input pin remains active.

(2) Leaving inputs unconnected can cause random noise to toggle the input stage and potentially harm the device. All inputs must be tied to

a valid logic level VILor VIHduring Shutdown or Standby Mode.

(1)

(most circuitry turned TXEN is low

activity

Operating Mode Transitions

MODE TRANSITION USE CASE TRANSITION SPECIFICS

Shutdown → Standby Drive TXEN high to enable 1. TXEN high > 10 µ s

Standby → Acquire Transmitter activity detected 1. PCLK input monitor detects clock input activity;

Acquire → Transmit Link is ready to transfer data 1. PLL is active and approaches lock

Transmit → Standby Request Transmitter to enter 1. PCLK Input monitor detects missing PCLK

Transmit/Standby → Turn off Transmitter 1. TXEN pulled low for longer than 10us

Shutdown

transmitter

Standby mode by stopping

PCLK

2. Transmitter enters standby mode

a. All outputs are high-impedance

b. Transmitter turns on clock input monitor

2. Outputs remain high-impedance;

3. PLL circuit is enabled

2. PLL achieved lock within 2 ms

3. Parallel Data input latches into shift register

4. CLK output turns on

5. selected Data outputs turn on and send out first serial data bit

2. Transmitter indicates standby, putting all outputs into high-impedance;

3. PLL shuts down;

4. PCLK activity input monitor remains active

2. Transmitter indicates standby, putting output CLK+ and CLK– into

high-impedance state;

3. Transmitter puts all other outputs into high-impedance state

4. Most IC circuitry is shut down for least power consumption

(1) (2)

(2)

Submit Documentation Feedback

9

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

PART NUMBER PACKAGE SHIPPING METHOD

SN65LVDS301ZQE Tray

SN65LVDS301ZQER Reel

ORDERING INFORMATION

ZQE

ABSOLUTE MAXIMUM RATINGS

(1)

over operating free-air temperature range (unless otherwise noted)

VALUE UNIT

Supply voltage range, V

Voltage range at any input When V

or output terminal

Electrostatic discharge Charged-Device Mode

DD

(2)

, V

When V

Human Body Model

Machine Model

, V

DDPLLA

DDx

DDx

, V

DDPLLD

DDLVDS

> 0 V -0.5 to 2.175 V

≤ 0 V -0.5 to V

(3)

(all Pins) ± 3 kV

(4)

l (all Pins) ± 500 V

(5)

(all pins) ± 200

-0.3 to 2.175 V

+ 2.175 V

DD

Continuous power dissipation See Dissipation Rating Table

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the GND terminals.

(3) In accordance with JEDEC Standard 22, Test Method A114-A.

(4) In accordance with JEDEC Standard 22, Test Method C101.

(5) In accordance with JEDEC Standard 22, Test Method A115-A

DISSIPATION RATINGS

PACKAGE TA< 25 ° C

ZQE Low-K

CIRCUIT DERATING FACTOR

BOARD MODEL ABOVE TA= 25 ° C POWER RATING

(2)

592 mW 7.407 mW/ ° C 148 mW

(1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

(2) In accordance with the Low-K thermal metric definitions of EIA/JESD51-2.

(1)

TA= 85 ° C

THERMAL CHARACTERISTICS

PARAMETER TEST CONDITIONS VALUE UNIT

Typical V

P

Device Power Dissipation

D

Maximum V

10

= 1.8 V, TA= 25 ° C mW

DDx

= 1.95 V, TA= –40 ° C mW

DDx

Submit Documentation Feedback

PCLK at 4 MHz 14.4

PCLK at 65 MHz 44.5

PCLK at 4 MHz 22.3

PCLK=65 MHz 71.8

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

RECOMMENDED OPERATING CONDITIONS

V

DD

V

DDPLLA

V

DDPLLD

V

DDLVDS

V

DDn(PP)

f

PCLK

tHx f

PCLK

T

A

t

jit(per)PCLK

t

jit(TJ)PCLK

t

jit(CC)PCLK

PCLK, R[0:7], G[0:7], B[0:7], VS, HS, DE, PCLK, LS[1:0], CPOL, TXEN, SWAP

V

IH

V

IL

t

DS

t

DH

(1) Unused single-ended inputs must be held high or low to prevent them from floating.

(2) PCLK input frequencies lower than 500 kHz force the SN65LVDS301into standby mode. Input frequencies between 500 kHz and 3 MHz

may or may not activate the SN65LVDS301. Input frequencies beyond 3 MHz activate the SN65LVDS301.

(3) Period jitter is the deviation in cycle time of a signal with respect to the ideal period over a random sample of 100,000 cycles.

(4) Cycle-to-cycle jitter is the variation in cycle time of a signal between adjacent cycles; over a random sample of 1,000 adjacent cycle

pairs.

Supply voltages 1.65 1.8 1.95 V

Test set-up see Figure 12

Supply voltage noise

magnitude 50 MHz (all mV

supplies)

f(PCLK) ≤ 50 MHz; f(noise) = 1 Hz to 2 GHz 100

f(PCLK) > 50 MHz; f(noise) = 1 Hz to 1 MHz 100

f(PCLK) > 50 MHz; f(noise) > 1 MHz 40

1-Channel transmit mode, see Figure 3 4 15

2-Channel transmit mode, see Figure 4 8 30

Pixel clock frequency MHz

3-Channel transmit mode, see Figure 5 20 65

Frequency threshold Standby mode to active 0.5 3

(2)

mode

, see Figure 16

PCLK input duty cycle 0.33 0.67

Operating free-air –40 85 ° C

temperature

PCLK RMS period jitter

PCLK total jitter 0.05/f

PCLK peak 0.02/f

cycle-to-cycle jitter

(3)

Measured on PCLK input

(4)

High-level input voltage 0.7 × V

Low-level input voltage 0.3 × V

Data set up time prior to 2.0 ns

PCLK transition

Data hold time after PCLK 2.0 ns

f (PCLK) = 65 MHz; see Figure 8

transition

(1)

MIN NOM MAX UNIT

5 ps-rms

PCLK

PCLK

DD

V

DD

DD

s

s

V

V

Submit Documentation Feedback

11

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

DEVICE ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAM TEST CONDITIONS MIN TYP

ETER

V

=V

DD

R

L(PCLK)

TXEN at VDD,

1ChM

alternating 1010 serial bit pattern

V

=V

DD

R

L(PCLK)

TXEN at VDD,

typical power test pattern (see Table 5 )

V

=V

DD

R

L(PCLK)

TXEN at VDD,

2ChM

I

DD

3ChM

alternating 1010 serial bit pattern;

V

=V

DD

R

L(PCLK)

TXEN at VDD,

typical power test pattern (see Table 6 )

V

=V

DD

R

L(PCLK)

TXEN at VDD,

alternating 1010 serial bit pattern

V

=V

DD

R

L(PCLK)

TXEN at VDD,

typical power test pattern (see Table 7 )

Standby Mode V

Shutdown Mode 0.55 10 µ A

(1) All typical values are at 25 ° C and with 1.8 V supply unless otherwise noted.

=V

DDPLLA

=R

L(D0)

=V

DDPLLA

=R

L(D0)

=V

DDPLLA

=R

L(D0)

=V

DDPLLA

=R

L(D0)

=V

DDPLLA

=R

L(D0)

=V

DDPLLA

=R

L(D0)

DDPLLD

=100 Ω , VIH=V

DDPLLD

=100 Ω , VIH=V

DDPLLD

=100 Ω , VIH=V

DDPLLD

=100 Ω , VIH=V

DDPLLD

=100 Ω , VIH=V

DDPLLD

=100 Ω , VIH=V

=V

=V

=V

=V

=V

=V

DDLVDS

, VIL=0 V,

DD

DDLVDS

, VIL=0 V,

DD

DDLVDS

, VIL=0 V,

DD

DDLVDS

, VIL=0 V,

DD

DDLVDS

, VIL=0 V,

DD

DDLVDS

, VIL=0 V,

DD

, f

, f

, f

, f

, f

, f

= 4 MHz 9.0 11.4

PCLK

f

= 6 MHz 10.6 12.6

PCLK

f

= 15 MHz 16 18.8

PCLK

= 4 MHz 8.0

PCLK

f

= 6 MHz 8.9

PCLK

f

= 15 MHz 14.0

PCLK

= 8 MHz 13.7 15.9

PCLK

f

= 22 MHz 18.4 22.0

PCLK

f

= 30 MHz 21.4 25.8

PCLK

= 8 MHz 11.5

PCLK

f

= 22 MHz 16.0

PCLK

f

= 30 MHz 19.1

PCLK

= 20 MHz 20.0 22.5

PCLK

f

= 65 MHz

PCLK

= 20 MHz 15.9

PCLK

f

= 65 MHz

PCLK

= V

DD

= V

DDLVDS

R

L(PCLK)

VIH=V

DD

inputs held static high or

DDPLLA

,

=R

L(D0)

, VIL=0 V, all

= V

DDPLLD

=100 Ω ,

static low

(1)

MAX UNIT

29.1 36.8

24.7

0.61 10 µ A

mA

mA

mA

mA

mA

mA

OUTPUT ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP

subLVDS output (D0+, D0–, D1+, D1–, D2+, D1–, CLK+, and CLK–)

V

OC(SS)M

V

OCM(SS)

V

OCM(PP)

|V

OD

∆ |V

Z

OD(CLK)

I

OSD

I

OS

I

OZ

(1) All typical values are at 25 ° C and with 1.8 V supply unless otherwise noted.

(2) All SN65LVDS301 outputs tolerate shorts to GND or V

12

Steady-state common-mode output voltage Output load see Figure 10 0.8 0.9 1.0 V

Change in steady-state common-mode output voltage –10 10 mV

Peak-to-peak common mode output voltage 75 mV

| Differential output voltage magnitude 100 150 200

|V

– V

|, |V

– V

Dx+

Dx–

CLK+

| Change in differential output voltage between logic states –10 10 mV

OD

Differential small-signal output impedance TXEN at V

Differential short-circuit output current V

Short circuit output current

CLK–

|

DD

= 0 V, f

(2)

OD

VO= 0 V or V

= 28 MHz 10

PCLK

DD

High-impedance state output current VO= 0 V or VDD(max), –3 3

TXEN at GND

without permanent device damage.

DD

Submit Documentation Feedback

(1)

MAX UNIT

210 Ω

5

mV

mA

µ A

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

INPUT ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP

PCLK, R[0:7], G[0:7], B[0:7], VS, HS, DE, PCLK, LS[1:0], CPOL, TXEN, SWAP

I

High-level input current VIN= 0.7 × V

IH

I

Low-level input current VIN= 0.3 × V

IL

C

Input capacitance 1.5 pF

IN

DD

DD

–200 200

–200 200

(1) All typical values are at 25 ° C and with 1.8 V supply unless otherwise noted.

SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP

t

r

t

f

f

BW

t

pd(L)

tH× f

CLK0

t

GS

t

pwrup

t

pwrdn

t

wakup

t

sleep

(1) All typical values are at 25 ° C and with 1.8 V supply unless otherwise noted.

(2) The Maximum Limit is based on statistical analysis of the device performance over process, voltage, and temp ranges. This parameter

(3) The TXEN input incorporates glitch-suppression circuitry to disregard short input pulses. tGSis the duration of either a high-to-low or

20%-to-80% differential See Figure 9 and Figure 10 250 500

output signal rise time

20%-to-80% differential See Figure 9 and Figure 10 250 500

output signal fall time

PLL bandwidth (3dB cutoff

frequency)

Tested from PCLK input to f

CLK output, See Figure 7

Propagation delay time, TXEN at VDD, VIH=V

input to serial output (data VIL=GND, RL=100 Ω

latency Figure 11 )

(2)

, 1-channel mode 0.8/f

DD

= 22 MHz 0.082 × f

PCLK

f

= 65 MHz 0.07 × f

PCLK

1/f

1.21/f

1.31/f

2-channel mode 1.0/f

3-channel mode 1.1/f

PCLK

PCLK

PCLK

Output CLK duty cycle 1-channel and 3-channel 0.45 0.50 0.55

mode

2-channel mode 0.49 0.53 0.58

TXEN Glitch suppression VIH=V

pulse width

(3)

, VIL=GND, TXEN toggles between VILand VIH, 3.8 10

DD

see Figure 14 and Figure 15

Enable time from power Time from TXEN pulled high to CLK and Dx outputs 0.24 2

down ( ↑ TXEN) enabled and transmit valid data; see Figure 15

Disable time from active TXEN is pulled low during transmit mode; time 0.5 11

mode ( ↓ TXEN) measurement until output is disabled and PLL is µ s

Shutdown; see Figure 15

Enable time from Standby TXEN at VDD; device in standby; time measurement from 0.23 2

( ↕ PCLK) PCLK starts switching to CLK and Dx outputs enabled and ms

transmit valid data; see Figure 15

Disable time from Active TXEN at VDD; device is transmitting; time measurement 0.4 100

mode (PCLK stopping) from PCLK input signal stops until CLK + Dx outputs are µ s

disabled and PLL is disabled; see Figure 15

is functionality tested only on Automatic Test Equipment (ATE).

low-to-high transition that is suppressed.

(1)

MAX UNIT

(1)

PCLK

PCLK

PCLK

MAX UNIT

PCLK

PCLK

1.2/f

PCLK

1.5/f

PCLK

1.6/f

PCLK

nA

ps

MHz

s

µ s

ms

Submit Documentation Feedback

13

www.ti.com

PLL frequency − MHz

4.0%

5.0%

6.0%

7.0%

8.0%

9.0%

10.0%

11.0%

12.0%

0 100 200 300 400 500 600 700

PLL BW[%ofPCLKFrequency]

9%

8.5%

7%

7.5%

RXPLL BW

TXPLL BW

0 40 50 60 7010 20 30

PCLKFREQUENCY -MHz

PLL BANDWIDTH-%

6.0

6.5

7.0

7.5

8.0

8.5

9.0

65MHz:

7.0%

4MHz:

8.5%

15MHz:

7.6%

SpecLimit3ChM

30MHz:

7.6%

Spec

Limit

2ChM

SpecLimit

1ChM

8MHz:

8.5%

20MHz:

8.3%

ps330

f30

x

PCLK

-

×

ps330

f30

x

PCLK

+

×

PCLK

x – 0.1845

f30 ×

PCLK

f30

x 0.1845+

×

ps330

f15

x

PCLK

-

×

ps330

f15

x

PCLK

+

×

PCLK

x – 0.1845

f15 ×

PCLK

x+0.1845

f15 ×

ps210

f10

x

PCLK

-

×

ps210

f10

x

PCLK

+

×

PCLK

f10

x 0.153-

×

PCLK

f10

x 0.153+

×

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Figure 7. LVDS301 PLL Bandwidth (also showing the LVDS302 PLL bandwidth)

TIMING CHARACTERISTICS

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

1ChM: x=0..29, f

VDD, VIH=V

pattern as in Table 10

1ChM: x=0..29,

f

=4 MHz to 15 MHz

PCLK

=15 MHz; TXEN at

PCLK

, VIL=GND, RL=100 Ω , test

DD

(3)

(4)

t

PPOSX

(1) This number also includes the high-frequency random and deterministic PLL clock jitter that is not traceable by the SN65LVDS302

(2) The pulse position min/max variation is given with a bit error rate target of 10

(3) The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temp ranges.

(4) These Minimum and Maximum Limits are simulated only.

14

2ChM: x = 0..14, f

Output Pulse Position,

serial data to ↑ CLK; see ps

and Figure 13

TXEN at VDD, VIH=V

RL=100 Ω , test pattern as in Table 11

2ChM: x=0..14,(1) (2)

f

= 8 MHz to 30 MHz

PCLK

3ChM: x=0..9, f

TXEN at VDD, VIH=V

RL=100 Ω , test pattern as in Table 12

3ChM: x=0..9,

f

=20 MHz to 65 MHz

PCLK

= 30 MHz

PCLK

, VIL=GND,

DD

(4)

=65 MHz,

PCLK

, VIL=GND,

DD

(4)

(3)

(3)

receiver PLL; tPPosx represents the total timing uncertainty of the transmitter necessary to calculate the jitter budget when combined

with the SN65LVDS302 receiver;

contribution to the total jitter contribution by multiplying the random RMS jitter by the factor 14; Measurements of the total jitter are taken

over a sample amount of > 10

–12

samples.

–12

; The measurement estimates the random jitter

This parameter is functionality tested only on Automatic Test Equipment (ATE).

Submit Documentation Feedback

www.ti.com

PARAMETER MEASUREMENT INFORMATION

R[7:0],G[7:0],B[7:0];

VS,HS,DE,LS0,LS1,

TXEN,SWAP,CPOL

PCLK

(CPOL=low)

t

DS

t

DH

t

R

V

IH

V

IL

V

IH

V

IL

0 V

20%

80%

150mV (nom)

−150mV (nom)

t

f

t

r

V

OD

SN65LVDS301

CLK−,Dx−

CLK+,Dx+

975mV(nom)

825mV(nom)

R1=49.9

R2=49.9

C2=1pFC1=1pF

V

OD

V

Dx+

orV

CLK+

V

Dx−

orV

CLK−

V

OCM

V

OCM

V

OCM

(pp) V

OCM

(ss)

NOTES:

A.20MHzoutputtestpatternonalldifferentaloutputs(CLK,D0,D1,andD2):

thisisachievedby: 1.Deviceissetto3-channel-mode;

2.f

PCLK

=20MHz

3.InputsR[7:3]=B[7:3]connectedtoV ,allotherdatainputssettoGND.

DD

B.C1,C2andC3includesinstrumentationandfixturecapacitance;tolerance± 20%;C,R1andR2tolerance± 1%.

C. ThemeasurementofV

OCM

(pp)andVOC(ss)aretakenwithtestequipmentbandwidth>1GHz.

Figure 8. Setup/Hold Time

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Figure 9. Rise and Fall Time Definitions

Figure 10. Driver Output Voltage Test Circuit and Definitions

Submit Documentation Feedback

15

www.ti.com

R6

(n)

R7

(n−1)

R7

R6

R7

D0+

CLK+

CLK−

CMOS

DataIn

PCLK

R6

CP CP

pixel

(n)

pixel

(n+1)

R7

(n)

R7

(n+1)

R6

(n+1)

R6

(n−1)

t

PROP

VDD/2

R6

(n−1)

R7

(n−1)

pixel

(n−2)

pixel

(n−1)

R6

(n)

R7

(n)

Note: Thegeneratorregulatesthe

noiseamplitudeatpointtothe

targetamplitudegivenunderthetable

RecommendedOperatingConditions

Noise

Generator

100mV

SN65LVDS301

V

DDPLLA

1.8V

supply

V

DDPLLD

V

DD

V

DDLVDS

GND

1.6 H

10 Fm

21

1

1

CLK+

Bit 0 Bit1 Bit2 Bitx Bit0

Bit1

Note:

1−channel mode: x=0..29; m=0

2−channel mode: x=0..14; m=1

3−channel mode: x=0....9; m=2

CLK−

t

CLK+

Current Cycle

Next Cycle

t

PPOS0

t

PPOS1

t

PPOS2

t

PPOSx

D[0:m]+

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

PARAMETER MEASUREMENT INFORMATION (continued)

Figure 11. t

Propagation Delay Input to Output (LS0 = LS1 = 0; CPOL = 0)

pd(L)

Figure 12. Power Supply Noise Test Set-Up

16

Figure 13. t

SK(0)

SubLVDS Output Pulse Position Measurement

Submit Documentation Feedback

www.ti.com

TXEN

PCLK

CLK

D0,D1,D2

t

GS

VDD/2

PLL ApproachesLock

t

pwr up

VCOInternalSignal

CLK+

PCLK

t

wakeup

t

sleep

TransmitterDisabled

(OFF)

Transmitter AquiresLock,

OutputsStillDisabled

TransmitterEnabled,

OutputDataValid

Transmitter

Enabled,

OutputData

Valid

Transmitter

Disabled

(OFF)

PARAMETER MEASUREMENT INFORMATION (continued)

Figure 14. Transmitter Behavior While Approaching Sync

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Figure 15. Transmitter Enable Glitch Suppression Time

Figure 16. Standby Detection

Submit Documentation Feedback

17

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

PARAMETER MEASUREMENT INFORMATION (continued)

Power Consumption Tests

Table 4 shows an example test pattern word.

Table 4. Example Test Pattern Word

Word R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x7C3E1E7

7 C 3 E 1 E 7

R7 R6 R5 R4 R3 R2 R1 R0 G7 G6 G5 G4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0 0 VS HS DE

0 1 1 1 1 1 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 1

Typical IC Power Consumption Test Pattern

The typical power consumption test patterns consists of sixteen 30-bit transmit words in 1-channel mode, eight

30-bit transmit words in 2-channel mode and five 30-bit transmit words in 3-channel mode. The pattern repeats

itself throughout the entire measurement. It is assumed that every possible transmit code on RGB inputs has the

same probability to occur during typical device operation.

Table 5. Typical IC Power Consumption Test Pattern,

1-Channel Mode

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x0000007

2 0xFFF0007

3 0x01FFF47

4 0xF0E07F7

5 0x7C3E1E7

6 0xE707C37

7 0xE1CE6C7

8 0xF1B9237

9 0x91BB347

10 0xD4CCC67

11 0xAD53377

12 0xACB2207

13 0xAAB2697

14 0x5556957

15 0xAAAAAB3

16 0xAAAAAA5

18

Submit Documentation Feedback

www.ti.com

Table 6. Typical IC Power Consumption Test Pattern,

2-Channel Mode

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x0000001

2 0x03F03F1

3 0xBFFBFF1

4 0x1D71D71

5 0x4C74C71

6 0xC45C451

7 0xA3aA3A5

8 0x5555553

Table 7. Typical IC Power Consumption Test Pattern,

3-Channel Mode

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0xFFFFFF1

2 0x0000001

3 0xF0F0F01

4 0xCCCCCC1

5 0xAAAAAA7

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Maximum Power Consumption Test Pattern

The maximum (or worst-case) power consumption of the SN65LVDS301 is tested using the two different test

patterns shown in Table 8 and Table 9 . The test patterns consist of sixteen 30-bit transmit words in 1-channel

mode, eight 30-bit transmit words in 2-channel mode and five 30-bit transmit words in 3-channel mode. The

pattern repeats itself throughout the entire measurement. It is assumed that every possible transmit code on

RGB inputs has the same probability to occur during typical device operation.

Table 8. Worst-Case Power Consumption Test Pattern

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0xAAAAAA5

2 0x5555555

Table 9. Worst-Case Power Consumption Test Pattern

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x0000000

2 0xFFFFFF7

Submit Documentation Feedback

19

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Output Skew Pulse Position & Jitter Performance

The following test patterns are used to measure the output-skew pulse position and the jitter performance of the

SN65LVDS301. The jitter test pattern stresses the interconnect, particularly to test for ISI. Very long run-lengths

of consecutive bits incorporate very high and low data rates, maximinges switching noise. Each pattern is

self-repeating for the duration of the test.

Table 10. Transmit Jitter Test Pattern, 1-Channel Mode

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x0000001

2 0x0000031

3 0x00000F1

4 0x00003F1

5 0x0000FF1

6 0x0003FF1

7 0x000FFF1

8 0x0F0F0F1

9 0x0C30C31

10 0x0842111

11 0x1C71C71

12 0x18C6311

13 0x1111111

14 0x3333331

15 0x2452413

16 0x22A2A25

17 0x5555553

18 0xDB6DB65

19 0xCCCCCC1

20 0xEEEEEE1

21 0xE739CE1

22 0xE38E381

23 0xF7BDEE1

24 0xF3CF3C1

25 0xF0F0F01

26 0xFFF0001

27 0xFFFC001

28 0xFFFF001

29 0xFFFFC01

30 0xFFFFF01

31 0xFFFFFC1

32 0xFFFFFF1

20

Submit Documentation Feedback

www.ti.com

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Table 11. Transmit Jitter Test Pattern, 2-Channel Mode

Word Test Pattern:

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

1 0x0000001

2 0x000FFF3

3 0x8008001

4 0x0030037

5 0xE00E001

6 0x00FF001

7 0x007E001

8 0x003C001

9 0x0018001

10 0x1C7E381

11 0x3333331

12 0x555AAA5

13 0x6DBDB61

14 0x7777771

15 0x555AAA3

16 0xAAAAAA5

17 0x5555553

18 0xAAA5555

19 0x8888881

20 0x9242491

21 0xAAA5571

22 0xCCCCCC1

23 0xE3E1C71

24 0xFFE7FF1

25 0xFFC3FF1

26 0xFF81FF1

27 0xFE00FF1

28 0x1FF1FF1

29 0xFFCFFC3

30 0x7FF7FF1

31 0xFFF0007

32 0xFFFFFF1

SN65LVDS301

Submit Documentation Feedback

21

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Table 12. Transmit Jitter Test Pattern, 3-Channel Mode

Word Test Pattern:

1 0x0000001

2 0x0000001

3 0x0000003

4 0x0101013

5 0x0303033

6 0x0707073

7 0x1818183

8 0xE7E7E71

9 0x3535351

10 0x0202021

11 0x5454543

12 0xA5A5A51

13 0xADADAD1

14 0x5555551

15 0xA6A2AA3

16 0xA6A2AA5

17 0x5555553

18 0x5555555

19 0xAAAAAA1

20 0x5252521

21 0x5A5A5A1

22 0xABABAB1

23 0xFDFCFD1

24 0xCAAACA1

25 0x1818181

26 0xE7E7E71

27 0xF8F8F81

28 0xFCFCFC1

29 0xFEFEFE1

30 0xFFFFFF1

31 0xFFFFFF5

32 0xFFFFFF5

R[7:4], R[3:0], G[7:4], G[3:0], B[7-4], B[3-0], 0,VS,HS,DE

22

Submit Documentation Feedback

www.ti.com

0.1

1.0

-50 -30 -10 10 30 50 70 90

Temperature-°C

IDDQ- Am

Power-DownCurrent

Standby Current

0

20

-50 -30 -10 10 30 50 70 90

Temperature-°C

IDD-mA

5

10

15

2-ChannelMode,11MHz(HVGA)

2-ChannelMode,22MHz(VGA)

5

10

15

20

25

30

0 40 50 60 7010 20 30

FREQUENCY -MHz

IDD-mA

1-ChannelMode

2-ChannelMode

3-ChannelMode

0 40 50 60 7010 20 30

FREQUENCY -MHz

100

110

120

130

140

150

160

170

180

190

200

DifferentialOutputSwingVOD-mV

–40°C

25°C

85°C

0 40 50 60 7010 20 30

FREQUENCY -MHz

0

100

200

300

400

500

CCJITTER-ps

2-ChannelMode

1-ChannelMode

3-ChannelMode

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

TYPICAL CHARACTERISTICS

POWERDOWN, STANDBY SUPPLY CURRENT

vs TEMPERATURE SUPPLY CURRENT IDDvs TEMPERATURE

Figure 17. Figure 18.

SUPPLY CURRENT vs PCLK FREQUENCY DIFFERENTIAL OUTPUT SWING vs PCLK FREQUENCY

PLL BANDWIDTH vs PCLK FREQUENCY

Figure 19. Figure 20.

CYCLE-TO-CYCLE OUTPUT JITTER

Figure 21. Figure 22.

Submit Documentation Feedback

23

www.ti.com

-50 -25 0 25 50 75 100

0

20

40

60

80

100

120

OUTPUTPULSEPOSITION(t )-PS

PPOS

2-ChannelMode,

22MHz(HVGA)

2-ChannelMode,

11MHz(VGA)

TEMPERATURE-°C

-50 -25 0 25 50 75 100

Temperature-°C

0

50

100

150

200

CCJITTER-ps

2-ChannelMode,

f(PCLK)=22MHz

2-ChannelMode,

f(PCLK)=11MHz

–251

–190

0

190

249

ResponseOver80-inchofFR-4+1mCoaxCable

1ns/div

1-ChannelMode,

f(PCLK)=5.5MHz

OutputVoltage Amplitude-mV

–250

–190

0

190

250

ResponseOver8-inchFR-4+1mCoaxCable

500ps/div

2-ChannelMode,

f(PCLK)=22MHz

OutputVoltage Amplitude-mV

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

TYPICAL CHARACTERISTICS (continued)

CYCLE-TO-CYCLE OUTPUT JITTER

vs TEMPERATURE OUTPUT PULSE POSITION vs TEMPERATURE

Figure 23. Figure 24.

DATA EYE PATTERN, 2-CHANNEL MODE DATA EYE PATTERN, 3-CHANNEL MODE

QVGA OUTPUT WAVEFORM VGA 2-CHANNEL OUTPUT WAVEFORM

24

Figure 25. Figure 26.

Figure 27. Figure 28.

Submit Documentation Feedback

www.ti.com

–251

–190

0

190

249

ResponseOver80-inchFR-4+1mCoaxCable

500ps/div

2-ChannelMode,

f(PCLK)=22MHz

OutputVoltage Amplitude-mV

–251

–190

0

190

249

OutputVoltage Amplitude-mV

ResponseOver80-inchFR-4+1mCoaxCable

1ns/div

3-ChannelMode,

f(PCLK)=22MHz

–251

–190

0

190

249

OutputVoltage Amplitude-mV

ResponseOver80-inchFR-4+1mCoaxCable

300ps/div

3-ChannelMode,

f(PCLK)=56MHz

OutputVoltage Amplitude-mV

400mV/div

ResponseWith10-pFLoad

3.5ns/div

3-ChannelMode,

f(PCLK)=56MHz

f(PCLK)=65MHz

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

-170

-180

1

10 100

1k

10k 100k

1M

10M

dBc/Hz

FREQUENCY -Hz

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

TYPICAL CHARACTERISTICS (continued)

VGA 2-CHANNEL OUTPUT WAVEFORM VGA3-CHANNEL OUTPUT WAVEFORM

Figure 29. Figure 30.

SN65LVDS301

XGA 3-CHANNEL OUTPUT WAVEFORM SN65LVDS302 WHEN DRIVEN BY THE SN65LVDS301

XGA 3-CHANNEL OUTPUT WAVEFORM ON THE

Figure 31. Figure 32.

PLL PHASE NOISE OUTPUT RETURN LOSS

Figure 33. Figure 34.

Submit Documentation Feedback

25

www.ti.com

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

OUTPUT COMMON MODE NOISE REJECTION CROSSTALK

Figure 35. Figure 36.

TYPICAL CHARACTERISTICS (continued)

GTEM SAE J1752/3 EMI TEST

(A)

Figure 37.

A. Figure 37 shows a superimposed image of three EMI measurements with the device operating at f(PCLK) = 5 MHz,

f(PCLK) = 22 MHz, and f(PCLK) = 65 MHz. This excellent EMI performance meets the system requirements of

dense, mobile designs with a noise floor of ~2 dBµV (-105 dBm) and all spurs being smaller than 16 dBµV (-101

dBm). The test was performed in compliance with the SAE J1752/3 EMI test guidelines.

26

Submit Documentation Feedback

www.ti.com

SPI

RESET

22MHz

27

PCLK

R[7:0]

G[7:0]

B[7:0]

HS,VS,DE

D[7:0]

D[15:8]

D[23:16]

HS,VS,DE

PixelCLK

VDDx

GND

2x0.01uF

2x0.1uF

LS0

LS1

TXEN

1.8V

VDDx

GND

2x0.01uF

2x0.1uF

LS0

LS1

RXEN

1.8V

D0+

D0-

CLK+

CLK-

D1+

D1-

D0+

D0-

CLK+

CLK-

D1+

D1-

GND

1.8V

2.7V

GND

1.8V

2.7V

GND GND

LCD w ith VGA

resolution

22MHz

27

PCLK

R[7:0]

G[7:0]

B[7:0]

HS,VS,DE

SPI

Serialportinterface

(3-wireIF)

3

Application

Processor

(e.g. OMAP)

SN65LVDS301

SN65LVDS302

VideoModeDisplay

Driver

FPC

22MHz

330Mbps

330Mbps

ENABLE

IfFPCwirecountiscritical, replacethis

connectionwithapull-upresistoratRXEN

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

APPLICATION INFORMATION

Preventing Increased Leakage Currents in Control Inputs

A floating (left open) CMOS input allows leakage currents to flow from V

Input unconnected or floating. Every input must be connected to a valid logic level V

supplied to V

. This also minimizes the power consumption of standby and power down mode.

DD

Power Supply Design Recommendation

For a multilayer pcb, it is recommended to keep one common GND layer underneath the device and connect all

ground terminals directly to this plane.

Decoupling Recommendation

The SN65LVDS301 was designed to operate reliably in a constricted environment with other digital switching

ICs. In cell phone designs, the SN65LVDS301 often shares a power supply with the application processor. The

SN65LVDS301 can operate with power supply noise as specified in Recommend Device Operating Conditions.

To minimize the power supply noise floor, provide good decoupling near the SN65LVDS301 power pins. The

use of four ceramic capacitors (2 × 0.01 µ F and 2 × 0.1 µ F) provides good performance. At the very least, it is

recommended to install one 0.1 µ F and one 0.01 µ F capacitor near the SN65LVDS301. To avoid large current

loops and trace inductance, the trace length between decoupling capacitor and IC power inputs pins must be

minimized. Placing the capacitor underneath the SN65LVDS301 on the bottom of the pcb is often a good choice.

to GND. Do not leave any CMOS

DD

or V

IH

while power is

OL

VGA Application

Figure 38 shows a possible implementation of a VGA display. The LVDS301 interfaces to the SN65LVDS302,

which is the corresponding receiver device to deserialize the data and drive the display driver. The pixel clock

rate of 22 MHz assumes ~10% blanking overhead and 60 Hz display refresh rate. The application assumes

24-bit color resolution. It is also shown, how the application processor provides a powerdown (reset) signal for

both serializer and the display driver. The signal count over the FPC could be further decreased by using the

standby option on the SN65LVDS302 and pulling RXEN high with a 30 k Ω resistor to V

Figure 38. Typical VGA Display Application

Submit Documentation Feedback

.

DD

27

www.ti.com

SCLK

5.5MHz

18+3

PCLK

R[5:0]

G[5:0]

B[5:0]

HS,VS,DE

D[5:0]

D[11:6]

D[17:12]

HS,VS,DE

PixelCLK

VDDx

GND

2x0.01uF

2x0.1uF

VDDx

GND

2x0.01uF

2x0.1uF

RXEN

D0+

D0-

CLK+

CLK-

D0+

D0-

CLK+

CLK-

GND

1.8V

2.7V

GND

1.8V

2.7V

GND GND

LCD with QVGA

resolution

21

R[5:0]

G[5:0]

B[5:0]

HS,VS,DE

SCLK

Application

Processor

(e.g. OMAP)

SN65LVDS301 SN65LVDS302

DisplayDriver2

FPC

5.5MHz

330Mbps

SIN

LCD with QVGA

resolution

DisplayDriver1

1.8V

LS0

LS1

TXEN

1.8V

LS0

LS1

SIN

SOUT

SEL2

SEL1

SOUT

EN

SCLK

SOUT

EN

SIN

PCLKPCLK

PCLK

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

APPLICATION INFORMATION (continued)

Dual LCD-Display Application

The example in Figure 39 shows a possible application setup driving two video mode displays from one

application processor. The data rate of 330 Mbps at a pixel clock rate of 5.5 MHz corresponds to QVGA

resolution at 60 Hz refresh rate and 10% blanking overhead.

Figure 39. Example Dual-QVGA Display Application

Typical Application Frequencies

The SN65LVDS301 supports pixel clock frequencies from 4 MHz to 65 MHz over 1, 2, or 3 data lanes. Table 13

provides a few typical display resolution examples and shows the number of data lanes necessary to connect

the LVDS301 with the display. The blanking overhead is assumed to be 20%. Often, blanking overhead is

smaller, resulting in a lower data rate. Furthermore, the examples in the table assumes a display frame refresh

rate of 60 Hz or 90 Hz. The actual refresh rate may differ depending on the application-processor clock

implementation.

Table 13. Typical Application Data Rates & Serial Lane Usage

Display Screen Visible Blanking Display Pixel Clock Frequency Serial Data Rate Per Lane

Resolution Pixel Count Overhead Refresh [MHz]

Rate

176x220 (QCIF+) 38,720 20% 90 Hz 4.2 MHz 125 Mbps

240x320 (QVGA) 76,800 60 Hz 5.5 MHz 166 Mbps

640x200 128,000 9.2 MHz 276 Mbps 138 Mbps

352x416 (CIF+) 146,432 10.5 MHz 316 Mbps 158 Mbps

352x440 154,880 11.2 MHz 335 Mbps 167 Mbps

320x480 (HVGA) 153,600 11.1 MHz 332 Mbps 166 Mbps

800x250 200,000 14.4 MHz 432 Mbps 216 Mbps

640x320 204,800 14.7 MHz 442 Mbps 221 Mbps

640x480 (VGA) 307,200 22.1 MHz 332 Mbps 221 Mbps

1024x320 327,680 23.6 MHz 354 Mbps 236 Mbps

854x480 (WVGA) 409,920 29.5 MHz 443 Mbps 295 Mbps

800x600 (SVGA) 480,000 34.6 MHz 346 Mbps

1024x768 (XGA) 786,432 56.6 MHz 566 Mbps

1-ChM 2-ChM 3-ChM

28

Submit Documentation Feedback

www.ti.com

Calculation Example: HVGA Display

Visiblearea=480column

Visiblearea

Entiredisplay

Vsync=5

VBP =3

Visiblearea

=320lines

VFP =10

Hsync=5

HFP =20

HBP

This example calculation shows a typical Half-VGA display with these parameters:

Display Resolution: 480 x 320

Frame Refresh Rate: 58.4 Hz

Horizontal Visible Pixel: 480 columns

Horizontal Front Porch: 20 columns

Horizontal Sync: 5 columns

Horizontal Back Porch: 3 columns

Vertical Visible Pixel: 320 lines

Vertical Front Porch: 10 lines

Vertical Sync: 5 lines

Vertical Back Porch: 3 lines

Calculation of the total number of pixel and Blanking overhead:

SN65LVDS301

SLLS681C – FEBRUARY 2006 – REVISED AUGUST 2006

Figure 40. HVGA Display Parameters

Visible Area Pixel Count: 480 × 320 = 153600 pixel

Total Frame Pixel Count: (480+20+5+3) × (320+10+5+3) = 171704 pixel

Blanking Overhead: (171704-153600) ÷ 153600 = 11.8 %

The application requires following serial-link parameters:

Pixel Clk Frequency: 171704 × 58.4 Hz = 10.0 MHz

Serial Data Rate: 1-channel mode: 10.0 MHz × 30 bit/channel = 300 Mbps

2-channel mode: 10.0 MHz × 15 bit/channel = 150 Mbps

Submit Documentation Feedback

29

PACKAGE OPTION ADDENDUM

www.ti.com

12-Sep-2006

PACKAGING INFORMATION

Orderable Device Status

SN65LVDS301ZQE ACTIVE BGA MI

(1)

Package

Type

CROSTA

Package

Drawing

Pins Package

Qty

Eco Plan

ZQE 80 360 Green (RoHS &

no Sb/Br)

R JUNI

OR

SN65LVDS301ZQER ACTIVE BGA MI

CROSTA

ZQE 80 2500 Green (RoHS &

no Sb/Br)

R JUNI

OR

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in

a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check

http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements

for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered

at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and

package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame

retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(2)

Lead/Ball Finish MSL Peak Temp

SNAGCU Level-3-260C-168 HR

SNAGCU Level-3-260C-168 HR

(3)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder

temperature.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the

accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on

incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited

information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI

to Customer on an annual basis.

Addendum-Page 1

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements,

improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.

Customers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s

standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this

warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily

performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should

provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask

work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services

are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such

products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under

the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is

accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an

unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties

may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service

voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business

practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would

reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement

specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications

of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related

requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any

applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its

representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is

solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in

connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products

are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any

non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Interface interface.ti.com Digital Control www.ti.com/digitalcontrol

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

Low Power www.ti.com/lpw Video & Imaging www.ti.com/video

Wireless

Wireless www.ti.com/wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated

Loading...

Loading...