SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Typically Meets or Exceeds ANSI

TIA/EIA-644-1995 Standard

D

Operates From a Single 2.4-V to 3.6-V

Supply

D

Signaling Rates up to 400 Mbit/s

D

Bus-T erminal ESD Exceeds 12 kV

D

Low-Voltage Differential Signaling With

Typical Output Voltages of 285 mV and a

100 Ω Load

D

Propagation Delay Times

– Driver: 1.7 ns Typ

– Receiver: 3.7 ns Typ

D

Power Dissipation at 200 MHz

– Driver: 25 mW Typical

– Receiver: 60 mW Typical

D

LVTTL Input Levels Are 5 V Tolerant

D

Driver Is High Impedance When Disabled or

With VCC < 1.5 V

D

Receiver Has Open-Circuit Fail Safe

D

Available in Thin Shink Outline Packaging

With 20-mil Lead Pitch

description

The SN65LVDS1050 is similar to the

SN65LVDS050 except that it is characterized for

operation with a lower supply voltage range and

packaged in the thin shrink outline package for

portable battery-powered applications.

The differential line drivers and receivers use

low-voltage differential signaling (LVDS) to

achieve signaling rates as high as 400 Mbps. The

drivers provide a minimum differential output

voltage magnitude of 247 mV into a 100-Ω load

and receipt of 100-mV signals with up to 1 V of

ground potential difference between a transmitter

and receiver.

The intended application of this device and signaling technique is for point-to-point baseband data transmission

over controlled impedance media of approximately 100-Ω characteristic impedance. The transmission media

may be printed-circuit board traces, backplanes, or cables. Note: The ultimate rate and distance of data transfer

is dependent upon the attenuation characteristics of the media, the noise coupling to the environment and other

application-specific characteristics.

The SN65LVDS1050 is characterized for operation from –40°C to 85°C.

Copyright 2000, Texas Instruments Incorporated

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

1B

1A

1R

RE

2R

2A

2B

GND

V

CC

1D

1Y

1Z

DE

2Z

2Y

2D

SN65LVDS1050PW

(Marked as DL1050 or DLS1050)

(TOP VIEW)

2D

1D

1Y

1Z

2Y

2Z

DE

9

15

12

14

13

10

11

2R

1R

1A

1B

2A

2B

RE

5

3

4

2

1

6

7

DRIVER FUNCTION TABLE

RECEIVER FUNCTION TABLE

INPUTS OUTPUTS

INPUTS OUTPUT

D

X

DE Y

X

VID = VA – V

B

VID ≥ 100 mV

–100 MV < VID < 100 mV

VID ≤ –100 mV

Open

RE

R

L

Open

Z

L

L

L

H

H

?

L

H

Z

Z

LL

HHHH

L

H

Z

L

HHL

H = high level, L = low level, Z = high impedance,

X = don’t care

H = high level, L = low level, Z = high impedance,

X = don’t care

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

equivalent input and output schematic diagrams

300 kΩ

50 Ω

V

CC

7 V

D or RE

Input

300 kΩ

50 Ω

V

CC

7 V

DE

Input

5 Ω

10 kΩ

7 V

Y or Z

Output

V

CC

7 V

V

CC

7 V

R Output

V

CC

5 Ω

B InputA Input

300 kΩ300 kΩ

7 V

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range, VCC (see Note 1) –0.5 V to 4 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range (D, R, DE, RE) –0.5 V to 6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range (Y, Z, A, and B) –0.5 V to 4 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Electrostatic discharge: Y, Z, A, B , and GND (see Note 2) CLass 3, A:12 kV, B:600 V. . . . . . . . . . . . . . . . . .

All terminals Class 3, A:7 kV, B:500 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous power dissipation See Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 250°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential I/O bus voltages are with respect to network ground terminal.

2. Tested in accordance with MIL-STD-883C Method 3015.7.

DISSIPATION RATING T ABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

TA = 85°C

POWER RATING

PW 774 mW 6.2 mW/°C 402 mW

recommended operating conditions (see Note 3)

MIN NOM MAX UNIT

Supply voltage, V

CC

2.4 2.7 3.6 V

High-level input voltage, V

IH

2 V

Low-level input voltage, V

IL

0.8 V

Magnitude of differential input voltage, VID 0.1 0.6 V

Common–mode input voltage, VIC (see Figure 8)

0

2.4

*

Ť

V

ID

Ť

2

V

g

IC

(g)

VCC–0.8

Operating free–air temperature, T

A

–40 85 °C

NOTE 3: The common-mode input voltage, VIC, is not fully 644 compliant when VCC = 2.4 V.

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

device electrical characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

Driver and receiver enabled, No receiver load,

Driver RL = 100 Ω

12 20

I

Supply current

Driver enabled, Receiver disabled, RL = 100 Ω

10 16

mA

ICCSu ly current

Driver disabled, Receiver enabled, No load 3 6

mA

Disabled 0.5 1

†

All typical values are at 25°C and with a 2.7-V supply.

driver electrical characteristics over recommended operating conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VOD Differential output voltage magnitude

247 285 454

∆VOD

Change in differential output voltage magnitude between logic

states

R

L

=

100Ω

,

See Fi gure 1 and Figure 2

–50 50

mV

V

OC(SS)

Steady-state common-mode output voltage 1.125 1.375 V

∆V

OC(SS)

Change in steady-state common-mode output voltage between

logic states

See Fi gure 3

–50 50 mV

V

OC(PP)

Peak-to-peak common-mode output voltage 50 150 mV

p

DE

–0.5 –20

IIHHigh-level input current

D

V

IH

=

5 V

2 20

µ

A

p

DE

–0.5 –10

IILLow-level input current

D

V

IL

= 0.8

V

2 20

µ

A

p

VOY or VOZ = 0 V 3 10

IOSShort-circuit output current

VOD = 0 V 3 10

mA

p

p

VOD = 600 mV ±1

IOZHigh-impedance output current

VO = 0 V or V

CC

±1

µ

A

I

O(OFF)

Power-off output current VCC = 0 V, VO = 3.6 V ±1 µA

C

IN

Input capacitance 3 pF

receiver electrical characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

V

ITH+

Positive-going differential input voltage threshold

100

V

ITH–

Negative-going differential input voltage threshold

See Figure 5

–100

mV

V

OH

High-level output voltage IOH = –8 mA 2 V

V

OL

Low-level output voltage IOL = 8 mA 0.4 V

p

p

VI = 0 –2 –20

IIInput current (A or B inputs)

VI = 2.4 V –1.2

µ

A

I

I(OFF)

Power-off input current (A or B inputs) VCC = 0 ±20 µA

I

IH

High-level input current (enables) VIH = 5 V ±10 µA

I

IL

Low-level input current (enables) VIL = 0.8 V ±10 µA

I

OZ

High-impedance output current VO = 0 or 5 V ±10 µA

†

All typical values are at 25°C and with a 2.7-V supply.

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

driver switching characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

t

PLH

Propagation delay time, low-to-high-level output 1.7 2.7 ns

t

PHL

Propagation delay time, high-to-low-level output 1.7 3 ns

t

r

Differential output signal rise time

RL = 100Ω,

p

0.8 1 ns

t

f

Differential output signal fall time

C

L

= 10 pF,

See

Figure 2

0.8 1 ns

t

sk(p)

Pulse skew (|t

pHL

– t

pLH

|)

See Figure 2

300 ps

t

sk(o)

Channel-to-channel output skew

‡

150 ps

t

PZH

Propagation delay time, high-impedance-to-high-level output 7.8 10 ns

t

PZL

Propagation delay time, high-impedance-to-low-level output

7.3 10 ns

t

PHZ

Propagation delay time, high-level-to-high-impedance output

See Figure 4

5.2 10 ns

t

pLZ

Propagation delay time, low-level-to-high-impedance output 6.6 10 ns

†

All typical values are at 25°C and with a 2.7-V supply.

‡

t

sk(o)

is the maximum delay time difference between drivers on the same device.

receiver switching characteristics over recommended operating conditions (unless otherwise

noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

t

PLH

Propagation delay time, low-to-high-level output 3.7 5.2 ns

t

PHL

Propagation delay time, high-to-low-level output

3.7 4.5 ns

t

sk(p)

Pulse skew (|t

pHL

– t

pLH

|)

CL = 10 pF,

0.3 ns

t

r

Output signal rise time

See Figure 6

0.8 1.5 ns

t

f

Output signal fall time 0.8 1.5 ns

t

PZH

Propagation delay time, high-level-to-high-impedance output 5.4 ns

t

PZL

Propagation delay time, low-level-to-low-impedance output

6.3 ns

t

PHZ

Propagation delay time, high-impedance-to-high-level output

See Figure 7

6.1 ns

t

PLZ

Propagation delay time, low-impedance-to-high-level output 6.9 ns

†

All typical values are at 25°C and with a 2.7-V supply.

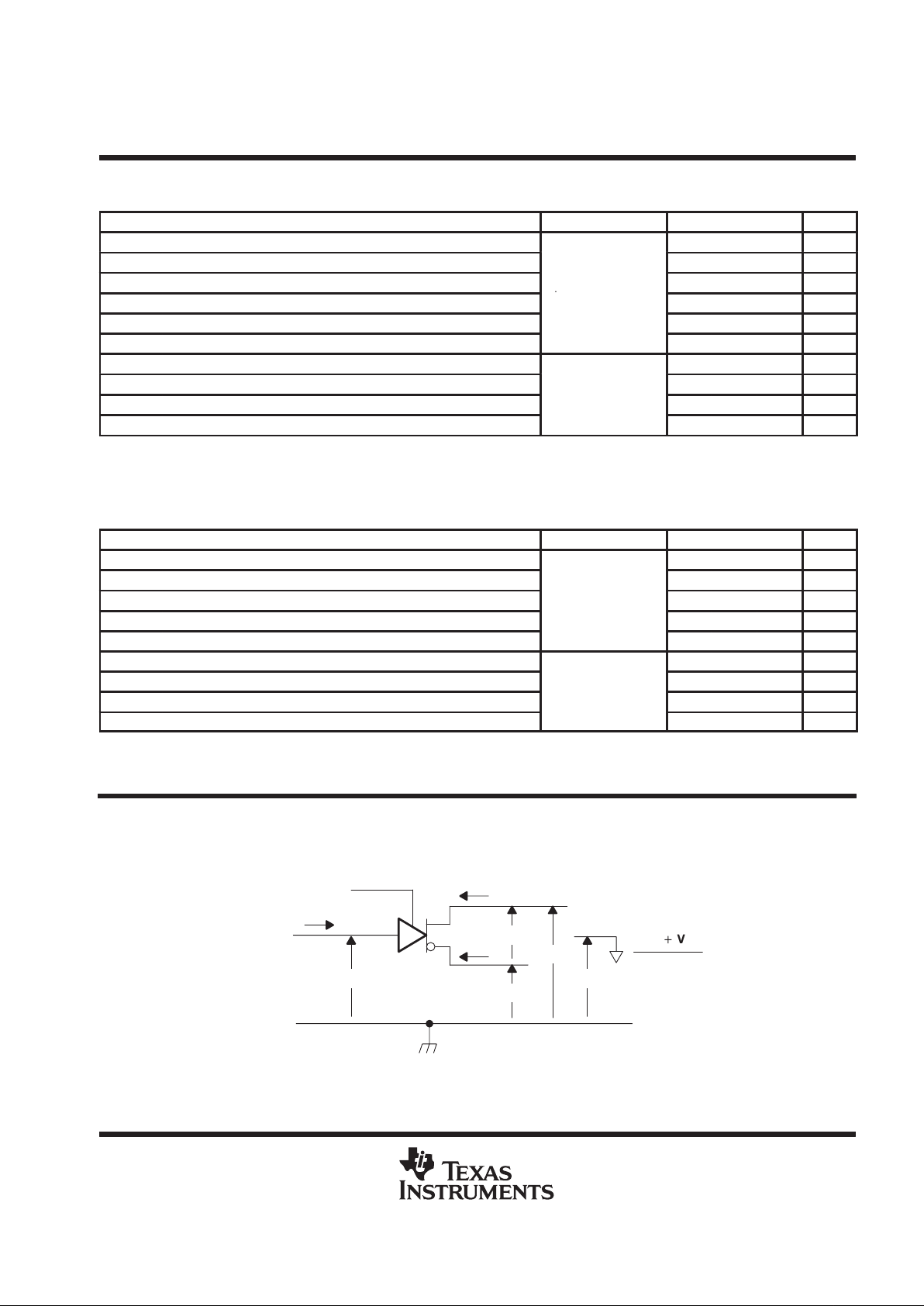

PARAMETER MEASUREMENT INFORMATION

driver

V

OD

V

OZ

V

OY

V

OC

V

I

I

OY

I

OZ

I

I

A

Z

Y

VOY)

V

OZ

2

Driver Enable

Figure 1. Driver Voltage and Current Definitions

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

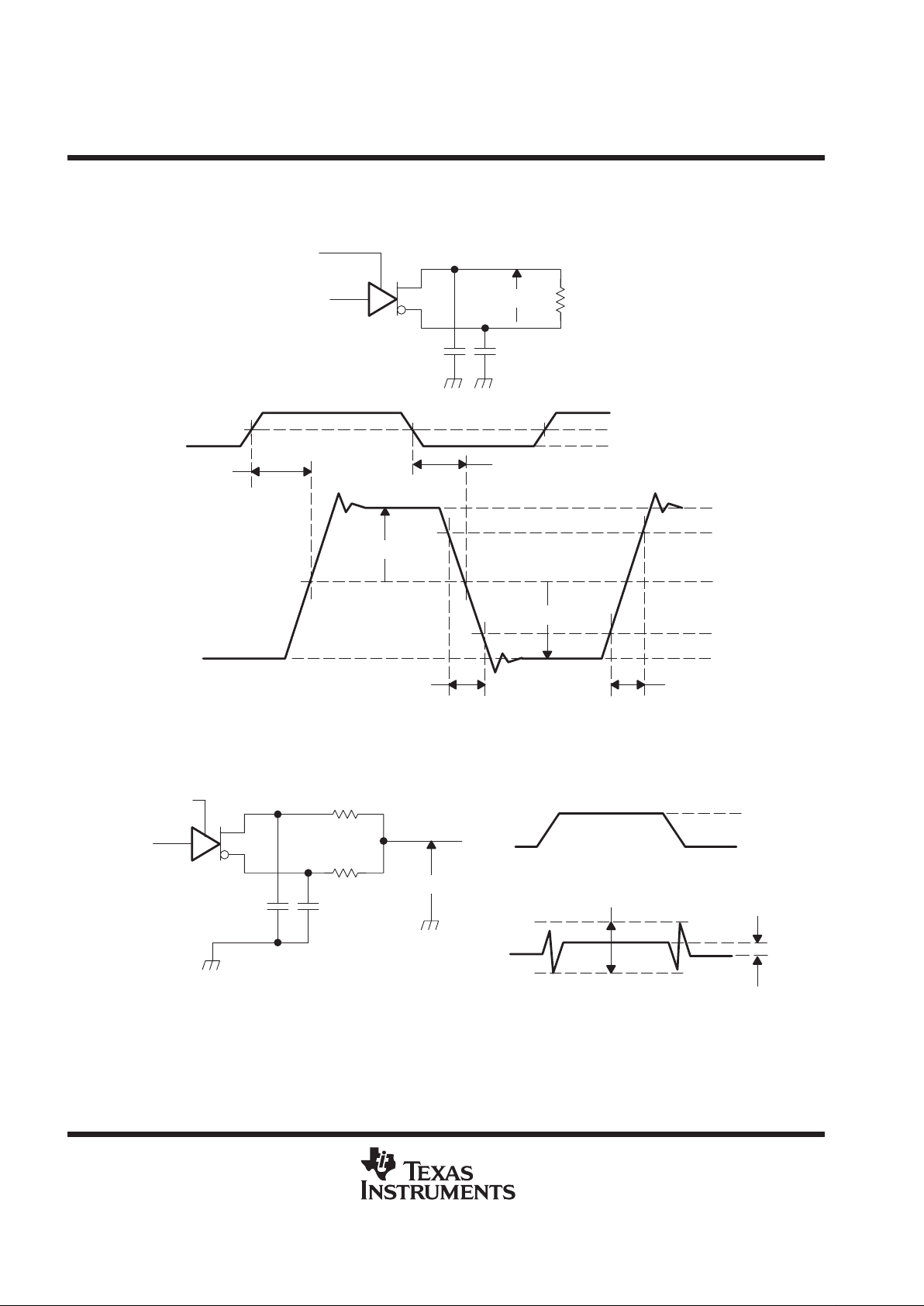

PARAMETER MEASUREMENT INFORMATION

driver (continued)

2 V

1.4 V

0.8 V

100%

80%

20%

0%

0 V

V

OD(H)

V

OD(L)

Output

Input

V

OD

Z

Y

Input

100 Ω

±1%

CL = 10 pF

(2 Places)

t

PHL

t

PLH

t

f

t

r

Driver Enable

NOTE A: All input pulses are supplied by a generator having the following characteristics: tr or tf ≤ 1 ns, pulse repetition rate (PRR) = 50 Mpps,

pulse width = 10 ± 0.2 ns . CL includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 2. Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

V

OC

Z

Y

Input

CL = 10 pF

(2 Places)

3 V

0 V

V

OC(PP)

V

OC(SS)

V

OC

49.9 Ω, ±1% (2 Places)

Driver Enable

NOTE A: All input pulses are supplied by a generator having the following characteristics: tr or tf ≤ 1 ns, pulse repetition rate (PRR) = 50 Mpps,

pulse width = 10 ± 0.2 ns . CL includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T . The measurement of V

OC(PP)

is made on test equipment with a –3 dB bandwidth of at least 300 MHz.

Figure 3. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

driver (continued)

1.2 V

Z

Y

0.8 V or 2 V

49.9 Ω, ±1% (2 Places)

CL = 10 pF

(2 Places)

DE

VOYV

OZ

2 V

0.8 V

t

PHZ

t

PZH

t

PLZ

t

PZL

1.4 V

~1.4 V

1.2 V

1.25 V

1.2 V

~1 V

1.15 V

DE

VOY or V

OZ

VOZ or V

OY

D at 2 V and input to DE

D at 0.8 V and input to DE

NOTE A: All input pulses are supplied by a generator having the following characteristics: tr or tf ≤ 1 ns, pulse repetition rate (PRR) = 0.5 Mpps,

pulse width = 500 ± 10 ns . CL includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 4. Enable and Disable Time Circuit and Definitions

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

receiver

V

IB

V

ID

V

IA

V

IC

V

O

A

B

R

VIA)

V

IB

2

Figure 5. Receiver Voltage Definitions

Table 1. Receiver Minimum and Maximum Input Threshold Test Voltages

APPLIED VOLTAGES

(V)

RESULTING DIFFERENTIAL

INPUT VOLTAGE

(mV)

RESULTING COMMON-

MODE INPUT VOLTAGE

(V)

V

IA

V

IB

V

ID

V

IC

1.25 1.15 100 1.2

1.15 1.25 –100 1.2

2.4 2.3 100 2.35

2.3 2.4 –100 2.35

0.1 0 100 0.05

0 0.1 –100 0.05

1.5 0.9 600 1.2

0.9 1.5 –600 1.2

2.4 1.8 600 2.1

1.8 2.4 –600 2.1

0.6 0 600 0.3

0 0.6 –600 0.3

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

receiver (continued)

V

IB

V

ID

V

IA

V

O

C

L

10 pF

V

OH

V

OL

1.4 V

V

O

V

IA

V

IB

V

ID

1.4 V

1 V

0.4 V

0 V

–0.4 V

t

PHL

t

PLH

t

r

t

f

0.4 V

2.4 V

NOTE A: All input pulses are supplied by a generator having the following characteristics: tr or tf ≤ 1 ns, pulse repetition rate (PRR) = 50 Mpps,

pulse width = 10 ± 0.2 ns. CL includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

Figure 6. Timing Test Circuit and Waveforms

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

receiver (continued)

V

O

C

L

10 pF

+

–

500 Ω

1.2 V

B

A

RE

Inputs

V

TEST

NOTE A: All input pulses are supplied by a generator having the following characteristics: tr or tf ≤ 1 ns, pulse repetition rate (PRR) = 0.5 Mpps,

pulse width = 500 ± 10 ns. CL includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

t

PZL

V

TEST

A

t

PZL

t

PLZ

2.5 V

1.4 V

VOL +0.5 V

V

OL

2 V

1.4 V

0.8 V

2.5 V

1 V

RE

R

t

PZH

V

TEST

A

t

PZH

t

PHZ

V

OH

1.4 V

VOH –0.5 V

0 V

2 V

1.4 V

0.8 V

0 V

1.4 V

RE

R

Figure 7. Enable/Disable Time Test Circuit and Waveforms

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

|VID|– Differential Input Voltage – V

1

0

0.1 0.3

2

1.5

0.5

0.2 0.4 0.6

2.5

0

0.5

– Common-Mode Input Voltage – V

V

IC

MIN

RECEIVER

COMMON-MODE INPUT VOLTAGE

vs

DIFFERENTIAL INPUT VOLTAGE

3

0.7 0.8

VCC = 3.6 V

VCC = 2.7 V

VCC = 2.4 V

Figure 8

Figure 9

0

DRIVER

LOW-LEVEL OUTPUT VOLTAGE

vs

LOW-LEVEL OUTPUT CURRENT

IOL – Low-Level Output Current – mA

4

3

0

4

2

2

1

V

OL

– Low-Level Output Voltage – V

VCC = 2.4 V

TA = 25°C

13

Figure 10

–4

DRIVER

HIGH-LEVEL OUTPUT VOLTAGE

vs

HIGH-LEVEL OUTPUT CURRENT

IOH – High-Level Output Current – mA

3.5

2.5

0

–2 0

1.5

–3

0.5

V

OH

– High-Level Output Voltage – V

–1

3

2

1

VCC = 2.4 V

TA = 25°C

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

Figure 11

0

RECEIVER

LOW-LEVEL OUTPUT VOLTAGE

vs

LOW-LEVEL OUTPUT CURRENT

IOL – Low-Level Output Current – mA

0

2

10

V

OL

20 30

3

1

– Low-Level Output Votlage – V

40

VCC = 2.4 V

TA = 25°C

Figure 12

–50

RECEIVER

HIGH-LEVEL OUTPUT VOLTAGE

vs

HIGH-LEVEL OUTPUT CURRENT

IOH – High-Level Output Current – mA

0

–10

2

–40

V

OH

–30 –20

3

1

– High-Level Output Voltage – V

VCC = 2.4 V

TA = 25°C

0

Figure 13

–50

DRIVER

HIGH-TO-LOW LEVEL PROPAGATION DELAY TIME

vs

FREE-AIR TEMPERATURE

TA – Free-Air Temperature – °C

2.5

1.5

50 90

2

–10

t

PLH – High-To-Low Propagation Delay Time – ns

–30

30 70

10

VCC = 3.6 V

VCC = 3.3 V

VCC = 2.7 V

Figure 14

–50

DRIVER

LOW-TO-HIGH LEVEL PROPAGATION DELAY TIME

vs

FREE-AIR TEMPERATURE

TA – Free-Air Temperature – °C

2.5

1.5

50 90

2

–10

t

PLH – Low-To-High Propagation Delay T ime – ns

–30

30 70

10

VCC = 3.6 V

VCC = 3.3 V

VCC = 2.7 V

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

Figure 15

–50

RECEIVER

HIGH-TO-LOW LEVEL PROPAGATION DELAY TIME

vs

FREE-AIR TEMPERATURE

TA – Free–Air Temperature – °C

4.5

2.5

50 90

3.5

–10

t

PLH

–30

30 70

10

VCC = 3.6 V

VCC = 2.7 V

4

3

VCC = 3.3 V

– High-To-Low Level Propagation Dealy T ime – ns

Figure 16

–50

RECEIVER

LOW-TO-HIGH LEVEL PROPAGATION DELAY TIME

vs

FREE–AIR TEMPERATURE

TA – Free-Air Temperature – °C

4.5

2.5

50 90

3.5

–10

t

PLH – Low-To-High Level Propagation Delay T ime – ns

–30

30 70

10

VCC = 3.6 V

VCC = 2.7 V

4

3

VCC = 3.3 V

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

The devices are generally used as building blocks for high-speed point-to-point data transmission. Ground

differences are less than 1 V with a low common–mode output and balanced interface for very low noise emissions.

Devices can interoperate with RS-422, PECL, and IEEE-P1596. Drivers/Receivers maintain ECL speeds without the

power and dual supply requirements.

10

0.1

1M

Data Rate – Hz

1

100k 10M 100M

100

Transmission Distance – m

1000

5% Jitter

30% Jitter

24 AWG UTP 96 Ω (PVC Dielectric)

Figure 17. Data Transmission Distance Versus Rate

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

15

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

APPLICATION INFORMATION

fail safe

One of the most common problems with differential signaling applications is how the system responds when

no differential voltage is present on the signal pair . The LVDS receiver is like most differential line receivers, in

that its output logic state can be indeterminate when the differential input voltage is between –100 mV and

100 mV and within its recommended input common-mode voltage range. TI’s L VDS receiver is different in how

it handles the open-input circuit situation, however.

Open-circuit means that there is little or no input current to the receiver from the data line itself. This could be

when the driver is in a high-impedance state or the cable is disconnected. When this occurs, the L VDS receiver

will pull each line of the signal pair to near V

CC

through 300-kΩ resistors as shown in Figure 1 1. The fail-safe

feature uses an AND gate with input voltage thresholds at about 2.3 V to detect this condition and force the

output to a high-level, regardless of the differential input voltage.

R

t

100 Ω Typ

300 kΩ 300 kΩ

V

CC

VIT ≈ 2.3 V

A

B

Y

Figure 18. Open-Circuit Fail Safe of the LVDS Receiver

It is only under these conditions that the output of the receiver will be valid with less than a 100-mV differential

input voltage magnitude. The presence of the termination resistor, Rt, does not af fect the fail-safe function as

long as it is connected as shown in the figure. Other termination circuits may allow a dc current to ground that

could defeat the pullup currents from the receiver and the fail-safe feature.

SN65LVDS1050

HIGH-SPEED DIFFERENTIAL LINE DRIVERS AND RECEIVERS

SLLS343A – APRIL 1999 – REVISED MARCH 2000

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MECHANICAL DATA

PW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

14 PINS SHOWN

0,65

M

0,10

0,10

0,25

0,50

0,75

0,15 NOM

Gage Plane

28

9,80

9,60

24

7,90

7,70

2016

6,60

6,40

4040064/F 01/97

0,30

6,60

6,20

8

0,19

4,30

4,50

7

0,15

14

A

1

1,20 MAX

14

5,10

4,90

8

3,10

2,90

A MAX

A MIN

DIM

PINS **

0,05

4,90

5,10

Seating Plane

0°–8°

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

Loading...

Loading...