Texas Instruments SN54HC191J, SN74HC191D, SN74HC191DR, SN74HC191N, SN74HC191N3 Datasheet

...

SN54HC191, SN74HC191

4-BIT SYNCHRONOUS UP/DOWN BINARY COUNTERS

SCLS121B – DECEMBER 1982 – REVISED MA Y 1997

D

Single Down/Up Count-Control Line

D

Look-Ahead Circuitry Enhances Speed of

Cascaded Counters

D

Fully Synchronous in Count Modes

D

Asynchronously Presettable With Load

Control

D

Package Options Include Plastic

Small-Outline (D) and Ceramic Flat (W)

Packages, Ceramic Chip Carriers (FK), and

Standard Plastic (N) and Ceramic (J)

300-mil DIPs

description

The ’HC191 are 4-bit synchronous, reversible,

up/down binary counters. Synchronous counting

operation is provided by having all flip-flops

clocked simultaneously so that the outputs

change coincident with each other when

instructed by the steering logic. This mode of

operation eliminates the output counting spikes

normally associated with asynchronous (rippleclock) counters.

The outputs of the four flip-flops are triggered on

a low-to-high-level transition of the clock (CLK)

input if the count-enable (CTEN) input is low. A

high at CTEN inhibits counting. The direction of

the count is determined by the level of the

down/up (D/U

counts up, and when D/U is high, it counts down.

) input. When D/U is low, the counter

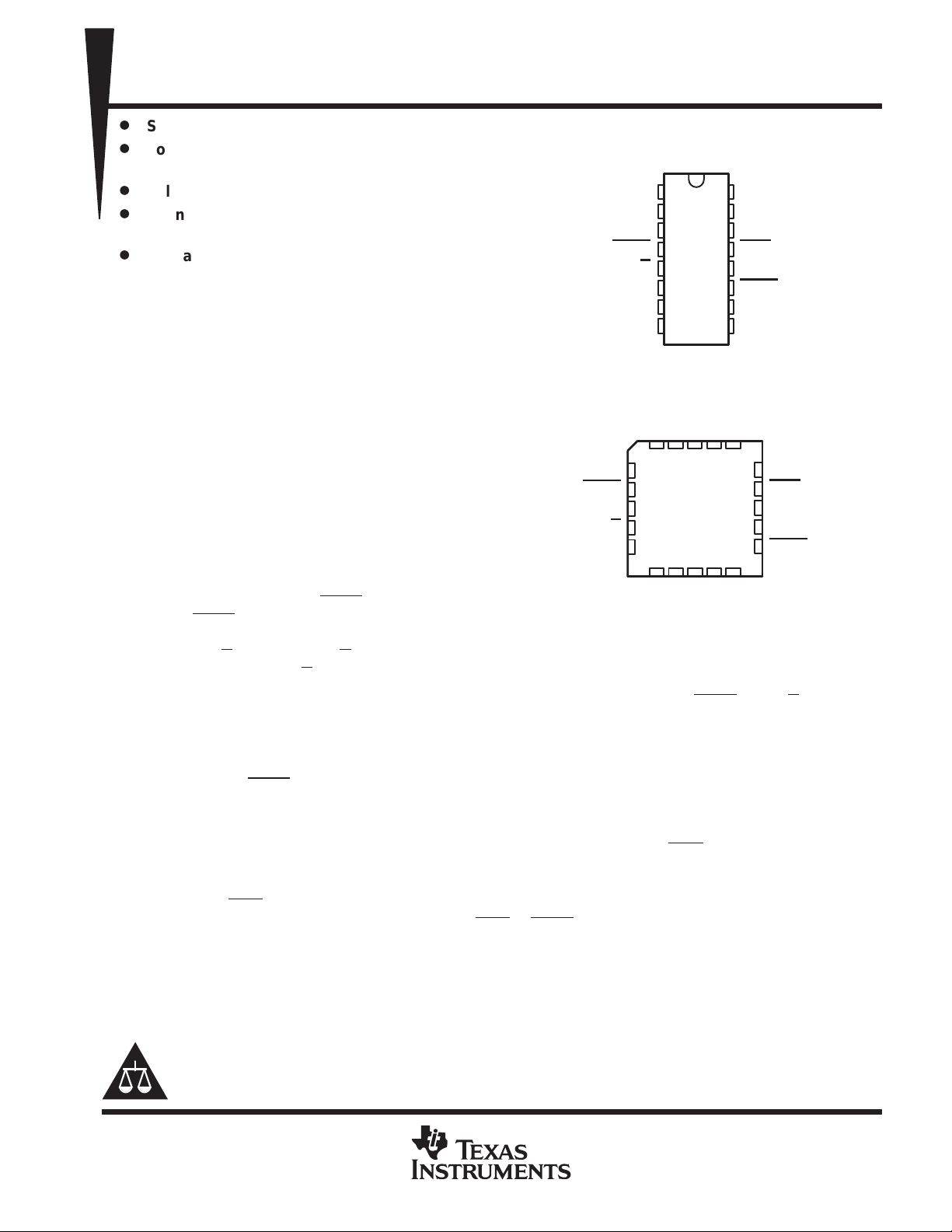

SN54HC191 ...J OR W PACKAGE

SN74HC191 . . . D OR N PACKAGE

CTEN

SN54HC191 . . . FK PACKAGE

Q

A

CTEN

NC

D/U

Q

C

NC – No internal connection

(TOP VIEW)

B

1

Q

2

B

Q

3

A

4

5

D/U

6

Q

C

7

Q

D

GND

8

(TOP VIEW)

B

QBNC

3212019

4

5

6

7

8

910111213

D

Q

GND

NC

16

15

14

13

12

11

10

9

CC

V

D

V

CC

A

CLK

RCO

MAX/MIN

LOAD

C

D

A

18

17

16

15

14

C

CLK

RCO

NC

MAX/MIN

LOAD

These counters feature a fully independent clock circuit. Change at the control (CTEN

and D/U) inputs that

modifies the operating mode have no effect on the contents of the counter until clocking occurs. The function

of the counter is dictated solely by the condition meeting the stable setup and hold times.

These counters are fully programmable; that is, each of the outputs can be preset to either level by placing a

low on the load (LOAD) input and entering the desired data at the data inputs. The output changes to agree with

the data inputs independently of the level of CLK. This feature allows the counters to be used as modulo-N

dividers by simply modifying the count length with the preset inputs.

Two outputs are available to perform the cascading function: ripple clock (RCO) and maximum/minimum

(MAX/MIN) count. MAX/MIN produces a high-level output pulse with a duration approximately equal to one

complete cycle of the clock while the count is zero (all outputs low) counting down, or maximum (9 or 15)

counting up. RCO

produces a low-level output pulse under those same conditions, but only while CLK is low.

The counters can be easily cascaded by feeding RCO to CTEN of the succeeding counter if parallel clocking

is used, or to CLK if parallel enabling is used. MAX/MIN can be used to accomplish look ahead for high-speed

operation.

The SN54HC191 is characterized for operation over the full military temperature range of –55°C to 125°C. The

SN74HC191 is characterized for operation from –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1997, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

1

SN54HC191, SN74HC191

4-BIT SYNCHRONOUS UP/DOWN BINARY COUNTERS

SCLS121B – DECEMBER 1982 – REVISED MA Y 1997

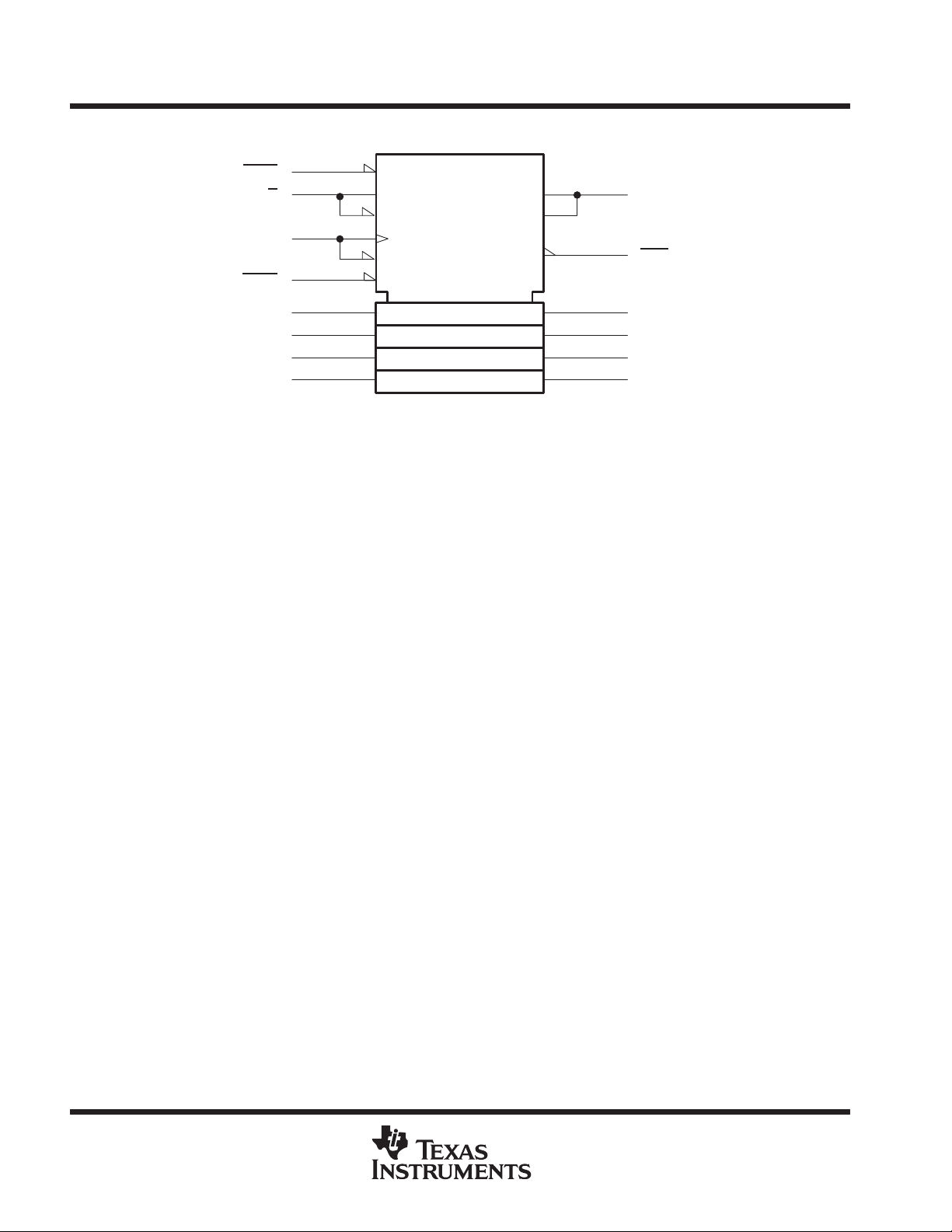

logic symbol

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, N, and W packages.

†

CTEN

D/U

CLK

LOAD

4

5

14

11

15

A

1

B

10

C

9

D

G1

M2 [DOWN]

M3 [UP]

G4

C5

5D

CTRDIV16

2(CT=0) Z6

3(CT=15) Z6

1,2–/1,3+

6,1,4

[1]

[2]

[4]

[8]

12

13

3

2

6

7

MAX/MIN

RCO

Q

A

Q

B

Q

C

Q

D

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

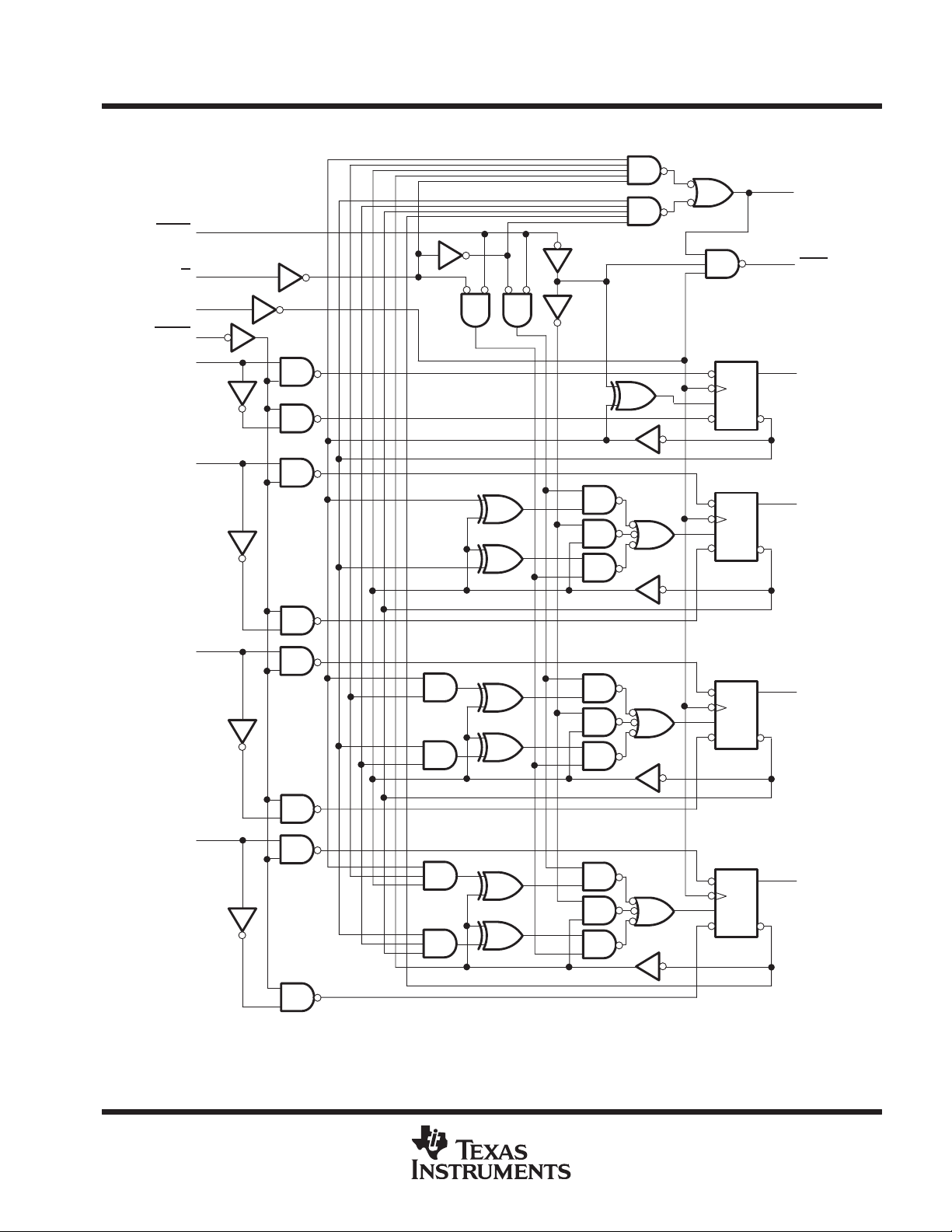

logic diagram (positive logic)

SN54HC191, SN74HC191

4-BIT SYNCHRONOUS UP/DOWN BINARY COUNTERS

SCLS121B – DECEMBER 1982 – REVISED MA Y 1997

12

MAX/MIN

CTEN

D/U

CLK

LOAD

4

13

5

14

11

15

A

1

B

10

C

S

C1

1D

R

S

C1

1D

R

RCO

3

Q

A

2

Q

B

9

D

Pin numbers shown are for the D, J, N, and W packages.

S

1D

R

S

1D

R

C1

C1

6

Q

C

7

Q

D

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Loading...

Loading...